(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-22900

(P2004-22900A)

(43) 公開日 平成16年1月22日(2004.1.22)

(51) Int.Cl.<sup>7</sup>

**H01L 21/20**

**G02F 1/1368**

**H01L 21/322**

**H01L 21/336**

**H01L 29/786**

F 1

H01L 21/20

G02F 1/1368

H01L 21/322

H01L 21/322

H01L 29/786

テーマコード(参考)

2 H092

5 F052

5 F110

審査請求 未請求 請求項の数 8 O L (全 28 頁) 最終頁に続く

(21) 出願番号

特願2002-177450 (P2002-177450)

(22) 出願日

平成14年6月18日 (2002. 6. 18)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 桑原 秀明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 中村 理

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 梶原 誠之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【要約】

【課題】半導体膜の結晶化を助長する金属元素を用いて結晶構造を有する半導体膜を得た後、該膜中に残存する当該金属元素を効果的に除去し、素子間のバラツキを低減する技術を提供することを課題とする。

【解決手段】ゲッタリングサイトを形成する工程として、非晶質構造を有する半導体膜、代表的にはアモルファスシリコン膜を形成した後、化合物イオン、代表的にはフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を添加した後、加熱処理してゲッタリングを行うものである。また、プラズマCVD法を用い、成膜段階でフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を含むゲッタリングサイトを形成してもよい。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

絶縁表面上に非晶質構造を有する第1の半導体膜を形成する第1工程と、

前記非晶質構造を有する第1の半導体膜に金属元素を添加する第2工程と、

前記第1の半導体膜を結晶化させて結晶構造を有する第1の半導体膜を形成する第3工程と、

前記結晶構造を有する第1の半導体膜上にバリア層を形成する第4の工程と、

前記バリア層上に第2の半導体膜を形成する第5工程と、

前記第2の半導体膜にハロゲン元素またはハロゲン元素を含む化合物を添加する第6工程と、

加熱処理を行って前記第2の半導体膜に前記金属元素をゲッタリングして結晶構造を有する第1の半導体膜中の前記金属元素を除去または低減する第7工程と、

前記第2の半導体膜を除去する第8工程と、

前記バリア層を除去する第9工程とを有することを特徴とする半導体装置の作製方法。

**【請求項 2】**

請求項1において、前記バリア層は、膜厚1nm～10nmの酸化シリコン膜または酸化窒化シリコン膜であることを特徴とする半導体装置の作製方法。

**【請求項 3】**

非晶質構造を有する半導体膜に金属元素を添加する第1工程と、

前記半導体膜を結晶化させて結晶構造を有する半導体膜を形成する第2工程と、

前記結晶構造を有する半導体膜に、ハロゲン元素またはハロゲン元素を含む化合物を選択的に添加して不純物領域を形成する第3工程と、

前記不純物領域に前記金属元素をゲッタリングして結晶構造を有する半導体膜中の前記金属元素を選択的に除去または低減する第4工程とを有することを特徴とする半導体装置の作製方法。

**【請求項 4】**

請求項1乃至3のいずれか一において、前記ハロゲン元素は、F、Cl、I、Brから選ばれた1種または複数種であり、前記ハロゲン元素を含む化合物は、それらの窒素化合物、または炭素化合物であることを特徴とする半導体装置の作製方法。

**【請求項 5】**

絶縁表面上に非晶質構造を有する第1の半導体膜を形成する第1工程と、

前記非晶質構造を有する第1の半導体膜に金属元素を添加する第2工程と、

前記第1の半導体膜を結晶化させて結晶構造を有する第1の半導体膜を形成する第3工程と、

前記結晶構造を有する第1の半導体膜上にバリア層を形成する第4の工程と、

前記バリア層上にフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を含む第2の半導体膜を形成する第5工程と、

加熱処理を行って前記第2の半導体膜に前記金属元素をゲッタリングして結晶構造を有する第1の半導体膜中の前記金属元素を除去または低減する第6工程と、

前記第2の半導体膜を除去する第7工程と、

前記バリア層を除去する第8工程とを有することを特徴とする半導体装置の作製方法。

**【請求項 6】**

請求項5において、前記第5工程は、プラズマCVD法であることを特徴とする半導体装置の作製方法。

**【請求項 7】**

請求項5において、前記第5工程は、スパッタ法で形成した半導体膜にフッ素化合物、炭素化合物、窒素化合物、または酸素化合物をドーピングすることを特徴とする半導体装置の作製方法。

**【請求項 8】**

請求項1乃至7のいずれか一において、前記金属元素はFe、Ni、Co、Ru、Rh、

10

20

30

40

50

Pd、Os、Ir、Pt、Cu、Auから選ばれた一種または複数種であることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明はゲッタリング技術を用いた半導体装置の作製方法に関する。特に本発明は、半導体膜の結晶化を助長する金属元素を添加して作製される結晶構造を有する半導体膜を用いた半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。 10

【0003】

【従来の技術】

結晶構造を有する半導体膜を用いた代表的な半導体素子として薄膜トランジスタ（以下、TFTと記す）が知られている。TFTはガラスなどの絶縁基板上に集積回路を形成する技術として注目され、駆動回路一体型液晶表示装置などが実用化されつつある。従来の技術において、結晶構造を有する半導体膜は、プラズマCVD法や減圧CVD法で堆積した非晶質半導体膜を、加熱処理やレーザーアニール法（レーザー光の照射により半導体膜を結晶化させる技術）により作製されている。

【0004】

こうして作製される結晶構造を有する半導体膜は多数の結晶粒の集合体であり、その結晶方位は任意な方向に配向して制御不能であるため、TFTの特性を制限する要因となっている。このような問題点に対し、特開平7-183540号公報で開示される技術は、ニッケルなど半導体膜の結晶化を助長する金属元素を添加し、結晶構造を有する半導体膜を作製するものであり、結晶化に必要とする加熱温度を低下させる効果ばかりでなく、結晶方位の配向性を單一方向に高めることが可能である。このような結晶構造を有する半導体膜でTFTを形成すると、電界効果移動度の向上のみでなく、サブスレッシュルド係数（S値）が小さくなり、飛躍的に電気的特性を向上させることができている。 20

【0005】

結晶化を助長する金属元素を用いることによって、結晶化における核発生が制御可能となるため、核発生がランダムである他の結晶化方法に比べて得られる膜質は均一であり、理想的には、完全に金属元素を除去または許容範囲までに低減することが望ましい。しかし、結晶化を助長する金属元素を添加する故に、結晶構造を有する半導体膜の膜中或いは膜表面には、当該金属元素が残存し、得られる素子の特性をばらつかせるなどの問題がある。その一例は、TFTにおいてオフ電流が増加し、個々の素子間でばらつくなどの問題がある。即ち、結晶化を助長する金属元素は、一旦、結晶構造を有する半導体膜が形成されてしまえば、かえって不要な存在となってしまう。 30

【0006】

リンを用いたゲッタリングは、結晶構造を有する半導体膜のうち特定の領域から結晶化を助長する金属元素を除去する手法として有効に活用されている。例えば、TFTのソース・ドレイン領域にリンを添加して450~700の熱処理を行うことで、チャネル形成領域から当該金属元素を容易に除去することが可能である。 40

【0007】

【発明が解決しようとする課題】

リンはイオンドープ法（PH<sub>3</sub>などをプラズマで解離して、イオンを電界で加速して半導体中に注入する方法であり、基本的にイオンの質量分離を行わない方法を指す）で結晶構造を有する半導体膜に注入するが、ゲッタリングのために必要なリン濃度は $1 \times 10^{20}$ /cm<sup>3</sup>以上である。イオンドープ法によるリンの添加は、結晶構造を有する半導体膜の非晶質化をもたらすが、リン濃度の増加はその後のアニールによる再結晶化の妨げとなり問題となっている。また、高濃度のリンの添加は、ドーピングに必要な処理時間の増大を 50

もたらし、ドーピング工程におけるスループットを低下させてるので問題となっている。

【0008】

さらに、pチャネル型TFTのソース・ドレイン領域に添加したリンに対し、その導電型を反転させるために必要な硼素の濃度は1.5~3倍が必要であり、再結晶化の困難さに伴って、ソース・ドレイン領域の高抵抗化をもたらし問題となっている。

【0009】

また、基板内でゲッタリングが十分にされず、ゲッタリングにバラツキが生じると、各々のTFT特性に若干の差、即ちバラツキが生じていた。透過型の液晶表示装置の場合、画素部に配置されるTFTに電気特性のバラツキがあれば、各画素電極に印加する電圧のバラツキが生じ、そのため透過光量のバラツキも生じ、これが表示むらとなって観察者の目に映ることになる。10

【0010】

また、OLEDを用いた発光装置にとって、TFTはアクティブマトリクス駆動方式を実現する上で、必須の素子となっている。従って、OLEDを用いた発光装置は、少なくとも、スイッチング素子として機能するTFTと、OLEDに電流を供給するTFTとが、各画素に設けられることになる。画素の回路構成、及び駆動方法によらず、OLEDと電気的に接続され、且つ、OLEDに電流を供給するTFTのオン電流( $I_{on}$ )で画素の輝度が決定されるため、例えば、全面白表示とした場合、オン電流が一定でなければ輝度にバラツキが生じてしまうという問題がある。

【0011】

本発明はこのような問題を解決するための手段であり、半導体膜の結晶化を助長する金属元素を用いて結晶構造を有する半導体膜を得た後、該膜中に残存する当該金属元素を効果的に除去する技術を提供することを目的とする。20

【0012】

【課題を解決するための手段】

ゲッタリング技術は単結晶シリコンウエハーを用いる集積回路の製造技術において主要な技術として位置付けられている。ゲッタリングは半導体中に取り込まれた金属不純物が、何らかのエネルギーでゲッタリングサイトに偏析して、素子の能動領域の不純物濃度を低減させる技術として知られている。それは、エクストリンシックゲッタリング(Extrinsic Gettering)とイントリンシックゲッタリング(Intrinsic Gettering)の二つに大別されている。エクストリンシックゲッタリングは外部から歪場や化学作用を与えてゲッタリング効果をもたらすものである。高濃度のリンを単結晶シリコンウエハーの裏面から拡散させるリンゲッタはこれに当たり、前述のリンを用いたゲッタリングもエクストリンシックゲッタリングの一種と見なすことができる。30

【0013】

一方、イントリンシックゲッタリングは単結晶シリコンウエハーの内部に生成された酸素が関与する格子欠陥の歪場を利用したものとして知られている。本発明は、上記したエクストリンシックゲッタリングやイントリンシックゲッタリングとは異なるゲッタリングのメカニズムを利用して、厚さ10~200nm程度の結晶構造を有する半導体膜に適用するために以下の手段を採用するものである。40

【0014】

本発明は、絶縁表面を有する基板上に金属元素を用いて結晶構造を有する第1の半導体膜を形成する工程と、エッティングストッパーとなる膜(バリア層)を形成する工程と、化合物(ハロゲン元素を含む化合物、炭素化合物、窒素化合物、または酸素化合物)を含む第2の半導体膜(ゲッタリングサイト)を形成する工程と、ゲッタリングサイトに金属元素をゲッタリングさせる工程と、前記第2の半導体膜を除去する工程と、バリア層を除去する工程とを有している。本発明により結晶構造を有する第1の半導体膜中に存在している金属元素を可能な限り低減または除去することができる。

【0015】

また、上記化合物(ハロゲン元素を含む化合物、炭素化合物、窒素化合物、または酸素化

10

20

30

40

50

合物)を含む第2の半導体膜は、第2の半導体膜の成膜後にドーピングを行ってもよいし、第2の半導体膜の成膜時にこれらの化合物を含ませてもよい。なお、上記第2の半導体膜は、非晶質構造を有する半導体膜、または結晶構造を有する半導体膜である。

#### 【0016】

本発明では、ゲッタリングサイトとなる第2の半導体膜に元素単体を添加するのではなく、化合物を添加することによって、より多くの未結合手を形成することを特徴としている。また、化合物を添加する場合、膜厚方向に深く注入しにくく、表面付近に選択的に添加させることができるために、活性層となる第1の半導体膜に影響を与えない。

#### 【0017】

なお、本明細書中において、ドーピング法とは、イオンシャワードーピング法、イオンインプランテーション法、プラズマドーピング法、拡散法、レーザードーピング法などを含む。10

#### 【0018】

ドーピング法により添加するハロゲン元素を含む化合物としては、F、Cl、I、Brなどのハロゲン元素を含む化合物とする。例えば、フッ素化合物としては、CF<sub>4</sub>、NF<sub>3</sub>、SF<sub>6</sub>、BF<sub>3</sub>、SiF<sub>4</sub>などが挙げられる。中でもフッ素と炭素の化合物でもあるCF<sub>4</sub>が好ましく、加熱処理の際、フッ素により酸素の析出が加速され、酸素と炭素の化合物が第2の半導体膜に形成され、強力なゲッタリングシンクとして機能する。

#### 【0019】

また、ドーピング法により添加する炭素化合物としては、CO<sub>2</sub>、CF<sub>4</sub>などが挙げられる。なお、CO<sub>2</sub>は、酸素化合物でもある。20

#### 【0020】

また、これらの化合物を複数選択して適宜添加してもよい。

#### 【0021】

さらに、第2の半導体膜に希ガス元素(Ar、He、Neなど)を添加してもよい。また、希ガス元素を含む第2の半導体膜に上記ドーピングを行えば、さらにゲッタリング効果が得られる。

#### 【0022】

ただし、本発明において、化合物とは、水素化合物は除く。例えば、フォスフィンなどの水素化合物やボロンの水素化合物は除く。水素化合物を添加した場合、水素が深く注入されてしまい、後に行われる熱処理によって水素が拡散し、TFTの電気特性に影響を与えてしまうためである。30

#### 【0023】

また、プラズマCVD法により化合物を含み非晶質構造を有する第2の半導体膜を形成する場合には、SiF<sub>4</sub>を成膜ガスとして用いればよく、得られた膜は、Si-F結合をしており、フッ素原子の局在化電荷による正イオンのゲッタリング性をもつ。また、他の成膜ガスとして、C<sub>2</sub>F<sub>6</sub>、NF<sub>3</sub>などを用い、化合物を含む第2の半導体膜を形成してもよい。加えて、希ガスを加えることによって膜の安定性を高めてもよい。また、プラズマCVD法により化合物を含む第2の半導体膜を形成する場合、ドーピングプロセスが省略され、好ましい。40

#### 【0024】

本明細書で開示する作製方法に関する発明の構成1は、

絶縁表面上に非晶質構造を有する第1の半導体膜を形成する第1工程と、

前記非晶質構造を有する第1の半導体膜に金属元素を添加する第2工程と、

前記第1の半導体膜を結晶化させて結晶構造を有する第1の半導体膜を形成する第3工程と、

前記結晶構造を有する第1の半導体膜上にバリア層を形成する第4の工程と、

前記バリア層上に第2の半導体膜を形成する第5工程と、

前記第2の半導体膜にハロゲン元素またはハロゲン元素を含む化合物を添加する第6工程と、50

加熱処理を行って前記第2の半導体膜に前記金属元素をゲッタリングして結晶構造を有する第1の半導体膜中の前記金属元素を除去または低減する第7工程と、

前記第2の半導体膜を除去する第8工程と、

前記バリア層を除去する第9工程とを有することを特徴とする半導体装置の作製方法である。

## 【0025】

また、上記構成1において、前記バリア層は、膜厚1nm～10nmの酸化シリコン膜、または酸化窒化シリコン膜であることを特徴としている。前記バリア層を形成する工程は、レーザー光の照射により結晶構造を有する半導体膜の表面を酸化した後、さらにオゾンを含む溶液で結晶構造を有する半導体膜の表面を酸化する工程、或いは、オゾンを含む溶液で結晶構造を有する半導体膜の表面を酸化する工程、もしくは酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する工程とすればよい。また、バリア層を形成する他の工程としては、酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する工程（酸素ラジカルを用いて酸化する工程）も挙げられる。また、バリア層を形成する他の工程としては、プラズマCVD法やスパッタ法や蒸着法などで1～10nm程度の酸化シリコン膜または酸化窒化シリコン膜を堆積して形成する工程としても良い。また、バリア層を形成する他の工程としては、クリーンオーブンを用い、200～350程度に加熱して結晶構造を有する半導体膜の表面に薄い酸化膜を形成しても良い。なお、バリア層を形成する他の工程として、上記形成方法のいずれか一の方法、またはそれらの方法を組み合わせて形成してもよい。なお、前記酸化窒化シリコン膜は、成膜室にシラン系ガスと窒素酸化物系ガスを原料ガスとして導入し、プラズマを発生させるプラズマCVD法により形成する。

## 【0026】

また、エッチングストッパーとなる膜（バリア層）を形成する他の工程として、プラズマCVD法を用いて、フッ素を含む薄い酸化窒化シリコン膜（SiONF膜）、またはフッ素を含む薄い酸化シリコン膜（SiOF膜）を形成してもよい。

## 【0027】

また、本明細書で開示する作製方法に関する他の発明の構成2は、

非晶質構造を有する半導体膜に金属元素を添加する第1工程と、

前記半導体膜を結晶化させて結晶構造を有する半導体膜を形成する第2工程と、

前記結晶構造を有する半導体膜に、ハロゲン元素またはハロゲン元素を含む化合物を選択的に添加して不純物領域を形成する第3工程と、

前記不純物領域に前記金属元素をゲッタリングして結晶構造を有する半導体膜中の前記金属元素を選択的に除去または低減する第4工程とを有することを特徴とする半導体装置の作製方法である。

## 【0028】

また、上記各構成において、前記ハロゲン元素は、F、Cl、I、Brから選ばれた1種または複数種であり、前記ハロゲン元素を含む化合物は、それらの窒素化合物、または炭素化合物であることを特徴としている。これらのイオン化合物を半導体膜中に含有させることにより、ダンギリングボンドや格子歪みを形成してゲッタリングサイトを形成することができる。

## 【0029】

また、ゲッタリングサイトとなる第2の半導体膜にハロゲン元素の濃度勾配をもたせ、効率よくゲッタリングさせてもよい。その場合、ドーピング条件、または成膜条件（RFパワー、成膜圧力、ガス流量など）を調節して第2の半導体膜にハロゲン元素の濃度勾配をもたせねばよい。第2の半導体膜にハロゲン元素の濃度勾配をもたせた場合、第2の半導体膜の下層部分にゲッタリングされた金属元素が濃度の高い表面に向かって移動しやすくなり、金属元素のゲッタリング能力が飽和しにくくなる。なお、ゲッタリングの際、ハロゲン元素を含む第2の半導体膜にある量の金属元素がゲッタリングされると、飽和し、それ以上金属元素がゲッタリングされない。

10

20

30

40

50

## 【0030】

また、本明細書で開示する作製方法に関する他の発明の構成3は、

絶縁表面上に非晶質構造を有する第1の半導体膜を形成する第1工程と、

前記非晶質構造を有する第1の半導体膜に金属元素を添加する第2工程と、

前記第1の半導体膜を結晶化させて結晶構造を有する第1の半導体膜を形成する第3工程と、

前記結晶構造を有する第1の半導体膜上にバリア層を形成する第4の工程と、

前記バリア層上にフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を含む第2の半導体膜を形成する第5工程と、

加熱処理を行って前記第2の半導体膜に前記金属元素をゲッタリングして結晶構造を有する第1の半導体膜中の前記金属元素を除去または低減する第6工程と、

前記第2の半導体膜を除去する第7工程と、

前記バリア層を除去する第8工程とを有することを特徴とする半導体装置の作製方法である。

10

## 【0031】

上記各構成において、前記第2の半導体膜は、スパッタ法またはプラズマCVD法により形成すればよい。例えば、プラズマCVD法でフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を含む第2の半導体膜を形成してもよいし、スパッタ法で形成した半導体膜にフッ素化合物、炭素化合物、窒素化合物、または酸素化合物をドーピングしてもよい。

20

## 【0032】

また、上記化合物を含む第2の半導体膜と、バリア層とともにプラズマCVD法により形成することもできる。なお、プラズマCVD法はガスによる成膜室（チャンバーとも呼ぶ）内のクリーニングが行えるため、スパッタ法に比べてメンテナンスが少なくて済み、量産には適した成膜方法である。

## 【0033】

また、上記各構成において、希ガス元素を含む第2の半導体膜と、バリア層を大気に触れさせることなく成膜することが可能であり、さらに同一チャンバーで連続的に成膜することも可能であるため、スループットに優れている。

## 【0034】

また、上記各構成において、金属元素は、Fe、Ni、Co、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選ばれた一種または複数種であることを特徴としている。これらの金属元素を非晶質構造を有する半導体膜に添加すると結晶化が良好に行われる。

30

## 【0035】

本発明により十分に結晶化を助長する金属元素が低減または除去された結晶構造を有する半導体膜を得ることができ、該半導体膜を活性層とするTFTにおいて電気特性の向上、特にオフ電流を低減し、個々の素子間でのバラツキを低減することができる。

## 【0036】

## 【発明の実施の形態】

本発明の実施形態について、以下に説明する。

## 【0037】

## (実施の形態1)

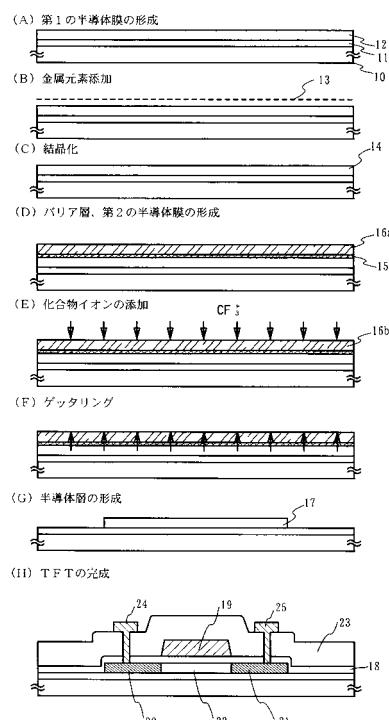

以下に本発明を用いた代表的なTFTの作製手順を簡略に図1を用いて示す。ここではプラズマCVD装置で第2の半導体膜と、該第2の半導体膜上に窒化酸化珪素膜の成膜を行う例を示す。

## 【0038】

図1(A)中、10は、絶縁表面を有する基板、11はプロッキング層となる絶縁膜、12は非晶質構造を有する半導体膜である。

## 【0039】

図1(A)において、基板10はガラス基板、石英基板、セラミック基板などを用いるこ

40

50

とができる。また、シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

#### 【0040】

まず、図1(A)に示すように基板10上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜( $\text{SiO}_x\text{N}_y$ )等の絶縁膜から成る下地絶縁膜11を形成する。代表的な一例は下地絶縁膜11として2層構造から成り、 $\text{SiH}_4$ 、 $\text{NH}_3$ 、及び $\text{N}_2\text{O}$ を反応ガスとして成膜される窒化酸化珪素膜を50~100nm、 $\text{SiH}_4$ 、及び $\text{N}_2\text{O}$ を反応ガスとして成膜される酸化窒化珪素膜を100~150nmの厚さに積層形成する構造が採用される。また、下地絶縁膜11の一層として膜厚10nm以下の窒化シリコン膜( $\text{SiN}$ 膜)、或いは酸化窒化珪素膜( $\text{SiN}_x\text{O}_y$ 膜(X)Y))を用いることが好ましい。ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、半導体膜と接する下地絶縁膜を窒化シリコン膜とすることは極めて有効である。また、窒化酸化珪素膜、酸化窒化珪素膜、窒化シリコン膜とを順次積層した3層構造を用いてもよい。

#### 【0041】

次いで、下地絶縁膜上に非晶質構造を有する第1の半導体膜12を形成する。第1の半導体膜12は、シリコンを主成分とする半導体材料を用いる。代表的には、非晶質シリコン膜又は非晶質シリコンゲルマニウム膜などが適用され、プラズマCVD法や減圧CVD法、或いはスパッタ法で10~100nmの厚さに形成する。後の結晶化で良質な結晶構造を有する半導体膜を得るためにには、非晶質構造を有する第1の半導体膜12の膜中に含まれる酸素、窒素などの不純物濃度を $5 \times 10^{18} / \text{cm}^3$ (二次イオン質量分析法(SIMS)にて測定した原子濃度)以下に低減させておくと良い。これらの不純物は後の結晶化を妨害する要因となり、また、結晶化後においても捕獲中心や再結合中心の密度を増加させる要因となる。そのために、高純度の材料ガスを用いることはもとより、反応室内の鏡面処理(電界研磨処理)やオイルフリーの真空排気系を備えた超高真空対応のCVD装置を用いることが望ましい。

#### 【0042】

次いで、非晶質構造を有する第1の半導体膜12を結晶化させる技術としてここでは特開平8-78329号公報記載の技術を用いて結晶化させる。同公報記載の技術は、非晶質シリコン膜(アモルファスシリコン膜とも呼ばれる)に対して結晶化を助長する金属元素を選択的に添加し、加熱処理を行うことで添加領域を起点として広がる結晶構造を有する半導体膜を形成するものである。まず、非晶質構造を有する第1の半導体膜12の表面上に、結晶化を促進する触媒作用のある金属元素(ここでは、ニッケル)を重量換算で1~100ppm含む酢酸ニッケル塩溶液をスピナーで塗布してニッケル含有層13を形成する。(図1(B))塗布によるニッケル含有層13の形成方法以外の他の手段として、スパッタ法、蒸着法、またはプラズマ処理により極薄い膜を形成する手段を用いてもよい。また、ここでは、全面に塗布する例を示したが、マスクを形成して選択的にニッケル含有層を形成してもよい。

#### 【0043】

次いで、加熱処理を行い、結晶化を行う。この場合、結晶化は半導体の結晶化を助長する金属元素が接した半導体膜の部分でシリサイドが形成され、それを核として結晶化が進行する。こうして、図1(C)に示す結晶構造を有する第1の半導体膜14が形成される。なお、結晶化後での第1の半導体膜14に含まれる酸素濃度は、 $5 \times 10^{18} / \text{cm}^3$ 以下とすることが望ましい。ここでは、脱水素化のための熱処理(450、1時間)の後、結晶化のための熱処理(550~650で4~24時間)を行う。また、強光の照射により結晶化を行う場合は、赤外光、可視光、または紫外光のいずれかーまたはそれらの組み合わせを用いることが可能であるが、代表的には、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いる。ランプ光源は、必要な時間点灯させて加熱

10

20

30

40

50

してもよいし、1～60秒、好ましくは30～60秒点灯させ、それを1回～10回繰り返し、半導体膜が瞬間に600～1000程度にまで加熱すればよい。なお、必要であれば、強光を照射する前に非晶質構造を有する第1の半導体膜14に含有する水素を放出させる熱処理を行ってもよい。また、熱処理と強光の照射とを同時にやって結晶化を行ってもよい。生産性を考慮すると、結晶化は強光の照射により結晶化を行うことが望ましい。

#### 【0044】

このようにして得られる第1の半導体膜14には、金属元素（ここではニッケル）が残存している。それは膜中において一様に分布していないにしろ、平均的な濃度とすれば、 $1 \times 10^{19} / \text{cm}^3$  を越える濃度で残存している。勿論、このような状態でもTFTをはじめ各種半導体素子を形成することが可能であるが、以降に示す本発明のゲッタリング方法で当該元素を除去する。10

#### 【0045】

次いで、結晶化率（膜の全体積における結晶成分の割合）を高め、結晶粒内に残される欠陥を補修するために、結晶構造を有する第1の半導体膜14に対してレーザー光を照射することが好ましい。レーザー光を照射した場合、表面に薄い酸化膜（図示しない）が形成される。このレーザー光としてはパルス発振であるレーザ光源から出射される波長400nm以下のエキシマレーザ光や、YAGレーザの第2高調波、第3高調波を用いればよい。また、レーザー光としては連続発振が可能な固体レーザを用い、基本波の第2高調波～第4高調波を用いてもよい。代表的には、Nd:YVO<sub>4</sub>レーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を適用すればよい。20

#### 【0046】

上記結晶化後のレーザー光の照射により形成された酸化膜では、不十分であるため、さらに、オゾン含有水溶液（代表的にはオゾン水）で酸化膜（ケミカルオキサイドと呼ばれる）を形成して合計1～10nmの酸化膜からなるバリア層15を形成し、このバリア層15上にフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を含む第2の半導体膜16を形成する。（図1（D））

#### 【0047】

なお、ここでは、結晶構造を有する第1の半導体膜14に対してレーザー光を照射した場合に形成される酸化膜もバリア層の一部と見なしている。このバリア層15は、後の工程で第2の半導体膜16のみを選択的に除去する際にエッチングストップとして機能する。また、オゾン含有水溶液に代えて、硫酸、塩酸、硝酸などと過酸化水素水を混合させた水溶液で処理しても同様にケミカルオキサイドを形成することができる。また、他のバリア層15の形成方法としては、酸素雰囲気下の紫外線の照射でオゾンを発生させて前記結晶構造を有する半導体膜の表面を酸化して形成してもよい。また、他のバリア層15の形成方法としては、プラズマCVD法やスパッタ法や蒸着法などで1～10nm程度の酸化膜を堆積してバリア層としても良い。また、他のバリア層15の形成方法としては、クリーンオーブンを用い、200～350程度に加熱して薄い酸化膜を形成しても良い。なお、上記方法のいずれか一の方法、またはそれらの方法を組み合わせて形成されたバリア層15は、後のゲッタリングで第1の半導体膜中のニッケルが第2の半導体膜に移動可能な膜質または膜厚とすることが必要である。40

#### 【0048】

また、上記バリア層上に形成する第2の半導体膜16aは、膜厚10nm～300nmでプラズマCVD法、またはスパッタ法により形成する。（図1（E））

#### 【0049】

ここでは、シリコンターゲットを用いたスパッタ法でアモルファスシリコン膜からなる第2の半導体膜16aを形成する。

#### 【0050】

次いで、第2の半導体膜16aにハロゲン元素化合物、炭素化合物、窒素化合物、または酸素化合物を添加して、化合物イオンを含む第2の半導体膜16bを形成する。（図1（50

F ) )

【 0 0 5 1 】

ここでは、フッ素と炭素の化合物である  $\text{CF}_4$  から生成した  $\text{CF}_3^+$  イオンをイオン注入法により添加する。後に行われる加熱処理の際、フッ素により酸素の析出が加速されて、第2の半導体膜に酸素と炭素の化合物が形成され、強力なゲッタリングシンクとして機能する。なお、ここでは  $\text{CF}_3^+$  イオンを一例としたが特に限定されず、他のハロゲン元素化合物、炭素化合物、窒素化合物、または酸素化合物を適宜、添加すればよい。

【 0 0 5 2 】

膜中に化合物イオンを含有させる意味は二つある。一つはダングリングボンドを形成し半導体膜に歪みを与えることであり、他の一つは半導体膜の格子間に歪みを与えることである。半導体膜の格子間に歪みを与えるにはシリコンより合計原子数の大きな化合物イオンを用いた時に顕著に得られる。また、膜中に化合物イオンを含有させることにより、格子歪だけでなく、不対結合手（添加された化合物イオンの不対結合手も含む）も形成させてゲッタリング作用に寄与する。

【 0 0 5 3 】

次いで、加熱処理を行い、第1の半導体膜中における金属元素（ニッケル）の濃度を低減、あるいは除去するゲッタリングを行う。（図1(F)）ゲッタリングを行う加熱処理としては、強光を照射する処理、炉を用いた熱処理、または加熱されたガスに基板を投入し、数分放置した後取りだすことによって加熱を行えばよい。このゲッタリングにより、図1(F)中の矢印の方向（即ち、基板側から第2の半導体膜表面に向かう方向）に金属元素が移動し、バリア層15で覆われた第1の半導体膜14に含まれる金属元素の除去、または金属元素の濃度の低減が行われる。金属元素がゲッタリングの際に移動する距離は、第1の半導体膜の厚さ程度の距離であればよく、比較的短時間でゲッタリングを完遂することができる。ここでは、ニッケルが第1の半導体膜14に偏析しないよう全て第2の半導体膜16bに移動させ、第1の半導体膜14に含まれるニッケルがほとんど存在しない、即ち膜中のニッケル濃度が  $1 \times 10^{18} / \text{cm}^3$  以下、望ましくは  $1 \times 10^{17} / \text{cm}^3$  以下になるように十分ゲッタリングする。なお、第2の半導体膜だけでなくバリア層15もゲッタリングサイトとして機能する。

【 0 0 5 4 】

なお、このゲッタリングの加熱処理の条件、或いは第2の半導体膜の膜厚によっては、第2の半導体膜が一部結晶化される場合もある。第2の半導体膜が結晶化してしまうとダングリングボンドや格子歪みや不対結合手が減少してゲッタリング効果の低減を招く。いずれにせよ、第2の半導体膜、即ち化合物イオンを含有する非晶質シリコン膜は、化合物イオンを含まない非晶質シリコン膜と比べて結晶化が生じにくいため、ゲッタリングサイトとして最適である。

【 0 0 5 5 】

また、このゲッタリングの加熱処理の条件によっては、ゲッタリングと同時に結晶粒内に残される欠陥を補修する、即ち結晶性の改善を行うことができる。また、ゲッタリングの加熱処理の条件を調節して、第2の半導体膜中に含まれる化合物イオンが拡散して第1の半導体膜に達する恐れを防ぐことも重要である。また、バリア層は、この化合物イオンの拡散を防止する役目も有している。

【 0 0 5 6 】

本明細書において、ゲッタリングとは、被ゲッタリング領域（ここでは第1の半導体膜）にある金属元素が熱エネルギーにより放出され、拡散によりゲッタリングサイトに移動することを指している。

【 0 0 5 7 】

強光を照射する処理を用いる場合は、基板が耐えうる範囲で照射しつづけてよく、例えば、加熱用のランプ光源を約3分間点灯させ、瞬間的には半導体膜が700℃に加熱されるようにする。或いは、加熱用のランプ光源を1~60秒、好ましくは30~60秒点灯させ、それを1~10回、好ましくは2~6回繰り返す。ランプ光源の発光強度は任意なもの

10

20

30

40

50

のとするが、瞬間的には 600 ~ 1000 、好ましくは 700 ~ 750 程度に半導体膜が加熱されるようとする。

#### 【0058】

また、熱処理で行う場合は、不活性雰囲気中、代表的には窒素雰囲気中で 450 ~ 800 、1 ~ 24 時間、例えば 550 にて 4 時間の熱処理を行えばよい。また、予め 450 ~ 800 に加熱された炉に基板を導入する場合、例えば 700 に加熱された炉の中に 3 分間配置して熱処理を行えばよい。また、熱処理に加えて強光を照射してもよい。

#### 【0059】

次いで、バリア層 15 をエッティングストッパーとして、16b で示した第 2 の半導体膜のみを選択的に除去し、バリア層 15 を除去し、第 1 の半導体膜 14 を公知のパターニング技術を用いて所望の形状の半導体層 17 を形成する。(図 1 (G)) 第 2 の半導体膜のみを選択的にエッティングする方法としては、 $\text{C}_1\text{F}_3$  によるプラズマを用いないドライエッティング、或いはヒドラジンや、テトラエチルアンモニウムハイドロオキサイド(化学式 $(\text{CH}_3)_4\text{NOH}$ )を含む水溶液などアルカリ溶液によるウエットエッティングで行うことができる。また、第 2 の半導体膜を除去した後、バリア層の表面を TXRF でニッケル濃度を測定したところ、ニッケルが高濃度で検出されるため、バリア層は除去することが望ましく、フッ酸を含むエッチャントにより除去すれば良い。また、バリア層を除去した後、レジストからなるマスクを形成する前に、オゾン水で表面に薄い酸化膜を形成することが望ましい。

#### 【0060】

所望の形状の半導体層 17 を形成する工程が終了したら、半導体層の表面をフッ酸を含むエッチャントで洗浄し、ゲート絶縁膜 18 となる珪素を主成分とする絶縁膜を形成する。この表面洗浄とゲート絶縁膜の形成は、大気にふれさせずに連続的に行なうことが望ましい。

#### 【0061】

次いで、ゲート絶縁膜 18 の表面を洗浄した後、ゲート電極 19 を形成する。次いで、半導体に n 型を付与する不純物元素(P、As 等)、ここではリンを適宜添加して、ソース領域 20 及びドレイン領域 21 を形成する。添加した後、不純物元素を活性化するために加熱処理、強光の照射、またはレーザー光の照射を行う。また、活性化と同時にゲート絶縁膜へのプラズマダメージやゲート絶縁膜と半導体層との界面へのプラズマダメージを回復することができる。特に、室温 ~ 300 の雰囲気中において、表面または裏面から YAG レーザーの第 2 高調波を照射して不純物元素を活性化させることは非常に有効である。YAG レーザーはメンテナンスが少ないため好ましい活性化手段である。

#### 【0062】

以降の工程は、層間絶縁膜 23 を形成し、水素化を行って、ソース領域、ドレイン領域に達するコンタクトホールを形成し、ソース電極 24 、ドレイン電極 25 を形成して TFT (n チャネル型 TFT) を完成させる。(図 1 (H))

#### 【0063】

こうして得られた TFT のチャネル形成領域 22 に含まれる金属元素の濃度は  $1 \times 10^7 / \text{cm}^3$  未満とすることができます。

#### 【0064】

また、本発明は図 1 (H) の TFT 構造に限定されず、必要があればチャネル形成領域とドレイン領域(またはソース領域)との間に LDD 領域を有する低濃度ドレイン(LDD : Lightly Doped Drain)構造としてもよい。この構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域を LDD 領域と呼んでいる。さらにゲート絶縁膜を介して LDD 領域をゲート電極と重ねて配置させた、いわゆる GOLD (Gate - drain Overlapped LDD) 構造としてもよい。

#### 【0065】

10

20

30

40

50

また、ここではnチャネル型TFTを用いて説明したが、n型不純物元素に代えてp型不純物元素を用いることによってpチャネル型TFTを形成することはできると言ふまでもない。

#### 【0066】

また、ここではトップゲート型TFTを例として説明したが、TFT構造に関係なく本発明を適用することが可能であり、例えばボトムゲート型(逆スタガ型)TFTや順スタガ型TFTに適用することが可能である。

#### 【0067】

また、ここではフッ素化合物、炭素化合物、窒素化合物、または酸素化合物を含む半導体膜を用いた例を示したが、さらに希ガス元素を含む半導体膜にこれらの化合物イオンを添加してもよい。スパッタ法で希ガス元素を含む半導体膜を形成する場合には、反応ガスにアルゴンなどを加えればよい。

10

#### 【0068】

また、プラズマCVD法で希ガス元素を含む半導体膜を形成する場合、例えば、原料ガスとしてモノシランとアルゴンを用い、比率(モノシラン：アルゴン)を0.1:99.9~1:9、好ましくは、1:99~5:95に制御して成膜すればよい。また、成膜時のRFパワー密度は、0.0017W/cm<sup>2</sup>~0.48W/cm<sup>2</sup>とすることが望ましい。RFパワー密度は、高ければ高いほど成膜速度が向上するため好ましい。また、成膜時の圧力は、1.333Pa(0.01Torr)~66.65Pa(0.5Torr)、好ましくは、53.32Pa(0.4Torr)未満とすることが望ましい。圧力は、高ければ高いほど成膜速度が向上するため好ましい。また、成膜温度は300~500とすることが望ましい。こうして、膜中にアルゴンを $1 \times 10^{18} / \text{cm}^3$ ~ $1 \times 10^{22} / \text{cm}^3$ の濃度で含み、ゲッタリング効果が得られる第2の半導体膜をプラズマCVD法で成膜することができる。さらに、上記第2の半導体膜の成膜条件とすることで、成膜の際、バリア層に与えるダメージを低減することができ、第1の半導体膜の膜厚のバラツキ発生や第1の半導体膜に穴が形成されるという不良の発生を防ぐことができる。

20

#### 【0069】

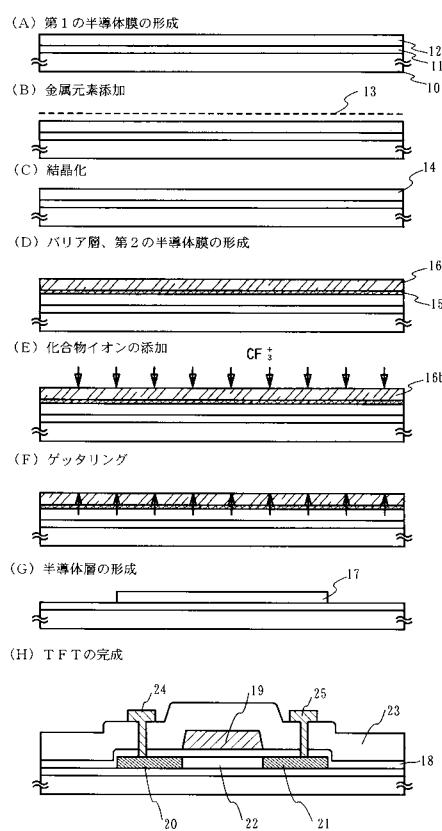

##### (実施の形態2)

ここでは、フッ素を含む第2の半導体膜を成膜段階で形成する例を図2に示す。なお、図2中、図1と同一の箇所は同一の符号を用いる。

30

#### 【0070】

まず、実施の形態1に従って、基板10上にプロッキング層となる絶縁膜11、第1の半導体膜、金属元素の添加を行い、加熱処理を行って結晶構造を有する第1の半導体膜14を形成する。(図2(A)~図2(C))次いで、実施の形態1に従って、レーザー光を照射する。

40

#### 【0071】

次いで、レーザー光により形成された表面の酸化膜を除去した後、プラズマCVD法で酸化窒化シリコン膜からなるバリア層35を形成する。次いで、プラズマCVD法でフッ素を含む第2の半導体膜36を形成する。(図2(D))

40

#### 【0072】

ここでは、成膜室にシラン系ガスと窒素酸化物系ガスを原料ガスとして導入し、プラズマを発生させるプラズマCVD法により形成した酸化窒化シリコン膜をバリア層35とする。

#### 【0073】

また、バリア層35を形成した後、大気にふれさせることなく、同一チャンバーで連続的にSiF<sub>4</sub>を成膜ガスとして、フッ素を含むアモルファシリコン膜を形成する。このように、フッ素を含む第2の半導体膜と、バリア層を大気に触れさせることなく成膜することが可能であり、さらに同一チャンバーで連続的に成膜することも可能であるため、スループットに優れている。

50

## 【0074】

次いで、加熱処理を行い、第1の半導体膜中における金属元素(ニッケル)の濃度を低減、あるいは除去するゲッタリングを行う。(図2(E))

## 【0075】

次いで、バリア層35をエッチングストッパーとして、36で示した第2の半導体膜のみを選択的に除去した後、バリア層35を除去し、第1の半導体膜36を公知のパターニング技術を用いて所望の形状の半導体層17を形成する。(図2(F))

## 【0076】

以降の工程は、実施の形態1に従ってTFTを完成させればよい。ここでは、実施の形態1に示した工程と同一であるので詳細な説明は省略する。

10

## 【0077】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

## 【0078】

(実施例)

## [実施例1]

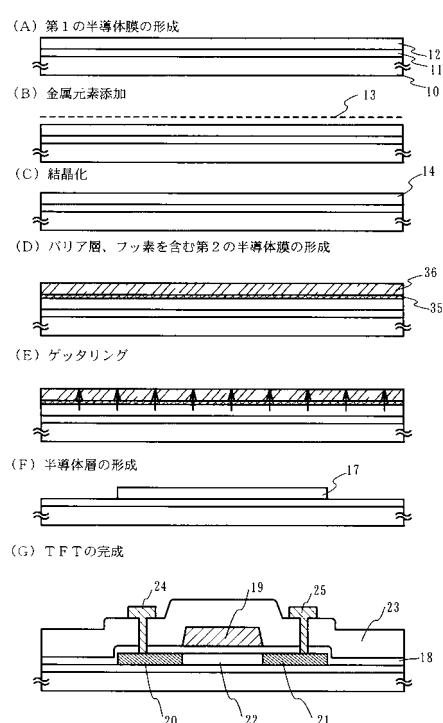

本発明の実施例を図3～図5を用いて説明する。ここでは、同一基板上に画素部と、画素部の周辺に設ける駆動回路のTFT(nチャネル型TFT及びpチャネル型TFT)を同時に作製する方法について詳細に説明する。

20

## 【0079】

まず、基板100上に下地絶縁膜101を形成し、結晶構造を有する第1の半導体膜を得た後、所望の形状にエッチング処理して島状に分離された半導体層102～106を形成する。

## 【0080】

基板100としては、ガラス基板(#1737)を用い、下地絶縁膜101としては、プラズマCVD法で成膜温度400℃、原料ガスSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜101a(組成比Si=32%、O=27%、N=24%、H=17%)を50nm(好ましくは10～200nm)形成する。次いで、表面をオゾン水で洗浄した後、表面の酸化膜を希フッ酸(1/100希釀)で除去する。次いでプラズマCVD法で成膜温度400℃、原料ガスSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜101b(組成比Si=32%、O=59%、N=7%、H=2%)を100nm(好ましくは50～200nm)の厚さに積層形成し、さらに大気解放せずにプラズマCVD法で成膜温度300℃、成膜ガスSiH<sub>4</sub>で非晶質構造を有する半導体膜(ここではアモルファスシリコン膜)を54nmの厚さ(好ましくは25～80nm)で形成する。

30

## 【0081】

本実施例では下地膜101を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。また、半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコングルマニウム(Si<sub>x</sub>Ge<sub>1-x</sub>(X=0.0001～0.02))合金などを用い、公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により形成すればよい。また、プラズマCVD装置は、枚葉式の装置でもよいし、バッチ式の装置でもよい。また、同一の成膜室で大気に触れることなく下地絶縁膜と半導体膜とを連続成膜してもよい。

40

## 【0082】

次いで、非晶質構造を有する半導体膜の表面を洗浄した後、オゾン水で表面に約2nmの極薄い酸化膜を形成する。次いで、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行う。ここでは、ジボラン(B<sub>2</sub>H<sub>6</sub>)を質量分離しないでプラズマ励起したイオンドープ法を用い、ドーピング条件を加速電圧15kV、ジボランを水素で1%に希釀したガス流量30sccm、ドーズ量2×10<sup>12</sup>/cm<sup>2</sup>で非晶質シリコン膜にボロンを添加した。

## 【0083】

50

次いで、重量換算で 10 ppm のニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布する。塗布に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。

#### 【0084】

次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜を形成する。この加熱処理は、電気炉の熱処理または強光の照射を用いればよい。電気炉の熱処理で行う場合は、500 ~ 650 で 4 ~ 24 時間で行えればよい。ここでは脱水素化のための熱処理（500、1 時間）の後、結晶化のための熱処理（550、4 時間）を行って結晶構造を有するシリコン膜を得る。なお、ここでは炉を用いた熱処理を用いて結晶化を行ったが、短時間での結晶化が可能なランプアニール装置で結晶化を行ってもよい。なお、ここではシリコンの結晶化を助長する金属元素としてニッケルを用いた結晶化技術を用いたが、他の公知の結晶化技術、例えば固相成長法やレーザー結晶化法を用いてもよい。

10

#### 【0085】

次いで、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去した後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザー光（XeCl：波長 308 nm）の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長 400 nm 以下のエキシマレーザ光や、YAG レーザの第 2 高調波、第 3 高調波を用いる。ここでは、繰り返し周波数 10 ~ 1000 Hz 程度のパルスレーザー光を用い、当該レーザー光を光学系にて 100 ~ 500 mJ / cm<sup>2</sup> に集光し、90 ~ 95 % のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数 30 Hz、エネルギー密度 470 mJ / cm<sup>2</sup> でレーザー光の照射を大気中で行なった。なお、大気中、または酸素雰囲気中で行うため、レーザー光の照射により表面に酸化膜が形成される。なお、ここではパルスレーザーを用いた例を示したが、連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためにには、連続発振が可能な固体レーザを用い、基本波の第 2 高調波 ~ 第 4 高調波を適用するのが好ましい。代表的には、Nd : YVO<sub>4</sub> レーザー（基本波 1064 nm）の第 2 高調波（532 nm）や第 3 高調波（355 nm）を適用すればよい。連続発振のレーザーを用いる場合には、出力 10 W の連続発振の YVO<sub>4</sub> レーザーから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中に YVO<sub>4</sub> 結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橜円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は 0.01 ~ 100 MW / cm<sup>2</sup> 程度（好ましくは 0.1 ~ 10 MW / cm<sup>2</sup>）が必要である。そして、10 ~ 2000 cm / s 程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すればよい。

20

30

40

#### 【0086】

次いで、上記レーザー光の照射により形成された酸化膜に加え、オゾン水で表面を 120 秒処理して合計 1 ~ 5 nm の酸化膜からなるバリア層を形成する。本実施例ではオゾン水を用いてバリア層を形成したが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマ CVD 法やスパッタ法や蒸着法などで 1 ~ 10 nm 程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザー光の照射により形成された酸化膜を除去してもよい。

#### 【0087】

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなる非晶質シリコン膜を 10 nm ~ 400 nm、ここでは膜厚 200 nm で形成した後、化合物イオンのドーピングを行う。本実施例では、非晶質シリコン膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成し、化合物イオンとして、CF<sub>3</sub><sup>+</sup> イオンをイオン注入法で添加する。

#### 【0088】

その後、650 に加熱された炉に入れて 3 分の熱処理を行いゲッタリングして、結晶構造を有する半導体膜中のニッケル濃度を低減する。炉に代えてランプアニール装置を用いてもよい。

50

## 【0089】

次いで、バリア層をエッチングストッパーとして、ゲッタリングサイトである化合物イオンを含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

## 【0090】

次いで、得られた結晶構造を有するシリコン膜（ポリシリコン膜とも呼ばれる）の表面にオゾン水で薄い酸化膜を形成した後、レジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層を形成する。半導体層を形成した後、レジストからなるマスクを除去する。

10

## 【0091】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜の表面を洗浄した後、ゲート絶縁膜303となる珪素を主成分とする絶縁膜を形成する。ここでは、プラズマCVD法により115nmの厚さで酸化窒化シリコン膜（組成比Si = 32%、O = 59%、N = 7%、H = 2%）で形成する。

## 【0092】

次いで、図3(A)に示すように、ゲート絶縁膜107上に膜厚20~100nmの第1の導電膜108aと、膜厚100~400nmの第2の導電膜108bとを積層形成する。本実施例では、ゲート絶縁膜107上に膜厚50nmの窒化タンタル膜、膜厚370nmのタンゲステン膜を順次積層する。

20

## 【0093】

第1の導電膜及び第2の導電膜を形成する導電性材料としてはTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成する。また、第1の導電膜及び第2の導電膜としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金（Al-Si）膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金（Al-Si）膜に代えてアルミニウムとチタンの合金膜（Al-Ti）を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。

30

## 【0094】

次に、図3(B)に示すように光露光工程によりレジストからなるマスク110~115を形成し、ゲート電極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第1及び第2のエッチング条件で行う。エッチングにはICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用いると良い。ICPエッチング法を行い、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節することによって所望のテーパー形状に膜をエッチングすることができる。なお、エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>、CCl<sub>4</sub>などを代表とする塩素系ガスまたはCF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>などを代表とするフッ素系ガス、またはO<sub>2</sub>を適宜用いることができる。

40

## 【0095】

本実施例では、基板側（試料ステージ）にも150WのRF（13.56MHz）電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、基板側の電極面積サイズは、12.5cm×12.5cmであり、コイル型の電極面積サイズ（ここではコイルの設けられた石英円板）は、直径25cmの円板である。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。第1のエッチング条件でのWに対するエッチング速度は200.39nm/min、TaNに対するエッチング速度

50

は 80.32 nm/min であり、TaNに対するWの選択比は約2.5である。また、この第1のエッティング条件によって、Wのテーパー角は、約26°となる。この後、レジストからなるマスク110～115を除去せずに第2のエッティング条件に変え、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30/30(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッティングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した第2のエッティング条件ではW膜及びTaN膜とも同程度にエッティングされる。第2のエッティング条件でのWに対するエッティング速度は58.97 nm/min、TaNに対するエッティング速度は66.43 nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10～20%程度の割合でエッティング時間を増加させると良い。10

#### 【0096】

上記第1のエッティング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15～45°とすればよい。

#### 【0097】

こうして、第1のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層117～121(第1の導電層117a～121aと第2の導電層117b～121b)を形成する。ゲート絶縁膜となる絶縁膜107は、10～20nm程度エッティングされ、第1の形状の導電層117～121で覆われない領域が薄くなつたゲート絶縁膜116となる。20

#### 【0098】

次いで、レジストからなるマスクを除去せずに第2のエッティング処理を行う。ここでは、エッティング用ガスにSF<sub>6</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を24/12/24(ccm)とし、1.3Paの圧力でコイル型の電極に700WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを25秒行った。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッティング処理でのWに対するエッティング速度は227.3 nm/min、TaNに対するエッティング速度は32.1 nm/minであり、TaNに対するWの選択比は7.1であり、絶縁膜116であるSiONに対するエッティング速度は33.7 nm/minであり、SiONに対するWの選択比は6.83である。このようにエッティングガス用ガスにSF<sub>6</sub>を用いた場合、絶縁膜116との選択比が高いので膜減りを抑えることができる。本実施例では絶縁膜116において約8nmしか膜減りが起きない。30

#### 【0099】

この第2のエッティング処理によりWのテーパー角は70°となった。この第2のエッティング処理により第2の導電層124b～129bを形成する。一方、第1の導電層は、ほとんどエッティングされず、第1の導電層124a～129aとなる。なお、第1の導電層124a～129aは、第1の導電層117a～122aとほぼ同一サイズである。実際には、第1の導電層の幅は、第2のエッティング処理前に比べて約0.3μm程度、即ち線幅全体で0.6μm程度後退する場合もあるがほとんどサイズに変化がない。40

#### 【0100】

また、2層構造に代えて、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムシリコンの合金(A1-Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造とした場合、第1のエッティング処理の第1のエッティング条件としては、BCl<sub>3</sub>とCl<sub>2</sub>とO<sub>2</sub>とを原料ガスに用い、それぞれのガス流量比を65/10/5(ccm)とし、基板側(試料ステージ)に300WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に450WのRF(13.56MHz)電力を投入してプラズマを生成して117秒のエッティングを行えばよく、第1のエッティング処理の第2の工50

ツチング条件としては、 $\text{CF}_4$  と  $\text{Cl}_2$  と  $\text{O}_2$  を用い、それぞれのガス流量比を 25 / 25 / 10 ( sccm ) とし、基板側（試料ステージ）にも 20W の RF ( 13.56 MHz ) 電力を投入し、1 Pa の圧力でコイル型の電極に 500W の RF ( 13.56 MHz ) 電力を投入してプラズマを生成して約 30 秒程度のエッチングを行えばよく、第 2 のエッチング処理としては  $\text{BCl}_3$  と  $\text{Cl}_2$  を用い、それぞれのガス流量比を 20 / 60 ( sccm ) とし、基板側（試料ステージ）には 100W の RF ( 13.56 MHz ) 電力を投入し、1.2 Pa の圧力でコイル型の電極に 600W の RF ( 13.56 MHz ) 電力を投入してプラズマを生成してエッチングを行えばよい。

#### 【 0101 】

次いで、レジストからなるマスクを除去した後、第 1 のドーピング処理を行って図 3 ( D ) の状態を得る。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーザ量を  $1.5 \times 10^{14}$  atoms/cm<sup>2</sup> とし、加速電圧を 60 ~ 100 keV として行う。 $n$  型を付与する不純物元素として、典型的にはリン ( P ) または砒素 ( As ) を用いる。この場合、第 1 の導電層及び第 2 の導電層 124 ~ 128 が  $n$  型を付与する不純物元素に対するマスクとなり、自己整合的に第 1 の不純物領域 130 ~ 134 が形成される。第 1 の不純物領域 130 ~ 134 には  $1 \times 10^{16} \sim 1 \times 10^{17}$  / cm<sup>3</sup> の濃度範囲で  $n$  型を付与する不純物元素を添加する。ここでは、第 1 の不純物領域と同じ濃度範囲の領域を  $n^-$  領域とも呼ぶ。

#### 【 0102 】

なお、本実施例ではレジストからなるマスクを除去した後、第 1 のドーピング処理を行ったが、レジストからなるマスクを除去せずに第 1 のドーピング処理を行ってもよい。

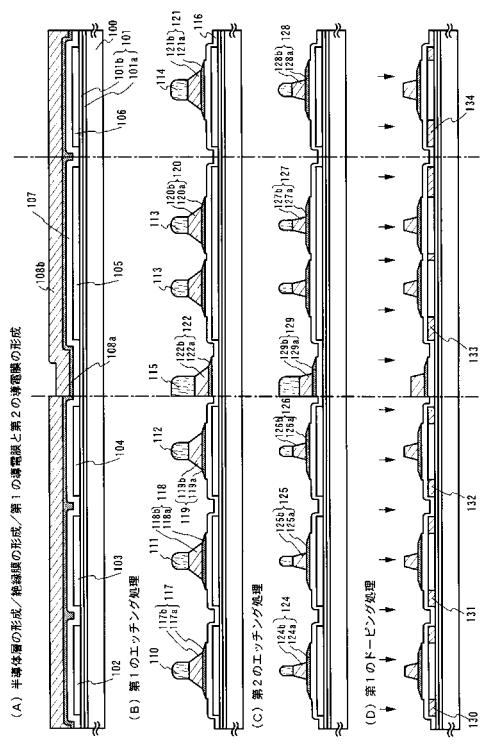

#### 【 0103 】

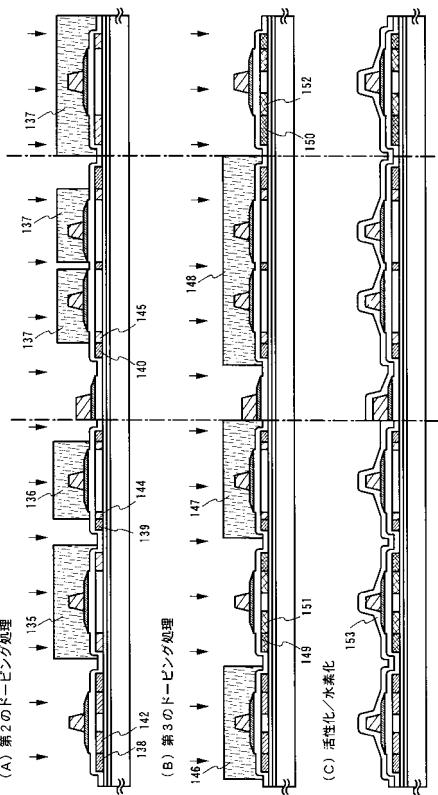

次いで、図 4 ( A ) に示すようにレジストからなるマスク 135 ~ 137 を形成し第 2 のドーピング処理を行う。マスク 135 は駆動回路の p チャネル型 TFT を形成する半導体層のチャネル形成領域及びその周辺の領域を保護するマスクであり、マスク 136 は駆動回路の n チャネル型 TFT の一つを形成する半導体層のチャネル形成領域及びその周辺の領域を保護するマスクであり、マスク 137 は画素部の TFT を形成する半導体層のチャネル形成領域及びその周辺の領域と保持容量となる領域とを保護するマスクである。

#### 【 0104 】

第 2 のドーピング処理におけるイオンドープ法の条件はドーザ量を  $1.5 \times 10^{15}$  atoms/cm<sup>2</sup> とし、加速電圧を 60 ~ 100 keV としてリン ( P ) をドーピングする。ここでは、第 2 の導電層 124b ~ 126b をマスクとして各半導体層に不純物領域が自己整合的に形成される。勿論、マスク 135 ~ 137 で覆われた領域には添加されない。こうして、第 2 の不純物領域 138 ~ 140 と、第 3 の不純物領域 142 が形成される。第 2 の不純物領域 138 ~ 140 には  $1 \times 10^{20} \sim 1 \times 10^{21}$  / cm<sup>3</sup> の濃度範囲で  $n$  型を付与する不純物元素を添加されている。ここでは、第 2 の不純物領域と同じ濃度範囲の領域を  $n^+$  領域とも呼ぶ。

#### 【 0105 】

また、第 3 の不純物領域は第 1 の導電層により第 2 の不純物領域よりも低濃度に形成され、 $1 \times 10^{18} \sim 1 \times 10^{19}$  / cm<sup>3</sup> の濃度範囲で  $n$  型を付与する不純物元素を添加されることになる。なお、第 3 の不純物領域は、テーパー形状である第 1 の導電層の部分を通過させてドーピングを行うため、テーパー部の端部に向かって不純物濃度が増加する濃度勾配を有している。ここでは、第 3 の不純物領域と同じ濃度範囲の領域を  $n^-$  領域とも呼ぶ。また、マスク 136、137 で覆われた領域は、第 2 のドーピング処理で不純物元素が添加されず、第 1 の不純物領域 144、145 となる。

#### 【 0106 】

次いで、レジストからなるマスク 135 ~ 137 を除去した後、新たにレジストからなるマスク 146 ~ 148 を形成して図 4 ( B ) に示すように第 3 のドーピング処理を行う。

#### 【 0107 】

駆動回路において、上記第 3 のドーピング処理により、p チャネル型 TFT を形成する半

10

20

30

40

50

導体層および保持容量を形成する半導体層に p 型の導電型を付与する不純物元素が添加された第 4 の不純物領域 149、150 及び第 5 の不純物領域 151、152 を形成する。

#### 【 0108 】

また、第 4 の不純物領域 149、150 には  $1 \times 10^{20} \sim 1 \times 10^{21} / \text{cm}^3$  の濃度範囲で p 型を付与する不純物元素が添加されるようとする。尚、第 4 の不純物領域 149、150 には先の工程でリン (P) が添加された領域 (n<sup>-</sup> 領域) であるが、p 型を付与する不純物元素の濃度がその 1.5 ~ 3 倍添加されていて導電型は p 型となっている。ここでは、第 4 の不純物領域と同じ濃度範囲の領域を p<sup>+</sup> 領域とも呼ぶ。

#### 【 0109 】

また、第 5 の不純物領域 151、152 は第 2 の導電層 125a のテープ部と重なる領域に形成されるものであり、 $1 \times 10^{18} \sim 1 \times 10^{20} / \text{cm}^3$  の濃度範囲で p 型を付与する不純物元素が添加されるようとする。ここでは、第 5 の不純物領域と同じ濃度範囲の領域を p<sup>-</sup> 領域とも呼ぶ。

#### 【 0110 】

以上までの工程でそれぞれの半導体層に n 型または p 型の導電型を有する不純物領域が形成される。導電層 124 ~ 127 は TFT のゲート電極となる。また、導電層 128 は画素部において保持容量を形成する一方の電極となる。さらに、導電層 129 は画素部においてソース配線を形成する。

#### 【 0111 】

次いで、ほぼ全面を覆う絶縁膜（図示しない）を形成する。本実施例では、プラズマ CVD 法により膜厚 50 nm の酸化シリコン膜を形成した。勿論、この絶縁膜は酸化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

#### 【 0112 】

次いで、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法 (RTA 法)、或いは YAG レーザーまたはエキシマレーザーを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方のうち、いずれかと組み合わせた方法によって行う。

#### 【 0113 】

また、本実施例では、上記活性化の前に絶縁膜を形成した例を示したが、上記活性化を行った後、絶縁膜を形成する工程としてもよい。

#### 【 0114 】

次いで、窒化シリコン膜からなる第 1 の層間絶縁膜 153 を形成して熱処理 (300 ~ 550 度 1 ~ 12 時間の熱処理) を行い、半導体層を水素化する工程を行う。（図 4 (C)）この工程は第 1 の層間絶縁膜 153 に含まれる水素により半導体層のダンギングボンドを終端する工程である。酸化シリコン膜からなる絶縁膜（図示しない）の存在に関係なく半導体層を水素化することができる。ただし、本実施例では、第 2 の導電層としてアルミニウムを主成分とする材料を用いているので、水素化する工程において第 2 の導電層が耐え得る熱処理条件とすることが重要である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

#### 【 0115 】

次いで、第 1 の層間絶縁膜 153 上に有機絶縁物材料から成る第 2 の層間絶縁膜 154 を形成する。本実施例では膜厚 1.6 μm のアクリル樹脂膜を形成する。次いで、ソース配線 129 に達するコンタクトホールと、導電層 127、128 に達するコンタクトホールと、各不純物領域に達するコンタクトホールを形成する。本実施例では複数のエッチング処理を順次行う。本実施例では第 1 の層間絶縁膜をエッチングストッパーとして第 2 の層間絶縁膜をエッチングした後、絶縁膜（図示しない）をエッチングストッパーとして第 1 の層間絶縁膜をエッチングしてから絶縁膜（図示しない）をエッチングした。

#### 【 0116 】

その後、Al、Ti、Mo、Wなどを用いて配線及び画素電極を形成する。これらの電極

10

20

30

40

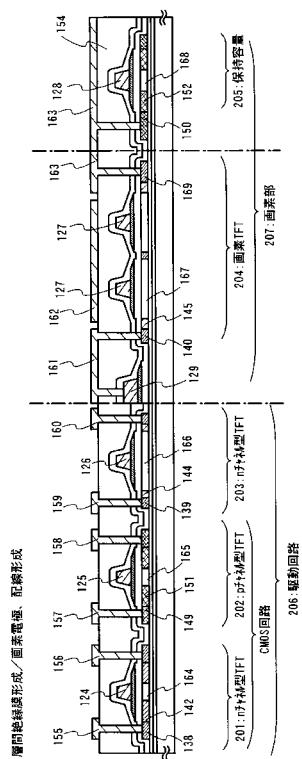

50

及び画素電極の材料は、A<sub>1</sub>またはA<sub>g</sub>を主成分とする膜、またはそれらの積層膜等の反射性の優れた材料を用いることが望ましい。こうして、ソース電極またはドレイン電極155～160、ゲート配線162、接続配線161、画素電極163が形成される。

#### 【0117】

以上の様にして、nチャネル型TFT201、pチャネル型TFT202、nチャネル型TFT203を有する駆動回路206と、nチャネル型TFTからなる画素TFT204、保持容量205とを有する画素部207を同一基板上に形成することができる。（図5）本明細書中ではこのような基板を便宜上アクティブマトリクス基板と呼ぶ。本明細書中ではこのような基板を便宜上アクティブマトリクス基板と呼ぶ。

#### 【0118】

画素部207において、画素TFT204（nチャネル型TFT）にはチャネル形成領域167、ゲート電極を形成する導電層127の外側に形成される第1の不純物領域（n<sup>-</sup>領域）145とソース領域として機能する第2の不純物領域（n<sup>+</sup>領域）140を有している。また、保持容量205の一方の電極として機能する半導体層には第4の不純物領域150、第5の不純物領域152が形成されている。保持容量205は、絶縁膜（ゲート絶縁膜と同一膜）116を誘電体として、第2の電極128と、半導体層150、152、168とで形成されている。

#### 【0119】

また、駆動回路206において、nチャネル型TFT201（第1のnチャネル型TFT）はチャネル形成領域164、ゲート電極を形成する導電層124の一部と絶縁膜を介して重なる第3の不純物領域（n<sup>-</sup>領域）142とソース領域またはドレイン領域として機能する第2の不純物領域（n<sup>+</sup>領域）138を有している。

#### 【0120】

また、駆動回路206において、pチャネル型TFT202にはチャネル形成領域165、ゲート電極を形成する導電層125の一部と絶縁膜を介して重なる第5不純物領域（p<sup>-</sup>領域）151とソース領域またはドレイン領域として機能する第4の不純物領域（p<sup>+</sup>領域）149を有している。

#### 【0121】

また、駆動回路206において、nチャネル型TFT203（第2のnチャネル型TFT）にはチャネル形成領域166、ゲート電極を形成する導電層126の外側に第1の不純物領域（n<sup>-</sup>領域）144とソース領域またはドレイン領域として機能する第2の不純物領域（n<sup>+</sup>領域）139を有している。

#### 【0122】

これらのTFT201～203を適宜組み合わせてシフトレジスタ回路、バッファ回路、レベルシフタ回路、ラッチ回路などを形成し、駆動回路206を形成すればよい。例えば、CMOS回路を形成する場合には、nチャネル型TFT201とpチャネル型TFT202を相補的に接続して形成すればよい。

#### 【0123】

特に、駆動電圧が高いバッファ回路には、ホットキャリア効果による劣化を防ぐ目的から、nチャネル型TFT203の構造が適している。

#### 【0124】

また、信頼性が最優先とされる回路には、GOLD構造であるnチャネル型TFT201の構造が適している。

#### 【0125】

また、半導体膜表面の平坦化を向上させることによって信頼性を向上させることができるので、GOLD構造のTFTにおいて、ゲート電極とゲート絶縁膜を介して重なる不純物領域の面積を縮小しても十分な信頼性を得ることができる。具体的にはGOLD構造のTFTにおいてゲート電極のテーパー部となる部分サイズを小さくしても十分な信頼性を得ることができる。

#### 【0126】

10

20

30

40

50

また、GOLD構造のTFTにおいてはゲート絶縁膜が薄くなると寄生容量が増加するが、ゲート電極（第1導電層）のテーパー部となる部分サイズを小さくして寄生容量を低減すれば、f特性も向上してさらなる高速動作が可能となり、且つ、十分な信頼性を有するTFTとなる。

#### 【0127】

また、本実施例では反射型の表示装置を形成するためのアクティブマトリクス基板を作製する例を示したが、画素電極を透明導電膜で形成すると、フォトマスクは1枚増えるものの、透過型の表示装置を形成することができる。

#### 【0128】

また、本実施例は実施の形態と自由に組み合わせることが可能である。

10

#### 【0129】

#### [実施例2]

本実施例では、実施例1で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を以下に説明する。説明には図6を用いる。

#### 【0130】

まず、実施例1に従い、図5の状態のアクティブマトリクス基板を得た後、図5のアクティブマトリクス基板上に配向膜を形成しラビング処理を行う。なお、本実施例では配向膜を形成する前に、アクリル樹脂膜等の有機樹脂膜をバターニングすることによって基板間隔を保持するための柱状のスペーサを所望の位置に形成した。また、柱状のスペーサに代えて、球状のスペーサを基板全面に散布してもよい。

20

#### 【0131】

次いで、対向基板を用意する。この対向基板には、着色層、遮光層が各画素に対応して配置されたカラーフィルタが設けられている。また、駆動回路の部分にも遮光層を設けた。このカラーフィルタと遮光層とを覆う平坦化膜を設けた。次いで、平坦化膜上に透明導電膜からなる対向電極を画素部に形成し、対向基板の全面に配向膜を形成し、ラビング処理を施す。

#### 【0132】

そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール材で貼り合わせる。シール材にはフィラーが混入されていて、このフィラーと柱状スペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料を注入し、封止剤（図示せず）によって完全に封止する。液晶材料には公知の液晶材料を用いれば良い。このようにしてアクティブマトリクス型液晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基板を所望の形状に分断する。さらに、公知の技術を用いて偏光板や位相差板等の光学フィルムを適宜設ける。そして、公知の技術を用いてFPCを貼りつける。

30

#### 【0133】

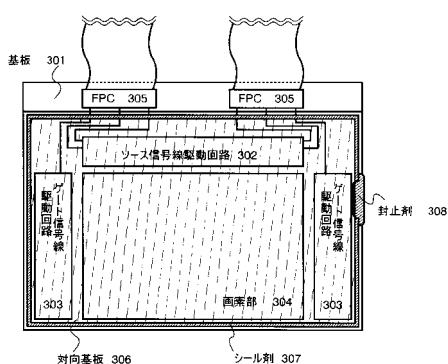

こうして得られた液晶モジュールの構成を図6の上面図を用いて説明する。

#### 【0134】

アクティブマトリクス基板301の中央には、画素部304が配置されている。画素部304の上側には、ソース信号線を駆動するためのソース信号線駆動回路302が配置されている。画素部304の左右には、ゲート信号線を駆動するためのゲート信号線駆動回路303が配置されている。本実施例に示した例では、ゲート信号線駆動回路303は画素部に対して左右対称配置としているが、これは片側のみの配置でも良く、液晶モジュールの基板サイズ等を考慮して、設計者が適宜選択すれば良い。ただし、回路の動作信頼性や駆動効率等を考えると、図6に示した左右対称配置が望ましい。

40

#### 【0135】

各駆動回路への信号の入力は、フレキシブルプリント基板（Flexible Print Circuit：FPC）305から行われる。FPC305は、基板301の所定の場所まで配置された配線に達するように、層間絶縁膜および樹脂膜にコンタクトホールを開口し、接続電極309を形成した後、異方性導電膜等を介して圧着される。本実施例

50

においては、接続電極はITOを用いて形成した。

【0136】

駆動回路、画素部の周辺には、基板外周に沿ってシール剤307が塗布され、あらかじめアクティブマトリクス基板上に形成されたスペーサ310によって一定のギャップ（基板301と対向基板306との間隔）を保った状態で、対向基板306が貼り付けられる。その後、シール剤307が塗布されていない部分より液晶素子が注入され、封止剤308によって密閉される。以上の工程により、液晶モジュールが完成する。

【0137】

また、ここでは全ての駆動回路を基板上に形成した例を示したが、駆動回路の一部に数個のICを用いてもよい。

10

【0138】

また、本実施例は、実施の形態、または実施例1と自由に組みあわせることが可能である。

【0139】

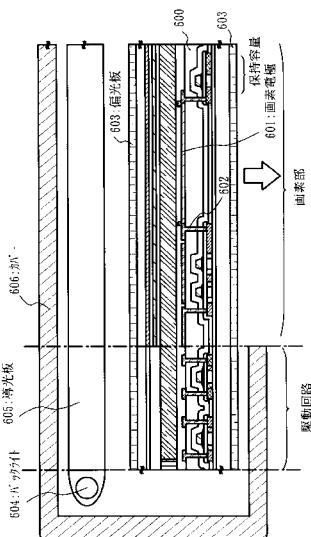

[実施例3]

実施例1では画素電極が反射性を有する金属材料で形成された反射型の表示装置の例を示したが、本実施例では画素電極を透光性を有する導電膜で形成した透過型の表示装置の例を示す。

【0140】

層間絶縁膜を形成する工程までは実施例1と同じであるので、ここでは省略する。実施例1に従って層間絶縁膜を形成した後、透光性を有する導電膜からなる画素電極601を形成する。透光性を有する導電膜としては、ITO（酸化インジウム酸化スズ合金）、酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub>—ZnO）、酸化亜鉛（ZnO）等を用いればよい。

20

【0141】

その後、層間絶縁膜600にコンタクトホールを形成する。次いで、画素電極と重なる接続電極602を形成する。この接続電極602は、コンタクトホールを通じてドレン領域と接続されている。また、この接続電極と同時に他のTFTのソース電極またはドレン電極も形成する。

【0142】

また、ここでは全ての駆動回路を基板上に形成した例を示したが、駆動回路の一部に数個のICを用いてもよい。

30

【0143】

以上のようにしてアクティブマトリクス基板が形成される。このアクティブマトリクス基板を用い、実施例2に従って液晶モジュールを作製し、バックライト604、導光板605を設け、カバー606で覆えば、図7にその断面図の一部を示したようなアクティブマトリクス型液晶表示装置が完成する。なお、カバーと液晶モジュールは接着剤や有機樹脂を用いて貼り合わせる。また、基板と対向基板を貼り合わせる際、枠で囲んで有機樹脂を枠と基板との間に充填して接着してもよい。また、透過型であるので偏光板603は、アクティブマトリクス基板と対向基板の両方に貼り付ける。

40

【0144】

また、本実施例は、実施の形態、実施例1、または実施例2と自由に組みあわせることが可能である。

【0145】

[実施例4]

本実施例では、有機発光素子（OLED：Organic Light Emission Device）を備えた発光表示装置を作製する例を図8に示す。

【0146】

OLEDは、電場を加えることで発生するルミネッセンス（Electroluminescence）が得られる有機化合物（有機発光材料）を含む層（以下、有機発光層と記

50

す)と、陽極と、陰極とを有している。有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とがあるが、本発明の発光装置は、上述した発光のうちの、いずれか一方の発光を用いていても良いし、または両方の発光を用いていても良い。

#### 【0147】

なお、本明細書では、OLEDの陽極と陰極の間に形成された全ての層を有機発光層と定義する。有機発光層には具体的に、発光層、正孔注入層、電子注入層、正孔輸送層、電子輸送層等が含まれる。基本的にOLEDは、陽極/発光層/陰極が順に積層された構造を有しており、この構造に加えて、陽極/正孔注入層/発光層/陰極や、陽極/正孔注入層/発光層/電子輸送層/陰極等の順に積層した構造を有していることもある。

10

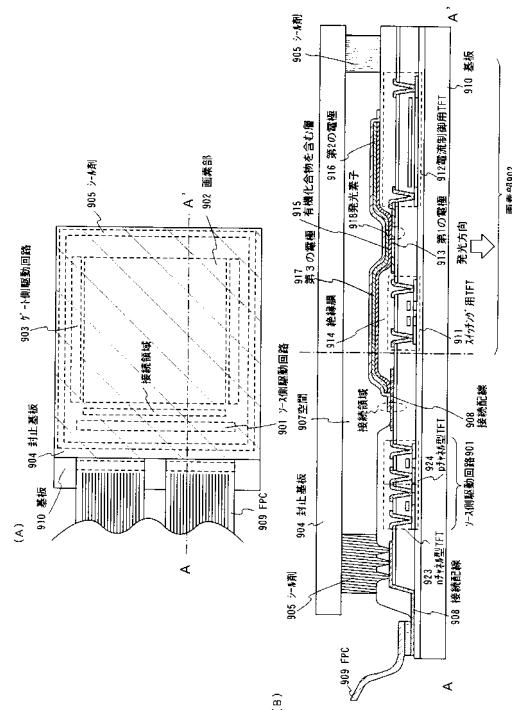

#### 【0148】

図8にアクティブマトリクス型発光装置の外観図について説明する。なお、図8(A)は、発光装置を示す上面図、図8(B)は図8(A)をA-A'で切断した断面図である。点線で示された901はソース信号線駆動回路、902は画素部、903はゲート信号線駆動回路である。これらの画素部や駆動回路は、上記実施例に従えば得ることができる。また、904は封止基板、905はシール剤であり、シール剤905で囲まれた内側は、空間907になっている。なお、空間ではなく、透明なシール剤を充填してもよい。

#### 【0149】

なお、908はソース信号線駆動回路901及びゲート信号線駆動回路903に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)909からビデオ信号やクロック信号を受け取る。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基盤(PWB)が取り付けられても良い。本明細書における発光装置には、発光装置本体だけでなく、それにFPCもしくはPWBが取り付けられた状態をも含むものとする。また、これらの画素部や駆動回路と同一基板上に複雑な集積回路(メモリ、CPU、コントローラ、D/Aコンバータ等)を形成することも可能であるが、少ないマスク数での作製は困難である。従って、メモリ、CPU、コントローラ、D/Aコンバータ等を備えたICチップを、COG(chip on glass)方式やTAB(tape automated bonding)方式やワイヤボンディング方法で実装することが好ましい。

20

#### 【0150】

次に、断面構造について図8(B)を用いて説明する。基板910上には駆動回路及び画素部が形成されているが、ここでは、駆動回路としてソース信号線駆動回路901と画素部902が示されている。

30

#### 【0151】

なお、ソース信号線駆動回路901はnチャネル型TFT923とpチャネル型TFT924とを組み合わせたCMOS回路が形成される。また、駆動回路を形成するTFTは、公知のCMOS回路、PMOS回路もしくはNMOS回路で形成しても良い。また、本実施例では、基板上に駆動回路を形成したドライバー一体型を示すが、必ずしもその必要はなく、基板上ではなく外部に形成することもできる。

40

#### 【0152】

また、画素部902はスイッチング用TFT911と、電流制御用TFT912とそのドレインに電気的に接続された第1の電極(陽極)913を含む複数の画素により形成される。なお、ここではトップゲート型TFTを用いた例を示したが、TFTの構造に限定されず、例えばボトムゲート型TFTを用いることも可能である。

#### 【0153】

また、第1の電極(陽極)913の両端には絶縁層914が形成され、第1の電極(陽極)913上には有機化合物層915が形成される。さらに、有機化合物層915上には同一波形形状であり、端面が一致する第2の電極(陰極)916が形成される。これにより、第1の電極(陽極)913、有機化合物層915、及び第2の電極(陰極)916からなる発光素子918が形成される。ここでは発光素子918は白色発光とする例であ

50

るので着色層とB Mからなるカラーフィルター（簡略化のため、ここでは図示しない）を基板910に設ける。

【0154】

ここでは、第2の電極916と接続配線908との電気的接続を行うため、実施の形態4に示した第3の電極917を形成する。第2の電極916および接続配線908と接する第3の電極917は、全画素に共通の配線としても機能し、接続配線908を経由してFPC909に電気的に接続されている。

【0155】

また、基板910上に形成された発光素子918を封止するためにシール剤905により封止基板904を貼り合わせる。なお、封止基板904と発光素子918との間隔を確保するために樹脂膜からなるスペーサを設けても良い。そして、シール剤905の内側の空間907には窒素等の不活性気体が充填されている。なお、シール剤905としてはエポキシ系樹脂を用いるのが好ましい。また、シール剤905はできるだけ水分や酸素を透過しない材料であることが望ましい。さらに、空間907の内部に酸素や水を吸収する効果をもつ物質を含有させても良い。

【0156】

また、本実施例では封止基板904を構成する材料としてガラス基板や石英基板の他、FRP(Fiberglass-Reinforced Plastics)、PVF(ポリビニルフロライド)、マイラー、ポリエステルまたはアクリル等からなるプラスチック基板を用いることができる。また、シール剤905を用いて封止基板904を接着した後、さらに側面(露呈面)を覆うようにシール剤で封止することも可能である。

【0157】

以上のようにして発光素子を空間907に封入することにより、発光素子を外部から完全に遮断することができ、外部から水分や酸素といった有機化合物層の劣化を促す物質が侵入することを防ぐことができる。従って、信頼性の高い発光装置を得ることができる。

【0158】

また、OLEDを有する表示装置においては、OLEDに一定の電圧を印加して電流を供給するように回路設計を行った駆動方法や、OLEDに一定の電流が供給されるようにOLEDに印加する電圧を調節するように回路設計を行った駆動方法や、OLEDに一定の電流が供給されるように回路設計を行った駆動方法などがあるが、駆動方法によらず、OLEDと電気的に接続され、且つ、OLEDに電流を供給するTFT(本明細書中、このTFT912を電流制御用TFTと呼ぶ)のオン電流(I<sub>on</sub>)で画素の輝度が決定される。従って、各TFTのオン電流が一定でなければ輝度にバラツキが生じてしまうという問題があった。これらの問題は、本発明により解決できる。

【0159】

また、金属材料からなる画素電極を陽極として、EL層と透光性を有する導電材料からなる陰極を積層して図8とは逆方向に発光する構成としてもよい。また、画素電極を陰極とし、EL層と陽極を積層して図8とは逆方向に発光する構成としてもよい。

【0160】

本実施例は実施の形態、実施例1と自由に組み合わせることができる。

【0161】

[実施例5]

本発明を実施して形成された駆動回路や画素部は様々なモジュール(アクティブマトリクス型液晶モジュール、アクティブマトリクス型ELモジュール、アクティブマトリクス型ECモジュール)に用いることができる。即ち、本発明を実施することによって、それらを組み込んだ全ての電子機器が完成される。

【0162】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パソコンコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍

10

20

30

40

50

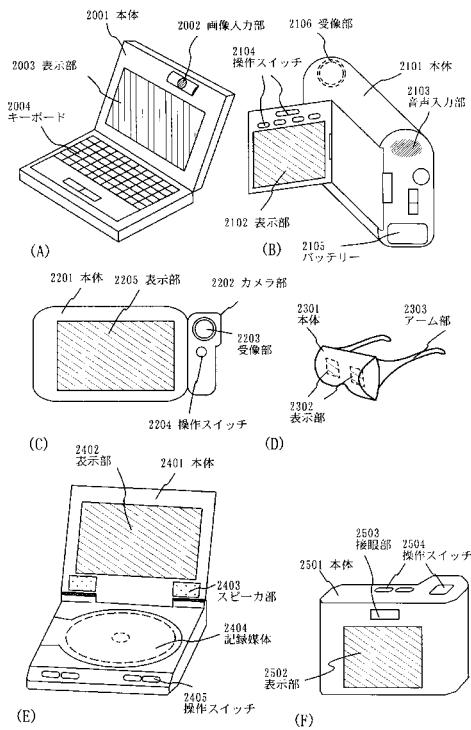

等)などが挙げられる。それらの一例を図9、図10に示す。

【0163】

図9(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。

【0164】

図9(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。

【0165】

図9(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205等を含む。 10

【0166】

図9(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303等を含む。

【0167】

図9(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405等を含む。なお、このプレーヤーは記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。 20

【0168】

図9(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。

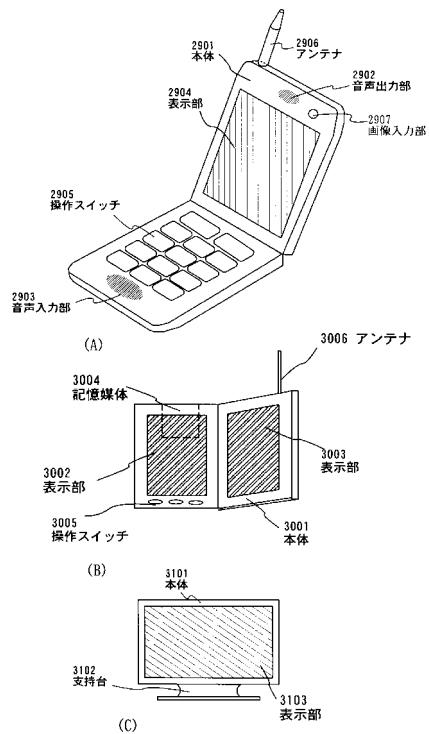

【0169】

図10(A)は携帯電話であり、本体2901、音声出力部2902、音声入力部2903、表示部2904、操作スイッチ2905、アンテナ2906、画像入力部(CCD、イメージセンサ等)2907等を含む。

【0170】

図10(B)は携帯書籍(電子書籍)であり、本体3001、表示部3002、3003、記憶媒体3004、操作スイッチ3005、アンテナ3006等を含む。 30

【0171】

図10(C)はディスプレイであり、本体3101、支持台3102、表示部3103等を含む。

【0172】

ちなみに図10(C)に示すディスプレイは中小型または大型のもの、例えば5~20インチの画面サイズのものである。また、このようなサイズの表示部を形成するためには、基板の一辺が1mのものを用い、多面取りを行って量産することができる。 40

【0173】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器の作製方法に適用することが可能である。また、本実施例の電子機器は、実施の形態、実施例1乃至4のどのような組み合わせからなる構成を用いても実現することができる。

【0174】

【発明の効果】

本発明により、十分に結晶化を助長する金属元素が低減または除去された結晶構造を有する半導体膜を得ることができ、該半導体膜を活性層とするTFTにおいて電気特性の向上、及び、個々の素子間でのバラツキを低減することができる。特に、液晶表示装置においては、TFT特性のバラツキに起因する表示むらを低減できる。

【0175】

加えて、OLEDを有する半導体装置においては、画素電極に一定の電流が流れるように配置されたTFT(駆動回路または画素に配置されるOLEDに電流を供給するTFT)のオン電流( $I_{on}$ )のバラツキを低減することができ、輝度のバラツキを低減できる。 50

## 【0176】

また、本発明により結晶化を助長する金属元素だけでなく、不純物となる他の金属元素（Fe、Cuなど）も除去または低減することができる。

## 【図面の簡単な説明】

【図1】実施の形態1を示す工程断面図である。

【図2】実施の形態2を示す工程断面図である。

【図3】工程断面図を示す図である。

【図4】工程断面図を示す図である。

【図5】工程断面図を示す図である。

【図6】液晶表示装置の上面図を示す図である。

10

【図7】アクティブマトリクス型液晶表示装置の断面構造図である。

【図8】発光装置の上面図および断面図を示す図である。

【図9】電子機器の一例を示す図。

【図10】電子機器の一例を示す図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 叁 8 】

【図9】

【 図 1 0 】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 0 1 L 29/78 6 2 7 Z

F ターム(参考) 2H092 GA29 GA50 GA59 JA25 JA26 JA46 KA05 KA10 KA11 KA19

KB25 MA04 MA05 MA07 MA08 MA10 MA13 MA17 MA27 MA29

MA30 NA22 NA24 NA25 PA02 PA03 PA04 PA06 PA08 PA09

PA10 PA11 PA13 RA05 RA10

5F052 AA02 AA17 AA24 BA02 BB02 BB07 DA02 DA03 DB02 DB03

DB07 EA12 EA15 EA16 FA06 FA19 HA06 JA01 JA04

5F110 AA01 BB01 BB02 BB04 CC02 CC05 CC07 DD01 DD02 DD03

DD05 DD13 DD14 DD15 DD17 EE01 EE02 EE03 EE04 EE05

EE06 EE09 EE14 EE15 EE23 EE28 FF04 FF12 FF30 GG01

GG02 GG13 GG25 GG32 GG33 GG34 GG43 GG45 GG47 GG51

HJ01 HJ04 HJ12 HJ13 HJ23 HL03 HL04 HL06 HL11 HM15

NN02 NN03 NN04 NN23 NN24 NN27 NN35 NN72 PP01 PP02

PP03 PP04 PP05 PP10 PP13 PP27 PP29 PP34 QQ04 QQ21

QQ23 QQ25 QQ28