(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 100 85 347 B4 2009.04.09

(12)

## Patentschrift

(21) Deutsches Aktenzeichen: 100 85 347.1

(86) PCT-Aktenzeichen: PCT/US00/31352

(87) PCT-Veröffentlichungs-Nr.: WO 2001/046989

(86) PCT-Anmeldetag: 13.11.2000

(87) PCT-Veröffentlichungstag: 28.06.2001

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: 30.01.2003

(45) Veröffentlichungstag

der Patenterteilung: 09.04.2009

(51) Int Cl.<sup>8</sup>: H01L 27/08 (2006.01)

H01L 23/58 (2006.01)

H01L 29/94 (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

09/469,406 22.12.1999 US

(73) Patentinhaber:

Intel Corporation, Santa Clara, Calif., US

(74) Vertreter:

ZENZ Patent- und Rechtsanwälte, 45128 Essen

(72) Erfinder:

Keshavarzi, Ali, Portland, Oreg., US; De, Vivek K., Beaverton, Oreg., US; Karnik, Tanay, Portland, Oreg., US; Nair, Rajendran, Hillsboro, Oreg., US

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

GB 21 38 206 A

US 59 65 928 A

US 53 41 009 A

US 50 32 892

(54) Bezeichnung: **Verwendung einer MOS-Struktur als Entstörkondensator bei dünnen Gate-Oxiden**

(57) Hauptanspruch: Verfahren zum Verwenden einer MOS-Struktur (134) als Entstörkapazität zwischen einem ersten, die Versorgungsspannung ( $V_{CC}$ ) einer auf einem Halbleiterchip integrierten Schaltung (130) führenden Leiter und einem zweiten, die Massespannung ( $V_{SS}$ ) führenden Leiter, wobei die MOS-Struktur (50, 60, 100, 110) in einem Substrat oder in einer in dem Substrat eingebrachten Wanne mit einem Source-Gebiet (S), einem Drain-Gebiet (D) und einem zwischen dem Source- und dem Drain-Gebiet angeordneten Gate (G), das aus einem über einer Gate-Isolatorschicht angeordneten Gate-Leiter besteht, angeordnet ist, wobei der Gate-Leiter mit dem ersten oder zweiten Leiter verbunden ist und das Source-Gebiet (S), das Drain-Gebiet und das Substrat bzw. die Wanne (B-Bulk) mit dem anderen Leiter verbunden sind, so dass die MOS-Struktur eine Kapazität zwischen den beiden Leitern bildet, wobei die MOS-Struktur so mit den beiden Leitern verbunden wird, dass bei den anliegenden Spannungen ( $V_{CC}, V_{SS}$ ) die MOS-Struktur sich im Verarmungsmodus befindet, so dass nur wenige...

## Beschreibung

**[0001]** Die Erfindung bezieht sich auf ein Verfahren zum Verwenden einer MOS-Struktur als Entstörkapazität in integrierten Schaltungen.

**[0002]** Entstörkondensatoren ("Decaps") werden bei der Entwicklung von integrierten Schaltungen (IC) zur Rauschentstörung verwendet. Sie werden tatsächlich in nahezu allen IC's häufig eingesetzt. Eine Art von Halbleiterkondensatoren wird MOS-C oder Metall-Oxid-Halbleiter-Kondensator genannt. Der MOS-C weist zwei durch ein dielektrisches Gebiet (das mindestens einen Isolator aufweist, wie z. B. ein Gate-Oxid) getrennte Anschlüsse auf. Einer der Anschlüsse ist das Gate und der andere ist das Substrat (und möglicherweise Source- und Drain-Diffusionsgebiete). Eine andere Art eines Halbleiterkondensators verwendet einen Feldeffekt-Transistor (FET), wie z. B. einen n-Kanal-Metall-Oxid-Halbleiter-FET (n-MOSFET) oder einen p-Kanal-Metall-Oxid-Halbleiter-FET (p-MOSFET). Einer der Anschlüsse ist das Gate und der andere Anschluß besteht aus Source, Drain und Substrat. Die Anschlüsse sind durch ein Dielektrikum getrennt (das mindestens einen Isolator umfaßt, wie z. B. ein Gate-Oxid). Ein Unterschied zwischen einem MOS-C und einem FET-Kondensator ist, daß bei einem FET Source und Drain andere Polaritäten als das Substrat haben. Bei einem MOS-C haben die Source/Drain-Diffusionsgebiete (wenn vorhanden) die gleiche Polarität wie das Substrat. Das Verhalten von Kondensatoren in integrierten Schaltungen wird in R. Pierret et al., "Field Effect Devices," (Addison-Wesley, 2. Auflage 1990), Seiten 47–59; und in N. Weste et al., "Principles of CMOS VLSI Design," (Addison-Wesley, 2. Auflage 1993), Seiten 180–82 beschrieben.

**[0003]** Andere Entstörkondensatoren, wie z. B. zwischen zwei Metalleitungen eingeschichtete Kondensatoren mit einem Isolator mit hoher Dielektrizitätskonstante sind ebenfalls möglich. Jedoch werden die Materialherausforderung und die Integration in heutige MOS-Technologien sehr schwierig.

**[0004]** Die Kapazität eines Kondensators ist durch die Gleichung  $C = \epsilon A/d$  gegeben, wobei  $\epsilon$  die Dielektrizitätskonstante, A die Fläche und d der Abstand ist. Es ist wünschenswert, daß bei dem Entwurf der ICs die Abmessungen der Bauelemente klein gehalten werden. Dementsprechend wurde die Fläche A der Kondensatoren mit den Jahren kleiner, während der Abstand d zwischen den Elektroden ebenfalls kleiner wurde. Gegenwärtig verwendete Kondensatorstrukturen arbeiten im allgemeinen recht gut mit dichten (non-leaking) Oxiden. An die gegenwärtigen Entstörkondensatorstrukturen werden Spannungen angelegt, um die MOS-C im Inversionszustand zu halten, wodurch eine maximale flächenbezogene Kapazität mit guter Hochfrequenz-Antwortzeit und geringem Reihenwiderstand erreicht wird. Während sich die Prozeßtechnologie verkleinert, verkleinern sich ebenfalls die Dicken der Gate-Oxide, um Transistoren mit guten Stromsteuerfähigkeiten und gutem Kurzkanalverhalten zu erhalten. Während sich die Gate-Oxide weiter verringerten, führte diese kapazitive Konfiguration zu hohen Leckströmen durch die Oxide (z. B. zunehmende Tunnelverluste).

**[0005]** Die Patentschrift US 5,032,892 A beschreibt einleitend, dass das Risiko eines Gateoxid-Durchbruchs aufgrund hoher Feldstärken verringert werden kann, indem unter dem Gateoxid eine an beweglichen Ladungsträgern verarmte Schicht geschaffen wird, indem eine Implantation von Dotanden des entgegengesetzten Leitfähigkeitstyps vorgenommen wird. Die Veröffentlichung GB 2 138 206 A beschreibt einen variablen Kondensator, dessen Kapazität unabhängig von der anliegenden Signalspannung sein soll, und schlägt die Stabilisierung des Kapazitätswerts durch Erzeugen einer Verarmungsschicht (Sperrschiicht) tief im Halbleitersubstrat vor. Die Patentschrift US 5,965,928 A befasst sich mit der Schaffung eines MOS-Kondensators, dessen Kapazität bei höheren Frequenzen unabhängig von der anliegenden Spannung (und Polarität) ist. Es wird hier die Parallel-Schaltung zweier Teilkondensatoren mit entgegengesetztem Leitfähigkeitstyp in dem oberflächennahen Halbleitersubstrat vorgeschlagen.

**[0006]** Aufgabe der Erfindung ist es, bei einer Verwendung als Entstörkondensator eingesetzten MOS-Struktur mit dünnem Gate-Oxid die Leckströme zu verringern.

**[0007]** Diese Aufgabe wird erfindungsgemäß durch ein Verfahren mit den Merkmalen des Anspruchs 1 gelöst. Weiterbildungen der Erfindung sind in den Unteransprüchen gekennzeichnet.

**[0008]** Verschiedene Konfigurationen können eingesetzt werden, einschließlich: n<sup>+</sup>-Poly-Gate und n<sup>+</sup>-Source/Drain-Gebiete in einem n-Substrat; p<sup>+</sup>-Poly-Gate und n<sup>+</sup>-Source/Drain-Gebiete in einem n-Substrat; p<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebiete in einem n-Substrat; p<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebiete in einem p-Substrat; n<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebiete in einem p-Substrat; n<sup>+</sup>-Poly-Gate und n<sup>+</sup>-Source/Drain-Gebiete in einem p-Substrat.

[0009] Die Erfindung wird anhand der folgenden ausführlichen Beschreibung und der begleitenden Zeichnungen näher beschrieben.

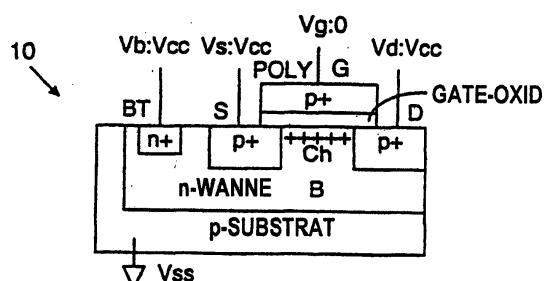

[0010] [Fig. 1](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit p<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebieten in einer n-Wanne im Inversionsmodus (Stand der Technik).

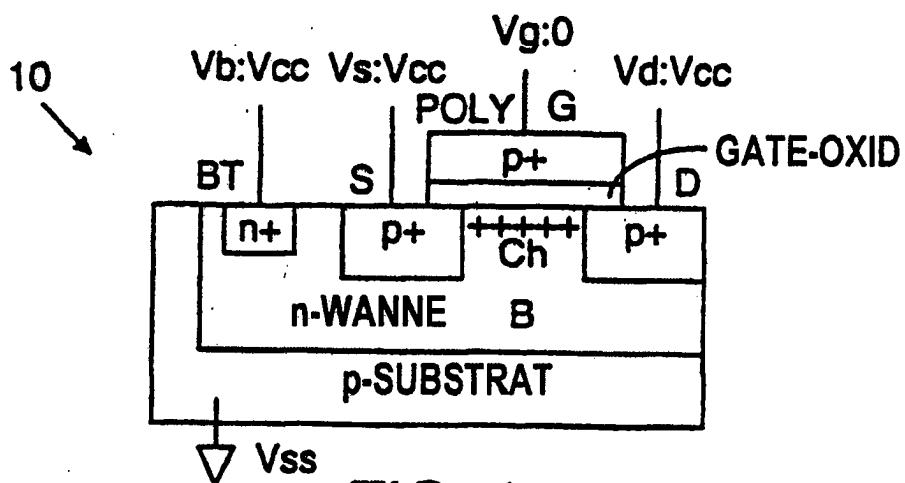

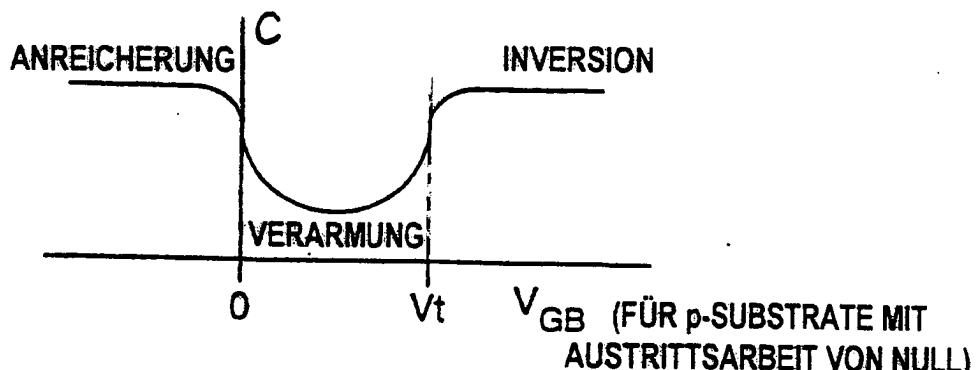

[0011] [Fig. 2](#) zeigt eine graphische Auftragung der Kapazität über der Gate-Substrat-Spannung für Kondensatoren mit n-Substraten mit einer verschwindenden Austrittsarbeit.

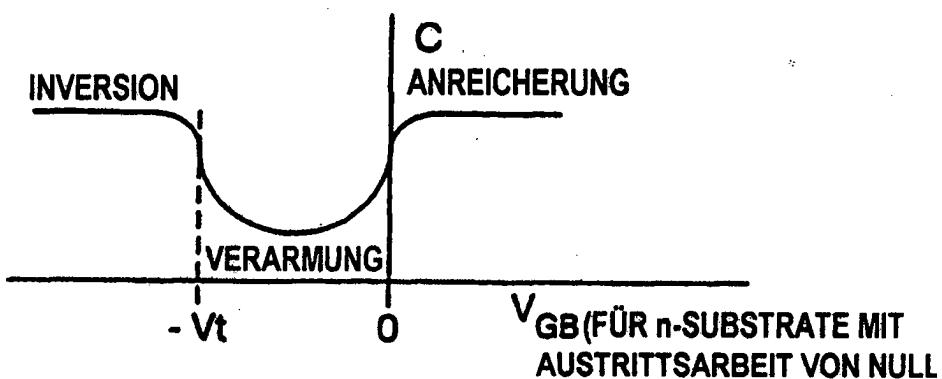

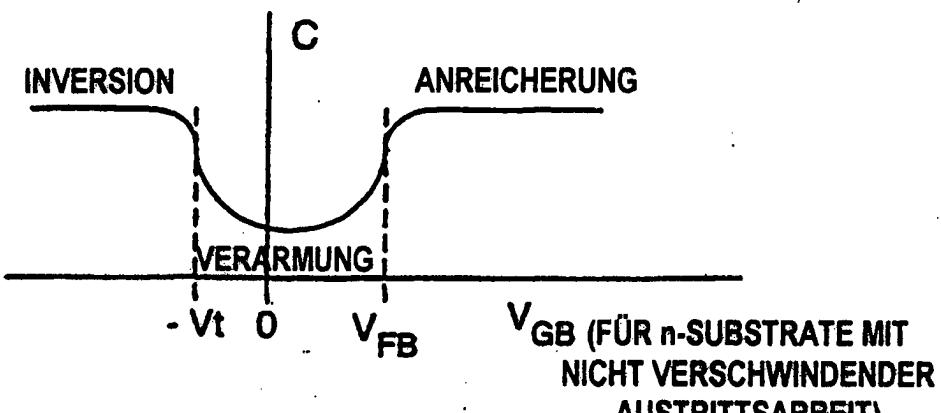

[0012] [Fig. 3](#) zeigt eine graphische Auftragung der Kapazität über der Gate-Substrat-Spannung für Kondensatoren mit n-Substraten mit einer nicht-verschwindenden Austrittsarbeit.

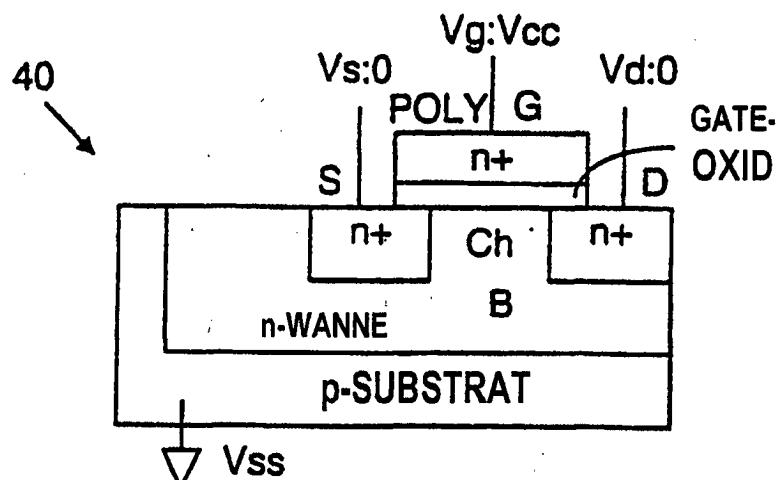

[0013] [Fig. 4](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit p<sup>+</sup>-Poly-Gate und n<sup>+</sup>-Source/Drain-Gebieten in einer n-Wanne.

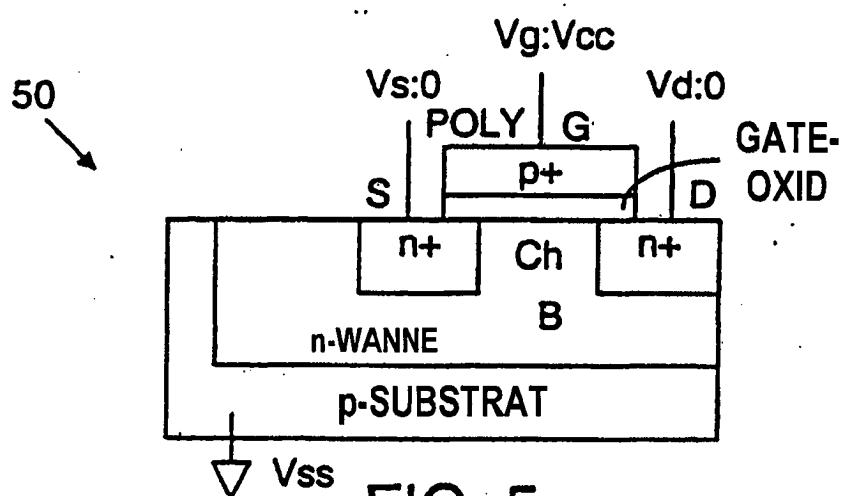

[0014] [Fig. 5](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit p<sup>+</sup>-Poly-Gate und n<sup>+</sup>-Source/Drain-Gebieten in einer n-Wanne.

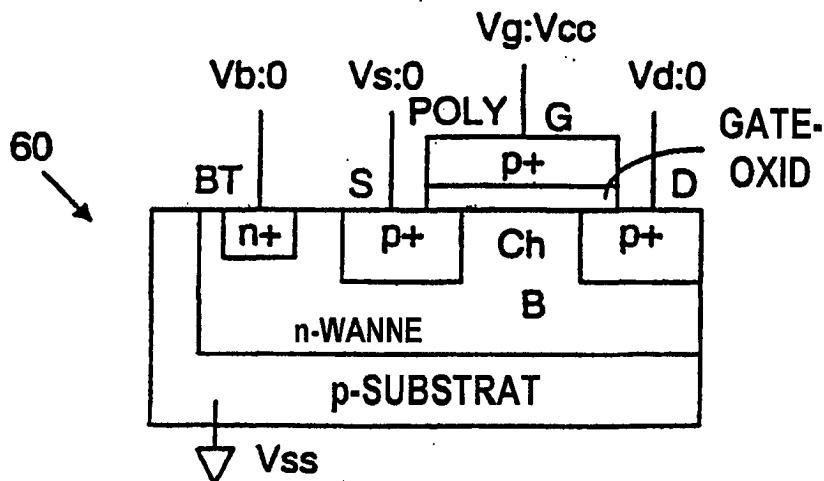

[0015] [Fig. 6](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit p<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebieten in einer n-Wanne.

[0016] [Fig. 7](#) zeigt eine graphische Auftragung der Kapazität über der Gate-Substrat-Spannung für Kondensatoren mit p-Substraten mit verschwindender Austrittsarbeit.

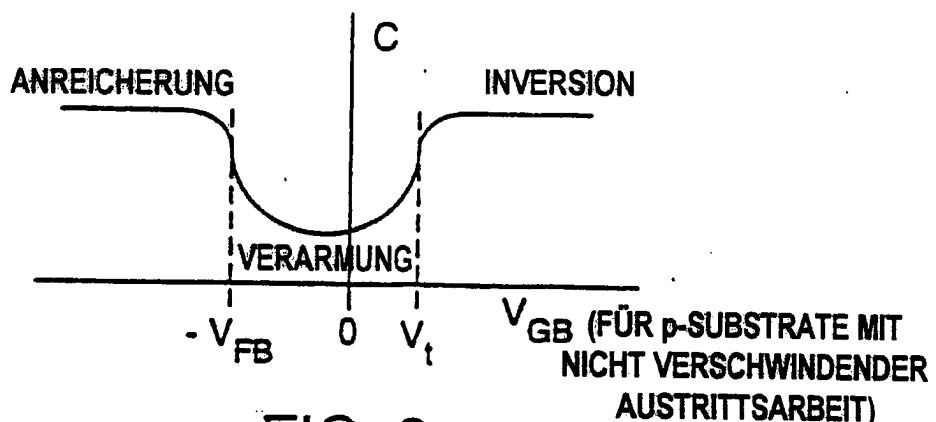

[0017] [Fig. 8](#) zeigt eine graphische Auftragung der Kapazität über der Gate-Substrat-Spannung für Kondensatoren mit p-Substraten mit nicht-verschwindender Austrittsarbeit.

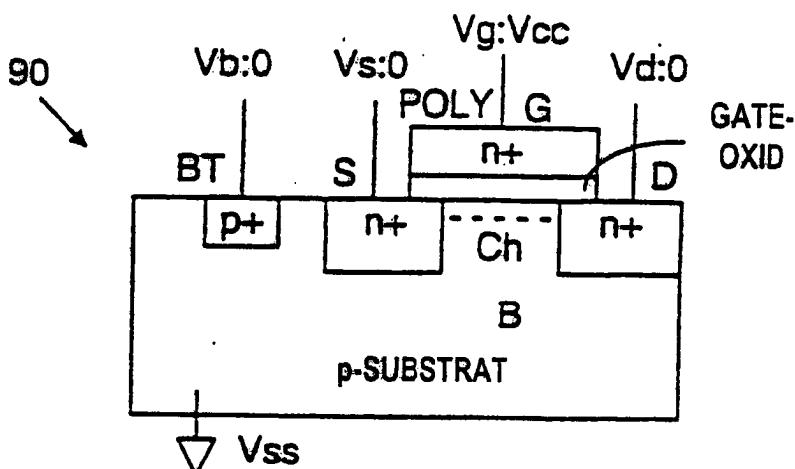

[0018] [Fig. 9](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit n<sup>+</sup>-Gate und n<sup>+</sup>-Source/Drain-Gebieten in einem p-Substrat im Inversionsmodus (Stand der Technik).

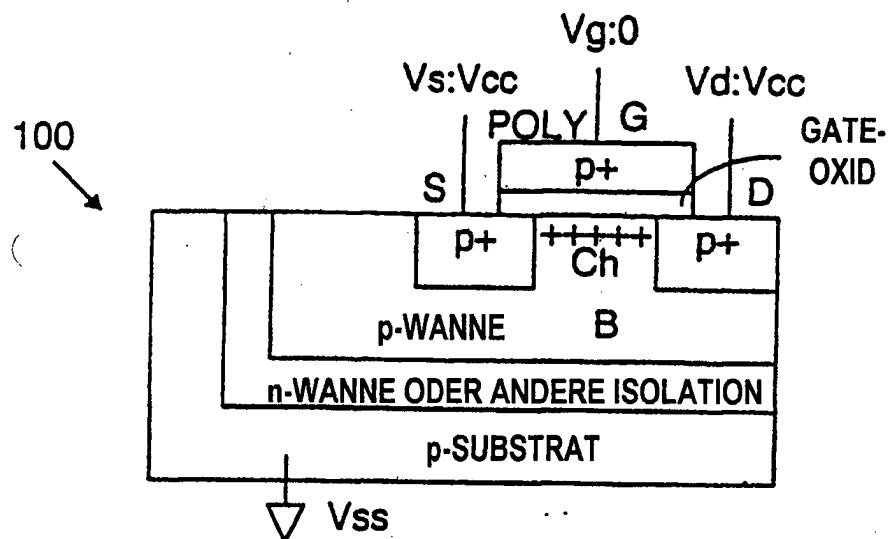

[0019] [Fig. 10](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit p<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebieten in einer p-Wanne.

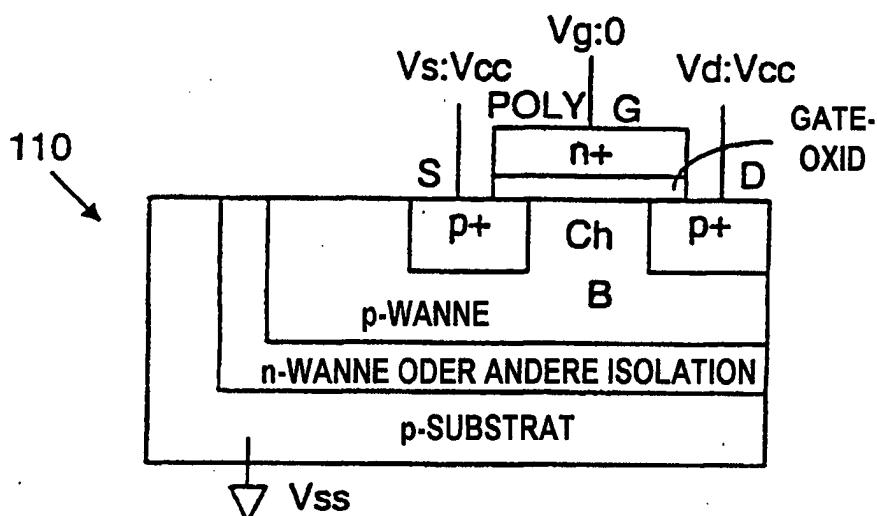

[0020] [Fig. 11](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit n<sup>+</sup>-Poly-Gate und p<sup>+</sup>-Source/Drain-Gebieten in einer p-Wanne.

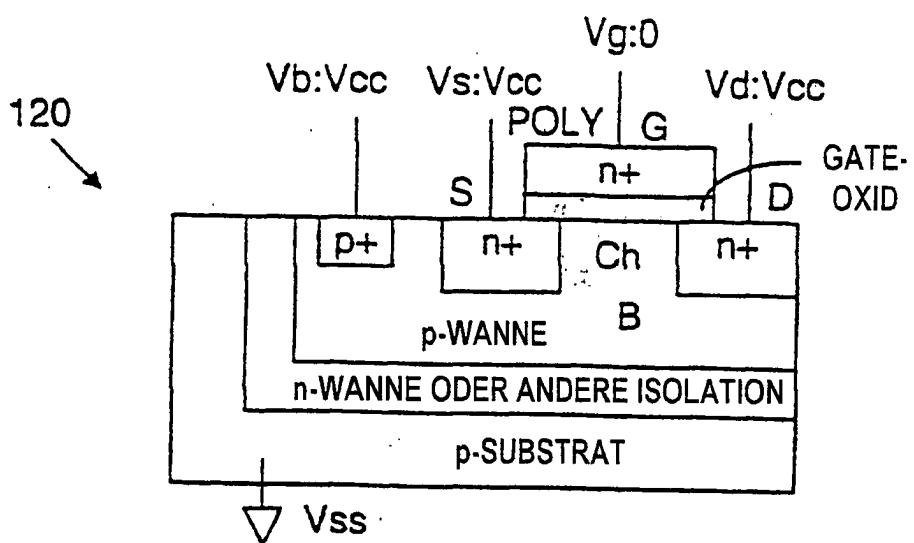

[0021] [Fig. 12](#) zeigt eine schematische Querschnittsansicht eines Kondensators mit n<sup>+</sup>-Poly-Gate und n<sup>+</sup>-Source/Drain-Gebieten in einer p-Wanne.

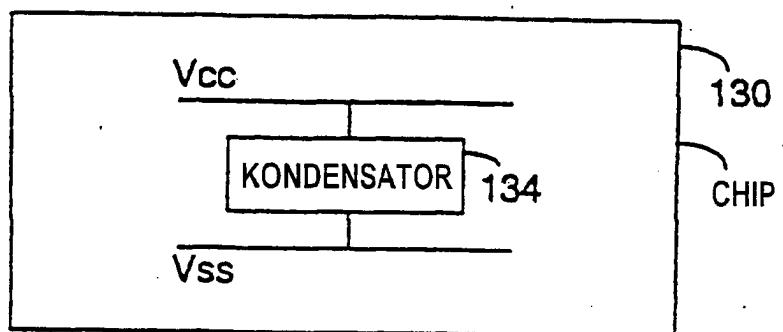

[0022] [Fig. 13](#) zeigt eine Blockdarstellung eines Chips mit einem Entstörkondensator zwischen Vcc und Vss.

[0023] Die Erfindung beruht auf Halbleiterkondensatoren (Transistor- oder MOS-C), die in einem Verarmungsmodus betrieben werden, um Verluste durch den Isolator (z. B. das Gate-Oxid) zu vermindern. Dies ist nicht naheliegend, weil der Betrieb im Verarmungsmodus die flächenbezogene Kapazität verringert. Um diese Verringerung der Kapazität wettzumachen, kann die Fläche vergrößert werden, was unerwünscht ist. Bei der Erschaffung der Erfindung bemerkten die Erfinder, daß die Anzahl der Ladungsträger beim Betrieb im Verarmungsmodus kleiner ist; daher tritt ein geringerer Tunnelstrom in Gate-Oxid auf und somit geringere Verluste.

[0024] Im allgemeinen ist es die Idee, von der Benutzung eines MOS-C-Kondensators, der aus einer MOS-Transistorstruktur, die im Inversionsmodus arbeitet, abgeleitet ist, abzurücken. Der alternative Vorschlag besteht darin, eine das Gate-Oxid als Isolator verwendende, im Verarmungsmodus betriebene Kondensatorstruktur zu verwenden. Die effektive Kapazität vermindert sich um etwa 25% (abgeschätzt), während sich die Verluste (Leck) bei einer Versorgungsspannung von etwa 1 Volt etwa um den Faktor 100 verringern. Die Verringerung der Kapazität ist in den C-V-Kurven zu beobachten, wenn der Kondensator im Verarmungsmodus vorgespannt ist (nahe dem Anreicherungsbereich). Die Verringerung der Verluste ist Folge der Tatsache, daß nun weniger Ladungsträger in dem verarmten Kanal unter dem Gate-Oxid vorhanden sind, die durch das dünne Gate-Oxid tunneln können. Der Q-Faktor eines solchen Kondensators ist ähnlich dem eines in Inversion befindlichen MOS-Transistor-Caps, insbesondere wenn man sich nicht auf die Generierung von Minoritätsladungsträgern und die Rekombination verläßt, um die Ladungsträger zur Verfügung zu stellen, die benötigt werden, um auf das Wechselstromsignal zu reagieren, das dem Decap überlagert ist. Die verminderte Kapazität

kann immer durch die Verwendung etwas größerer Kondensatorflächen kompensiert werden, wenn man den Leckstrom durch den Decap um mehr als eine Größenordnung verringern soll hat.

### Entstörkondensatoren mit n-Substrat

**[0025]** Gemäß [Fig. 1](#) weist ein PMOS-Transistorkondensator **10** nach dem Stand der Technik ein p-Substrat, eine n-Wanne, eine p<sup>+</sup>-Source S, ein p<sup>+</sup>-Drain D, eine p<sup>+</sup>-Polysilizium-Gate-Elektrode (Poly) G und einen n<sup>+</sup>-Substratabgriff BT für ein Substrat B (Body) auf. Gemäß der Terminologie der vorliegenden Offenbarung wird der Transistorkondensator **10** ein p<sup>+</sup>/p<sup>+</sup>-Cap auf n-Substrat (n-Wanne) genannt, wobei das erste p<sup>+</sup> die Poly-Art anzeigt und das zweite p<sup>+</sup> die Art der S/D-Gebiete anzeigt. Es ist zu beachten, daß es im Falle einer Kondensatorstruktur nicht besonders sinnvoll ist, ein Diffusionsgebiet als Source und das andere als Drain zu bezeichnen, jedoch wird dies aus Vereinfachungsgründen in der Terminologie getan. Eine Oberfläche **12** befindet sich unmittelbar unterhalb des Gate-Oxids. Ein Kanal Ch befindet sich unter der Oberfläche des Gate-Oxids. In der vorliegenden Offenbarung wird dieser Bereich auch im Falle einer MOS-Struktur Kanal genannt, obwohl diese kein Transistor ist. An den Transistorkondensator **10** werden die Spannungen wie folgt angelegt: Die Substratspannung V<sub>b</sub> liegt an der Versorgungsspannung V<sub>cc</sub> (manchmal als V<sub>dd</sub> bezeichnet), die Source/Drain-Spannungen V<sub>s</sub> und V<sub>d</sub> liegen beide an V<sub>cc</sub> und die Gate-Spannung V<sub>g</sub> und das p-Substrat liegen beide auf Masse (als V<sub>ss</sub> oder 0 bezeichnet). Das Substrat kann von der Unterseite, von der Oberseite oder von irgendwo sonst auf Masse gelegt sein. In [Fig. 1](#) ist V<sub>g</sub> an V<sub>ss</sub> angebunden. [Fig. 2](#) zeigt die Auftragung der Kapazität über der Gate-Substrat-Spannung V<sub>GB</sub> für n-Substrat-(z. B. n-Wannen-)Kondensatorstrukturen mit einer Austrittsarbeit von Null, da das Poly und das Substrat von der gleichen Art sind. Es ist zu beachten, daß eine Drain- und Source-Spannung gleich der Substrat-Spannung sein könnte. Die Auftragung soll nur allgemeine Zusammenhänge und nicht präzise Werte oder Formen zeigen. Die tatsächliche Kurve kann etwas anders aussehen. Weiterhin kann sich die Form der Kurve bei verschiedenen Frequenzen ändern. Es ist zu erkennen, daß die Kapazität bei der Anreicherung und Inversion größer und bei Verarmung niedriger ist. V<sub>t</sub> ist eine Schwellspannung. Obwohl im allgemeinen die Grenzen zwischen Anreicherungs-, Verarmungs- und Inversionsmodus nicht exakt sind, tritt der Anreicherungsmodus auf, wenn 0 < V<sub>GB</sub> ist, der Verarmungsmodus tritt auf, wenn -V<sub>t</sub> < V<sub>GB</sub> < 0 ist, und der Inversionsmodus tritt auf, wenn V<sub>GB</sub> < -V<sub>t</sub> ist.

**[0026]** [Fig. 3](#) zeigt die Auftragung einer Kapazität über der Gate-Substrat-Spannung V<sub>GB</sub> für n-Substrat-Kondensatorstrukturen mit einer nicht-verschwindenden (ungleich Null) Austrittsarbeit (die Flachbandspannung V<sub>FB</sub> ist ungleich Null), weil das Poly und das Substrat von unterschiedlicher Art sind. Die Kurve soll nur allgemeine Zusammenhänge und nicht präzise Werte oder Formen zeigen. Die tatsächliche Kurve kann etwas anders aussehen. Weiterhin kann sich die Form der Kurve bei unterschiedlichen Frequenzen ändern. Es ist ersichtlich, daß die Kapazität bei Anreicherung und Inversion höher und bei Verarmung geringer ist. V<sub>FB</sub> beträgt für stark dotiertes Poly etwa 1,0 Volt. Obwohl im allgemeinen die Grenzen zwischen Anreicherungs-, Verarmungs- und Inversionsmodus nicht exakt sind, tritt der Anreicherungsmodus auf, wenn V<sub>FB</sub> < V<sub>GB</sub> ist, der Verarmungsmodus tritt auf, wenn -V<sub>t</sub> < V<sub>GB</sub> < V<sub>FB</sub> ist und der Inversionsmodus tritt auf, wenn V<sub>GB</sub> < -V<sub>t</sub> ist. Es ist zu beachten, daß die relativen Abstände zwischen -V<sub>t</sub> und 0 und zwischen 0 und V<sub>FB</sub> und zwischen 0 und V<sub>t</sub> nicht als Einschränkung für die tatsächlichen Werte von V<sub>FB</sub> oder V<sub>t</sub> verstanden werden sollen, die von Ausführungsbeispiel zu Ausführungsbeispiel variieren können.

**[0027]** Man betrachte den Fall eines Kondensators **10** nach dem Stand der Technik in [Fig. 1](#). Die Kurve in [Fig. 3](#) würde zutreffen, weil dort ein n-Substrat vorhanden ist und das Poly und das Substrat von unterschiedlicher Art sind, so daß die Austrittsarbeit ungleich Null ist. Die Flachbandspannung (V<sub>FB</sub>) dieser Struktur beträgt etwa 1 Volt. Im Falle von [Fig. 1](#) ist V<sub>GB</sub> = -V<sub>cc</sub>, wobei diese negativer als V<sub>t</sub> sind. Daher befindet sich der Transistorkondensator **10** im Inversionsmodus (genauer gesagt, befindet sich der Kanal in Inversion, weil er Löcher aufweist, die vom entgegengesetzten Typ des Substrates sind). Dementsprechend hat er eine sehr große (vielleicht eine maximale) flächenbezogene Kapazität, sehr gutes Frequenzverhalten und geringen Reihenwiderstand. Jedoch tritt auch Verlust durch das Gate-Oxid auf, insbesondere sind diese bei dünnen Gate-Oxiden auch groß (vielleicht maximal). V<sub>cc</sub> sollte bei dieser Decap-Konfiguration größer als V<sub>t</sub> sein. Es ist zu beachten, daß die Kapazität als Funktion der Frequenz und des Widerstandes in Reihe mit dem Cap (für den Verschiebungssstrom) repräsentativ für den Q-Faktor des Decaps ist. Es ist zu beachten, daß die Flachbandspannung (V<sub>FB</sub>) etwa 1 Volt (nicht 0) für den PMOS-Cap in Inversion beträgt, wegen des p<sup>+</sup>-Poly-Gates und des n-Substrats.

**[0028]** [Fig. 4](#) zeigt einen MOS-C **40**. Es ist zu beachten, daß der Begriff MOS(Metall-Oxid-Halbleiter) weit interpretierbar sein soll, wobei das Metall nicht auf irgendeine besondere Art von Leitung beschränkt ist (z. B. es muß nicht Polysilizium sein), ein Isolator muß nicht unbedingt ein Oxid aufweisen und der Halbleiterteil ist nicht auf eine bestimmte Strukturart beschränkt. Der MOS-C **40** wird als n<sup>+</sup>/n<sup>+</sup> auf n-Substrat gemäß der oben be-

schriebenen Terminologie bezeichnet (d. h. Poly ist  $n^+$ , S/D ist  $n^+$ ).  $V_g$  ist  $V_{cc}$  und S/D/B liegen auf 0 ( $V_{ss}$ ). Die Kurve in [Fig. 2](#) trifft zu, da eine n-Wanne verwendet wird und das Poly und das Substrat von der gleichen Art sind.  $V_{FB}$  des MOS-C **40** liegt auf 0 Volt.  $V_{GB} = V_{cc}$ , so daß sich der MOS-C **40** im Anreicherungsmodus befindet (der Kanal ist mit Elektronen angereichert, was demselben Typ wie das Substrat entspricht).

**[0029]** Mit der Anordnung nach [Fig. 4](#) kann es wünschenswert sein, solch ein Layout (Zeichnen von n-Poly auf n-Wanne) bei Entwurfshilfsmitteln zu erlauben. MOS-C **40** arbeitet mit allen  $V_{cc}$ -Werten. Es weist eine hohe (gute) flächenbezogene Kapazität bei etwas geringeren Verlusten auf. Es weist ein gutes Frequenzverhalten und geringen Reihenwiderstand auf.

**[0030]** [Fig. 5](#) zeigt ein MOS-C **50**. MOS-C **50** wird als  $p^+/n^+$  auf n-Substrat bezeichnet, entsprechend der oben beschriebenen Terminologie.  $V_g$  hat den Wert  $V_{cc}$  und S/D/B liegen auf 0 ( $V_{ss}$ ). Die Kurve in [Fig. 3](#) trifft zu, weil eine n-Wanne verwendet wird und das Poly und das Substrat von unterschiedlicher Art sind.  $V_{FB}$  von MOS-C **50** ist ungefähr 1 Volt.  $V_{GB} = V_{cc}$ . Wenn  $V_{cc} > V_{FB}$  ist, befindet sich MOS-C **50** im Anreicherungsmodus (der Kanal wird angereichert), und wenn  $V_{cc} < V_{FB}$  ist, dann befindet sich MOS-C **40** im Verarmungsmodus (der Kanal verarmt). Wenn  $V_{cc} = V_{FB}$  ist, so befindet sich der Modus zwischen Anreicherungs- und Verarmungsmodus. Erfindungsgemäß ist  $V_{cc} < V_{FB}$ , so daß sich MOS-C **50** in dem Verarmungsmodus befindet und Verluste verringert werden. Diese Anordnung kann ein spezielles Layout erfordern. MOS-C **50** weist eine geringere flächenbezogene Kapazität auf, jedoch mit viel geringeren Verlusten aufgrund des Verarmungsmodus (es sind weniger Ladungsträger vorhanden, die zum Verlust beitragen können). Es weist ein gutes Frequenzverhalten auf, kann jedoch einen hohen Reihenwiderstand haben. Man beachte, daß die Struktur der MOS-Transistorstruktur mit vergrabenem Kanal ähnelt.

**[0031]** [Fig. 6](#) zeigt einen PMOS-Transistorkondensator **60** (MOS-C **60**). Der Transistorkondensator **60** wird als  $p^+/p^+$  auf n-Substrat bezeichnet, gemäß der oben beschriebenen Terminologie.  $V_g$  hat den Wert  $V_{cc}$  und S/D/B liegen auf 0 ( $V_{ss}$ ) (im Gegensatz zu [Fig. 1](#)). Die Kurve aus [Fig. 3](#) trifft zu, weil eine n-Wanne verwendet wird und das Poly und das Substrat von unterschiedlicher Art sind.  $V_{FB}$  des MOS-C **50** hat ungefähr den Wert von 1 Volt.  $V_{GB} = V_{cc}$ . Wenn  $V_{cc} > V_{FB}$  ist, befindet sich MOS-C **60** im Anreicherungsmodus (der Kanal wird angereichert), und wenn  $V_{cc} < V_{FB}$  ist, befindet sich der MOS-C **60** im Verarmungsmodus (der Kanal verarmt). Bei der Erfindung ist  $V_{cc} < V_{FB}$ , so daß sich MOS-C **60** im Verarmungsmodus befindet und die Verluste reduziert werden. MOS-C **60** weist aufgrund des Verarmungsmodus eine geringere flächenbezogene Kapazität auf, jedoch mit viel geringeren Verlusten (es gibt weniger Ladungsträger, die zu den Verlusten beitragen können). Das Frequenzverhalten und der Reihenwiderstand können jedoch ein Problem darstellen.

#### Entstörkondensatoren mit p-Substrat

**[0032]** Im folgenden werden Beispiele von Transistoren und MOS-C-Kondensatorstrukturen mit p-Substraten (p-Wanne oder p-Substrat) beschrieben. Es ist zu beachten, daß das Substrat (body) nur aus dem p-Substrat bestehen kann, obwohl p-Wannen dargestellt sind. Auch kann das Substrat vom n-Typ mit einer p-Wanne sein.

**[0033]** [Fig. 7](#) zeigt die Auftragung einer Kapazität über der Gate-Substrat-Spannung  $V_{GB}$  für kapazitive p-Substrat-Strukturen mit einer verschwindenden Austrittsarbeit, da das Poly und das Substrat von der gleichen Art sind. Die Kurve soll nur allgemeine Zusammenhänge darstellen und nicht präzise Werte oder Formen. Die tatsächliche Kurve kann etwas anders aussehen. Außerdem kann sich die Form der Kurve bei verschiedenen Frequenzen ändern. Es ist zu erkennen, daß die Kapazität bei der Anreicherung und Inversion größer und bei der Verarmung kleiner ist. Auch wenn die Grenzen zwischen Anreicherungs-, Verarmungs- und Inversionsmodus nicht exakt sein mögen, tritt Anreicherung ein, wenn  $V_{GB} < 0$  ist, tritt der Verarmungsmodus ein, wenn  $0 < V_{GB} < V_t$  ist, und tritt der Inversionsmodus ein, wenn  $V_{GB} > V_t$  ist.

**[0034]** [Fig. 8](#) zeigt die Auftragung einer Kapazität über der Gate-Substrat-Spannung  $V_{GB}$  für p-Substrat-Kondensatorstrukturen mit nicht-verschwindender Austrittsarbeit (die Flachbandspannung  $V_{FB}$  hat nicht den Wert 0), weil das Poly und das Substrat von unterschiedlicher Art sind. Die Kurve soll nur allgemeine Zusammenhänge und nicht präzise Werte oder Formen zeigen. Die tatsächliche Kurve kann etwas anders aussehen. Außerdem ändert sich die Form der Kurve bei unterschiedlichen Frequenzen. Es ist zu sehen, daß die Kapazität bei Anreicherung und Inversion höher und bei Verarmung niedriger ist.  $V_{FB}$  ist für stark dotiertes Poly ungefähr 1,0 Volt (allerdings ist es im negativen Bereich der Kurve). Obwohl die Grenzen zwischen Anreicherungs-, Verarmungs- und Inversionsmodus nicht exakt sein mögen, tritt der Anreicherungsmodus ein, wenn  $V_{GB} < -V_{FB}$  (z. B.  $-1 \text{ V}$ ) ist, der Verarmungsmodus ein, wenn  $-V_{FB} < V_{GB} < V_t$  ist, und der Inversionsmodus ein, wenn  $V_t < V_{GB}$  ist. Es ist zu beachten, daß die relativen Abstände zwischen  $-V_{FB}$  und 0 und zwischen 0 und  $V_t$  nicht als einschränkend für die tatsächlichen Werte von  $V_{FB}$  oder  $V_t$  verstanden werden sollen, die von Ausführungsbeispiel

zu Ausführungsbeispiel variieren können.

**[0035]** [Fig. 9](#) zeigt einen NMOS-Transistorkondensator **90** gemäß dem Stand der Technik, der gemäß der oben beschriebenen Terminologie als  $n^+/n^+$  auf p-Substrat bezeichnet wird. In diesem Fall handelt es sich um einen p-Substrat, aber es könnte eine p-Wanne auf einem n-Substrat oder eine p-Wanne in einem p-Substrat sein.  $V_g = V_{cc}$ , und S/D/B haben den Wert 0 ( $V_{ss}$ ). Da das Poly und das Substrat von unterschiedlichem Typ sind, wird die Kurve aus [Fig. 8](#) verwendet.  $V_{GB} = V_{cc}$ . In Kurve **8** ist  $V_{cc} > V_t$ , so daß sich der Transistorkondensator **90** im Inversionsmodus befindet (der Kanal befindet sich in Inversion). Decap **90** erfordert keinen Drei-Wannen-Prozeß und stellt keine besonderen Layout-Anforderungen. Es weist eine sehr hohe (vielleicht maximale) flächenbezogene Kapazität, sehr gute Frequenzeigenschaften und einen geringen Reihenwiderstand auf.

**[0036]** Das wesentliche Problem ist, daß die Verluste durch das Gate-Oxid, insbesondere bei dünnen Gate-Oxiden, ebenfalls groß sind (vielleicht maximal).  $V_{cc}$  sollte bei dieser Decap-Konfiguration größer als  $V_t$  sein.

**[0037]** [Fig. 10](#) zeigt einen MOS-C-Kondensator **100** mit einer  $p^+/p^+$ -auf-p-Substrat-Konfiguration gemäß der obigen Terminologie. Obwohl eine p-Wanne dargestellt ist, ist sie nicht notwendig.  $V_g = 0$  ( $V_{ss}$ ), und S/D/B =  $V_{cc}$ . Weil das Poly und das Substrat vom gleichen Typ sind, trifft die Kurve aus [Fig. 7](#) zu.  $V_{GB} = V_{cc}$ , so daß sich der Kondensator **100** im Anreicherungsmodus befindet (der Kanal würde angereichert werden). Bei einigen Ausführungsbeispielen weist der Kondensator **100** ein n-Substrat oder einen anderen Isolator zwischen der p-Wanne und dem p-Substrat auf. Der Zweck ist es, zu verhindern, daß die  $V_{cc}$ -Spannung die Spannung des Substrates oder anderer Teile beeinflußt. Dieser Dreifach-Wannen-Prozeß kann zusätzliches Layout in den Design-Werkzeugen erforderlich machen (Zeichnen von p-Poly auf p-Wanne). Decap **100** arbeitet mit allen  $V_{cc}$ -Werten. Es weist eine hohe (gute) flächenbezogene Kapazität bei etwas geringeren Verlusten auf. Es hat ein gutes Frequenzverhalten und einen geringen Reihenwiderstand.

**[0038]** [Fig. 11](#) zeigt einen MOS-C-Kondensator **110** mit einer  $n^+/p^+$ -auf-p-Substrat-Konfiguration gemäß der oben beschriebenen Terminologie. Obwohl eine p-Wanne dargestellt ist, ist sie nicht nötig.  $V_g = 0$  ( $V_{ss}$ ), und S/D/B =  $V_{cc}$ . Da das Poly und das Substrat von unterschiedlichem Typ sind, trifft die Kurve aus [Fig. 8](#) zu.  $V_{GB} = -V_{cc}$ . Wenn  $V_{cc} < V_{FB}$  ( $-V_{cc} > -V_{FB}$ ) ist, würde sich der Kondensator **110** im Verarmungsmodus befinden (der Kanal würde verarmen). Zur Verminderung von Verlusten wird bei einigen Ausführungsbeispielen der Verarmungsmodus verwendet. Bei einigen Ausführungsbeispielen weist der Kondensator **110** einen n-Substrat oder einen anderen Isolator zwischen der p-Wanne und dem p-Substrat auf. Der Kondensator **110** hat eine geringere flächenbezogene Kapazität bei wesentlich geringeren Verlusten. Er weist ein gutes Frequenzverhalten auf, jedoch einen großen Reihenwiderstand.

**[0039]** [Fig. 12](#) zeigt einen NMOS-Transistor **120** mit einer  $n^+/n^+$ -auf-p-Substrat-Konfiguration gemäß der oben beschriebenen Terminologie. Obwohl eine p-Wanne dargestellt ist, ist diese nicht nötig.  $V_g = 0$  ( $V_{ss}$ ), und S/D/B =  $V_{cc}$ . Weil das Poly und das Substrat von unterschiedlichem Typ sind, trifft die Kurve aus [Fig. 8](#) zu.  $V_{GB} = -V_{cc}$ . Wenn  $V_{cc} > V_{FB}$  ( $-V_{cc} < -V_{FB}$ ) würde sich der Kondensator **120** im Anreicherungsmodus befinden (der Kanal würde angereichert werden). Wenn  $V_{cc} < V_{FB}$  ( $-V_{cc} > -V_{FB}$ ) würde sich der Kondensator **120** im Verarmungsmodus befinden (der Kanal würde verarmen). Zur Verminderung von Verlusten wird bei einigen Ausführungsbeispielen der Verarmungsmodus genutzt. Bei einigen Ausführungsbeispielen weist der Kondensator **120** ein n-Substrat oder einen anderen Isolator zwischen der p-Wanne und dem p-Substrat auf. Die Verluste sind bei dieser Anordnung gut (geringer). Das Frequenzverhalten und der Reihenwiderstand können jedoch ein Problem sein. Diese Anordnung kann einen Drei-Wannen-Prozeß erfordern.

**[0040]** Ein beigefügter Anhang stellt eine vergleichende, zusammenfassende Tabelle für die oben dargestellten Kondensatoren zur Verfügung.

Weitere Informationen und Ausführungsbeispiele

**[0041]** [Fig. 13](#) zeigt einen Chip **130**, der Kondensatoren (z. B. Kondensator **134**) einer oder mehrerer der hier beschriebenen Anordnungen aufweist. Der Chip **130** kann jede Art von elektrischer Einrichtung sein, einschließlich Mikroprozessoren, DSP (digitaler Signal-Prozessor), integrierte Steuerungseinheiten, ASIC (anwendungs-spezifische integrierte Schaltung) und Kommunikationschips.

**[0042]** Erfindungsgemäß ist es, wie oben beschrieben, wünschenswert, einen Kondensator im Verarmungsmodus zu verwenden. Es wäre möglich, die Kapazität durch die Einstellung der Gate-Spannung, Subst-

rat-Spannung, Source/Drain-Spannung, Schwellspannung und/oder Dotierungsstärke zu optimieren.

**[0043]** Lediglich als Beispiel sei angenommen, daß bei einigen Ausführungsbeispielen die effektive Kapazität um ungefähr 25% verringert werden kann, während die Verluste bei einer Versorgungsspannung von etwa 1 Volt ungefähr um einen Faktor 100 verringert werden. Die Verringerung der Kapazität ist in den C-V-Kurven zu beobachten, wenn der Kondensator in einem Verarmungsmodus vorgespannt wird. Die Verringerung der Verluste ist Folge der Tatsache, daß weniger Ladungsträger in dem verarmten Kanal unter dem Gate-Oxid vorhanden sind, die durch das dünne Gate-Oxid tunneln können. Der Q-Faktor eines solchen Kondensators wird ähnlich dem eines MOS-Transistor-Caps in Inversion sein, insbesondere da man sich nicht auf die Erzeugung von Minoritätsladungsträgern und die Rekombination verläßt, um die Ladungsträger zur Verfügung zu stellen, die benötigt werden, um auf das Wechselspannungssignal zu reagieren, das auf dem Decap überlagert ist. Man kann die verringerte Kapazität durch die Verwendung etwas größerer Kondensatorflächen kompensieren, wenn man die Verluste durch den Decap um mehr als eine Größenordnung verringern soll. Die Erfindung unterstützt entsprechend zusätzliche Versorgungsspannungsskalierung und die Entwicklung von Prozeßtechnologien für niedrige Spannungen, Hochleistungs- und Niederleistungs-CMOS-Schaltungen. Mit dem vorgeschlagenen Aufbau kann man in der Zukunft weiterhin Decaps zur Rausch-Entstörung in unseren IC's verwenden, auch wenn wir die Gate-Oxid-Dicke an die schneller skalierten Transistoren anpassen müssen.

**[0044]** Die Erfindung kann in Verbindung mit SOI(Silizium auf Isolator)-Anordnungen verwendet werden.

**[0045]** Es ist ferner bekannt, daß die Versorgungs- und Massespannung nicht unbedingt konstant sind, sondern aufgrund von Rauschen, Belastung oder anderen Ursachen Schwankungen aufweisen.

E

**[0046]** Anhang: Zusammenfassende Vergleichstabelle, die einige Möglichkeiten auflistet. Diese wird nicht als vollständig angesehen. Weitere Möglichkeiten bestehen. Einige der Informationen sind lediglich Schätzungen.

| Typ                                                               | $V_{cc}$               | Modus | Cap      | Leckstrom      | Hi freq | Rs     |                   |

|-------------------------------------------------------------------|------------------------|-------|----------|----------------|---------|--------|-------------------|

|                                                                   |                        |       |          |                |         |        | Anwendung         |

| DeCap auf n-Wanne                                                 |                        |       |          |                |         |        |                   |

| p <sup>+</sup> /p <sup>+</sup><br>(Stand der Technik)<br>(FIG. 1) | > V <sub>t</sub>       | inv.  | max.     | max.           | gut     | gering |                   |

| n <sup>+</sup> /n <sup>+</sup><br>(FIG. 4)                        | Jede                   | anr.  | ~max.    | etwas geringer | gut     | gering | kein LO           |

| p <sup>+</sup> /p <sup>+</sup><br>(FIG. 6)                        | < 1 V                  | ver.  | geringer | geringer       | OK      | hoch   | Kein LO           |

| p <sup>+</sup> /p <sup>+</sup>                                    | > 1 V                  | anr.  | ~max.    | etwas geringer | OK      | hoch   | Kein LO           |

| p <sup>+</sup> /n <sup>+</sup><br>(FIG. 5)                        | < 1 V                  | ver.  | geringer | geringer       | OK      | hoch   | LO                |

| p <sup>+</sup> /n <sup>+</sup>                                    | > 1 V                  | anr.  | ~max.    | etwas geringer | gut     | gering | LO                |

| n <sup>+</sup> /p <sup>+</sup>                                    | > 1 V + V <sub>t</sub> | inv.  | max.     | max.           | gut     | gering | LO.<br>$V_{cc}$ ? |

| n <sup>+</sup> /p <sup>+</sup>                                    | < 1 V + V <sub>t</sub> | ver.  | geringer | geringer       | OK      | hoch   | LO.<br>$V_{cc}$ ? |

| DeCap auf p-Wanne                                                 |                        |       |          |                |         |        |                   |

| n <sup>+</sup> /n <sup>+</sup><br>Stand der Technik<br>(FIG. 9)   | > V <sub>t</sub>       | inv.  | max.     | max.           | gut     | gering |                   |

| p <sup>+</sup> /p <sup>+</sup><br>(FIG. 10)                       | Jede                   | anr.  | ~max     | etwas geringer | gut     | gering | Kein LO           |

| n <sup>+</sup> /n <sup>+</sup><br>(FIG. 12)                       | < 1 V                  | ver.  | geringer | geringer       | OK      | hoch   | Kein LO,<br>TW    |

| n <sup>+</sup> /n <sup>+</sup>                                    | > 1 V                  | anr.  | ~max     | etwas geringer | OK      | hoch   | Kein LO,<br>TW    |

| n <sup>+</sup> /p <sup>+</sup><br>(FIG. 11)                       | < 1 V                  | ver.  | geringer | geringer       | OK      | hoch   | LO,<br>TW         |

| n <sup>+</sup> /p <sup>+</sup>                                    | > 1 V                  | am.   | ~max     | etwas geringer | gut     | gering | LO,<br>TW         |

| p <sup>+</sup> /n <sup>+</sup>                                    | > 1 V + V <sub>t</sub> | inv.  | max.     | max.           | gut     | gering | LO.<br>$V_{cc}$ ? |

| p <sup>+</sup> /n <sup>++</sup>                                   | < 1 V + V <sub>t</sub> | ver.  | geringer | geringer       | OK      | hoch   | LO.<br>$V_{cc}$ ? |

## Legende:

p<sup>+</sup>/p<sup>+</sup> auf n-Wanne bezeichnet einen Kondensator mit p<sup>+</sup>-Poly- und p<sup>+</sup>-S/D-Gebieten auf n-Wanne

Kein LO = Kein über das herkömmliche Design hinausgehender Layout- oder Hilfsmittelwechsel

LO = Kann über das herkömmliche Design hinausgehende Änderungen am Layout erfordern

$V_{FB}$  = ~1 Volt, wird für die  $V_{cc}$ -Spalte verwendet

TW = Kann zur Isolation des Kondensator-Substrat eine Dreifach-Wanne erfordern

**Patentansprüche**

1. Verfahren zum Verwenden einer MOS-Struktur (**134**) als Entstörkapazität zwischen einem ersten, die Versorgungsspannung ( $V_{cc}$ ) einer auf einem Halbleiterchip integrierten Schaltung (**130**) führenden Leiter und einem zweiten, die Massespannung ( $V_{ss}$ ) führenden Leiter,

wobei die MOS-Struktur (**50, 60, 100, 110**) in einem Substrat oder in einer in dem Substrat eingebrachten Wanne mit einem Source-Gebiet (S), einem Drain-Gebiet (D) und einem zwischen dem Source- und dem Drain-Gebiet angeordneten Gate (G), das aus einem über einer Gate-Isolatorschicht angeordneten Gate-Leiter besteht, angeordnet ist,

wobei der Gate-Leiter mit dem ersten oder zweiten Leiter verbunden ist und das Source-Gebiet (S), das Drain-Gebiet und das Substrat bzw. die Wanne (B-Bulk) mit dem anderen Leiter verbunden sind, so dass die MOS-Struktur eine Kapazität zwischen den beiden Leitern bildet,

wobei die MOS-Struktur so mit den beiden Leitern verbunden wird, dass bei den anliegenden Spannungen ( $V_{cc}, V_{ss}$ ) die MOS-Struktur sich im Verarmungsmodus befindet, so dass nur wenige Ladungsträger unter der Gate-Isolatorschicht vorhanden sind, die durch die Gate-Isolatorschicht tunneln können.

2. Verfahren nach Anspruch 1, wobei die MOS-Struktur ein  $n^+$ -Poly-Gate und  $n^+$ -Source/Drain-Gebiete in einem n-Substrat aufweist.

3. Verfahren nach Anspruch 1, wobei die MOS-Struktur ein  $p^+$ -Poly-Gate und  $n^+$ -Source/Drain-Gebiete in einem n-Substrat aufweist.

4. Verfahren nach Anspruch 1, wobei die MOS-Struktur ein  $p^+$ -Poly-Gate und  $p^+$ -Source/Drain-Gebiete in einem n-Substrat aufweist.

5. Verfahren nach Anspruch 1, wobei die MOS-Struktur ein  $p^+$ -Poly-Gate und  $p^+$ -Source/Drain-Gebiete in einem p-Substrat aufweist.

6. Verfahren nach Anspruch 1, wobei die MOS-Struktur ein  $n^+$ -Poly-Gate und  $p^+$ -Source/Drain-Gebiete in einem p-Substrat aufweist.

7. Verfahren nach Anspruch 1, wobei die MOS-Struktur ein  $n^+$ -Poly-Gate und  $n^+$ -Source/Drain-Gebiete in einem p-Substrat aufweist.

Es folgen 5 Blatt Zeichnungen

**FIG. 1**

**(STAND DER TECHNIK)**

**FIG. 2**

**FIG. 3**

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

(STAND DER TECHNIK)

FIG. 10

FIG. 11

FIG. 12

FIG. 13