(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7360246号**

**(P7360246)**

(45)発行日 令和5年10月12日(2023.10.12)

(24)登録日 令和5年10月3日(2023.10.3)

(51)国際特許分類

|         |                |     |         |      |         |

|---------|----------------|-----|---------|------|---------|

| G 0 9 F | 9/30 (2006.01) | F I | G 0 9 F | 9/30 | 3 4 8 A |

| G 0 9 G | 3/32 (2016.01) |     | G 0 9 G | 3/32 | A       |

| G 0 9 G | 3/20 (2006.01) |     | G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 F | 9/33 (2006.01) |     | G 0 9 F | 9/33 |         |

|         |                |     | G 0 9 F | 9/30 | 3 3 8   |

請求項の数 11 (全24頁) 最終頁に続く

(21)出願番号 特願2019-47597(P2019-47597)

(22)出願日 平成31年3月14日(2019.3.14)

(65)公開番号 特開2020-148964(P2020-148964)

A)

(43)公開日 令和2年9月17日(2020.9.17)

審査請求日 令和4年3月11日(2022.3.11)

(73)特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74)代理人 110002147

弁理士法人酒井国際特許事務所

池田 雅延

東京都港区西新橋三丁目7番1号 株式

会社ジャパンディスプレイ内

青木 義典

東京都港区西新橋三丁目7番1号 株式

会社ジャパンディスプレイ内

小川 耀博

東京都港区西新橋三丁目7番1号 株式

会社ジャパンディスプレイ内

金谷 康弘

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

基板と、

前記基板に設けられた複数の画素と、

複数の前記画素の各々に設けられる発光素子と、

前記基板に設けられ、前記発光素子と電気的に接続される第1電極と、

前記第1電極と電気的に接続されるトランジスタと、

前記基板に設けられ、前記発光素子に駆動信号を供給する画素回路と、

前記画素回路に設けられた発熱抵抗体と、を有し、

前記発熱抵抗体は、前記第1電極よりも高いシート抵抗値を有し、

前記基板に垂直な方向からの平面視で、前記発熱抵抗体はミアンダ状の配線パターンを有し、

前記複数の画素の一は、赤色の赤色を表示する第1副画素と、緑色を表示する第2副画素と、青色を表示する第3副画素とを含み、

前記第1副画素は、前記発熱抵抗体として第1発熱抵抗体を有し、

前記第2副画素は、前記発熱抵抗体として第2発熱抵抗体を有し、

前記第3副画素は、前記発熱抵抗体として第3発熱抵抗体を有し、

前記第1副画素が有する前記第1発熱抵抗体の抵抗値は、前記第2発熱抵抗体の抵抗値及び前記第3発熱抵抗体の抵抗値よりも小さい

表示装置。

**【請求項 2】**

前記発熱抵抗体の一端側は前記第1電極に電気的に接続される

請求項1に記載の表示装置。

**【請求項 3】**

前記基板に設けられ、前記発光素子と電気的に接続される第2電極と、

前記第2電極を介して、第2電位を前記発光素子に供給する第2電源線と、を有し、

前記発熱抵抗体の一端側は前記第2電極に電気的に接続される

請求項1に記載の表示装置。

**【請求項 4】**

前記画素回路は、前記第1電極を介して、前記発光素子に第1電位を供給する第1電源

線を有し、

前記発熱抵抗体の他端側は前記第1電源線に電気的に接続される

請求項2又は請求項3に記載の表示装置。

**【請求項 5】**

前記画素回路は、前記発熱抵抗体に抗体駆動信号を供給する抗体信号線を有し、

前記発熱抵抗体の他端側は前記抗体信号線に電気的に接続される

請求項2又は請求項3に記載の表示装置。

**【請求項 6】**

前記第1電極の少なくとも一部は、前記基板に垂直な方向からの平面視で、前記発熱抵抗体と重なって設けられる

請求項1から請求項5のいずれか1項に記載の表示装置。

**【請求項 7】**

複数の前記発光素子の間に設けられ、複数の前記発光素子の少なくとも側面の一部を覆う素子絶縁膜を有し、

前記第2電極は、複数の前記発光素子及び前記素子絶縁膜を覆って、複数の前記発光素子に電気的に接続される

請求項3に記載の表示装置。

**【請求項 8】**

前記発熱抵抗体は、絶縁膜を介して前記第1電極と異なる層に設けられ、前記絶縁膜に設けられたコンタクトホールを介して前記第1電極と接続される

請求項1から請求項7のいずれか1項に記載の表示装置。

**【請求項 9】**

前記トランジスタに映像信号を供給する信号線をさらに有し、

前記基板に垂直な方向において、前記信号線、前記発熱抵抗体、前記第1電極の順に積層される

請求項1から請求項8のいずれか1項に記載の表示装置。

**【請求項 10】**

前記画素に設けられた温度センサと、

前記温度センサからの出力信号を受け取って、前記出力信号の温度依存性に基づいて温度を検出する検出回路と、を有する

請求項1から請求項9のいずれか1項に記載の表示装置。

**【請求項 11】**

前記発熱抵抗体は、前記トランジスタよりも上層であって、前記第1電極よりも下層に設けられる

請求項1から請求項10のいずれか1項に記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置に関する。

**【背景技術】**

10

20

30

40

50

**【0002】**

近年、表示素子として微小サイズの発光ダイオード（マイクロLED（micro LED））を用いたディスプレイが注目されている（例えば、特許文献1参照）。複数の発光ダイオードは、アレイ基板（特許文献1ではドライババックプレーン）に接続され、アレイ基板は、発光ダイオードを駆動するための画素回路（特許文献1では電子制御回路）を備える。

**【先行技術文献】****【特許文献】****【0003】**

**【文献】**特表2017-529557号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

発光ダイオードは、温度上昇に伴い発光効率が低下する。このため、発光ダイオードを利用した表示装置では、温度上昇に伴い輝度が低下し、表示特性が低下する可能性がある。

**【0005】**

本発明は、表示特性の低下を抑制することができる表示装置を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

本発明の一態様の表示装置は、基板と、前記基板に設けられた複数の画素と、複数の前記画素の各々に設けられる発光素子と、前記基板に設けられ、前記発光素子に駆動信号を供給する画素回路と、前記画素回路に設けられた発熱抵抗体と、を有する。

20

**【図面の簡単な説明】****【0007】**

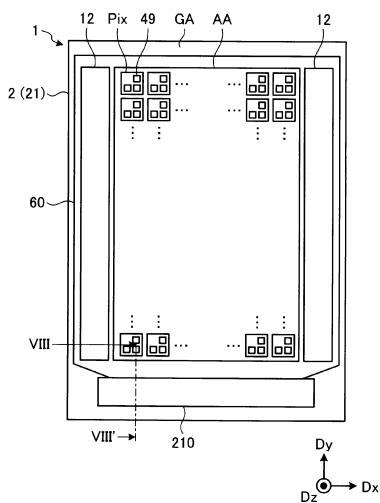

**【図1】**図1は、第1実施形態に係る表示装置を模式的に示す平面図である。

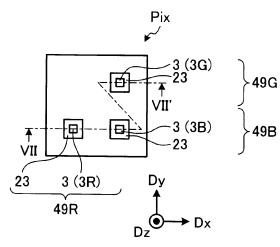

**【図2】**図2は、複数の副画素を示す平面図である。

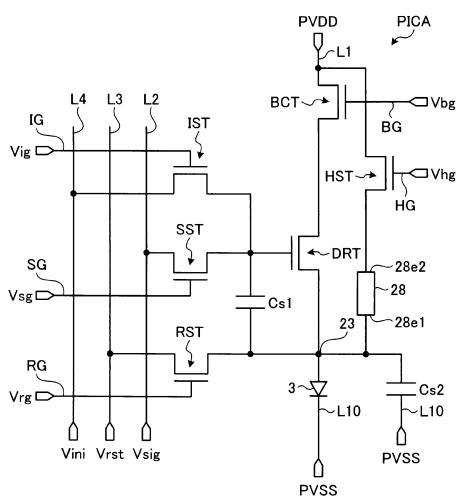

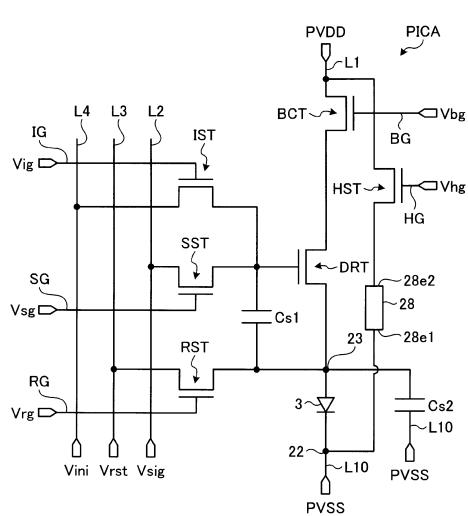

**【図3】**図3は、画素回路を示す回路図である。

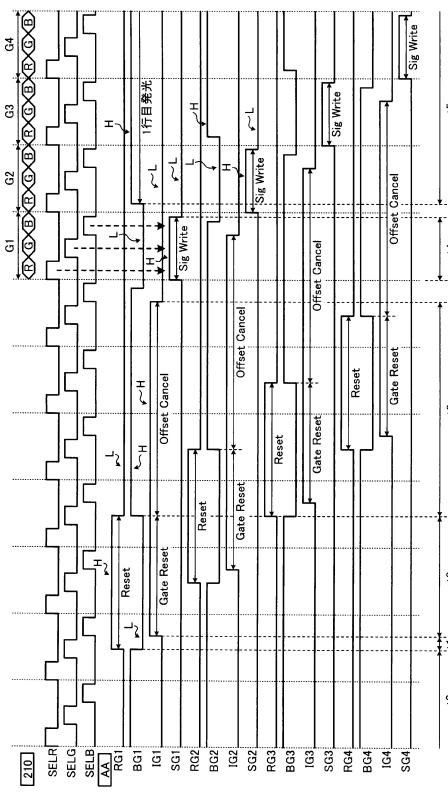

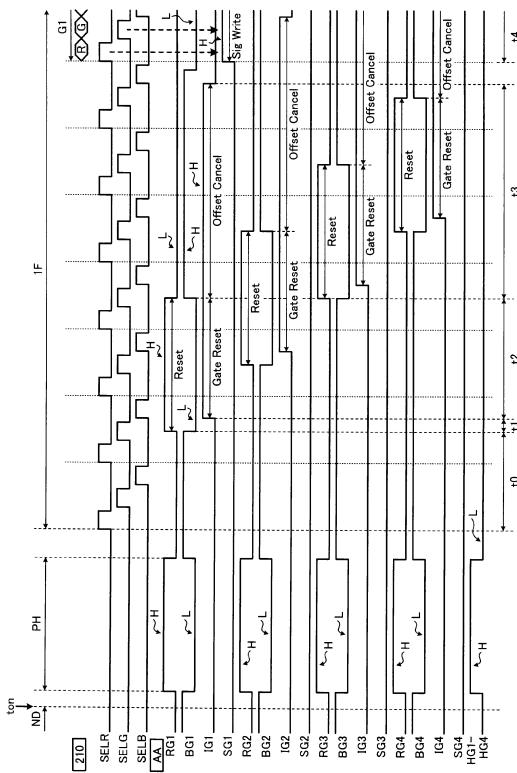

**【図4】**図4は、表示装置の動作例を示すタイミングチャートである。

**【図5】**図5は、表示装置の起動時の動作例を示すタイミングチャートである。

30

**【図6】**図6は、比較例における発光素子の輝度及び温度と、時間との関係を模式的に示すグラフである。

**【図7】**図7は、図2のVII-VII'断面図である。

**【図8】**図8は、図1のVIII-VIII'断面図である。

**【図9】**図9は、第1実施形態に係る表示装置の、1つの副画素を拡大して示す平面図である。

**【図10】**図10は、図9のX-X'断面図である。

**【図11】**図11は、第1副画素が有する第1発熱抵抗体、第2副画素が有する第2発熱抵抗体及び第3副画素が有する第3発熱抵抗体を比較して説明するための説明図である。

40

**【図12】**図12は、第2実施形態に係る画素回路を示す回路図である。

**【図13】**図13は、第3実施形態に係る画素回路を示す回路図である。

**【図14】**図14は、第4実施形態に係る、温度センサを有する画素を示す平面図である。

**【図15】**図15は、温度センサの一例を説明するための説明図である。

**【発明を実施するための形態】****【0008】**

本発明を実施するための形態（実施形態）につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成要素には、当業者が容易に想定できるもの、実質的に同一のものが含まれる。さらに、以下に記載した構成要素は適宜組み合わせることが可能である。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想

50

到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

#### 【 0 0 0 9 】

本明細書及び特許請求の範囲において、ある構造体の上に他の構造体を配置する態様を表現するにあたり、単に「上に」と表記する場合、特に断りの無い限りは、ある構造体に接するように、直上に他の構造体を配置する場合と、ある構造体の上方に、さらに別の構造体を介して他の構造体を配置する場合との両方を含むものとする。

10

#### 【 0 0 1 0 】

##### ( 第 1 実施形態 )

図 1 は、第 1 実施形態に係る表示装置を模式的に示す平面図である。図 1 に示すように、表示装置 1 は、アレイ基板 2 と、画素 P i x と、駆動回路 1 2 と、駆動 I C ( Integrated Circuit ) 2 1 0 と、カソード配線 6 0 と、を含む。アレイ基板 2 は、各画素 P i x を駆動するための駆動回路基板であり、バックプレーン又はアクティブマトリックス基板とも呼ばれる。アレイ基板 2 は、基板 2 1 、複数のトランジスタ、複数の容量及び各種配線等を有する。

#### 【 0 0 1 1 】

図 1 に示すように、表示装置 1 は、表示領域 A A と、周辺領域 G A とを有する。表示領域 A A は、複数の画素 P i x と重なって配置され、画像を表示する領域である。周辺領域 G A は、複数の画素 P i x と重ならない領域であり、表示領域 A A の外側に配置される。

20

#### 【 0 0 1 2 】

複数の画素 P i x は、基板 2 1 の表示領域 A A において、第 1 方向 D x 及び第 2 方向 D y に配列される。なお、第 1 方向 D x 及び第 2 方向 D y は、基板 2 1 の表面に対して平行な方向である。第 1 方向 D x は、第 2 方向 D y と直交する。ただし、第 1 方向 D x は、第 2 方向 D y と直交しないで交差してもよい。第 3 方向 D z は、第 1 方向 D x 及び第 2 方向 D y と直交する方向である。第 3 方向 D z は、例えば、基板 2 1 の法線方向に対応する。なお、以下、平面視とは、第 3 方向 D z から見た場合の位置関係を示す。

#### 【 0 0 1 3 】

30

駆動回路 1 2 は、駆動 I C 2 1 0 からの各種制御信号に基づいて複数のゲート線（例えば、発光制御走査線 B G 、リセット制御走査線 R G 、初期化制御走査線 I G 、書き制御走査線 S G 及び発熱制御走査線 H G （図 3 参照））を駆動する回路である。駆動回路 1 2 は、複数のゲート線を順次又は同時に選択し、選択されたゲート線にゲート駆動信号を供給する。これにより、駆動回路 1 2 は、ゲート線に接続された複数の画素 P i x を選択する。

#### 【 0 0 1 4 】

駆動 I C 2 1 0 は、表示装置 1 の表示を制御する回路である。駆動 I C 2 1 0 は、基板 2 1 の周辺領域 G A に C O G ( Chip On Glass ) として実装される。これに限定されず、駆動 I C 2 1 0 は、基板 2 1 の周辺領域 G A に接続されたフレキシブルプリント基板やリジット基板の上に C O F ( Chip On Film ) として実装されてもよい。

40

#### 【 0 0 1 5 】

カソード配線 6 0 は、基板 2 1 の周辺領域 G A に設けられる。カソード配線 6 0 は、表示領域 A A の複数の画素 P i x 及び周辺領域 G A の駆動回路 1 2 を囲んで設けられる。複数の発光素子 3 のカソードは、共通のカソード配線 6 0 に電気的に接続され、固定電位（例えば、グランド電位）が供給される。より具体的には、発光素子 3 のカソード端子 3 2 （図 7 参照）は、カソード電極 2 2 （第 2 電極）を介して、カソード配線 6 0 に接続される。

#### 【 0 0 1 6 】

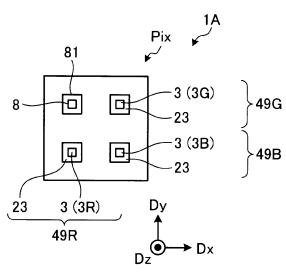

図 2 は、複数の副画素を示す平面図である。図 2 に示すように、1 つの画素 P i x は、複数の副画素 4 9 を含む。例えば、画素 P i x は、第 1 副画素 4 9 R と、第 2 副画素 4 9

50

Gと、第3副画素49Bとを有する。第1副画素49Rは、第1色としての原色の赤色を表示する。第2副画素49Gは、第2色としての原色の緑色を表示する。第3副画素49Bは、第3色としての原色の青色を表示する。図2に示すように、1つの画素P<sub>i</sub>xにおいて、第1副画素49Rと第3副画素49Bは第1方向D<sub>x</sub>で並ぶ。また、第2副画素49Gと第3副画素49Bは第2方向D<sub>y</sub>で並ぶ。なお、第1色、第2色、第3色は、それぞれ赤色、緑色、青色に限られず、補色などの任意の色を選択することができる。以下において、第1副画素49Rと、第2副画素49Gと、第3副画素49Bとをそれぞれ区別する必要がない場合、副画素49という。

#### 【0017】

副画素49は、それぞれ発光素子3と、アノード電極23（第1電極）と、を有する。表示装置1は、第1副画素49R、第2副画素49G及び第3副画素49Bにおいて、発光素子3R、3G、3Bごとに異なる光（例えば、赤色、緑色、青色の光）を射出することで画像を表示する。発光素子3は、複数の副画素49の各々に設けられる。発光素子3は、平面視で、3μm以上、300μm以下程度の大きさを有する発光ダイオード（LED：Light Emitting Diode）チップであり、マイクロLED（micro LED）と呼ばれる。各画素にマイクロLEDを備える表示装置1は、マイクロLED表示装置とも呼ばれる。なお、マイクロLEDのマイクロは、発光素子3の大きさを限定するものではない。

#### 【0018】

なお、複数の発光素子3は、4色以上の異なる光を射出してもよい。また、複数の副画素49の配置は、図2に示す構成に限定されない。例えば、第1副画素49Rは第2副画素49Gと第1方向D<sub>x</sub>に隣り合っていてもよい。また、第1副画素49R、第2副画素49G及び第3副画素49Bが、この順で第1方向D<sub>x</sub>に繰り返し配列されてもよい。

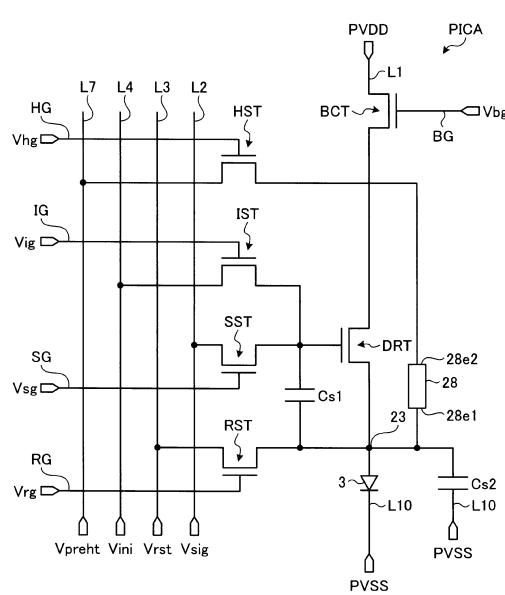

#### 【0019】

図3は、画素回路を示す回路図である。図3に示す画素回路PICAは、第1副画素49R、第2副画素49G及び第3副画素49Bのそれぞれに設けられる。画素回路PICAは、基板21に設けられ、駆動信号（電流）を発光素子3に供給する回路である。なお、図3において、画素回路PICAについての説明は、第1副画素49R、第2副画素49G及び第3副画素49Bのそれぞれが有する画素回路PICAに適用できる。

#### 【0020】

図3に示すように、画素回路PICAは、発光素子3と、6つのトランジスタと、2つの容量と、発熱抵抗体28と、を含む。具体的には、画素回路PICAは、発光制御トランジスタBCT、初期化トランジスタIST、書きトランジスタSST、リセットトランジスタRST、駆動トランジスタDRT及び発熱制御トランジスタHSTを含む。一部のトランジスタは、隣接する複数の副画素49で共有されていてもよい。例えば、発光制御トランジスタBCTは、共通配線を介して、3つの副画素49で共有されていてもよい。また、リセットトランジスタRSTは、周辺領域GAに設けられ、例えば副画素49の各行に1つ設けられていてもよい。この場合、リセットトランジスタRSTは、共通配線を介して複数の駆動トランジスタDRTのソースに接続される。

#### 【0021】

画素回路PICAが有する複数のトランジスタは、それぞれn型TFT（Thin Film Transistor）で構成される。ただし、これに限定されず、各トランジスタは、それぞれp型TFTで構成されてもよい。p型TFTを用いる場合は、適宜電源電位や保持容量Cs1及び容量Cs2の接続を適合させてよい。

#### 【0022】

発光制御走査線BGは、発光制御トランジスタBCTのゲートに接続される。初期化制御走査線IGは、初期化トランジスタISTのゲートに接続される。書き制御走査線SGは、書きトランジスタSSTのゲートに接続される。リセット制御走査線RGは、リセットトランジスタRSTのゲートに接続される。発熱制御走査線HGは、発熱制御トランジスタHSTのゲートに接続される。

10

20

30

40

50

## 【0023】

発光制御走査線 B G、初期化制御走査線 I G、書込制御走査線 S G、リセット制御走査線 R G 及び発熱制御走査線 H G は、それぞれ、周辺領域 G A に設けられた駆動回路 1 2 ( 図 1 参照 ) に接続される。駆動回路 1 2 は、発光制御走査線 B G、初期化制御走査線 I G、書込制御走査線 S G、リセット制御走査線 R G 及び発熱制御走査線 H G に、それぞれ、発光制御信号 V b g、初期化制御信号 V i g、書込制御信号 V s g、リセット制御信号 V r g 及び発熱制御信号 V h g を供給する。

## 【0024】

駆動 I C 2 1 0 ( 図 1 参照 ) は、第 1 副画素 4 9 R、第 2 副画素 4 9 G 及び第 3 副画素 4 9 B のそれぞれの画素回路 P I C A に、時分割で映像信号 V s i g を供給する。第 1 副画素 4 9 R、第 2 副画素 4 9 G 及び第 3 副画素 4 9 B の各列と、駆動 I C 2 1 0 との間には、マルチプレクサ等のスイッチ回路が設けられる。映像信号 V s i g は、映像信号線 L 2 を介して書込トランジスタ S S T に供給される。また、駆動 I C 2 1 0 は、リセット信号線 L 3 を介して、リセット電源電位 V r s t をリセットトランジスタ R S T に供給する。駆動 I C 2 1 0 は、初期化信号線 L 4 を介して、初期化電位 V i n i を初期化トランジスタ I S T に供給する。

10

## 【0025】

発光制御トランジスタ B C T、初期化トランジスタ I S T、書込トランジスタ S S T、リセットトランジスタ R S T 及び発熱制御トランジスタ H S T は、2 ノード間の導通と非導通とを選択するスイッチング素子として機能する。駆動トランジスタ D R T は、ゲートとドレインとの間の電圧に応じて、発光素子 3 に流れる電流を制御する電流制御素子として機能する。

20

## 【0026】

発光素子 3 のカソード ( カソード端子 3 2 ) は、カソード電源線 L 1 0 ( 第 2 電源線 ) に接続される。また、発光素子 3 のアノード ( アノード端子 3 3 ) は、駆動トランジスタ D R T 及び発光制御トランジスタ B C T を介してアノード電源線 L 1 ( 第 1 電源線 ) に接続される。アノード電源線 L 1 には、アノード電源電位 P V D D ( 第 1 電位 ) が供給される。カソード電源線 L 1 0 には、カソード電源電位 P V S S ( 第 2 電位 ) が供給される。アノード電源電位 P V D D は、カソード電源電位 P V S S よりも高い電位である。カソード電源線 L 1 0 は、カソード配線 6 0 を含む。なお、発光素子 3 の発光動作については後述する。

30

## 【0027】

発熱抵抗体 2 8 の一端側 2 8 e 1 は、アノード電極 2 3 に接続される。発熱抵抗体 2 8 の他端側 2 8 e 2 は、発熱制御トランジスタ H S T を介してアノード電源線 L 1 に電気的に接続される。

## 【0028】

また、画素回路 P I C A は、保持容量 C s 1 及び容量 C s 2 を含む。保持容量 C s 1 は、駆動トランジスタ D R T のゲートとソースとの間に形成される容量である。容量 C s 2 は、駆動トランジスタ D R T のソース及び発光素子 3 のアノードと、カソード電源線 L 1 0 との間に形成される付加容量である。

40

## 【0029】

図 4 は、表示装置の動作例を示すタイミングチャートである。図 4 に示す期間 G 1 から期間 G 4 のそれぞれが 1 水平期間である。なお、図 4 では、1 行目の副画素 4 9 から 4 行目の副画素 4 9 を駆動する動作を示しているが、5 行目以降、最終行の副画素 4 9 まで継続して駆動される。また、以下の説明では、1 行目の副画素 4 9 から最終行の副画素 4 9 までの駆動を行う期間をフレーム期間 1 F と表す。

## 【0030】

図 4 に示す期間 t 0 から期間 t 5 までの動作例について、以下詳細に説明する。期間 t 0 は、前フレーム発光期間である。つまり、あるフレーム期間 1 F での処理が開始されるまでの期間 t 0 では、副画素 4 9 は、前フレームの発光状態を継続している。

50

**【 0 0 3 1 】**

次に、期間  $t_1$  は、駆動トランジスタ D R T のソース初期化期間である。具体的には、期間  $t_1$  では、駆動回路 1 2 から供給される各制御信号により、発光制御走査線 B G 1 の電位が L (ロウ) レベルとなり、リセット制御走査線 R G 1 の電位が H レベルとなる。これにより、発光制御トランジスタ B C T がオフ（非導通状態）となり、リセットトランジスタ R S T がオン（導通状態）となる。

**【 0 0 3 2 】**

なお、発光制御走査線 B G 1 は、1 行目の副画素 4 9 に接続された発光制御走査線 B G を示し、発光制御走査線 B G 2 は、2 行目の副画素 4 9 に接続された発光制御走査線 B G を示す。発光制御走査線 B G 3 は、3 行目の副画素 4 9 に接続された発光制御走査線 B G を示し、発光制御走査線 B G 4 は、4 行目の副画素 4 9 に接続された発光制御走査線 B G を示す。リセット制御走査線 R G 1、R G 2、R G 3、R G 4 等の各走査線も同様である。

10

**【 0 0 3 3 】**

期間  $t_1$  では、1 行目に属する副画素 4 9 において、アノード電源線 L 1 からの電流が発光制御トランジスタ B C T により遮断される。発光素子 3 の発光が停止するとともに、副画素 4 9 内に残留していた電荷が、リセットトランジスタ R S T を通じて外部に流れ。これにより、駆動トランジスタ D R T のソースがリセット電源電位 V r s t に固定される。リセット電源電位 V r s t は、カソード電源電位 P V S S に対して所定の電位差を有して設定される。この場合、リセット電源電位 V r s t とカソード電源電位 P V S S との電位差は、発光素子 3 が発光を開始する電位差よりも小さい。

20

**【 0 0 3 4 】**

次に、期間  $t_2$  は、駆動トランジスタ D R T のゲート初期化期間である。具体的には、期間  $t_2$  では、駆動回路 1 2 から供給される各制御信号により、初期化制御走査線 I G 1 の電位が H レベルとなる。初期化トランジスタ I S T は、オンとなる。1 行目に属する副画素 4 9 において、初期化トランジスタ I S T を介して駆動トランジスタ D R T のゲートが初期化電位 V i n i に固定される。初期化電位 V i n i は、リセット電源電位 V r s t に対して、駆動トランジスタ D R T のしきい値よりも大きい電位を有している。このため、駆動トランジスタ D R T はオンとなる。ただし、期間  $t_2$  では、発光制御トランジスタ B C T がオフの状態を維持しているので、駆動トランジスタ D R T には電流が流れない。

30

**【 0 0 3 5 】**

次に、期間  $t_3$  は、オフセットキャンセル動作期間である。具体的には、期間  $t_3$  では、駆動回路 1 2 から供給される各制御信号により、発光制御走査線 B G 1 の電位が H レベルとなり、リセット制御走査線 R G 1 の電位が L レベルとなる。これにより、発光制御トランジスタ B C T がオンとなり、リセットトランジスタ R S T がオフとなる。

**【 0 0 3 6 】**

駆動トランジスタ D R T は、期間  $t_2$  の動作によりオン状態となっている。このため、アノード電源線 L 1 (アノード電源電位 P V D D ) から、発光制御トランジスタ B C T を介して駆動トランジスタ D R T に電流が供給される。

**【 0 0 3 7 】**

この段階では、発光素子 3 のアノードとカソードとの間の電圧は、発光開始電圧よりも小さいので、電流が流れない。したがって、アノード電源電位 P V D D によって駆動トランジスタ D R T のソースが充電され、ソースの電位が上昇する。駆動トランジスタ D R T のゲート電位は、初期化電位 V i n i となっている。このため、駆動トランジスタ D R T のソース電位が (V i n i - V t h) となった段階で駆動トランジスタ D R T がオフになり、電位の上昇が停止する。ここで、V t h は、駆動トランジスタ D R T のしきい値電圧 V t h である。

40

**【 0 0 3 8 】**

しきい値電圧 V t h は、副画素 4 9 ごとにばらつきがある。このため、電位の上昇が停止したときの駆動トランジスタ D R T のソースの電位は、副画素 4 9 ごとに異なる。つまり、期間  $t_3$  の動作によって、各副画素 4 9 で、駆動トランジスタ D R T のしきい値電圧

50

$V_{th}$ に相当する電圧が取得される。このとき、発光素子3には、 $((V_{ini} - V_{th}) - PVSS)$ の電圧が印加される。この電圧は、発光素子3の発光開始電圧よりも小さいので、発光素子3には電流が流れない。

#### 【0039】

次に、期間 $t_4$ は、映像信号書き動作期間である。具体的には、期間 $t_4$ では、駆動回路12から供給される各制御信号により、発光制御走査線BG1の電位がLレベルとなり、初期化制御走査線IG1の電位がLレベルとなり、書き制御走査線SG1がHレベルとなる。

#### 【0040】

これにより、発光制御トランジスタBCTがオフになり、初期化トランジスタISTがオフになり、書きトランジスタSSTがオンになる。期間 $t_4$ では、1行目に属する副画素49において、映像信号Vsigが駆動トランジスタDRTのゲートに入力される。駆動トランジスタDRTのゲート電位は、初期化電位 $V_{ini}$ から映像信号Vsigの電位に変化する。一方、駆動トランジスタDRTのソースの電位は、 $(V_{ini} - V_{th})$ を維持している。この結果、駆動トランジスタDRTのゲートとソースとの間の電圧は、 $(V_{sig} - (V_{ini} - V_{th}))$ となり、副画素49間のしきい値電圧 $V_{th}$ のばらつきが反映されたものとなる。

10

#### 【0041】

映像信号線L2は、第2方向Dy(図1参照)に延在し、同列に属する複数行の副画素49に接続される。このため、映像書き動作を行う期間 $t_4$ は、1行ごとに実施される。

20

#### 【0042】

次に、期間 $t_5$ は、発光動作期間である。具体的には、期間 $t_5$ では、駆動回路12から供給される各制御信号により、発光制御走査線BG1の電位がHレベルとなり、書き制御走査線SG1がLレベルとなる。これにより、発光制御トランジスタBCTがオンになり、書きトランジスタSSTがオフになる。アノード電源線L1(アノード電源電位PVDD)から、発光制御トランジスタBCTを介して駆動トランジスタDRTに電流が供給される。

#### 【0043】

駆動トランジスタDRTは、期間 $t_4$ までに設定されたゲートソース間の電圧に応じた電流を、発光素子3に供給する。発光素子3は、この電流に応じた輝度で発光する。このとき、発光素子3のアノードとカソードとの間の電圧は、駆動トランジスタDRTを通して供給された電流値に応じた電圧となる。これにより、発光素子3のアノードの電位が上昇する。ここで、駆動トランジスタDRTのゲートとソースとの間の電圧は、保持容量Cs1によって保持される。このため、保持容量Cs1のカップリングにより、発光素子3のアノードの電位上昇に伴って、駆動トランジスタDRTのゲート電位も上昇する。

30

#### 【0044】

実際には、駆動トランジスタDRTのゲートには、保持容量Cs1に加えて容量Cs2等の付加容量が存在するので、アノードの電位上昇よりも、駆動トランジスタDRTのゲート電位の上昇はわずかに小さくなる。ただし、この値は既知であるため、最終的な駆動トランジスタDRTのゲートとソースとの間の電圧において、所望の電流値となるように、映像信号Vsigの電位を決定すればよい。

40

#### 【0045】

以上の動作を1行目から最終行まで完了すると、1フレーム分の画像の表示が行われる。例えば、2行目に属する副画素49のリセット動作は、期間 $t_2$ 及び期間 $t_3$ と重なる期間に実行される。2行目に属する副画素49のオフセットキャンセル動作は、期間 $t_3$ 及び期間 $t_4$ と重なる期間に実行される。2行目に属する副画素49の映像信号書き動作は、期間 $t_5$ と重なる期間に行われる。以後、このような動作を繰り返して映像の表示が行われる。

#### 【0046】

なお、図4に示す動作例では、期間 $t_1$ から期間 $t_5$ において、1行分の副画素49の

50

駆動が実施されているが、これに限定されない。駆動回路 12 は、2 行の副画素 49 を同時に駆動してもよいし、3 行分以上の副画素 49 を同時に駆動してもよい。

#### 【0047】

なお、上述した図 3 に示す画素回路 PICA の構成及び図 4 に示す動作例はあくまで一例であり、適宜変更することができる。例えば 1 つの副画素 49 での配線の数及びトランジスタの数は異なっていてもよい。また、画素回路 PICA はカレントミラー回路等の構成を採用することもできる。

#### 【0048】

図 5 は、表示装置の起動時の動作例を示すタイミングチャートである。図 5 に示すように、表示装置 1 は、非表示期間 NDP とフレーム期間 1F との間にプレヒート期間 PH を有する。非表示期間 NDP は、表示装置 1 が画像の表示を停止した状態の期間である。非表示期間 NDP は、例えば、表示装置 1 の電源が停止している期間や、所定の期間入力操作がない場合に、表示を停止するスリープモードの期間を含む。

10

#### 【0049】

時刻  $t_{on}$ において、表示装置 1 の電源が投入され又はスリープモードからの復帰の操作が行われた場合に、駆動 ICI 210 は、プレヒート期間 PH を実行する。具体的には、駆動回路 12 から供給される各制御信号により、各行に属するリセット制御走査線 RG の電位が H レベルとなり、発熱制御走査線 HG の電位が H レベルとなり、発光制御走査線 BG、初期化制御走査線 IG 及び書き制御走査線 SG の電位が L レベルとなる。

20

#### 【0050】

これにより、発熱制御トランジスタ HST 及びリセットトランジスタ RST がオンになり、他のトランジスタがオフになる。これにより、アノード電源線 L1、発熱制御トランジスタ HST、発熱抵抗体 28、リセットトランジスタ RST 及びリセット信号線 L3 が導通して電流経路が形成される。このため、アノード電源線 L1（アノード電源電位 PVD）から、発熱制御トランジスタ HST を介して発熱抵抗体 28 に電流が供給される。

20

#### 【0051】

これにより、発熱抵抗体 28 の温度が上昇する。発熱抵抗体 28 は、画素回路 PICA に設けられているので、発熱抵抗体 28 で発生する熱が発光素子 3 に伝えられ、発光素子 3 の温度が上昇する。なお、プレヒート期間 PH において、アノード電源線 L1 から供給される電位は、フレーム期間 1F に供給されるアノード電源電位 PVD と異なる電位であってもよい。これにより、表示装置 1 は、発熱抵抗体 28 に流れる電流を適切に調整して、発熱抵抗体 28 の発熱を制御することができる。

30

#### 【0052】

所定の期間、発熱抵抗体 28 に電流を供給した後、各行に属するリセット制御走査線 RG 及び発熱制御走査線 HG の電位が L レベルとなり、発光制御走査線 BG の電位が H レベルとなる。これにより、発熱抵抗体 28 への電流の供給が停止する。その後、表示装置 1 は、上述したフレーム期間 1F の表示を実行する。

#### 【0053】

図 5 に示す動作例では、プレヒート期間 PH において、4 行分の副画素 49 に属する発熱抵抗体 28 が同時に駆動されているが、これに限定されない。駆動回路 12 は、3 行以下、又は 5 行以上の副画素 49 に属する発熱抵抗体 28 を同時に駆動してもよいし、1 行目から最終行の副画素 49 に属する全ての発熱抵抗体 28 を同時に駆動してもよい。

40

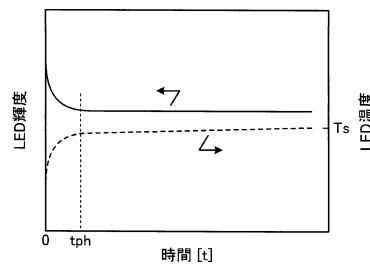

#### 【0054】

図 6 は、比較例における発光素子の輝度及び温度と、時間との関係を模式的に示すグラフである。図 6 に示すグラフの横軸は、発光素子 3 へ電流が供給された時間であり、時間  $t = 0$  は、発光素子 3 への電流の供給が開始された時間を示す。図 6 に示すグラフの縦軸は、発光素子 3 の輝度及び温度を示す。

#### 【0055】

図 6 に示すように、比較例に係る発光素子 3 は、温度の上昇に伴って発光効率が低下す

50

る温度特性を有する。具体的には、比較例に係る発光素子 3 に電流が流れ始める時間  $t = 0$  から時間  $t \sim h$  までの期間において、発光素子 3 の温度が上昇すると、輝度（発光効率）が低下し、発光動作が不安定になる傾向を有する。時間  $t \sim h$  以降では、発光素子 3 は一定の温度  $T_s$  となり、輝度も安定する。

#### 【0056】

本実施形態では、プレヒート期間 PHにおいて、発熱抵抗体 28によりあらかじめ発光素子 3 が加熱され、この期間には発光素子 3 には電流が流れない。例えば、図 6 に示す温度  $T_s$  まで発光素子 3 の温度が上昇した後に、フレーム期間 1F が開始される。これにより、表示装置 1 は、期間  $t_5$ （発光動作期間）において発光素子 3 に電流が流れた場合の、発光素子 3 の温度上昇を抑制することができる。つまり、発光素子 3 は、図 6 に示す時間  $t \sim h$  以降の発光動作が安定になった領域で電流の供給が開始され駆動される。これにより、表示装置 1 は、発光素子 3 の温度上昇に伴う輝度（発光効率）の低下を抑制することができる。この結果、表示装置 1 は、表示特性の低下を抑制することができる。

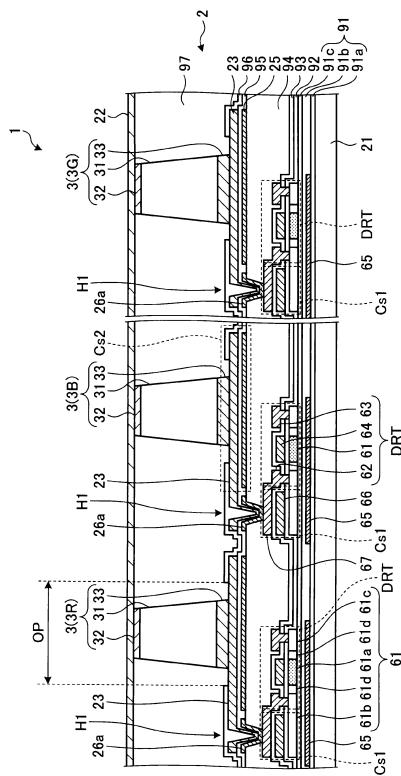

#### 【0057】

次に、表示装置 1 の断面構成について説明する。図 7 は、図 2 の V I I - V I I ' 断面図である。図 8 は、図 1 の V I I I - V I I I ' 断面図である。図 7 に示すように、発光素子 3 は、アレイ基板 2 の上に設けられる。アレイ基板 2 は、基板 21、アノード電極 23、対向電極 25、接続電極 26a、発熱抵抗体 28（図 10 参照）、各種トランジスタ、各種配線及び各種絶縁膜を有する。

#### 【0058】

基板 21 は絶縁基板であり、例えば、石英、無アルカリガラス等のガラス基板、又はポリイミド等の樹脂基板が用いられる。基板 21 として、可撓性を有する樹脂基板を用いた場合には、シートディスプレイとして表示装置 1 を構成することができる。また、基板 21 は、ポリイミドに限らず、他の樹脂材料を用いても良い。

#### 【0059】

なお、本明細書において、基板 21 の表面に垂直な方向において、基板 21 から発光素子 3 に向かう方向を「上側」又は単に「上」とする。また、発光素子 3 から基板 21 向かう方向を「下側」又は単に「下」とする。

#### 【0060】

基板 21 の上にアンダーコート膜 91 が設けられる。アンダーコート膜 91 は、例えば、絶縁膜 91a、91b、91c を有する 3 層積層構造である。絶縁膜 91a はシリコン酸化膜であり、絶縁膜 91b はシリコン窒化膜であり、絶縁膜 91c はシリコン酸化膜である。下層の絶縁膜 91a は、基板 21 とアンダーコート膜 91 との密着性向上のために設けられる。中層の絶縁膜 91b は、外部からの水分及び不純物のプロック膜として設けられる。上層の絶縁膜 91c は、絶縁膜 91b のシリコン窒化膜中に含有する水素原子が半導体層 61 側に拡散しないようにするプロック膜として設けられる。

#### 【0061】

アンダーコート膜 91 の構成は、図 7 に示すものに限定されない。例えば、アンダーコート膜 91 は、単層膜あるいは 2 層積層膜であってもよく、4 層以上積層されていてもよい。また、基板 21 がガラス基板である場合、シリコン窒化膜は比較的密着性が良いため、基板 21 上に直接シリコン窒化膜を形成してもよい。

#### 【0062】

遮光膜 65 は、絶縁膜 91a の上に設けられる。遮光膜 65 は、半導体層 61 と基板 21 との間に設けられる。遮光膜 65 により、半導体層 61 のチャネル領域 61a への基板 21 側からの光の侵入を抑制することができる。あるいは、遮光膜 65 を導電性材料で形成して、所定の電位を与えることで、駆動トランジスタ D R T へのバックゲート効果を与えることができる。なお、遮光膜 65 は、基板 21 上に設けられ、遮光膜 65 を覆って絶縁膜 91a が設けられていてもよい。

#### 【0063】

駆動トランジスタ D R T は、アンダーコート膜 91 の上に設けられる。なお、図 7 では

10

20

30

40

50

、複数のトランジスタのうち、駆動トランジスタD R Tを示しているが、画素回路P I C Aに含まれる発光制御トランジスタB C T、初期化トランジスタI S T、書きトランジスタS S T、リセットトランジスタR S T及び発熱制御トランジスタH S Tも、駆動トランジスタD R Tと同様の積層構造を有する。

#### 【0064】

駆動トランジスタD R Tは、半導体層6 1、ソース電極6 2、ドレイン電極6 3及びゲート電極6 4を有する。半導体層6 1は、アンダーコート膜9 1の上に設けられる。半導体層6 1は、例えば、ポリシリコンが用いられる。ただし、半導体層6 1は、これに限定されず、微結晶酸化物半導体、アモルファス酸化物半導体、低温ポリシリコン等であってもよい。駆動トランジスタD R Tとして、n型T F Tのみ示しているが、p型T F Tを同時に形成しても良い。n型T F Tでは、半導体層6 1は、チャネル領域6 1 a、ソース領域6 1 b、ドレイン領域6 1 c及び低濃度不純物領域6 1 dを有する。低濃度不純物領域6 1 dは、チャネル領域6 1 aとソース領域6 1 bとの間に設けられ、また、チャネル領域6 1 aとドレイン領域6 1 cとの間に設けられる。

10

#### 【0065】

ゲート絶縁膜9 2は、半導体層6 1を覆ってアンダーコート膜9 1の上に設けられる。ゲート絶縁膜9 2は、例えばシリコン酸化膜である。ゲート電極6 4は、ゲート絶縁膜9 2の上に設けられる。また、ゲート電極6 4と同層に第1配線6 6が設けられる。ゲート電極6 4及び第1配線6 6は、例えば、モリブデンタングステン(MoW)が用いられる。図7に示す例では、駆動トランジスタD R Tは、ゲート電極6 4が半導体層6 1の上側に設けられたトップゲート構造である。ただし、これに限定されず、駆動トランジスタD R Tは、半導体層6 1の下側にゲート電極6 4が設けられたボトムゲート構造でもよく、半導体層6 1の上側及び下側の両方にゲート電極6 4が設けられたデュアルゲート構造でもよい。

20

#### 【0066】

層間絶縁膜9 3は、ゲート電極6 4を覆ってゲート絶縁膜9 2の上に設けられる。層間絶縁膜9 3は、例えば、シリコン窒化膜とシリコン酸化膜との積層構造を有する。ソース電極6 2及びドレイン電極6 3は、層間絶縁膜9 3の上に設けられる。ソース電極6 2は、ゲート絶縁膜9 2及び層間絶縁膜9 3に設けられたコンタクトホールを介して、ソース領域6 1 bに接続される。ドレイン電極6 3は、ゲート絶縁膜9 2及び層間絶縁膜9 3に設けられたコンタクトホールを介して、ドレイン領域6 1 cに接続される。ソース電極6 2には、引き回し配線となる第2配線6 7が接続される。ソース電極6 2、ドレイン電極6 3及び第2配線6 7は、例えば、チタン(Ti)、アルミニウム(Al)、チタン(Ti)の3層積層構造を採用することができる。

30

#### 【0067】

第2配線6 7の一部は、第1配線6 6と重なる領域に形成される。層間絶縁膜9 3を介して対向する第1配線6 6と第2配線6 7とで、保持容量C s 1が形成される。また、第1配線6 6は、半導体層6 1の一部と重なる領域に形成される。保持容量C s 1は、ゲート絶縁膜9 2を介して対向する半導体層6 1と第1配線6 6とで形成される容量も含む。

40

#### 【0068】

平坦化膜9 4は、駆動トランジスタD R T及び第2配線6 7を覆って層間絶縁膜9 3の上に設けられる。平坦化膜9 4としては感光性アクリル等の有機材料が用いられる。感光性アクリル等の有機材料は、C V D等により形成される無機絶縁材料に比べ、配線段差のカバレッジ性や、表面の平坦性に優れる。

#### 【0069】

平坦化膜9 4の上に、対向電極2 5、容量絶縁膜9 5、アノード電極2 3、アノード電極絶縁膜9 6の順に積層される。対向電極2 5は、例えばITO(Indium Tin Oxide)等の透光性を有する導電性材料で構成される。対向電極2 5と同層に接続電極2 6 aが設けられる。接続電極2 6 aは、平坦化膜9 4に設けられたコンタクトホールH 1の内部を覆って設けられ、コンタクトホールH 1の底部で第2配線6 7と接続される。

50

## 【0070】

容量絶縁膜95は、対向電極25及び接続電極26aを覆って設けられ、コンタクトホールH1と重なる領域に開口を有する。容量絶縁膜95は、例えば、シリコン窒化膜である。アノード電極23は、容量絶縁膜95を介して対向電極25と対向する。アノード電極23は、コンタクトホールH1を介して接続電極26a及び第2配線67と電気的に接続される。これにより、アノード電極23は、駆動トランジスタDRTと電気的に接続される。アノード電極23は、モリブデン(Mo)、アルミニウム(Al)の積層構造としている。ただし、これに限定されず、アノード電極23は、モリブデン、チタンの金属のいずれか1つ以上を含む材料であってもよい。又は、アノード電極23は、モリブデン、チタンのいずれか1つ以上を含む合金、又は透光性導電材料であってもよい。

10

## 【0071】

容量絶縁膜95を介して対向するアノード電極23と対向電極25との間に容量Cs2が形成される。また、ITOで形成される対向電極25は、アノード電極23を形成する工程において、第2配線67等の各種配線を保護するためのバリア膜としての機能も有する。ところで、アノード電極23のパターニング時、一部において対向電極25がエッチング環境にさらされるが、対向電極25の形成からアノード電極23の形成までの間に行われるアニール処理によって、対向電極25はアノード電極23のエッチングに対し十分な耐性を有する。

## 【0072】

アノード電極絶縁膜96は、アノード電極23を覆って設けられる。アノード電極絶縁膜96は、例えばシリコン窒化膜である。アノード電極絶縁膜96は、アノード電極23の周縁部を覆っており、隣り合う副画素49のアノード電極23を絶縁する。

20

## 【0073】

アノード電極絶縁膜96は、アノード電極23と重なる位置に、発光素子3を実装するための開口OPを有する。開口OPの大きさは、発光素子3の実装工程における実装ズレ量等を考慮し、発光素子3よりも大きい面積の開口とする。すなわち、基板21に垂直な方向からの平面視で、アノード電極23の面積は、発光素子3の面積よりも大きい。さらに、発光素子3は、少なくとも2つの端子(アノード端子33及びカソード端子32)を有し、基板21に垂直な方向からの平面視で、アノード電極23の面積は、少なくとも2つの端子(アノード端子33及びカソード端子32)の一方の面積よりも大きい。例えば発光素子3が平面視で、 $10\mu m \times 10\mu m$ 程度の実装面積である場合、開口OPの面積として、 $20\mu m \times 20\mu m$ 程度は確保されることが好ましい。

30

## 【0074】

発光素子3R、3G、3Bは、それぞれに対応するアノード電極23に実装される。各発光素子3は、アノード端子33がアノード電極23に接するように実装される。発光素子3は、半導体層31、カソード端子32及びアノード端子33を有する。半導体層31は、n型クラッド層、活性層及びp型クラッド層が積層された構成を採用することができる。

## 【0075】

半導体層31は、例えば、窒化ガリウム(GaN)、アルミニウムインジウム燐(AlInP)等の化合物半導体が用いられる。半導体層31は、発光素子3R、3G、3Bごとに異なる材料が用いられてもよい。また、活性層として、高効率化のために数原子層からなる井戸層と障壁層とを周期的に積層させた多重量子井戸構造(MQW構造)が採用されてもよい。また、発光素子3として、半導体基板上に半導体層31が形成された構成でもよい。あるいは、発光素子3単体がアレイ基板2に実装される構成に限定されず、発光素子3を含むLEDチップがアレイ基板2に実装される構成であってもよい。LEDチップは、例えば、発光素子基板と、発光素子基板に設けられた発光素子3と、発光素子基板に設けられ、発光素子3を駆動する回路素子群とを有し、発光素子基板、発光素子3及び回路素子群が1チップに集積された構成が挙げられる。

40

## 【0076】

50

複数の発光素子 3 の間に素子絶縁膜 9 7 が設けられる。素子絶縁膜 9 7 は樹脂材料で形成される。素子絶縁膜 9 7 は、発光素子 3 の側面を覆っており、発光素子 3 のカソード端子 3 2 は、素子絶縁膜 9 7 から露出する。素子絶縁膜 9 7 の上面と、カソード端子 3 2 の上面とが同一面を形成するように、素子絶縁膜 9 7 は平坦に形成される。ただし、素子絶縁膜 9 7 の上面の位置は、カソード端子 3 2 の上面の位置と異なっていてもよい。

#### 【 0 0 7 7 】

カソード電極 2 2 は、複数の発光素子 3 及び素子絶縁膜 9 7 を覆って、複数の発光素子 3 に電気的に接続される。より具体的には、カソード電極 2 2 は、素子絶縁膜 9 7 の上面と、カソード端子 3 2 の上面とに亘って設けられる。カソード電極 2 2 は、例えば I T O 等の透光性を有する導電性材料が用いられる。これにより、発光素子 3 からの出射光を効率よく外部に取り出すことができる。カソード電極 2 2 は、表示領域 A A に実装された複数の発光素子 3 のカソード端子 3 2 と電気的に接続される。

10

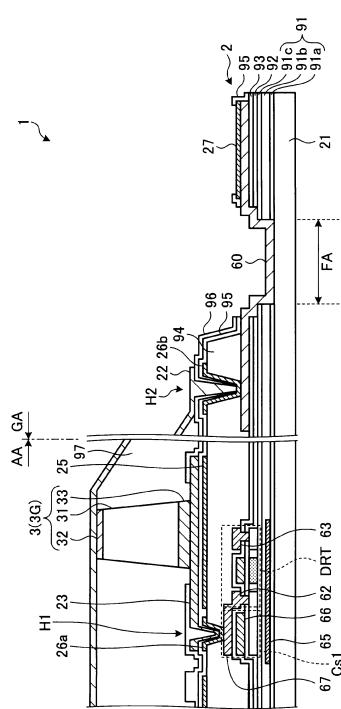

#### 【 0 0 7 8 】

図 8 に示すように、カソード電極 2 2 は、表示領域 A A の外側に設けられた陰極コンタクト部（コンタクトホール H 2 ）で、アレイ基板 2 側に設けられたカソード配線 6 0 と接続される。なお、図 6 では、周辺領域 G A の断面構成と、表示領域 A A の断面構成との対応関係を分かりやすくするために、周辺領域 G A と表示領域 A A とを併せて示している。

20

#### 【 0 0 7 9 】

図 8 に示すように、表示装置 1 は、周辺領域 G A において、端子部 2 7 、折曲領域 F A 及び陰極コンタクト部（コンタクトホール H 2 ）を有する。端子部 2 7 は、駆動 I C 2 1 0 又はフレキシブルプリント基板等の配線基板と接続される端子である。折曲領域 F A は、アレイ基板 2 のうち、端子部 2 7 側の周辺領域 G A を折り曲げるため領域である。なお、折曲領域 F A が設けられる場合には、基板 2 1 として可撓性を有する樹脂材料が用いられる。

20

#### 【 0 0 8 0 】

具体的には、アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 は、表示領域 A A から周辺領域 G A に亘って、基板 2 1 の端部まで設けられている。アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 は、折曲領域 F A で除去される。アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 は、折曲領域 F A において、エッチングにより除去される。この場合、ポリイミド等の樹脂材料で構成される基板 2 1 の表面が一部エッチングにより浸食されて凹部が形成される場合がある。

30

#### 【 0 0 8 1 】

カソード配線 6 0 は、層間絶縁膜 9 3 の上に設けられる。つまり、カソード配線 6 0 は、ソース電極 6 2 、ドレイン電極 6 3 及び第 2 配線 6 7 と同層に設けられ、同じ材料で形成される。カソード配線 6 0 は、折曲領域 F A に跨がって設けられ、アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 と、基板 2 1 とで形成される段差に沿って設けられる。また、カソード配線 6 0 は、折曲領域 F A において基板 2 1 の上に設けられ、折曲領域 F A と基板 2 1 の端部との間ににおいて、層間絶縁膜 9 3 の上に設けられる。

30

#### 【 0 0 8 2 】

平坦化膜 9 4 は、周辺領域 G A の、折曲領域 F A 及び折曲領域 F A と基板 2 1 の端部との間の領域で除去される。平坦化膜 9 4 には、折曲領域 F A と表示領域 A A との間の領域にコンタクトホール H 2 が設けられる。カソード配線 6 0 はコンタクトホール H 2 の底面に露出する、また、素子絶縁膜 9 7 の厚さは、表示領域 A A の周縁部から周辺領域 G A に向かって、薄くなるように設けられる。カソード電極 2 2 は、コンタクトホール H 2 の内部に設けられた接続電極 2 6 b を介して、カソード配線 6 0 と電気的に接続される。接続電極 2 6 b は、対向電極 2 5 及び接続電極 2 6 a と同層に設けられ、対向電極 2 5 及び接続電極 2 6 a と同じ材料で形成される。

40

#### 【 0 0 8 3 】

また、端子部 2 7 は、折曲領域 F A と基板 2 1 の端部との間の領域で、カソード配線 6 0 の上に設けられる。容量絶縁膜 9 5 は、端子部 2 7 を覆って設けられ、端子部 2 7 と重

50

なる領域に開口を有する。

【0084】

以上のように、表示素子として発光素子3を用いた表示装置1が構成される。なお、表示装置1は、必要に応じて、カソード電極22の上側に、カバーガラスやタッチパネル等を設けてよい。また、この場合、表示装置1とカバーガラス等の部材との間に、樹脂などを用いた充填材が設けられていてもよい。また、表示装置1において、発光素子3の上部でカソード電極22に接続されるフェースアップ構造に限定されず、発光素子3の下部が、アノード電極23及びカソード電極22に接続される、いわゆるフェースダウン構造であってもよい。

【0085】

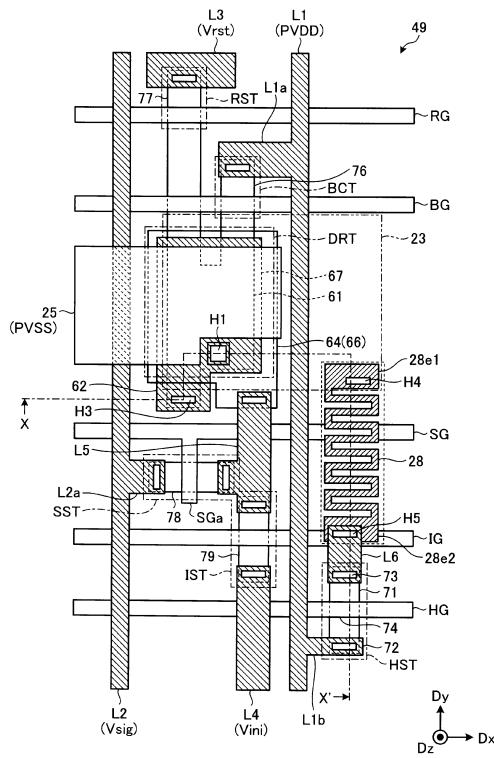

次に、副画素49及び発熱抵抗体28の詳細な構成について説明する。図9は、第1実施形態に係る表示装置の、1つの副画素を拡大して示す平面図である。図10は、図9のX-X'断面図である。なお、図9では、図面を見やすくするために、発光素子3を省略して示す。また、図9では、アノード電極23を二点鎖線で示し、アノード電源線L1、映像信号線L2、リセット信号線L3、初期化信号線L4、接続配線L5、L6及び発熱抵抗体28に斜線を付けて示している。また、各トランジスタが有する半導体層61、71、76、77、78、79を点線で示している。

10

【0086】

図9に示すように、アノード電源線L1、映像信号線L2及び初期化信号線L4は、第2方向Dyに延在する。リセット信号線L3はアノード電源線L1と映像信号線L2との間に設けられる。なお、リセット信号線L3は、図面を見やすくするために簡略化して示しているが、アノード電源線L1等と同様に第2方向Dyに延在して設けられる。

20

【0087】

リセット制御走査線RG、発光制御走査線BG、書き制御走査線SG、初期化制御走査線IG及び発熱制御走査線HGは、それぞれ、第1方向Dxに延在し、平面視で、アノード電源線L1及び映像信号線L2とそれぞれ交差する。接続配線L5は、駆動トランジスタDRT、初期化トランジスタIST及び書きトランジスタSSTを接続する。接続配線L6は、発熱抵抗体28と、発熱制御トランジスタHSTとを接続する。

【0088】

駆動トランジスタDRTを構成する半導体層61、ソース電極62(第2配線67)、ゲート電極64(第1配線66)は、アノード電源線L1、映像信号線L2、発光制御走査線BG及び書き制御走査線SGで囲まれた領域に設けられる。半導体層61は、ゲート電極64(第1配線66)と重ならない部分で、コンタクトホールH3を介してソース電極62(第2配線67)と接続される。アノード電極23及び対向電極25は、駆動トランジスタDRTと重なる領域に設けられる。対向電極25は、カソード電源線L10に接続され、カソード電源電位PVSSが供給される。これにより、対向電極25は、アレイ基板2の各トランジスタ及び各種配線と、アノード電極23及び発光素子3との間をシリルドすることができる。

30

【0089】

アノード電極23は、駆動トランジスタDRTと重ならない領域まで延在し、アノード電極23の一部が発熱抵抗体28の一端側28e1と重なる。発熱抵抗体28は、平面視でミアンダ状の配線パターンを有し、全体として、アノード電源線L1に沿って第2方向Dyに延在する。発熱抵抗体28の一端側28e1は、コンタクトホールH4を介してアノード電極23と接続される。また、発熱抵抗体28の他端側28e2は、コンタクトホールH5を介して接続配線L6と接続される。

40

【0090】

発熱制御トランジスタHSTは、半導体層71、ソース電極72、ドレイン電極73及びゲート電極74を有する。半導体層71は、第2方向Dyに延在し、発熱制御走査線HGと平面視で交差する。半導体層71のうち、発熱制御走査線HGと重なる領域にチャネル領域が形成される。発熱制御走査線HGのうち半導体層71と重なる部分が、発熱制御

50

トランジスタHSTのゲート電極74として機能する。半導体層71の一端側は、アノード電源線接続部L1bと接続される。半導体層71の他端側は、接続配線L6と接続される。アノード電源線接続部L1bは、アノード電源線L1から第1方向Dxに分岐された部分である。アノード電源線接続部L1b及び接続配線L6の一部が、それぞれソース電極72及びドレイン電極73として機能する。

#### 【0091】

このような構成により、発熱抵抗体28の一端側28e1がアノード電極23に電気的に接続され、発熱抵抗体28の他端側28e2が発熱制御トランジスタHSTを介してアノード電源線L1に電気的に接続される。

#### 【0092】

発光制御トランジスタBCTは、半導体層76有する。半導体層76は駆動トランジスタDRTの半導体層61と接続されており、発光制御走査線BGと平面視で交差する。半導体層76の一端側は、アノード電源線接続部L1aと電気的に接続される。アノード電源線接続部L1aは、アノード電源線L1から第1方向Dxに分岐された部分である。これにより、駆動トランジスタDRT及び発光制御トランジスタBCTには、アノード電源線L1に電気的に接続される。

#### 【0093】

リセットトランジスタRSTは、半導体層77を有する。半導体層77の一端側は、リセット信号線L3と接続され、半導体層77の他端側は、駆動トランジスタDRTの半導体層61と接続される。半導体層77は、第2方向Dyに延在し、平面視で発光制御走査線BG及びリセット制御走査線RGと交差する。半導体層77の、リセット制御走査線RGと重なる部分にチャネル領域が形成される。

#### 【0094】

半導体層77及び半導体層76は、半導体層61と接続されているので、図3に示す回路図に示す、駆動トランジスタDRT、発光制御トランジスタBCT及びリセットトランジスタRSTの接続構成が実現される。

#### 【0095】

書込トランジスタSSTは半導体層78を有する。半導体層78の一端側は、映像信号線接続部L2aと接続される。映像信号線接続部L2aは、映像信号線L2から第1方向Dxに分岐された部分である。半導体層78の他端側は、接続配線L5と接続される。半導体層78は、第1方向Dxに延在し、平面視で分岐部SGaと交差する。分岐部SGaは、書込制御走査線SGから第2方向Dyに分岐された部分である。

#### 【0096】

初期化トランジスタISTは半導体層79を有する。半導体層79の一端側は、初期化信号線L4と接続される。半導体層79の他端側は、接続配線L5と接続される。半導体層79は、第2方向Dyに延在し、平面視で初期化制御走査線IGと交差する。

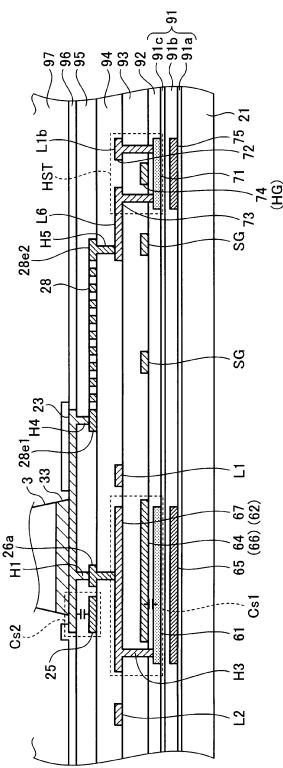

#### 【0097】

図10に示すように、発熱抵抗体28は、平坦化膜94の上に設けられる。発熱抵抗体28は、対向電極25と同層に設けられ、基板21に垂直な方向において、映像信号線L2、発熱抵抗体28、アノード電極23の順に積層される。発熱抵抗体28は、対向電極25と同じ材料、すなわちITO等の透光性を有する導電性材料で構成される。発熱抵抗体28は、アノード電極23よりも高いシート抵抗値を有し、発熱抵抗体28に電流が流れた場合に、電気エネルギーが良好に熱に変換される。なお、発熱抵抗体28は、ITOに限定されず、In<sub>2</sub>O<sub>3</sub>にGe、Mo、F、Ti、Zr、Hf、Nb、Ta、W、あるいはTeをドープした透光性導電膜、ZnOにAl、Ga、B、In、Y、Sc、F、V、Si、Ge、Ti、Zr、あるいはHfをドープした透光性導電膜、SnO<sub>2</sub>にSb、F、As、Nb、あるいはTaをドープした透光性導電膜であってもよい。又は、発熱抵抗体28は、モリブデン(Mo)若しくはMo合金、タンゲステン(W)若しくはW合金、又はチタン(Ti)若しくはTi合金等の高融点材料で形成されてもよい。

#### 【0098】

10

20

30

40

50

また、発熱抵抗体 28 は、容量絶縁膜 95 を介してアノード電極 23 と異なる層に設けられ、容量絶縁膜 95 に設けられたコンタクトホール H4 を介してアノード電極 23 と接続される。これにより、発熱抵抗体 28 で発生した熱が、コンタクトホール H4 及びアノード電極 23 を経由して発光素子 3 に良好に伝わる。また、アノード電極 23 は、発熱抵抗体 28 よりも、平面視での面積が大きく、熱伝導率が高い。このため、コンタクトホール H4 の周囲の、アノード電極 23 と発熱抵抗体 28 との重畠部分でも、発熱抵抗体 28 で発生した熱がアノード電極 23 に伝わる。

#### 【 0 0 9 9 】

発熱制御トランジスタ HST の積層構造は、図 7 に示した駆動トランジスタ DRT と同様であり、詳細な説明は省略する。ソース電極 72 (アノード電源線接続部 L1b) 及びドレイン電極 73 (接続配線 L6) 、アノード電源線 L1 及び映像信号線 L2 は、駆動トランジスタ DRT のソース電極 62 (第 2 配線 67) 及びドレイン電極 63 と同層に設けられる。なお、図 10 では図示されないが、リセット信号線 L3 、初期化信号線 L4 及び接続配線 L5 もアノード電源線 L1 等と同層に設けられる。

10

#### 【 0 1 0 0 】

発熱制御走査線 HG 、初期化制御走査線 IG 及び書き制御走査線 SG は、ゲート電極 64 (第 1 配線 66) と同層に設けられる。なお、図 10 では図示されないが、発光制御走査線 BG 及びリセット制御走査線 RG も発熱制御走査線 HG 等と同層に設けられる。

#### 【 0 1 0 1 】

発熱制御トランジスタ HST の半導体層 71 及び各トランジスタが有する半導体層 76 、77、78、79 は、駆動トランジスタ DRT の半導体層 61 と同層に設けられる。ただし、発熱制御トランジスタ HST の半導体層 71 、ソース電極 72 (アノード電源線接続部 L1b) 及びドレイン電極 73 及びゲート電極 74 は、それぞれ駆動トランジスタ DRT と異なる層に設けられていてもよい。

20

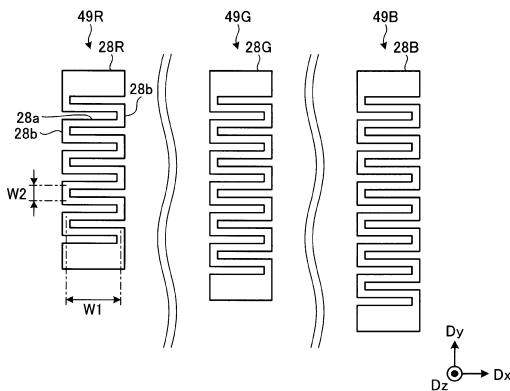

#### 【 0 1 0 2 】

図 11 は、第 1 副画素が有する第 1 発熱抵抗体、第 2 副画素が有する第 2 発熱抵抗体及び第 3 副画素が有する第 3 発熱抵抗体を比較して説明するための説明図である。図 11 に示すように、第 1 副画素 49R は第 1 発熱抵抗体 28R を有する。第 2 副画素 49G は第 2 発熱抵抗体 28G を有する。第 3 副画素 49B は第 3 発熱抵抗体 28B を有する。図 11 では、第 1 発熱抵抗体 28R 、第 2 発熱抵抗体 28G 及び第 3 発熱抵抗体 28B を模式的に並べて示している。

30

#### 【 0 1 0 3 】

第 1 発熱抵抗体 28R 、第 2 発熱抵抗体 28G 及び第 3 発熱抵抗体 28B は、それぞれ複数の第 1 部分 28a と、複数の第 2 部分 28b とを有する。複数の第 1 部分 28a は、それぞれ第 1 方向 Dx に延在し、第 2 方向 Dy に配列される。第 2 部分 28b は、第 2 方向 Dy に隣り合う 2 つの第 1 部分 28a の同じ側の端部を接続する。複数の第 1 部分 28a と複数の第 2 部分 28b とが接続されてミアンダ状の配線パターンが形成される。

30

#### 【 0 1 0 4 】

第 1 発熱抵抗体 28R 、第 2 発熱抵抗体 28G 及び第 3 発熱抵抗体 28B は、配線パターンの配線長が異なる。第 1 発熱抵抗体 28R 、第 2 発熱抵抗体 28G 、第 3 発熱抵抗体 28B の順に配線長が長い。ここで、各発熱抵抗体 28 の配線長は、配線パターンに沿った合計の長さである。つまり、各発熱抵抗体 28 の配線長は、複数の第 1 部分 28a の配線長 W1 と、複数の第 2 部分 28b の配線長 W2 との合計の長さである。

40

#### 【 0 1 0 5 】

これにより、第 1 発熱抵抗体 28R 、第 2 発熱抵抗体 28G 及び第 3 発熱抵抗体 28B は、異なる抵抗値を有する。具体的には、第 1 発熱抵抗体 28R の抵抗値は、第 2 発熱抵抗体 28G の抵抗値及び第 3 発熱抵抗体 28B の抵抗値よりも小さい。また、第 2 発熱抵抗体 28G の抵抗値は、第 3 発熱抵抗体 28B の抵抗値よりも小さい。

#### 【 0 1 0 6 】

これにより、第 1 発熱抵抗体 28R に流れる電流が、第 2 発熱抵抗体 28G 及び第 3 發

50

熱抵抗体 28B よりも大きくなり、第1発熱抵抗体 28R の発熱量が大きくなる。これにより、各副画素 49 が有する発光素子 3R の発光効率が、発光素子 3G、発光素子 3B よりも小さい場合であっても、第1発熱抵抗体 28R により発光素子 3R を良好に加熱することで、発光素子 3R を安定して発光させることができる。

#### 【0107】

なお、図 11 では、第1発熱抵抗体 28R、第2発熱抵抗体 28G 及び第3発熱抵抗体 28B の第2方向 Dy の長さを異ならせる例を示したが、他の構成で抵抗値を異ならせてよい。例えば、第2方向 Dy の長さ、つまり第1部分 28a 及び第2部分 28b の配線長 W1、W2 を異ならせててもよく、第1部分 28a 及び第2部分 28b のそれぞれの配線幅を異ならせててもよい。あるいは、第1発熱抵抗体 28R、第2発熱抵抗体 28G 及び第3発熱抵抗体 28B としてそれぞれ異なる材料を用いてもよい。

10

#### 【0108】

なお、図 11 に示した各発熱抵抗体 28 の配線パターンはあくまで一例であり、異なる配線パターンであってもよい。第1発熱抵抗体 28R、第2発熱抵抗体 28G 及び第3発熱抵抗体 28B は、同じ配線パターンで形成され、同じ抵抗値を有していてもよい。また、第1副画素 49R、第2副画素 49G 及び第3副画素 49B の全てが、発熱抵抗体 28 を有する構成に限定されない。少なくとも第1副画素 49R が第1発熱抵抗体 28R を有し、第2副画素 49G 及び第3副画素 49B の少なくとも一方が発熱抵抗体 28 を有しない構成を採用することもできる。

#### 【0109】

20

##### (第2実施形態)

図 12 は、第2実施形態に係る画素回路を示す回路図である。なお、以下の説明においては、上述した実施形態で説明したものと同じ構成要素には同一の符号を付して重複する説明は省略する。

#### 【0110】

図 12 に示すように、第2実施形態に係る画素回路 PICA は、第1実施形態に比べて、抗体信号線 L7 を有する構成が異なる。抗体信号線 L7 には、駆動 ICA210 から、抗体駆動信号 Vpreht が供給される。発熱抵抗体 28 の他端側 28e2 は、発熱制御トランジスタ HST を介して抗体信号線 L7 に接続される。発熱抵抗体 28 の一端側 28e1 は、第1実施形態と同様にアノード電極 23 に接続される。

30

#### 【0111】

各トランジスタの動作は、図 5 に示すプレヒート期間 PH と同様であり、発熱制御トランジスタ HST 及びリセットトランジスタ RST がオンになり、その他のトランジスタがオフになる。これにより、抗体信号線 L7、発熱制御トランジスタ HST、発熱抵抗体 28、リセットトランジスタ RST 及びリセット信号線 L3 が導通して電流経路が形成される。発熱抵抗体 28 には、抗体信号線 L7 から供給される抗体駆動信号 Vpreht に応じて電流が流れる。

#### 【0112】

本実施形態では、発熱抵抗体 28 に供給される電位が、アノード電源線 L1 (アノード電源電位 PVDD) から独立して制御される。このため、表示装置 1 の表示期間に、発熱抵抗体 28 の発熱を制御することも可能である。

40

#### 【0113】

##### (第3実施形態)

図 13 は、第3実施形態に係る画素回路を示す回路図である。図 13 に示すように、第3実施形態に係る画素回路 PICA は、第1実施形態に比べて、発熱抵抗体 28 の一端側 28e1 が、カソード電極 22 に電気的に接続される構成が異なる。発熱抵抗体 28 の他端側 28e2 は、第1実施形態と同様に、発熱制御トランジスタ HST を介してアノード電源線 L1 に電気的に接続される。

#### 【0114】

第3実施形態では、図 5 に示すプレヒート期間 PH において、発熱制御トランジスタ H

50

S Tがオンになり、その他のトランジスタがオフになる。これにより、アノード電源線L 1、発熱制御トランジスタH S T、発熱抵抗体2 8及びカソード電源線L 1 0が導通して電流経路が形成される。発熱抵抗体2 8には、アノード電源線L 1(アノード電源電位P V D D)から電流が流れる。

#### 【0 1 1 5】

第3実施形態では、プレヒート期間P Hにおいて、発熱制御トランジスタH S Tのオン、オフの切り換えのみで発熱抵抗体2 8の発熱が制御できるので、プレヒート期間P Hでの画素回路P I C Aの駆動を簡易にできる。なお、第3実施形態では、発熱抵抗体2 8の一端側2 8 e 1がアノード電極2 3に接続されていない。この場合であっても、図9及び図1 0と同様に、アノード電極2 3の一部が発熱抵抗体2 8と重なって設けられる構成とすることで、発熱抵抗体2 8で発生した熱を、アノード電極2 3に効率よく伝えることができる。

10

#### 【0 1 1 6】

なお、本実施形態の構成は第2実施形態にも適用できる。すなわち、図1 2に示す画素回路P I C Aにおいて、抵抗体信号線L 7、発熱制御トランジスタH S T、発熱抵抗体2 8及びカソード電源線L 1 0が導通して電流経路が形成される構成も採用できる。

#### 【0 1 1 7】

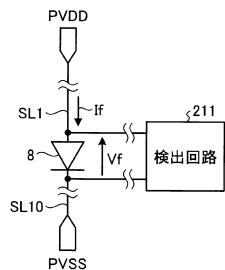

##### (第4実施形態)

図1 4は、第4実施形態に係る、温度センサを有する画素を示す平面図である。図1 5は、温度センサの一例を説明するための説明図である。図1 4に示すように、表示装置1 Aは、画素P i xに温度センサ8及び温度センサ回路8 1を有する。温度センサ8は、例えばp n接合ダイオードを用いることができる。温度センサ回路8 1は、温度センサ8を駆動するための回路である。温度センサ回路8 1は、複数のトランジスタ等の回路素子を備え、温度センサ8への駆動信号の供給を制御する。

20

#### 【0 1 1 8】

図1 5に示すように、温度センサ8は、センサアノード電源線S L 1及びセンサカソード電源線S L 1 0に接続され、センサアノード電源線S L 1及びセンサカソード電源線S L 1 0から順バイアス電圧信号が印加される。温度センサ回路8 1は、温度センサ8に一定の順方向電流I fが流れるように制御する。

#### 【0 1 1 9】

検出回路2 1 1は、温度センサ8から、出力信号としてアノードとカソードとの間の出力電圧V fを受け取る。検出回路2 1 1は、駆動I C 2 1 0に設けられていてもよいし、駆動I C 2 1 0とは別のI Cとして設けられていてもよい。検出回路2 1 1は、p n接合ダイオードの出力電圧V fの温度依存性に基づいて画素P i xの温度を検出することができる。駆動I C 2 1 0は、画素P i xの温度の情報に基づいて、プレヒート期間P Hにおいて、発熱抵抗体2 8に流れる電流値又は発熱制御トランジスタH S Tのオン時間を適切に制御することができる。

30

#### 【0 1 2 0】

なお、温度センサ回路8 1は、温度センサ8に一定の逆バイアス電圧信号を印加してもよい。検出回路2 1 1は、温度センサ8の出力信号として逆バイアス電流値を受け取って、逆バイアス電流値の温度依存性に基づいて温度を検出してもよい。また、温度センサ8は、各画素P i xに設けられていてもよいし、複数の画素P i xに対して1つの温度センサ8が設けられていてもよい。また、温度センサ8は各副画素4 9の画素回路P I C Aに設けられていてもよい。この場合、温度センサ8は、画素回路P I C Aに設けられたトランジスタの一部をセンサとして共用してもよい。又は、温度センサ8は、発光素子3を逆バイアス駆動することでセンサとして共用してもよい。

40

#### 【0 1 2 1】

これまでの説明において、アノード端子3 3、カソード端子3 2として表記してきた部分においては、発光素子3の接続方向、及び電圧の印加方向によっては明細書中の記載に限定するものではなく、逆転していても良い。また、図7、図8においては、発光素子3

50

の一方の電極が下側に、他方の電極が上側にある構成を示しているが、その両方が下側、つまりアレイ基板 2 に対面する側に有る構成であっても良い。

### 【 0 1 2 2 】

以上、本発明の好適な実施の形態を説明したが、本発明はこのような実施の形態に限定されるものではない。実施の形態で開示された内容はあくまで一例にすぎず、本発明の趣旨を逸脱しない範囲で種々の変更が可能である。本発明の趣旨を逸脱しない範囲で行われた適宜の変更についても、当然に本発明の技術的範囲に属する。上述した各実施形態及び各変形例の要旨を逸脱しない範囲で、構成要素の種々の省略、置換及び変更のうち少なくとも 1 つを行うことができる。

### 【 符号の説明 】

#### 【 0 1 2 3 】

- |                       |    |

|-----------------------|----|

| 1、 1 A 表示装置           | 10 |

| 2 アレイ基板               |    |

| 3、 3 R、 3 G、 3 B 発光素子 |    |

| 8 温度センサ               |    |

| 1 2 駆動回路              |    |

| 2 1 基板                |    |

| 2 2 カソード電極            |    |

| 2 3 アノード電極            |    |

| 2 7 端子部               | 20 |

| 2 8 発熱抵抗体             |    |

| 2 8 R 第 1 発熱抵抗体       |    |

| 2 8 G 第 2 発熱抵抗体       |    |

| 2 8 B 第 3 発熱抵抗体       |    |

| 2 8 e 1 一端側           |    |

| 2 8 e 2 他端側           |    |

| 3 1 半導体層              |    |

| 3 2 カソード端子            |    |

| 3 3 アノード端子            |    |

| 4 9 副画素               | 30 |

| 6 0 カソード配線            |    |

| 2 1 0 駆動 I C          |    |

| D R T 駆動トランジスタ        |    |

| B C T 発光制御トランジスタ      |    |

| I S T 初期化トランジスタ       |    |

| S S T 書込トランジスタ        |    |

| R S T リセットトランジスタ      |    |

| H S T 発熱制御トランジスタ      |    |

| B G 発光制御走査線           |    |

| H G 発熱制御走査線           | 40 |

| I G 初期化制御走査線          |    |

| R G リセット制御走査線         |    |

| S G 書込制御走査線           |    |

| L 1 アノード電源線           |    |

| L 1 0 カソード電源線         |    |

| P i x 画素              |    |

| P I C A 画素回路          |    |

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【図5】

【 叁 6 】

10

20

【図7】

〔 四 8 〕

30

40

50

【図 9】

【図 10】

10

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

10

20

【図 1 5】

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

G 0 9 F      9/30      3 3 0

東京都港区西新橋三丁目 7 番 1 号 株式会社ジャパンディスプレイ内

審査官 道祖土 新吾

(56)参考文献

特開 2007 - 081094 (JP, A)

特開 2005 - 309731 (JP, A)

特開 2002 - 307734 (JP, A)

特開 2005 - 321684 (JP, A)

特開 2014 - 082383 (JP, A)

米国特許出願公開第 2005 / 0258446 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 F 9 / 0 0 - 9 / 4 6

G 0 9 G 3 / 0 0 - 3 / 3 8