### (10) **DE 103 10 554 B4** 2007.10.04

(12)

# **Patentschrift**

(21) Aktenzeichen: 103 10 554.9(22) Anmeldetag: 11.03.2003(43) Offenlegungstag: 30.09.2004

(45) Veröffentlichungstag

der Patenterteilung: 04.10.2007

(51) Int Cl.8: **H01L 23/522** (2006.01)

**H01L 23/62** (2006.01) **H01L 29/78** (2006.01) **H03F 1/00** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

#### (73) Patentinhaber:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler & Zinkler, 82049 Pullach

(72) Erfinder:

Krumbein, Ulrich, Dr., 83026 Rosenheim, DE; Taddiken, Hans, Dr., 81737 München, DE; Herzum, Christian, 82343 Pöcking, DE; Kühn, Christian, Dr., 80339 München, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US 59 43 598 A US 55 21 418 A US 50 94 965 A

### $(54) \ Bezeichnung: \textbf{Feldeffekttransistor und Verst\"{a}rkerschaltung \ mit \ dem \ Feldeffekttransistor}$

(57) Hauptanspruch: Feldeffekttransistor, mit einem Substrat (10):

einem Sourcebereich (14) und einem Drainbereich (16), die in dem Substrat (10) gebildet sind;

einem Gate (20);

einer ersten nicht-planaren Metallisierungsebene (42), die auf dem Substrat (10) gebildet ist und einen ersten Abschnitt (42a), der mit dem Sourcebereich (14) verbunden ist, einen zweiten Abschnitt (42b), der mit dem Drainbereich (16) verbunden ist, und einen dritten Abschnitt (42c), der das Gate (20) zumindest teilweise überdeckt, umfasst, wobei der dritte Abschnitt (42c) von dem Gate (20) isoliert ist, um das Gate (20) gegenüber elektrostatischen oder elektrodynamischen Störungen abzuschirmen, und wobei der dritte Abschnitt (42c) eine dem Substrat (10) abgewandte Oberfläche des Gates (20), eine sourceseitige Seitenwand des Gates (20) und zumindest teilweise die drainseitige Seitenwand des Gates (20) bedeckt; und einer zweiten, planaren Metallisierungsebene (30), die oberhalb des Substrats (10) beabstandet von der ersten Metallisierungsebene (42) angeordnet ist und über eine Durchkontaktierung...

### **Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf einen Feldeffekttransistor mit planaren und nicht-planaren Metallisierungsebenen bzw. planaren und nicht-planaren Abschnitten von Metallisierungsebenen sowie einer Verstärkerschaltung mit dem Feldeffekttransistor.

**[0002]** Als Großsignalverstärker, die beispielsweise in Basisstationen oder Mobiltelefonen verwendet werden, werden LDMOS-Transistoren (LDMOS = lateral diffused metal oxide semiconductor) verwendet. Die auf dem Markt verfügbaren LDMOS-Transistoren können dabei in zwei Typen unterschieden werden.

**[0003]** Der erste Typ umfasst eine oder mehrere planare Metallisierungsebenen, die über Kontaktlöcher und Vias bzw. Durchgangslochleiter, wie sie auch in Standard-CMOS-Technologien Verwendung finden, mit Source, Drain und Gate des Feldeffekttransistors verbunden sind.

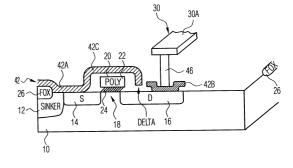

[0004] Fig. 1A zeigt ein Beispiel für eine bekannte Ausführungsform eines Feldeffekttransistors mit einer oder mehreren planaren Metallisierungsebenen. In Fig. 1A ist schematisch ein Feldeffekttransistor gezeigt, welcher in einem Substrat 10 gebildet ist. In dem Substrat ist ein Sinker- bzw. Substratkontakt 12, ein Sourcebereich 14 sowie ein Drainbereich 16 gebildet. Zwischen dem Sourcebereich 14 und dem Drainbereich 16 liegt der Kanalbereich 18. Oberhalb des Kanalbereichs 18 ist das Gate 20 gebildet, welches eine Polysiliziumschicht 22 aufweist, die über eine dünne Oxidschicht 24 von dem Kanalbereich 18 beabstandet ist. Ferner ist in Bereichen des Substrats 10, in dem keine Abschnitte gebildet sind, eine Feldoxidschicht 26 an der Oberfläche des Substrats 10 gebildet.

[0005] Bei dem in Fig. 1A gezeigten, bekannten Beispiel sind zwei planare Metallisierungsebenen 28 und 30 gebildet, die beabstandet voneinander oberhalb der Substratoberfläche 32 gebildet sind. Die erste Metallisierungsebene 28 umfasst einen ersten Abschnitt 28a sowie einen zweiten Abschnitt 28b. Der Abschnitt 28a der ersten Metallisierungsebene ist über einen ersten Kontakt 34 mit dem Sinker 12 verbunden. Über einen zweiten Kontakt 36 ist der erste Abschnitt 28a der ersten planaren Metallisierungsebene 28 mit dem Sourcebereich 14 verbunden. Der zweite Abschnitt 28b der ersten Metallisierungsebene 28 ist über einen dritten Kontakt 38 mit dem Drainbereich 16 verbunden.

[0006] Die zweite planare Metallisierungsebene 30 umfasst einen ersten Abschnitt 30a, der sich bei dem dargestellten Beispiel im wesentlichen parallel beabstandet von dem zweiten Abschnitt 28b der ersten planaren Metallisierungsebene 28 erstreckt und mit

diesem ersten Abschnitt 28b der ersten planaren Metallisierungsebene über einen vierten Kontakt 40 verbunden ist. Wie oben schon erwähnt, beschreibt das anhand der Fig. 1A dargestellte Beispiel eine Standard CMOS-Version mit planaren Metallisierungen. Zur Herstellung einer planaren Leiterbahn für den Drainbereich wird die Topologie mit einem Oxid aufgefüllt und, beispielsweise durch CMP (CMP = chemisch mechanisches Polieren) planarisiert. Anschließend werden Kontaktlöcher zum Silizium geätzt und mit Wolfram aufgefüllt, um die in Fig. 1A gezeigten Kontakte zu erzeugen. Auf die so gebildete Struktur wird dann eine planare Metallisierungsebene angeordnet. Der Nachteil dieser Anordnung besteht darin, dass eine Abschirmung des Gates 20 nicht ausreichend gut wirksam ist.

**[0007]** Ein Vorteil der Verwendung von planaren Metallisierungsebenen besteht darin, dass an planaren Metallisierungsebenen Elektromigration nicht oder kaum auftritt. Planare Metallisierungsebenen und mit ihnen aufgebaute Bauelemente weisen deshalb eine erhöhte Stromtragfähigkeit auf. Ein weiterer Vorteil der Verwendung planarer Metallisierungsebenen besteht darin, dass eine hohe Packungsdichte, beispielsweise eine hohe Packungsdichte von Speicherzellen, erreichbar ist.

**[0008]** Der zweite Typ von LDMOS-Transistoren weist eine oder mehrere nicht-planare Metallisierungsebenen auf.

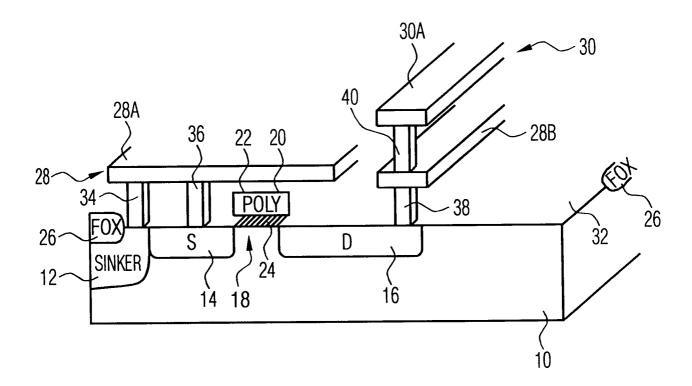

[0009] Fig. 1B zeigt einen herkömmlichen Ansatz, bei dem nicht-planare Metallisierungsebenen verbunden werden. In Fig. 1B ist ein Feldeffekttransistor gezeigt, ähnlich wie in Fig. 1A wobei hier gleiche Bezugszeichen für gleiche Elemente verwendet werden, und wobei eine erneute Beschreibung der bereits anhand der Fig. 1A beschriebenen Elemente nicht erfolgt. Anders als bei dem in Fig. 1A gezeigten, herkömmlichen Ansatz werden Fig. 1B keine planaren Metallisierungsebenen verwendet, sondern nicht-planare Metallisierungsebenen, welche sich im wesentlichen an die Kontur der Oberfläche des Halbleiterbauelements anpassen. Auch hier werden zwei Metallisierungsebenen verwendet, nämlich die erste nicht-planare Metallisierungsebene 42 und die zweite nicht-planare Metallisierungsebene 44. Die erste nicht-planare Metallisierungsebene 42 umfasst einen ersten Abschnitt 42a, der sich ausgehend von dem Feldoxid 26 über den Sinker 12, den Sourcebereich 14, das Gate 20 bis über den Drainbereich 16 erstreckt. Der erste Abschnitt 42a der ersten nicht-planaren Metallisierungsebene 42 ist zumindest teilweise auf der Oberfläche des Substrats 10 angeordnet und ist so in Kontakt mit dem Feldoxid 26, dem Sinker 12 und zumindest einem Abschnitt des Sourcebereichs 14. Wie zu erkennen ist, erstreckt sich der erste Abschnitt 42a weiter um das Gate 20, wobei dieser durch eine geeignete Isolationsschicht beabstandet von dem Gate **20** angeordnet ist. In <u>Fig. 1B</u> ist ferner der Abstand delta gezeigt, der zwischen dem Drainbereich **16** und dem Ende des ersten Abschnitts **42a** eingestellt ist.

[0010] Die erste nicht-planare Metallisierungsebene 42 umfasst ferner einen zweiten Abschnitt 42b, der den Drainbereich 16 zumindest teilweise kontaktiert.

[0011] Die zweite nicht-planare Metallisierungsebene 44 umfasst einen ersten Abschnitt 44a, der durch eine geeignete Isolationsschicht von den übrigen Schichten getrennt ist und sich im Bereich des Drainbereichs 16 zu dem zweiten Abschnitt 42b der ersten nicht-planaren Metallisierungsebene erstreckt und mit demselben in Kontakt ist.

[0012] Gemäß dem in Fig. 1B dargestellten Beispiel werden die Metallisierungsebenen ohne Planarisierung aufgebracht. Der Nachteil dieser Vorgehensweise besteht in den sich ergebenden Kanten und Stufen über die Leiterbahnen der Metallisierungsebene laufen. Dies kostet zum einen Platz und beeinträchtigt zum anderen die Elektromigrationfestigkeit. Im Drainbereich befindet sich die Stufe am Ende des Fingers, wenn die Leiterbahn 42b aus dem aktiven Gebiet herausgeführt wird und auf den in Fig. 1B rechts gezeigten Feldoxidbereich 26 geführt werden muss. Auf dieses Feldoxid 26 kann allein schon aus Kapazitätsgründen nicht verzichtet werden.

[0013] An nicht-planaren Metallisierungsebenen und insbesondere an stromdurchflossenen Kanten bzw. Stufen derselben tritt eine erhöhte Elektromigration auf, wodurch die Stromtragfähigkeit begrenzt ist. Ein Vorteil der Verwendung nicht nicht-planaren Metallisierungsebenen besteht darin, dass durch ein Masseschild um das Gate eine deutlich bessere Abschirmwirkung erzielbar ist als bei ausschließlicher Verwendung von planaren Metallisierungsebenen.

**[0014]** Die US-A-5,094,965 beschreibt einen MOS-Feldeffekttransistor, der durch eine Feldabschirmung isoliert ist. Die Feldabschirmung umfasst ein Gate aus leitfähigen Schichten, die voneinander beabstandet auf einem Siliziumsubstrat gebildet sind. In Regionen, die durch die Feldabschirmung isoliert sind, sind MOS-Feldeffekttransistoren gebildet.

**[0015]** Die US-A-5,943,598 beschreibt eine integrierte Schaltung mit einem Halbleitersubstrat, die eine Mehrzahl von ersten Leiterstrukturen umfasst, die auf der Oberfläche des Substrats angeordnet sind und eine unebene Oberfläche auf dem Substrat bilden. Eine erste dielektrische Schicht ist auf der unebenen Oberfläche angeordnet. Zweite leitfähige Strukturen sind auf der ersten dielektrischen Schicht angeordnet, auf der wiederum eine zweite dielektrischen

sche Schicht abgeschieden ist. Eine dritte dielektrische Schicht ist auf der zweiten dielektrischen Schicht abgeschieden, auf der wiederum eine Metallschicht angeordnet ist.

[0016] Die US-A-5,521,418 beschreibt ein Halbleiterbauelement mit einer ersten leitfähigen Schicht, die auf einer Oberfläche eines Halbleitersubstrats gebildet ist. Eine isolierende Schicht ist oberhalb des Halbleitersubstrats gebildet, wobei die isolierende Schicht ein Kontaktloch aufweist, das zu der ersten leitfähigen Schicht führt, um diese frei zu legen. Eine zweite leitfähige Schicht ist auf der isolierenden Schicht angeordnet, sowie auf den Seitenwänden des Kontaktlochs und auf der ersten isolierenden Schicht. Eine Anti-Oxidationsschicht ist auf zumindest einem Teil der Oberfläche der zweiten leitfähigen Schicht gebildet.

**[0017]** Ausgehend von diesem Stand der Technik liegt der vorliegenden Erfindung die Aufgabe zugrunde, einen Feldeffekttransistor zu schaffen, der ein verbessertes Verhalten und verbesserte Eigenschaften aufweist.

**[0018]** Diese Aufgabe wird durch einen Feldeffekttransistor gemäß Anspruch 1 gelöst.

[0019] Die vorliegende Erfindung schafft einen Feldeffekttransistor, mit einem Substrat, einem Sourcebereich und einem Drainbereich, die in dem Substrat gebildet sind, einem Gate, einer ersten nicht-planaren Metallisierungsebene, die auf dem Substrat gebildet ist und einen ersten Abschnitt, der mit dem Sourcebereich verbunden ist, einen zweiten Abschnitt, der mit dem Drainbereich verbunden ist, und einen dritten Abschnitt, der das Gate zumindest teilweise überdeckt, umfasst, wobei der dritte Abschnitt von dem Gate isoliert ist, um das Gate gegenüber elektrostatischen oder elektrodynamischen Störungen abzuschirmen, und wobei der dritte Abschnitt eine dem Substrat abgewandte Oberfläche des Gates, eine sourceseitige Seitenwand des Gates und zumindest teilweise die drainseitige Seitenwand des Gates bedeckt, und einer zweiten, planaren Metallisierungsebene, die oberhalb des Substrats beabstandet von der ersten Metallisierungsebene angeordnet ist und über eine Durchkontaktierung mit dem ersten Abschnitt oder mit dem zweiten Abschnitt der ersten Metallisierungsebene verbunden ist.

**[0020]** Gemäß einem besonderen Aspekt der vorliegenden Erfindung wird ferner eine Verstärkerschaltung mit einem erfindungsgemäßen Feldeffekttransistor geschaffen.

**[0021]** Erfindungsgemäß werden die Vorteile der oben beschriebenen herkömmlichen Ansätze kombiniert, so dass erfindungsgemäße durch die Einführung der nicht-planaren Metallisierungsebene die

Rückwirkungskapazität und damit die Verstärkung des Transistors wesentlich verbessert wird. Von einer nicht-planaren Metallisierung aus gesehen verbessert der erfindungsgemäße Ansatz die Integrationsfähigkeit zu komplexen Schaltungen, beispielsweise für Linearisierungsschaltungen, wesentlich. Ferner ist es möglich, die parasitären Kapazitäten der Anschlussflächen/Pads weiter deutlich zu reduzieren. Zusätzlich wird die Stromtragfähigkeit der Leiterbahnen erhöht, da Elektromigrationseinbußen an Kanten vermieden werden. Der Kern der Erfindung ist somit die Kombination der nicht-planaren Metallisierungsebene mit planaren Metallisierungsebenen.

**[0022]** Nachfolgend werden bevorzugte Ausführungsbeispiele der vorliegenden Erfindung anhand der beiliegenden Figuren näher erläutert. Es zeigen:

**[0023]** Fig. 1A eine Darstellung eines Feldeffekttransistors mit planaren Metallisierungsebenen gemäß dem Stand der Technik;

**[0024]** Fig. 1B eine schematische Darstellung eines Feldeffekttransistors mit nicht-planaren Metallisierungsebenen gemäß dem Stand der Technik;

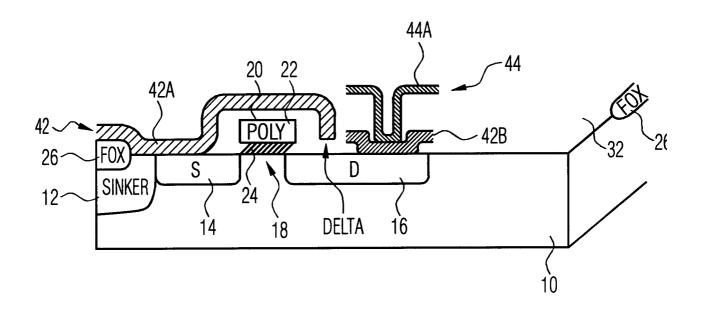

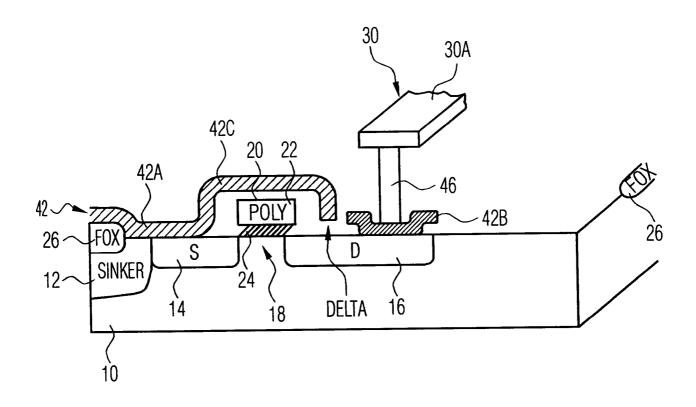

[0025] Fig. 2 eine Darstellung eines bevorzugten Ausführungsbeispiels der vorliegenden Erfindung;

**[0026]** Fig. 3 eine Darstellung eines Feldeffekttransistors gemäß einem weiteren Ausführungsbeispiel der vorliegenden Erfindung;

[0027] <u>Fig. 4</u> eine Ausschnittsvergrößerung der Darstellung aus <u>Fig. 3</u>; und

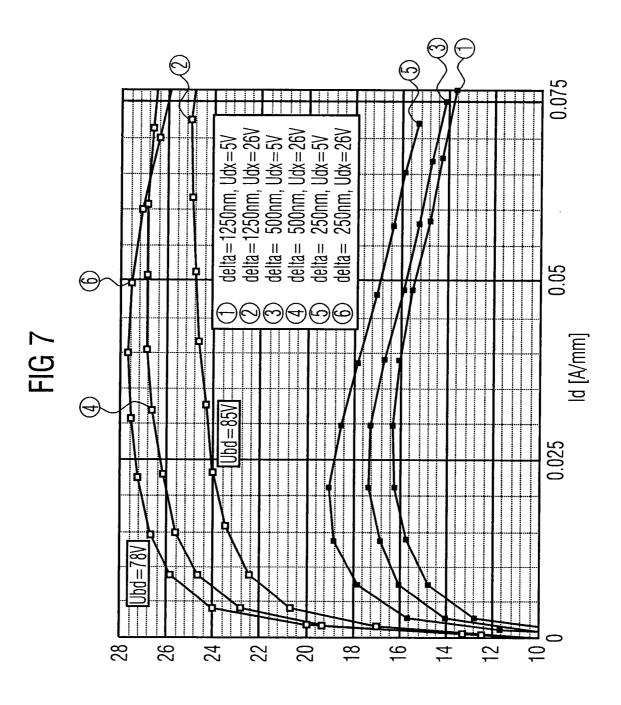

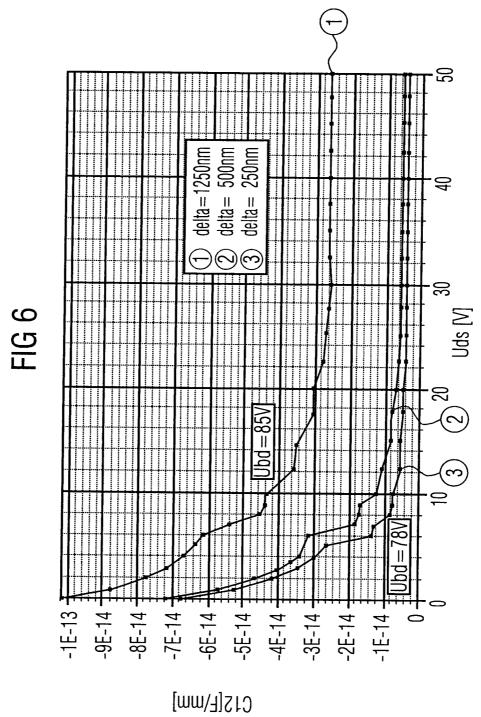

**[0028]** Fig. 5 bis Fig. 7 Graphen, welche die Verbesserungen des erfindungsgemäßen Ansatzes gegenüber herkömmlichen Ansätzen verdeutlichen.

**[0029]** Anhand der Fig. 2 wird nachfolgend ein bevorzugtes Ausführungsbeispiel näher beschrieben, wobei bei der nachfolgenden Erläuterung des erfindungsgemäßen Ansatzes in den Figuren diejenigen Elemente, welche bereits anhand der Fig. 1A und Fig. 1B beschrieben wurden, mit gleichen Bezugszeichen versehen sind.

[0030] Fig. 2 zeigt eine Feldeffekttransistorstruktur ähnlich zu Fig. 1A und Fig. 1B, welche in einem Substrat den Sinker oder Kontaktanschluss 12 aufweist. Ferner ist in dem Substrat der Sourcebereich 14 sowie der Drainbereich 16 gebildet, zwischen denen ein Kanalbereich 18 definiert ist. Oberhalb des Kanalbereichs 18 ist die Gatestruktur 20 bestehend aus dem Polysiliziumgute 22 und der Oxidschicht 24 angeordnet. Wie aus Fig. 2 zu erkennen ist, wird erfindungsgemäß der Ansatz gemäß Fig. 1A (planare Metallisierungsebenen) mit dem Ansatz gemäß Fig. 1B (nicht-planare Metallisierungsebenen) kombiniert.

Die erste Metallisierungsebene ist hier durch die nicht-planare Metallisierungsebene 42 mit den drei Abschnitten 42a, 42b und 42c gebildet, wobei, anders als im Stand der Technik, nun die zweite Metallisierungsebene durch die planare Metallisierungsebene 30 gebildet ist, welche, ähnlich wie in Fig. 1B eine Leiterbahn 30a aufweist. Die Leiterbahn 30a ist hier direkt mit dem nicht-planaren Abschnitt 42b der ersten Metallisierungsebene 42 über einen Kontakt 46 verbunden.

[0031] Erfindungsgemäß wird somit, wie aus Fig. 2 zu erkennen ist, die oben anhand der Fig. 1A und Fig. 1B beschriebenen Vorgehensweisen kombiniert. Die erste Metallisierungsebene ist nicht-planar, wodurch eine gute Abschirmung des Gates erreicht wird. Im Drainbereich wird diese Metallisierungsebene vor sich möglicherweise einstellenden Stufen aufgrund des Feldoxids 26 beendet, die Leiterbahn gemäß Abschnitt 42b wird also nicht so weit ausgebildet, dass sich diese stufenförmig über das Feldoxid 26 im rechten Bereich der Fig. 2 erstreckt. Über Vias (Stöpsel zwischen Metallebenen) wird die zweite Metallisierungsebene angeschlossen. Diese trägt den Strom aus dem Finger und ist planar.

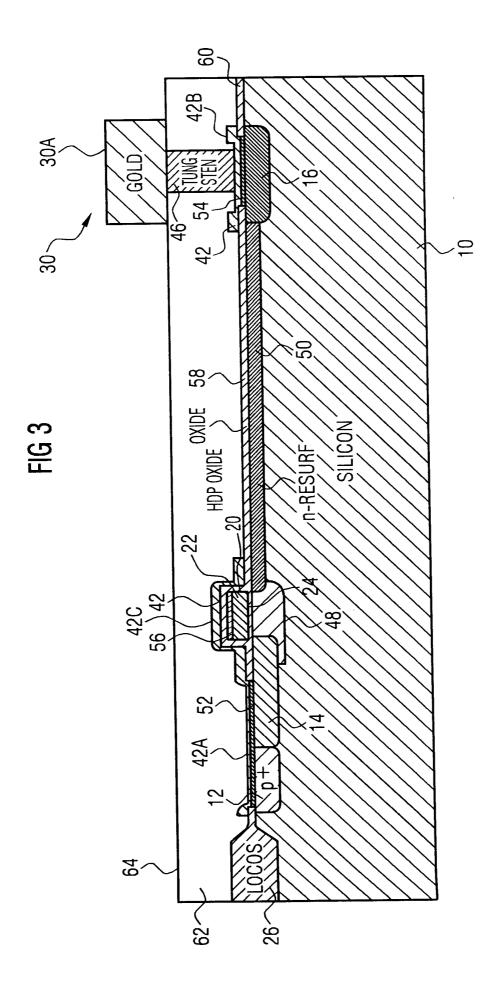

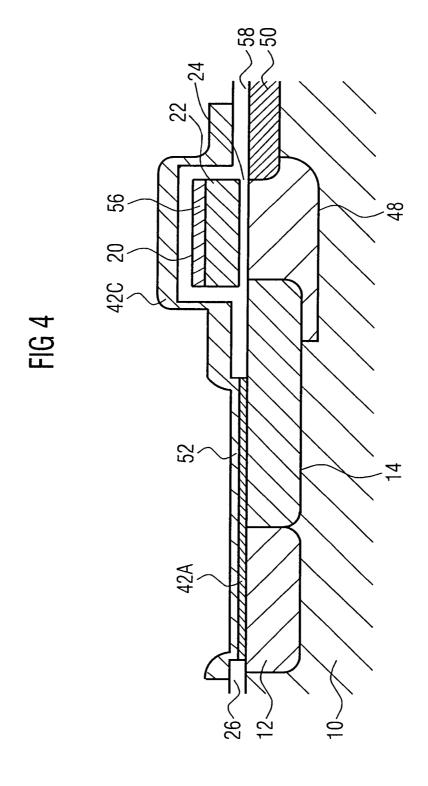

**[0032]** Anhand der Fig. 3 und Fig. 4 wird nachfolgend eine detaillierte Darstellung eines Feldeffektransistors gemäß einem bevorzugten Ausführungsbeispiel der vorliegenden Erfindung näher erläutert, wobei Fig. 4 eine vergrößerte Ausschnittdarstellung ist. Auch hier werden wiederum gleiche Bezugszeichen für gleiche Elemente verwendet.

**[0033]** Die <u>Fig. 3</u> und <u>Fig. 4</u> sind schematische Darstellungen eines vertikalen Schnitts durch einen Feldeffekttransistor gemäß einem bevorzugten Ausführungsbeispiel der vorliegenden Erfindung. Dabei ist <u>Fig. 4</u> eine vergrößerte Darstellung eines Ausschnitts aus <u>Fig. 3</u>.

[0034] Der Feldeffekttransistor gemäß diesem bevorzugten Ausführungsbeispiel umfasst das Substrat 10 (z.B. ein p-dotiertes Substrat), in dem der p+-dotierte Sinker- bzw. Substratkontakt 12, die n+-dotierte Source bzw. der n+-dotierter Sourcebereich 14, ein p-dotierter Body bzw. Body-Bereich 48, ein n-dotierter Resurf-Bereich 50 (Resurf = reduced surface field = reduziertes Oberflächenfeld) und die n+-dotierte Drain bzw. der n+-dotierter Drainbereich 16 angeordnet sind.

[0035] Eine Titansilizid-Schicht (TiSi-Schicht) 52 ist auf der Oberfläche des Substrats 10 so angeordnet, dass sie an die Source 14 und den Sinker 12 angrenzt und diese zumindest teilweise überdeckt. Da die TiSi-Schicht 52 eine hohe elektrische Leitfähigkeit aufweist und vorzugsweise jeweils eine möglichst große Fläche des Sinkers 12 und der Source 14 bedeckt, fließt ein Strom zwischen der n+-dotierten

Source und dem p+-dotierten Sinker über die Ti-Si-Schicht 52, die somit eine Silizid-Strombrücke darstellt. Eine weitere TiSi-Schicht 54 ist auf der Oberfläche des Substrats 10 so angeordnet, dass sie an die Drain 16 angrenzt. Das Gate 20 ist an der Oberfläche des Substrats 10 derart angeordnet, dass es dem Body-Bereich 48 gegenüber liegt und nur durch die dünne Oxidschicht 24, von diesem Bereich getrennt ist. Das Gate 20 ist ein Stapel aus der Polysiliziumschicht 22 und einer weiteren TiSi-Schicht 56, die eine geringere Dicke als die Polysiliziumschicht 22 aufweist und an einer von dem Substrat 10 abgewandten Seite der Polysiliziumschicht 22 angeordnet ist.

[0036] Abschnitte der Oberfläche des Substrats 10, die nicht von einer der TiSi-Schichten 52, 54 oder von dem Gate 20 bedeckt sind; sind mit der LO-COS-Schicht 26 (LOCOS = local oxidation of silicon = lokale Oxidation von Silizium) oder von Oxidschichten 58, 60 bedeckt. Dabei bedeckt die Oxidschicht 58 das Gate 20 bzw. alle Oberflächen desselben, wobei die Gateoxidschicht 24 hier durch einen Teil der Oxidschicht 58 zwischen dem Gate 20 und der Oberfläche des Substrats 10 gebildet ist.

[0037] Über den TiSi-Schichten 52, 54, der LO-COS-Schicht 26 und den Oxidschichten 58, 60 ist die erste, nicht-planare Metallisierungsebene 42 gebildet, die den ersten Abschnitt 42a, der an die Ti-Si-Schicht 52 über der Source 14 und dem Sinker 12 angrenzt, den zweiten Abschnitt 42b, der an die Ti-Si-Schicht 54 über der Drain 16 angrenzt und dieselbe elektrisch kontaktiert bzw. elektrisch leitfähig mit ihr verbunden ist, und den dritten Abschnitt 42c, der an den ersten Abschnitt 42a angrenzt und mit diesem vorzugsweise einstückig ausgebildet ist, umfasst. Der dritte Abschnitt 42c überdeckt das Gate 20 zumindest teilweise, wobei es von diesem durch die dazwischenliegende Oxidschicht 58 beabstandet und elektrisch isoliert ist. Die Abschnitte 42a, 42b und 42c der nicht-planaren Metallisierungsebene 42 werden vorzugsweise erzeugt, indem zunächst eine unstrukturierte Metallschicht ganzflächig über der LO-COS-Schicht 26, den TiSi-Schichten 52, 54 und den Oxidschichten 58, 60 erzeugt und dann durch einen Lift-off-Prozess oder mittels einer Photolackmaske und eines Ätzbades lateral strukturiert wird. Die erste Metallisierungsebene bzw. Schicht ist somit im wesentlichen an die Kontur der Substratoberfläche angepasst und somit nicht-planar.

[0038] Der Feldeffekttransistor umfasst ferner eine Oxidschicht 62 (HDP-Schicht), die auf der Struktur, wie sie sich nach dem Erzeugen der ersten Metallisierungsebene 42 ergibt, angeordnet ist. Die dem Substrat 10 abgewandte Oberfläche 64 der Oxidschicht 62 ist planarisiert. Auf der planarisierten Oberfläche 64 der Oxidschicht 62 ist die zweite, planare Metallisierungsebene 30 gebildet. Bei dem ge-

zeigten Ausführungsbeispiel umfasst diese Leiterbahnen **30a** zur Verdrahtung des Feldeffekttransistors und gegebenenfalls weiterer aktiver und passiver Bauelemente.

[0039] Die Leiterbahn 30a ist durch Wolframstopfen 46 in der Oxidschicht 62 elektrisch leitfähig mit dem zweiten Abschnitt 42b der ersten, nicht-planaren Metallisierungsebene 42 und damit mit der Drain 16 verbunden. Die Source 14 kann auf die gleiche Weise kontaktiert sein wie die Drain 16, indem sich ein Wolframstopfen von einem weiteren Abschnitt der zweiten, planaren Metallisierungsebene durch die Oxidschicht 62 zu dem ersten Abschnitt 42a der ersten, nicht-planaren Metallisierungsebene 42 erstreckt.

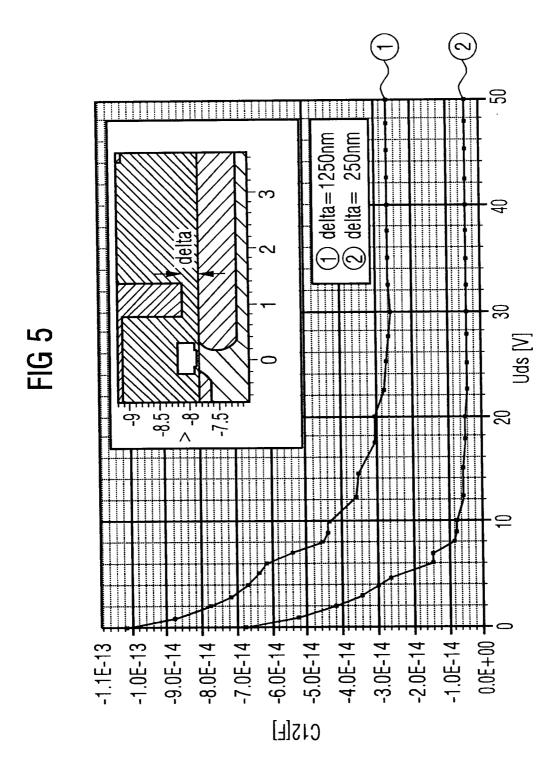

**[0040]** Anhand der <u>Fig. 5</u> bis <u>Fig. 7</u> wird nachfolgend anhand der dort dargestellten Graphen die Funktionalität und die Vorteile der erfindungsgemäßen Anordnung näher erläutert, unter anderem in Verbindung mit einem bekannten Ansatz.

[0041] In Fig. 5 ist die Rückwirkungskapazität C12 als Funktion der Drainspannung UDS aufgetragen. Das in Fig. 5 eingefügte, schematische Bild eines Ausschnitts der anhand der Fig. 2 bzw. der Fig. 3 beschriebenen Halbleiterstruktur zeigt das Bauelement mit einem Sourcebereich auf der linken Seite und einem Drainbereich auf der rechten Seite. Über das Gatepolysilizium 22 ist der dritte Abschnitt 42c als Abschirmung (Shield) gelegt und drainseitig nach unten gezogen, so dass dieser einen Abstand zu dem darunterliegenden Bereich hat, der ähnlich wie in Fig. 1B und Fig. 2 mit delta bezeichnet ist. Je nach dem, wie weit das Shield heruntergezogen wird, ergeben sich andere Rückwirkungskapazitäten. Bei einem Wert von delta = 1,25 µm (Kurve 1) beträgt die Rückwirkungskapazität der Zelle für Drainspannungen über 30 V etwa 26 fF. In diesem Fall wäre die Metallisierung drainseitig überhaupt nicht heruntergezogen worden und würde dem Fall einer ausschließlich planaren Metallisierung entsprechen, wie er anhand der Fig. 1A beschrieben wurde. Für einen Wert von delta = 250 nm (Kurve 2) ist das Shield 42c drainseitig wie in dem Fig. 5 gezeigten Bild oder ähnlich wie in Fig. 2 und Fig. 3 heruntergezogen, wobei hier von einer Gatepolysiliziumdicke von etwa 300 nm ausgegangen wird. Wie zu erkennen ist, wird bei hohen Trennspannungen eine Rückwirkungskapazität C12 von etwa 4 fF erreicht, und somit stellt sich aufgrund der erfindungsgemäßen Ausgestaltung eine deutliche Reduzierung der Rückwirkungskapazität ein.

[0042] In <u>Fig. 5</u> ist wiederum die Rückwirkungskapazität C12 gegen die Drainspannung UDS aufgetragen, wobei hier die in <u>Fig. 6</u> gezeigte Kurve 1 der Kurve 1 aus <u>Fig. 5</u> entspricht, und die Kurve 3 entspricht der Kurve 2 aus <u>Fig. 5</u>. Zusätzlich wurde eine weitere Kurve für einen Wert von delta = 500 nm (Kurve 3) eingefügt, woraus sich ergibt, dass auch für

Shieldanordnungen **42c**, welche nicht so weit hinuntergezogen sind wie anhand der <u>Fig. 5</u> beschrieben auch eine deutliche Reduzierung der Rückwirkungskapazität erreicht werden kann, verglichen mit einem planaren Metallisierungsansatz (siehe Kurve 1).

[0043] In Fig. 7 ist der maximal erreichbare Gewinn bei stabiler Anpassung (Maximum Stable Gain = MSG) als Funktion des Drainstroms für zwei Drainspannungen, 5 V und 26 V, aufgetragen. Wie aus Fig. 7 zu erkennen ist, nimmt das MSG mit abnehmendem delta jeweils zu, wobei durch das bessere Shielding (die bessere Abschirmung) der Gain um bis zu 3 dB ansteigt, was einen deutlichen Anstieg bedeutet. Bei den Kurven 2 und 6 wurde zusätzlich die Drain-Durchbruchsspannung angegeben, ähnlich wie bei den Kurven 1 und 3 in Fig. 6. Wie ferner zu erkennen ist, nimmt auch die Drain-Durchbruchsspannung leicht ab, dadurch, dass das Shield die Resurf-Strecke 50 des LDMOS elektrisch etwas verkürzt.

[0044] Die vorliegende Erfindung wurde oben anhand eines LDMOS-Feldeffekttransistors mit einem langen Resurf-Bereich 50 dargestellt. Die vorliegende Erfindung ist jedoch ebenso gut auf andere Feldeffekttransistor-Typen vorteilhaft anwendbar. Ferner setzt die vorliegende Erfindung nicht voraus, dass es sich, wie dargestellt, um einen n-Kanal-Feldeffekttransistor handelt, sondern ist ebenso gut mit einem p-Kanal-Feldeffekttransistor realisierbar. Auch die Materialien des Substrats 10 und damit der Source 14, der Drain 16, des Sinkers 20, des Body-Bereichs 48 und des Resurf-Bereichs 50 sowie des Gates 20 können ohne weiteres durch andere Materialien, beispielsweise Galliumarsenid (GaAs) ersetzt werden. Anstelle der LOCOS-Schicht 26 und der Oxidschichten 58, 60 sind Schichten aus anderen elektrisch isolierenden Materialien, beispielsweise Nitriden, verwendbar. Ebenso sind anstelle der TiSi-Schichten 52, 54, 56 andere Silizide oder andere zur Kontaktierung von dotierten Halbleiterbereichen geeignete elektrisch leitfähige Materialien verwendbar. Auch der Wolframstopfen 46 ist durch einen Stopfen bzw. Durchgangslochleiter aus einem anderen Material ersetzbar.

[0045] Bei dem in den Fig. 1 und Fig. 2 dargestellten bevorzugten Ausführungsbeispiel weist die LO-COS-Schicht 26 vorzugsweise eine Dicke von 330 nm auf. Die Oxidschicht 62 ist vorzugsweise ein HDP-Oxid (HDP = high density plasma = hochdichtes Plasma) mit einer Dicke von 2,5 μm bis 3 μm. Die lateral strukturierte Metallschicht weist vorzugsweise Titan Ti oder Titannitrid TiN oder Aluminium auf. Titan und Titannitrid weisen einen höheren spezifischen Widerstand auf, können jedoch ohne eine Barriere auf eine Siliziumoberfläche aufgebracht werden. Aluminium weist einen geringeren spezifischen Widerstand auf, zwischen Aluminium und einer Siliziumo-

berfläche ist jedoch eine Barriereschicht vorzusehen.

[0046] Obwohl die vorliegende Erfindung oben anhand eines bevorzugten Ausführungsbeispiels, welches einen Feldeffekttransistor umfasst, näher erläutert wurde, ist offensichtlich, dass der erfindungsgemäße Ansatz unter der Verwendung von zwei Metallisierungsebenen, von denen die eine planarisiert ist und die andere nicht-planarisiert ist, auch für andere Bauelemente mit aktiven Bereichen Anwendung finden kann, wie beispielsweise andere Feldeffekttransistorstrukturen, Bipolartransistorstrukturen, Diodenstrukturen und ähnliches.

#### **Patentansprüche**

Feldeffekttransistor, mit einem Substrat (10);

einem Sourcebereich (14) und einem Drainbereich (16), die in dem Substrat (10) gebildet sind; einem Gate (20);

einer ersten nicht-planaren Metallisierungsebene (42), die auf dem Substrat (10) gebildet ist und einen ersten Abschnitt (42a), der mit dem Sourcebereich (14) verbunden ist, einen zweiten Abschnitt (42b), der mit dem Drainbereich (16) verbunden ist, und einen dritten Abschnitt (42c), der das Gate (20) zumindest teilweise überdeckt, umfasst, wobei der dritte Abschnitt (42c) von dem Gate (20) isoliert ist, um das Gate (20) gegenüber elektrostatischen oder elektrodynamischen Störungen abzuschirmen, und wobei der dritte Abschnitt (42c) eine dem Substrat (10) abgewandte Oberfläche des Gates (20), eine sourceseitige Seitenwand des Gates (20) und zumindest teilweise die drainseitige Seitenwand des Gates (20) bedeckt; und

einer zweiten, planaren Metallisierungsebene (30), die oberhalb des Substrats (10) beabstandet von der ersten Metallisierungsebene (42) angeordnet ist und über eine Durchkontaktierung (46) mit dem ersten Abschnitt (42a) oder mit dem zweiten Abschnitt (42b) der ersten Metallisierungsebene (42) verbunden ist.

- 2. Feldeffekttransistor nach Anspruch 1, bei dem der erste Abschnitt (42a) und der dritte Abschnitt (42c) der ersten, nicht-planaren Metallisierungsebene (42) verbunden sind.

- 3. Feldeffekttransistor nach Anspruch 1 oder 2, bei dem zwischen der ersten, nicht-planaren Metallisierungsebene (42) und der zweiten, planaren Metallisierungsebene (30) eine isolierende Schicht (62) angeordnet ist, wobei in der isolierenden Schicht (62) zumindest eine Durchkontaktierung (46) für eine Verbindung der ersten, nicht-planaren Metallisierungsebene (42) mit der zweiten, planaren Metallisierungsebene (30) gebildet ist.

- 4. Feldeffekttransistor nach einem der Ansprüche 1 bis 3, bei dem der dritte Abschnitt (42c) der ersten

## DE 103 10 554 B4 2007.10.04

nicht-planaren Metallisierungsebene (42) derart über die drainseitige Seitenwand des Gates (20) gezogen ist, dass sich ein vorbestimmter Abstand (delta) zu dem darunterliegenden Drainbereich (16) einstellt, der kleiner ist als eine Dicke des Gates (20).

- 5. Feldeffekttransistor nach Anspruch 4, bei dem der Abstand einen Größe zwischen etwa 250 nm und etwa 500 nm hat.

- 6. Verstärkerschaltung mit einem Feldeffekttransistor gemäß einem der Ansprüche 1 bis 5.

Es folgen 8 Blatt Zeichnungen

### Anhängende Zeichnungen

FIG 1A

FIG 1B

FIG 2

. . . . . .