(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4959046号

(P4959046)

(45) 発行日 平成24年6月20日(2012.6.20)

(24) 登録日 平成24年3月30日(2012.3.30)

(51) Int.Cl.

F 1

G 11 C 11/4074 (2006.01)

G 11 C 11/403 (2006.01)G 11 C 11/34 354 F

G 11 C 11/34 363 M

請求項の数 2 (全 32 頁)

(21) 出願番号 特願2000-239598 (P2000-239598)

(22) 出願日 平成12年8月8日 (2000.8.8)

(65) 公開番号 特開2002-56673 (P2002-56673A)

(43) 公開日 平成14年2月22日 (2002.2.22)

審査請求日 平成19年6月29日 (2007.6.29)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配置された複数のメモリセルを有するメモリセルアレイと、

前記メモリセルの行に対応して設けられ、第1の制御信号の活性化に応答して、少なくとも1本が選択的に活性化される複数のワード線と、

前記メモリセルの列に対応して設けられ、活性化されたワード線に対応するメモリセルに保持されるデータが伝達される複数のビット線対と、

前記複数のビット線対にそれぞれ対応して設けられ、第2の制御信号の活性化に応答して、前記複数のビット線対のうちの対応する1つを構成するビット線間に生じる電位レベル差を増幅する複数のセンスアンプ回路と、

外部電源電位を内部電源電位に変換する電源回路とを備え、

前記電源回路は、

前記外部電源電位を供給する外部電源配線と、

少なくとも前記センスアンプに結合され、前記前記内部電源電位を供給する内部電源配線と、

前記内部電源電位と基準電位との電位レベル差を増幅して制御ノードに出力する電位差增幅回路と、

前記外部電源配線と前記内部電源配線との間に設けられ、前記制御ノードの電位レベルに応じた供給電流量を前記外部電源配線から前記内部電源配線に供給する電流供給回路と、

10

20

前記第1および第2の制御信号に応じて、前記電位レベル差にかかわらず前記外部電源配線から前記内部電源配線への電流供給を強制的に実行するための強制電流供給制御回路とを備え、

前記強制電流供給制御回路は、前記第1の制御信号の活性化に応答して定められる第1の時刻から、前記第2の制御信号の活性化に応答して定められる第2の時刻までの所定期間ににおいて、前記電流供給を強制的に実行し、

前記強制電流供給制御回路は、

前記所定期間ににおいて強制電流供給制御信号を活性化するための強制電流供給期間制御回路を含み、

前記半導体記憶装置は、1回のロウアクセス動作の対象となるメモリセルの個数が、通常動作時よりもリフレッシュ動作時において多く、 10

前記強制電流供給期間制御回路は、前記通常動作時において前記所定期間ににおける前記強制電流供給制御信号の活性化を中止し、前記リフレッシュ動作時において前記所定期間ににおける前記強制電流供給制御信号の活性化を実行する、半導体記憶装置。

#### 【請求項2】

行列状に配置された複数のメモリセルを有するメモリセルアレイと、

前記メモリセルの行に対応して設けられ、第1の制御信号の活性化に応答して、少なくとも1本が選択的に活性化される複数のワード線と、

前記メモリセルの列に対応して設けられ、活性化されたワード線に対応するメモリセルに保持されるデータが伝達される複数のビット線対と、 20

前記複数のビット線対にそれぞれ対応して設けられ、第2の制御信号の活性化に応答して、前記複数のビット線対のうちの対応する1つを構成するビット線間に生じる電位レベル差を増幅する複数のセンスアンプ回路と、

外部電源電位を内部電源電位に変換する電源回路とを備え、

前記電源回路は、

前記外部電源電位を供給する外部電源配線と、

少なくとも前記センスアンプに結合され、前記前記内部電源電位を供給する内部電源配線と、

前記内部電源電位と基準電位との電位レベル差を増幅して制御ノードに出力する電位差增幅回路と、 30

前記外部電源配線と前記内部電源配線との間に設けられ、前記制御ノードの電位レベルに応じた供給電流量を前記外部電源配線から前記内部電源配線に供給する電流供給回路と、

前記第1および第2の制御信号に応じて、前記電位レベル差にかかわらず前記外部電源配線から前記内部電源配線への電流供給を強制的に実行するための強制電流供給制御回路とを備え、

前記強制電流供給制御回路は、前記第1の制御信号の活性化に応答して定められる第1の時刻から、前記第2の制御信号の活性化に応答して定められる第2の時刻までの所定期間ににおいて、前記電流供給を強制的に実行し、

前記強制電流供給制御回路は、

前記所定期間ににおいて強制電流供給制御信号を活性化するための強制電流供給期間制御回路を含み、

前記半導体記憶装置は、1回のロウアクセス動作の対象となるメモリセルの個数が、通常動作時よりもリフレッシュ動作時において多く、

前記強制電流供給期間制御回路は、前記動作状態が前記通常動作であり、かつ、前記通常動作時において1回のロウアクセス動作の対象となるメモリセルの個数が所定数以下に設定されている場合において、前記所定期間ににおける前記強制電流供給制御信号の活性化を中止し、

前記強制電流供給期間制御回路は、前記リフレッシュ動作時、または、前記通常動作時において1回のロウアクセス動作の対象となるメモリセルの個数が前記所定数よりも多く 50

設定されている場合において、前記所定期間における前記強制電流供給制御信号の活性化を実行する、半導体記憶装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、外部電源電位を内部電源電位に変換して負荷に供給する電源回路を備えた半導体記憶装置の構成に関するものである。

【0002】

【従来の技術】

半導体記憶装置の大容量化の要請に伴う微細加工化の進展により、半導体装置内の内部回路の耐圧が低くなっている。このような状況に対応するために、半導体記憶装置は、たとえば5V、3.3Vといった外部電源電位を内部に備えられた電源回路（以下、内部電源回路とも称する）によって、適当な内部電源電位（たとえば2.5V、2.0V等）に降圧して使用している。このような内部電源回路は、電圧降下回路（VDC；Voltage Down Converter）とも称される。

10

【0003】

電源回路が発生する内部電源電位は、半導体記憶装置の内部回路群で使用されるため、内部電源電位が所定範囲を超えて低下した場合には、各内部回路が所定の応答速度に基づいて所定の動作を実行することができなくなるおそれがある。一方、内部電源電位が所定範囲を超えて上昇し過ぎると、消費電力の増大に加えて、高集積化が進み微細化されたトランジスタが破壊されてしまうおそれがある。したがって、電源回路は、内部電源電位の変動が仕様で決定される所定範囲内に収まるように、内部電源電位の電位レベルを安定的に制御する必要がある。

20

【0004】

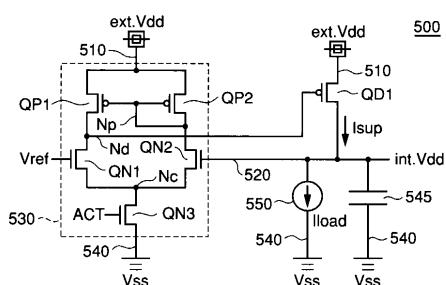

図25は、VDCの代表的な構成を有する従来の技術の内部電源回路500の構成を示す回路図である。

【0005】

内部電源回路500は、外部電源配線510より外部電源電位ext.Vddを受けて、負荷550に供給される内部電源電位int.Vddを基準電位Vrefに保持するための回路である。

30

【0006】

図25を参照して、内部電源回路500は、外部電源電位ext.Vddを供給する外部電源配線510と、内部電源電位int.Vddを供給する内部電源配線520と、内部電源電位int.Vddと基準電位Vrefとの電位差を増幅して出力する電位差增幅回路530と、電位差增幅回路530の出力に応じて、外部電源配線510から内部電源配線520に電流Isupを供給する電流供給トランジスタQD1と、内部電源配線520の電位レベル変動を抑制するための安定化容量545とを備える。負荷550は、内部電源配線520から内部電源電位int.Vddの供給を受けて、負荷電流Iloadを消費する。

40

【0007】

電位差增幅回路530は、外部電源配線510と接地配線540との間に結合されるカレントミラーアンプを構成する、P型MOSトランジスタQP1, QP2、およびN型MOSトランジスタQN1, QN2, QN3を含む。トランジスタQN1およびQN2のゲートには、基準電位Vrefおよび内部電源電位int.Vddがそれぞれ入力される。トランジスタQP1およびQP2のゲートはノードNpと結合される。トランジスタQN3は、制御信号ACTの活性化に応答して、カレントミラーアンプの動作電流を供給する。

【0008】

カレントミラーアンプを構成するトランジスタQP1, QP2, QN1, QN2, QN3の各々が飽和領域で動作するように設計することによって、電位差增幅回路530は、トランジスタQN1およびQN2のゲート電位差を差動増幅して、ノードNdの電位レベル

50

に反映する。

**【0009】**

内部電源電位  $i_{nt}.V_{dd}$  が基準電位  $V_{ref}$  よりも低下した場合には、ノード N d の電位レベルが接地電位 V ss 側にシフトし、これに応答して電流供給トランジスタ Q D 1 が外部電源配線 510 から内部電源配線 520 に電流を供給する。一方、内部電源電位  $i_{nt}.V_{dd}$  が基準電位  $V_{ref}$  よりも上昇した場合には、ノード N d の電位レベルは外部電源電位  $e_{xt}.V_{dd}$  側にシフトされるので、電流供給トランジスタ Q D 1 はオフされ、内部電源配線 520 に対する電流供給は停止される。これにより、内部電源回路 500 は、内部電源電位  $i_{nt}.V_{dd}$  の変動を補償して、基準電位  $V_{ref}$  レベルに保持しようとする。

10

**【0010】**

**【発明が解決しようとする課題】**

しかしながら、内部電源配線 520 から内部電源電位  $i_{nt}.V_{dd}$  の供給を受ける負荷 550 の消費する電流には、種々のパターンが存在する。

**【0011】**

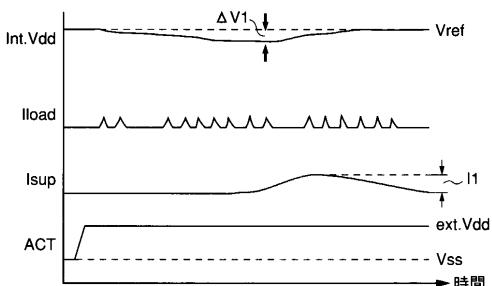

図 26 は、負荷 550 の電流消費パターンの一例に対応する内部電源回路の動作を示すタイミングチャートである。図 26 においては、連続的に少量の電流を消費する負荷の電流波形が示される。このような、電流消費パターンを有する負荷の代表例としては、DRAM (Dynamic Random Access Memory) における信号バッファ等の周辺回路が挙げられる。

20

**【0012】**

図 26 を参照して、制御信号 A C T が活性化されている期間中において内部電源回路は活性化される。負荷 550 の負荷電流  $I_{load}$  は、連続的に消費されるため、負荷電流の瞬時値  $I_1$  と平均値との間に大きな差が生じない。よって、内部電源電位  $i_{nt}.V_{dd}$  の電位レベルの低下  $V_1$  は、安定化容量 545 の作用によって比較的小さなレベルに抑えることができる。

**【0013】**

したがって、電流供給トランジスタ Q D 1 が電位差增幅回路 530 に制御されて内部電源配線 520 に供給する電流  $I_{sup}$  によって、内部電源配線 520 に生じる緩やかな電位レベルの低下に追従することができる。この結果、内部電源電位  $i_{nt}.V_{dd}$  は基準電位  $V_{ref}$  から大きく低下することはない。よって、内部電源電位の供給を受ける負荷である内部回路において誤動作等の問題は生じる可能性は低い。

30

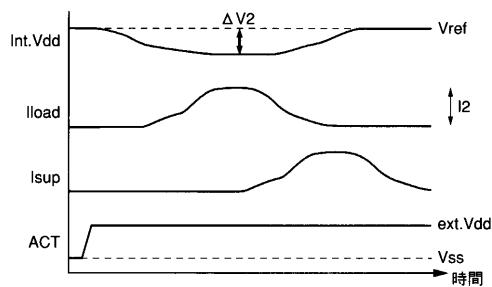

**【0014】**

図 27 は、負荷の電流消費パターンの他の一例に対応する内部電源回路の動作を示すタイミングチャートである。図 27 においては、断続的かつ振幅が大きい負荷電流  $I_{load}$  を消費する負荷の電流波形が示される。このような、電流消費パターンを有する負荷の代表例としては、DRAM におけるセンスアンプが挙げられる。

**【0015】**

図 27 の場合においても、制御信号 A C T が活性化されている期間中において内部電源回路は活性化される。しかしながら、断続的かつ大量の負荷電流においては、負荷電流の瞬時値  $I_2$  と平均値との間に大きな差が生じるので、電位差增幅回路 530 に制御される電流供給トランジスタ Q D 1 の供給電流  $I_{sup}$  によっては、内部電源電位  $i_{nt}.V_{dd}$  を十分保持することができない。この結果、内部電源電位の降下量  $V_2$  が大きくなってしまう。この降下量の低下が大きいと、内部電源電位の供給を受ける負荷である内部回路の動作に支障をきたす可能性も生じてしまう。

40

**【0016】**

このような急峻かつ振幅の大きい負荷電流に対して、安定化容量 545 によって内部電源電位  $i_{nt}.V_{dd}$  の電位レベルの低下を抑制しようとすると、大きな容量値が必要となり、チップの面積増加という問題が新たに生じてしまう。

**【0017】**

したがって、このような急峻な電流消費に対応して、安定化容量に大きく依存することな

50

く内部電源電位を安定的に維持するための技術として、電流消費タイミングに合致させて内部電源配線に強制的に電流を供給する内部電源回路が、たとえば特開平6-266452号公報等に開示されている。

#### 【0018】

このような技術を適用する内部電源回路においては、強制的な電流供給を実行するタイミングを、負荷における電流消費タイミングに応じて適切に調整することが重要となる。強制的な電流供給を開始するタイミングが負荷の電流消費開始よりも遅いと、内部電源電位の大きな低下を招いてしまう一方で、強制的な電流供給を停止させるタイミングが遅すぎると、内部電源配線520が過充電されて内部電源電位が上昇しすぎて、かえって不具合を生じてしまうおそれもあるからである。

10

#### 【0019】

この発明は、このような問題点を解決するためになされたものであって、この発明の目的は、急峻に電流を消費する負荷に対しても内部電源電位を安定的に維持できる内部電源回路および、それを備える半導体記憶装置の構成を提供することである。

#### 【0031】

##### 【課題を解決するための手段】

請求項1記載の半導体記憶装置は、行列状に配置された複数のメモリセルを有するメモリセルアレイと、メモリセルの行に対応して設けられ、第1の制御信号の活性化に応答して、少なくとも1本が選択的に活性化される複数のワード線と、メモリセルの列に対応して設けられ、活性化されたワード線に対応するメモリセルに保持されるデータが伝達される複数のビット線対と、複数のビット線対にそれぞれ対応して設けられ、第2の制御信号の活性化に応答して、複数のビット線対のうちの対応する1つを構成するビット線間に生じる電位レベル差を増幅する複数のセンスアンプ回路と、外部電源電位を内部電源電位に変換する電源回路とを備え、電源回路は、外部電源電位を供給する外部電源配線と、少なくともセンスアンプに結合され内部電源電位を供給する内部電源配線と、内部電源電位と基準電位との電位レベル差を増幅して制御ノードに出力する電位差増幅回路と、外部電源配線と内部電源配線との間に設けられ、制御ノードの電位レベルに応じた供給電流量を外部電源配線から内部電源配線に供給する電流供給回路と、第1および第2の制御信号に応じて、電位レベル差にかかわらず外部電源配線から内部電源配線への電流供給を強制的に実行するための強制電流供給制御回路とを備え、強制電流供給制御回路は、第1の制御信号の活性化に応答して定められる第1の時刻から、第2の制御信号の活性化に応答して定められる第2の時刻までの所定期間において、電流供給を強制的に実行する。さらに、強制電流供給制御回路は、所定期間において強制電流供給制御信号を活性化するための強制電流供給期間制御回路を含む。そして、半導体記憶装置は、1回のロウアクセス動作の対象となるメモリセルの個数が、通常動作時よりもリフレッシュ動作時において多く、強制電流供給期間制御回路は、通常動作時において強制期間における強制電流供給制御信号の活性化を中止し、リフレッシュ動作時において所定期間における強制電流供給制御信号の活性化を実行する。

20

#### 【0032】

請求項2記載の半導体記憶装置は、行列状に配置された複数のメモリセルを有するメモリセルアレイと、メモリセルの行に対応して設けられ、第1の制御信号の活性化に応答して、少なくとも1本が選択的に活性化される複数のワード線と、メモリセルの列に対応して設けられ、活性化されたワード線に対応するメモリセルに保持されるデータが伝達される複数のビット線対と、複数のビット線対にそれぞれ対応して設けられ、第2の制御信号の活性化に応答して、複数のビット線対のうちの対応する1つを構成するビット線間に生じる電位レベル差を増幅する複数のセンスアンプ回路と、外部電源電位を内部電源電位に変換する電源回路とを備え、電源回路は、外部電源電位を供給する外部電源配線と、少なくともセンスアンプに結合され内部電源電位を供給する内部電源配線と、内部電源電位と基準電位との電位レベル差を増幅して制御ノードに出力する電位差増幅回路と、外部電源配線と内部電源配線との間に設けられ、制御ノードの電位レベルに応じた供給電流量を外

30

40

50

部電源配線から内部電源配線に供給する電流供給回路と、第1および第2の制御信号に応じて、電位レベル差にかかわらず外部電源配線から内部電源配線への電流供給を強制的に実行するための強制電流供給制御回路とを備え、強制電流供給制御回路は、第1の制御信号の活性化に応答して定められる第1の時刻から、第2の制御信号の活性化に応答して定められる第2の時刻までの所定期間ににおいて、電流供給を強制的に実行する。さらに、強制電流供給制御回路は、所定期間ににおいて強制電流供給制御信号を活性化するための強制電流供給期間制御回路を含む。そして、1回のロウアクセス動作の対象となるメモリセルの個数が、通常動作時よりもリフレッシュ動作時において多く、強制電流供給期間制御回路は、動作状態が通常動作であり、かつ、通常動作時において1回のロウアクセス動作の対象となるメモリセルの個数が所定数以下に設定されている場合において、所定期間における強制電流供給制御信号の活性化を中止し、強制電流供給期間制御回路は、リフレッシュ動作時、または、通常動作時において1回のロウアクセス動作の対象となるメモリセルの個数が所定数よりも多く設定されている場合において、所定期間における強制電流供給制御信号の活性化を実行する。

**【0033】****【発明の実施の形態】**

以下において、本発明の実施の形態について図面を参照して詳細に説明する。なお図中ににおける同一符号は、同一または相当部分を示すものとする。

**【0034】****[実施の形態1]**

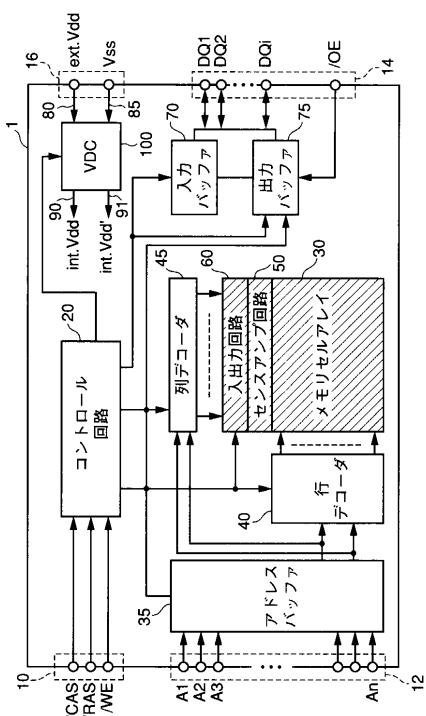

図1は、本発明の実施の形態1に従う内部電源回路を備えた半導体記憶装置1の全体構成を示す概略ブロック図である。

**【0035】**

図1を参照して、半導体記憶装置1は、コラムアドレスストローブ信号/CAS、ロウアドレスストローブ信号/RASおよびライトイネーブル信号/WEを受ける制御信号入力端子10と、アドレス信号A1～An(n:自然数)を受けるアドレス入力端子12と、入出力データDQ1～DQi(i:自然数)およびアウトプットイネーブル信号/OEとを授受するデータ入出力端子14と、外部電源電位ext.Vddおよび接地電位Vssの入力を受ける電源入力端子16とを備える。

**【0036】**

半導体記憶装置1は、さらに、制御信号入力端子10に入力された制御信号に応じて半導体記憶装置1の全体動作を制御するコントロール回路20と、行列状に配置された複数のメモリセルを有するメモリセルアレイ30と、メモリセルアレイ中のアドレス信号に応答したメモリセルを特定するためのアドレスバッファ35、行デコーダ40および列デコーダ45をさらに備える。

**【0037】**

メモリセルアレイ30には、ワード線がメモリセルの各行ごとに配置され、ビット線対がメモリセルの各列ごとに配置される。各メモリセルは、ワード線とビット線との交点のそれぞれに配置される。

**【0038】**

アドレスバッファ35は、外部から供給されたアドレス信号を行デコーダおよび列デコーダに選択的に供給する。行デコーダ40は、アドレスバッファ35から供給される行アドレス信号に応答して、複数のワード線のうちの少なくとも1つを選択的に駆動する。列デコーダ45は、アドレスバッファから供給される列アドレス信号に応答して、複数のビット線対のうちの1つを選択する。センスアンプ回路50は、各ビット線対に対応して設けられる複数のセンスアンプを含む。各センスアンプは、対応するビット線対間に生じる電位差を増幅する。

**【0039】**

入出力回路60は、列デコーダによって選択されたビット線対の電位レベルを出力バッファ75に供給する。出力バッファ75は、供給された電位レベルを増幅して出力データD

10

20

30

40

50

Q<sub>1</sub> ~ DQ<sub>i</sub> として外部に出力する。入力バッファ70は、外部から書込データが供給された場合に、入力データDQ<sub>1</sub> ~ DQ<sub>i</sub>を増幅する。入出力回路60は、入力バッファ70によって増幅された入力データを列デコーダ45によって選択されたビット線対に供給する。

#### 【0040】

制御信号入力端子10に入力された/CAS, /RASおよび/WEは、コントロール回路20に与えられ、コントロール回路20は、半導体記憶装置1全体の読出動作および書込動作における各回路のタイミング動作を決定する。

#### 【0041】

半導体記憶装置1は、さらに、電源入力端子16に入力された外部電源電位ext.Vddおよび接地電位Vssに基づいて、内部電源電位int.Vddを出力する内部電源回路100を備える。半導体記憶装置1内部において、外部電源電位ext.Vddおよび接地電位Vssは、外部電源配線80および接地配線85によって供給される。

#### 【0042】

一般的にメモリセルアレイ30、センスアンプ回路50および入出力回路60を除く他の周辺回路で消費される負荷電流は、図26に示したような連続的かつ小振幅なものとなる。一方、図中に斜線で示した、メモリセルアレイ30、センスアンプ回路50および入出力回路60（以下、これらを合わせて「メモリアレイ」とも称する）で消費される負荷電流は、メモリアクセスに応答したセンスアンプ回路50によるデータ増幅動作の実行時に、図27に示したような断続的かつ大振幅なものとなる。

#### 【0043】

したがって、周辺回路用電源と、メモリアレイ用電源とは独立に設けられることが多い。本発明の実施の形態においても、周辺回路用とメモリアレイ用とに独立のVDCおよび内部電源配線が配置されるものとする。

#### 【0044】

本発明の実施の形態においては、内部電源回路100のうち、特にメモリアレイ用電源に対応する部分について説明する。メモリアレイに対する内部電源電位int.Vddの供給は、内部電源配線90によって行なわれる。

#### 【0045】

一方、周辺回路に対する内部電源電位int.Vdd'の供給は、内部電源配線91によって行なわれる。周辺回路回路に供給される内部電源電位を生成するVDC（内部電源回路）については詳細に説明しないが、その電流消費パターンから、たとえば図25に示した従来の一般的な構成のVDC（内部電源回路）を適用することができる。

#### 【0046】

なお、図1においては、半導体記憶装置1を非同期型のDRAMとして表記しているが、半導体記憶装置1は、同期型のSDRAM（Synchronous DRAM）であってもよい。この場合には、コントロール回路20に対して、クロック信号CLK、クロックイネーブル信号CLEおよびチップセレクト信号/CS等がさらに入力され、半導体記憶装置1は、クロック信号CLKに同期して動作する。

#### 【0047】

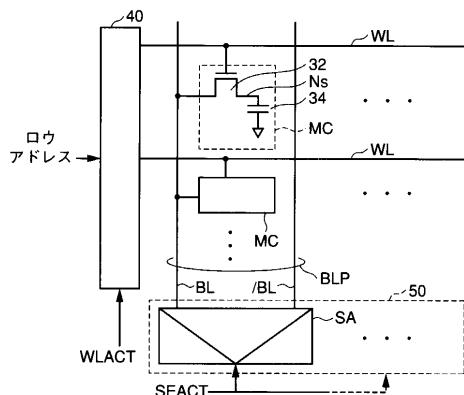

図2は、メモリセルアレイ30およびセンスアンプ回路50の構成を説明するブロック図である。

#### 【0048】

図2を参照して、メモリセルアレイ30は、行列状に配列された複数のメモリセルMCを有する。メモリセルMCは、アクセストランジスタ32およびデータ保持キャッシュ34を含む。アクセストランジスタ32は、各メモリセル列ごとに配置されるビット線対の一方であるビット線BLとデータ記憶ノードNsとの間に電気的に結合される。アクセストランジスタ32のゲートは、メモリセルの各行ごとに設けられるワード線WLと結合される。

#### 【0049】

10

20

30

40

50

デコード回路 40 は、ワード線活性化信号 W L A C T の活性化に応答して、行アドレス信号に対応したワード線 W L を活性化する。活性状態のワード線と対応するメモリセルの各々において、ビット線 B L とデータ記憶ノード N s とが結合されて、メモリセルに対するデータ読出・書込が実行される。非活性状態のワード線と対応するメモリセルの各々においては、データ記憶ノード N s に伝達された電荷が、データ保持キャパシタ 34 によって保持される。

#### 【 0 0 5 0 】

ビット線 B L P の他方のビット線 / B L は、ビット線 B L と相補のデータを伝達するため 10 に設けられる。センスアンプ回路 50 は、各ビット線対 B L P ごとに配置されるセンスアンプ S A を有する。

#### 【 0 0 5 1 】

センスアンプ S A は、センスアンプ活性化信号 S E A C T の活性化に応答して、対応するビット線対 B L P を形成する、ビット線 B L および / B L の間に生じる電位差を増幅する。

#### 【 0 0 5 2 】

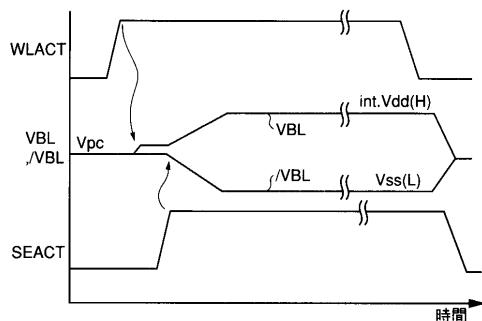

図 3 は、メモリアクセス時におけるワード線およびセンスアンプの活性化に伴う動作を説明するタイミングチャートである。

#### 【 0 0 5 3 】

図 3 を参照して、ワード線活性化信号 W L A C T の活性化 ( H レベル ) に応答して、行デコード 40 は、行アドレス信号に対応するワード線 W L を選択的に活性化する。ワード線 W L が活性化されると、対応するメモリセル行に属する各メモリセル M C において、アクセストランジスタ 32 がオンすることによってビット線 B L とデータ記憶ノード N s とが接続される。これにより、ビット線 B L の電位は、プリチャージレベル V p c から、データ記憶ノード N s に保持されるデータレベルに応じて上昇あるいは下降する。 20

#### 【 0 0 5 4 】

図 3 においては、データ記憶ノード N s に H レベルデータが保持されている場合を示している。この場合においては、アクセストランジスタ 32 のオンに応じて、ビット線 B L の電位 V B L がわずかに上昇する。一方、相補のビット線 / B L の電位レベルは変化しない。この状態で、センスアンプ活性化信号 S E A C T が活性化されると、センスアンプ S E は、ビット線対間に生じる電位レベル差の増幅を実行する。 30

#### 【 0 0 5 5 】

したがって、図 3 の場合においてはビット線 B L の電位 V B L は、データの H レベルに相当する内部電源電位 i n t . V d d に上昇する。一方、相補のビット線 / B L の電位 / V B L は、データの L レベルに対応する接地電位 V s s レベルに下降する。このようにして、ワード線 W L の活性化に応答して、各メモリセル M C に記憶されたデータの増幅動作が実行される。

#### 【 0 0 5 6 】

半導体記憶装置においては、1 回の行選択動作にあたって、同一のワード線に接続されるすべてのメモリセルのデータをビット線対に読出す構成となるため、同時に多数のセンスアンプが動作する。よって、センスアンプ回路の動作時には、短時間に大量の電流が消費されて、内部電源電位 i n t . V d d の電位レベルが一時的に低下する。この現象は、ビット線対 B L P に生じた微小な電位レベル差の速やかな増幅を妨げ、動作速度の低下を招くおそれがある。 40

#### 【 0 0 5 7 】

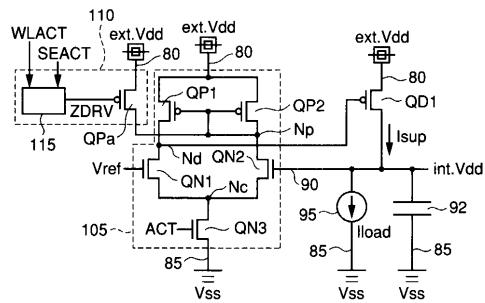

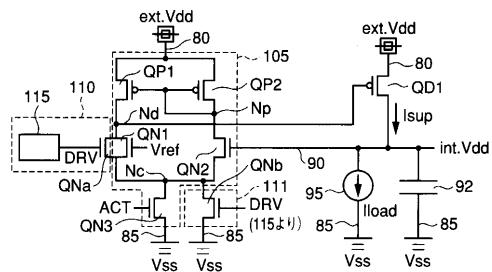

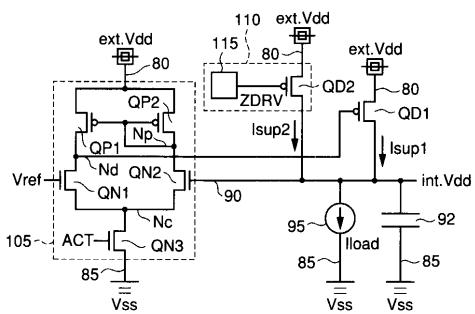

図 4 は、実施の形態 1 に従う内部電源回路 100 の構成を示す回路図である。

図 4 を参照して、内部電源回路 100 は、外部電源電位 e x t . V d d を供給する外部電源配線 80 と、内部電源電位 i n t . V d d を供給する内部電源配線 90 と、外部電源配線 80 および接地配線 85 の間に結合されて、内部電源電位 i n t . V d d と基準電位 V r e f との電位差を増幅して出力する電位差增幅回路 105 と、電位差增幅回路 105 の出力に応じて外部電源配線 80 から内部電源配線 90 に電流 I s u p を供給する電流供給

トランジスタ Q D 1 と、内部電源配線 9 0 の電位レベル変動を抑制するための安定化容量 9 2 とを備える。負荷 9 5 は、内部電源配線 9 0 から内部電源電位  $i_{n t} . V_{d d}$  の供給を受けて、負荷電流  $I_{l o a d}$  を消費する。負荷 9 5 は、たとえば図 1 で示したセンスアンプ回路 5 0 に相当する。

#### 【 0 0 5 8 】

内部電源回路のうちの上述した構成は、図 2 5 に示した従来の技術の V D C の構成と同様である。

#### 【 0 0 5 9 】

電位差増幅回路 1 0 5 は、図 2 5 で説明した電位差増幅回路 5 3 0 と同様の構成を有する。

したがって、電位差増幅回路 1 0 5 においては、トランジスタ Q N 3 によって供給される動作電流は、トランジスタ Q N 1 および Q N 2 のゲート電位差に応じて、ノード N d を流れる電流とノード N p を流れる電流とに分割される。この結果、ノード N d には、トランジスタ Q N 1 および Q N 2 のゲート電位差が増幅されて現われる。ノード N d は電流供給トランジスタ Q D 1 のゲートと結合される。

10

#### 【 0 0 6 0 】

したがって、電流供給トランジスタ Q D 1 は、内部電源配線 9 0 の電位レベル  $i_{n t} . V_{d d}$  が基準電位  $V_{r e f}$  よりも低い場合には、外部電源配線 8 0 から内部電源配線 9 0 に電流を供給する。一方、内部電源電位  $i_{n t} . V_{d d}$  が基準電位  $V_{r e f}$  よりも高い場合においては、電流供給トランジスタ Q D 1 はオフされて、外部電源配線 8 0 から内部電源配線 9 0 に対する電流供給は停止される。

20

#### 【 0 0 6 1 】

内部電源回路 1 0 0 は、所定期間において、内部電源電位  $i_{n t} . V_{d d}$  と基準電位  $V_{r e f}$ との電位差にかかわらず、外部電源配線 8 0 から内部電源配線 9 0 への電流供給を強制的に実行するための強制電流供給制御回路 1 1 0 をさらに備える。

#### 【 0 0 6 2 】

強制電流供給制御回路 1 1 0 は、内部電源配線 9 0 に対する強制的な電流供給期間を制御するための内部電源制御回路 1 1 5 と、外部電源配線 8 0 とノード N p との間に結合されて、内部電源制御回路 1 1 5 が生成する強制電流供給制御信号 Z D R V をゲートに受ける P 型 M O S トランジスタ Q P a とを含む。

#### 【 0 0 6 3 】

内部電源制御回路 1 1 5 は、負荷 9 5 の電流消費タイミングに応じて、強制電流供給制御信号 Z D R V を L レベル（接地電位  $V_{s s}$ ）に活性化する。強制電流供給制御信号 Z D R V の活性化に応答して、トランジスタ Q P a は、外部電源配線 8 0 からノード N p へ電流を供給する。これに応じて、ノード N p の電位レベルが上昇し、ノード N p と動作電流を分け合うノード N d の電位レベルが下降する。この結果、電流供給トランジスタ Q D 1 による供給電流  $I_{s u p}$  が増加する。

30

#### 【 0 0 6 4 】

したがって、内部電源回路 1 0 0 においては、内部電源電位  $i_{n t} . V_{d d}$  にかかわらず、強制電流供給制御信号 Z D R V の活性化に応答して、内部電源配線 9 0 に強制的に電流供給を行なうことができる。

40

#### 【 0 0 6 5 】

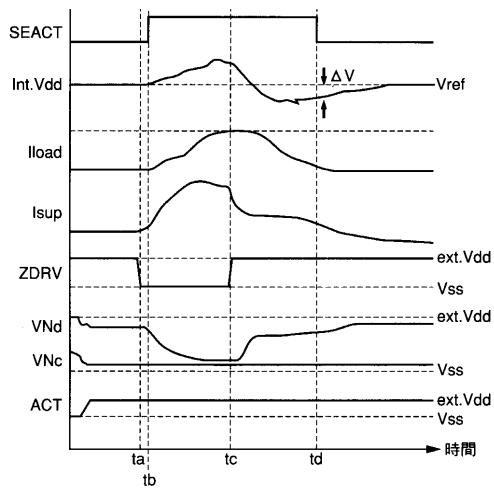

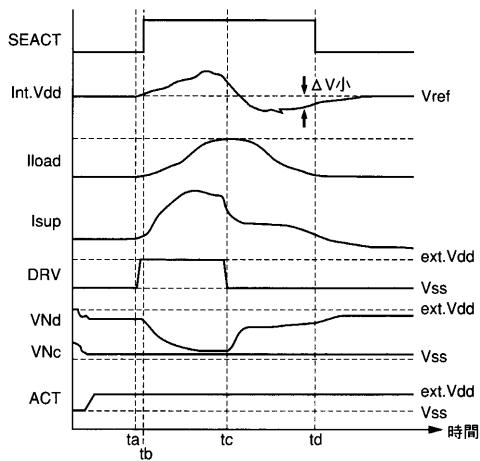

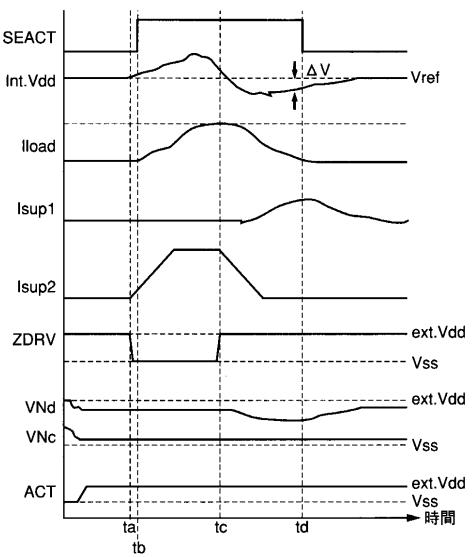

図 5 は、内部電源回路 1 0 0 の動作を説明するタイミングチャートである。

図 5 を参照して、制御信号 A C T の活性化に応じて、ノード N c の電位レベル  $V_{N c}$  が接地電位  $V_{s s}$  近くまで低下して、電位差増幅回路 1 0 5 の動作電流が供給される。これに応じて、内部電源回路 1 0 0 は、内部電源電位  $i_{n t} . V_{c c}$  と基準電位  $V_{r e f}$  の比較結果に基づいて、電流供給トランジスタ Q D 1 によって供給される電流量  $I_{s u p}$  を制御する。

#### 【 0 0 6 6 】

次に、負荷（たとえばセンスアンプ S A）における電流消費が開始されるタイミングよりも早い時刻  $t_a$  において、強制電流供給制御信号 Z D R V が L レベル（接地電位  $V_{s s}$ ）

50

に活性化される。これに応答してノードN<sub>p</sub>に強制的に電流が供給されることから、反対にノードN<sub>d</sub>の電位レベルV<sub>Nd</sub>は低下し始める。これに応じて、電流供給トランジスタQD1のゲート電位が低下し、外部電源配線80から内部電源配線90に対する強制的な電流供給が実行される。

#### 【0067】

時刻t<sub>b</sub>において、制御信号（たとえばセンスアンプ活性化信号S E A C T）の活性化に応答して、負荷電流I<sub>l o a d</sub>の消費が開始される。しかし、予め内部電源配線90に強制的に過剰供給された供給電流I<sub>s u p</sub>の影響によって、安定化容量92の容量値に大きく依存することなく、内部電源電位i<sub>n t . V d d</sub>の低下を防止できる。

#### 【0068】

時刻t<sub>c</sub>において、負荷における電流消費が終了するよりも前に、強制電流供給制御信号Z D R VがHレベル（外部電源電位e x t . V d d）に非活性化される。さらに、時刻t<sub>d</sub>において、制御信号（たとえばセンスアンプ活性化信号S E A C T）が非活性化されると、負荷における電流消費動作は完全に終了する。なお、負荷がセンスアンプである場合には、制御信号S E A C T活性化後の比較的初期の期間に消費電流I<sub>l o a d</sub>のピークが生じ、以降の消費電流は小さい。強制電流供給制御信号Z D R Vを非活性化するタイミングは、このような負荷の消費電流波形のパターンを考慮して設定すればよい。

10

#### 【0069】

時刻t<sub>c</sub>以後においては、ノードN<sub>p</sub>に対する強制的な電流供給は停止されるので、電流供給トランジスタQD1によって供給される電流量I<sub>s u p</sub>は、時刻t<sub>a</sub>以前と同様に、内部電源電位i<sub>n t . V c c</sub>と基準電位V<sub>r e f</sub>との電位レベルの比較結果に基づいて制御される。このように、負荷による電流消費が終了するより前に、内部電源配線90に対する強制的な電流供給を停止することによって、内部電源配線が過充電されて、内部電源電位i<sub>n t . V d d</sub>のが上昇しすぎることを防止できる。

20

#### 【0070】

このように、内部電源回路100においては、内部電源配線90に対する強制的な電流供給の実行タイミングを制御する強制電流供給制御信号Z D R Vの活性化期間の設定が非常に重要なものとなる。

#### 【0071】

次に、強制電流供給制御信号Z D R Vの活性化タイミングについて詳細に説明する。

30

#### 【0072】

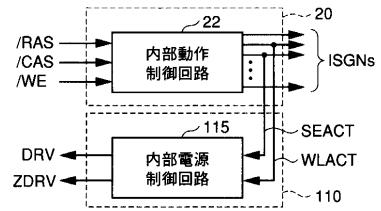

図6は、内部電源制御回路115の入出力関係を示すブロック図である。

図6を参照して、コントロール回路20は、半導体記憶装置1内の各内部回路の動作タイミングを制御するための内部動作制御回路22を含む。内部動作制御回路22は、制御信号入力端子10に入力される制御信号/C A S、/R A Sおよび/W Eに応答して、データの読み出し・書き込み動作等を実行するための制御信号群I S G N sを生成し、各内部回路に供給する。これらの制御信号群には、図3で説明したセンスアンプ動作に関連するワード線活性化信号W L A C Tおよびセンスアンプ活性化信号S E A C Tが含まれる。

#### 【0073】

強制電流供給制御回路110に含まれる内部電源制御回路115は、ワード線活性化信号W L A C Tおよびセンスアンプ活性化信号S E A C Tを受けて、内部電源回路100を制御するための強制電流供給制御信号D R VおよびZ D R Vを生成する。強制電流供給制御信号D R VおよびZ D R Vは、内部電源配線に対する強制的な電流供給を実行する期間において、Hレベル（外部電源電位e x t . V d d）およびLレベル（接地電位V<sub>s s</sub>）にそれぞれ活性化される。

40

#### 【0074】

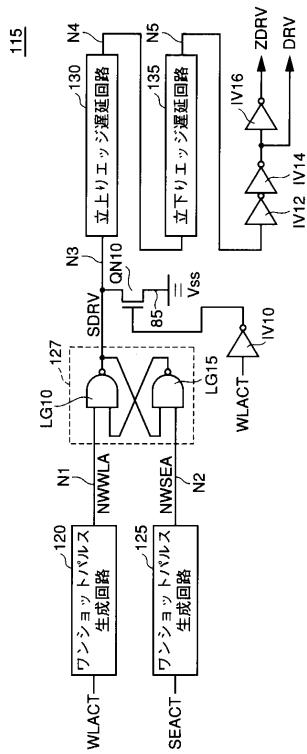

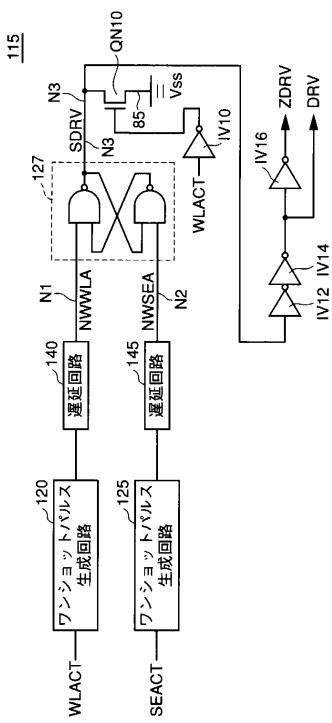

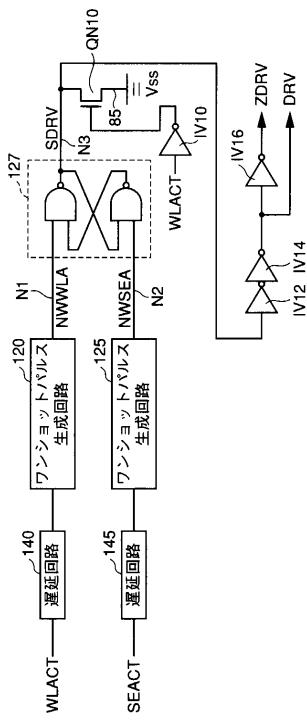

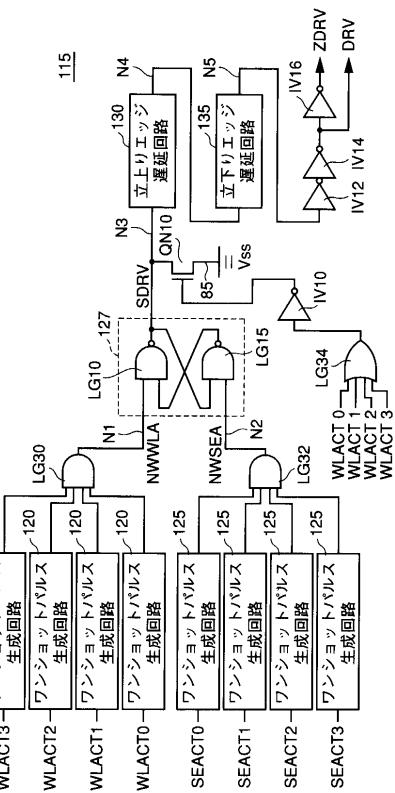

図7は、内部電源制御回路115の構成を示すブロック図である。

図7を参照して、内部電源制御回路115は、ワード線活性化信号W L A C Tの活性化に応答してLレベルに活性化されるワンショットパルス信号N W W L AをノードN1に出力するワンショットパルス回路120と、センスアンプ活性化信号S E A C Tの活性化に応

50

答して L レベルに活性化されるワンショットパルス信号 N W S E A をノード N 2 に生成するワンショットパルス発生回路 1 2 5 と、ワンショットパルス信号 N W W L A および N W S E A をそれぞれセット入力およびリセット入力として動作するフリップフロップ 1 2 7 を形成する論理ゲート L G 1 0 および L G 1 5 とを含む。

#### 【 0 0 7 5 】

ワンショットパルス N W W L A および N W S E A は、新たにワード線活性化信号 W L A C T および S E A C T が活性化された場合に、対応してワンショット状に活性化される。フリップフロップ 1 2 7 は、制御信号 S D R V をノード N 3 に生成する。制御信号 S D R V は、ワンショットパルス N W W L A の活性化（L レベル）、すなわちワード線活性化信号 W L A C T の活性化ごとに、H レベルに活性化される。一方、制御信号 S D R V は、ワンショットパルス信号 N W S E A の活性化（L レベル）、すなわちセンスアンプ活性化信号 S E A C T の活性化ごとに、リセットされて L レベルに非活性化される。10

#### 【 0 0 7 6 】

内部電源制御回路 1 1 5 は、さらに、ノード N 3 および N 4 の間に接続される立上がりエッジ遅延回路 1 3 0 と、ノード N 4 および N 5 の間に接続される立下がりエッジ遅延回路 1 3 5 とを含む。立上がりエッジ遅延回路 1 3 0 は、制御信号 S D R V の立上がりエッジ（L レベル → H レベル遷移）を遅延して伝達する。同様に、立下がりエッジ遅延回路 1 3 5 は、制御信号 S D R V の立下がりエッジ（H レベル → L レベル遷移）を遅延して伝達する。

#### 【 0 0 7 7 】

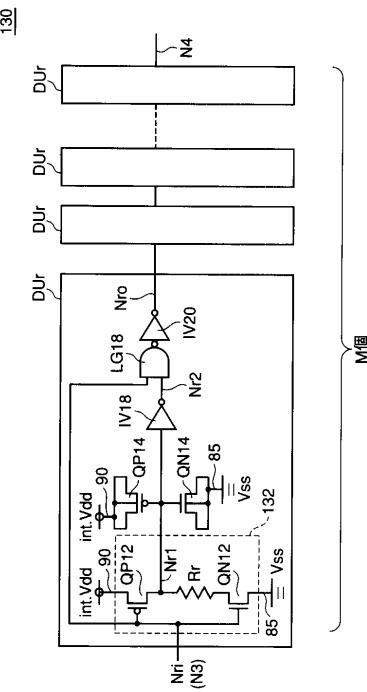

図 8 は、立上がりエッジ遅延回路 1 3 0 の構成を示す回路図である。20

図 8 を参照して、立上がりエッジ遅延回路 1 3 0 は、直列に接続された M 個（M：自然数）の遅延ユニット D U r を有する。各遅延ユニット D U r は、入力ノード N r i に入力された信号の立上がりエッジを遅延させて出力ノード N r o に伝達する。初段の各遅延ユニット D U r の入力ノード N r i は、ノード N 3 と結合される。最終段の各遅延ユニット D U r の出力ノード N r o は、ノード N 4 と結合される。

#### 【 0 0 7 8 】

遅延ユニット D U r は、入力ノード N r i の信号レベルをノード N r 1 に反転して伝達するインバータ 1 3 2 を形成する、P 型 MOS トランジスタ Q P 1 2 、N 型 MOS トランジスタ Q N 1 2 および遅延抵抗 R r と、ノード N r 1 に付加される遅延容量を形成する P 型 MOS トランジスタ Q P 1 4 および N 型 MOS トランジスタ Q N 1 4 とを有する。30

#### 【 0 0 7 9 】

遅延ユニット D U r は、さらに、ノード N r 1 の信号レベルを反転してノード N r 2 に伝達するインバータ I V 1 8 と、ノード N r i および N r 2 の N A N D 論理演算結果を出力する論理ゲート L G 1 8 と、論理ゲート L G 1 8 の出力を反転して出力ノード N r o に伝達するインバータ I V 2 0 とを有する。

#### 【 0 0 8 0 】

入力ノード N r i の信号レベルが L レベルから H レベルに立上がる場合において、遅延ユニット D U r の出力ノード N r o の信号レベルが L レベルから H レベルに変化するには、入力ノード N r i およびノード N r 2 の両方の信号レベルが H レベルに遷移する必要がある。ここで、ノード N r 2 の電位の H レベルへの遷移は、遅延抵抗 R r および遅延容量として作用するトランジスタ Q P 1 2 , Q N 1 2 の影響を受ける。40

#### 【 0 0 8 1 】

一方、入力ノード N r i の信号レベルが H レベルから L レベルに立下がる場合においては、入力ノード N r i およびノード N r 2 のいずれか一方の信号レベルが L レベルに遷移すれば、出力ノード N r o の信号レベルは、L レベルに変化する。

#### 【 0 0 8 2 】

したがって、遅延ユニット D U r は、入力ノード N r i に対して、伝達信号の立下りエッジを遅延させずに伝達し、立上がりエッジのみを抵抗素子 R 1 および遅延容量として作用するトランジスタ Q P 1 2 および Q N 1 2 によって生じる遅延時間だけ遅延して伝達する50

。

### 【0083】

よって、遅延抵抗および遅延容量の抵抗値および容量値、ならびに遅延ユニットの個数Mを制御することによって、制御信号S D R Vの立上がりエッジに対する遅延時間T rを設定することができる。

### 【0084】

図9は、立下がりエッジ遅延回路135の構成を示す回路図である。

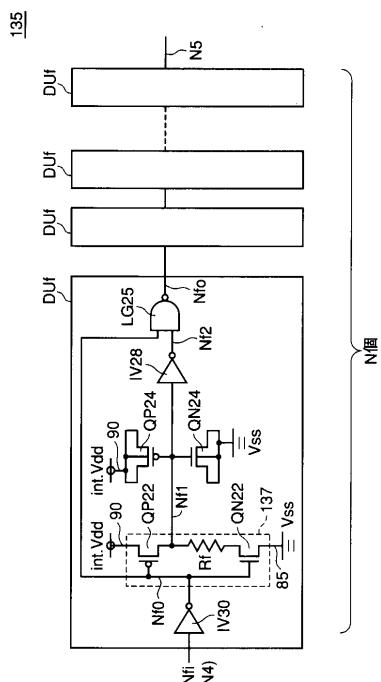

図9を参照して、立下がりエッジ遅延回路135は、直列に接続されたN個(N:自然数)の遅延ユニットD U fを有する。各遅延ユニットD U fは、入力ノードN f iに入力された信号の立下がりエッジを遅延させて出力ノードN f oに伝達する。初段の各遅延ユニットD U fの入力ノードN f iは、ノードN 4と結合される。最終段の各遅延ユニットD U fの出力ノードN f oは、ノードN 5と結合される。10

### 【0085】

遅延ユニットD U fは、入力ノードN f iの信号レベルを反転してノードN f oに伝達するインバータI V 3 0と、インバータ137を形成するP型MOSトランジスタQ P 2 2およびQ N 2 2および抵抗素子R fと、遅延容量となるP型MOSトランジスタQ P 2 4およびQ N 2 4と、インバータI V 2 8と、ノードN f 0およびN f 2のN A N D演算結果を出力する論理ゲートL G 2 5とを有する。

### 【0086】

遅延ユニットD U f中のインバータ137、遅延容量として作用するトランジスタQ P 2 4およびQ N 2 4、インバータI V 2 8および論理ゲートL G 2 5は、図8に示した遅延ユニットD U r中の、インバータ132、トランジスタQ P 1 4およびQ N 1 4、インバータI V 1 8および論理ゲートL G 2 0にそれぞれ相当する。20

### 【0087】

遅延ユニットD U fは、図8に示した遅延ユニットD U rと比較すると、入力ノードN f iの信号レベルがインバータI V 3 0によって反転されてインバータ137に伝達される点と、論理ゲートL G 2 5の出力がそのまま出力ノードN f oに伝達される点が異なる。

### 【0088】

したがって、遅延ユニットD U fにおいては、遅延ユニットD U rの場合とは反対に、入力ノードN f iにおけるLレベルからHレベルへの遷移は、インバータ30および論理ゲートL G 2 5によって出力ノードN f oに直ちに伝達される。これに対し、入力ノードN f iのHレベルからLレベルへの遷移は、抵抗素子R fおよび遅延容量として作用するトランジスタQ P 2 4およびQ N 2 4によって付加される遅延時間の経過後に出力ノードN f oに伝達される。30

### 【0089】

よって、立下がりエッジ遅延回路135全体で付加される遅延時間T fは、遅延ユニットD U f中における抵抗素子および遅延容量の抵抗値および容量値と、遅延ユニットの個数Nとによって、立上がりエッジに対する遅延時間T rとは独立に設定することができる。

### 【0090】

このように、図8および図9に示すように、立上がりエッジ遅延回路130および立下がりエッジ遅延回路135において、抵抗素子および容量素子によって遅延時間を付与する構成とすることで、温度や内部電源電位の変動の影響を受け難い遅延段を構成することを可能としている。40

### 【0091】

再び、図7を参照して、フリップフロップ127によって、ワード線活性化信号およびセンスアンプ活性化信号の活性化毎に、それぞれ活性化(Lレベル Hレベル)および非活性化(Hレベル Lレベル)される制御信号S D R Vの立上がりエッジ(Lレベル Hレベル)および立下がりエッジ(Hレベル Lレベル)は、立上がりエッジ遅延回路130および立下がりエッジ遅延回路135によって、遅延時間T rおよびT fそれぞれ遅50

延されてノードN5に伝達される。

【0092】

ノードN5の信号レベルは、インバータIV12およびIV14によって増幅されて強制電流供給制御信号DRVとして出力される。一方、インバータIV16は、信号DRVの反転信号である強制電流供給制御信号ZDRVを出力する。この結果、強制電流供給制御信号DRVおよびZDRVは、センスアンプの活性化に先立って実行されるワード線の活性化から遅延時間Trによって調整可能な所定時間経過後において、HレベルおよびLレベルにそれぞれ活性化され、センスアンプの活性化から遅延時間Tfによって調整可能な所定時間経過後において、LレベルおよびHレベルにそれぞれ非活性化される。

【0093】

図3で説明したように、負荷となるセンスアンプSAが実行するデータ増幅動作は、一連のメモリアクセス動作の中で実行されるので、まずワード線活性化信号WLACTが活性化された後に、実際の電流消費トリガとなるセンスアンプ活性化信号SEACTが活性化されて開始される。したがって、上述したタイミングで強制電流供給制御信号DRVおよびZDRVを活性化および非活性化することによって、負荷であるセンスアンプの電流消費が開始される前に内部電源電位int.Vddを供給する内部電源配線に対して強制的に電流を供給して、安定化容量92の容量値に大きく依存することなく、センスアンプによる急激かつ大量な電流消費に備えることができる。また、センスアンプの電流消費が終了するよりも前に内部電源配線に対する強制的な電流供給を中止することによって、内部電源配線の過充電を回避できる。

10

【0094】

内部電源制御回路115は、さらに、ノードN3と接地配線85との間に結合されるN型MOSトランジスタQN10を有する。トランジスタQN10のゲートには、インバータIV10によって反転されたワード線活性化信号WLACTが入力される。これにより、少なくともワード線活性化信号WLACTの非活性化時においては、制御信号SDRVの信号レベルはLレベルにリセットされることから、少なくともこの期間において、内部電源回路100において電流供給トランジスタQD1による強制的な電流供給が実行されることはない。

20

【0095】

また、内部電源回路110の電位差増幅回路105に動作電流を供給するための制御信号ACCTには、ワード線活性化信号WLACTを用いればよい。

30

【0096】

なお、メモリセルアレイ30においてメモリセルMCが複数のブロックに分割配置され、複数のブロックごとにワード線の活性化およびセンスアンプの活性化が独立に制御される場合、すなわち各ブロックごとにワード線活性化信号およびセンスアンプ活性化信号が設けられる場合も考えられる。

【0097】

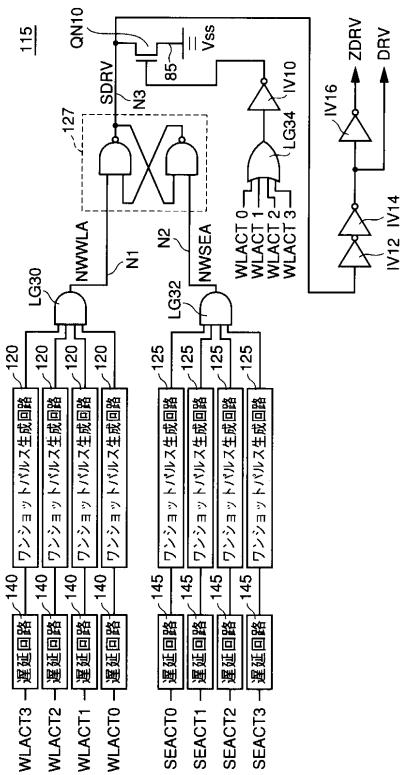

図28は、メモリセルアレイ30が複数のブロックに分割される場合に対応する内部電源制御回路115の構成を示すブロック図である。

40

【0098】

図28には、一例としてメモリセルアレイ30が4個のブロックに分割されている場合における、内部電源制御回路115の構成が示される。4個のブロックのそれぞれに対応して、ワード線活性化信号WLACT0～WLACT3およびセンスアンプ活性化信号SEACT0～SEACT3がそれぞれ設けられる。

【0099】

ワード線活性化信号WLACT0～WLACT3の各々に対応してワンショットパルス生成回路120が設けられる。同様に、センスアンプ活性化信号SEACT0～SEACT3の各々に対応して、ワンショットパルス生成回路125が設けられる。論理ゲートLG30は、これらのワンショットパルス回路120がそれぞれ出力するワンショットパルスのOR演算（ただし負論理のOR演算であり、正論理ではAND演算に相当）結果をノー

50

D N 1 に出力する。これにより、いずれか 1 つのブロックにおいてワード線活性化信号が活性化された場合に、ワンショットパルス信号 N W W L A が活性化される。

#### 【 0 1 0 0 】

同様に、論理ゲート L G 3 2 は、これらのワンショットパルス回路 1 2 5 がそれぞれ出力するワンショットパルスの O R 演算（ただし負論理の O R 演算であり、正論理では A N D 演算に相当）結果をノード N 2 に出力する。これにより、いずれか 1 つのブロックにおいてセンスアンプ活性化信号が活性化された場合に、ワンショットパルス信号 N W S E A が活性化される。

#### 【 0 1 0 1 】

ワンショットパルス信号 N W W L A および N W S E A に応答した、強制電流供給制御信号 D R V および Z D R V を活性化および非活性化については、すでに説明したとおりであるので、詳細な説明は繰り返さない。このようにして、メモリセルアレイ 3 0 が複数のブロックに分割される場合においても、負荷における電流に対応して、強制電流供給制御信号 D R V および Z D R V を生成することができる。10

#### 【 0 1 0 2 】

また、トランジスタ Q N 1 0 のオン / オフは、複数のブロックのそれぞれに対応して設けられるワード線活性化信号 W L A C T 0 ~ W L A C T 3 の O R 演算を行なう論理ゲート L G 3 4 の出力に基づいて制御すればよい。制御信号 A C T についても、複数のブロックのそれぞれに対応して設けられるワード線活性化信号の O R 演算結果、すなわち論理ゲート L G 3 4 の出力に基づいて生成すればよい。20

#### 【 0 1 0 3 】

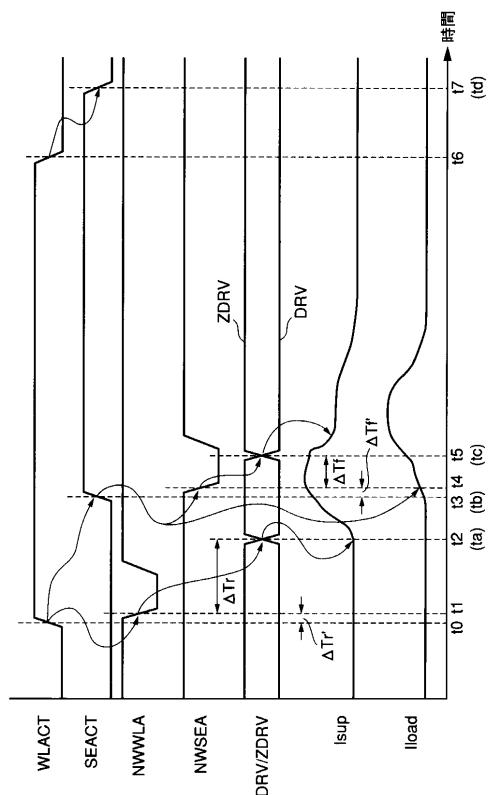

図 1 0 は、内部電源制御回路 1 1 5 の動作を説明するためのタイミングチャートである。

#### 【 0 1 0 4 】

時刻 t 0 においてワード線活性化信号 W L A C T が活性化（L レベル H レベル）される。これに応答して、ワンショットパルス発生回路 1 2 0 は、時刻 t 0 から T r ' 経過後の時刻 t 1 を起点として、ワンショットパルス信号 N W W L A を一定期間 L レベルに活性化する。20

#### 【 0 1 0 5 】

ワンショットパルス信号 N W W L A の活性化に応答して、フリップフロップ 1 2 7 の出力信号 S D R V は、L レベルから H レベルに立上がる（図示せず）。この立上がりエッジは、立上がりエッジ遅延回路 1 3 0 によって T r 遅延される。これに応じて、強制電流供給制御信号 D R V , Z D R V は、時刻 t 1 から遅延時間 T r 経過後の時刻 t 2 において活性化される。時刻 t 2 は、図 5 に示した時刻 t a に相当する。これに応答して、内部電源回路 1 0 0 においては、電流供給トランジスタ Q D 1 のゲート電位が低下を始め、供給電流 I s u p が強制的に流れ始める。30

#### 【 0 1 0 6 】

一方、図 5 に示した時刻 t b に相当する時刻 t 3 において、センスアンプ活性化信号 S E A C T が活性化されると、これに応答してセンスアンプ S A における電流消費が開始されて、負荷電流 I l o a d が流れ始める。40

#### 【 0 1 0 7 】

一方、時刻 t 3 におけるセンスアンプ活性化信号 S E A C T の活性化（L レベル H レベル）に応答して、ワンショットパルス発生回路 1 2 5 は、時刻 t 3 から T f ' 経過後の時刻 t 4 を起点として、ワンショットパルス信号 N W S E A を一定期間 L レベルに活性化する。

#### 【 0 1 0 8 】

これに応答して、フリップフロップ 1 2 7 の出力信号 S D R V は、H レベルから L レベルに立上がる（図示せず）。この立下がりエッジは、立上がりエッジ遅延回路 1 3 5 によって T f 遅延される。これに応じて、強制電流供給制御信号 D R V , Z D R V は、時刻 t 4 から遅延時間 T f 経過後の時刻 t 5 において非活性化される。時刻 t 5 は、図 5 に示した時刻 t c に相当する。50

**【0109】**

これに応じて、内部電源回路100における電流供給トランジスタQD1による強制的な電流供給は中止される。時刻t2から時刻t5において、内部電源配線90に予め過剰に供給された電荷によって、負荷電流Iloadの供給が行なわれる。

**【0110】**

この後、時刻t6においてワード線活性化信号WLASTが非活性化され、時刻t7(図5に示す時刻tdに相当)において、センスアンプ活性化信号SEACTが非活性化されて、負荷電流の消費は終了する。すでに説明したように、負荷がセンスアンプSAである場合には、消費電流は、センスアンプ活性化信号SEACTの活性化期間内の一時間間に集中する。

10

**【0111】**

時刻t5以降においては、内部電源回路100においては、内部電源電位int.Vccと基準電位Vrefとの電位レベルの比較結果に基づいて、内部電源配線90に対する電流供給が実行される。

**【0112】**

このように、負荷(センスアンプSA)における電流消費よりも確実に前のタイミングにおいて、内部電源回路100による強制的な電流供給を開始し、かつ負荷における電流消費が終了する前に強制的な電流供給を停止することによって、安定化容量92の容量値に大きく依存することなく負荷の電流消費開始時における内部電源電位の過渡的なへたりを防止し、かつ内部電源配線90の過充電による定常時における内部電源電位int.Vddの上昇とを両立して確実に防止することができる。

20

**【0113】**

次に、内部電源制御回路115の構成のバリエーションについて説明する。

図11は、内部電源制御回路の他の構成例を示すブロック図である。

**【0114】**

図11に示される内部電源制御回路115は、図7に示される内部電源制御回路と比較して、立上がりエッジ遅延回路130および立下がりエッジ遅延回路135に代えて、ワンショットパルス発生回路120および125とノードN1およびN2との間にそれぞれ設けられる遅延回路140および145を備える点で異なる。その他の構成については図7の場合と同様であるので詳細な説明は繰返さない。

30

**【0115】**

遅延回路140は、ワンショットパルス発生回路120が、ワード線活性化信号WLASTの活性化に応答してLレベルに活性化するワンショットパルス信号NWWLAをTr遅延してノードN1に伝達する。同様に、遅延回路145は、センスアンプ活性化信号SEACTの活性化に応答してLレベルに活性化するワンショットパルス信号NWSEAをTf遅延してノードN2に伝達する。

**【0116】**

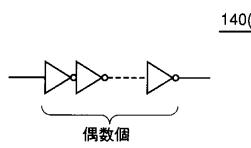

図29は、遅延回路140および145の第1の構成例を示す図である。図29を参照して、遅延回路140および145は、直列に接続された偶数個のインバータによって構成することができる。

40

**【0117】**

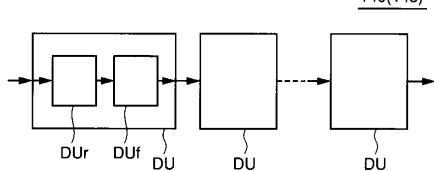

図30は、遅延回路140および145の第2の構成例を示す図である。図30を参照して、遅延回路140および145は、図8および図9で説明した遅延ユニットDUrおよびDUFの組で構成される遅延段DUを複数個直列に配置することによって形成することができる。

**【0118】**

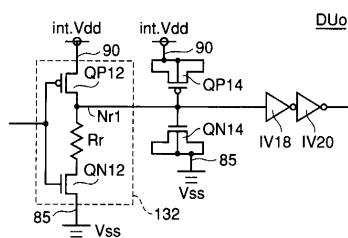

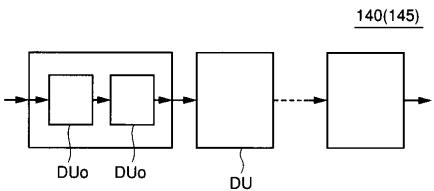

図31は、遅延回路140および145の第3の構成例を示す図である。図30を参照して、遅延回路140および145は、遅延ユニットDUrおよびDUFと類似の構成を有する遅延ユニットDUoによっても構成することができる。

**【0119】**

50

図32は、遅延回路ユニットDUoの構成を示す回路図である。

図32を参照して、遅延回路ユニットDUoは、図8に示された遅延ユニットDURと比較して、入力ノードNriへの入力信号を入力の一方とする論理ゲートL G18を有さない点で異なる。遅延回路ユニットDUoのその他の部分の構成については、遅延ユニットDURと同様である。このような構成とすることにより、2個の遅延回路ユニットDUoの組によって構成された遅延段DUは、入力信号の立上りエッジおよび立下りエッジを均等に遅延することができる。

#### 【0120】

既に説明したように、単純なインバータ段ではなく遅延ユニットDUF, DUR, DUoを使用することによって、温度条件や内部電源電位の変動に影響されない安定した遅延時間10を設定することができる。

#### 【0121】

このような構成とすることによっても、遅延回路140および150において、独立の遅延時間TrおよびTfをそれぞれ付与して、図10に示したのと同様のタイミングで、強制電流供給制御信号DRV, ZDRVの活性化期間を制御することが可能である。

#### 【0122】

図12は、内部電源制御回路115のさらに他の構成例を示すブロック図である。

#### 【0123】

図12に示される内部電源制御回路115は、図11に示した内部電源制御回路と比較して、遅延回路140および145をワンショットパルス発生回路120および125の前段に設けている点が異なる。その他の構成および動作については図11の場合と同様であるので詳細な説明は繰返さない。

#### 【0124】

このような構成とすることによって、遅延回路140および145は、ワード線活性化信号WLACTおよびセンスアンプ活性化信号SEACTを独立の遅延時間TrおよびTfずつそれぞれ遅延して、ワンショットパルス生成回路120および125にそれぞれ伝達する。

#### 【0125】

このような構成とすることによっても、図7および図11に示した内部電源制御回路の場合と同様に、図10に示したタイミングで強制電流供給制御信号DRV, ZDRVの活性化期間を制御することが可能である。

#### 【0126】

なお、メモリセルアレイ30においてメモリセルMCが複数のブロックに分割配置され、複数のブロックごとにワード線の活性化およびセンスアンプの活性化が独立に制御される場合、すなわち各ブロックごとにワード線活性化信号およびセンスアンプ活性化信号が設けられる場合には、図11および図12の回路構成においても、図28で説明したように、ワンショットパルス発生回路120および125のそれについて、OR演算結果を取る必要が生じる。

#### 【0127】

図33を参照して、特に、図12の構成の内部電源制御回路115を複数のブロックに分割されたメモリセルアレイ30に適用する場合には、分割されたブロックの数に対応して遅延回路140, 145を複数設けることが必要となってしまう。したがって、このような場合には、図7もしくは図11に示した内部電源制御回路115の構成を採用することが好ましい。

#### 【0128】

#### [実施の形態2]

実施の形態2においては、内部電源回路、すなわちVDCの構成のバリエーションについて説明する。

#### 【0129】

実施の形態2で説明する内部電源回路の各構成においては、強制電流供給制御信号DRV

10

20

30

40

50

およびZDRVの活性化期間は、実施の形態1で説明したのと同様であるので説明は繰り返さない。

#### 【0130】

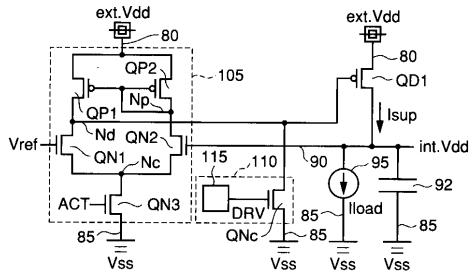

図13は、実施の形態2に従う内部電源回路の構成を示す回路図である。

図13を参照して、実施の形態2に従う内部電源回路は、図4に示される内部電源回路100の構成と比較して、強制電流供給制御回路110が、トランジスタQPaに代えて、電位差增幅回路105内のトランジスタQNaと並列に結合されるN型MOSトランジスタQNaを有する点で異なる。トランジスタQNaのゲートには、活性化時にHレベルに設定される強制電流供給制御信号DRVが入力される。

#### 【0131】

トランジスタQNaは、図4に示されるトランジスタQPaと同様のタイミングでオンして、内部電源電位int.Vddの電位レベルにかかわらずノードNdの電位レベルを強制的に低下させる。電流供給トランジスタQD1のゲート電位は、これに応じて低下するため、強制電流供給制御信号DRVの活性化期間中ににおいて、外部電源配線80から内部電源配線90に対して強制的な電流供給が実行される。

10

#### 【0132】

また、必要に応じて、強制電流供給制御回路111をさらに配置することもできる。強制電流供給制御回路111は、ノードNcと接地配線85との間に電気的に結合されるN型MOSトランジスタQNbを有する。トランジスタQNbのゲートには、強制電流供給制御信号DRVが入力される。強制電流供給制御信号DRVがHレベルに活性化されると、電位差增幅回路105を構成するカレントミラーアンプの動作電流が増加するので、内部電源電位int.Vddの変動をノードNdの電位レベルに反映する速度を上昇させて、内部電源電位int.Vddの制御性を向上することができる。

20

#### 【0133】

また、強制電流供給制御回路111によって、強制電流供給制御信号DRVの活性化期間中ににおけるノードNcの電位レベルが接地電位Vssにより近づくので、この期間中ににおける電流供給トランジスタQD1の強制的な供給電流Isupを増加させることができる。

#### 【0134】

その他の部分の構成は、内部電源回路100と同様であるので詳細な説明は繰り返さない。

30

#### 【0135】

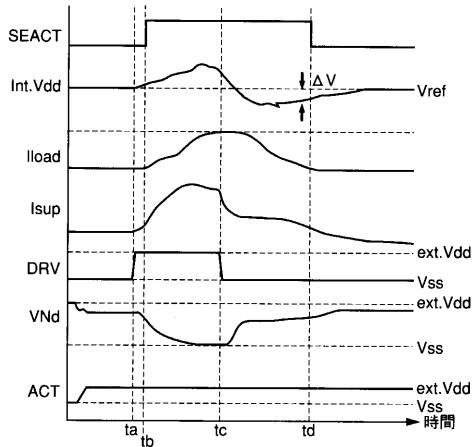

図14は、実施の形態2に従う内部電源回路の動作を説明するタイミングチャートである。

#### 【0136】

図14を参照して、時刻taにおいて、強制電流供給制御信号DRVがHレベルに活性化され、これに応じてノードNdの電位レベル、すなわち電流供給トランジスタQD1のゲート電位が低下を始める。これにより、電流供給トランジスタQD1が電流Isupを強制的に供給し、内部電源配線90は、負荷95による電流消費の開始に先立って電流の供給を受けるため、時刻tbにおいて、センスアンプ活性化信号SEACTの活性化に応答して、負荷であるセンスアンプで負荷電流Iloadの消費が開始されても、内部電源電位int.Vddが大きく降下することはない。

40

#### 【0137】

さらに、時刻tcにおいて、図10の場合と同様に強制電流供給制御信号DRVをLレベルに非活性化することによって、電流供給トランジスタQD1のゲート電位の強制的な操作は中止されるので、以降は内部電源電位int.Vddと基準電位Vrefとの電位レベルの比較に応じて、通常の内部電源電位の制御が実行される。これにより、内部電源配線90の過充電を防止することができる。

#### 【0138】

このような内部電源回路の構成によっても、実施の形態1に示される内部電源回路100

50

の場合と同様に、負荷における電流消費タイミングと合致させた、安定的な内部電源電位  $i_{nt} . V_{dd}$  の保持を安定化容量の容量値に大きく依存することなく実行することができる。

#### 【0139】

##### [実施の形態2の変形例1]

図15は、実施の形態2の変形例1に従う内部電源回路の構成を示す回路図である。

#### 【0140】

図15を参照して、実施の形態2の変形例1に従う内部電源回路は、図4に示される内部電源回路100の構成と比較して、強制電流供給制御回路110が、トランジスタQPaに代えて、ノードNdと接地配線85との間に電気的に結合されるN型MOSトランジスタQNcを有する点が異なる。 10

#### 【0141】

トランジスタQNcのゲートには、強制電流供給制御信号DRVが入力される。強制電流供給制御信号DRVの活性化(Hレベル)に応答して、電流供給トランジスタQD1のゲートは、接地配線85と接続される。これに応じて、電流供給トランジスタQD1は、内部電源電位  $i_{nt} . V_{dd}$  にかかわらず内部電源配線90に電流を供給する。その他の部分の構成は、内部電源回路100と同様であるので詳細な説明は繰り返さない。

#### 【0142】

図16は、実施の形態2の変形例1に従う内部電源回路の動作を説明するタイミングチャートである。 20

#### 【0143】

時刻taにおいて、制御信号DRVが活性化されると、ノードNdの電位レベルは、接地電位Vssまで低下する。この期間において、電流供給トランジスタQD1は、内部電源電位  $i_{nt} . V_{dd}$  の電位レベルに関係なく、外部電源配線80から内部電源配線90に対して電流Isupを強制的に供給する。

#### 【0144】

これにより、内部電源配線90は、負荷95による電流消費の開始に先立って電流の供給を受けるため、時刻tbにおいて、センスアンプ活性化信号SEACTの活性化に応答して、負荷であるセンスアンプで負荷電流Iloadの消費が開始されても、内部電源電位  $i_{nt} . V_{dd}$  が大きく下降することはない。 30

#### 【0145】

さらに、時刻tcにおいて、図10の場合と同様に強制電流供給制御信号DRVをLレベルに非活性化することによって、電流供給トランジスタQD1のゲート電位の強制的な操作は中止されるので、以降は内部電源電位  $i_{nt} . V_{dd}$  と基準電位Vrefとの電位レベルの比較に応じて、通常の内部電源電位の制御が実行される。これにより、内部電源配線90の過充電を防止することができる。

#### 【0146】

このような内部電源回路の構成によつても、実施の形態1に示される内部電源回路100の場合と同様に、負荷における電流消費タイミングと合致させた、安定的な内部電源電位  $i_{nt} . V_{dd}$  の保持を安定化容量の容量値に大きく依存することなく実行することができる。 40

#### 【0147】

また、実施の形態2の変形例1に従う内部電源回路の構成によれば、強制的な電流供給を実行する期間において、電流供給トランジスタQD1のゲート電位を接地電位Vssまで低下させることができるので、電流供給トランジスタQD1による供給電流Isupを大きく設定して、強制的な電流供給をより速やかに実行することができる。これにより、負荷95による電流消費がより急峻な場合にも対応することができる。

#### 【0148】

##### [実施の形態2の変形例2]

図17は、本発明の実施の形態2の変形例2に従う内部電源回路の構成を示す回路図であ 50

る。

**【0149】**

図17を参照して、本発明の実施の形態2の変形例2に従う内部電源回路は、図4に示される内部電源回路100の構成と比較して、強制電流供給制御回路110が、外部電源配線80と内部電源90との間に電流供給トランジスタQD1と並列に接続されるP型MOSトランジスタQD2を有する点が異なる。トランジスタQD2のゲートには、強制電流供給制御信号ZDRVが入力される。

**【0150】**

その他の部分の構成については、内部電源回路100と同様であるので詳細な説明は繰り返さない。

10

**【0151】**

図18は、本発明の実施の形態2の変形例2に従う内部電源回路の動作を説明するタイミングチャートである。

**【0152】**

実施の形態2の変形例2に従う内部電源回路においても、時刻taから時刻tcの期間中において、強制電流供給制御信号ZDRVはLレベルに活性化される。強制電流供給制御回路110を構成するトランジスタQD2は、強制電流供給制御信号ZDRVの活性化に応答して、電流Isup2を外部電源配線80から内部電源配線90に供給する。

**【0153】**

これに対して、電流供給トランジスタQD1は、内部電源配線90の電位レベルint.Vddと基準電位Vrefの電位レベル差に応じて電位差増幅回路105がノードNdに出力する電位レベルVNdに応じて電流Isup1を外部電源配線80から内部電源配線90に供給する。

20

**【0154】**

このような構成とすることによっても、制御信号ZDRVの活性化期間を負荷95の電流消費期間に対応して適切に調整することによって、これまでに説明した内部電源回路と同様の効果を享受することが可能となる。

**【0155】**

実施の形態1および2に示した内部電源回路の構成においては、図25に示した一般的なVDCの構成に対して、強制電流供給制御回路110を新たに外付けすることによって、上述した所定の新たな効果を得ることができる。したがって、VDCの基本的な構成部分については変更を加える必要がなく、回路設計を簡易化できる。

30

**【0156】**

なお、実施の形態1および2においては、電位差増幅回路105を、P型MOSトランジスタを負荷とするカレントミラーアンプで構成したが、これに代えて、N型MOSトランジスタを負荷とするカレントミラーアンプを適用することも可能である。

**【0157】**

[実施の形態3]

実施の形態3においては、実施の形態1および2で説明した、内部電源配線に対して強制的な電流を実行する内部電源回路を半導体記憶装置に適用した場合において、半導体記憶装置の動作状態に応じて、このような強制的な電流供給機能を実行するか否かを選択することが可能な構成について説明する。

40

**【0158】**

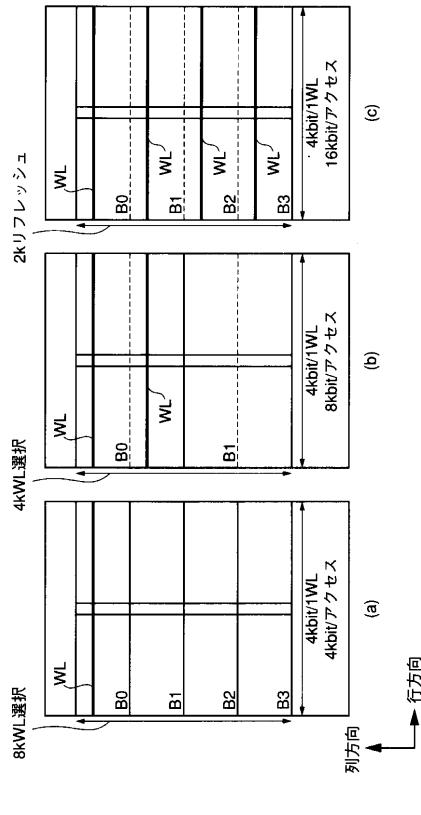

図19は、半導体記憶装置の動作状態に対応した消費電流量の相違を説明するための概念図である。

**【0159】**

図19においては、たとえば32MbitのDRAMコアの構成が示される。図19(a)においては、DRAMコアは4個のバンクB0~B3に分割され、1回のロウアクセスごとに、いずれか1個のバンクにおいて1本のワード線WLが選択的に活性化されて、8kのワード線選択が実行される。各ワード線には4kbitのメモリセルが接続される。

50

したがって、図19(a)の場合においては、通常動作時における1回のロウアクセス動作ごとに、 $1 \times 4\text{ kbit}$ のデータがセンスアンプ回路に読出される。以下においては、このように1回のロウアクセスで読出されるデータのビット数をページサイズとも称する。

#### 【0160】

図19(b)においては、 $32\text{ Mbit}$ のDRAMコアは2個のバンクB0およびB1に分割される。通常動作時における1回のロウアクセス動作ごとに、いずれか1個のバンクにおいて、2本のワード線WLが選択される。したがって、この場合においては、 $4\text{ k}$ のワード線選択が実行されて、ページサイズは $8\text{ kbit}$ となる。

#### 【0161】

図19(c)には、リフレッシュ動作におけるワード線選択が示される。特に、プロセスの微細化が進んでメモリセルのデータ保持容量が小さくなると、リフレッシュ周期を短くしていく必要が生じる。このため、リフレッシュ動作1回当たりに選択されるワード線の個数を通常動作時よりも増やすざるを得ないという背景がある。

#### 【0162】

すなわち、図19(c)の場合においては、リフレッシュ動作時において、1回のロウアクセスに対応して、4本のワード線が選択される。これにより、リフレッシュ動作時においては、1回のロウアクセスに対応して $16\text{ kbit}$ のデータをセンスアンプ回路によって增幅する必要が生じる。

#### 【0163】

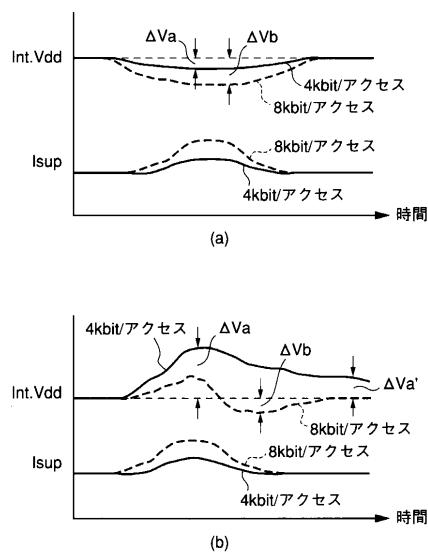

図20は、動作状態に対応した負荷電流の相違を説明する概念図である。

図20(a)においては、実施の形態1および実施の形態2で説明した強制的な電流供給を実行しない場合における、内部電源電位int.Vddの推移が示される。

#### 【0164】

図20(a)を参照して、ページサイズが $4\text{ kbit}$ および $8\text{ kbit}$ の場合における消費電流Iloadおよび内部電源電位int.Vddの推移がそれぞれ実線および点線で示される。

#### 【0165】

図20(a)に示されるように、ページサイズが増えるとセンスアンプ回路によって増幅されるデータの個数も増大するため、消費電流Iloadは増大する。この結果、ページサイズが $8\text{ kbit}$ の場合の内部電源電位int.Vddの低下量Vbは、ページサイズが $4\text{ kbit}$ の場合の電位低下量Vaよりも大きくなってしまう。

#### 【0166】

図20(b)においては、実施の形態1および2で説明した強制的な電流供給を実行した場合の内部電源電位int.Vddの推移が示される。

#### 【0167】

図20(b)の場合においては、強制電流供給制御信号DRV, ZDRVの活性化によって、負荷における電流消費期間に対応して外部電源配線80から内部電源配線90に対して強制的な電流供給が実行される。

#### 【0168】

このような、強制的な電流供給が、図20(a)に示したページサイズが $8\text{ kbit}$ である場合と適合するものと仮定した場合には、図20(b)において点線で示される、ページサイズが $8\text{ kbit}$ の場合における内部電源電位int.Vddの推移は、実施の形態1および2で説明したような良好な推移となる。

#### 【0169】

しかしながら、ページサイズが $4\text{ kbit}$ の場合においては、負荷電流Iloadが小さいので、内部電源配線90に対する強制的な電流供給が、内部電源配線90の過充電につながってしまう。このように、電流が過剰供給されると、内部電源電位int.VddのオーバーシュートVaが大きくなってしまう。定常状態においても、オーバーシュート

Va'は解消されず、内部電源電位int.Vddが基準電位Vrefよりも高いレベ

10

20

30

40

50

ルで定常的に推移してしまうという問題点が生じてしまう。これにより電力消費量が増加してしまい、オーバーシュート量が大きい場合には、回路素子の破壊につながるおそれもある。

#### 【0170】

また、図19(a)および(b)で示されるような通常動作時においては、ページサイズが4kbitおよび8kbitのいずれであっても、強制的な電流供給を実行することなく内部電源電位int.Vddを保持できるが、リフレッシュ動作時に初めて、強制的な電流供給が必要となってしまうようなケースも考えられる。

#### 【0171】

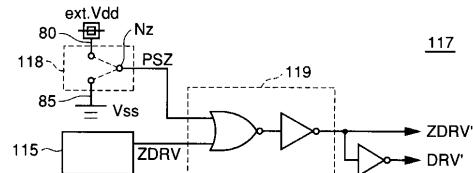

図21は、実施の形態3に従う内部電源制御回路117の第1の構成例を示す回路図である。10

#### 【0172】

図21を参照して、内部電源制御回路117は、実施の形態1で説明した内部電源制御回路115の構成によって生成される制御信号ZDRVと、ページサイズ設定信号PSZとの信号レベルに応じて、強制電流供給制御回路DRV'，ZDRV'を生成する論理回路119を有する。

#### 【0173】

実施の形態3においては、実施の形態1および2で説明した内部電源回路の構成の各々を適用することができる。実施の形態3においては、内部電源回路は、内部電源制御回路115が生成する制御信号DRV，ZDRVに代えて、内部電源制御回路117が生成する強制電流供給制御信号DRV'，ZDRV'に応答して動作する。20

#### 【0174】

ページサイズ設定信号PSZは、ページサイズが4kbitの場合はHレベルに設定され、ページサイズが8kbitの場合にはLレベルに設定される。モード信号PSZの電位レベルは、配線領域118における、ノードNzと外部電源配線80および接地配線85との間の選択的な配線の形成によって実行される。すなわち、図21に示される内部電源制御回路は、配線形成時のマスク切換によって、ページサイズが設定される場合に対応するものである。

#### 【0175】

内部電源制御回路115の構成によって生成される制御信号ZDRVは、強制的な電流供給を実行する区間ににおいてLレベルに活性化される信号であるため、論理回路119によって、ページサイズ設定信号PSZと制御信号ZDRVとのOR演算結果を取ることによって、ページサイズに応じて、強制的な電流供給の実行を選択することができる。30

#### 【0176】

具体的には、ページサイズが4kbitに設定されている場合には、ページサイズ設定信号PSZがHレベルに固定されるため、強制電流供給制御信号ZDRV'の電位レベルは、内部電源制御回路115の出力にかかわらず常にHレベルに非活性化されて、内部電源回路における強制的な電流供給は実行されない。

#### 【0177】

これに対して、ページサイズが8kbitであり、ページサイズ設定信号PSZの信号レベルがLレベルである場合においては、制御信号ZDRVの信号レベルは、そのまま強制電流供給制御信号ZDRV'に反映される。40

#### 【0178】

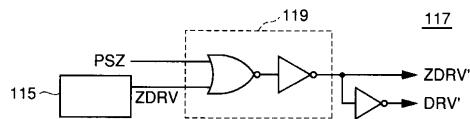

図22は、実施の形態3に従う内部電源制御回路の第2の構成例を示す回路図である。図22には、ページサイズの設定が電気信号に応答して切換えられる場合に対応する内部電源制御回路の構成が示される。

#### 【0179】

図22を参照して、ページサイズの設定は、ページサイズ設定信号PSZの信号レベルに応じて切換えられる。ページサイズ設定信号PSZは、図21で説明したのと同様に、ページサイズが4kbitの場合にはHレベルに設定され、ページサイズが8kbitの場50

合には L レベルに設定されるものとする。

**【 0 1 8 0 】**

内部電源制御回路 117 は、図 21 の構成と同様に、内部電源制御回路 115 が出力する制御信号 ZDRV とページサイズ設定信号 PSZ の OR 演算結果を出力する論理回路 119 を有する。

**【 0 1 8 1 】**

論理回路 119 の出力およびその反転信号を、強制電流供給制御信号 ZDRV' および DDRV' として内部電源回路に供給することによって、図 21 の場合と同様の効果を得ることができる。

**【 0 1 8 2 】**

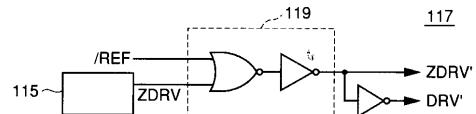

図 23 は、実施の形態 3 に従う内部電源制御回路の第 3 の構成例を示す回路図である。図 23 には、リフレッシュ動作時に対応して強制的な電流供給を実行するための内部電源制御回路の構成が示される。

**【 0 1 8 3 】**

図 23 の回路構成は、1 回のロウアクセス動作の対象となるデータの個数が、通常動作時よりもリフレッシュ動作時において多く、通常動作時においては、ページサイズの設定にかかわらず強制的な電流供給を実行することなく内部電源電位 int.Vdd を保持できるものの、リフレッシュ動作時において、強制的な電流供給が必要となってしまう場合に適用される。

**【 0 1 8 4 】**

図 23 を参照して、内部電源制御回路 117 は、リフレッシュモード信号 / REF と、内部電源制御回路 115 が出力する制御信号 ZDRV との OR 演算結果を、強制電流供給制御信号 ZDRV' として出力する論理回路 119 を有する。

**【 0 1 8 5 】**

リフレッシュモード信号 / REF は、半導体装置の動作モードが通常動作であるかリフレッシュ動作であるかを示す信号である。具体的には、リフレッシュモード信号 / REF は、通常動作時においては H レベルに非活性化され、リフレッシュ動作時においては、L レベルに活性化される。

**【 0 1 8 6 】**

したがって、通常動作時においては、制御信号 ZDRV の信号レベルにかかわらず、強制電流供給制御信号 ZDRV' は、常に H レベルに非活性化され、内部電源回路において強制的な電流供給が実行されることはない。

**【 0 1 8 7 】**

一方、リフレッシュ動作時においては、リフレッシュモード信号 / REF が L レベルに活性化されることに対応して、強制電流供給制御信号 ZDRV' の信号レベルは、内部電源制御回路 115 の構成によって生成される制御信号 ZDRV に対応して設定される。これにより、負荷の電流消費期間に合わせたタイミングで、内部電源回路において強制的な電流供給が実行されることになる。

**【 0 1 8 8 】**

このような構成とすることにより、強制的な電流供給を実行することなく内部電源電位 int.Vdd の電位レベルの保持が可能な通常動作時においては、内部電源配線 90 の過充電による電位レベルの上昇を防ぎ、消費電流の大きいリフレッシュ動作時において、容量値の大きい安定化容量を設けることなく、内部電源電位 int.Vdd の電位レベルを良好に維持することが可能となる。

**【 0 1 8 9 】**

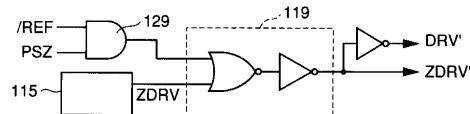

図 24 は、実施の形態 3 に従う内部電源制御回路の第 4 の構成例を示す回路図である。図 24 には、ページサイズと動作モードとの両方に対応して、強制的な電流供給の実行の有無を選択することが可能な内部電源制御回路の構成が示される。

**【 0 1 9 0 】**

図 24 を参照して、内部電源制御回路 125 は、ページサイズ設定信号 PSZ とリフレッ

10

20

30

40

50

シユモード信号 / R E F との間で論理演算を実行する論理ゲート 129 と、論理ゲート 129 の出力および内部電源制御回路 115 に相当する構成から出力される制御信号 Z D R V の間ににおいて論理演算を実行する論理回路 119 とを有する。

#### 【 0191 】

ページサイズ設定信号 P S Z およびリフレッシュモード信号 / R E F の信号レベルについては、図 21 から図 23 での説明と同様であるので説明は繰返さない。

#### 【 0192 】

すなわち論理ゲート 129 の出力が H レベルに設定されると、制御信号 Z D R V の信号レベルにかかわらず強制電流供給制御信号 Z D R V' は非活性化 (H レベル) されて、内部電源回路における強制的な電流供給は実行されない。論理ゲート 129 の出力が H レベルに設定されるのは、リフレッシュモード信号 / R E F が H レベル、すなわち通常動作モード時であって、かつ、ページサイズ設定信号 P S Z が H レベル、すなわちページサイズが 4 k b i t である場合に限られる。このように、動作モードおよびページサイズに基づいて、消費電流が小さいと判断される動作状態においては、強制的な電流供給を行なわずに、内部電源配線の過充電による内部電源電位 i n t . V d d の上昇を抑制する。

10

#### 【 0193 】

一方、リフレッシュモード信号 / R E F が L レベルに設定される場合、すなわちリフレッシュ動作が実行される場合、もしくは通常動作時であってページサイズが 8 k b i t と大きい場合、すなわち負荷であるセンスアンプの消費電流が大きくなる動作状態においては、負荷の電流消費期間に対応して、強制電流供給制御信号 Z D R V' および D R V' を活性化させることによって、内部電源電位 i n t . V d d の電位レベルを良好に維持することが可能となる。

20

#### 【 0194 】

このように、実施の形態 3 に従う内部電源制御回路の構成によれば、ページサイズもしくは動作モードに代表される半導体記憶装置の動作状態に応じて、内部電源回路における強制的な電流供給の実行有無を選択することが可能である。これにより、消費電流の大きい動作状態において負荷電流の影響による内部電源電位 i n t . V d d の低下を防止するとともに、消費電流が小さい動作状態においては、内部電源配線に対する過充電を防止して、内部電源電位 i n t . V d d のオーバーシュートを抑制することができる。

30

#### 【 0195 】

なお、実施の形態 3 においては、ページサイズおよび動作モード（通常動作 / リフレッシュ動作）に基づいて、負荷であるセンスアンプの消費電流の程度を判断したが、他の内部回路を負荷として内部電源電位 i n t . V d d を供給する場合には、適宜他の動作条件に基づいて、内部電源回路における強制的な電流供給の実行 / 中止を選択する構成とすればよい。

#### 【 0196 】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

40

#### 【 0204 】

##### 【発明の効果】

請求項 1 および 2 に記載の半導体記憶装置は、センスアンプが活性化されて電流が消費される前に、内部電源配線に対して強制的に電流を供給することができる。この結果、センスアンプ回路による急峻かつ大量の電流消費に対応して、内部電源配線に大容量の安定化容量を配置することなく、内部電源電位の降下量を抑制してセンスアンプ回路によるデータ読出動作を高速化できるとともに、通常動作時およびリフレッシュ動作時の少なくとも一方における、1 回のロウアクセス動作の対象となるメモリセルの個数によって消費電流量を判断することにより、消費電流量が比較的小さい動作状態が設定されている場合には、センスアンプの電流消費に対応するための強制的な電流供給を実行しないようにして

50

内部電源配線の過充電を防止できる。

【図面の簡単な説明】

【図 1】 本発明の実施の形態 1 に従う内部電源回路を備えた半導体記憶装置 1 の全体構成を示す概略ブロック図である。

【図 2】 メモリセルアレイ 30 およびセンスアンプ回路 50 の構成を説明するブロック図である。

【図 3】 メモリアクセス時におけるワード線およびセンスアンプの活性化に伴う動作を説明するタイミングチャートである。

【図 4】 実施の形態 1 に従う内部電源回路の構成を示す回路図である。

【図 5】 実施の形態 1 に従う内部電源回路の動作を説明するタイミングチャートである 10

。

【図 6】 内部電源制御回路の入出力関係を示すブロック図である。

【図 7】 内部電源制御回路の構成を示すブロック図である。

【図 8】 立上がりエッジ遅延回路の構成を示す回路図である。

【図 9】 立下がりエッジ遅延回路の構成を示す回路図である。

【図 10】 内部電源制御回路の動作を説明するためのタイミングチャートである。

【図 11】 内部電源制御回路の他の構成例を示すブロック図である。

【図 12】 内部電源制御回路のさらに他の構成例を示すブロック図である。

【図 13】 実施の形態 2 に従う内部電源回路の構成を示す回路図である。

【図 14】 実施の形態 2 に従う内部電源回路の動作を説明するタイミングチャートである 20

【図 15】 実施の形態 2 の変形例 1 に従う内部電源回路の構成を示す回路図である。

【図 16】 実施の形態 2 の変形例 1 に従う内部電源回路の動作を説明するタイミングチャートである。

【図 17】 本発明の実施の形態 2 の変形例 2 に従う内部電源回路の構成を示す回路図である。

【図 18】 本発明の実施の形態 2 の変形例 2 に従う内部電源回路の動作を説明するタイミングチャートである。

【図 19】 半導体記憶装置の動作状態に対応した消費電流量の相違を説明するための概念図である 30

【図 20】 動作状態に対応した負荷電流の相違を説明する概念図である。

【図 21】 実施の形態 3 に従う内部電源制御回路の第 1 の構成例を示す回路図である。

【図 22】 実施の形態 3 に従う内部電源制御回路の第 2 の構成例を示す回路図である。

【図 23】 実施の形態 3 に従う内部電源制御回路の第 3 の構成例を示す回路図である。

【図 24】 実施の形態 3 に従う内部電源制御回路の第 4 の構成例を示す回路図である。

【図 25】 VDC の代表的な構成を有する従来の技術の内部電源回路の構成を示す回路図である。

【図 26】 負荷の電流消費パターンの一例に対応する内部電源回路の動作を示すタイミングチャートである。

【図 27】 負荷の電流消費パターンの他の一例に対応する内部電源回路の動作を示すタイミングチャートである 40

【図 28】 メモリセルアレイ 30 が複数のブロックに分割される場合に対応する内部電源制御回路 115 の構成を示すブロック図である。

【図 29】 遅延回路 140 および 145 の第 1 の構成例を示す図である。

【図 30】 遅延回路 140 および 145 の第 2 の構成例を示す図である。

【図 31】 遅延回路 140 および 145 の第 3 の構成例を示す図である。

【図 32】 遅延回路ユニット DUO の構成を示す回路図である。

【図 33】 図 12 に示される内部電源制御回路 115 を複数のブロックに分割されたメモリセルアレイ 30 に適用する場合の構成を示す回路図である。

【符号の説明】

30 メモリセルアレイ、50 センスアンプ回路、80 外部電源配線、85 接地配線、90 内部電源配線、92 安定化容量、95 負荷、105 電位差増幅回路、110 強制電流供給制御回路、115, 117 内部電源制御回路、120, 125 ワンショットパルス生成回路、130 立上がりエッジ遅延回路、135 立下がりエッジ遅延回路、140, 145 遅延回路、QD1 電流供給トランジスタ、SA センスアンプ。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

140(145)

【図30】

140(145)

【図32】

【図31】

140(145)

【図 3 3】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(74)代理人 100098316

弁理士 野田 久登

(72)発明者 加藤 宏

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 堀田 和義

(56)参考文献 特開平8-153388(JP,A)

特開平11-144465(JP,A)

特開2000-228084(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/4074