**DESCRIÇÃO

DA

PATENTE DE INVENÇÃO**

**N.º 97 810**

**REQUERENTE:** THOMSON CONSUMER ELECTRONICS, INC., norte-americana, com sede em 4704 West 81st Place, Indianapolis, Indiana 46268, Estados Unidos da América

**EPÍGRAFE:** "Dispositivo de sincronização de campo com controlo de indicador de escrita/leitura"

**INVENTORES:** Nathaniel Haluk Ersoz e Barth Alan Canfield

**Reivindicação do direito de prioridade ao abrigo do artigo 4º da Convenção de Paris de 20 de Março de 1883.**

Reino Unido em 1 de Junho de 1990 sob o nº 9012326.6

PATENTE N<sup>o</sup> 97 810

"Dispositivo de sincronização de campo com controlo de indicador de escrita/leitura"

RESUMO

O presente invento refere-se a um dispositivo de sincronização de campo para sinais video assíncronos com controlo de indicador de escrita/leitura, que compreende meios de visionamento video sincronizados com um primeiro sinal video, tendo um primeiro componente de frequência de linha e um primeiro componente de frequência de campo; uma memória de campo de um segundo sinal video tendo um segundo componente de frequência de linha; uma memória de linha múltipla, tendo indicadores de escrita e leitura reposicionáveis independentemente; meios operativos sincronamente com o dito segundo componente de frequência de linha, para subamostrarem o dito segundo do sinal video, para lerem e escreverem o dito sinal video subamostrado na dita memória de campo, respectivamente, e para escrever o dito sinal video subamostrado na dita memória de linha múltipla; meios operativos sincronamente com o dito componente de frequência de linha para leitura do dito sinal video subamostrado da dita memória de linha múltipla; meios para reposição do dito indicador de escrita, para amostragem do dito primeiro componente de frequência de campo com o dito segundo componente de frequência de linha e, meios para reposição do dito indicador de leitura para amostragem do dito componente de frequência de campo com o dito primeiro componente de frequência de linha. O indicador de escrita é reposto por meios, que fazem a amostragem do primeiro componente de frequência de campo, com o segundo componente de frequência de linha. O indicador de leitura é reposto por meios que fazem a amostragem do primeiro componente de frequência de campo com o primeiro componente de frequência de linha. Meios de retardo asseguram que o indicador de escrita é reposto na primeira extremidade de um período de linha do segundo sinal video, após cada início do campo do segundo sinal video, e asseguram que o indicador de leitura é reposto na segunda extremidade de um período de linha do primeiro sinal video, após a reposição do indicador de escrita.

O presente invento é aplicável na indústria electrónica de televisão, mais particularmente em televisores de alta definição visionamentos de imagem múltipla para sinais video assíncronos.

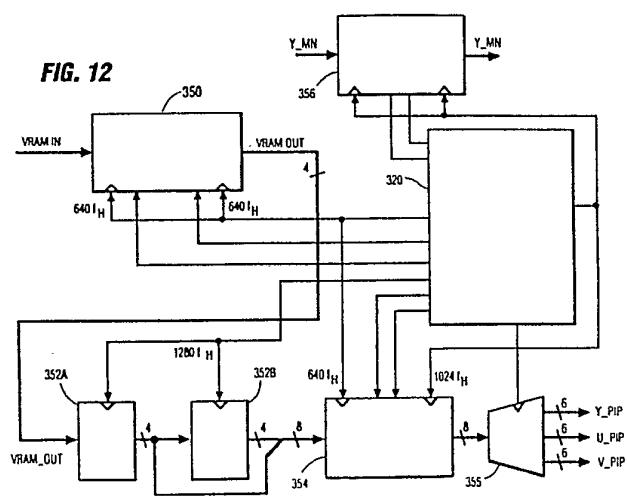

FIG. 12

MEMÓRIA DESCRIPTIVA

O invento refere-se ao campo de televisões que têm visionamentos de imagem múltipla para sinais video assíncronos, e em particular, para aquelas televisões que têm um ecrã de relação de formato de visionamento largo. A maior parte das televisões de hoje têm uma relação de formato de visionamento, de entre largura horizontal e a altura vertical, de 4:3. Uma relação de formato de visionamento largo corresponde mais aproximadamente à relação de formato de visionamento dos filmes por exemplo 16:9. O invento é aplicável tanto a televisões de visão directa como a televisões de projecção.

As televisões que têm uma relação de formato de visionamento de 4:3, referidas muitas vezes como de 4x3, estão limitadas no sentido em que podem ser visionadas fontes de sinal video simples e múltiplo. As transmissões de sinal de televisão de estações comerciais, excepto para material experimental, são emitidas com uma relação de formato de visionamento de 4x3. Muitos espectadores acham o formato de visionamento de 4x3 menos agradável do que as relações de formato de visionamento mais largos associadas a filmes. As televisões com uma relação de formato de visionamento largo fornecem não apenas um visionamento mais agradável, mas são também capazes de visionar fontes de sinal de formato de visionamento largo num correspondente formato de visionamento largo. Filmes "parecem" semelhantes a filmes, não cortados ou suas versões distorcidas. A fonte video não necessita ser cortada, mesmo quando convertida de filme para video, por exemplo com um dispositivo de accionamento de cinescópio, ou por processadores na televisão.

As televisões com uma relação de formato de visionamento largo são também apropriadas para uma variedade de visionamentos para sinais de formato de visionamento tanto convencional como largo, bem como suas combinações nos visionamentos de imagem múltipla. Contudo, a utilização de um ecrã de relação de formato de visionamento largo impõe numerosos problemas. Mudar as relações de formato de visionamento de fontes de sinal múltiplo, desenvolver sinais de temporização consistentes de fontes

assíncronas mas simultaneamente visionadas, comutar entre fontes múltiplas para gerar visionamentos de imagem múltipla, e fornecer imagens de alta resolução a partir de sinais de dados comprimidos são as categorias gerais de tais problemas. Estes problemas são resolvidos numa televisão de ecrã largo de acordo com este invento. Uma televisão de ecrã largo de acordo com este invento é capaz de fornecer alta resolução, visionamento de imagem simples e múltipla, a partir de fontes assíncronas simples e múltiplas que têm relações de formatos semelhantes ou diferentes, e com relações de formato de visionamento seleccionáveis.

Quando uma imagem auxiliar é uma pequena inserção, são toleráveis vários artefactos de sincronização imprecisa com o sinal principal. Contudo, para alguns formatos particularmente apropriados para uma televisão de ecrã largo, tal como duas imagens lado a lado de dimensão igual, tal imprecisão e os artefactos não podem ser tolerados. A dimensão grande da imagem auxiliar pode tornar tais artefactos penosamente óbvios. Geralmente, o visionamento video e o dispositivo de deflexão para visionamentos de imagem composta estão sincronizados com o sinal video auxiliar e com o visionamento video. Num dispositivo relativamente barato, o sinal video auxiliar pode ser atrasado por uma fração de um período de campo numa memória de campo, e então acelerado numa memória de linha. Num dispositivo sofisticado e relativamente caro, tal como é utilizado habitualmente nos estúdios de emissão de qualidade, um dispositivo de sincronização de quatro campos utiliza quatro memórias de campo assíncronas de acesso duplo. Memórias assíncronas, isto é, as que têm acessos de relógio independentes de escrita e leitura, são geralmente mais caras do que as memórias síncronas.

De acordo com as disposições do invento, aqui descritas, pode ser alcançado um grau de sincronização de campo que conjuga substancialmente o desempenho de um dispositivo de quatro campos, mas utiliza apenas uma única RAM video síncrona como uma memória de campo e um único dispositivo de memória de linha múltipla assíncrono primeiro a entrar primeiro a sair (FIFO). Se a FIFO é

um memória de cinco linhas, podem ser encontrados os seguintes artefactos: (1) duas mudanças de linha de quadro e 1 mudança de linha de campo ocorrerão cada vez que dois sinais precessam através de um quadro video; e (2) o canal video auxiliar torna-se arrastado no fundo da imagem quando a frequência de precessão entre os sinais principal e auxiliar é maior do que duas linhas por quadro. Tem-se verificado que esta frequência de precessão provavelmente não ocorre no ambiente da electrónica de consumo. A economia de custo num dispositivo de quatro campos é aproximadamente de 4:1, sem incorrer a qualquer sacrifício significativo no desempenho. A dimensão da FIFO refere-se à capacidade de armazenamento de linha mínima pensada ser razoavelmente necessária para evitar colisões do ponteiro de leitura/escrita. Colisões do ponteiro de leitura/escrita ocorrem quando dados antigos são lidos da FIFO antes de novos dados terem uma oportunidade de serem escritos na FIFO. Também ocorrem colisões quando os novos dados cancelam a memória antes dos dados antigos terem uma oportunidade de serem lidos da FIFO. A dimensão da FIFO utilizada nisto aqui, por exemplo 2048 x 8, corresponde a aproximadamente cinco linhas.

De acordo com uma disposição do invento, um dispositivo de sincronização de campo para sinais video assíncronos compreende um visor video sincronizado com um primeiro sinal video. O primeiro sinal video tem um primeiro componente de frequência de linha e um primeiro componente de frequência de campo, correspondendo aos componentes de sincronização horizontal e vertical do primeiro sinal video. Uma memória de campo tendo acessos síncronas de escrita e leitura, é fornecida por um segundo sinal video. O segundo sinal video tem um segundo componente de frequência de linha, correspondendo ao componente de sincronização horizontal do segundo sinal video. Uma memória de linha múltipla (FIFO) para o segundo sinal video tem acessos síncronas de escrita e leitura e ponteiros de escrita e leitura independentemente restabelecível. O segundo sinal video, subamostrado se necessário, é armazenado na memória de campo e escrito para a memória de campo sincronizadamente com o segundo componente de frequência de linha. O segundo sinal video,

subamostrado se necessário, é escrito na memória de linha múltipla sincronizada com o segundo componente de frequência de linha. Os dados que correspondem ao segundo sinal video são por isso completamente perpendiculares, tendo sido subamostrados e armazenados sincronizada com os seus próprios componentes de sincronização. O segundo sinal video, subamostrado se necessário, é lido da memória de linha múltipla sincronizada com o primeiro componente de frequência de linha. Um circuito de amostragem e atraso controla restabelecendo os ponteiros de escrita e leitura. Um sinal de restabelecimento do ponteiro de escrita é gerado amostrando-se o primeiro componente de frequência de campo com o segundo componente de frequência de linha. O ponteiro de escrita é restabelecido até um período de linha do segundo sinal video antes de cada início de campo do primeiro sinal video. Um sinal de restabelecimento do ponteiro de leitura é gerado amostrando-se o primeiro componente de frequência de campo com o primeiro componente de frequência de linha. O ponteiro de leitura é restabelecido pelo menos dois períodos de linha do primeiro sinal video depois de cada início de campo do primeiro sinal video, e mais particularmente, pelo menos dois mas não mais do que três períodos de linha do primeiro sinal video depois de cada início de campo do primeiro sinal video.

Blocos de dados da RAM video são escritos na FIFO 2048 x 8 com o mesmo relógio que foi utilizado para amostrar os dados video, por exemplo um relógio  $640f_H$  que está bloqueado para o sinal auxiliar, preferivelmente ao sinal principal. A FIFO é lida utilizando a frequência de relógio de visionamento, por exemplo  $1024f_H$ , que está bloqueado para o componente de sincronização horizontal do canal video principal. A utilização de uma memória de linha múltipla (FIFO) que tem relógios de acesso de leitura e escrita independente possibilita aos dados que foram amostrados perpendicularmente numa primeira frequência serem visionados perpendicularmente numa segunda frequência. A utilização da FIFO assíncrono para o canal auxiliar não resolve todos os problemas associados à sincronização video. Dado que a leitura e escrita de dados do canal FIFO auxiliar é assíncrona, há a possibilidade de

colisão do ponteiro de leitura/escrita. Uma colisão do ponteiro de leitura/escrita ocorre quando um sinal que possibilita a leitura que é recebido antes dos dados antigos, que foram já lidos previamente, foi substituído por dados escritos recentemente. Deve ser também preservada a integridade do entrelaçamento.

Deve ser escolhida uma memória suficientemente grande no primeiro caso a fim de evitar a colisão do ponteiro de leitura/escrita no canal FIFO auxiliar. Para visionar relações de formato de visionamento normal de video cortado de 33%, A FIFO auxiliar, que é da dimensão de 2048 x 8, é capaz de armazenar 5,9 linhas de dados video, por exemplo, baseado nos 82% do período de linha activo. Uma disposição do invento reconhece que as frequências de precessão maiores do que 2 linhas/campo não são provavelmente encontradas. Além disso, um critério de projecto de uma FIFO de 5 linhas para o canal auxiliar pode ser suficiente para evitar colisões do ponteiro de leitura/escrita.

Visto que os sinais principal e auxiliar são assíncronos, há alguma ambiguidade acerca de exactamente onde o ponteiro de escrita está quando o ponteiro de leitura é restabelecido. É sabido que o ponteiro de escrita precede o ponteiro de leitura de pelo menos duas linhas. Contudo, se a frequência de sincronismo horizontal do canal auxiliar é maior do que a frequência de sincronismo horizontal do canal principal, então o ponteiro de escrita terá avançado para além da segunda linha. Para sinais diferentes que têm uma frequência de precessão menor do que 2 linhas/campo, a quantidade que o ponteiro de escrita pode ter de avançar pode ser por exemplo, 10 bytes.

É deste modo que é evitada uma colisão do ponteiro para todos os sinais com frequência de precessão de menos de 2 linhas/campo. O canal auxiliar FIFO pode ser dividido em 5 bocados de linha através de leitura temporizada apropriada e de sinais de restabelecimento de escrita. Nesta disposição, os ponteiros de leitura e escrita são iniciados no início de cada campo visionado em pelo menos 2 linhas afastadas entre si.

~~SECRET~~

Se a FIFO não for um conjunto completo de 5 linhas de comprimento, o dispositivo sacrificaria a distância de memória do ponteiro de escrita ao ponteiro de leitura. É este o caso para diferentes modos de compressão. No caso de uma compressão de 16%, a extensão da FIFO actual é de 4,7 linhas de comprimento. Além do mais no caso do ponteiro de escrita apanhar o ponteiro de leitura há ainda pelo menos 2,6 linhas de memória entre os ponteiros no inicio do campo. No caso da compressão de 33%, a extensão da FIFO actual é de 4,0 linhas de comprimento. Isto não é o suficiente para assegurar a integridade do ponteiro para frequências de precessão até 2 linhas/campo.

As figuras 1(a)-1(i) são úteis para explicar os diferentes formatos de visionamento de uma televisão de ecran largo.

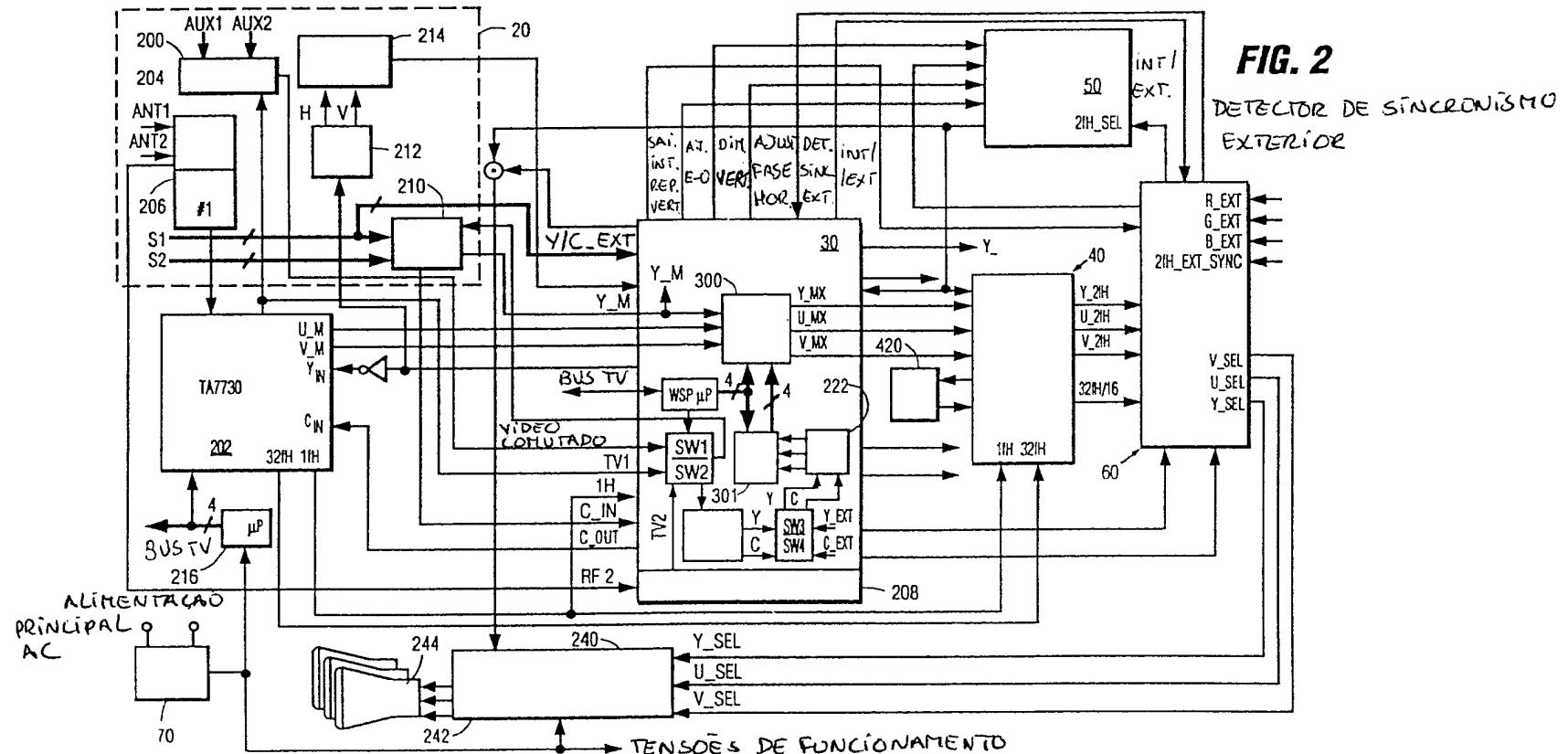

A figura 2 é um diagrama de blocos de uma televisão de ecran largo de acordo com aspectos deste invento e adaptado para funcionamento em exploração horizontal  $2f_H$ .

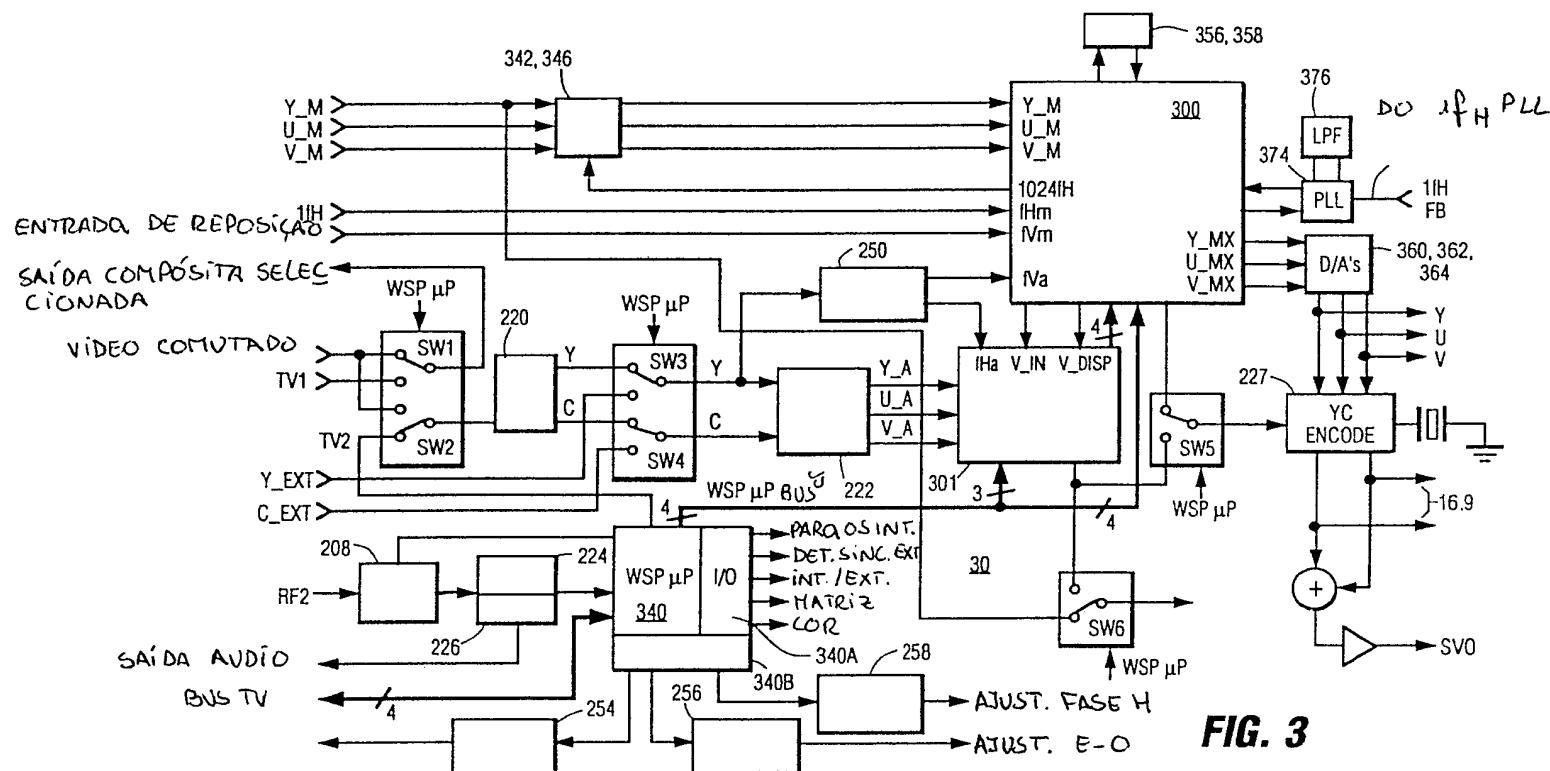

A figura 3 é um diagrama de blocos do processador de ecran largo mostrado na figura 2.

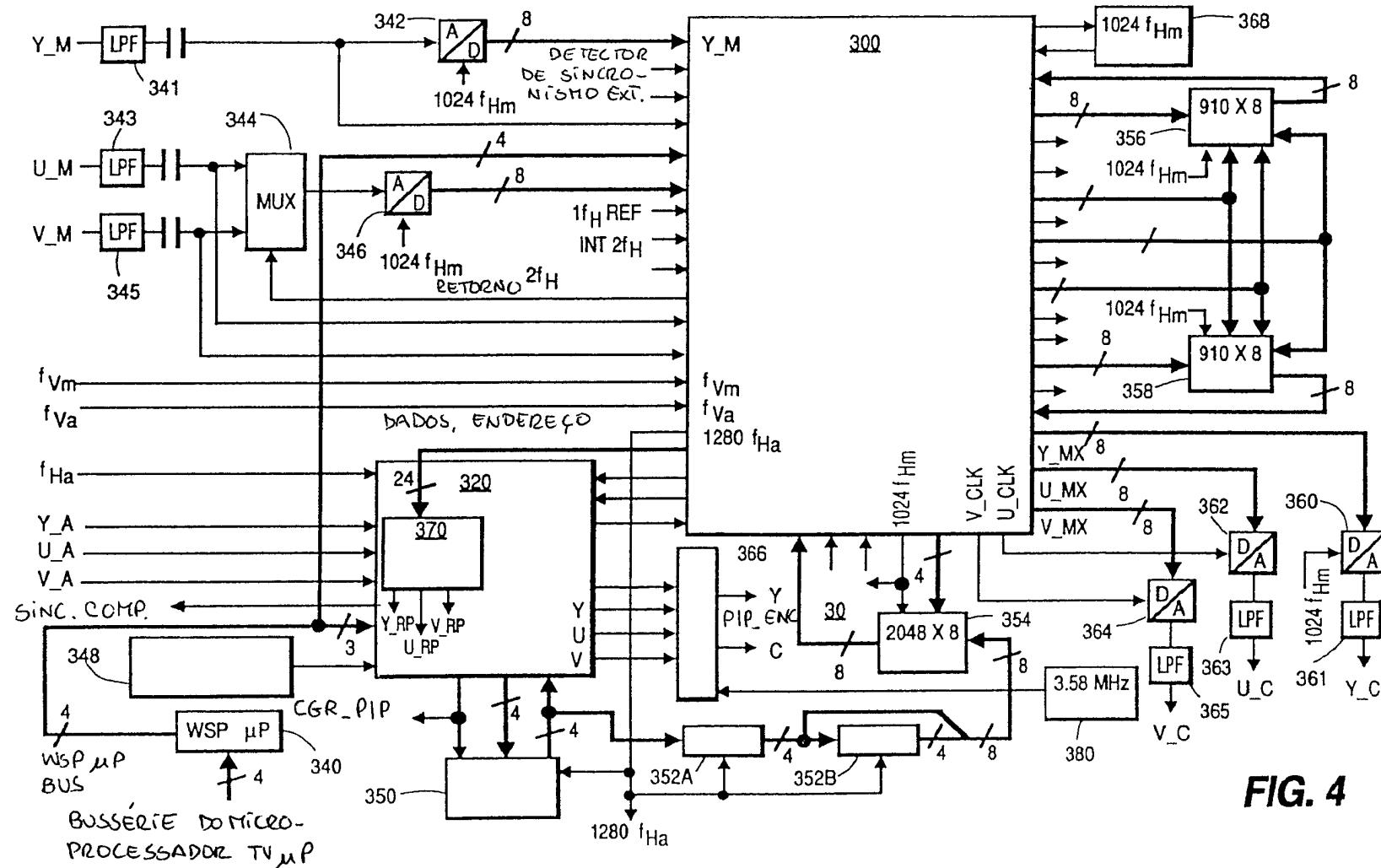

A figura 4 é um diagrama de blocos que mostra detalhes adicionais do processador de ecran largo mostrado na figura 3.

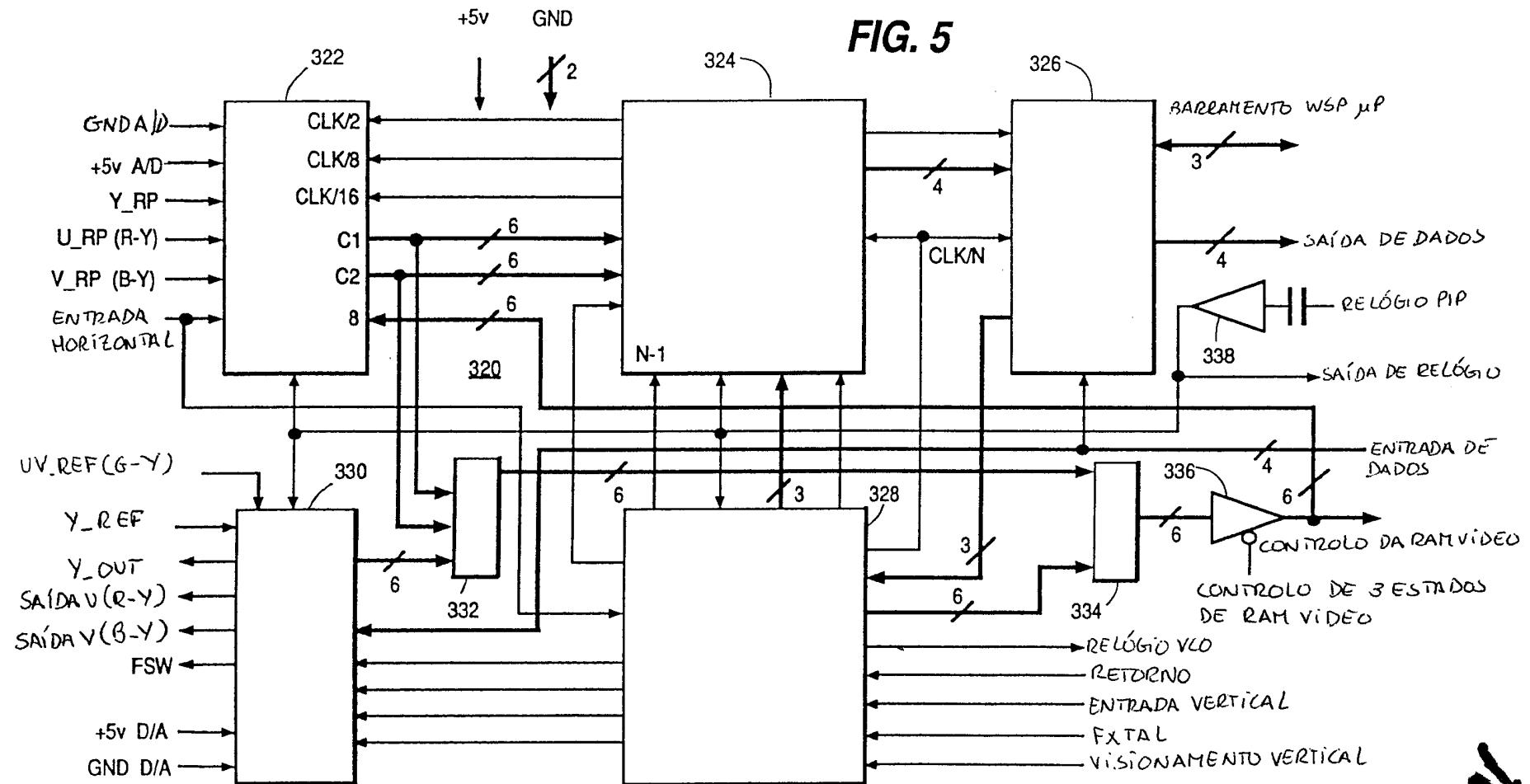

A figura 5 é um diagrama de blocos do processador de imagem em imagem mostrado na figura 4.

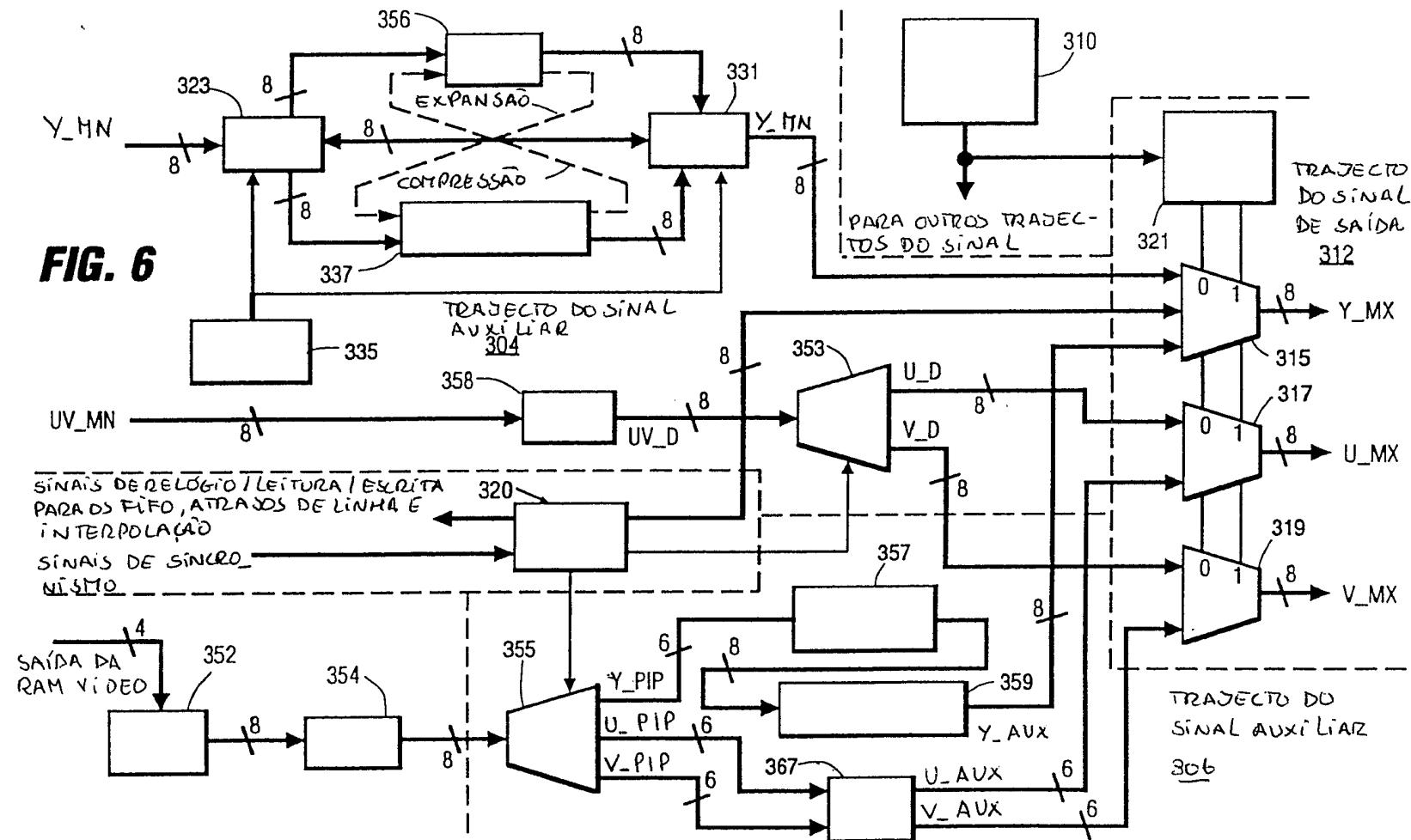

A figura 6 é um diagrama de blocos da disposição de portas mostrada na figura 4 e que ilustra os trajectos de sinal principal, auxiliar e de saída.

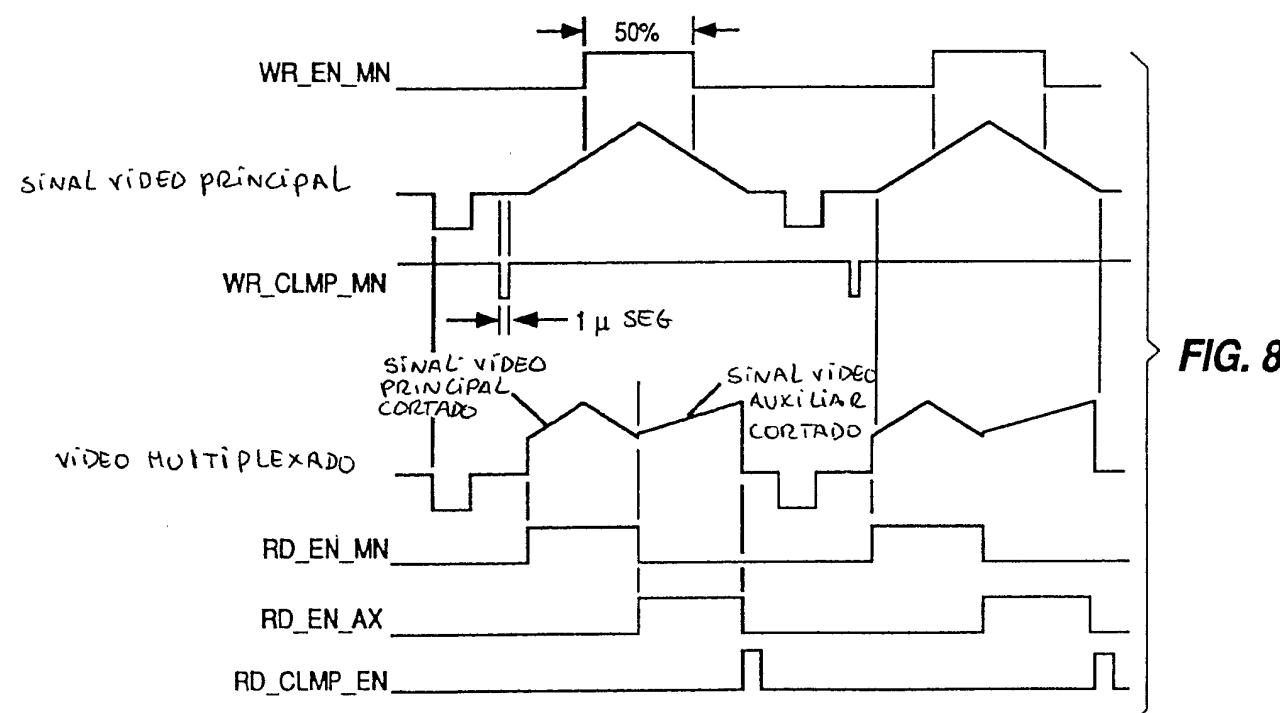

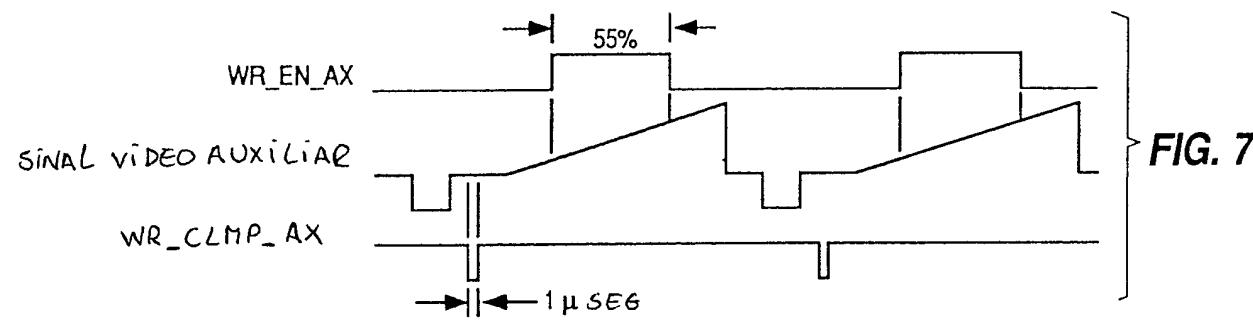

As figuras 7 e 8 são diagramas de temporização úteis para explicar a geração do formato de visionamento mostrado na figura 1(d), utilizando sinais completamente cortados.

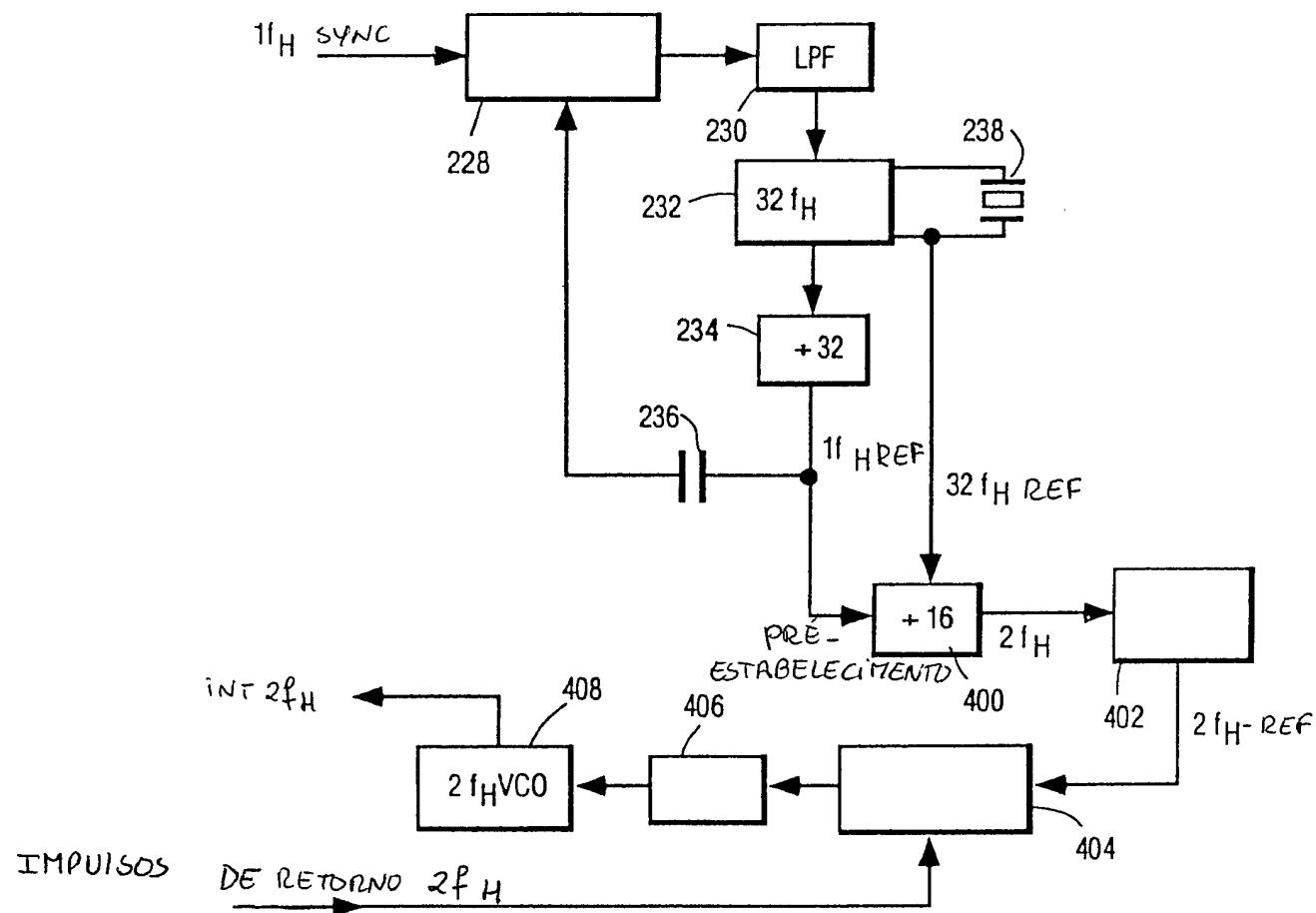

A figura 9 é um diagrama de blocos de um circuito para gerar o sinal interno  $2f_H$  na conversão de  $1f_H$  para  $2f_H$ .

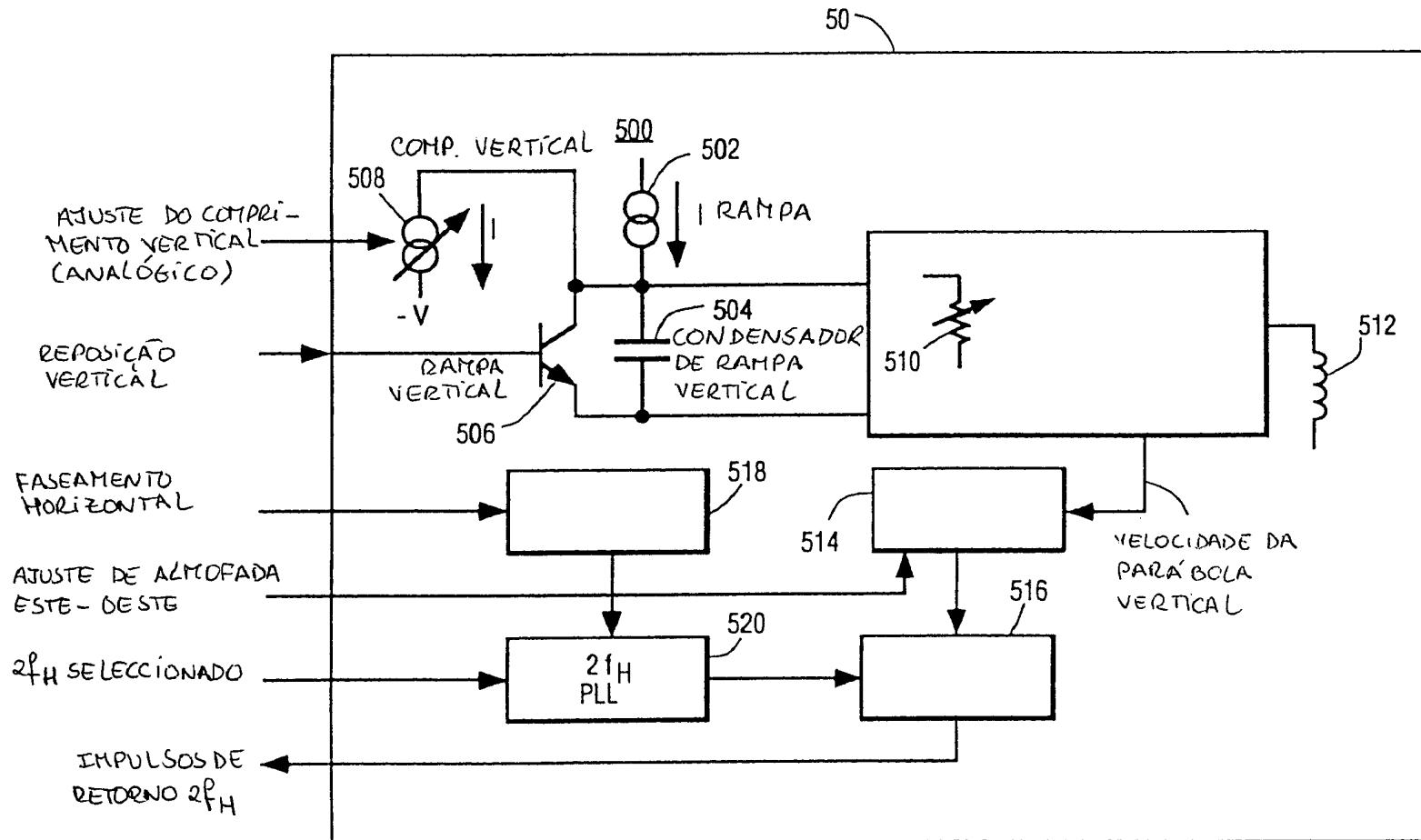

A figura 10 é um bloco de combinação e diagrama do circuito para o circuito de deflexão mostrado na figura 2.

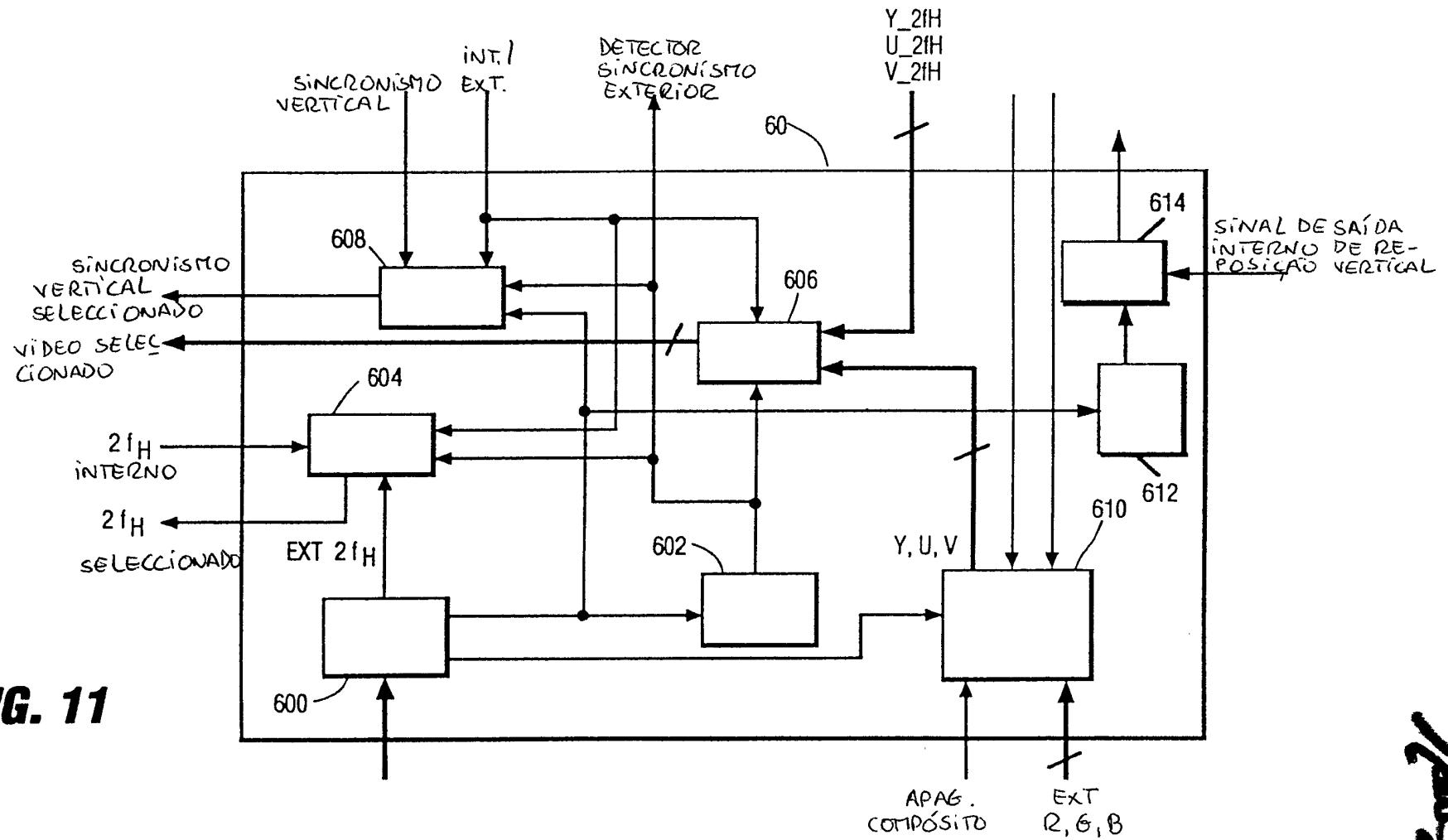

A figura 11 é um diagrama de blocos da interface RGB mostrada na figura 2.

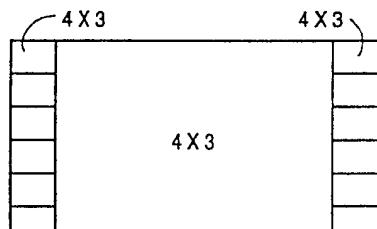

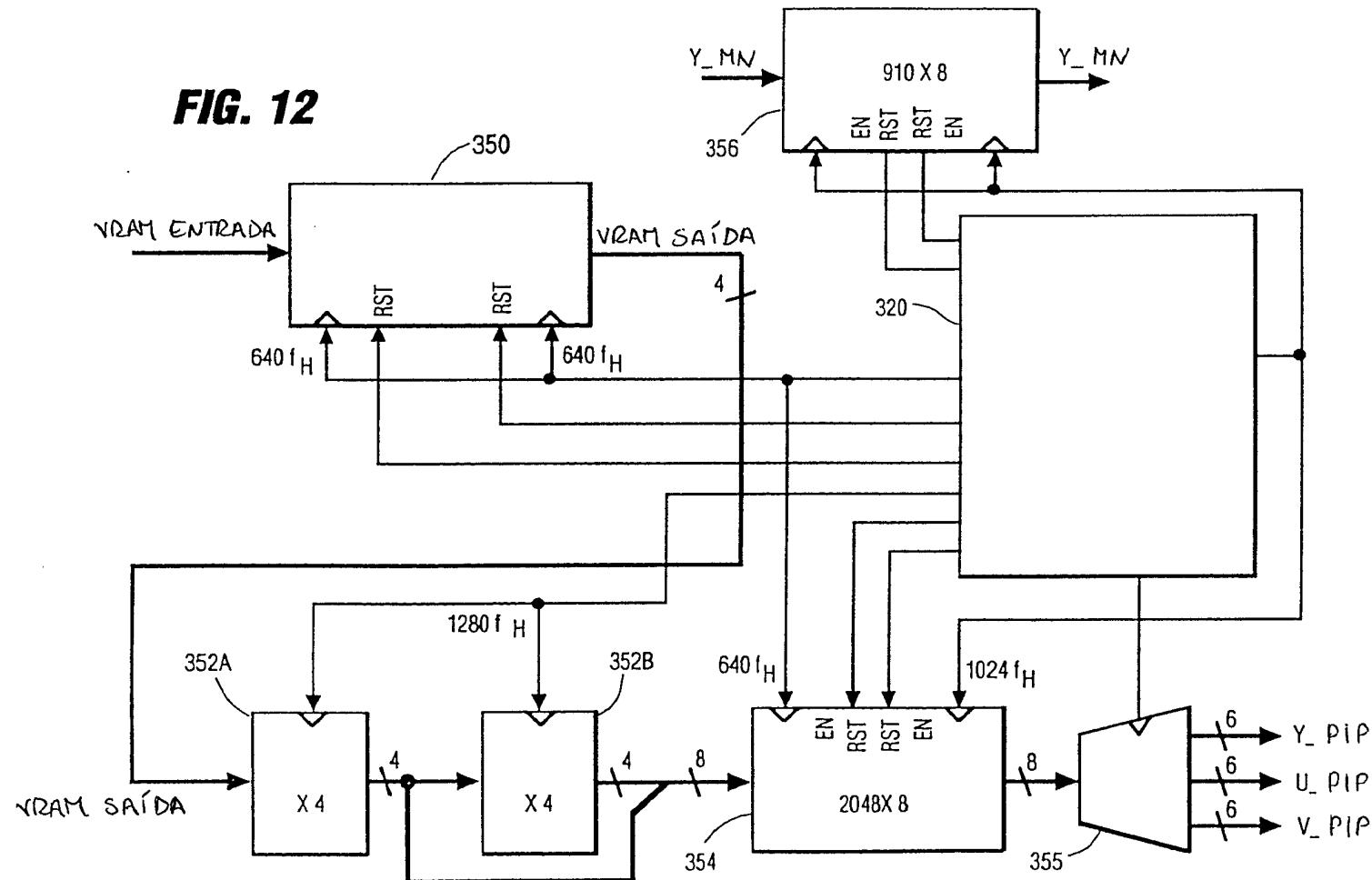

A figura 12 é um diagrama de blocos de uma porção do trajecto do sinal auxiliar mostrado na figura 6.

A figura 13 é um diagrama de uma memória de linha FIFO de cinco linhas útil para explicar a anulação das colisões do ponteiro de leitura/escrita.

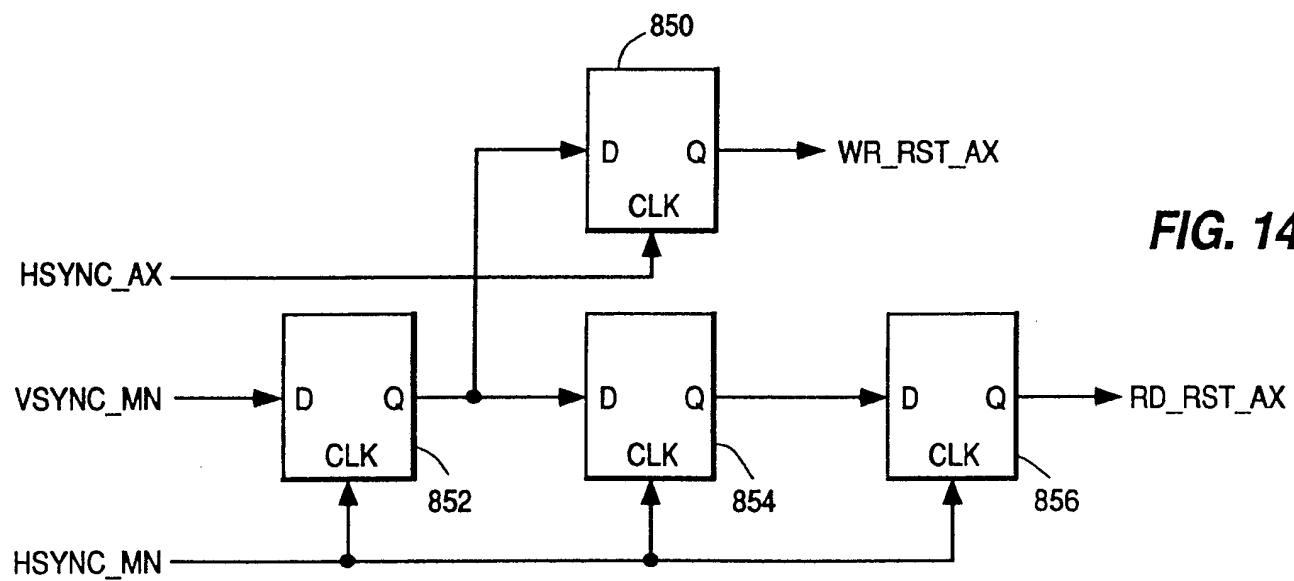

A figura 14 é um diagrama de blocos de um circuito simplificado para implementar um circuito de sincronização de trajecto auxiliar para a disposição de portas.

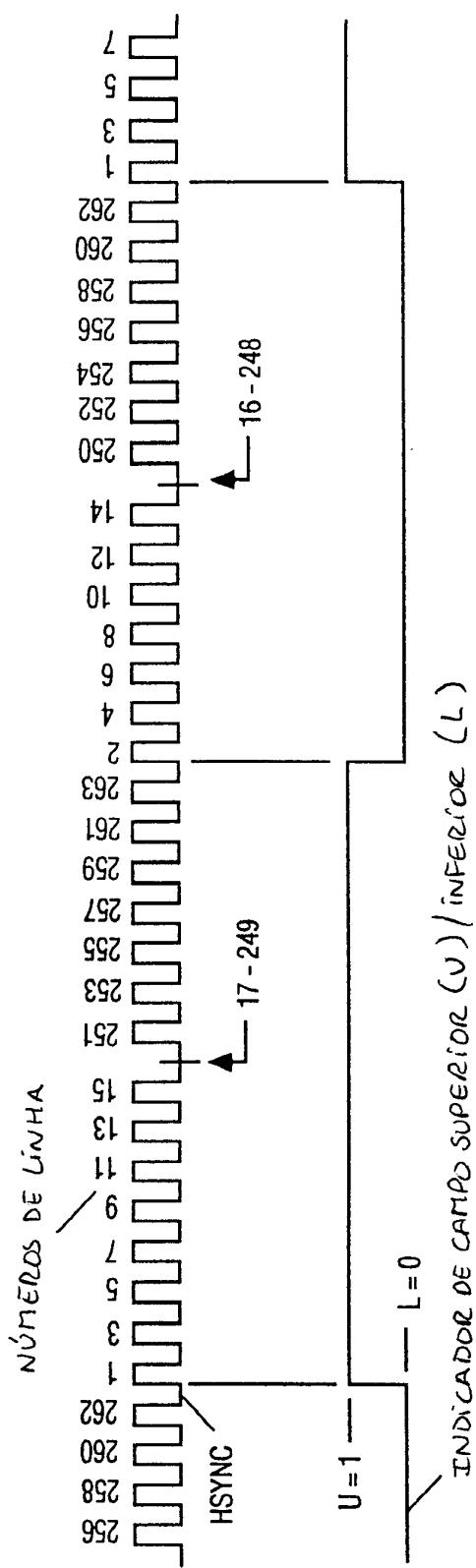

A figura 15 é um diagrama de temporização que ilustra a correspondência de um ponteiro de campo superior/inferior às linhas horizontais de um quadro video.

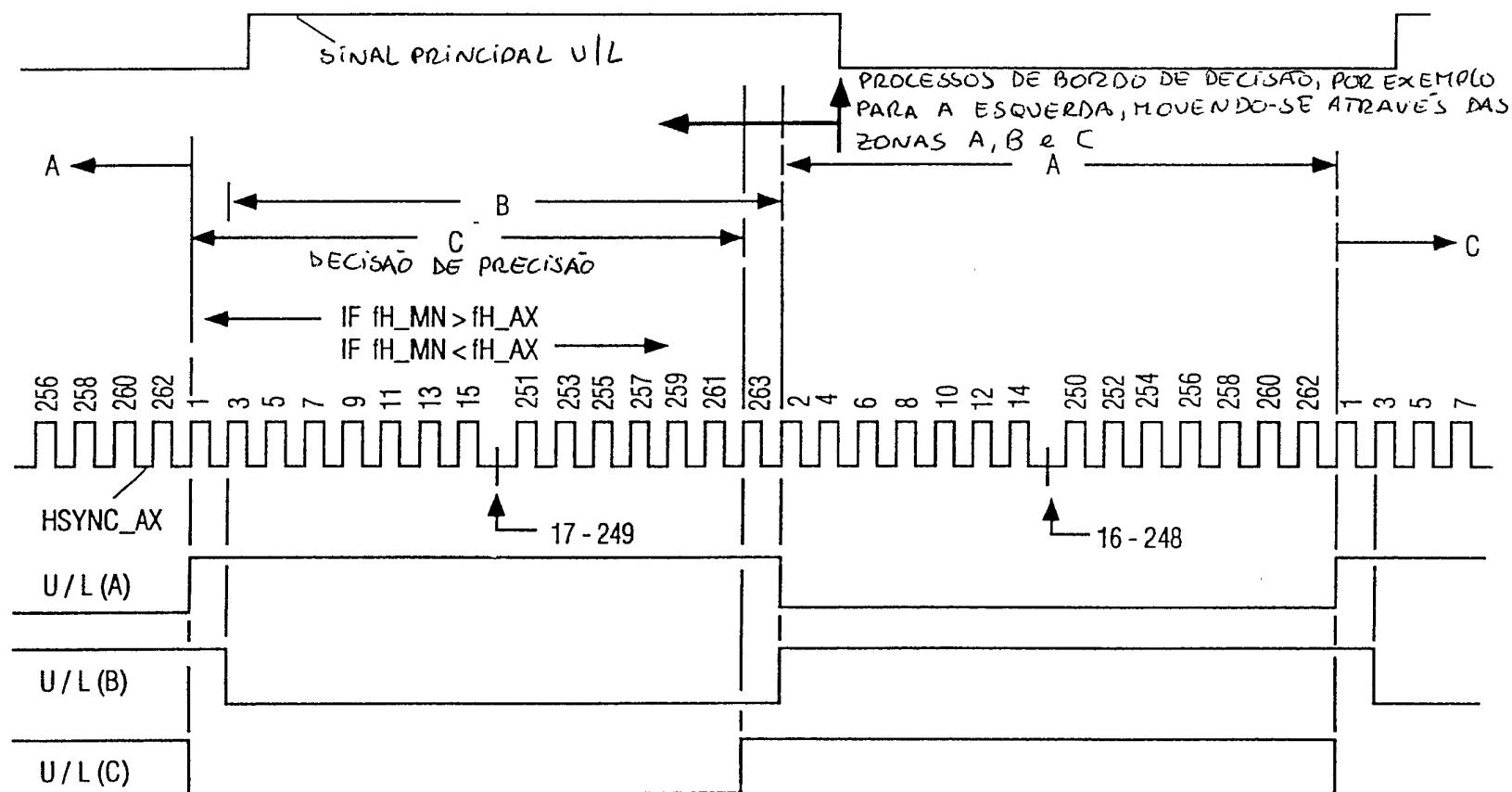

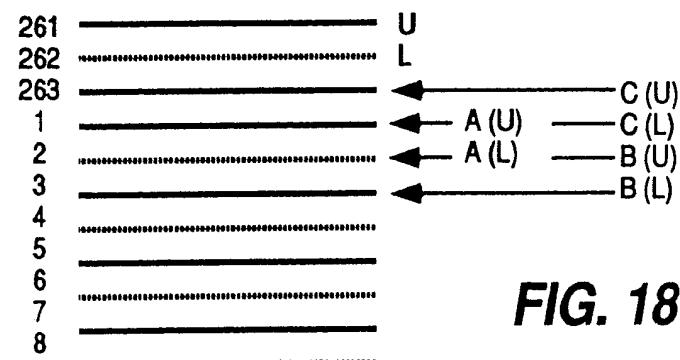

As figuras 16-18 são úteis para explicar um processo para manter a integridade do entrelaçamento para sinais video visionados simultaneamente que exibem precessão relativa.

As várias partes da figura 1 ilustram algumas, mas não todas das várias combinações de formatos de visionamento de imagem simples e múltipla que podem ser implementados de acordo com as diferentes disposições do invento. As seleccionadas para ilustração pretendem facilitar a descrição de circuitos particulares que compreendem televisões de ecrã largo de acordo com as disposições do invento. Para efeitos de conveniência na ilustração e explicação disto, uma relação de formato de visionamento convencional de entre largura e altura para uma fonte video ou sinal é julgado geralmente ser de 16 x 9. As disposições do invento não estão limitadas por estas definições.

A figura 1(a) ilustra uma televisão, de visão directa ou de

projeção, que tem uma relação de formato de visionamento convencional de 4x3. Quando uma imagem de relação de formato de visionamento de 16x9 é transmitida, como um sinal de relação de formato de visionamento de 4x3, aparecem barras pretas no topo e no fundo. Isto é habitualmente referido como formato de letra de forma. Neste caso, a imagem visionada é algum tanto pequena relativamente à área total de visionamento disponível. Alternativamente, a fonte de relação de formato de visionamento de 16x9 é convertida antes da transmissão, de modo a encher a extensão vertical de uma superfície de visionamento de formato de visionamento de 4x3. Contudo, muita informação será cortada a partir dos lados esquerdo e/ou direito. Como uma alternativa adicional, a imagem em letra de forma pode ser expandida verticalmente mas não horizontalmente, pelo que a imagem resultante evidenciará distorção por alongamento vertical. Nenhuma das três alternativas é particularmente atraente.

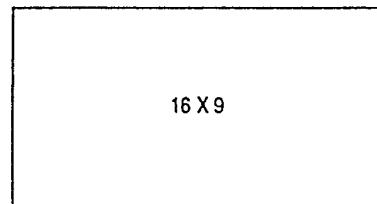

A figura 1(b) mostra um écran 16x9. Uma fonte video de relação de formato de visionamento de 16x9 seria completamente visionada, sem cortes e sem distorção. Uma imagem em letra de forma de relação de formato de visionamento de 16x9, que está ela própria num sinal de relação de formato de visionamento de 4x3, pode ser progressivamente explorada por duplicação de linha ou adição de linha, de modo a fornecer um visionamento maior com suficiente resolução vertical. Uma televisão de écran largo de acordo com este invento pode visionar um tal sinal de relação de formato de visionamento de 16x9 quer a fonte principal, a fonte auxiliar ou uma fonte externa RGB.

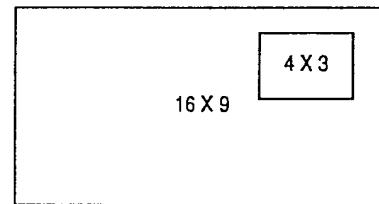

A figura 1(c) ilustra um sinal principal de relação de formato de visionamento de 16x9 em que é visionada uma imagem inserida de relação de formato de visionamento de 4x3. Se ambos os sinais video principal e auxiliar forem fontes de relação de formato de visionamento de 16x9, a imagem inserida pode também ter uma relação de formato de visionamento de 16x9. A imagem inserida pode ser visionada em muitas posições diferentes.

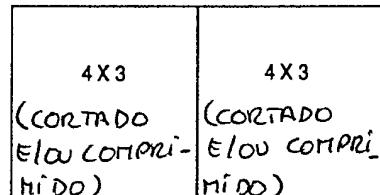

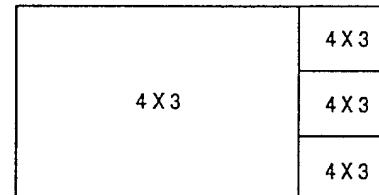

A figura 1(d) ilustra um formato de visionamento, em que os

sinais video principal e auxiliar são visionados com a mesma dimensão de imagem. Cada área de visionamento tem uma relação de formato de visionamento de 8x9, que é certamente diferente de tanto 16x9 como de 4x3. A fim de mostrar uma fonte de relação de formato de visionamento de 4x3 num tal área de visionamento, sem distorção horizontal ou vertical, o sinal deve ser cortado nos lados esquerdo e/ou direito. A maior parte da imagem pode ser mostrada, com menos cortes, se for tolerada alguma distorção da relação de aspecto por compressão da imagem. Compressão horizontal resulta em alongamento vertical dos objectos na imagem. A televisão de ecran largo de acordo com este invento pode fornecer qualquer mistura de corte e distorção da relação de aspecto desde corte máximo sem distorção da relação de aspecto até corte com a máxima distorção da relação de aspecto.

As limitações de amostragem no trajecto de processamento do sinal video auxiliar complicam a geração de uma imagem de alta resolução que é tão grande em dimensão como o visionamento do sinal video principal. Vários processos podem ser desenvolvidos para superar estas complicações.

A figura 1(e) é um formato de visionamento em que uma imagem de relação de formato de visionamento de 4x3 é visionada no centro de um ecran de relação de formato de visionamento de 16x9. Barras escuras são evidentes nos lados direito e esquerdo.

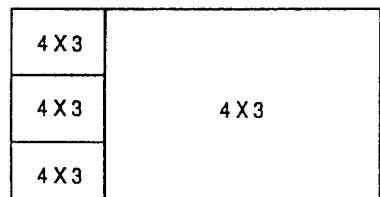

A figura 1(f) ilustra um formato de visionamento em que um imagem grande de relação de formato de visionamento de 4x3 e três imagens mais pequenas de relação de formato de visionamento de 4x3 são visionadas simultaneamente... Uma imagem mais fora do perímetro da imagem grande é referida algumas vezes como um POP, isto é uma imagem fora de imagem, em vez de um PIP, uma imagem em imagem. Os termos PIP ou imagem em imagem são aqui utilizados para ambos os formatos de visionamento. Nas circunstâncias em que a televisão de ecran largo está fornecida com dois sintonizadores, quer ambos internos quer um interno e um externo, por exemplo num gravador de cassetes video, duas das imagens visionadas podem ser visionadas movimento em tempo real de acordo com a fonte. As restantes imagens podem ser visionadas no formato

de quadro de imobilização. Será apreciado que a adição de sintonizadores adicionais e trajectos de processamento adicionais de sinal auxiliar podem fornecer mais do que duas imagens em movimento. Será também apreciado que a imagem grande por um lado, e as três imagens pequenas por outro lado, podem ser comutadas em posição, como mostrado na figura 1(g).

A figura 1(h) ilustra uma alternativa em que a imagem de relação de formato de visionamento de 4x3 está centrada, e seis imagens mais pequenas de relação de formato de visionamento são visionadas em colunas verticais de ambos os lados. Como no formato anteriormente descrito, uma televisão de ecrã largo fornecida com dois sintonizadores pode fornecer duas imagens em movimento. As restantes onze imagens serão no formato de quadro de imobilização.

A figura 1(i) mostra um formato de visionamento que tem uma grelha de doze imagens de relação de formato de visionamento de 4x3. Um tal formato de visionamento é particularmente apropriado para um guia de selecção de canal, em que cada imagem está pelo menos num quadro de imobilização de um canal diferente. Como anteriormente, o número de imagens em movimento dependerá do número de sintonizadores disponíveis e dos trajectos de processamento de sinal.

Os vários formatos mostrados na figura 1 são ilustrativos, e não limitativos, e podem ser implementados por televisões de ecrã largo mostradas nos restantes desenhos e descritos em detalhe mais abaixo.

Um diagrama de blocos global para uma televisão de ecrã largo de acordo com as disposições do invento, e adaptada para funcionar com exploração horizontal  $2f_H$ , está mostrado na figura 2 e designado geralmente por 10. A televisão 10 comprehende geralmente uma secção de entrada de sinais video 20, uma base ou microprocessador TV 216, um processador de ecrã largo 30, um conversor de  $1f_H$  para  $2f_H$  40, um circuito de deflexão 50, uma interface RGB 60, um conversor de YUV para RGB 240, accionadores

de cinescópio 242, tubos de projecção ou de visão directa 244 e um fonte de energia 70. O agrupamento de vários circuitos nos diferentes blocos funcionais é feita para efeitos de conveniência na descrição, e não pretende ser limitativa da posição física relativa de tais circuitos entre si.

A secção de entrada de sinais video 20 está adaptada para receber uma pluralidade de sinais video compostos de diferentes fontes video. Os sinais video podem ser comutados selectivamente para visionamento como sinais video principal e auxiliar. Um comutador RF 204 tem duas entradas de antena ANT1 e ANT2. Estas representam entradas tanto para a recepção via antena aérea como para recepção por cabo. O comutador RF 204 controla que entrada de antena é fornecida a um primeiro sintonizador 206 e a um segundo sintonizador 208. A saída do primeiro sintonizador 206 é uma entrada para uma monopastilha 202, que executa uma pluralidade de funções relativas à sintonia, deflexão horizontal e vertical e controlos video. A monopastilha particular mostrada é do tipo industrialmente designado por TA7730. O sinal video de banda de base VIDEO OUT (saída video) desenvolvido na monopastilha e resultando do sinal do primeiro sintonizador 206 é uma entrada tanto para o comutador video 200 como para a entrada TV1 do processador de écran largo 30. Outras entradas video de banda de base para o comutador video 200 são designadas AUX1 e AUX2. Estas devem ser utilizadas por câmaras video, reprodutores de discos laser, reprodutores de cassetes video, jogos video e similares. A saída do comutador video 200, que é controlada pela base ou microprocessador TV 216 é designado SWITCHED VIDEO (video comutado). O SWITCHED VIDEO é uma outra entrada para o processador de écran largo 30.

Com referência adicional à figura 3, um processador de écran largo de comutador SW1 selecciona entre os sinais TV1 e SWITCHED VIDEO como um sinal video SEL COMP OUT que é uma entrada para um descodificador Y/C 210. O descodificador Y/C 210 pode ser implementado como um filtro pente de linha adaptativo. Duas fontes video adicionais S1 e S2 são também entradas para o descodificador Y/C 210. Cada uma das S1 e S2 representam fontes

diferentes S-VHS, e cada uma consiste de sinais de luminância e crominância separados. Um comutador, que pode ser incorporado como acessório do descodificador Y/C, como em alguns filtros pente de linha adaptativos, ou que podem ser implementados como um comutador separado, responde ao microprocessador 216 para seleccionar um par de sinais de luminância e crominância como saídas designadas por Y\_M e C\_IN respectivamente. O par de sinais de luminância e crominância seleccionados é depois disso considerado o sinal principal e é processado ao longo de um trajecto de sinal principal. As designações de sinal que incluem \_M ou \_MN referem-se ao trajecto de sinal principal. O sinal de crominância C\_IN é redireccionado pelo processador de ecrã largo de volta à monopastilha, para desenvolver diferentes sinais de cor U\_M e V\_M. Relativamente a isto, U é uma designação equivalente para (R-Y) e V é uma designação equivalente para (B-Y). Os sinais Y\_M, U\_M, e V\_M são convertidos para o formato digital no processador de ecrã largo para processamento de sinal ulterior.

O segundo sintonizador 208, definido funcionalmente como acessório do processador de ecrã largo 30, desenvolve um sinal video de banda de base TV2. Um comutador SW2 selecciona entre os sinais TV2 e SWITCHED VIDEO como uma entrada para um descodificador Y/C 220. O descodificador Y/C 220 pode ser implementado como um filtro pente de linha adaptativo. Os comutadores SW3 e SW4 seleccionam entre as saídas de luminância e crominância do descodificador Y/C 220 e os sinais de luminância e crominância de uma fonte video externa, designada por Y\_EXT e C\_EXT respectivamente. Os sinais Y\_EXT e C\_EXT correspondem à entrada S\_VHS S1. O descodificador Y/C 220 e os comutadores SW3 e SW4 podem ser combinados, como em alguns filtros pente de linha adaptativos. A saída dos comutadores SW3 e SW4 é consequentemente considerada o sinal auxiliar e é processado ao longo de um trajecto de sinal auxiliar. A saída de luminância seleccionada é designada Y\_A. As designações de sinal que incluem \_A, \_AX e \_AUX referem-se ao trajecto do sinal auxiliar. A crominância seleccionada é convertida a sinais de diferença de cor U\_A e V\_A. Os sinais Y\_A, U\_A e V\_A são convertidos para o formato digital

para processamento de sinal ulterior. A disposição da fonte de sinal video comutando entre os trajectos de sinal principal e auxiliar maximiza a flexibilidade em gerir a selecção da fonte para partes diferentes dos diferentes formatos de visionamento de imagem.

Um sinal de sincronização composto COMP SYNC, correspondendo ao Y\_M é fornecido pelo processador de ecrã largo para um separador síncrono 212. Os componentes de sincronização horizontal e vertical H e V respectivamente são entradas para um circuito de contagem descendente vertical 214. O circuito de contagem descendente vertical desenvolve um sinal VERTICAL RESET (restabelecimento vertical) que é dirigido para o processador de ecrã largo 30. O processador de ecrã largo gera um sinal de saída de restabelecimento vertical interno INT VERT RST OUT dirigido para a interface RGB 60. Um comutador na interface RGB 60 selecciona entre o sinal de saída de restabelecimento vertical interno e o componente de sincronização vertical da fonte RGB externa. A saída deste comutador é um componente de sincronização vertical seleccionado SEL\_VERT\_SYNC dirigida ao circuito de deflexão 50. Sinais de sincronização horizontal e vertical do sinal video auxiliar são desenvolvidos pelo separador síncrono 250 no processador de ecrã largo.

O conversor de  $1f_H$  para  $2f_H$  40 é responsável por converter sinais video entrelaçado para sinais não entrelaçados progressivamente explorados, por exemplo um em que cada linha horizontal é visionado duas vezes, ou um conjunto adicional de linhas horizontais é gerado interpolando-se linhas horizontais adjacentes do mesmo campo. Em alguns casos, a utilização de uma linha anterior ou a utilização de uma linha interpolada dependerá do nível de movimento que é detectado entre campos adjacentes ou quadros. O circuito conversor 40 funciona em conjunção com uma RAM video 420. A RAM video pode ser utilizada para armazenar um ou mais campos de um quadro, para possibilitar o visionamento progressivo. Os dados video convertidos como sinais  $Y_{2f_H}$ ,  $U_{2f_H}$  e  $V_{2f_H}$  são fornecidos à interface RGB 60.

A interface RGB 60, mostrada em maior detalhe na figura 11, possibilita a selecção dos dados video convertidos ou dados video RGB externos para visionamento pela secção de entrada dos sinais video. O sinal RGB externo é julgado ser um sinal de relação de formato de visionamento largo adaptado para exploração  $2f_H$ . A componente de sincronização vertical do sinal principal é fornecido à interface RGB pelo processador de ecrã largo como INT VERT RST OUT, possibilitando um sincronismo vertical seleccionado ( $f_{V_m}$  ou  $f_{V_{ext}}$ ) para estar disponível ao circuito de deflexão 50. O funcionamento da televisão de ecrã largo possibilita a selecção pelo utilizador de um sinal RGB externo, gerando-se um sinal de controlo interno/externo INT/EXT. Contudo, a selecção de uma entrada de sinal RGB externo, na ausência de um tal sinal, pode resultar num colapso vertical do quadro, e danos no tubo de raios catódicos ou tubos de projecção. Consequentemente, o circuito interface RGB detecta um sinal de sincronização externo, a fim de cancelar a selecção de uma entrada externa RGB não existente. O microprocessador WSP  $\mu$ P 340 fornece também controlos de cor e matiz para o sinal RGB externo.

O processador de ecrã largo 30 comprehende um processador de imagem em imagem 320 para processamento de sinal especial do sinal video auxiliar. O termo imagem em imagem é algumas vezes abreviado como PIP ou pix-in-pix. Um disposição de portas 300 combina dados de sinal video principal e auxiliar numa variedade larga de formatos de visionamento, como mostrado pelos exemplos das figuras 1(b) a 1(i). O processador de imagem em imagem 320 e um disposição de portas 300 estão sob controlo de um microprocessador de ecrã largo (WSP  $\mu$ P) 340. O microprocessador 340 responde ao microprocessador TV 216 sobre um bus série. O bus série inclui quatro linhas de sinal, para dados, sinais relógio, possibilidades de sinais e sinais de restabelecimento. O processador de ecrã largo 30 gera também um sinal de apagamento/restabelecimento vertical composto, como um sinal castelo de areia de três níveis. Alternativamente, os sinais de apagamento vertical e restabelecimento podem ser gerados como sinais separados. Um sinal de apagamento composto é fornecido pela secção de entrada do sinal video à interface RGB.

O circuito de deflexão 50, mostrado em maior detalhe na figura 10, recebe um sinal de restabelecimento vertical do processador de ecrã largo, um sinal de sincronização horizontal  $2f_H$  seleccionado da interface RGB 60 e sinais de controlo adicionais do processador de ecrã largo. Estes sinais de controlo adicionais referem-se ao faseamento horizontal, ajustamento da dimensão vertical e ajustamento do pino este-oeste.. O circuito de deflexão 50 fornece impulsos de retorno  $2f_H$  ao processador de ecrã largo 30, o conversor de  $1f_H$  para  $2f_H$  40 e o conversor de YUV para RGB 240.

As tensões de funcionamento para toda a televisão de ecrã largo são gerados por um fonte de energia 70 que pode ser alimentada por um fonte principal CA (corrente alternada).

O processador de ecrã largo 30 está mostrado em maior detalhe na figura 3. Os componentes principais do processador de ecrã largo são um disposição de portas 300, um circuito de imagem em imagem 301, conversores de analógico para digital e digital para analógico, o segundo sintonizador 208, um microprocessador processador de ecrã largo 340 e um codificador de saída de ecrã largo 227. Detalhes adicionais do processador de ecrã largo estão mostrados na figura 4. Um processador de imagem em imagem 320, que constitui uma parte significativa do circuito PIP 301, está mostrado em maior detalhe na figura 5. A disposição de portas 300 está mostrada em maior detalhe na figura 6. Uma pluralidade de componentes mostrado na figura 3 já foram descritos em detalhe.

O segundo sintonizador 208 tem a ele associados um andar IF 224 e um andar audio 226. O segundo sintonizador 208 funciona também em conjunção com o WSP  $\mu$ P 340. O WSP  $\mu$ P 340 comprehende uma secção de entrada saída I/O 340A e uma secção de saída analógica 340B. A secção I/O 340A fornece sinais de controlo de cor e matiz, o sinal INT/EXT para seleccionar a fonte video RGB externa e sinais de controlo para os comutadores de SW1 a SW6. A secção I/O controla também o sinal EXT SYNC DDET da interface RGB para proteger o circuito de deflexão e o tubo(s) de raios

catódicos. A secção de saída analógica 340B fornece sinais de controlo para a dimensão vertical, ajuste este-oeste e fase horizontal, através dos respectivos circuitos de interface 254, 256 e 258.

A disposição de portas 300 é responsável por combinar a informação video dos trajectos de sinal principal e auxiliar para implementar um visionamento de ecrã largo composto, por exemplo, um dos mostrados nas diferentes partes da figura 1. A informação de relógio para a disposição de portas é fornecida pelo circuito fechado de bloqueio de fase 374, que funciona em conjunção com o filtro de passagem de baixas frequências 376. O sinal video principal é fornecido ao processador de ecrã largo no formato analógico, e no formato Y U V, como sinais designados por Y\_M, U\_M e V\_M. Estes sinais principais são convertidos do formato analógico para o digital pelos conversores de analógico para digital 342 e 346, mostrados em maior detalhe na figura 4.

Os sinais da componente de cor são referidos pelas designações genéricas de U e V, que podem ser atribuídas a quer aos sinais R-Y ou B-Y, quer aos sinais I e Q. A largura de banda da luminância amostrada está limitada a 8 MHz porque a frequência do relógio do dispositivo é de  $1024f_H$ , que é aproximadamente de 16 MHz. Um conversor simples de analógico para digital e um comutador analógico podem ser utilizados para amostrar os dados do componente de cor porque os sinais U e V estão limitados a 500 kHz, ou 1,5 MHz para a largura I. A linha seleccionada UV\_MUX para o comutador analógico, ou dispositivo de multiplexação 344, é um sinal de 8 MHz derivado dividindo-se o relógio do dispositivo por 2. Um início largo do mono relógio do impulso de linha SOL restabelece sincronizadamente este sinal para zero no começo de cada linha video horizontal. A linha UV\_MUX que oscila em estado cada ciclo de relógio através da linha horizontal. Visto que o comprimento da linha é um número ímpar de ciclos de relógio, o estado do UV\_MUX, uma vez iniciado, oscilará consistentemente 0, 1, 0, 1, ..., sem interrupção. Os fluxos de dados Y e UV fora dos conversores de analógico para digital 324 e 346 são deslocados porque cada um dos conversores de analógico

para digital têm 1 ciclo de relógio de atraso. A fim de se acomodar a esta mudança de dados, a informação de acesso de relógio do trajecto de processamento do sinal principal 304 deve ser atrasada de maneira semelhante. Onde a informação da acesso de relógio não é atrasada, os dados UV não serão correctamente emparelhados quando apagados. Isto é importante porque cada par UV representa um vector. Um elemento U de um vector não pode ser emparelhado com um elemento V de um outro vector sem originar uma mudança de cor. Em vez disso, uma amostra V de um par anterior será apagado juntamente com a amostra de corrente U. Este processo de multiplexação UV é referido como 2:1:1, visto haver duas amostras de luminância para cada par de componentes de cor (U, V). A frequência Nyquist tanto para U como para V é efectivamente reduzida para metade da frequência Nyquist da luminância. Consequentemente a frequência Nyquist da saída do conversor de analógico para digital para o componente de luminância é 8 MHz, ao passo que a frequência Nyquist da saída do conversor de analógico para digital para os componentes de cor é de 4 MHz.

O circuito PIP e/ou a disposição de portas pode incluir também meios para aumentar a resolução dos dados auxiliares não obstante a compressão de dados. Foram desenvolvidas uma pluralidade de esquemas de redução de dados e recuperação de dados, incluindo por exemplo compressão de pixels emparelhados e excitação e não excitação. Além do mais, são contempladas sequências diferentes de excitação envolvendo diferentes números de bits e diferentes compressões de pixel emparelhado envolvendo diferentes números de bits. Um de uma pluralidade de esquemas de redução e restauração de dados particular pode ser seleccionada pelo WSP  $\mu$ P 340 a fim de maximizar a resolução do video visionado para cada tipo particular de formato de visionamento de imagem.

A disposição de portas inclui interpoladores que funcionam em conjunção com memórias de linha, que podem ser implementadas como os FIFO 356 e 358. O interpolador e as FIFO são utilizados para reamostrar o sinal principal como desejado. Um interpolador

adicional pode reamostrar o sinal auxiliar. Circuitos de relógio e sincronização na disposição de portas controlam a manipulação de dados de ambos os sinais principal e auxiliar, incluindo a sua combinação num único sinal video de saída que tem componentes Y\_MX, U\_MX e V\_MX. Estes componentes de saída são convertidos para o formato analógico pelos conversores de analógico para digital 360, 362 e 364. Os sinais de formato analógico, designados Y, U e V, são fornecidos ao conversor de  $1f_H$  para  $2f_H$  40 para conversão para exploração não entrelaçado. Os sinais Y, U, e V são também codificados para o formato Y/C pelo codificador 227 para definir um sinal de saída de relação de formato largo Y\_OUT\_EXT/C\_OUT\_EXT disponível no painel das tomadas. O comutador SW5 selecciona um sinal de sincronização para o codificador 227 a partir quer da disposição de portas, C\_SYNC\_MN, quer a partir do circuito PIP, C\_SYNC\_AUX.

O comutador SW6 selecciona entre Y\_M e C\_SYNC\_AUX como sinal de sincronização para a saída de painel de ecrã largo.

Porções do circuito de sincronização horizontal estão mostradas em maior detalhe na figura 9. O comparador de fase 228 é um acessório de um circuito fechado de bloqueio de fase que inclui um filtro de passagem de baixas frequências 230, o oscilador de tensão controlada 232, o divisor 234 e o condensador 236. O oscilador de tensão controlada 232 funciona a  $32f_H$ , responsável a um ressonador cerâmico ou algo semelhante 238. A saída do oscilador de tensão controlada é dividido por 32 para fornecer um segundo sinal de entrada de frequência própria ao comparador de fase 228. A saída do divisor 234 é um sinal de temporização REF  $1f_H$ . Os sinais REF  $32f_H$  e  $1f_H$  são fornecidos a um contador 400 dividido por 16. Uma saída  $2f_H$  é fornecida a um circuito de largura de impulso 402. Preajustando o divisor 400 pelo sinal REF  $1f_H$  assegura que o divisor funciona sincronizadamente com o circuito fechado de bloqueio de fase da secção de entrada dos sinais video. O circuito de largura de impulso 402 assegura que um sinal REF  $2f_H$  terá uma largura de impulso adequada para assegurar o funcionamento apropriado do comparador de fase 404, por exemplo um do tipo CA1391, que

constitui parte de segundo circuito fechado de bloqueio de fase que inclui um filtro de passagem de baixas frequências 406 e o oscilador de tensão controlada 408. O oscilador de tensão controlada 408 gera um sinal de temporização interno  $2f_H$ , o qual é utilizado para accionar o visionamento progressivamente explorado. O outro sinal de entrada para o comparador de fase 404 são os impulsos de retorno  $2f_H$  ou um sinal de temporização a ele referido. A utilização do segundo circuito fechado de bloqueio de fase que inclui o comparador de fase 404 é útil para assegurar que cada período de exploração  $2f_H$  é simétrico dentro de cada período  $1f_H$  do sinal de entrada. Caso contrário, o visor pode exibir uma separação do quadro, por exemplo, em que metade das linhas video são deslocadas para a direita e metade das linhas video são deslocadas para a esquerda.

O circuito de deflexão 50 está mostrado em maior detalhe na figura 10. Um circuito 500 é fornecido para ajustar a dimensão vertical do quadro, de acordo com a quantidade desejada de sobreexploração vertical necessário para implementar diferentes formatos de visionamento. Como ilustrado diagramaticamente, uma fonte de corrente constante 502 fornece uma quantidade constante de corrente  $I_{RAMP}$  que carrega um condensador em rampa vertical 504. Um transístor 506 está acoplado em paralelo ao condensador em rampa, e descarrega periodicamente o condensador responsivo ao sinal de restabelecimento vertical. Na ausência de qualquer ajustamento, a corrente  $I_{RAMP}$  fornece a dimensão vertical máxima disponível para o quadro. Isto pode corresponder à extensão do sobreexploração necessário para encher o visionamento de ecran largo por uma fonte expandida de sinal de relação de formato de visionamento de 4x3, como mostrado na figura 1(a). Para as extensões em que é necessário menor dimensão vertical do quadro, uma fonte de corrente ajustável 508 desvia uma quantidade variável de corrente  $I_{ADJ}$  da  $I_{RAMP}$ , para que o condensador em rampa 504 carregue mais lentamente e para um valor de pico menor. A fonte de corrente variável 508 responde a um sinal de ajuste da dimensão vertical, por exemplo no formato analógico, gerado por um circuito de controlo de dimensão vertical. O ajustamento da dimensão vertical 500 é independente de um ajustamento manual da

dimensão vertical 510, o qual pode ser implementado por um potenciómetro ou botão de ajustamento do painel posterior. Em qualquer caso, a bobina(s) de deflexão vertical 512 recebe(m) corrente de accionamento da grandeza apropriada. A deflexão horizontal é fornecida pelo circuito de ajustamento de fase 518, circuito de correcção do pino este-oeste 514, um circuito fechado de bloqueio de fase  $2f_H$  520 e circuito de saída horizontal 516.

O circuito interface RGB 60 está mostrado em maior detalhe na figura 11. O sinal que está para ser enfim visionado será seleccionado entre a saída do conversor de  $1f_H$  para  $2f_H$  40 e uma entrada RGB externa. Para efeitos da televisão de ecrã largo aqui descrita, a entrada RGB externa é presumida ser de uma fonte progressivamente explorada, de relação de formato de visionamento largo. Os sinais RGB externos e um sinal de apagamento composto da secção de entrada dos sinais video 20 são entradas para um conversor de RGB para Y U V 610. O sinal de sincronização composto externo  $2f_H$  para o sinal RGB externo é uma entrada para o separador de sinal de sincronização externo 600. A selecção do sinal de sincronização vertical é implementada pelo comutador 608. A selecção do sinal de sincronização horizontal é implementado pelo comutador 604. A selecção do sinal video é implementado pelo comutador 606. Cada um dos comutadores 604, 606 e 608 é responsivo a um sinal de controlo interno/externo gerado pelo WSP  $\mu$ P 340. A selecção das fontes video internas ou externas é uma selecção do utilizador. Contudo, se um utilizador selecciona inadvertidamente uma fonte RGB externa, quando nenhuma de tal fonte está ligada ou conectada, ou se a fonte externa cai, o quadro vertical colapsará, e podem resultar danos sérios ao tubo(s) de raios catódicos. Consequentemente, um detector de sincronização externo 602 verifica a presença de um sinal de sincronização externo. Na ausência de um tal sinal, um sinal de controlo de cancelamento da comutação é transmitido a cada um dos comutadores 604, 606 e 608, para evitar a selecção da fonte RGB externa se o sinal daquilo não está presente. O conversor de RGB para YUV 610 recebe também sinais de controlo de matiz e cor do WSP  $\mu$ P 340.

A figura 4 é um diagrama de blocos que mostra detalhes adicionais do processador de ecran largo 30 mostrado na figura 3. Os sinais Y\_A, U\_A e V\_A são uma entrada para o processador de imagem em imagem 320, que pode incluir um circuito de processamento de resolução 370. A televisão de ecran largo de acordo com aspectos deste invento pode expandir e comprimir video. Os efeitos especiais caracterizados pelos vários formatos de visionamento compostos ilustrados em parte na figura 1 são gerados pelos processador de imagem em imagem 320, que pode receber sinais de dados processados de resolução Y\_RP, U\_RP e V\_RP do circuito de processamento de resolução 370. O processamento de resolução não necessita de ser utilizado todas as vezes, mas durante formatos de visionamento seleccionados. O processador de imagem em imagem 320 está mostrado em maior detalhe na figura 5. Os componentes principais do processador de imagem em imagem são uma secção do conversor de analógico para digital 322, uma secção de entrada 324, uma secção colectora de comutação rápida (FSW) 326, uma secção de controlo e temporização 328 e uma secção do conversor de digital para analógico 330.

O processador de imagem em imagem 320 pode ser caracterizado como uma variação melhorada de um pastilha básica CPIP desenvolvida por Thomson Consumer Electronics, Inc. A pastilha básica CPIP está descrita mais detalhadamente numa publicação intitulada "The CTC 140 Picture in Picture (CPIP) Technical Training Manual", da Thomson Consumer Electronics, Inc., Indianapolis, Indiana. São possíveis uma pluralidade de características especiais ou efeitos especiais, sendo ilustrativos os seguintes. O efeito especial básico é uma imagem grande tendo uma imagem pequena sobrepondo uma sua porção como mostrado na figura 1(c). As imagens grande e pequena podem resultar do mesmo sinal video, de sinais video diferentes e podem ser alternados ou permutados. Geralmente falando, o sinal audio é comutado para corresponder sempre à imagem grande. A imagem pequena pode ser movida para qualquer posição sobre o ecran ou pode andar através de um número de posições predeterminadas. Uma característica de ampliação aumenta e diminui a dimensão da imagem pequena, por exemplo para uma

qualquer de uma pluralidade de dimensões preajustadas. Em algum ponto, por exemplo o formato de visionamento mostrado na figura 1(d), as imagens grande e pequena são de facto da mesma dimensão.

Num modo de imagem simples, por exemplo a mostrada nas figuras 1(b), 1(e) ou 1(f) um utilizador pode ampliar o conteúdo da imagem simples, por exemplo, em passos de uma relação de 1,0:1 a 5,0:1. Embora no modo de ampliação um utilizador possa procurar ou tornar panorâmico através do conteúdo da imagem possibilitando mover a imagem do ecrã através de diferentes zonas da imagem. Em ambos os casos, quer a imagem pequena ou a imagem grande quer a imagem ampliada podem ser visionadas no quadro de imobilização (ainda no formato de imagem). Esta função possibilita um formato estroboscópico, em que os últimos nove quadros de video podem ser repetidos sobre o ecrã. A frequência de repetição do quadro pode ser alterada de trinta quadros por segundo para zero quadros por segundo.

O processador de imagem em imagem utilizado na televisão de ecrã largo de acordo com uma outra disposição do invento difere da presente configuração da pastilha básica CPIP acima descrita. Se a pastilha básica CPIP for utilizada por uma televisão que tem um ecrã de 16x9, e sem um circuito de aceleração video, as imagens inseridas exibiriam distorção da relação de aspecto, devido à expansão horizontal efectiva de 4/3 vezes resultante da exploração através do ecrã mais largo de 16x9. Os objectos na imagem seriam alongados horizontalmente. Se um circuito de aceleração externo for utilizado, não haveria distorção da relação de aspecto, mas a imagem não encheria todo o ecrã.

Os processadores de imagem em imagem existentes baseados na pastilha básica CPIP como utilizada nas televisões convencionais são operadas de uma maneira particular que tem certas consequências indesejáveis. O video de entrada é amostrado por um relógio  $640f_H$  que está bloqueado para o sinal de sincronização horizontal da fonte video principal. Por outras palavras, os dados armazenados na RAM video associada com a pastilha CPIP é amostrada não perpendicularmente relativamente à fonte video

auxiliar de entrada. Isto é uma limitação fundamental no processo de pastilha básica CPIP da sincronização de campo. A natureza não perpendicular da frequência de amostragem de entrada resulta em erros de inclinação dos dados amostrados. A limitação é um resultado da RAM video utilizada com a pastilha CPIP, que deve utilizar o mesmo relógio para escrever e ler dados. Quando os dados da RAM video, tal como da RAM video 350, são visionados, os erros de inclinação são vistos como agitação aleatória ao longo dos bordos verticais da imagem e são geralmente considerados sujeitos a bastantes objecções.

O processador de imagem em imagem 320, de acordo com uma disposição do invento e diferente da pastilha básica CPIP, é adaptado para comprimir assimetricamente os dados video num de uma pluralidade de modos de visionamento seleccionáveis. Neste modo de funcionamento, as imagens são comprimidas 4:1 na direcção horizontal e 3:1 na direcção vertical. Este modo assimétrico de compressão produz imagens de relação de aspecto distorcidas para armazenamento na RAM video. Objectos nas imagens são comprimidos horizontalmente. Contudo, se estas imagens são lidas normalmente, como por exemplo no modo de exploração de canal, para visionamento de um ecrã de relação de formato de visionamento de 16x9, as imagens parecem correctas. A imagem enche o ecrã e não há distorção da relação de aspecto. O modo de compressão assimétrica de acordo com este aspecto do invento torna possível gerar formatos de visionamento especiais num ecrã de 116x9 sem o conjunto de circuitos de aceleração.

Nos modos de ecrã cheio PIP, o processador de imagem em imagem, em conjunção com um oscilador de curso livre 348 tomará a entrada Y/C de um descodificador, por exemplo um filtro pente de linha adaptativo, descodificam o sinal nos componentes de cor Y, U, V e geram impulsos de sincronismo horizontal e vertical. Estes sinais são processados no processador de imagem em imagem para os vários modos de ecrã cheio tal como ampliação, imobilização e exploração de canal. Durante o modo de exploração de canal, por exemplo, o sincronismo horizontal e vertical presentes a partir da secção de entrada dos sinais video terá muitas

~~CONFIDENTIAL~~

discontinuidades porque os sinais amostrados (diferentes canais) terão impulsos de sincronismos não referidos e serão comutados em momentos aleatórios no tempo convenientes. Além disso o relógio de amostra (e relógio de RAM video de leitura/escrita) é determinado pelo oscilador de curso livre. Para modos de imobilização e ampliação, o relógio de amostra estará bloqueado para sincronismo horizontal video de entrada, que nestes casos especiais é o mesmo que a frequência do relógio de visionamento.

Referindo outra vez a figura 4, as saídas Y, U, V e C\_SYNC (sincronismo composto) do processador de imagem em imagem no formato analógico podem ser recodificadas em componentes Y/C pelo circuito de codificação 366, que funciona em conjunção com um oscilador de 3,58 MHz 380. Este sinal Y/C\_PIP\_ENC pode ser ligado a um comutador Y/C, não mostrado, que possibilita aos componentes Y/C recodificados serem substituídos pelos componentes Y/C do sinal principal. A partir deste ponto, os sinais PIP codificados Y, U, V e de sincronismo seriam a base para a temporização horizontal e vertical no resto da base. Este modo de funcionamento é apropriado para implementar um modo de ampliação para o PIP baseado no funcionamento do interpolador e da FIFO no trajecto de sinal principal.

Além disso, com referência à figura 5, o processador de imagem em imagem 320 comprehende a secção de conversão de analógico para digital 322, a secção de entrada 324, a secção de comutação rápida FSW e de controlo de bus 326, a secção de temporização e controlo 328 e a secção de conversão de digital para analógico 330. Geralmente, o processador de imagem em imagem 320 digitaliza o sinal video em sinais de luminância e de diferença de cor (U, V), subamostrando e armazenando os resultados numa RAM video de 1 megabit 350 como acima explicado. A RAM video 350 associada ao processador de imagem em imagem 320 tem uma capacidade de memória de 1 megabit, que não é suficientemente grande para armazenar um campo completo de dados video com amostras de 8 bits. Capacidade de memória aumentada tende a ser cara e pode necessitar de um conjunto de circuitos de gestão mais complexo. O menor número de bits por amostra no canal

auxiliar representa uma redução na resolução da quantificação, ou largura de banda, relativa ao sinal principal, que é processado inteiramente com amostras de 8 bits. Esta redução efectiva da largura de banda não é usualmente um problema quando a imagem auxiliar visionada é relativamente pequena, por exemplo da mesma dimensão que a da imagem principal visionada. O circuito de processamento de resolução 370 pode implementar selectivamente um ou mais esquemas para aumentar a resolução da quantificação ou a largura de banda efectiva dos dados video auxiliares. Foram desenvolvidos uma pluralidade de esquemas de redução de dados e recuperação de dados, incluindo por exemplo, compressão de pixels emparelhados e excitação e não excitação. Um circuito de não excitação estaria disposto operativamente a jusante da RAM video 350, por exemplo no trajecto do sinal auxiliar da disposição de portas, como explicado em maior detalhe mais abaixo. Além do mais, estão contempladas as sequências diferentes de excitação e não excitação envolvendo diferentes números de bits e diferentes compressões de pixels emparelhados envolvendo diferentes números de bits. Um de uma pluralidade de esquemas de redução e recuperação de dados pode ser seleccionado pelo WSP  $\mu$ P a fim de maximizar a resolução do video visionado para cada tipo de formato de visionamento de imagem.

Os sinais de luminância e diferença de cor do sinal auxiliar são armazenados numa RAM video 350 num modo de 8:1:1 Y, U, V de seis bits formando parte do processador de imagem em imagem. Por outras palavras, cada componente é quantificado em amostras de seis bits. Há oito amostras de luminância para cada par de amostras de diferença de cor. Resumidamente, o processador de imagem em imagem 320 é operado num modo por meio do qual dados video de entrada são amostrados com uma frequência de relógio de  $640f_H$  bloqueada por sua vez ao sinal de sincronização video auxiliar de entrada. Neste modo, dados armazenados na RAM video 350 são amostrados perpendicularmente. Quando os dados são lidos da RAM video 350 processadora de imagem em imagem, eles são lidos utilizando o mesmo relógio  $640f_H$  bloqueado para o sinal video auxiliar de entrada. Contudo, mesmo considerando que estes dados são amostrados perpendicularmente e armazenados, e que podem ser

lidos perpendicularmente, não podem ser visionados perpendicularmente directamente da RAM video 350, devido à natureza assíncrona das fontes video principal e auxiliar. Pode-se esperar que as fontes video principal e auxiliar sejam sincronas apenas naqueles casos em que estão visionando sinais da mesma fonte video.

O trajecto do sinal principal 304, o trajecto do sinal auxiliar 306 e o trajecto do sinal de saída 312 da disposição de portas 300 estão mostrados na forma de diagrama de blocos na figura 6. A disposição de portas comprehende também um circuito de relógios/sincronismo 320 e um descodificador WSP  $\mu$ P 310. Dados e linhas de saída de endereços do descodificador WSP  $\mu$ P 310, identificados como WSP DATA, são fornecidos a cada um dos trajectos e circuitos principais acima identificados, bem como ao processador de imagem em imagem 320 e ao circuito de processamento de resolução 370. Será apreciado que de qualquer forma certos circuitos serem, ou não serem, definidos como fazendo parte da disposição de portas é claramente uma questão de conveniência para facilitar a explicação das disposições do invento.

A disposição de portas é responsável por expandir, comprimir e cortar dados video do canal video principal, quando e se necessário para implementar diferentes formatos de visionamento de imagem. O componente de luminância Y\_MN é armazenado numa primeira memória de linha primeiro a entrar primeiro a sair (FIFO) 356 para uma extensão de tempo dependente da natureza da interpolação do componente de luminância. Os componentes de crominância combinados U/V\_MN são armazenados na FIFO 358. Os componentes de luminância e crominância do sinal auxiliar Y\_PIP, U\_PIP e V\_PIP são desenvolvidos pelo dispositivo de desmultiplexação 355. O componente de luminância suporta o processamento de resolução, como desejado, no circuito 357, e é expandido tanto quanto necessário pelo interpolador 359, gerando o sinal Y\_AUX como uma saída.

Nalguns casos, o visionamento auxiliar será tão grande como

o visionamento do sinal principal, como mostrado por exemplo na figura 1(d). As limitações de memória associadas ao processador de imagem em imagem e à RAM video 350 podem fornecer um número insuficiente de pontos de dados, ou pixels para encher uma tal zona de visionamento grande. Nestas circunstâncias, o circuito de processamento de resolução 357 pode ser utilizado para recuperar pixels ao sinal video auxiliar para substituir os perdidos durante a compressão ou redução de dados. O processamento de resolução pode corresponder ao processamento de resolução levado a cabo pelo circuito 370 mostrado na figura 4. Como um exemplo, o circuito 370 pode ser um circuito de excitação e o circuito 357 pode ser um circuito de não excitação.

Além disso, com referência à figura 12, os dados de entrada video auxiliares são amostrados numa frequência de  $640f_H$  e armazenados numa RAM video 350. Os dados auxiliares são lidos da RAM video 350 e são designados por VRAM\_OUT. O circuito PIP 301 tem também a capacidade de reduzir a imagem auxiliar por factores inteiros iguais horizontalmente e verticalmente, bem como assimetricamente. Os dados do canal auxiliar são armazenados num acumulador intermédio e sincronizados ao video digital de canal principal pelos trincos de 4 bits 352A e 352B, pela FIFO auxiliar 354, pelo circuito de temporização 369 e pelo circuito de sincronização 368. Os dados VRAM\_OUT são armazenados em Y (luminância), U, V (componentes de cor), e FSW\_DAT (dados de comutação rápida) pelo dispositivo de desmultiplexação 355. O FSW\_DATA indica que tipo de campo foi escrito na RAM video. O sinal PIP\_FSW é recebido directamente do circuito PIP e aplicado ao circuito de controlo de saída 321 para determinar qual o campo lido da RAM video é para ser visionado durante os modos de imagem pequena.

O canal auxiliar é amostrado à frequência de  $640f_H$  enquanto o canal principal é amostrado numa frequência de  $1024f_H$ . O canal auxiliar FIFO 354 converte os dados da frequência de amostra do canal auxiliar para a frequência de relógio do canal principal. Neste processo, o sinal video suporta uma compressão de 8/5(1024/640). Isto é mais do que a compressão de 4/3 necessária

para visionar correctamente o sinal do canal auxiliar. Além disso, o canal auxiliar deve ser expandido pelo interpolador 359 para visionar correctamente uma imagem pequena de 4x3. O interpolador 359 é controlado pelo circuito de controlo do interpolador 371, que responde ele próprio a WSP  $\mu$ P 340. A quantidade da expansão do interpolador necessária é de 5/6. O factor de expansão X é determinado como se segue:

$$X = (640/1024) * (4/3) = 5/6$$

Os componentes de crominância U\_PIP e V\_PIP são atrasados pelo circuito 367 para uma extensão de tempo dependente da natureza da interpolação do componente de luminância, gerando os sinais U\_AUX e V\_AUX como saídas. Os respectivos componentes Y, U e V dos sinais principal e auxiliar são combinados nos respectivos dispositivos de multiplexação 315, 317 e 319 no trajecto do sinal de saída 312, controlando-se os sinais que possibilitam a leitura dos FIFO 354, 356 e 358. Os dispositivos de multiplexação 315, 317 e 319 respondem ao circuito de controlo 321 do dispositivo de multiplexação de saída. O circuito de controlo 321 do dispositivo de multiplexação de saída responde a um sinal de relógio, a um início de sinal de linha, a um sinal de contador de linha horizontal, ao sinal de restabelecimento de apagamento vertical e à saída do comutador rápido do processador de imagem em imagem e ao WSP  $\mu$ P 340. Os componentes de luminância e crominância multiplexados Y\_MX, U\_MX e V\_MX são fornecidos aos respectivos conversores de digital/analógico 360, 362 e 364 respectivamente. Os conversores de digital para analógico são seguidos pelos filtros de passagem de baixas frequências 361, 363 e 365 respectivamente, mostrados na figura 4. As várias funções do processador de imagem em imagem, a disposição de portas e o circuito de redução de dados são controlados pelo WSP  $\mu$ P 340. O WSP  $\mu$ P 340 responde ao TV  $\mu$ P 216, estando a ele ligado por um bus série. O bus série pode ser um bus de quatro fios como mostrado, que tem linhas para dados, sinais de relógio, sinais de capacitação e sinais de restabelecimento. O WSP  $\mu$ P 340 comunica com os diferentes circuitos da disposição de portas através de um descodificador

WSP  $\mu$ P 310.

Num caso, é necessário comprimir o video NTSC 4x3 por um factor de 4/3 para evitar distorção da relação de aspecto da imagem visionada. Noutro caso, o video pode ser expandido para executar operações de ampliação horizontal geralmente acompanhadas por ampliação vertical. As operações de ampliação horizontal até 33% podem ser efectuadas reduzindo-se as compressões para menos do que 4/3. Um interpolador de amostra é utilizado para recalcular o video de entrada para novas posições de pixel por causa da largura de banda, até 5,5 MHz para o formato S-VHS, ocupa uma grande percentagem da frequência Nyquist envolvida, que é 8 MHz para um relógio  $1024f_H$ .

Como mostrado na figura 6, os dados de luminância  $Y_{MN}$  são encaminhados através de um interpolador 337 no trajecto do sinal principal 304 que recalcula valores de amostra baseados na compressão ou expansão do video. A função dos comutadores ou selectores do caminho 323 e 331 é inverter a topologia do trajecto do sinal principal 304 relativamente às posições relativas da FIFO 356 e o interpolador 337. Em particular, estes comutadores seleccionam se o interpolador 337 precede a FIFO 356, como necessário para a compressão de imagem, ou se a FIFO 356 precede o interpolador 337, como necessário para a expansão de imagem. Os comutadores 323 e 331 respondem a um circuito de controlo de trajecto 335, que é ele próprio responsivo ao WSP  $\mu$ P 340. Será recordado que o sinal video auxiliar está comprimido para armazenamento na RAM video 350, e para efeitos práticos apenas é necessário expansão. Consequentemente, não é necessária comutação comparável no trajecto do sinal auxiliar.

A fim de implementar as compressões video através da utilização de uma FIFO, por exemplo, todas as quartas amostras podem ser inibidas de serem escritas na FIFO 356. Isto constitui uma compressão 4/3. A função do interpolador 337 é recalcular as amostras de luminância que estão a ser escritas na FIFO para que os dados lidos da FIFO sejam lisas em vez de recortadas. As expansões podem ser executadas de maneira exactamente oposta à

das compressões. No caso das compressões o sinal que possibilita a escrita tem a informação de acesso de relógio a ele ligada na forma de impulsos de inibição. Para expandir dados, a informação de acesso de relógio é aplicada ao sinal que possibilita a leitura. Isto interromperá os dados que estão a ser lidos da FIFO 356. Neste caso é função do interpolador 337, que segue a FIFO 356 durante este processo, recalcular os dados amostrados de recortados para lisos. No caso da expansão os dados devem parar enquanto estão a ser lidos da FIFO 356 e enquanto estão a ser cronometrados no interpolador 337. Isto é diferente do caso da compressão em que os dados são continuamente cronometrados através do interpolador 337. Para ambos os casos, a compressão e expansão, as operações de acesso de relógio podem ser facilmente executadas de uma maneira síncrona, isto é, podem ocorrer casos baseados nos bordos de fuga do relógio do dispositivo  $1024f_H$ .

A interpolação do sinal auxiliar tem lugar no trajecto do sinal auxiliar 306. O circuito PIP 301 manipula uma memória de campo 8:1:1 Y, U, V, de 6 bits, RAM video 350, para armazenar dados video de entrada. A RAM video 350 suporta dois campos de dados video numa pluralidade de localizações de memória. Cada localização de memória suporta oito bits de dados. Em cada localização de 8 bits há uma amostra (luminância) Y de 6 bits (amostrada a  $640f_H$ ) e 2 outros bits. Estes dois outros bits suportam quer dados de comutação rápida (FSW\_DATA) quer parte de uma amostra U ou V (amostrada a  $80f_H$ ). Os valores FSW\_DAT indicam que tipo de campo foi escrito na RAM video. Visto que há dois campos de dados armazenados na RAM video 350, e toda a RAM video 350 é lida durante o período de visionamento, ambos os campos são lidos durante o varrimento do visionamento. O circuito PIP 301 determinará que campo será lido da memória a ser visionada através da utilização dos dados de comutação rápida. O circuito PIP lê sempre o oposto do tipo de campo que está a ser lido para superar um problema de movimento rápido. Se o tipo do campo que está a ser lido é do tipo oposto do que está a ser visionado, então o campo equiparado armazenado na RAM video é invertido apagando-se a linha de topo do campo quando o campo é lido da memória. O resultado é que a imagem pequena mantém o

entrelaçamento correcto sem um movimento rápido.

O circuito de relógio/sincronismo 320 gera sinais de leitura e escrita e de capacitação necessários para operar as FIFO 354, 356 e 358. As FIFO para os canais principal e auxiliar estão capacitados para escrever dados no armazenamento para as porções de cada linha video que é necessária para o subsequente visionamento. Os dados são escritos a partir de um dos canais principal ou auxiliar, mas não ambos, como necessário para combinar dados de cada fonte sobre a mesma linha video ou linhas do visionamento. A FIFO 354 do canal auxiliar é escrita sincronizadamente com o sinal video auxiliar, mas é lido da memória sincronizadamente com o sinal video principal. Os componentes do sinal video principal são lidos nas FIFO 356 e 358 sincronizadamente com o sinal video principal, e são lidos da memória sincronizadamente com o video principal. Quantas vezes a função de leitura é comutada de um lado para o outro entre os canais principal e auxiliar é uma função do efeito especial particular escolhido.

A geração dos diferentes efeitos especiais tal como imagens cortadas lado a lado são realizadas através da manipulação dos sinais de controlo que possibilitam a leitura e escrita para os FIFO de memória de linha. O processo para este formato de visionamento está ilustrado nas figuras 7 e 8. No caso de imagens visionadas cortadas de lado a lado, o sinal que possibilita a escrita (WR\_EN\_AX) para a FIFO 354 de 2048x8 do canal auxiliar está activo para  $(1/2) * (5/2) = 5/2$  ou aproximadamente 41% do período de linha activo de visionamento (depois de aceleração), ou 67% do período de linha activo de visionamento (antes de aceleração), como mostrado na figura 7. Isto corresponde a cortar aproximadamente 33% (aproximadamente 67% da imagem activa) e a expansão interpoladora do sinal de 5/6. No canal video principal, mostrado na parte superior da figura 8, o sinal de controlo que possibilita a escrita (WR\_EN\_MN\_Y) para as FIFO 356 e 358 de 910x8 está activo para  $(1/2) * (4/3) = 0,67$  ou 67% do período de linha activo de visionamento. Isto corresponde a cortar aproximadamente 33% e ser executada uma relação de compressão de

4/3 no video canal principal pelas FIFO de 910x8.

Em cada uma das FIFO, os dados video são aramazenados num acumulador intermédio para serem lidos num ponto particular no tempo. A zona activa de tempo em que os dados podem ser lidos a partir de cada FIFO é determinado pelo formato de visionamento escolhido. No exemplo do modo cortado de lado a lado mostrado, o video canal principal está a ser visionado na metade esquerda do visionamento e o video canal auxiliar é visionado na metade direita do visionamento. As porções de video arbitrárias das formas de onda são diferentes para os canais principal e auxiliar como ilustrado. O sinal que possibilita a leitura (RD\_EN\_MN) das FIFO de 910x8 do canal principal é activo para 50% do periodo de linha activo de visionamento, que começa com o inicio de video activo, seguindo imediatamente a entrada video posterior. O sinal de controlo que possibilita a leitura do canal auxiliar (RD\_EN\_AX) é activo para os outros 50% do periodo de linha activo de visionamento que começa com os bordo de fuga do sinal RD\_EN\_MN e acabando com o começo da entrada video frontal do canal principal. Pode ser observado que os sinais de controlo que possibilitam a escrita são sincronos com os seus respectivos dados de entrada FIFO (principal ou auxiliar) enquanto que os sinais de controlo que possibilitam a leitura são sincronos com o video canal principal.

O formato de visionamento mostrado na figura 1(d) é particularmente desejável dado que possibilita que sejam visionadas duas imagens de campo cheio relativamente próximas num formato de lado a lado. O visionamento é particularmente efectivo e apropriado para um visor de relação de formato de visionamento largo, por exemplo 16x9. A maior parte dos sinais NTSC são representados num formato de 4x3 que corresponde certamente a 12x9. Duas imagens NTSC de relação de formato de visionamento de 4x3 podem estar presentes no mesmo visor de relação de formato de visionamento de 16x9, quer cortando-se as imagens em 33% quer comprimindo as imagens em 33%, e introduzindo distorção da relação de aspecto. Dependendo da preferência do utilizador, a relação do corte de imagem para a distorção da relação de aspecto

pode ser ajustada a qualquer valor entre os limites de 0% e 33%. Como um exemplo, duas imagens lado a lado podem estar presentes como comprimidas a 16,7% e cortadas a 16,7%.

O tempo de visionamento horizontal para um visor de relação de formato de visionamento de 16x9 é o mesmo que o de um visor de relação de formato de visionamento de 4x3, porque ambos têm o comprimento nominal de linha de 62,5 microssegundos. Consequentemente, um sinal video NTSC deve ser acelerado por um factor de 4/3 para preservar uma relação de aspecto correcta, sem distorção. O factor 4/3 é calculado como a relação de dois formatos de visionamento:

$$4/3 = (16/9) / (4/3)$$

Interpoladores variáveis são utilizados de acordo com aspectos deste invento para acelerar os sinais video. No passado, as FIFO tendo diferentes frequências de relógio nas entradas e saídas foram utilizadas para executar uma função semelhante. Por meio de comparação, se dois sinais NTSC de relação de formato de visionamento de 4x3 são visionados num visor simples de relação de formato de visionamento de 4x3, cada imagem deve ser distorcida ou cortada, ou alguma sua combinação, de 50%. Uma aceleração comparável à necessária para uma aplicação de ecrã largo é desnecessária.

Geralmente, o visor video e o dispositivo de deflexão estão sincronizadas com o sinal video principal. O sinal video principal deve ser acelerado, como acima explicado, para encher o visionamento de ecrã largo. O sinal video auxiliar deve ser sincronizado verticalmente com o primeiro sinal video e o visor video. O sinal video auxiliar pode ser apagado por uma fração de um período de campo numa memória de campo, e então expandida numa memória de linha. A sincronização dos dados video auxiliar com os dados video auxiliar é realizado utilizando-se a RAM video 350 como uma memória de campo e um dispositivo de memória primeiro a entrar primeiro a sair (FIFO) 354 para expandir o sinal.

A natureza assíncrona dos relógios de leitura e escrita necessita os passos a serem empreendidos para evitar as colisões do ponteiro de leitura/escrita. As colisões do ponteiro de leitura/escrita podem ocorrer quando dados antigos são lidos da FIFO antes de novos dados terem uma oportunidade para serem escritos na FIFO. As colisões do ponteiro de leitura/escrita ocorrem também quando dados novos cancelam a memória antes dos dados antigos terem uma oportunidade para serem lidos da FIFO. A dimensão da FIFO refere-se à capacidade de armazenamento mínima pensada ser razoavelmente necessária para evitar colisões do ponteiro de leitura/escrita. Um dispositivo de sincronização de campo para evitar colisões do ponteiro de leitura/escrita e manter a integridade do entrelaçamento é explicado mais detalhadamente em ligação com as figuras 12-18.

O processador de imagem em imagem funciona de uma tal maneira que os dados video auxiliar são amostrados por um relógio de  $640f_H$  bloqueado para o componente de sincronização horizontal do sinal video auxiliar de entrada. Este funcionamento possibilita que dados amostrados perpendicularmente sejam armazenados na RAM video 350. Os dados devem ser lidos da RAM video na mesma frequência de  $640f_H$ . Os dados não podem ser visionadas perpendicularmente a partir da RAM video sem modificação devido à natureza geralmente assíncrona das fontes video principal e auxiliar. A fim de facilitar a sincronização do sinal auxiliar com o sinal principal, uma memória de linha com relógios de acesso de escrita e leitura independentes está disposta no trajecto de sinal auxiliar depois da saída da RAM video 350.

Mais particularmente, como mostrado na figura 12, a saída da RAM video 350 é uma entrada para o primeiro de dois trincos de 4 bits 352A e 352B. A saída VRAM\_OUT está em blocos de dados de 4 bits. Os trincos de 4 bits são utilizados para recombinar o sinal auxiliar de volta para os blocos de dados de 8 bits. Os trincos reduzem também a frequência do relógio de dados a partir de  $1280f_H$  até a  $640f_H$ . Os blocos de dados de 8 bits são escritos na FIFO 354 pelo mesmo relógio de  $640f_H$  utilizado para amostrar os

dados video auxiliares para armazenamento na RAM video 350. A dimensão da FIFO 354 é de 2048x8. Os blocos de dados de 8 bits são lidos da FIFO 354 pelo relógio de visionamento de  $1024f_H$ , que está bloqueado para o componente de sincronização horizontal do sinal video principal. Esta configuração básica, que utiliza uma memória de linha múltipla com relógios de acesso de leitura e escrita independentes, possibilita que dados que foram amostrados perpendicularmente sejam visionados perpendicularmente. Os blocos de dados de 8 bits são divididos em amostras de diferença de cor e de luminância de 6 bits por um dispositivo de desmultiplexação 355. As amostras de dados podem então ser interpoladas como necessário para a relação de formato de visionamento desejada e escritas como saídas de dados video.

Deve ser escolhida uma memória suficientemente grande, no primeiro caso, a fim de evitar a colisão do ponteiro de escrita/leitura no canal auxiliar FIFO. Para visionar a relação de formato de visionamento normal de video cortado de 33%, a FIFO auxiliar, que é da dimensão de 2048x8, é capaz de armazenar 5,9 linhas de dados video, calculados como se segue, onde N é o número de vezes e L é o comprimento de cada linha:

$$N = (2/3) * (0,82) * (640) = 350 \text{ baseado no período de linha activo de } 82\%$$

$$L = 2048/350 = 5,9$$

Um aspecto do invento reconhece que frequências de precessão maiores do que 2 linhas/campo não são plausíveis de serem encontradas. Além disso, um critério de projecto de uma FIFO de 5 linhas para o canal auxiliar pode ser suficiente para evitar colisões do ponteiro de leitura/escrita.

A utilização da memória do canal auxiliar FIFO pode ser mapeada como mostrada na figura 13. Um diagrama de blocos para um circuito simplificado constituído por multivibradores biestáveis do tipo D para gerarem atrasos de linha ( $Z^{-1}$ ) e impulsos de restabelecimento para controlar a escrita e a leitura na FIFO 354 no trajecto do sinal auxiliar está mostrado na figura 14. No

*(Handwritten mark: A large 'X' is drawn across the top right corner of the page.)*

começo de um campo de sinal principal novo, o ponteiro de escrita é restabelecido para o início da FIFO. Este impulso de restabelecimento, denominado WR\_RST\_AX é a combinação do V\_SYNC\_MN amostrado por H\_SYNC\_AX. Por outras palavras, WR\_RST\_AX ocorre no primeiro impulso de sincronização horizontal do sinal video auxiliar que ocorre depois de um impulso de sincronização vertical do sinal principal. Duas linhas horizontais do sinal principal mais tarde o ponteiro de leitura é restabelecido para o inicio da FIFO 354. Este impulso de restabelecimento é denominado RD\_RST\_AX. Por outras palavras, RD\_RST\_AX ocorre no terceiro impulso de sincronização horizontal do sinal video principal que ocorre depois de um impulso de sincronização do sinal principal, ou fixado ainda por outro lado, no segundo impulso de sincronização horizontal do sinal principal que ocorre depois do impulso WR\_RST\_AX.