(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5907697号

(P5907697)

(45) 発行日 平成28年4月26日(2016.4.26)

(24) 登録日 平成28年4月1日(2016.4.1)

|                        |               |

|------------------------|---------------|

| (51) Int.Cl.           | F 1           |

| G09F 9/30 (2006.01)    | GO9F 9/30 338 |

| G02F 1/1368 (2006.01)  | GO2F 1/1368   |

| G02F 1/1343 (2006.01)  | GO2F 1/1343   |

| H01L 21/768 (2006.01)  | H01L 21/90 A  |

| H01L 21/3205 (2006.01) | H01L 21/88 M  |

請求項の数 16 (全 26 頁) 最終頁に続く

(21) 出願番号 特願2011-245103 (P2011-245103)

(22) 出願日 平成23年11月9日 (2011.11.9)

(65) 公開番号 特開2013-101232 (P2013-101232A)

(43) 公開日 平成25年5月23日 (2013.5.23)

審査請求日 平成26年10月20日 (2014.10.20)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 永野 慎吾

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 島村 武志

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

上層導電膜と、

平面視で前記上層導電膜の内側に形成された割り抜き部と、

前記上層導電膜の上に絶縁膜を介さず直接形成され、前記上層導電膜の上面および前記割り抜き部に露出した前記上層導電膜の端面を覆い、且つ、前記上層導電膜の外周の端面を覆わないように形成された第1の透明導電膜とを備える

ことを特徴とする配線構造。

## 【請求項 2】

前記上層導電膜は、異なる種類の導電性の膜を積層した積層膜である

ことを特徴とする請求項1記載の配線構造。

10

## 【請求項 3】

前記第1の透明導電膜上に形成された絶縁膜と、

前記絶縁膜に形成され、前記第1の透明導電膜に達する第1のコンタクトホールと、

前記絶縁膜上に形成され、前記第1のコンタクトホールを介して前記第1の透明導電膜に接続する第2の透明導電膜とをさらに備える

請求項1または請求項2記載の配線構造。

## 【請求項 4】

上層導電膜と、

平面視で前記上層導電膜の内側に形成された割り抜き部と、

20

前記上層導電膜の上面および前記割り抜き部に露出した前記上層導電膜の端面を覆い、且つ、前記上層導電膜の外周の端面を覆わないように形成された第1の透明導電膜と、

前記第1の透明導電膜上に形成された絶縁膜と、

前記絶縁膜に形成され、前記第1の透明導電膜に達する第1のコンタクトホールと、

前記絶縁膜上に形成され、前記第1のコンタクトホールを介して前記第1の透明導電膜に接続する第2の透明導電膜とを備え、

前記第1のコンタクトホールは、平面視で前記割り抜き部を内包するように形成されている

ことを特徴とする配線構造。

【請求項5】

10

上層導電膜と、

平面視で前記上層導電膜の内側に形成された割り抜き部と、

前記上層導電膜の上面および前記割り抜き部に露出した前記上層導電膜の端面を覆い、且つ、前記上層導電膜の外周の端面を覆わないように形成された第1の透明導電膜と、

前記第1の透明導電膜上に形成された絶縁膜と、

前記絶縁膜に形成され、前記第1の透明導電膜に達する第1のコンタクトホールと、

前記絶縁膜上に形成され、前記第1のコンタクトホールを介して前記第1の透明導電膜に接続する第2の透明導電膜とを備え、

前記第1のコンタクトホールは、前記割り抜き部とは異なる位置に形成されていることを特徴とする配線構造。

20

【請求項6】

前記上層導電膜は、最上層と最上層以外の層とから成る積層膜であり、

前記最上層以外の層と前記第1の透明導電膜との間の電気的接続性は、前記最上層と前記第1の透明導電膜との間の電気的接続性よりも良い

ことを特徴とする請求項1から請求項5のいずれか一項記載の配線構造。

【請求項7】

前記上層導電膜は、最上層と最上層以外の層とから成る積層膜であり、

前記最上層はA1を主成分とした金属膜であり、前記最上層以外の層は高融点金属を主成分とする合金膜である

ことを特徴とする請求項1から請求項6のいずれか一項記載の配線構造。

30

【請求項8】

上層導電膜と、

平面視で前記上層導電膜の内側に形成された割り抜き部と、

前記上層導電膜の上面を覆い、且つ、前記割り抜き部に露出した前記上層導電膜の端面および前記上層導電膜の外周の端面を覆わないように形成された第1の透明導電膜と、

前記第1の透明導電膜上に形成された絶縁膜と、

前記絶縁膜に形成され、平面視で前記割り抜き部を内包するように形成された第1のコンタクトホールと、

前記絶縁膜上に形成され、前記第1のコンタクトホールを介して、前記割り抜き部に露出した前記上層導電膜の端面に接続する第2の透明導電膜とを備える

40

ことを特徴とする配線構造。

【請求項9】

前記上層導電膜は、異なる種類の導電性の膜を積層した積層膜である

ことを特徴とする請求項8記載の配線構造。

【請求項10】

前記上層導電膜は、最上層と最上層以外の層とから成る積層膜であり、

前記最上層以外の層と前記第2の透明導電膜との間の電気的接続性は、前記最上層と前記第2の透明導電膜との間の電気的接続性よりも良い

ことを特徴とする請求項9に記載の配線構造。

【請求項11】

50

前記上層導電膜は、最上層と最上層以外の層とから成る積層膜であり、

前記最上層はA1を主成分とした金属膜であり、前記最上層以外の層は高融点金属を主成分とする合金膜である

ことを特徴とする請求項9または請求項10に記載の配線構造。

**【請求項12】**

前記上層導電膜の下に、当該上層導電膜と電気的に接続した半導体層をさらに備えることを特徴とする請求項1から請求項11のいずれか一項記載の配線構造。

**【請求項13】**

前記上層導電膜の下には半導体層が形成されていないことを特徴とする請求項1から請求項11のいずれか一項記載の配線構造。 10

**【請求項14】**

前記絶縁膜よりも下に形成され、前記上層導電膜とは異なる層の下層導電膜と、前記第2の透明導電膜は、前記絶縁膜に形成された第2のコンタクトホールを介して前記下層導電膜と接続していることを特徴とする請求項3から請求項5および請求項8から請求項11のうちのいずれか一項記載の配線構造。

**【請求項15】**

請求項1から請求項14のいずれか一項記載の配線構造を備える薄膜トランジスタアレイ基板。 20

**【請求項16】**

請求項15記載の薄膜トランジスタアレイ基板を用いて形成した表示パネルを備える表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、例えば液晶表示装置の表示パネルなどに配設される、透明導電膜の配線を含む配線構造に関するものである。

**【背景技術】**

**【0002】**

近年、広視野角と高透過率という特徴を両立できる液晶モードとして、FFS (Fringe Field Switching) モードの液晶表示装置への採用が急速に拡大している。FFSモードのTFTアレイ基板は、例えば下記の特許文献1に示されるように、二層の透明導電膜が絶縁膜を介して重ねられた構造を含んでいる。それに対し、一般的なTN (Twisted Nematic) モードのTFTアレイ基板が有する透明導電膜は一層である。従って、FFSモードのTFTアレイ基板の製造に必要な写真製版工程数は、一般的なTNモードのTFTアレイ基板の製造と比較して、少なくとも一工程増加することとなる。 30

**【0003】**

この工程数の増加への対策として、例えば下記の特許文献2では、FFSモードのTFTアレイ基板に設ける透明導電膜パターンの配置を工夫することによって、必要となる写真製版工程数を減らす技術が開示されている。特許文献2に開示されているFFSモードのTFTアレイ基板の構成は、一般的なTNモードのTFTアレイ基板の構成と同じ数の写真製版工程を用いて形成可能である。 40

**【先行技術文献】**

**【特許文献】**

**【0004】**

【特許文献1】特許第3826217号公報

【特許文献2】特願2010-191410号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

上記したように、FFSモードのTFTアレイ基板は、二層の透明導電膜が絶縁膜を介して重なった構造を備えている。この場合、下層の透明導電膜に生じる応力とその上層の絶縁膜に生じる応力とのバランスがとれず、透明導電膜の端部などで上層の絶縁膜が剥離する「膜浮き」もしくは「膜剥がれ」と呼ばれる現象（以下「膜浮き」と総称する）が発生する場合がある。

#### 【0006】

この膜浮きの発生頻度は透明導電膜のパターン密度とも関係しており、TFTアレイ基板における表示領域より外側の額縁領域など、透明導電膜のパターン密度が比較的疎な領域において、例えば外部接続端子部や配線変換部などで、発生頻度が高くなる。絶縁膜の膜浮きが発生した部分では絶縁膜の保護膜としての機能が失われるため、膜浮きは、電極の耐腐食性の低下や絶縁破壊の発生など、TFTアレイ基板の製造における歩留まりの低下、およびTFTアレイ基板の信頼性の低下を引き起こす要因となる。従って、歩留まりおよび高信頼性の高いTFTアレイ基板を得るために、絶縁膜の膜浮きへの対策が有効である。

10

#### 【0007】

特許文献2には、FFSモードのTFTアレイ基板の写真製版工程数を一般的なTNモードのTFTアレイ基板と同数にする目的で、ソース配線となる金属膜パターン上に絶縁膜を介さずに透明導電膜を配置する構成を採用している。この構成では、TFTアレイ基板上における透明導電膜パターンの面積が大きく、絶縁膜の膜浮きの発生頻度が高くなることが懸念されるため、膜浮きの対策は更に重要となる。

20

#### 【0008】

また特許文献2のTFTアレイ基板では、金属膜と透明導電膜とが電気的に同一の電極または配線として機能する必要があるため、金属膜と透明導電膜との電気的接続性が重要となる。例えば、ITO(Indium Tin Oxide)などの透明電極とA1との間では容易に良好な電気的接続性を得ることができないため、最上層がA1系金属の積層膜の上にITOの透明導電膜を配設する必要がある場合に問題となる。本発明者は、A1上にITOが配置される配線構造を有するTFTアレイ基板を用いた液晶表示装置において、TFTアレイ基板の異なる層の配線同士を接続する配線変換部の抵抗が上昇し、線欠陥等の表示異常を引き起こすことを確認している。

#### 【0009】

30

一方、A1系の薄膜は抵抗値が低いため、液晶表示装置の高解像度化および大画面化とともに、TFTアレイ基板の信号配線へA1系薄膜の適用が拡大している。よって、FFSモードのTFTアレイ基板の開発においては、透明導電膜と金属膜、特にA1系薄膜を上面に有する積層膜との間の電気的接続性を向上させることが重要な課題となる。

#### 【0010】

本発明は以上のような課題を解決するためになされたものであり、透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造およびそれを備えるTFTアレイ基板、並びに液晶表示装置を提供すること目的とする。

#### 【課題を解決するための手段】

40

#### 【0011】

本発明に係る配線構造は、上層導電膜と、平面視で前記上層導電膜の内側に形成された割り抜き部と、前記上層導電膜の上に絶縁膜を介さず直接形成され、前記上層導電膜の上面および前記割り抜き部に露出した前記上層導電膜の端面を覆い、且つ、前記上層導電膜の外周の端面を覆わないように形成された第1の透明導電膜とを備えるものである。

#### 【発明の効果】

#### 【0012】

本発明によれば、第1の透明導電膜の端部に応力が集中することが防止され、当該第1の透明絶縁膜の上に設ける絶縁膜の膜浮きの発生を抑制できる。また、第1の透明導電性

50

膜が、割り抜き部内に露出した第1の導電膜の端面に接続するため、第1の導電膜の最上層が第1の透明導電膜との電気的接続性が悪くても、他の層によって良好な電気的接続性を得ることができる。

【図面の簡単な説明】

【0013】

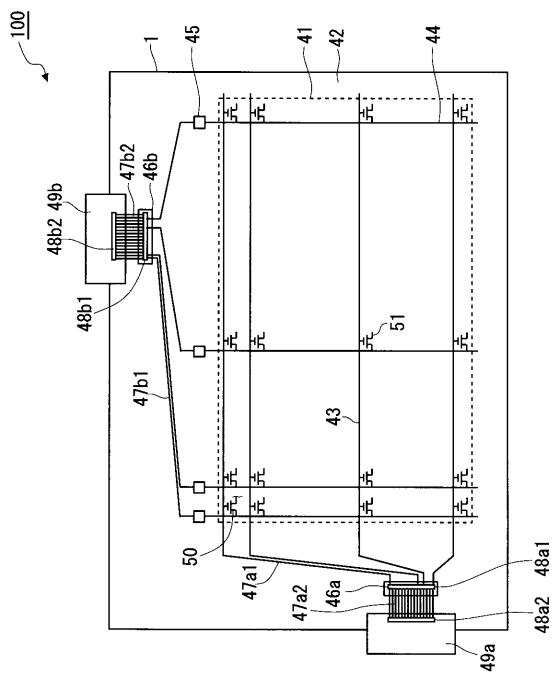

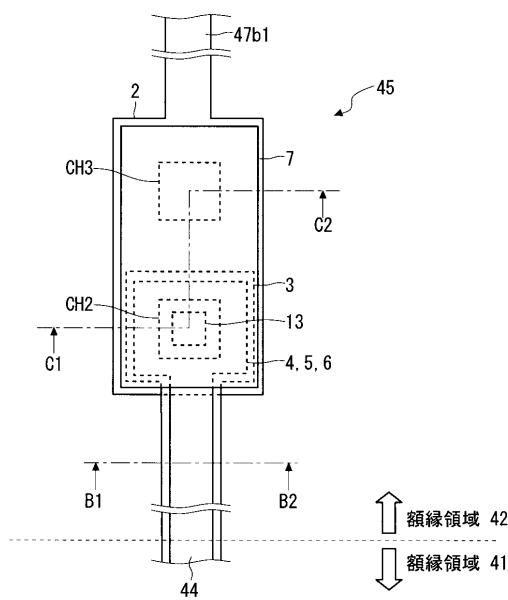

【図1】本発明の実施の形態に係る液晶表示装置に用いられるTFTアレイ基板の構成を示す平面図である。

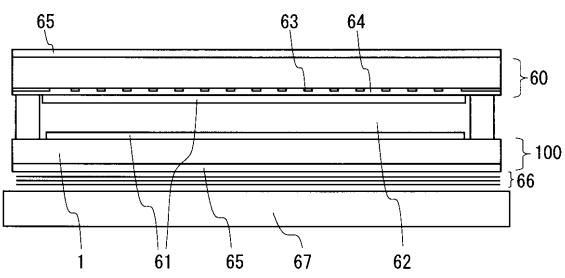

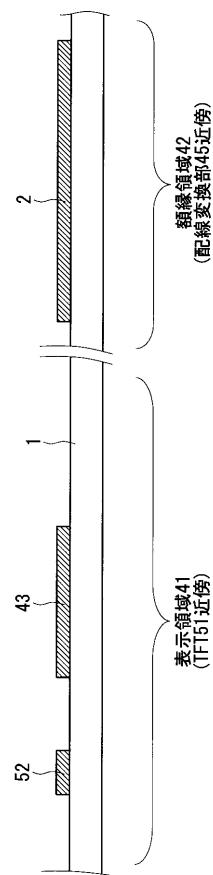

【図2】本発明の実施の形態に係る液晶表示装置を示す断面図である。

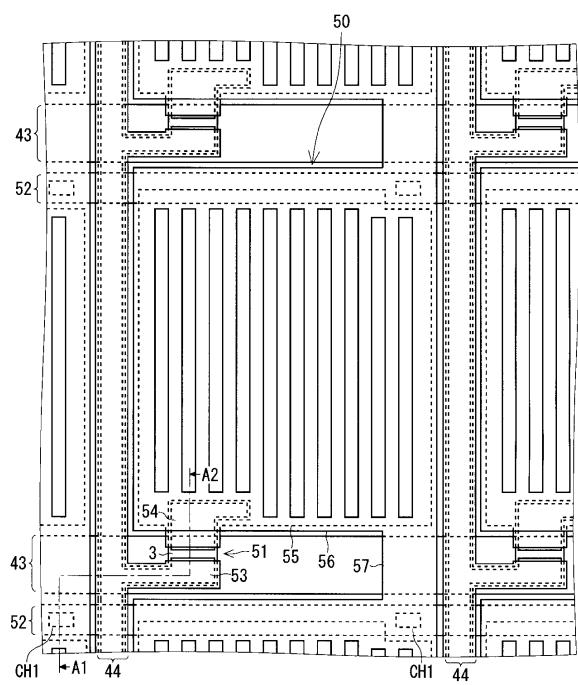

【図3】本発明の実施の形態に係るTFTアレイ基板の表示領域の平面図である。

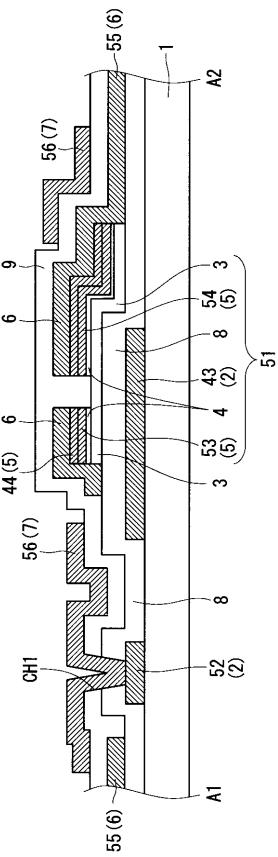

【図4】本発明の実施の形態に係るTFTアレイ基板の表示領域の断面図である。 10

【図5】実施の形態1に係るTFTアレイ基板の配線変換部の平面図である。

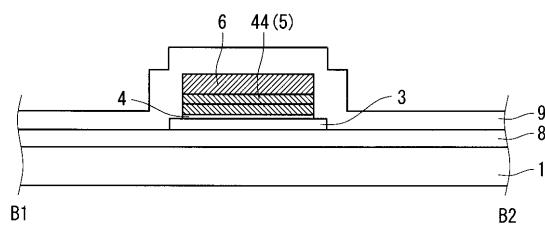

【図6】実施の形態1に係るTFTアレイ基板のソース配線の延在部分の断面図である。

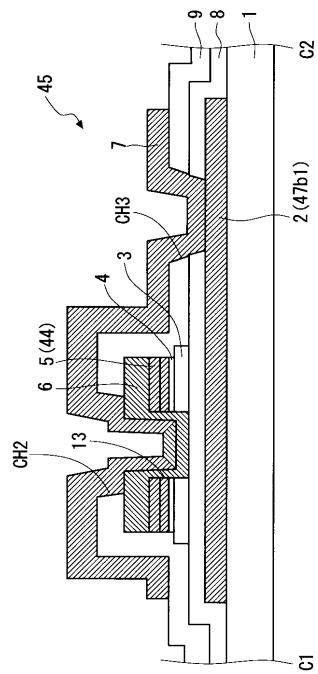

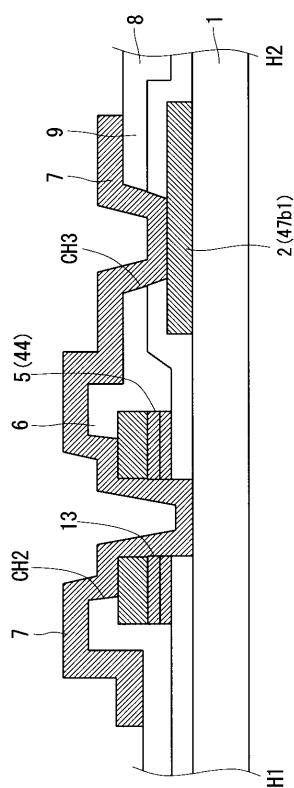

【図7】実施の形態1に係るTFTアレイ基板の配線変換部の断面図である。

【図8】実施の形態1に係るTFTアレイ基板の製造方法を説明するための工程図である。

【図9】実施の形態1に係るTFTアレイ基板の製造方法を説明するための工程図である。

【図10】実施の形態1に係るTFTアレイ基板の製造方法を説明するための工程図である。

【図11】実施の形態1に係るTFTアレイ基板の製造方法を説明するための工程図である。 20

【図12】実施の形態1に係るTFTアレイ基板の製造方法を説明するための工程図である。

【図13】実施の形態1に係るTFTアレイ基板の製造方法を説明するための工程図である。

【図14】本発明が適用されたソース配線の断面図である。

【図15】ソース配線に本発明を適用した場合における、ソース配線上における割り抜き部のレイアウトの一例を示す図である。

【図16】実施の形態2に係るTFTアレイ基板の配線変換部の平面図である。

【図17】実施の形態2に係るTFTアレイ基板の配線変換部の断面図である。 30

【図18】実施の形態3に係るTFTアレイ基板の配線変換部の平面図である。

【図19】実施の形態3に係るTFTアレイ基板の配線変換部の断面図である。

【図20】実施の形態4に係るTFTアレイ基板の配線変換部の平面図である。

【図21】実施の形態4に係るTFTアレイ基板の配線変換部の断面図である。

【図22】実施の形態5に係るTFTアレイ基板の配線変換部の平面図である。

【図23】実施の形態5に係るTFTアレイ基板の配線変換部の断面図である。

【図24】実施の形態6に係るTFTアレイ基板の配線変換部の平面図である。

【図25】実施の形態6に係るTFTアレイ基板の配線変換部の断面図である。

【発明を実施するための形態】

【0014】

以下、本発明の好ましい実施の形態を説明するが、本発明の適用はそれに限定されるものではない。また、説明の便宜のため、説明および図面の記載は、適宜、省略または簡略化している。例えば、図面は模式的なものであり、それに示された構成要素の正確な大きさなどを特定するものではない。また、各図において同一の符号を付されたものは、それぞれ同様の要素を示しており、それらに関しては重複する説明は省略する。

【0015】

<実施の形態1>

始めに、本発明に係る配線構造を適用可能な液晶表示装置の構成例を示す。図1は、本発明の実施の形態に係る液晶表示装置を構成するTFTアレイ基板100を示す平面図である。図1に示すように、当該TFTアレイ基板100は、基板1上にアレイ状(マトリ 50

クス状)に配設された、画像の表示単位となる画素50を備える。各画素50には、画素電極(不図示)に表示電圧を供給するスイッチング素子であるTFT51が配置される。TFT51を搭載した基板1から構成される部材を「TFTアレイ基板」と呼ぶのは、TFT51が画素50ごとにアレイ状に配列されるためである。基板1は、例えば、ガラス基板や半導体基板により構成される。

【0016】

TFTアレイ基板100は、TFT51がアレイ状に配列した領域であるアレイ領域41(図1における点線の矩形の内側)と、アレイ領域41を囲む額縁領域42(図1における点線の矩形の外側)とを有している。液晶表示装置では、アレイ領域41は画像を表示する領域である表示領域に対応する。以下、アレイ領域41を「表示領域41」と称す。 10

【0017】

TFTアレイ基板100の表示領域41には、複数のゲート配線(走査信号線)43と複数のソース配線(表示信号線)44とが形成されている。複数のゲート配線43はそれぞれ平行に延在し、同様に、複数のソース配線44はそれぞれ平行に延在する。ゲート配線43とソース配線44とは、互いに交差するように配設される。隣接する一対のゲート配線43と、隣接する一対のソース配線44とで囲まれた領域のそれぞれが画素50となる。従って、表示領域41においては、画素50がマトリクス状に配列されることとなる。 20

【0018】

TFTアレイ基板100の額縁領域42には、走査信号駆動回路46a、表示信号駆動回路46b、配線変換部45、引き出し配線47a1, 47a2, 47b1, 47b2、および外部接続端子48a1, 48a2, 48b1, 48b2などが配設される。 20

【0019】

ゲート配線43は、表示領域41の外側の額縁領域42まで延設され、当該ゲート配線43と同一の配線層(下層導電膜である第1の導電膜)で形成された引き出し配線47a1によってTFTアレイ基板100の端部まで引き出される。引き出し配線47a1により引き出されたゲート配線43は、外部接続端子48a1を介して走査信号駆動回路46aに接続される。 30

【0020】

ソース配線44は、表示領域41の外側の額縁領域42まで延設され、配線変換部45にてゲート配線43と同一の配線層(第1の導電膜)で形成された引き出し配線47b1に電気的に接続され、その引き出し配線47b1によってTFTアレイ基板100の端部まで引き出される。引き出し配線47b1によって引き出されたソース配線44は、外部接続端子48b1を介して表示信号駆動回路46bに接続される。 30

【0021】

走査信号駆動回路46aの近傍には外部配線49aが配設されており、走査信号駆動回路46aと外部配線49aとの間は、引き出し配線47a2および外部接続端子48a2を介して接続される。また、表示信号駆動回路46bの近傍には、外部配線49bが配設されており、表示信号駆動回路46bと外部配線49bとの間は、引き出し配線47b2および外部接続端子48b2を介して接続される。上記の外部配線49a, 49bは、例えばFPC(Flexible Printed Circuit)などの配線基板である。 40

【0022】

走査信号駆動回路46aには、外部配線49aおよび引き出し配線47a2を介して外部からの各種信号が供給される。表示信号駆動回路46bには、外部配線49bおよび引き出し配線47b2を介して外部からの各種信号が供給される。

【0023】

走査信号駆動回路46aは、外部から供給される制御信号に基づいて、ゲート信号(走査信号)をゲート配線43に供給する。このゲート信号は、ゲート配線43の各々を順次選択する信号である。表示信号駆動回路46bは、外部から供給される制御信号や表示デ 50

ータに基づき、各ゲート配線 4 3 が選択されるタイミングに同期して、表示信号をソース配線 4 4 の各々に供給する。この動作により、表示データに応じた表示電圧が、画素 5 0 のそれぞれに供給される。

【 0 0 2 4 】

画素 5 0 のそれぞれには、少なくとも 1 つの TFT 5 1 が設けられる。TFT 5 1 は、ソース配線 4 4 とゲート配線 4 3 の交点近傍に配置され、TFT 5 1 のゲート電極はゲート配線 4 3 に、ソース電極はゲート配線 4 3 にそれぞれ接続される。TFT 5 1 は、ゲート配線 4 3 から供給されるゲート信号に応じてオンし、ソース配線 4 4 から供給される表示電位をドレイン電極が接続した画素電極に印加する。

【 0 0 2 5 】

FFS モードの TFT アレイ基板 1 0 0 には、画素電極だけでなく、当該画素電極と絶縁膜を介して対向配置される対向電極（共通電極）も配設される。通常、画素電極は平板状であり、共通電極は櫛歯状（複数のスリットを有する形状）である。対向電極には共通電位が与えられており、画素電極と対向電極との間には、表示電圧（表示電位と共通電位との差）に応じたフリンジ電界が生じる。なお、画素 5 0 の構成の詳細については後述する。

10

【 0 0 2 6 】

続いて、実施の形態 1 に係る液晶表示装置の全体構成について説明する。図 2 は、上記の TFT アレイ基板 1 0 0 を含む液晶表示装置の全体構成を示す断面図である。図 2 の如く、液晶表示装置は、対向配置された TFT アレイ基板 1 0 0 と対向基板 6 0 との間に、液晶層 6 2 を封止した構造を有している。

20

【 0 0 2 7 】

対向基板 6 0 は、TFT アレイ基板 1 0 0 に対して液晶表示装置の前面側（視認側）に配置される。対向基板 6 0 には、カラーフィルター 6 4 、ブラックマトリクス（BM）6 3 などが形成されている。対向基板 6 0 は、一般に「カラーフィルター基板」と呼ばれる。

【 0 0 2 8 】

TFT アレイ基板 1 0 0 および対向基板 6 0 それぞれの液晶層 6 2 側の表面には、配向膜 6 1 が形成される。また、TFT アレイ基板 1 0 0 の背面側（反視認側）および対向基板 6 0 の前面側には、それぞれ偏光板 6 5 が設けられる。これら TFT アレイ基板 1 0 0 、対向基板 6 0 、液晶層 6 2 および偏光板 6 5 により、液晶表示パネルが構成される。

30

【 0 0 2 9 】

さらに、液晶表示パネルの背面側に、位相差板などの光学フィルム 6 6 を介してバックライトユニット 6 7 を配置し、これらを樹脂や金属などよりなるフレーム（不図示）に収納することにより、液晶表示装置が構成される。

【 0 0 3 0 】

偏光板 6 5 を通過して直線偏光となった光は、液晶層 6 2 によってその偏光状態が変化する。FFS モードの液晶表示装置では、TFT アレイ基板 1 0 0 の画素電極と対向電極との間に発生するフリンジ電界によって液晶層 6 2 を駆動し（液晶層 6 2 の配向方向を変化させる）、それにより液晶層 6 2 を通過する光の偏光状態を変化させている。

40

【 0 0 3 1 】

より具体的には、バックライトユニット 6 7 からの光は、液晶表示パネルの背面側の偏光板 6 5 により直線偏光になる。この直線偏光は、液晶層 6 2 を通過することによって、偏光状態が変化し、それにより液晶表示パネルの前面側の偏光板 6 5 を通過する光量が変化する。つまり、バックライトユニット 6 7 から出射されて液晶表示パネルを透過する透過光のうち、前面側の偏光板 6 5 を通過する光の量が変化する。液晶層 6 2 の配向方向は、印加される表示電圧によって変化する。従って、表示電圧を制御することによって、前面側の偏光板 6 5 を通過する光量を変化させることができる。よって、画素 5 0 ごとに表示電圧を変化させることによって、所望の画像を表示させることができる。

【 0 0 3 2 】

50

次に、実施の形態 1 に係る TFT アレイ基板 100 の表示領域 41 の詳細構成について、図 3 および図 4 を用いて説明する。図 3 は、TFT アレイ基板 100 の表示領域 41 の中央部近傍に位置する画素 50 の平面図、図 4 は、図 3 における A1 - A2 線に沿った断面図である。なお、画素 50 の構成は、表示領域 41 の最外周に位置するものを除いて、図 3 および図 4 と同様の構成となる。

#### 【0033】

例えばガラス基板などの絶縁性材料よりなる基板 1 の上に、TFT51 のゲート電極に接続するゲート配線 43 が複数個形成される。本実施の形態では、ゲート配線 43 の一部が TFT51 のゲート電極として機能する。複数のゲート配線 43 は、平行にそれぞれ直線的に配設される。また基板 1 上には、ゲート配線 43 と同じ配線層（第 1 の導電膜 2）を用いて形成された複数の共通配線 52 が平行に形成されている。共通配線 52 は、ゲート配線 43 間に、ゲート配線 43 とほぼ平行に配設される。

10

#### 【0034】

これらゲート配線 43（ゲート電極）および共通配線 52 を構成する第 1 の導電膜 2 は、例えば Cr, Al, Ta, Ti, Mo, W, Ni, Cu, Au, Ag などの高融点金属または低抵抗金属やこれらを主成分とする合金膜、またはこれらの積層膜によって形成される。

#### 【0035】

ゲート配線 43 および共通配線 52 上には、第 1 の絶縁膜 8 が形成される。第 1 の絶縁膜 8 の一部（ゲート配線 43 上の部分）は、TFT51 のゲート絶縁膜として機能する。

20

#### 【0036】

第 1 の絶縁膜 8 の上には半導体層 3 が形成される。本実施の形態では、半導体膜 3 は、ソース配線 44 の形成領域に合わせて、ゲート配線 43 と交差する直線状に形成される（図 3 において、半導体膜 3 のパターンは、ゲート配線 43 に直交している）。半導体層 3 は、非結晶シリコンや多結晶シリコンなどにより形成される。

#### 【0037】

この直線状の半導体層 3 は、ソース配線 44 の冗長配線としても機能する。即ち、ソース配線 44 が断線した場合でも、半導体膜 3 がソース配線 44 に沿って配設されていることにより、電気信号の途絶を防止することが可能になる。

#### 【0038】

30

また、半導体層 3 の一部は、ゲート配線 43 との交差部で分岐し、ゲート配線 43 に沿って延び、さらに画素 50 内へと延設される。TFT51 は、ゲート配線 43 との交差部から分岐した半導体膜 3 の部分を用いて形成される。即ち、分岐した半導体層 3 のうち、ゲート配線 43（ゲート電極）と重複する部分が、TFT51 を構成する活性領域となる。

#### 【0039】

半導体層 3 の上には、導電性不純物がドーピングされたオーミックコンタクト膜 4 が形成される。オーミックコンタクト膜 4 は、半導体膜 3 上のほぼ全面に形成されるが、TFT51 のチャネル領域となる部分（ソース配線 44 とドレイン電極 54 との間の領域）の上では除去されている。オーミックコンタクト膜 4 は、例えば、リン（P）などの不純物が高濃度にドーピングされた n 型非結晶シリコンや n 型多結晶シリコンなどにより形成される。

40

#### 【0040】

半導体層 3 のゲート配線 43 と重複する部分のうち、オーミックコンタクト膜 4 が形成された領域は、ソース・ドレイン領域となる。図 4 を参照すると、半導体膜 3 において、ゲート配線 43 と重複する左側のオーミックコンタクト膜 4 の下の領域がソース領域となり、ゲート配線 43 と重複する右側のオーミックコンタクト膜 4 の下の領域がドレイン領域となる。そして、半導体膜 3 におけるソース領域とドレイン領域とに挟まれた領域がチャネル領域となる。

#### 【0041】

50

オーミックコンタクト膜4の上には、ソース配線44、ソース電極53およびドレイン電極54が、同一の配線層（上層導電膜である第2の導電膜5）を用いて形成されている。具体的には、TFT51のソース領域側のオーミックコンタクト膜4上にソース電極53が形成され、ドレイン領域側のオーミックコンタクト膜4上にドレイン電極54が形成される。このような構成のTFT51は「チャネルエッチ型TFT」と呼ばれる。

【0042】

ソース配線44は、半導体層3の上にオーミックコンタクト膜4を介して形成され、ゲート配線43と交差する方向に直線的に延在するように配設されている。ソース電極53とドレイン電極54は分離しているが、ソース電極53はソース配線44と繋がっている。即ち、ソース配線44は、ゲート配線43との交差部で分岐してゲート配線43に沿って延設され、その延設された部分がソース電極53となる。ソース配線44、ソース電極53およびドレイン電極54を構成する第2の導電膜5は、オーミックコンタクト膜4と同様に、半導体膜3上のほぼ全面に形成されるが、TFT51のチャネル領域となる部分の上では除去されている。

【0043】

本実施の形態では、ソース配線44、ソース電極53およびドレイン電極54を構成する第2の導電膜5は、Alを主成分とした金属膜である上層と、Cr, Ta, Ti, Mo, W, Ni, Cu, Au, Agなどの高融点金属または低抵抗金属やこれらを主成分とする合金膜である下層から成る積層膜であるとする。

【0044】

以上の説明から分かるように、半導体層3は、ソース配線44、ソース電極53およびドレイン電極54の下のほぼ全領域と、ゲート配線43上に位置するソース電極53とドレイン電極54の間の領域に配設されている。また、オーミックコンタクト膜4は、ソース配線44、ソース電極53およびドレイン電極54と半導体層3との間にそれぞれ配設されている。

【0045】

ドレイン電極54は、画素50の領域（ソース配線44とゲート配線43とに囲まれた領域）のほぼ全面に形成された第1の透明導電膜6である画素電極55に電気的に接続される。第1の透明導電膜6は、ITOなどの透明導電膜によって形成される。

【0046】

図4に示すように、画素電極55は、ドレイン電極54上に直接重ねられた部分を有している。即ち、その部分では、画素電極55を構成する第1の透明導電膜6の下面が、ドレイン電極54の上面に直接接触する。また、第1の透明導電膜6は、ドレイン電極54上のほぼ全面を覆っている。但し、第1の透明導電膜6のチャネル領域側の端部は、ドレイン電極54のチャネル領域側の端部とほぼ同じ位置、或いは若干ドレイン電極5の端部よりも後退して配置される。よって、ドレイン電極54のチャネル領域側の端面は、第1の透明導電膜6に覆われない。なお、第1の透明導電膜6は、ドレイン電極54のチャネル領域側以外の端面は覆うように形成されている。

【0047】

なお、本明細書において「端面を覆うように形成」とは、上層膜を、下層膜の上面と端面とを分け隔てなく覆うように形成することを意味し、例えば、下層膜の端面の凹凸により上層膜が下層膜の端面に充分接觸できない状態（いわゆる「カバレッジ不良」の状態）も含むものとする。しかし、下層膜を覆うように上層膜を形成した後、上層膜を加工して意図的に下層膜の端面を露出させた状態は含まない。

【0048】

このように、画素電極55の一部を、絶縁膜を介さずに、ドレイン電極54に直接重ねる構成をとることにより、画素電極55とドレイン電極54と電気的に接続するためのコンタクトホールが不要になり、写真製版工程を減らすことができる。また、当該コンタクトホールを配置するエリアを確保する必要がなくなるため、画素50の開口率を高くできるという利点もある。

10

20

30

40

50

## 【0049】

また、画素電極55と同一の配線層である第1の透明導電膜6は、ソース電極53およびソース配線44上のほぼ全面にも直接重ねて形成される。ソース電極53上の第1の透明導電膜6におけるチャネル領域側の端部は、ソース電極53のチャネル領域側の端部とほぼ同じ位置、或いはソース電極53の端部よりも若干後退して配置される。よって、ソース電極53のチャネル領域側の端部は、第1の透明導電膜6には覆われていない。なお、第1の透明導電膜6は、ソース電極53のチャネル領域側以外の端面は覆うように形成されている。

## 【0050】

ソース電極53上の第1の透明導電膜6と、ドレイン電極54上の第1の透明導電膜6 (画素電極55)とは、離間している。つまり、半導体層3のチャネル領域上には、第1の透明導電膜6は設けられていない。

10

## 【0051】

図4に示されるように、ソース配線44は、ソース電極53およびドレイン電極54と同じ第2の導電膜5を用いて形成される。ソース配線44の下のほぼ全面には半導体層3が配設され、ソース配線44と半導体層3との間にはオーミックコンタクト膜4が形成される。

## 【0052】

またソース配線44、オーミックコンタクト膜4および半導体層3は、画素電極55と同層の第1の透明導電膜6により覆われ、第1の透明導電膜6は、ソース配線44の幅から食み出しており、ソース配線44の端面を覆っている。図4ではソース配線44の一方の端面(左側の端面)しか図示されないが、もう一方の端面も、ソース配線44の幅から食み出した第1の透明導電膜6によって覆われる。

20

## 【0053】

このように画素電極55と同層の第1の透明導電膜6は、第2の導電膜5を用いて形成したソース配線44、ソース電極53およびドレイン電極54上のほぼ全面に形成されている。特に、ソース配線44上の第1の透明導電膜6は、ソース配線44の冗長配線としても機能する。即ち、ソース配線44が断線した場合でも、第1の透明導電膜6がソース配線44に沿って配設されていることにより、電気信号の途絶を防止することが可能になる。

30

## 【0054】

図4の如く、画素電極55を含む第1の透明導電膜6の上は、第2の絶縁膜9で覆われる。第2の絶縁膜9上には、第2の透明導電膜7である対向電極56が形成される。第2の絶縁膜9は、TFT51の保護膜として機能すると共に、画素電極55と対向電極56との間の層間絶縁膜としても機能する。第2の絶縁膜9は、窒化シリコンや酸化シリコンなどの絶縁膜、塗布型の(塗布により形成される)絶縁膜、またはそれらの積層膜により形成される。

## 【0055】

対向電極56は、第2の絶縁膜9を介して画素電極55に対向配置され、画素電極55との間でフリンジ電界を発生させるためのスリットが設けられている。図3のように、対向電極56のスリットは、ソース配線44とほぼ平行に複数設けられている。言い換れば、対向電極56は、スリットの存在により櫛歯状となっている。上記したように、FFSモードの液晶表示装置では、画素電極55と対向電極56との間に発生するフリンジ電界によって液晶を駆動する。

40

## 【0056】

対向電極56は、第2の絶縁膜9および第1の絶縁膜8を貫通するコンタクトホールCH1を介して、共通電位が供給される共通配線52と電気的に接続されている。また、対向電極56は、ゲート配線43を挟んで隣接する他の画素50の対向電極56に繋がるよう に一体的に形成されている。つまり、ゲート配線43を挟んで隣接する画素50の対向電極56の間は、それらと同じ配線層(第2の透明導電膜7)である対向電極連結部57

50

により連結されている。ここでは、対向電極連結部 57 は、ソース配線 44 および TFT 51 と重複しない領域に、ゲート配線 43 を跨ぐように形成されている。即ち、第 2 の透明導電膜 7 は、ゲート配線 43 と一部が重なり合うように形成されている。

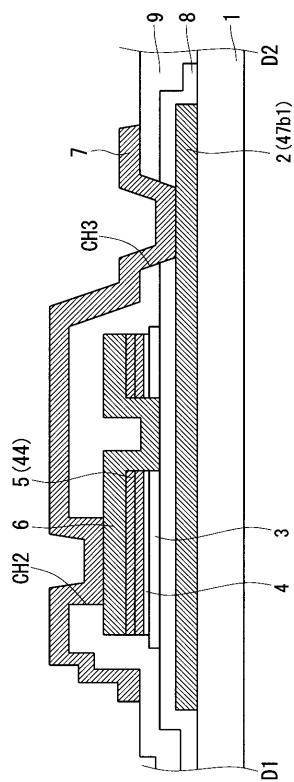

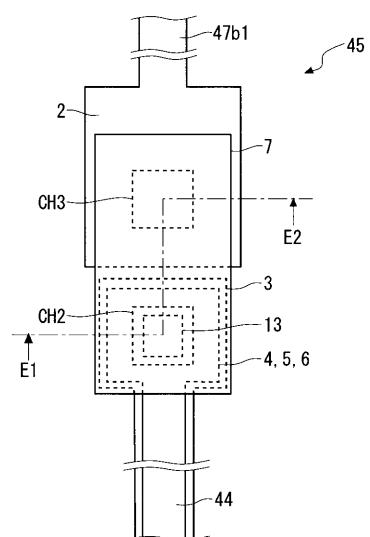

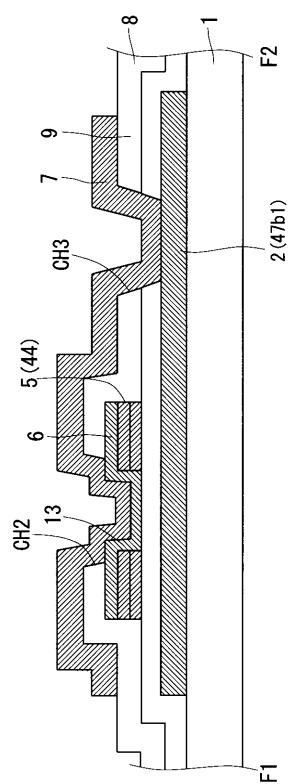

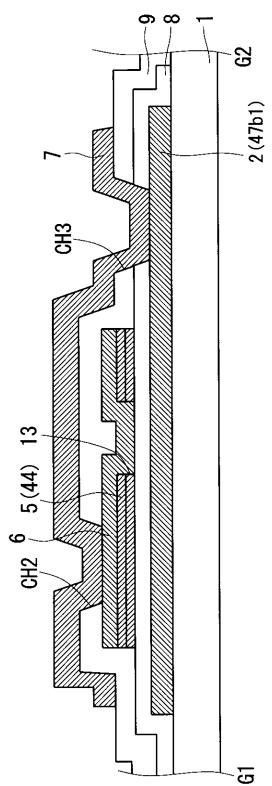

#### 【0057】

続いて、実施の形態 1 に係る液晶表示装置の TFT アレイ基板 100 が備える配線変換部 45 の構成について、図 5 ~ 図 7 を用いて説明する。図 5 は、配線変換部 45 の平面図であり、図 6 は、図 5 の B1 - B2 線に沿った断面図、図 7 は、図 5 の C1 - C2 線に沿った断面図である。

#### 【0058】

なお、図 5 ~ 図 7 において、図 3 および図 4 に示したものと同層を用いて形成された要素には同一符号を付してある。例えば、図 5 ~ 図 7 の第 1 の導電膜 2 は、ゲート配線 43 である図 4 の第 1 の導電膜 2 と同層である。同様に、図 5 ~ 図 7 の第 1 の絶縁膜 8 は、TFT 51 のゲート絶縁膜として働く図 4 の第 1 の絶縁膜 8 と同層である。また、図 5 ~ 図 7 の半導体膜 3 は、TFT 51 の活性領域である図 4 の半導体膜 3 と同層である。その他のオーミックコンタクト膜 4、第 2 の導電膜 5、第 1 の透明導電膜 6、第 2 の透明導電膜 7、第 2 の絶縁膜 9 などについても同様である。

#### 【0059】

図 5 に示すように、配線変換部 45 は、TFT アレイ基板 100 の額縁領域 42 に配設される。表示信号駆動回路 46b や外部配線 49b に接続する引き出し配線 47b1 は、ゲート配線 43 と同層の第 1 の導電膜 2 により形成されており、配線変換部 45 に引き込まれている。また表示領域 41 からは、第 2 の導電膜 5 であるソース配線 44 の延在部分が配線変換部 45 まで引き込まれている。

#### 【0060】

図 6 に示すように、ソース配線 44 の延在部分において、ソース配線 44 (第 2 の導電膜 5) の下面にはオーミックコンタクト膜 4 および半導体膜 3 が形成されており、第 2 の導電膜 5 の上面には、画素電極 55 と同層の第 1 の透明導電膜 6 が形成されている。これら半導体膜 3、オーミックコンタクト膜 4、第 2 の導電膜 5 および第 1 の透明導電膜 6 は、第 1 の絶縁膜 8 上に積層されている。

#### 【0061】

また、オーミックコンタクト膜 4、第 2 の導電膜 5、第 1 の透明導電膜 6 の端部はほぼ同じ位置に配置されており、それらの端部は、半導体膜 3 の端部よりも内側に配置されている。つまり、オーミックコンタクト膜 4、第 2 の導電膜 5、第 1 の透明導電膜 6 は、半導体膜 3 の幅よりも若干狭い幅で形成されている。従って、半導体膜 3、オーミックコンタクト膜 4、第 2 の導電膜 5 の端面は、第 1 の透明導電膜 6 に覆われていない。

#### 【0062】

ソース配線 44 の延在部分において、第 1 の透明導電膜 6 上には、第 2 の絶縁膜 9 が形成される。この第 2 の絶縁膜 9 は、半導体膜 3、オーミックコンタクト膜 4、第 2 の導電膜 5 および第 1 の透明導電膜 6 の端面を覆うように形成される。

#### 【0063】

続いて、図 7 を参照して、第 1 の導電膜 2 である引き出し配線 47b1 と、第 2 の導電膜 5 であるソース配線 44 の延在部分とを接続させる配線変換部 45 の構成を説明する。

#### 【0064】

図 7 のように、配線変換部 45 には、引き出し配線 47b1 としての第 1 の導電膜 2 が引き込まれている。第 1 の導電膜 2 上には、第 1 の絶縁膜 8 が形成されている。

#### 【0065】

また、配線変換部 45 における第 1 の絶縁膜 8 上には、図 6 に示した構造のソース配線 44 も引き込まれている。つまり配線変換部 45 において、第 1 の絶縁膜 8 の上には、半導体膜 3、オーミックコンタクト膜 4、第 2 の導電膜 5、第 1 の透明導電膜 6 の積層構造が形成されている。

#### 【0066】

10

20

30

40

50

図7の如く、オーミックコンタクト膜4、第2の導電膜5および第1の透明導電膜6の外周の端部は、半導体膜3の外周の端部よりも内側に後退している。言い換えれば、配線変換部45において、オーミックコンタクト膜4、第2の導電膜5および第1の透明導電膜6は、平面視で半導体膜3に内包されている。また、オーミックコンタクト膜4、第2の導電膜5および第1の透明導電膜6の外周の端部は、ほぼ同じ位置に配置される。従って、第1の透明導電膜6は、半導体膜3、オーミックコンタクト膜4および第2の導電膜5の外周の端部を覆っていない。

【0067】

また、配線変換部45において、平面視で第2の導電膜5の内側の領域に、第2の導電膜5、オーミックコンタクト膜4および半導体膜3が存在しない割り抜き部13が設けられている。半導体膜3、オーミックコンタクト膜4、第2の導電膜5における割り抜き部13側の端部はほぼ同じ位置であり、割り抜き部13の内部にそれらの端面が露出している。

【0068】

一方、第2の導電膜5の上に形成される第1の透明導電膜6には割り抜き部13に対応する開口は無く、第1の透明導電膜6は割り抜き部13の内部にも形成される。第1の透明導電膜6は、割り抜き部13内に露出した半導体層3、オーミックコンタクト膜4および第2の導電膜5の各端面を覆うように形成される。

【0069】

配線変換部45においても、第1の透明導電膜6の上層には、第2の絶縁膜9が形成される。図7に示すように、第2の絶縁膜9は、半導体膜3、オーミックコンタクト膜4、第2の導電膜5および第1の透明導電膜6の端面を直接覆うように形成される。

【0070】

配線変換部45において、第2の絶縁膜9には、第1の透明導電膜6に達するコンタクトホールCH2が形成される。また、第1の絶縁膜8および第2の絶縁膜9には、第1の導電膜2に達するコンタクトホールCH3が形成される。実施の形態1では、コンタクトホールCH2は、平面視で割り抜き部13を内包するように設けられており、割り抜き部13内の第1の透明導電膜6の表面を露出している。

【0071】

そして、第2の絶縁膜9上に、対向電極56と同層の第2の透明導電膜7が、コンタクトホールCH2とコンタクトホールCH3とを跨ぐように形成される。第2の透明導電膜7は、コンタクトホールCH2を通して第1の透明導電膜6に接続すると共に、コンタクトホールCH3を通して第1の導電膜2に接続する。この第2の透明導電膜7によって、第1の導電膜2と第1の透明導電膜6とが電気的に接続される。その結果、第1の導電膜2である引き出し配線47b1と、第2の導電膜5であるソース配線44とが電気的に接続されることとなる。

【0072】

このように実施の形態1の配線変換部45は、二層の透明導電膜を用いて構成される。FFSモードのTFTアレイ基板100は、必然的に二層の透明導電膜（画素電極55と対向電極56）を備えるため、配線変換部45の二層の透明導電膜として、画素電極55と同層の第1の透明導電膜6と、対向電極56と同層の第2の透明導電膜7を用いることにより、製造工程数を増やすことなく、配線変換部45を形成することができる（具体的な形成工程は後述する）。

【0073】

また、配線変換部45において、第1の透明導電膜6は、第2の導電膜5の外周の端面を覆わないように形成される。つまり、半導体膜3、オーミックコンタクト膜4および第2の導電膜5の端部において、第1の透明導電膜6は端部が第1の絶縁膜8と接することなく形成される。それにより、第2の絶縁膜9を形成した後に、第1の透明導電膜6の端部に応力が集中することを回避できる。従って、第2の絶縁膜9の剥がれが生じ難く、第2の絶縁膜9の膜浮きによる歩留まりの低下を抑制することができる。

10

20

30

40

50

## 【0074】

さらに、配線変換部45では、第2の導電膜5の内側に、第2の導電膜5、半導体膜3およびオーミックコンタクト膜4の端面が露出される割り抜き部13を設け、その内部に第1の透明導電膜6を形成している。そのため、第1の透明導電膜6は、割り抜き部13の内部において、半導体層3、オーミックコンタクト膜4、第2の導電膜5の端面に接触することになる。よって、第2の導電膜5が積層膜である場合、第1の透明導電膜6は、その最上層のみならず下層にも接続することができる。

## 【0075】

従って、積層膜である第2の導電膜5の最上層と第1の透明導電膜6との電気的接続性が悪い場合においても、少なくとも第2の導電膜5の下層の金属膜に第1の透明導電膜6との電気的接続性の良い材料を用いていれば、第2の導電膜5と第1の透明導電膜6との良好な電気的接続性を得ることができる。例えば、二層構造の第2の導電膜5において、上層がAl系の金属膜であり、第1の透明導電膜6がITOである場合でも、第2の導電膜5の下層にITOとの電気的接続性の良い材料を用いることにより、第2の導電膜5と第1の透明導電膜6との良好な電気的接続性を得ることができる。よって、配線材料の選択肢を増やすことが可能となる。

## 【0076】

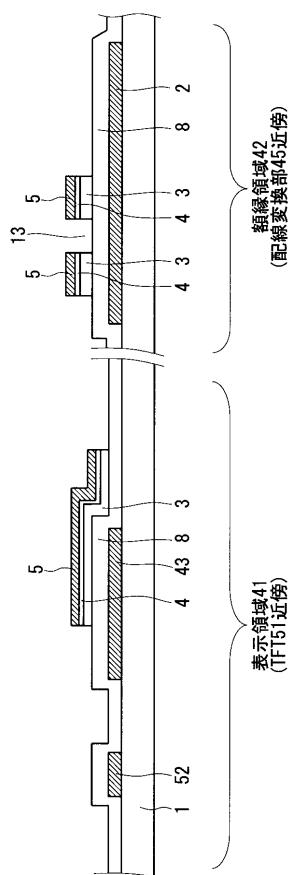

続いて、実施の形態1に係る液晶表示装置の製造方法について、図8～図13を用いて説明する。図8～図13は、実施の形態1に係るTFTアレイ基板100の製造工程を示した断面図である。これらの各図においては、左側にTFT51が形成される表示領域41が示され、右側に配線変換部45が形成される額縁領域42が示されている。

## 【0077】

まず、ガラスなどの透明な絶縁性材料よりなる基板1上の全面に、例えば、スパッタ法や蒸着法などを用いて第1の導電膜2を成膜する。第1の導電膜2の材料としては、例えばCr、Al、Ta、Ti、Mo、W、Ni、Cu、Au、Ag、またはこれらを主成分とする合金膜、あるいはそれらの2以上から成る積層膜を用いることができる。

## 【0078】

次に、レジストを塗布し、当該レジストをフォトマスク上から露光し、レジストを感光させる。感光させたレジストを現像して、レジストをパターニングし、レジストパターンを形成する。以下では、このレジストパターンを形成するための一連の工程を「フォトリソグラフィ工程」と呼ぶ。

## 【0079】

そして、このレジストパターンをマスクとするエッチングにより第1の導電膜2をパターニングし、レジストパターンを除去する。以下では、レジストパターンを用いたパターニングの工程を「微細加工工程」と呼ぶ。

## 【0080】

その結果、図8に示すように、表示領域41にはゲート配線43（ゲート電極）、共通配線52を含む第1の導電膜2のパターンが形成される。具体的には、表示領域41にゲート配線43、共通配線52が形成され、額縁領域42には配線変換部45に引き込まれる引き出し配線47b1が形成される。

## 【0081】

その後、基板1全面に、第1の導電膜2のパターンを覆うように、例えばプラズマCVD、常圧CVD、減圧CVDなどを用いて、第1の絶縁膜8、半導体層3およびオーミックコンタクト膜4をこの順に成膜する。

## 【0082】

第1の絶縁膜8としては、窒化シリコン、酸化シリコンなどを用いることができる。第1の絶縁膜8はゲート電極としても機能するため、ピンホールなどの膜欠損発生による短絡を防止する目的で、複数回に分けて成膜することが好ましい。半導体層3としては、非晶質シリコン、多結晶ポリシリコンなどを用いることができる。また、オーミックコンタクト膜4としては、リン（P）などの不純物を高濃度に添加したn型非晶質シリコンやn

10

20

30

40

50

型多結晶シリコンなどを用いることができる。

【0083】

さらに、成膜したオーミックコンタクト膜4の上に、例えばスパッタ法や蒸着法などにより、第2の導電膜5を成膜する。第2の導電膜5は、Cr、Al、Ta、Ti、Mo、W、Ni、Cu、Au、Agやこれらを主成分とする合金膜を用いた積層膜を用いる。

【0084】

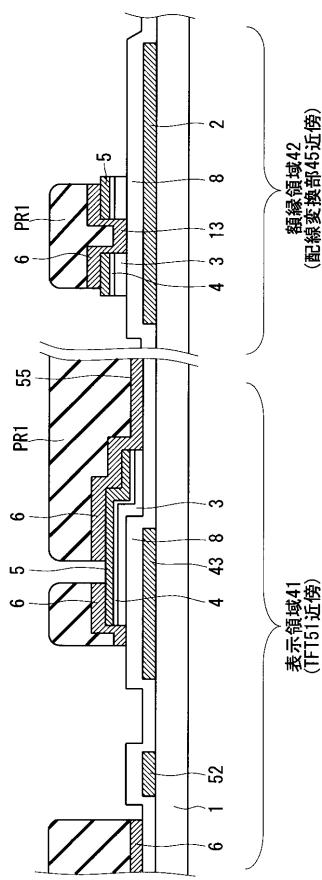

その後、フォトリソグラフィ工程および微細加工工程により、第2の導電膜5をパターニングする。これにより、表示領域41には、ソース配線44、ソース電極53およびドレイン電極54のパターンが形成される。但し、この段階では、ソース電極53とドレイン電極54との間は分離されていない(つまり、半導体膜3のチャネル領域上に第2の導電膜5が残存している)。この工程では、配線変換部45の第2の導電膜5も同時にパターニングするが、このとき配線変換部45の第2の導電膜5には割り抜き部13に対応する開口を設ける。

【0085】

続いて、パターニングされた第2の導電膜5をマスクとして、もしくは第2の導電膜5のパターニングに使用したレジストパターンをマスクとして(つまり、第2の導電膜5をパターニングに使用したレジストパターンを残した状態で)、オーミックコンタクト膜4および半導体層3をエッチングする。それにより、図9に示すように、第2の導電膜5に覆われていない部分のオーミックコンタクト膜4および半導体層3が除去される。その結果、表示領域41では半導体膜3およびオーミックコンタクト膜4がソース配線44と同じ形状にパターニングされる。また額縁領域42においては、第2の導電膜5、オーミックコンタクト膜4および半導体膜3を貫通する割り抜き部13が形成される。

【0086】

このように、第2の導電膜5とオーミックコンタクト膜4および半導体層3のパターニングは、1回のフォトリソグラフィ工程で連続して行われる。

【0087】

次に、スパッタ法などにより、ITOなどの透明導電膜を基板1全面に成膜する。本実施の形態では、一般的なITOを非結晶状態で成膜した。そして、フォトリソグラフィ工程によりレジストパターンPR1を形成し、それを用いた微細加工工程により、透明導電膜をパターニングすることによって、図10のように第1の透明導電膜6を形成する。このパターニングには、非結晶状態のITOのエッチングに適当なシュウ酸系などの弱酸のエッチャントによるウエットエッチングを使用することができる。

【0088】

この工程により、表示領域41には、第2の導電膜5上を覆う第1の透明導電膜6と画素電極55が形成される。また図10に示すように、半導体膜3のチャネル領域上の透明導電膜はこのとき除去される(つまり第1の透明導電膜6はソース領域側とドレイン領域側に分離される)。なお、画素電極55を含む第1の透明導電膜6の配置及び形状は、この工程により確定する。

【0089】

また、額縁領域42においては、第1の透明導電膜6が、第2の導電膜5の上面および割り抜き部13の内部に形成される。またこのとき、額縁領域42の第1の透明導電膜6のパターンは、第2の導電膜5のパターンよりも若干狭い幅で形成される。

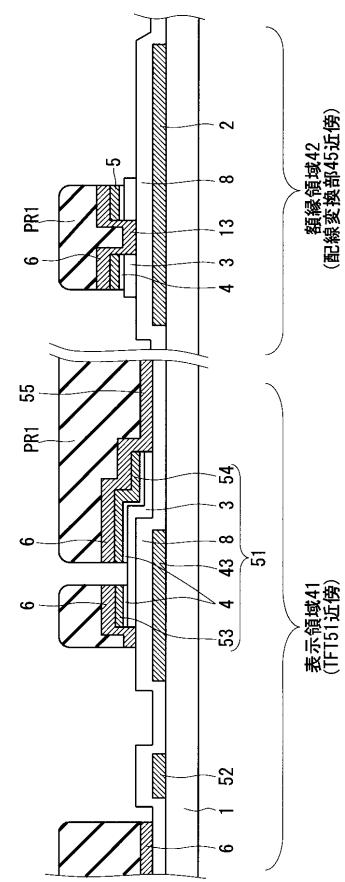

【0090】

続いて、上記のレジストパターンPR1をマスクにするエッチングにより、チャネル領域上の第2の導電膜5およびオーミックコンタクト膜4を順次除去する。チャネル領域上の第2の導電膜5がエッチングにより除去されることで、第2の導電膜5がソース電極53とドレイン電極54とに分離される。これにより、図11に示すように、TFT51のチャネル領域となる半導体層3が、ソース電極53とドレイン電極54間に露出し、TFT51の構成が完成する。

【0091】

10

20

30

40

50

またこのとき、額縁領域42では、第1の透明導電膜6から食み出た部分のオーミックコンタクト膜4および第2の導電膜5が除去されるため、オーミックコンタクト膜4、第2の導電膜5および第1の透明導電膜6の端部がほぼ同じ位置になり、且つ、それらの端部が半導体膜3よりも後退した位置になる。

#### 【0092】

レジストパターンPR1を除去した後、図12に示すように、基板1の全面に第2の絶縁膜9を成膜する。これにより、画素電極55を含む第1の透明導電膜6、並びに半導体膜3のチャネル領域が、第2の絶縁膜9により覆われる。第2の絶縁膜9としては、例えば窒化シリコンや酸化シリコンなどの無機絶縁膜を用いることができ、成膜手法としてはCVD法などを用いることができる。また、第2の絶縁膜9は、窒化シリコン、酸化シリコンなどの無機絶縁膜の上に、更に塗布型の（塗布により形成される）絶縁膜などを形成した積層膜としてもよい。10

#### 【0093】

上で説明したように、本実施の形態では、額縁領域42（配線変換部45）において、第1の透明導電膜6が、半導体膜3、オーミックコンタクト膜4および第2の導電膜5の外周の端面を覆わない構成をとることにより、第2の絶縁膜9を形成した後に第1の透明導電膜6の端部に応力が集中することを抑制し、それによって第2の絶縁膜9の膜浮きが防止される。

#### 【0094】

従って、第2の絶縁膜9の成膜条件については、例えば、第1の透明導電膜6の透過率が向上する成膜条件や、或いは第2の絶縁膜9にコンタクトホールCH2を形成したときに第1の透明導電膜6で良好なコンタクト端面形状を形成できる成膜条件など、膜浮き防止に特化しない条件を採用しても、膜浮きの発生頻度を低減することができる。また、第1の透明導電膜6の形成条件についても、透過率が向上する成膜条件を採用すると第2の絶縁膜9の膜浮き発生を助長することがあるが、上記の構成により膜浮き発生頻度を低減することができる。20

#### 【0095】

なお、第1の透明導電膜6の透過率が向上する第2の絶縁膜9の成膜条件としては、成膜時の材料ガス中の酸素含有量の高い成膜条件、より具体的には、酸化シリコン膜を形成する成膜条件、酸素を含む窒化シリコン膜を形成する成膜条件などが挙げられる。一方、第2の絶縁膜9にコンタクトホールCH2を形成したときに第1の透明導電膜6で良好なコンタクト端面形状を形成できる第2の絶縁膜9の成膜条件としては、窒化シリコン膜の成膜時の材料ガス中に窒素含有量の高い成膜条件、より具体的には、成膜時の材料ガス中において、窒素ガス或いはアンモニアガスの分圧比が、シリコンを含むガス（シランガス、ジシランガス、TEOSガスなど）に対して2以上である成膜条件が挙げられる。30

#### 【0096】

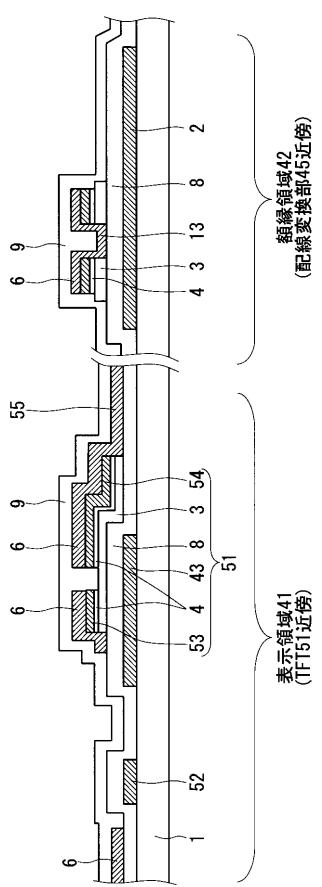

更に、ITOなどの第1の透明導電膜6の透過率が向上する成膜条件としては、スパッタ法などによる成膜時に酸素濃度が高い条件を選択することが挙げられる。第2の絶縁膜9および第1の透明導電膜6の成膜条件は、TFTアレイ基板100の用途に応じて使い分けなければならない。40

#### 【0097】

続いて、フォトリソグラフィ工程および微細加工工程により、第2の絶縁膜9および第1の絶縁膜8に、コンタクトホールCH1～CH3を形成する。これにより、表示領域41においては、共通配線52に達するコンタクトホールCH1が形成される。また、額縁領域42においては、第1の透明導電膜6に達するコンタクトホールCH2が、割り抜き部13を内包する位置に形成されると共に、第1の導電膜2に達するコンタクトホールCH3が形成される。

#### 【0098】

次に、第2の絶縁膜9の上に、ITOなどの透明導電膜をスパッタ法などにより基板1全面に成膜する。そして、フォトリソグラフィ工程および微細加工工程により、この透明

10

20

30

40

50

導電膜をパターニングして第2の透明導電膜7を形成する。これにより、図13に示すように、表示領域41では、画素電極55に対抗する位置に対向電極56が形成される。また対向電極56は、コンタクトホールCH1を介して共通配線52と接続するように形成される。額縁領域42では、第2の透明導電膜7が、コンタクトホールCH2およびコンタクトホールCH3を介して第1の導電膜2と第1の透明導電膜6とを電気的に接続するように形成される。

#### 【0099】

なお、額縁領域42に配設される外部接続端子48b1は、第1の導電膜2である引き出し配線47b1にコンタクトホールを介して接続する第2の透明導電膜7によって構成されている。この外部接続端子48b1は、配線変換部45と同時に形成される。

10

#### 【0100】

以上の工程により、実施の形態1のTFTアレイ基板100が完成する。

#### 【0101】

完成したTFTアレイ基板100の上と、別途作製された対向基板60の上にそれぞれ配向膜61を形成し、それら配向膜61にラビングなどの手法で、液晶との接触面に一方向に微小な傷をつける配向処理を施す。そして、TFTアレイ基板100または対向基板60の周縁部にシール材を塗布し、TFTアレイ基板100と対向基板60とを、それらの配向膜61が向き合うように所定の間隔で貼り合わせる。その後、真空注入法などにより、TFTアレイ基板100と対向基板60との間に液晶を注入して封止する。そしてTFTアレイ基板100および対向基板60のそれぞれに偏光板65を貼り付け、駆動回路を接続して液晶表示パネルを形成する。

20

#### 【0102】

その後、液晶表示パネルの背面側となるTFTアレイ基板100の裏面側に、位相差板などの光学フィルム66を介して、バックライトユニット67を配設し、それらを樹脂や金属などよりなるフレーム内に収納することにより、液晶表示装置が完成する。

#### 【0103】

実施の形態1の液晶表示装置においては、透明導電膜のパターン密度が比較的疎な領域である額縁領域42に配設される配線変換部45において、第1の透明導電膜6が、第2の導電膜5の端面を覆うことなく形成された構成となっており、それにより、第1の透明導電膜6上を覆う第2の絶縁膜9の膜浮きの発生が抑制される。

30

#### 【0104】

さらに、配線変換部45では、第2の導電膜5の内側に割り抜き部13を設け、割り抜き部13内に第1の透明導電膜6が形成された構成となっている。それにより、第1の透明導電膜6は、割り抜き部13に露出した第2の導電膜5の下層の金属膜に接続される。よって、第2の導電膜5の最上層と第1の透明導電膜6との間の電気的接続性が悪い場合でも、第2の導電膜5の下層と第1の透明導電膜6との間の電気的接続性が良ければ、第2の導電膜5と第1の透明導電膜6との良好な電気的接続性を得ることができる。

#### 【0105】

なお、以上の説明では、本発明に係る配線構造を、TFTアレイ基板100の額縁領域42に配置される配線変換部45に適用した例を示したが、額縁領域42における配線（例えばソース配線44の延在部分）に適用してもよい。額縁領域42における配線の周辺も、表示領域41に比較して透明導電膜のパターン密度が疎な領域であるため、第2の絶縁膜9の膜浮きが発生し易いが、当該配線に本発明の配線構造を適用することにより、第2の絶縁膜9の膜浮きの発生を抑えることができる。

40

#### 【0106】

図14は、本実施の形態を額縁領域42に延設されたソース配線44（ソース配線44の延在部分）に適用した場合における、当該ソース配線44の構成を示す断面図である。同図は、例えば図5のB1-B2線に沿った断面に対応する。

#### 【0107】

この場合、図14に示すように、ソース配線44である第2の導電膜5の内部に、第2

50

の導電膜 5、オーミックコンタクト膜 4 および半導体膜 3 が除去された割り抜き部 13 が設けられる。そして第 2 の導電膜 5 の上に配設される第 1 の透明導電膜 6 は、割り抜き部 13 に露出した第 2 の導電膜 5、オーミックコンタクト膜 4 および半導体膜 3 の端面を覆い、且つ、第 2 の導電膜 5、オーミックコンタクト膜 4 および半導体膜 3 の外側端面を覆わないように形成される。そして、その上に第 2 の絶縁膜 9 が、第 2 の導電膜 5、オーミックコンタクト膜 4 および半導体膜 3 の外側端面を覆うように形成される。割り抜き部 13 は、図 15 に示すように、ソース配線 44 に所定の間隔で設ければよい。

【0108】

この構成により、ソース配線 44 においても上記の配線変換部 45 と同様の効果が得られる。つまり、ソース配線 44 における第 2 の絶縁膜 9 の膜浮きを防止できる。さらに、第 2 の導電膜 5 の最上層に第 1 の透明導電膜 6 との電気的接続性が悪い材料が用いられた場合でも、第 2 の導電膜 5 と第 1 の透明導電膜 6 との間で良好な電気的接続性を得ることができる。

10

【0109】

また、本実施の形態の TFT アレイ基板 100 では、第 1 の透明導電膜 6 により形成された平板状の画素電極 55 の上方に、第 2 の透明導電膜 7 により形成された櫛歯状の対向電極 56 が配置される構成とした。しかし、FFS モードの液晶表示装置においては、画素電極 55 の形状と対向電極 56 の形状を上記と逆にしてもよい。すなわち、第 1 の透明導電膜 6 により櫛歯状の画素電極 55 を形成してもよい。但し、この場合には、平板状の対向電極 56 を、櫛歯状の画素電極 55 よりも下層に配置する必要があるため、平板状の対向電極 56 を構成する透明導電膜は、第 2 の透明導電膜 7 とは別に形成する必要がある。

20

【0110】

< 実施の形態 2 >

図 16 および図 17 は、実施の形態 2 に係る TFT アレイ基板 100 の配線変換部 45 の構成を示す図である。図 16 は配線変換部 45 の平面図であり、図 17 はその D1 - D2 線に沿った断面図である。

【0111】

実施の形態 2 の配線変換部 45 は、実施の形態 1 の構成（図 5、図 7）に対し、第 2 の導電膜 5 の内側に当該第 2 の導電膜 5 の端面を露出させる割り抜き部 13 と、第 2 の透明導電膜 7 を第 1 の透明導電膜 6 に接続させるためのコンタクトホール CH2 とを、互いに異なる位置に配設したものである。図 16 の例では、コンタクトホール CH2 は 2 箇所に設けられ、割り抜き部 13 はその間に配設されている。また、第 2 の透明導電膜 7 を第 1 の導電膜 2 に接続させるためのコンタクトホール CH3 も 2 箇所に設けられている。

30

【0112】

この構成によれば、実施の形態 1 と比較して、第 2 の絶縁膜 9 上で第 2 の透明導電膜 7 が乗り越える段差が小さくなる。そのため、第 2 の透明導電膜 7 が段差部で断線する確率が低下し、より信頼性の高い配線変換部を得ることができる。また、実施の形態 1 と同様に、膜浮きの発生の抑制の効果、並びに、第 1 の透明導電膜 6 と第 2 の導電膜 5 との間で良好な電気的接続性が得られる効果も得られる。

40

【0113】

なお、本実施の形態の配線変換部 45 の製造方法は、割り抜き部 13 およびコンタクトホール CH2 の形成位置を除いて実施の形態 1 と同様である。

【0114】

< 実施の形態 3 >

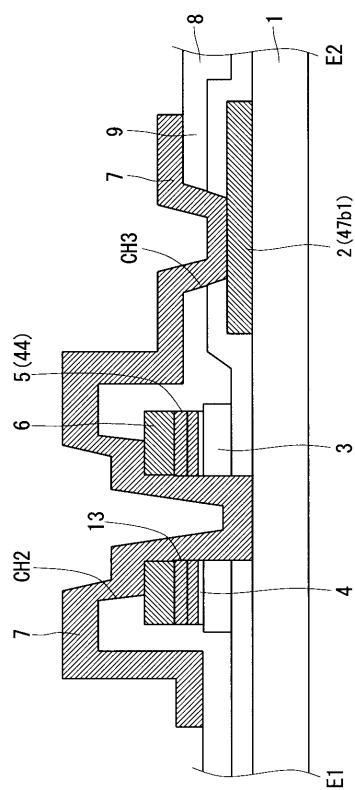

図 18 および図 19 は、実施の形態 3 に係る TFT アレイ基板 100 の配線変換部 45 の構成を示す図である。図 18 は配線変換部 45 の平面図であり、図 19 はその E1 - E2 線に沿った断面図である。

【0115】

実施の形態 3 の配線変換部 45 は、実施の形態 1 の構成（図 5、図 7）に対し、第 1 の

50

透明導電膜 6 にも割り抜き部 13 に対応する開口を設けたものである。つまり、割り抜き部 13 は、割り抜き部 13 の内部には形成されず、第 2 の導電膜 5 の上面のみに形成される。

【 0 1 1 6 】

また、コンタクトホール CH 2 は、実施の形態 1 と同様に割り抜き部 13 を内包するよう 10 に形成される。その結果、割り抜き部 13 に露出した第 2 の導電膜 5 、オーミックコンタクト膜 4 および半導体膜 3 の端面は、第 2 の透明導電膜 7 によって覆われることになる。

【 0 1 1 7 】

この構成によれば、配線変換部 45 内のどの部位においても、第 1 の透明導電膜 6 の端部が第 1 の絶縁膜に接することができないため、第 1 の透明導電膜 6 の全ての端部で応力の集中が抑制され、第 2 の絶縁膜 9 の膜浮きを抑制することができる。さらに、積層膜である第 2 の導電膜 5 の最上層と第 1 の透明導電膜 6 との電気的接続性が悪い場合においても、第 2 の透明導電膜 7 と第 2 の導電膜 5 の何れかの層との電気的接続性が良ければ、第 1 の透明導電膜 6 と第 2 の導電膜 5 との間で良好な電気的接続性が得られる。

【 0 1 1 8 】

なお、本実施の形態の配線変換部 45 の製造方法は、第 1 の透明導電膜 6 に割り抜き部 13 に対応する開口を設けることを除いて、実施の形態 1 と同様である。

【 0 1 1 9 】

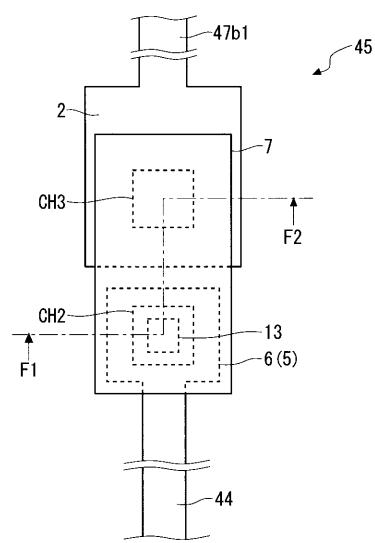

< 実施の形態 4 >

図 20 および図 21 は、実施の形態 4 に係る TFT アレイ基板 100 の配線変換部 45 の構成を示す図である。図 20 は配線変換部 45 の平面図であり、図 21 はその F1 - F2 線に沿った断面図である。

【 0 1 2 0 】

実施の形態 4 の配線変換部 45 は、実施の形態 1 の構成（図 5 、図 7 ）に対し、第 2 の導電膜 5 の下方にオーミックコンタクト膜 4 および半導体層 3 を配設しないようにしたものである。

【 0 1 2 1 】

この構成によれば、実施の形態 1 と比較して、第 2 の絶縁膜 9 上で第 2 の透明導電膜 7 が乗り越える段差が小さくなる。そのため、第 2 の透明導電膜 7 が段差部で断線する確率が低下し、より信頼性の高い配線変換部を得ることができる。また、実施の形態 1 と同様に、膜浮きの発生の抑制の効果、並びに、第 1 の透明導電膜 6 と第 2 の導電膜 5 との間で良好な電気的接続性が得られる効果も得られる。

【 0 1 2 2 】

なお、実施の形態 4 に係る配線変換部 45 の製造方法は、実施の形態 1 の場合とほぼ同じであるが、オーミックコンタクト膜 4 および半導体層 3 のパターニングと第 2 の導電膜 5 のパターニングとを、それぞれレジストパターンを用いて行う必要がある。

【 0 1 2 3 】

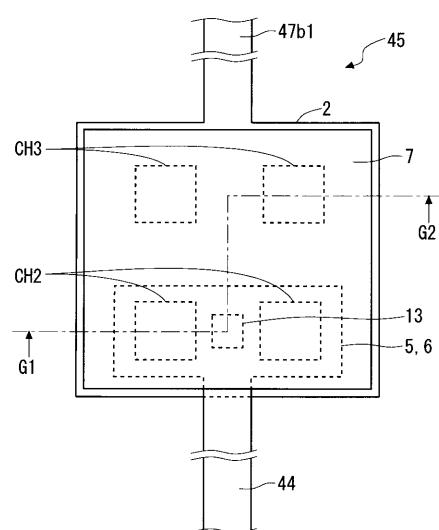

< 実施の形態 5 >

図 22 および図 23 は、実施の形態 5 に係る TFT アレイ基板 100 の配線変換部 45 の構成を示す図である。図 22 は配線変換部 45 の平面図であり、図 23 はその G1 - G2 線に沿った断面図である。

【 0 1 2 4 】

実施の形態 5 の配線変換部 45 は、実施の形態 1 の構成（図 5 、図 7 ）に対し、割り抜き部 13 とコンタクトホール CH 2 とを互い異なる位置にし、且つ、第 2 の導電膜 5 の下方にオーミックコンタクト膜 4 および半導体層 3 を配設しないようにしたものである。言い換えれば、実施の形態 2 の構成（図 16 、図 17 ）に対し、実施の形態 4 を適用したものである。

【 0 1 2 5 】

この構成によれば、実施の形態 2 と比較して、第 2 の絶縁膜 9 上で第 2 の透明導電膜 7

10

20

30

40

50

が乗り越える段差が小さくなる。そのため、第2の透明導電膜7が段差部で断線する確率が低下し、より信頼性の高い配線変換部を得ることができる。また、実施の形態1と同様に、膜浮きの発生の抑制の効果、並びに、第1の透明導電膜6と第2の導電膜5との間で良好な電気的接続性が得られる効果も得られる。

【0126】

なお、本実施の形態の配線変換部45の製造方法は、割り抜き部13およびコンタクトホールCH2の形成位置を除いて、実施の形態4と同様である。

【0127】

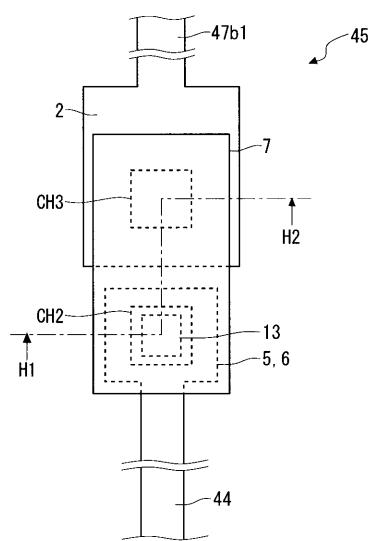

<実施の形態6>

図24および図25は、実施の形態6に係るTFTアレイ基板100の配線変換部45の構成を示す図である。図24は配線変換部45の平面図であり、図25はそのH1-H2線に沿った断面図である。

10

【0128】

実施の形態6の配線変換部45は、実施の形態1の構成(図5、図7)に対し、第1の透明導電膜6にも割り抜き部13に対応する開口を設け、且つ、第2の導電膜5の下方にオーミックコンタクト膜4および半導体層3を配設しないようにしたものである。言い換えれば、実施の形態3の構成(図18、図17)に対し、実施の形態4を適用したものである。

【0129】

この構成によれば、実施の形態3と同様に、配線変換部45内のどの部位においても、第1の透明導電膜6の端部が第1の絶縁膜に接することができないため、第1の透明導電膜6の全ての端部で応力の集中が抑制され、第2の絶縁膜9の膜浮きを抑制することができる。さらに、実施の形態3と比較して、第2の絶縁膜9上で第2の透明導電膜7が乗り越える段差が小さくなるので、第2の透明導電膜7が段差部で断線する確率が低下し、より信頼性の高い配線変換部を得ることができる。また、実施の形態1と同様に、第1の透明導電膜6と第2の導電膜5との間で良好な電気的接続性が得られる効果も得られる。

20

【0130】

なお、本実施の形態の配線変換部45の製造方法は、第1の透明導電膜6に割り抜き部13に対応する開口を設けることを除いて、実施の形態4と同様である。

【0131】

30

以上の各実施の形態では、本発明をFFSモードのTFTアレイ基板に適用した例を示した。その理由は、FFSモードのTFTアレイ基板が二層の透明導電膜を備えるため、その製造工程の増加を抑えつつ本発明を適用可能だからである。本発明は、透明導電膜を配線または電極として使用する薄膜電子デバイスに広く適用可能である。TFTアレイ基板を備える液晶表示装置以外の薄膜電子デバイスとしては、例えば、有機EL表示装置などの平面型表示装置(フラットパネルディスプレイ)や、イメージセンサ等の光電変換装置が挙げられる。それらのTFTアレイ基板に設けられる配線や配線変換部においても、金属パターン上に透明導電膜パターンが設けられ、さらに透明導電膜パターン上に絶縁膜が設けられる構造に対し、本発明は適用可能である。

【0132】

40

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0133】

1 基板、2 第1の導電膜、3 半導体膜、4 オーミックコンタクト膜、5 第2の導電膜、6 第1の透明導電膜、7 第2の透明導電膜、8 第1の絶縁膜、9 第2の絶縁膜、13 割り抜き部、43 ゲート配線、44 ソース配線、45 配線変換部、50 画素、51 TFT、52 共通配線、53 ソース電極、54 ドレイン電極、55 画素電極、56 対向電極。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 23/532 (2006.01) H 01 L 29/78 6 1 2 C

H 01 L 29/786 (2006.01)

(72)発明者 外 徳仁

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 田辺 正樹

(56)参考文献 特開2002-214638 (JP, A)

特開平11-288007 (JP, A)

特開2009-117620 (JP, A)

国際公開第2008/015813 (WO, A1)

特開2000-077666 (JP, A)

特開平07-263700 (JP, A)

特開2006-113571 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 136 - 1 / 1368

G 09 F 9 / 30 - 9 / 46

H 01 L 21 / 3205 - 21 / 3213, 21 / 336, 21 / 768,

23 / 522, 23 / 532, 27 / 32, 29 / 786