(72) 발명자

히다 도시카즈

일본 도쿄도 미나토구 시바우라 1-1-1 가부시끼가

이샤 도시바 지데키 자이산부 나이

기초나이 가즈야

일본 도쿄도 미나토구 시바우라 1-1-1 가부시끼가

이샤 도시바 지데키 자이산부 나이

---

야노 준지

일본 도쿄도 미나토구 시바우라 1-1-1 가부시끼가

이샤 도시바 지데키 자이산부 나이

## 특허청구의 범위

### 청구항 1

데이터 소거 단위로서 복수의 블록들을 포함하는 비휘발성 메모리;

각 블록의 데이터가 소거되는 소거 시간을 측정하는 측정부; 및

각 블록에 대하여 공백 상태와 사용중 상태 중 하나를 나타내는 상태값과 상기 소거 시간을 연관시키는 블록 테이블을 가지는 블록 제어기;

단기간 내에 재기록이 집중적으로 발생되는 블록들을 검출하는 검출기;

상기 블록 테이블의 정보에 기초하여, 오래된 소거 시간을 가지는 공백 상태 블록을 제 1 블록으로서 선택하는 제 1 선택기;

상기 블록 테이블의 정보에 기초하여, 오래된 소거 시간을 가지는 사용중 상태 블록을 제 2 블록으로서 선택하는 제 2 선택기; 및

상기 제 1 블록이 상기 검출기에 의해 검출된 블록들에 포함되는 경우, 상기 제 2 블록의 데이터를 상기 제 1 블록으로 이동시키는 평준화부를 구비하는 메모리 시스템.

### 청구항 2

제 1 항에 있어서, 상기 제 1 선택기는, 상기 제 2 블록의 데이터가 상기 제 1 블록으로 이동되는 경우, 블록을 재선택하는 것인 메모리 시스템.

### 청구항 3

제 1 항에 있어서, 상기 블록 제어기는 각 블록의 소거 횟수를 카운트하여, 그 소거 횟수를 상기 블록 테이블에 저장하는 것인 메모리 시스템.

### 청구항 4

제 3 항에 있어서, 상기 평준화부는, 상기 제 1 블록이 상기 검출기에 의해 검출되는 블록들에 포함되는 경우 또는 상기 제 1 블록과 상기 제 2 블록의 소거 횟수의 차가 임계값을 초과하는 경우에, 상기 제 2 블록의 데이터를 상기 제 1 블록으로 이동시키는 것인 메모리 시스템.

### 청구항 5

제 1 항에 있어서, 상기 검출기는 블록들의 소거 시간의 차가 큰 경계를 검출하고, 상기 경계보다 더 새로운 소거 시간을 가지는 블록을 단기간 내에 재기록이 집중적으로 발생되는 블록으로서 검출하는 것인 메모리 시스템.

### 청구항 6

제 1 항에 있어서, 상기 블록 테이블은, 단기간 내에 재기록이 블록에 집중적으로 발생되는지 여부를 나타내는 플래그를 저장하는 것인 메모리 시스템.

### 청구항 7

제 1 항에 있어서,

상기 검출기는, 사용중 상태 블록들 중에서, 제 3 블록의 소거 시간과, 소거 시간이 상기 제 3 블록의 소거 시간 다음으로 새로운 제 4 블록의 소거 시간 사이의 차를 산출하고, 이 차가 미리 결정된 간격 보다 더 큰 경우, 전체 블록들 중에서 상기 제 4 블록의 소거 시간 보다 더 새로운 소거 시간을 가지는 블록들을 검출하는 것인 메모리 시스템.

### 청구항 8

제 7 항에 있어서,

상기 검출기는 사용중 상태의 블록들의 정보를 소거 시간순으로 정렬하는 정렬부 및 상기 정렬된 정보에 기초하여 상기 제 3 블록과 상기 제 4 블록의 소거 시간의 차를 산출하는 판정부를 포함하는 것인 메모리 시스템.

#### 청구항 9

제 1 항에 있어서,

상기 검출기는 사용중 상태 블록들에 대한 현재 시각과 소거 시간 사이의 차를 산출하고, 그 차가 임계값을 초과하는 블록들 중에서 소거 시간이 가장 새로운 제 5 블록을 판정하고, 전체 블록들 중에서 상기 제 5 블록의 소거 시간보다 새로운 소거 시간을 가지는 블록들을 검출하는 것인 메모리 시스템.

#### 청구항 10

제 9 항에 있어서,

상기 검출기는 사용중 상태 블록들의 정보를 소거 시간순으로 정렬하는 정렬부 및 상기 정렬된 정보에 기초하여 현재 시각과 소거 시간 사이의 차가 임계값을 초과하는지 여부를 판정하는 판정부를 포함하는 것인 메모리 시스템.

#### 청구항 11

제 1 항에 있어서, 상기 제 1 선택기는 가장 오래된 소거 시간을 가지는 공백 상태 블록을 상기 제 1 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 12

제 3 항에 있어서, 상기 제 1 선택기는, 가장 오래된 소거 시간을 가지는 블록으로부터 시작하는 미리 결정된 개수의 공백 상태 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 1 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 13

제 3 항에 있어서, 상기 제 1 선택기는, 가장 오래된 소거 시간을 가지는 블록으로부터 시작하는 미리 결정된 비율의 공백 상태 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 1 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 14

제 3 항에 있어서, 상기 제 1 선택기는, 미리 결정된 시간 보다 더 오래된 소거 시간을 가지는 공백 상태 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 1 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 15

제 1 항에 있어서, 상기 제 2 선택기는, 가장 오래된 소거 시간을 가지는 사용중 상태 블록을 상기 제 2 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 16

제 3 항에 있어서, 상기 제 2 선택기는, 가장 오래된 소거 시간을 가지는 블록으로부터 시작하는 미리 결정된 개수의 사용중 상태 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 2 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 17

제 3 항에 있어서, 상기 제 2 선택기는, 가장 오래된 소거 시간을 가지는 블록으로부터 시작하는 미리 결정된 비율의 사용중 상태 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 2 블록으로서 선택하는 것인 메모리 시스템.

#### 청구항 18

제 3 항에 있어서, 상기 제 2 선택기는, 미리 결정된 시간 보다 더 오래된 소거 시간을 가지는 사용중 상태 블

록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 2 블록으로서 선택하는 것인 메모리 시스템.

### 청구항 19

제 3 항에 있어서, 상기 비휘발성 메모리로부터 판독되는 데이터의 에러 수를 산출하는 에러 체크 및 정정 회로를 더 구비하며,

상기 블록 테이블은 각 블록의 에러 수를 저장하며,

상기 제 2 선택기는 미리 결정된 값보다 더 큰 에러 수를 가지는 사용중 상태 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 상기 제 2 블록으로서 선택하는 것인 메모리 시스템.

### 청구항 20

제 1 항에 있어서, 상기 측정부는, 전체 블록에서 실행되는 소거 횟수를 카운트하는 카운터를 포함하며,

상기 소거 시간은 상기 카운터의 카운트값에 대응하는 것인 메모리 시스템.

### 청구항 21

제 1 항에 있어서, 상기 측정부는 각 블록의 데이터가 소거되는 소거 타이밍을 측정하며,

상기 소거 시간은 상기 소거 타이밍에 대응하는 것인 메모리 시스템.

### 청구항 22

제 1 항에 있어서, 상기 측정부는 각 블록의 데이터가 소거될 때 상기 메모리 시스템의 전력 공급 시간을 측정하며,

상기 소거 시간은 상기 전력 공급 시간에 대응하는 것인 메모리 시스템.

## 명세서

### 기술 분야

[0001]

본 발명은 메모리 시스템에 관한 것으로, 예를 들어 NAND 플래시 메모리를 포함하는 메모리 시스템에 관한 것이다.

### 배경 기술

[0002]

최근, 비휘발성 반도체 메모리는, 대형 컴퓨터, 퍼스널 컴퓨터, 가전 제품, 휴대 전화기 등과 같이 여러 가지 부분에서 사용되고 있다. 특히, NAND 플래시 메모리는 전기적으로 재기록가능하고, 대용량 및 고집적 밀도로 형성될 수 있는 비휘발성 반도체 메모리이다. 또한, 최근에는, 하드 디스크 드라이브(HDD) 대신에 NAND 플래시 메모리를 사용하는 것이 고려되고 있다.

[0003]

NAND 플래시 메모리는 기록 처리를 수행하기 이전에 소거 처리를 필요로 하는 반도체 메모리이다. 그 서비스 수명은 재기록 동작의 횟수에 의존한다. NAND 플래시 메모리의 데이터 기록/소거 동작은, 기판과 제어 게이트 사이에 고전압을 인가함으로써 플로팅 게이트에 대하여 전자를 주입/방출시키는 것이다. 상기 동작을 복수회 수행하면, 플로팅 게이트 부근에 놓여 있는 게이트 산화막이 열화되고, 플로팅 게이트에 주입된 전자가 적출되어 데이터를 파괴한다. 즉, 재기록 동작의 횟수가 증가되는 경우, 데이터가 기록된 이후에 데이터가 유지되는 기간이 짧아지게 된다(유지 특성이 저하됨).

[0004]

또한, 퍼스널 컴퓨터 등을 사용함으로써 기록되는 데이터는, 시간적 국소성 및 영역적 국소성을 가진다(문헌 1: David A. Patterson 및 John L. Hennessy, "Computer Organization and Design: The hardware/software Interface", Morgan Kaufmann Pub, 2004/8/31). 따라서, 데이터를 기록하는 경우에 외부로부터 지정되는 어드레스에 데이터 항목들이 존재하므로 데이터 항목을 순차적으로 기록하면, 특정 영역에 단기간에 재기록 처리 즉, 소거 처리가 집중되므로, 소거 처리의 횟수가 크게 불균형화된다.

[0005]

NAND 플래시 메모리의 서비스 수명은 또한 소거 처리간의 간격에 의존하고, 상기 간격이 길어짐에 따라 상기 유지 특성이 좋아지고 상기 서비스 수명이 길어지게 된다(문헌 2: Neal Mielke et al., "Flash EEPROM Threshold Instabilities due to Charge Trapping During Program/Erase Cycling", IEEE TRANSACTIONS ON DEVICE AND

MATERIALS RELIABILITY, VOL. 4, NO. 3, SEPTEMBER 2004, PP.335-344). 또한, 이는 소거 간격이 짧아짐에 따라 유지 특성이 열화되고, 상기 서비스 수명이 짧아지게 됨을 나타낸다.

[0006] 또한, 기록 동작이 짧은 간격으로 수행되는 경우에도 소거 처리가 대응하는 장기간 동안 수행되지 않으면 유지 특성이 회복되는 것으로 알려져 있다(문현 3: Neal Mielke et al., "Recovery Effects in the Distributed Cycling of Flash Memories", 44th Annual International Reliability Physics Symposium, San Jose, 2006, pp.29-35).

### 발명의 상세한 설명

[0007] 본 발명의 양태에 따르면,

[0008] 데이터 소거 단위로서 복수의 블록들을 포함하는 비휘발성 메모리; 각 블록의 데이터가 소거되는 소거 시간을 측정하는 측정부; 및 각 블록에 대하여 공백 상태와 사용중 상태 중 하나를 나타내는 상태값과 상기 소거 시간을 연관시키는 블록 테이블을 가지는 블록 제어기; 단기간 내에 재기록이 집중적으로 발생되는 블록들을 검출하는 검출기; 상기 블록 테이블의 정보에 기초하여, 오래된 소거 시간을 가지는 공백 상태 블록을 제 1 블록으로서 선택하는 제 1 선택기; 상기 블록 테이블의 정보에 기초하여, 오래된 소거 시간을 가지는 사용중 상태 블록을 제 2 블록으로서 선택하는 제 2 선택기; 및 상기 제 1 블록이 상기 검출기에 의해 검출된 블록들에 포함되는 경우, 상기 제 2 블록의 데이터를 상기 제 1 블록으로 이동시키는 평준화부를 포함하는 메모리 시스템이 제공된다.

### 실시 예

[0045] 이하, 본 발명의 실시형태들을 첨부 도면을 참조하여 설명한다. 이하의 설명에서는, 동일한 기능 및 배열을 가지는 요소는 동일한 참조 부호로 표시하며 중복되는 설명은 필요한 경우에만 행한다.

[0046] [제 1 실시형태]

[0047] 이 실시형태의 메모리 시스템은, 호스트 장치가 실장되는 인쇄 회로 기판 상에 실장되고, 버스를 통하여 상기 호스트 장치와 데이터를 교환한다. 다른 방법으로, 이 실시형태의 메모리 시스템은 호스트 장치에 착탈 가능하게 부착되도록 설계된다. 이 메모리 시스템은 호스트 장치에 연결되며, 버스를 통하여 상기 호스트 장치와 데이터를 교환한다. 도 1은 이 실시형태의 메모리 시스템(1)을 포함하는 컴퓨터 시스템의 일례를 나타내는 개략도이다.

[0048] 컴퓨터 시스템은, 중앙 처리 장치(CPU)(2), 동적 랜덤 액세스 메모리(DRAM)과 같은 메인 메모리(3), 상기 메인 메모리(3)를 제어하기 위한 메모리 제어기(4) 및 이 실시형태의 메모리 시스템(1)을 구비한다. CPU(2), 메인 메모리(3) 및 메모리 시스템(1)은, 어드레스 버스(5) 및 데이터를 처리하는 데이터 버스(6)를 통하여 서로 연결되어 있다.

[0049] 이 컴퓨터 시스템에서, CPU(2)로 부터의 전송 요청(판독 요청 또는 기록 용청)이 기록 요청이면, CPU(2)의 데이터(외부로부터 입력된 데이터를 포함함) 또는 메인 메모리(3)의 데이터가 메모리 시스템(1)으로 전송된다. CPU(2)로부터의 전송 요청이 판독 요청이면, 메인 메모리(1)의 데이터가 CPU(2) 또는 메인 메모리(3)로 전송된다.

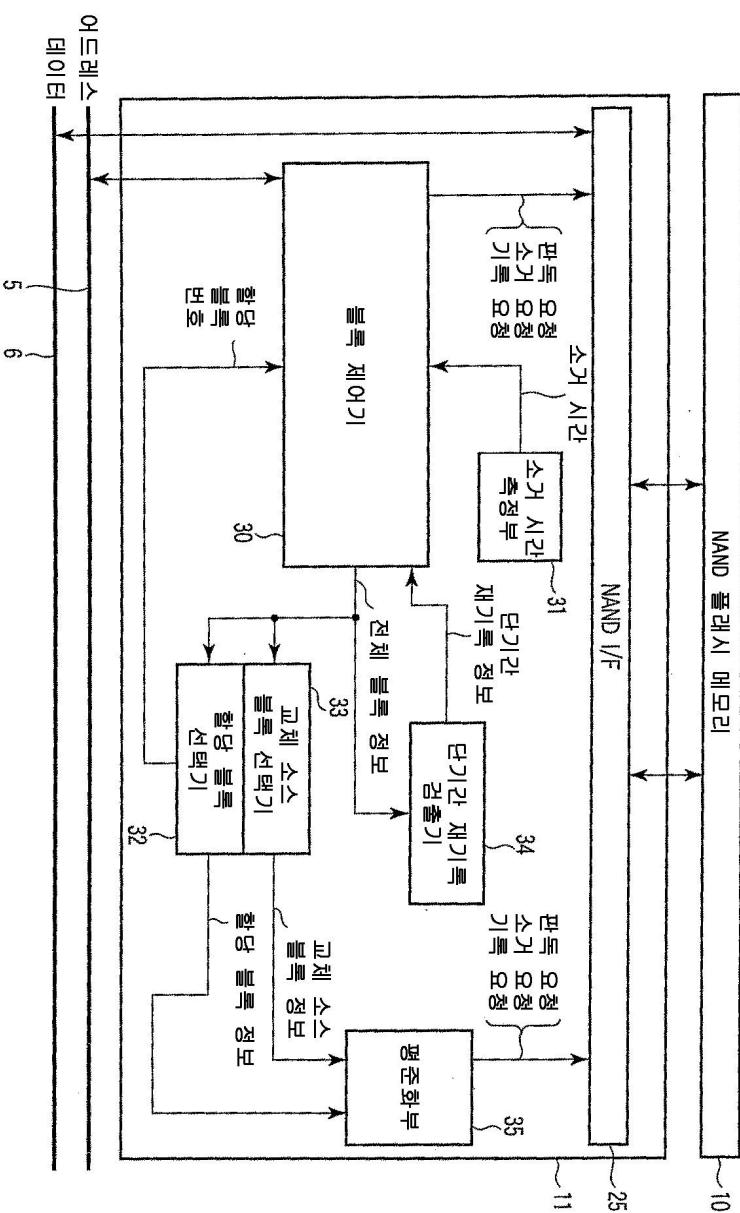

[0050] 메모리 시스템(1)은, 비휘발성 반도체 메모리의 일종인 NAND 플래시 메모리(10) 및 상기 NAND 플래시 메모리(10)를 제어하기 위한 NAND 제어기(11)를 구비한다. 이하에서는 메모리 시스템(1)의 구성의 일례를 설명한다.

[0051] [1. 메모리 시스템(1)의 구성]

[0052] 도 2는 메모리 시스템(1)의 구성을 나타내는 개략도이다. 메모리 시스템(1)은 NAND 플래시 메모리(10) 및 NAND 제어기(11)를 구비한다. NAND 제어기(11)는 호스트 인터페이스 회로(host I/F), MPU(micro processing unit)(22), ROM(read only memory)(23), RAM(random access memory)(24) 및 NAND 인터페이스 회로(NAND I/F)(25)를 포함한다.

[0053] 호스트 인터페이스 회로(21)는 미리 결정된 프로토콜에 따라서 NAND 제어기(11)와 호스트 장치[CPU(2), 메인 메모리(3) 등] 사이의 인터페이스 처리를 수행한다.

[0054] MPU(22)는 메모리 시스템(1)의 전체 동작을 제어한다. 메모리 시스템(1)의 전원이 온(on)되는 경우, 예를 들어, MPU(22)는 ROM(23)에 저장된 펌웨어를 RAM(24) 상에서 판독하고, 미리 결정된 처리를 실행하여, RAM(24)

상에 여러 가지 테이블을 형성한다. 또한, MPU(22)는 호스트 장치들로부터 기록 요청, 판독 요청 및 소거 요청을 수신하고, 이러한 요청에 따라서 NAND 플래시 메모리(10)에 미리 결정된 처리를 실행한다.

[0055] ROM(23)은, 예를 들어 MPU(22)에 의해 제어되는 제어 프로그램을 저장한다. RAM(24)은 MPU(22)의 작업 영역으로서 사용되고, ROM(23)으로부터 로딩되는 제어 프로그램 및 여러 가지 테이블을 저장한다. NAND 인터페이스 회로(25)는, 미리 결정된 프로토콜에 따라서 NAND 제어기(11)와 NAND 플래시 메모리(10) 사이의 인터페이스 처리를 수행한다.

[0056] NAND 플래시 메모리(10)는 데이터 소거의 최소 단위로서 복수의 블록을 배열함으로써 형성된다. 도 3a는 NAND 플래시 메모리(10)에 포함되는 하나의 블록의 배열을 나타내는 회로도이다. 각 블록은 X 방향에 따라 순서대로 배열되는  $(m+1)$ 개의 NAND 스트링을 포함한다( $m$ 은 0 이상의 정수).  $(m+1)$  개의 NAND 스트링 각각에 포함되는 선택 트랜지스터(ST1)는, 비트선들(BL0 내지 BL $m$ ) 중 대응하는 하나에 연결되는 드레인, 및 공통 선택 게이트선(SGD)에 연결된 게이트를 가진다.  $(m+1)$ 개의 NAND 스트링 각각에 포함되는 선택 트랜지스터(ST2)는 소스선(SL)에 연결되는 소스 및 공통 선택 게이트선(SGS)에 연결된 게이트를 가진다.

[0057] 각 NAND 스트링에서,  $(n+1)$ 개의 메모리 셀 트랜지스터(MT)는, 메모리 셀 트랜지스터(MT)의 전류 경로가 직렬로 연결되도록 선택 트랜지스터(ST1)의 소스와 선택 트랜지스터(ST2)의 드레인 사이에 배열된다( $n$ 은 0 이상의 정수). 즉,  $(n+1)$  개의 메모리 셀 트랜지스터(MT)는, 인접 트랜지스터들이 확산 영역(소스 영역 또는 드레인 영역)을 공유하도록 Y 방향으로 직렬 연결된다.

[0058] 제어 게이트 전극은, 드레인측에 가장 가까이 위치하는 메모리 셀 트랜지스터(MT)로부터의 순서로 워드선들(WL0 내지 WL $n$ )에 연결된다. 따라서, 워드선(WL0)에 연결되는 메모리 셀 트랜지스터(MT)의 드레인은 상기 선택 트랜지스터(ST1)의 소스에 연결되며, 워드선(WL $n$ )에 연결되는 메모리 셀 트랜지스터(MT)의 소스는 상기 선택 트랜지스터(ST2)의 드레인에 연결되어 있다.

[0059] 워드선(WL0 내지 WL $n$ )은, 블록 내의 NAND 스트링 사이에서 메모리 셀 트랜지스터(MT)의 제어 게이트 전극을 함께 연결하고 있다. 즉, 블록 내에서 동일한 행에 있는 메모리 셀 트랜지스터(MT)의 제어 게이트 전극은 동일한 워드선(WL)에 연결된다. 동일한 워드선(WL)에 연결되는  $(m+1)$  개의 메모리 셀 트랜지스터(MT)는 페이지로서 처리되고, 페이지마다 데이터 기록 및 데이터 판독이 수행된다.

[0060] 비트선(BL0 내지 BL $m$ )은 블록들 사이에서 선택 트랜지스터(ST1)의 드레인을 함께 연결한다. 즉, 복수의 블록 내에서 동일한 열에 있는 NAND 스트링이 동일한 비트선(BL)에 연결된다.

[0061] 각 메모리 셀 트랜지스터(MT)는, 반도체 기판 상에 형성된 적층 게이트 구조를 가지는 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)이다. 적층 게이트 구조는, 반도체 기판 상에 게이트 절연막, 전하 저장층(플로팅 게이트 전극), 게이트간 절연막, 제어 게이트 전극을 순차적으로 적층함으로써 형성된다. 메모리 셀 트랜지스터(MT)는, 플로팅 게이트 전극에 저장된 전자의 개수에 따라서 그 임계 전압을 변경하고, 그 임계 전압들 사이의 차에 따라서 데이터를 저장한다. 메모리 셀 트랜지스터(MT)는 2진 데이터(1 비트) 또는 멀티레벨(multilevel) 데이터(2 이상의 비트를 가지는 데이터)를 저장하도록 설계될 수 있다.

[0062] 메모리 셀 트랜지스터(MT)의 구조는, 플로팅 게이트 전극을 가지는 구조로 제한되지 않고, 전하 저장층으로서의 질화물막의 계면에서 전자들을 포획함으로써 임계값을 조정할 수 있는 MONOS(metal oxide nitride oxide silicon)와 같은 구조일 수도 있다. 또한, 이 MONOS 구조를 가지는 메모리 셀 트랜지스터(MT)는 1 비트 또는 멀티레벨 데이터(2 이상의 비트를 가지는 데이터)를 저장하도록 설계될 수도 있다.

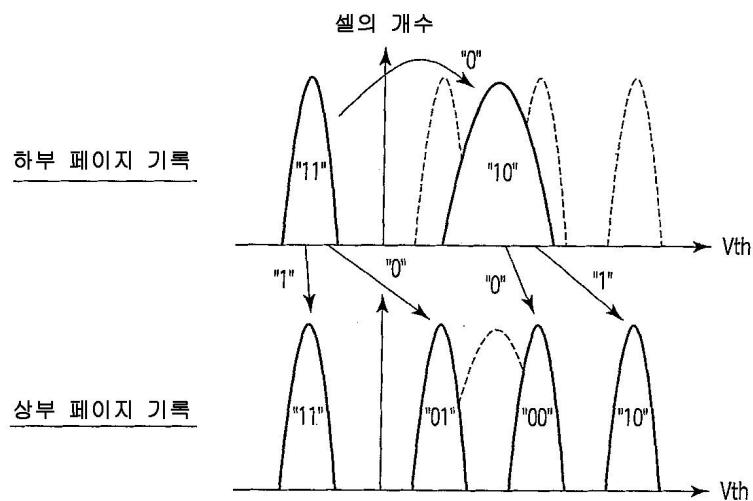

[0063] 도 3b는 4 레벨 데이터 기록 시스템 즉, 하나의 메모리 트랜지스터(MT)에 2 비트가 기록되는 시스템을 사용하는 경우에 획득되는 임계값 분포의 일례를 나타낸다.

[0064] 4 레벨 데이터 기록 시스템에서, 상부 페이지 데이터 “x” 및 하부 페이지 데이터 “y”에 의해 정의되는 4 레벨 데이터 “xy” 중 하나는 메모리 셀 트랜지스터(MT)에 유지될 수 있다.

[0065] 데이터 “11”, “01”, “00” 및 “10” (메모리 셀 트랜지스터(MT)의 임계 전압의 오름 차순으로 존재)는 4 레벨 데이터 “xy”로서 할당된다. 데이터 “11”는 메모리 셀 트랜지스터(MT)의 임계 전압이 네가티브인 경우의 소거 상태를 나타낸다.

[0066] 하부 페이지 기록에서, 데이터 “10”은 데이터 “11” 상태(소거 상태)에 있는 메모리 셀 트랜지스터(MT)에 하부 비트 데이터 “y”를 선택적으로 기록함으로써 기록된다.

[0067] 상부 페이지 기록 이전에 존재하는, 데이터 “10”의 임계값 분포는, 상부 페이지 기록 이후에 존재하는, 데이터 “01” 및 데이터 “00”의 임계값 분포 사이에 위치된다. 데이터 “10”의 임계값 분포는 상부 페이지 기록 이후의 데이터의 임계값 분포보다 넓게 되도록 허용된다.

[0068] 상부 페이지 기록에서, 상부 비트 데이터 “x”는 데이터 “11” 상태로 존재하는 메모리 셀 및 데이터 “10” 상태로 존재하는 메모리 셀에 선택적으로 기록된다.

[0069] 본 발명의 각 실시형태의 각 기능 블록은, 하드웨어, 소프트웨어 또는 하드웨어와 소프트웨어의 조합에 의해 실행될 수 있다. 따라서, 각 기능 블록은, 상기 블록이 하드웨어 및 소프트웨어 중 하나 또는 양자에 의해 실행될 수 있는지를 명확하게 나타내기 위하여 그 기능의 관점으로부터 이하에 설명된다. 그 기능은 실제적인 실시 형태 또는 전체 시스템에 부여되는 설계 제약에 따라서 하드웨어 또는 소프트웨어로서 실행된다. 당업자는 각각의 실제적인 실시형태에 대한 다양한 방법에 의해 이러한 기능들을 실행할 수 있고, 본 발명의 범위는 실행의 결정을 포함한다.

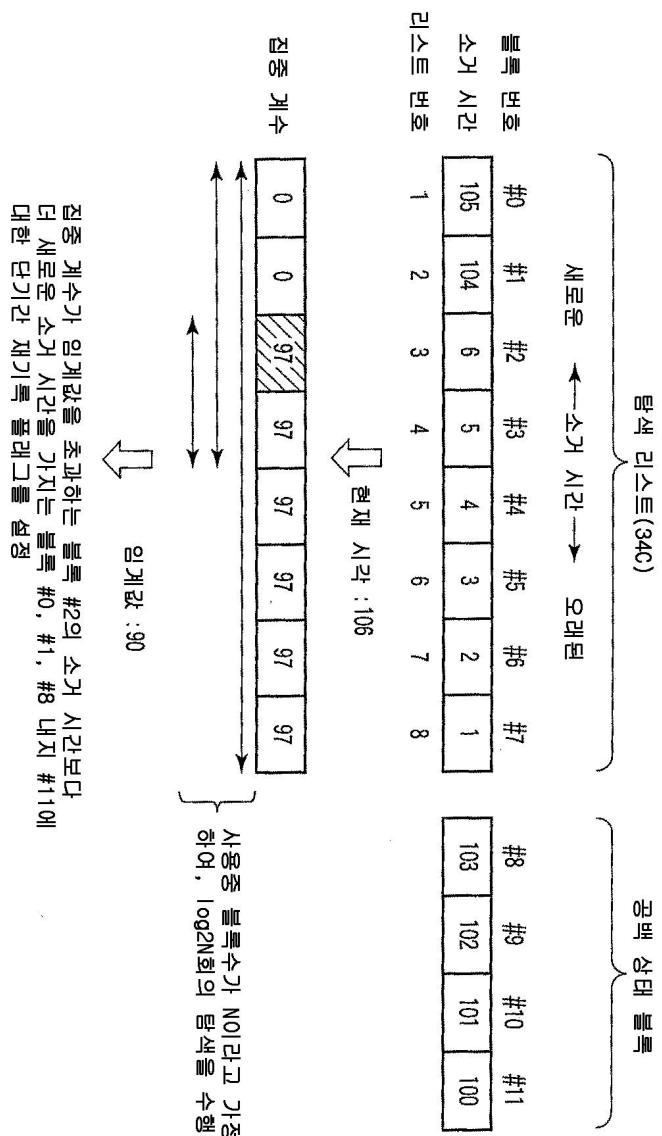

[0070] 이하, NAND 제어기(11)의 더욱 실제적인 배열의 일례를 설명한다. 도 4는 이 실시형태에 따른 NAND 제어기(1)의 배열의 일례를 나타내는 블록도이다.

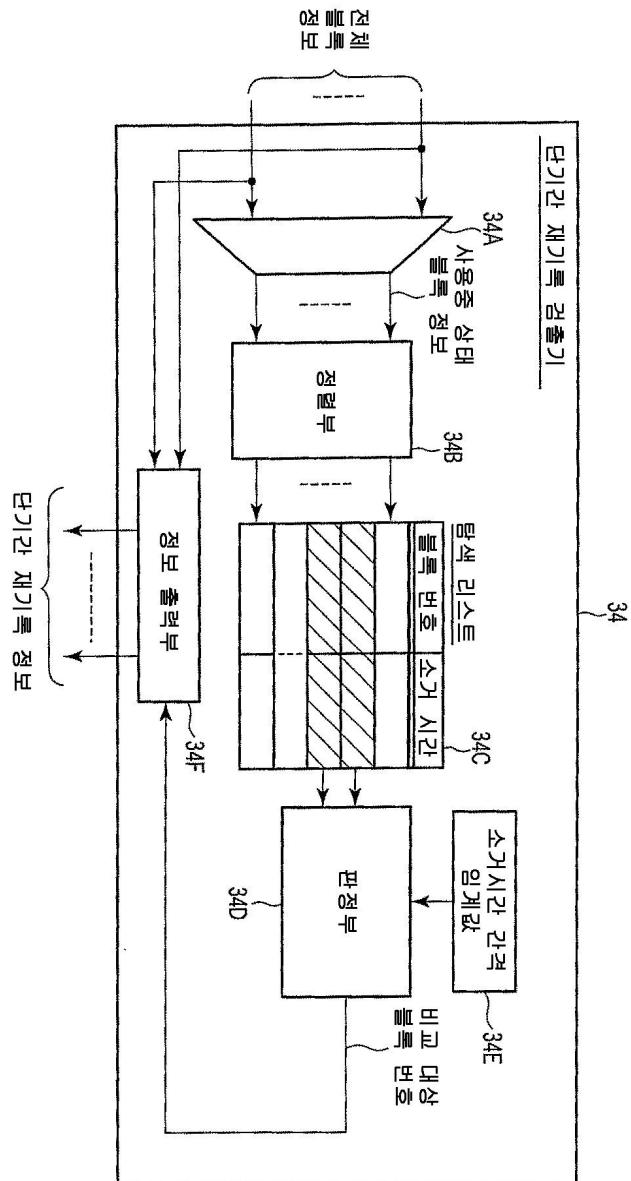

[0071] NAND 제어기(11)는 블록 제어기(30), 소거 시간 측정부(31), 할당 블록 선택기(32), 교체 소스 블록 선택기(33), 단시간 재기록 검출기(34), 평준화부(35) 및 NAND 인터페이스 회로(NAND I/F)(25)를 구비한다.

[0072] NAND 플래시 메모리(10)에 포함되는 각 블록의 데이터가 소거될 때마다, 소거 시간 측정부(31)는 블록의 소거 시간을 측정한다. 상기 소거 시간 측정부(31)는 측정된 소거 시간을 블록 제어기(30)에 송신한다.

[0073] 블록 제어기(30)는 소거 횟수 및 소거 시간을 포함하는 다양한 종류의 정보를 관리한다. 또한, 블록 제어기(30)는 CPU(2)로부터의 전송 요청에 응답하여 NAND 플래시 메모리(10)에 기록 요청, 판독 요청 및 소거 요청을 발행한다. 보다 상세하게는, 블록 제어기(30)는 (후술되는) 어드레스 테이블(30A) 및 블록 테이블(30B)을 포함하여, 이러한 테이블들을 이용하여 NAND 플래시 메모리(10)에 기록 요청, 판독 요청 및 소거 요청을 발행한다.

[0074] 외부[예를 들어, CPU(2) 또는 메인 메모리(3)]로부터 공급되는 새로운 데이터를 NAND 플래시 메모리(10)에 기록하는 경우, 할당 블록 선택기(32)는 이 기록을 위해 할당되는 블록(이하, 할당 블록으로 지정됨)을 선택한다. 즉, 할당 블록 선택기(32)는 블록 테이블(30B)에 저장된 전체 블록의 정보(전체 블록 정보)를 상기 블록 제어기(30)로부터 수신하고, 미리 결정된 조건에 따라서 할당 블록을 선택한다. 할당 블록 선택기(32)는 상기 할당 블록에 대응하는 블록 번호(할당 블록 번호)를 블록 제어기(30)에 송신한다. 또한, 할당 블록 선택기(32)는 전체 블록 정보 중 할당 블록에 대응하는 정보(할당 블록 정보)를, 평준화부(35)에 송신한다. NAND 플래시 메모리(10)에 기록될 데이터의 일례들은, 외부에서 메모리 시스템(1)에 공급되는 사용자 데이터 및 메모리 시스템(1)의 내부를 관리하도록 요구되는 시스템 데이터이다.

[0075] 평준화부(35)는 (후술되는) 평준화 처리를 실행한다. 이 평준화 처리와 동시에, 평준화부(35)는 상기 NAND 플래시 메모리(10)에 기록 요청, 판독 요청 및 소거 요청을 발행한다. 평준화는 블록의 소거 횟수를 서로 동일하게 설정하는 것(즉, 웨어(wear) 레밸링)임을 주목한다. 이와 같이 블록 소거 횟수를 서로 동일하게 설정함으로써, 일부 블록들에 소거 처리가 집중되는 것을 방지할 수 있다. 이는 NAND 플래시 메모리(10)의 서비스 수명을 연장시킬 수 있다.

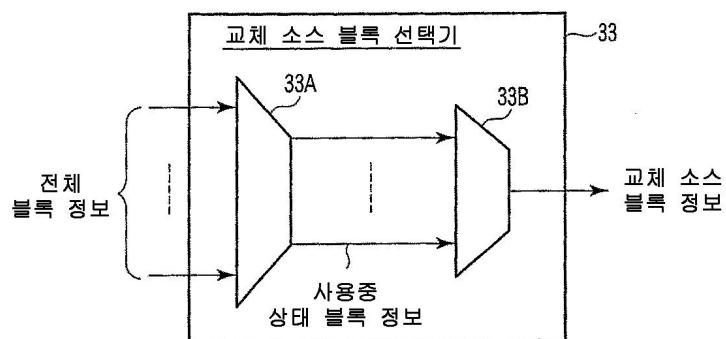

[0076] 교체 소스 블록 선택기(33)는 평준화부(35)에 의해 수행되는 평준화 처리에 사용되는 데이터 교체 소스로서의 블록(이하, 교체 소스 블록으로 지정됨)을 선택한다. 즉, 교체 소스 블록 선택기(33)는 블록 제어기(30)로부터 전체 블록 정보를 수신하고, 미리 결정된 조건 하에서 교체 소스 블록을 선택한다. 그 후, 교체 소스 블록 선택기(33)는 전체 블록 정보 중 교체 소스 블록에 대응하는 정보(교체 소스 블록 정보)를, 평준화부(35)에 송신한다.

[0077] NAND 인터페이스 회로(25)는 블록 제어기(30) 및 평준화부(35)로부터 기록 요청, 판독 요청 및 소거 요청을 수신한다. 이러한 요청들에 응답하여, NAND 인터페이스 회로(25)는 NAND 플래시 메모리(10)에게 데이터의 기록, 판독 및 소거를 지시한다.

[0078] 단기간 재기록 검출기(34)는 (짧은 기간 내에서) 재기록이 빈번하게 수행되는 블록(짧은 소거 간격을 가짐)을 검출한다. 재기록이 짧은 기간 내에서 수행되는 블록의 소거 시간은 빈번하게 업데이트(새로운 소거 시간으로 교체됨)되는 반면에, 짧은 기간 내에서 재기록이 수행되지 않는 블록의 소거 시간은 오래된 채로 남겨진다. 이 실시형태는 소거 시간들 사이의 차를 이용하여 짧은 기간 내에서 재기록을 수행하는 블록을 검출한다. 이를 위

하여, 단기간 재기록 검출기(34)는 사용중 상태의 블록들을 소거 시간순으로 배열(정렬)하고, 어떤 탐색 대상 블록의 소거 시간과 상기 탐색 대상 블록의 소거 시간 다음으로 새로운 소거 시간을 가지는 비교 대상 블록의 소거 시간 사이의 차를 산출한다. 이 소거 시간 차가 미리 결정된 임계값을 초과하면, 단기간 재기록 검출기(34)는, 소거 시간이 비교 대상 블록의 소거 시간보다 더 새로운 블록을 짧은 기간 내에 재기록이 수행되는 블록이라고 판정한다. 이 판정 결과는 단기간 재기록 정보로서 블록 제어기(30)에 공급된다.

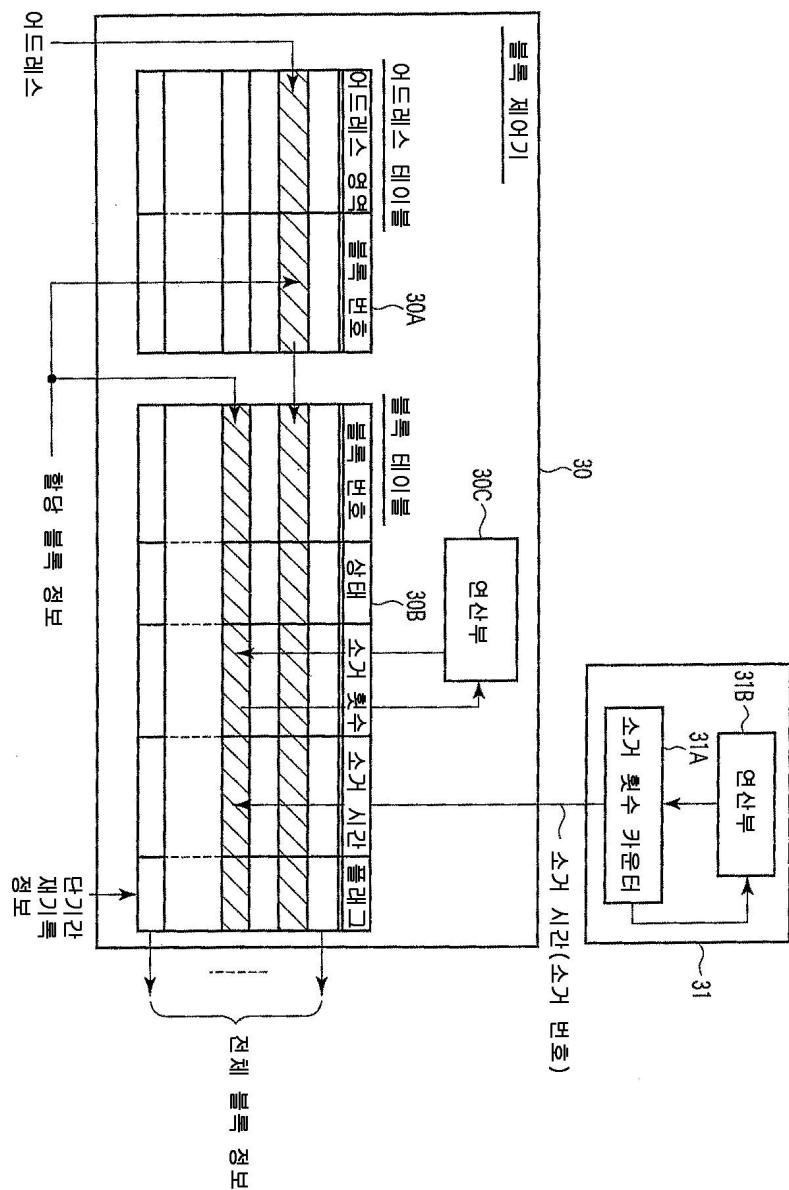

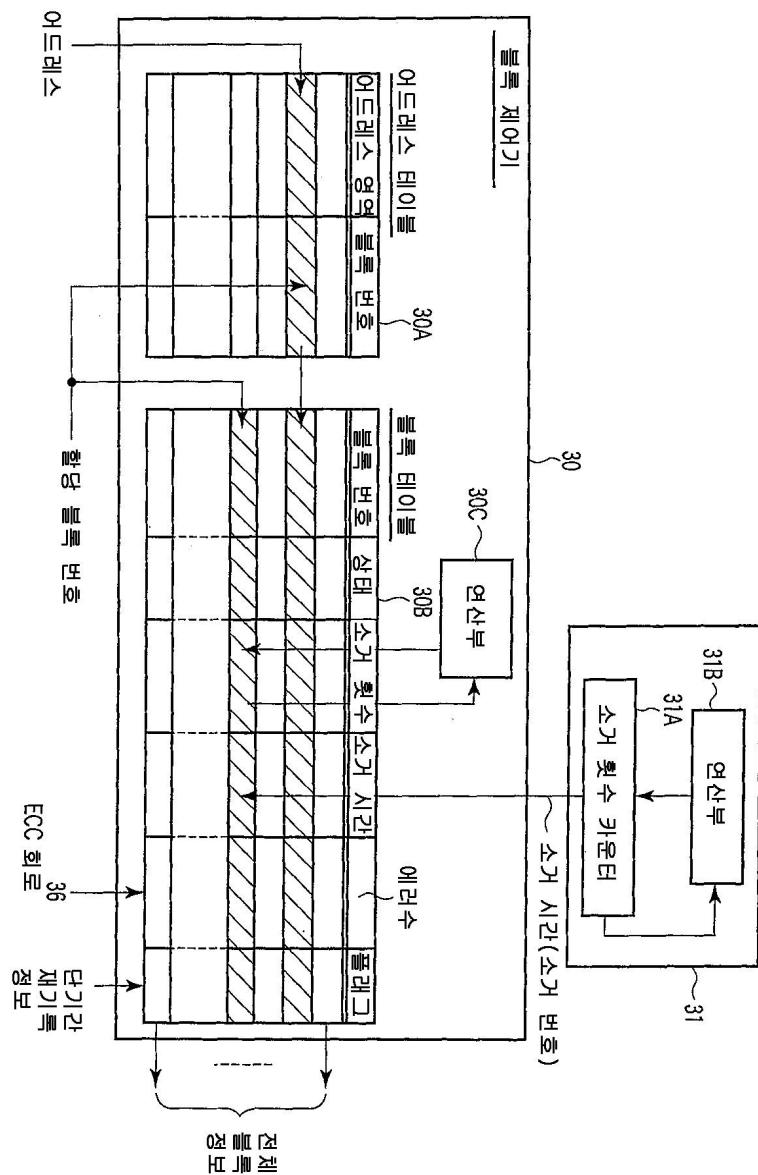

[0079] 도 5는 블록 제어기(30) 및 소거 시간 측정부(31)의 배열을 나타내는 블록도이다. 블록 제어기(30)는 어드레스 테이블(30A), 블록 테이블(30B) 및 연산부(30C)를 가진다. 상기 블록 제어기(30)는 외부로부터 공급되는 어드레스 및 여러가지 종류의 정보를 수신하고, 이러한 정보에 기초하여 어드레스 테이블(30A) 및 블록 테이블(30B)을 업데이트한다.

[0080] 어드레스 테이블(30A)은 호스트 장치[CPU(2)]로부터 어드레스 버스를 통하여 공급되는 어드레스를 포함하는 어드레스 영역(논리 블록 어드레스)과 이 어드레스 영역에 대응하는 NAND 플래시 메모리(10) 내의 블록 번호(물리 블록 어드레스) 사이의 대응 관계를 나타낸다. 이 어드레스 테이블(30A)을 이용함으로써, 블록 제어기(30)는 호스트 장치로부터 공급되는 어드레스를 포함하는 어드레스 영역의 데이터가 대응하는 블록을 특정할 수 있다. 어드레스 테이블(30A)은 예를 들어 (후술되는) 블록 릴리즈 처리 및 블록 할당 처리와 동시에 업데이트된다.

[0081] 블록 테이블(30B)은 각 블록 번호에 대한 정보로서 이하의 데이터를 저장한다. 상기 데이터는, 블록 번호가 어드레스 테이블(30A)에 등록되어 있지 않은지 여부(블록이 공백 상태 블록인지 여부) 또는 블록 번호가 어드레스 테이블(30A)에 등록되어 있는지 여부(블록이 사용중 상태 블록인지 여부)를 나타내는 블록 상태, 데이터의 소거 횟수(소거 횟수), 소거 시간 측정부(31)로부터 공급되는 소거 시간 및 단기간 재기록 검출기로부터 공급되는 단기간 재기록 정보에 대응하는 단시간 재기록 플래그(도 5에서는 간단히 "플래그"로 기재함)를 포함한다. 블록 테이블(30B)은 예를 들어, (후술되는) 블록 릴리즈 처리, 블록 할당 처리, 블록 소거 처리 및 단기간 재기록 검출 처리와 동시에 업데이트된다. 블록 테이블(30B)에 포함되는 전체 블록 정보는 할당 블록 선택기(32), 교체 소스 블록 선택기(33) 및 단기간 재기록 검출기(34)에 공급된다.

[0082] 블록이 공백 상태 블록이면, 호스트 장치는, NAND 플래시 메모리(10)에서 블록 내의 데이터가 실제로 소거되는지 여부에 상관없이, 상기 블록에 대응하는 어드레스 영역을, 데이터를 저장하지 않는 공백 영역이라고 인식한다. 한편, 블록이 사용중 상태 블록이면, 호스트 장치는 상기 블록에 대응하는 어드레스 영역을, 데이터를 저장하는 사용중 영역이라고 인식한다.

[0083] 어드레스 테이블(30A) 및 블록 테이블(30B)은, 실제로 RAM(24) 및 NAND 플래시 메모리(10) 모두에 저장됨을 주목한다. 그러나, NAND 플래시 메모리(10)에 비휘발성 테이블로서 저장되는 어드레스 테이블(30A) 및 블록 테이블(30B)은, RAM(24)이 업데이트 될 때마다 항상 업데이트될 필요는 없다.

[0084] NAND 플래시 메모리(10)의 데이터가 소거될 때마다, 연산부(30C)는 블록 테이블(30B)에 포함되는 데이터가 소거된 블록의 소거 횟수를 하나씩 카운트 업한다. 실제로, MPU(22)가 연산부(30C)의 처리를 수행한다는 점에 주목한다.

[0085] 블록 제어기(30)는 할당 블록 선택기(32)로부터 할당 블록 번호를 수신하고, 이 할당 블록 번호를 이용하여 어드레스 테이블(30A)의 블록 번호를 업데이트한다. 또한, 블록 제어기(30)는, 이 할당 블록 번호에 대한 기록 요청을 NAND 플래시 메모리(10)에 발행한다. 또한, 블록 제어기(30)는 외부 어드레스에 대응하는 정규 판독 요청 및 소거 요청을 NAND 플래시 메모리(10)에 발행한다.

[0086] 소거 시간 측정부(31)는 소거 횟수를 카운트하는 소거 횟수 카운터(31A) 및 소거 횟수 카운터(31A)의 카운트 값을 업데이트하는 연산부(31B)를 구비한다. 소거 시간 측정부(31)는 NAND 플래시 메모리(10) 내의 블록에 대하여 수행되는 소거 횟수를 측정하고, 그 측정된 값을 소거 시간으로서 출력한다.

[0087] 더욱 상세하게는, 어떤 블록의 데이터가 소거될 때마다, 연산부(31B)는 1만큼 소거 횟수 카운터(31A)를 카운트 업한다. 소거 횟수 카운터(31A)의 카운트값(소거 번호)은 소거 시간으로서 블록 제어기(30)(즉, 블록 테이블(30B))에 공급된다. 이 실시형태의 소거 시간 측정부(31)에서, 소거 번호가 보다 작아짐에 따라 소거 시간은 더 길어진다. 실제로, MPU(22)가 연산부(31B)의 처리를 수행한다는 점에 주목한다.

[0088] 소거 시간으로서, 예를 들어 데이터가 소거되는 시간(소거 타이밍) 또는 NAND 제어기(11)의 전력 공급 시간을 또한 이용할 수 있다. 상기 소거 타이밍을 소거 시간으로서 이용하는 경우, 소거 시간 측정부(31)는, 시계를 가지며, 데이터가 소거될 때마다, 소거 타이밍을 소거 시간으로 출력한다. 전력 공급 시간을 소거 시간으로서 이용하는 경우에, 소거 시간 측정부(31)는 타이머를 포함하며, 데이터가 소거될 때마다, 이 때까지의 전력 공

급 시간을 측정하고, 그 측정된 전력 공급 시간을 소거 시간으로 출력한다. 따라서, 소거 횟수, 소거 타이밍 또는 전력 공급 시간을 소거 시간으로서 자유롭게 선택할 수 있다. 소거 시간을 특정할 수 있는 한, 상술된 3 가지 타입의 정보 이외의 정보를 사용할 수도 있음을 주목 한다.

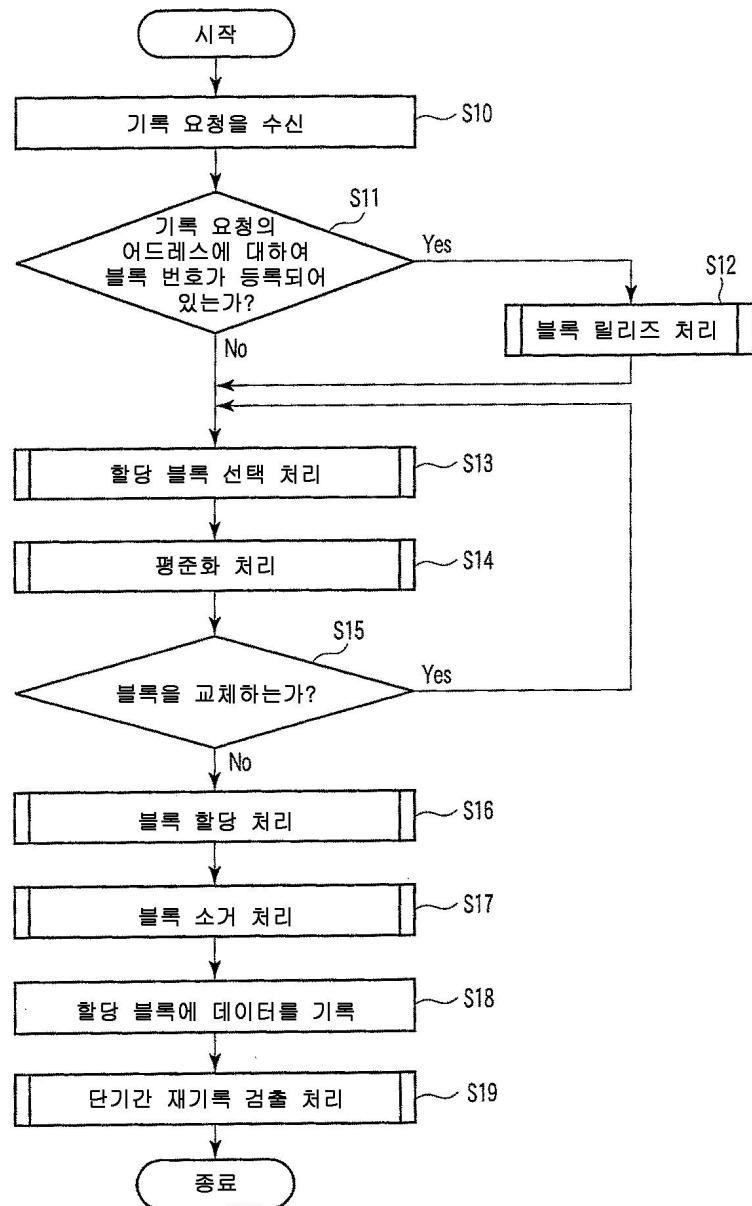

[0089] [2. NAND 제어기(11)의 기록 동작]

[0090] 이하, NAND 제어기(11)의 기록 동작을 설명한다. 도 6은 NAND 제어기(11)에 의해 수행되는 일련의 기록 동작을 나타내는 흐름도이다.

[0091] 먼저, NAND 제어기(11)는 CPU(2)로부터 기록 요청의 수신 시에, 기록 동작을 시작한다(단계 S10). 이후에, 블록 제어기(30)는 어드레스 테이블(30A)을 이용하여 기록 요청의 어드레스를 포함하는 어드레스 영역에 대하여 블록 번호가 등록되어 있는지(블록이 할당되어 있는지) 여부를 체크한다(단계 S11). 블록 번호가 등록되어 있는 경우(블록이 할당되어 있는 경우), 이 어드레스 영역에 데이터를 오버라이트(overwrite) 해야 하므로, 블록 제어기(30)는 상기 블록 번호에 대응하는 블록을 릴리즈하는 블록 털리즈 처리를 실행한다(단계 S12).

[0092] 단계 S11에서, 블록 번호가 등록되어 있지 않다고(블록이 할당되어 있지 않다고) 판정되는 경우 또는 단계 S12에서 블록 털리즈 처리를 실행한 이후에, 할당 블록 선택기(32)는 상기 어드레스 영역에 할당되는 블록(할당 블록)을 선택하는 할당 블록 선택 처리를 실행한다(단계 S13).

[0093] 그 후, 평준화부(35) 및 교체 소스 블록 선택기(33)는 평준화 처리를 실행한다(단계 S14). 이 후에, 블록 제어기(30)는 평준화 처리에서 그 할당 블록을 교체할지 여부를 체크한다(단계 S15). 할당 블록을 교체하면, 그 처리는 단계 S13으로 리턴되고, 할당 블록 선택기(32)는 다시 할당 블록 선택 처리를 실행한다.

[0094] 단계 S15에서 할당 블록이 교체되지 않으면, 블록 제어기(30)는, 어드레스 테이블(30A) 및 블록 테이블(30B)을 업데이트하기 위하여, 할당 블록에 대응하는 블록 번호(할당 블록 번호)을 이용함으로써 블록 할당 처리를 실행한다(단계 S16). 그 후, 블록 제어기(30)는 할당 블록에 대하여 블록 소거 처리를 실행한다(단계 S17).

[0095] 이후에, 블록 제어기(30)는 데이터가 소거된 할당 블록에 새로운 데이터를 기록한다(단계 S18). 즉, 블록 제어기(30)는 NAND 인터페이스 회로(25)에 기록 요청을 발행한다. 이 기록 요청에 기초하여, NAND 인터페이스 회로(25)는 NAND 플래시 메모리(10)에게 상기 할당 블록에 새로운 데이터를 기록하도록 지시한다.

[0096] 그 후에, 단기간 채기록 검출기(34)는 단기간 채기록 검출 처리를 실행한다(단계 S19). 블록 제어기(30)는 상기 단기간 채기록 검출기(34)로부터 공급되는 정보를 이용함으로써 블록 테이블(30B)의 플래그를 업데이트한다. 이러한 방식으로, NAND 제어기(11)는 일련의 기록 동작을 실행한다.

[0097] 다음으로, 기록 동작에 포함되는 각 처리의 세부사항을 설명한다.

[0098] [2-1. 블록 릴리즈 처리]

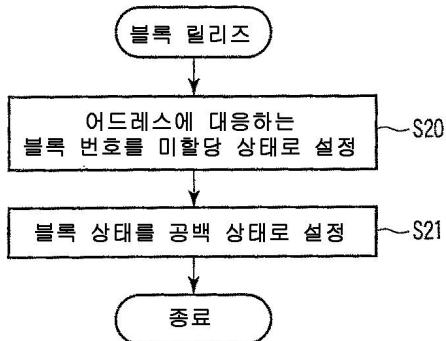

[0099] 도 7은 NAND 제어기(11)에 의해 수행되는 블록 릴리즈 처리를 나타내는 흐름도이다. 블록 제어기(30)는, 어드레스 테이블(30A)에 포함되는, 기록 요청의 어드레스를 포함하는 어드레스 영역에 대응하는 블록 번호를 미할당된 상태로 설정한다(단계 S20). 이후에, 블록 제어기(30)는 블록 테이블(30B)에 포함되는 블록 번호의 상태를 공백 상태로 설정한다(단계 S21). 블록 릴리즈 처리에 의해 공백 상태로 새롭게 설정된 블록은 이후에 릴리즈 블록으로 지정된다. 그 후에, NAND 제어기(11)는 릴리즈 블록에 새로운 데이터를 기록할 수 있다.

[0100] [2-2. 할당 블록 선택 처리]

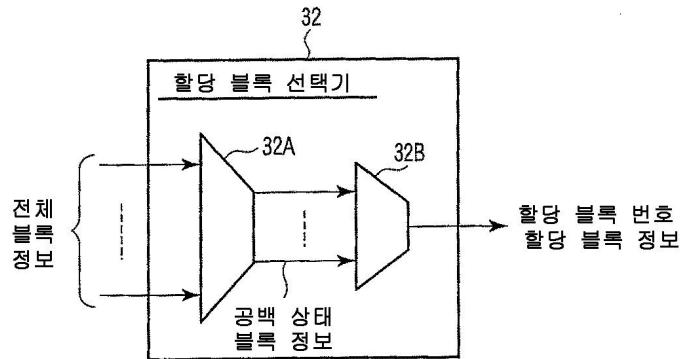

[0101] 도 8은 할당 블록 선택기(32)의 배열을 나타내는 블록도이다. 도 9는 할당 블록 선택기(32)에 의해 수행되는 할당 블록 선택 처리를 나타내는 흐름도이다.

[0102] 할당 블록 선택기(32)는 2 개의 선택기(32A 및 32B)를 구비한다. 할당 블록 선택기(32)는 블록 제어기(30)로부터 전체 블록 정보를 수신한다(단계 S30). 이 전체 블록 정보는 선택기(32A)에 공급된다. 선택기(32A)는 모든 블록의 상태를 체크하고, 모든 블록으로부터 공백 상태의 블록을 추출한다(단계 S31). 그 후, 선택기(32A)는 공백 상태 블록에 대응하는 블록 정보(공백 상태 블록 정보)를 선택기(32B)에 송신한다.

[0103] 선택기(32B)는 선택기(32A)에 의해 추출되는 블록들 중에서 가장 오래된 소거 시간을 가지는 블록을 할당 블록으로서 선택한다(단계 S32). 이 할당 블록에 대응하는 할당 블록 번호는 블록 제어기(30)에 공급된다. 또한, 할당 블록에 대응하는 할당 블록 정보는 평준화부(35)에 공급된다.

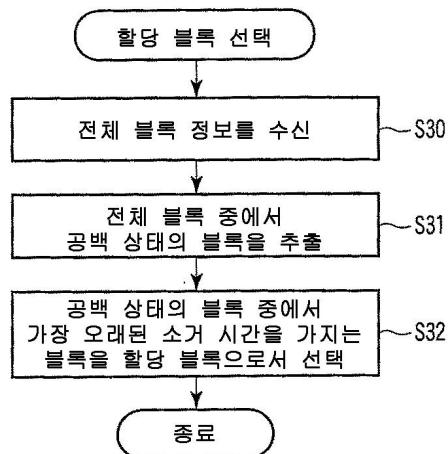

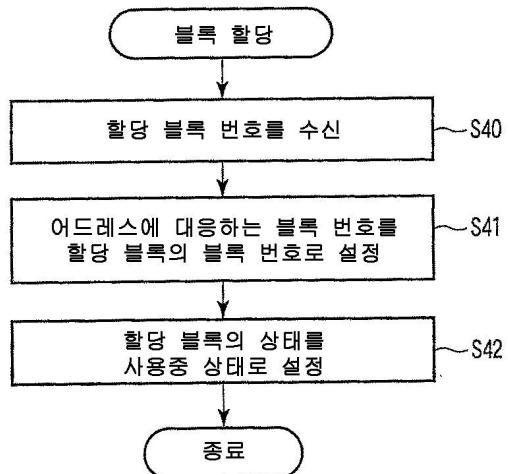

[0104] [2-3. 블록 할당 처리]

[0105] 도 10은 NAND 제어기(11)에 의해 수행되는 블록 할당 처리를 나타내는 흐름도이다. NAND 제어기(11)는, 할당 블록 선택기(32)에 의해 선택되는 할당 블록에 대하여, 어드레스 테이블(30A)과 블록 테이블(30B)의 정보를 업데이트한다.

[0106] 먼저, 블록 제어기(30)는 할당 블록 선택기(32)로부터 할당 블록 번호를 수신한다(단계 S40). 그 후, 블록 제어기(30)는 어드레스 테이블(30A)에 포함되는 기록 요청의 어드레스를 포함하는 어드레스 영역에, 할당 블록의 블록 번호를 설정한다(단계 S41). 이후에, 블록 제어기(30)는 상기 블록 테이블(30B)에 포함되는 할당 블록의 상태를 사용중 상태로 설정한다(단계 S42). 이러한 방식으로, 할당 블록 선택기(32)에 의해 선택된 할당 블록을 공백 상태로부터 사용중 상태로 변경한다.

[0107] [2-4. 블록 소거 처리]

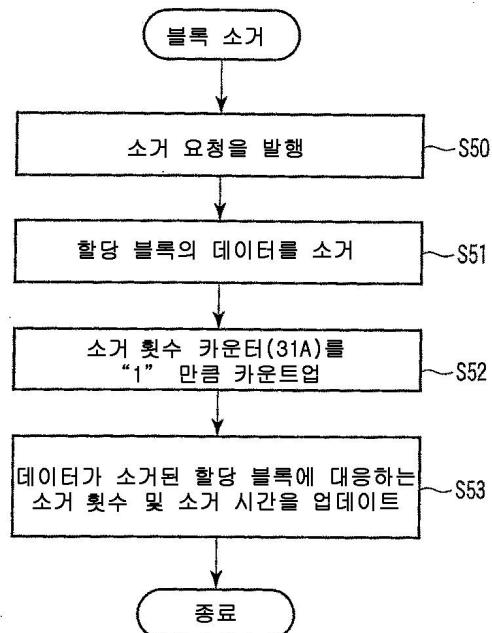

[0108] 도 11은 NAND 제어기(11)에 의해 수행되는 블록 소거 처리를 나타내는 흐름도이다. 블록 제어기(30)는 NAND 인터페이스 회로(25)에 할당 블록에 대한 소거 요청을 발행한다(단계 S50). 이 소거 요청에 기초하여, NAND 인터페이스 회로(25)는 NAND 플래시 메모리(10)에게 할당 블록의 데이터를 소거하도록 지시한다(단계 S51). 이후에, 소거 시간 측정부(31)(특히, 연산부(31B))는 소거 횟수 카운터(31A)의 카운트값(소거 번호)을 1 만큼 카운트 업한다(단계 S52).

[0109] 그 후, 블록 제어기(30)는, 블록 테이블(30B)에 포함되며 데이터가 소거되는 할당 블록에 대응하는 소거 횟수 및 소거 시간을 업데이트한다(단계 S53). 보다 상세하게는, 블록 제어기(30)는 소거 시간 측정부(31)로부터 공급되는 소거 시간을 이용함으로써 블록 테이블(30B)에 포함되는 소거된 할당 블록의 블록 번호에 대응하는 소거 시간을 업데이트한다. 또한, 연산부(30C)는 블록 테이블(30B)에 포함되는 소거된 할당 블록의 블록 번호에 대응하는 소거 횟수를 “1” 만큼 카운트업한다.

[0110] [2-5. 단기간 재기록 검출 처리]

[0111] 도 12는 단기간 재기록 검출기(34)의 배열을 나타내는 블록도이다. 단기간 재기록 검출기(34)는, 선택기(34A), 정렬부(34B), 탐색 리스트(34C), 판정부(34D), 소거 시간 간격 임계값을 기억하는 기억부(34E) 및 정보 출력부(34F)를 구비한다.

[0112] 선택기(34A)는 블록 제어기(30)로부터 공급되는 전체 블록 정보를 이용하여 전체 블록의 상태를 체크하고, 전체 블록 중에서 사용중 상태 블록들을 추출한다. 정렬부(34B)는, 사용중 상태의 블록들을 소거 시간순으로 배열(정렬)한다. 탐색 리스트(34C)는 그 정렬된 블록 정보를 일시적으로 기억한다. 탐색 리스트(34C)는 실제로 RAM(24)에 저장되어 있음에 주목한다.

[0113] 탐색 리스트(34C)에서, 판정부(34D)는 가장 새로운 소거 시간을 가지는 블록을 “탐색 대상 블록”으로서 선택하고, 그 탐색 대상 블록의 소거 시간 다음으로 새로운 소거 시간을 가지는 블록을 “비교 대상 블록”으로서 선택한다. 또한, 판정부(34D)는, 탐색 대상 블록의 소거 시간과 비교 대상 블록의 소거 시간 사이의 차를 산출하고, 그 차가 소거 시간 간격 임계값을 초과하였는지 여부를 판정한다. 이 판정 결과에 기초하여, 판정부(34D)는, 소거 시간이 급격하게 변하는 경계를 탐색한다.

[0114] 판정부(34D)로부터 공급되는 판정 결과(비교 대상 블록의 번호)를 이용하여, 정보 출력부(34F)는 전체 블록들 중에서 비교 대상 블록의 소거 시간보다 더 새로운 소거 시간을 가지는 블록들의 범위를 산출한다. 정보 출력부(34F)는 상기 범위를 단기간 재기록 정보로서 블록 제어기(30)에 송신한다.

[0115] 기억부(34E)에 기억되는 소거 시간 간격 임계값은, 데이터가 빈번하게 재기록되는 블록들의 범위를 특정하는데 사용되며, NAND 플래시 메모리(10)의 서비스 수명(또는 데이터 유지 기간)을 연장시키는 정도를 나타내는 기준에 기초하여 설정된다. 단기간 재기록 검출의 가능성은, 소거 시간 간격 임계값이 감소되는 경우에 증가하고, 그 임계값이 증가되는 경우에 감소된다. 즉, 소거 시간 간격 임계값이 감소되는 경우에 평준화 처리의 횟수가 증가하며, 그 임계값이 증가되는 경우에 평준화 처리의 횟수가 감소된다. 이 평준화 처리에는 블록 데이터 소거 처리가 수반된다.

[0116] 데이터가 소거될 때마다, NAND 플래시 메모리(10)의 유지 특성은 저하된다(즉, 서비스 수명이 단축됨). 한편, 소거 간격이 연장될 때, NAND 플래시 메모리(10)의 유지 특성이 회복된다. 즉, 데이터 소거가 짧은 간격에서 연속적으로 수행되면, 유지 특성의 회복 시간을 확보할 수 없기 때문에, NAND 플래시 메모리(10)의 서비스 수명은 단축된다. 따라서, 이 실시형태에서는, 데이터가 빈번하게 재기록되고 있는 블록들에 대하여 단기간 재기록 플래그들이 설정되므로, 이러한 블록들을 평준화의 대상으로서 설정한다. NAND 플래시 메모리(10)의 특성을 고

려하여, 소거 간격을 미리 결정된 시간 만큼 연장시킴으로써 획득되는 서비스 수명의 회복 정보를 나타내는 소거 시간 간격 임계값을 결정하여, 평준화될 블록들 및 평준화 횟수를 최적화한다.

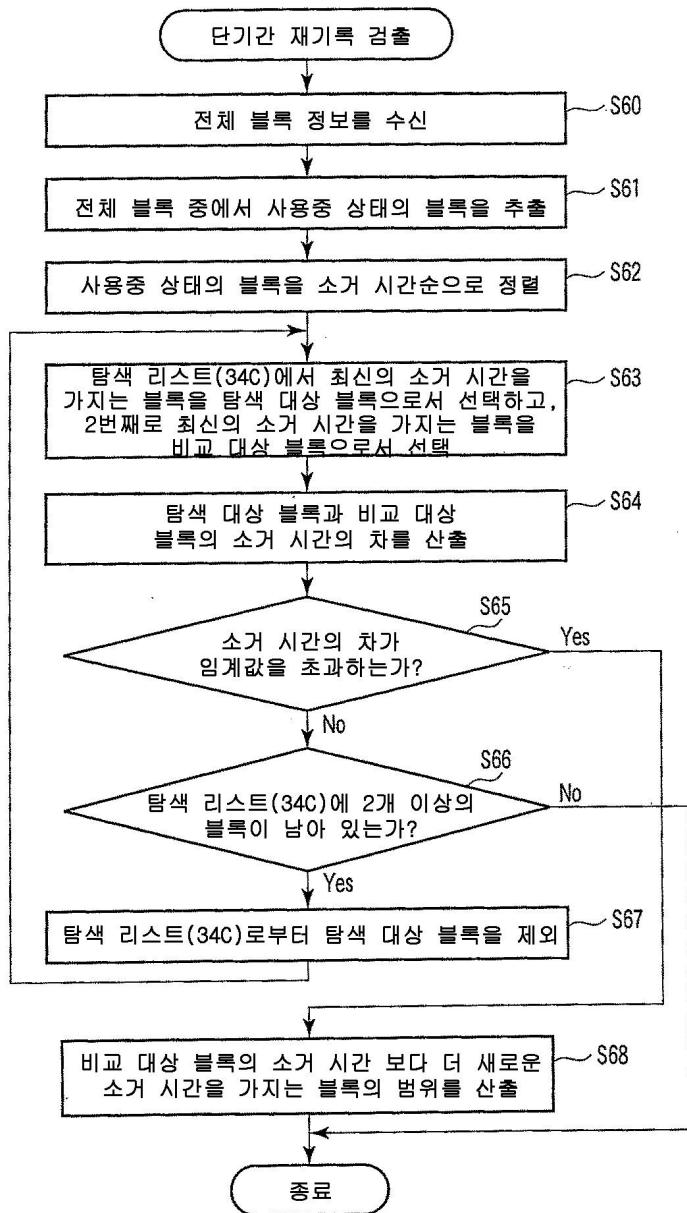

[0117] 도 13은 단기간 재기록 검출기(34)에 의해 수행되는 단기간 재기록 검출 처리를 나타내는 흐름도이다. 먼저, 단기간 재기록 검출기(34)는 블록 제어기(30)로부터 전체 블록 정보를 수신한다(단계 S60). 이 전체 블록 정보는 선택기(34A)에 공급된다. 선택기(34A)는 전체 블록의 상태를 체크하고, 전체 블록 중에서 사용중 상태 블록들을 추출한다(단계 S61). 그 후, 선택기(34A)는 사용중 상태 블록에 대응하는 블록 정보(사용중 상태 블록 정보)를 정렬부(34B)에 송신한다.

[0118] 정렬부(34B)는 사용중 상태 블록 정보에 포함되는 소거 시간을 체크하고, 그 사용중 상태 블록들을 소거 시간 순으로 정렬한다(단계 S62). 정렬부(34B)에 의해 정렬되는 블록 정보는 탐색 리스트(34C)에 배치된다.

[0119] 이후에, 판정부(34D)는, 탐색 리스트(34C)에서, 가장 새로운 소거 시간을 가지는 블록을 탐색 대상 블록으로 선택하고, 그 탐색 대상 블록의 소거 시간 다음으로 새로운 소거 시간을 가지는 블록을 비교 대상 블록으로서 선택한다(단계 S63).

[0120] 그 후에, 판정부(34D)는 탐색 대상 블록의 소거 시간과 비교 대상 블록의 소거 시간 사이의 차를 산출한다(단계 S64). 그 후, 판정부(34D)는 산출된 소거 시간차가 소거 시간 간격 임계값을 초과했는지 여부를 체크한다(단계 S65). 그 차가 소거 시간 간격 임계값을 초과하지 않으면, 판정부(34D)는, 2 개 이상의 블록이 탐색 리스트(34C)에 남아 있는지 여부를 체크한다(단계 S66). 2 개 이상의 블록이 남아 있으면, 판정부(34D)는 탐색 리스트(34C)에서 탐색 대상 블록을 제외하고, 단계 S63으로 리턴하여, 탐색 대상 블록 및 비교 대상 블록을 다시 선택한다.

[0121] 단계 S65에서, 그 차가 소거 시간 간격 임계값을 초과하면, 판정부(34D)는 비교 대상 블록 번호를 정보 출력부(34F)에 송신한다. 이 비교 대상 블록 번호를 이용함으로써, 정보 출력부(34F)는 전체 블록 중에서 비교 대상 블록의 소거 시간 보다 더 새로운 소거 시간을 가지는 블록들의 범위를 산출한다(단계 S68). 정보 출력부(34F)는 상기 범위를 단기간 재기록 정보로서 블록 제어기(30)에 송신한다. 이 단기간 재기록 정보의 수신시에, 블록 제어기(30)는 단기간 재기록 정보에 포함되는 블록들에 대응하는 단기간 재기록 플래그를 설정하고, 다른 블록들에 대응하는 단기간 재기록 플래그를 클리어한다.

[0122] 단계 S66에서 2 개 이상의 블록들이 남아있지 않으면, 단기간 재기록된 블록을 검출할 수 없다고 판정하고, 단기간 재기록 검출 처리를 종료한다.

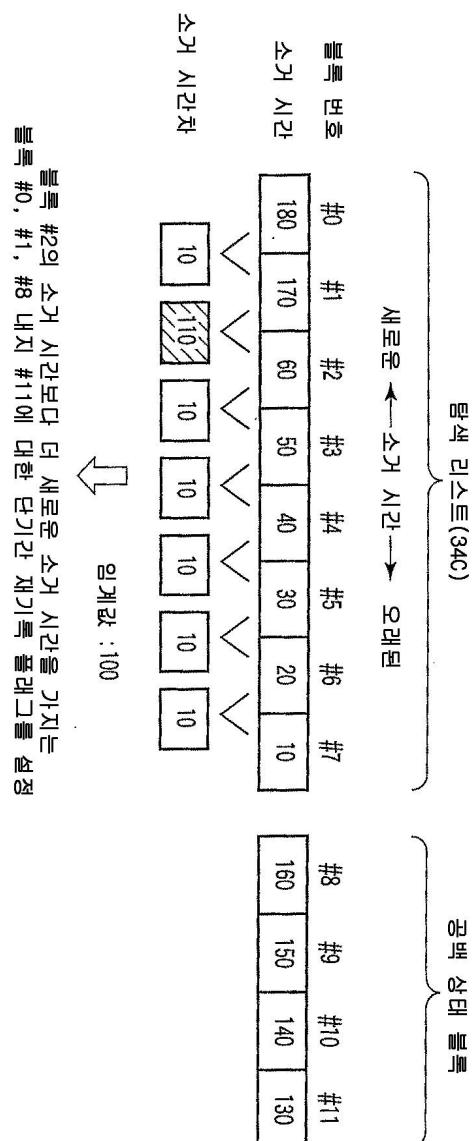

[0123] 도 14는 단기간 재기록 검출기(34)에 의해 수행되는 단기간 재기록 검출 처리의 실용예를 설명하기 위한 도면이다. NAND 플래시 메모리(10)가 12개의 블록(블록 #0 내지 블록 #11)을 포함하고, 블록 #0 내지 블록 #7은 탐색 리스트(34C)에 포함되는 사용중 상태 블록이며, 블록 #8 내지 블록 #11은 공백 상태 블록이라고 가정한다. 블록 #0 내지 블록 7은 가장 새로운 소거 시간을 가지는 블록순으로 정렬된다. 개별 블록들의 소거 시간은 도 14에 도시된 바와 같다.

[0124] 먼저, 탐색 리스트(34C)에서, 가장 새로운 소거 시간을 가지는 블록 #0은 탐색 대상 블록으로서 선택되며, 2 번째로 가장 새로운 소거 시간을 가지는 블록 #1은 비교 대상 블록으로서 선택된다. 블록 #0 및 블록 #1의 소거 시간의 차는 "10"이다. 이 차 "10"은 소거 시간 간격 임계값(예를 들어, "100")을 초과하지 않는다. 따라서, 탐색 대상 블록 #0은 탐색 리스트(34C)에서 제외된다.

[0125] 이후에, 탐색 리스트(34C)에서, 가장 새로운 소거 시간을 가지는 블록 #1은 탐색 대상 블록으로서 선택되며, 2 번째로 가장 새로운 소거 시간을 가지는 블록 #2은 비교 대상 블록으로서 선택된다. 블록 #1과 블록 #2의 소거 시간의 차는 "110"이다. 이 차 "110"은 소거 시간 간격 임계값을 초과한다. 그러므로, 비교 대상 블록 #2의 번호가 판정부(34D)에서 정보 출력부(34F)로 공급된다.

[0126] 공백 상태 블록들을 포함하는 전체 블록 중에서, 정보 출력부(34F)는 비교 대상 블록 #2의 소거 시간 보다 더 새로운 소거 시간을 가지는 블록 #0, #1 및 #8 내지 #11을 산출한다. 정보 출력부(34F)는 블록 #0, #1 및 #8 내지 #11을 단기간 재기록 정보로서 블록 제어기(30)에 송신한다. 블록 제어기(30)는 블록 #0, #1 및 #8 내지 #11에 대응하는 단기간 재기록 플래그들을 설정하고, 다른 블록들에 대응하는 단기간 재기록 플래그들을 클리어한다. 따라서, 블록 테이블(30B)의 정보를 업데이트한다.

[0127] [2-5. 평준화 처리]

[0128] NAND 플래시 메모리(10)의 서비스 수명을 연장하기 위하여, 개별 블록들의 소거 횟수를 동일하게 하고, 단기간

내에 특정 영역에 재기록 처리가 빈번하게 수행되는 것을 피해야 할 필요가 있다. 단지 소거 횟수를 동일화함으로써 NAND 플래시 메모리(10)의 서비스 수명을 연장시키려고 한다면, 기록 상태에 따라서 특정 영역에 대한 재기록 처리가 단기간에 진행될 수도 있다. 단기간에 수정(평준화) 처리를 빈번하게 수행하면, 소거 횟수를 동일하게 하고 단기간 내에 특정 영역에 대한 기록 집중을 피할 수 있다. 그러나, 수정 처리는 소거 횟수를 증가시키므로, 이는 서비스 수명을 연장시킬 수 없다. 한편, 수정 간격을 너무 많이 연장하면, 특정 영역에 짧은 간격의 소거 처리가 집중되므로, 이는 서비스 수명을 단축시킨다. 이러한 발견에 기초하여, 본 실시형태의 평준화 처리에서는, 평준화 처리의 횟수를 최적화하고, 개별 블록의 소거 횟수를 동일하게 한다.

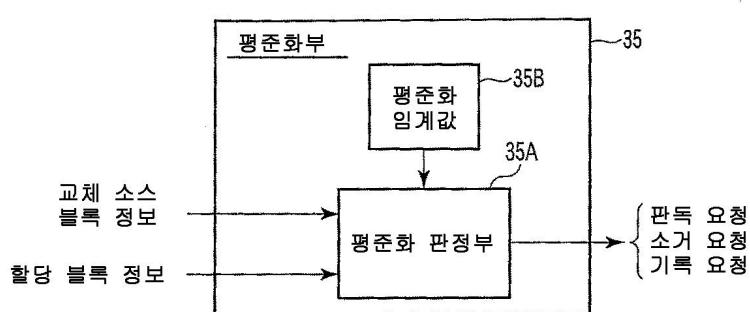

[0129] 평준화부(35) 및 교체 소스 블록 선택기(33)는 평준화 처리를 실행한다. 도 15는 평준화부(35)의 배열을 나타내는 블록도이다. 평준화부(35)는 평준화 판정부(35A) 및 평준화 임계값을 저장하는 기억부(58B)를 포함한다.

[0130] 상기 평준화 판정부(35A)는 평준화 임계값 및 할당 블록 선택기(32)로부터 공급되는 할당 블록 정보 및 교체 소스 블록 선택기(33)로부터 공급되는 교체 소스 블록 정보를 이용함으로써 금회의 기록 동작 동안에 평준화 처리를 수행할 것인지 여부를 판정한다. 평준화 처리를 수행하는 경우, 평준화 판정부(35A)는, 평준화 처리와 연관되는 판독 요청, 소거 요청 및 기록 요청을 NAND 인터페이스 회로(25)에 발행한다.

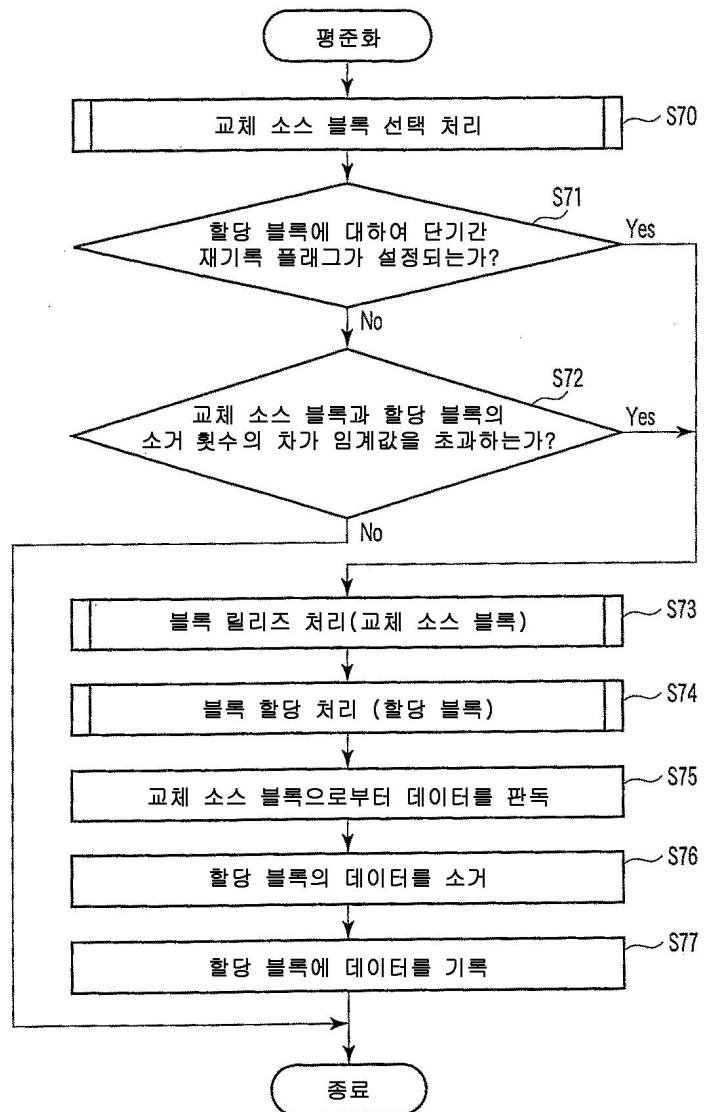

[0131] 도 16은 NAND 제어기(11)에 의해 수행되는 평준화 처리를 나타내는 흐름도이다. 먼저, 교체 소스 블록 선택기(33)는 교체 소스 블록 선택 처리를 실행한다(단계 S70). 이 선택 처리의 결과로서, 교체 소스 블록 정보는 교체 소스 블록 선택기(33)로부터 평준화부(35)로 공급된다.

[0132] 이후에, 평준화 판정부(35A)는 할당 블록 선택기(32)로부터 공급되는 할당 블록 정보를 체크하고, 이 할당 블록 정보에 포함되는 단기간 재기록 플래그가 ON인지 여부를 판정한다(단계 S71). 단기간 재기록 플래그가 OFF이면, 즉, 할당 블록의 재기록이 빈번하게 수행되지 않으면, 평준화 판정부(35A)는 교체 소스 블록과 할당 블록의 소거 횟수의 차가 평준화 임계값을 초과하는지 여부를 판정한다(단계 S72). 그 차가 평준화 임계값을 초과하지 않으면, 평준화부(35)는 금회의 기록 동작에서 평준화 처리를 수행하지 않는다.

[0133] 이 평준화 임계값은 평준화 처리를 실행할지 여부를 판정하는데 사용되며, NAND 플래시 메모리의 서비스 수명(또는 데이터 유지 기간)을 연장시키는 정도를 나타내는 기준에 기초하여 설정된다. 전술된 바와 같이, 단지 소거 횟수를 동일화함으로써 NAND 플래시 메모리(10)의 서비스 수명을 연장시키려고 한다면, 평준화 처리로 인하여 데이터 소거가 복수회 발생하므로, 이는 특정 영역에서의 소거 횟수를 증가시킨다. 따라서, 이 실시형태에서, 평준화 처리는 교체 소스 블록과 할당 블록의 소거 횟수의 차가 평준화 임계값을 초과한 경우에만 실행된다.

[0134] 단계 S71에서 단기간 재기록 플래그가 ON이거나 또는 단계 S72에서 평준화 임계값을 초과하면, 블록 제어기(30)는 교체 소스 블록에서 블록 릴리즈 처리를 실행한다(단계 S73). 이 블록 릴리즈 처리는 도 7의 블록 릴리즈 처리와 동일하다.

[0135] 이후에, 블록 제어기(30)는 할당 블록 선택기(32)에 의해 선택되는 할당 블록을 교체 소스 블록의 데이터를 이동시키는 블록으로서 할당하는 블록 할당 처리를 실행한다(단계 S74). 이 블록 할당 처리는 도 10에 도시된 블록 할당 처리와 동일하다.

[0136] 그 후, NAND 제어기(11)는 NAND 플래시 메모리(10)에 포함되는 교체 소스 블록의 데이터를 판독한다(단계 S75). 보다 상세하게는, 평준화 판정부(35A)는 교체 소스 블록 선택기(33)로부터 공급되는 교체 소스 블록 정보를 이용함으로써 NAND 인터페이스 회로(25)에 판독 요청을 발행한다. 이 판독 요청에 기초하여, NAND 인터페이스 회로(25)는 NAND 플래시 메모리(10)에게 교체 소스 블록으로부터 데이터를 판독하도록 지시한다. 그 판독된 데이터는 예를 들어 RAM(24)에 일시적으로 저장된다.

[0137] 그 후에, NAND 제어기(11)는 할당 블록의 데이터를 소거한다(단계 S76). 더욱 상세하게는, 평준화 판정부(35A)는 할당 블록 선택기(32)로부터 공급되는 할당 블록 정보를 이용함으로써 NAND 인터페이스 회로(25)에 소거 요청을 발행한다. 이 소거 요청에 기초하여, NAND 인터페이스 회로(25)는 NAND 플래시 메모리(10)에게 할당 블록의 데이터를 소거하도록 지시한다. 이 단계에서, 블록 제어기(30)는 할당 블록의 소거 횟수 및 소거 시간이 업데이트된다(도 11 참조).

[0138] 이후에, NAND 제어기(11)는 교체 소스 블록으로부터 판독된 데이터를 NAND 플래시 메모리(10)에 포함되는 할당 블록에 기록한다(단계 S77). 보다 상세하게는, 평준화 판정부(35A)는 할당 블록 정보를 이용함으로써 NAND 인터페이스 회로(25)에 기록 요청을 발행한다. 이 기록 요청에 기초하여, NAND 인터페이스 회로(25)는 NAND 플래시

시 메모리(10)에게 교체 목적지 블록에 데이터를 기록하도록 지시한다.

[0139] 상기 처리는 교체 소스 블록의 데이터를 할당 블록으로 이동시키며, 교체 소스 블록을 공백 상태 블록으로 사용하는 것을 가능하게 한다. 따라서, 재기록이 빈번하게 수행되지 않는다고 가정되는 교체 소스 블록을 할당 블록으로서 재사용할 수 있다. 또한, 빈번하게 재기록되지 않는 데이터를 이미 큰 소거 횟수를 가지는 할당 블록으로 이동시킨다. 이는 장래에 할당 블록의 소거 횟수가 증가하는 것을 방지할 수 있다.

[0140] [2-6-1. 교체 소스 블록 선택 처리]

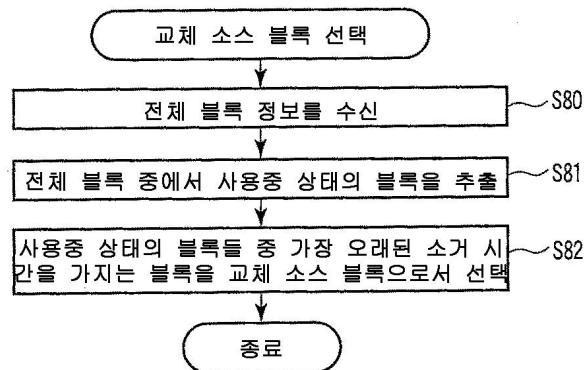

[0141] 도 17은 교체 소스 블록 선택기(33)의 배열을 나타내는 블록도이다. 도 18은 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리를 나타내는 흐름도이다.

[0142] 교체 소스 블록 선택기(33)는, 2 개의 선택기(33A 및 33B)를 구비한다. 교체 소스 블록 선택기(33)는 블록 제어기(30)로부터 전체 블록 정보를 수신한다(단계 S80). 이 전체 블록 정보는 선택기(33A)에 공급된다. 선택기(33A)는 전체 블록의 상태를 체크하고, 전체 블록 중에서 사용중 상태의 블록들을 추출한다(단계 S81). 그 후, 선택기(33A)는 사용중 상태의 블록들에 대응하는 블록 정보(사용중 상태 블록 정보)를 선택기(33B)에 송신한다.

[0143] 선택기(33A)에 의해 추출된 블록들로부터, 선택기(33B)는 가장 오래된 소거 시간을 가지는 블록을 교체 소스 블록으로서 선택한다(단계 S82). 이 교체 소스 블록에 대응하는 교체 소스 블록 정보는 평준화 회로(35)에 공급된다. 상술된 바와 같이 교체 소스 블록 선택 처리는, 빈번하게 재기록되지 않는 데이터를 기억하며 양호한 유지 특성을 가지는 블록을, 교체 소스 블록으로서 선택할 수 있다.

[0144] 위에서 상세히 설명된 바와 같이 이 실시형태에서는, 각 블록으로부터 데이터가 소거된 소거 시간을 측정하고, 블록들과 소거 시간을 이들과 서로 연관되는 블록 테이블(30B)에 기억한다. 외부로 공급된 데이터를 NAND 플래시 메모리(10)에 기록하는 경우에, 가장 오래된 소거 시간을 가지는 공백 상태 블록을 할당 블록으로서 선택하고, 이 할당 블록에 데이터를 기록한다.

[0145] 따라서, 이 실시형태는 각 블록의 소거 간격을 연장시킬 수 있다. 이는 소거 간격을 연장시킴으로써 유지 특성을 회복시키는 메모리 셀 트랜지스터 특성을 이용하여 각 블록의 유지 특성의 저하를 감소시킬 수 있다. 그 결과, NAND 플래시 메모리(10)의 서비스 수명을 연장시킬 수 있다.

[0146] 또한, 이 실시형태에서는, 단기간 재기록 검출기(34)는 데이터가 빈번하게 재기록되는 블록을 특정한다. 이 블록이 할당 블록으로서 선택되면, 이 할당 블록은 오래된 소거 시간을 가지는 교체 소스 블록이 교체되고, 교체 소스 블록에 기억되며 빈번하게 교체되지 않는 데이터를 할당 블록으로 이동시킨다. 그 결과, 한번 기록되고 할당된 채로 장기간 동안 릴리지되지 않은 교체 소스 블록도 평준화 처리에 의해 릴리즈된다. 따라서, 데이터가 빈번하게 재기록되지 않는다고 가정되는 교체 소스 블록을 할당 블록으로서 재사용할 수 있다. 또한, 빈번하게 재기록되지 않는 데이터는 할당 블록에 기억된다. 이는 이후의 데이터 소거 횟수를 감소시키며 할당 블록의 유지 특성의 저하를 감소시킬 수 있다.

[0147] 또한, 교체 소스 블록과 할당 블록의 소거 횟수 사이의 차가 임계값을 초과하는 경우에 평준화 처리를 수행한다. 이는 평준화가 빈번하게 수행되지 않기 때문에 평준화의 횟수를 최적화하고 블록들의 소거 횟수를 서로 동일하게 할 수 있다. 그 결과, 일부 블록의 소거 횟수를 증가시킴으로써 전체 NAND 플래시 메모리(10)의 서비스 수명이 단축되는 것을 방지할 수 있다.

[0148] 멀티레벨 데이터 기록 시스템을 적용하는 경우에, 메모리 셀의 트랜지스터(MT)의 임계값 분포에 대하여 미세한 제어가 요구된다. 따라서, 유지 특성의 저하를 방지하는 것이 이점이 된다.

[0149] [제 2 실시형태]

[0150] 제 2 실시형태는 할당 블록 선택기(32)에 의해 수행되는 할당 블록 선택 처리의 또 다른 일례를 개시한다. 즉, 오래된 소거 시간 및 작은 소거 횟수를 가지는 블록을 할당 블록으로서 선택한다.

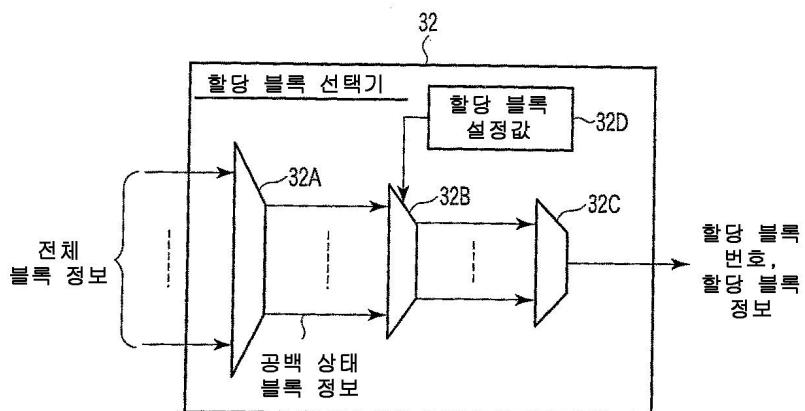

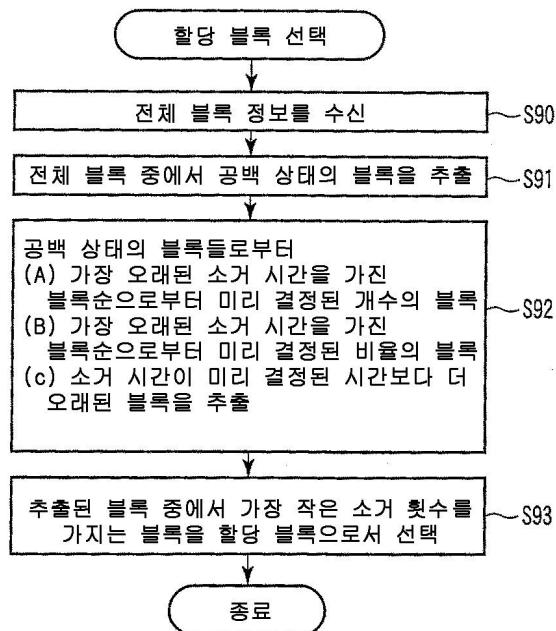

[0151] 도 19는 제 2 실시형태에 따른 할당 블록 선택기(32)의 배열을 나타내는 블록도이다. 도 20은 할당 블록 선택기(32)에 의해 수행되는 할당 블록 선택 처리를 나타내는 흐름도이다. NAND 제어기(11)의 배열은, 할당 블록 선택기(32)를 제외하고는, 제 1 실시형태의 배열과 동일하다.

[0152] 할당 블록 선택기(32)는, 3 개의 선택기(32A 내지 32C) 및 할당 블록 설정값을 기억하는 기억부(32D)를 가진다. 할당 블록 선택기(32)는 블록 제어기(30)로부터 전체 블록 정보를 수신한다(단계 S90). 이 전체 블록 정보는 선택기(32A)에 공급된다. 선택기(32A)는 전체 블록의 상태를 체크하고, 전체 블록 중에서 공백 상태 블록들을

추출한다(단계 S91). 그 후, 선택기(32A)는 공백 상태 블록들에 대응하는 블록 정보(공백 상태 블록 정보)를 선택기(32B)에 송신한다.

[0153] 선택기(32B)는 공백 상태 블록 정보로부터 할당 블록 설정값에 의해 설정된 조건을 충족하는 블록 정보를 추출한다(단계 S92). 할당 블록 설정값은,

(A) 가장 오래된 소거 시간을 가진 블록으로부터 시작하는 미리 결정된 개수의 블록들

[0155] (B) 가장 오래된 소거 시간을 가진 블록으로부터 시작하는 미리 결정된 비율의 블록들

[0156] (C) 소거 시간이 미리 결정된 시간 보다 더 오래된 블록들

[0157] 중 하나이다.

[0158] 조건 (A) 내지 (C) 중 임의의 하나는 할당 블록 설정값으로서 선택될 수 있다. 예를 들어, 할당 블록 설정값으로서 조건 (A)를 이용하면, 선택기(32B)는 공백 상태 블록들로부터 가장 오래된 소거 시간을 가진 블록순으로 미리 결정된 개수의 블록들을 추출한다. 그 후, 선택기(32B)는 추출된 블록들에 대응하는 블록 정보를 선택기(32C)에 보낸다.

[0159] 조건 (A) 및 (B) 하에서, 공백 상태 블록들은, 소거 시간순으로 정렬되고, 가장 오래된 소거 시간을 가지는 블록순으로 미리 결정된 개수/미리 결정된 비율의 블록들을 탐색한다. 따라서, 단계 S92에서 선택되는 블록들의 개수를 증가시킬 수 있기 때문에, 단계 S93에서 작은 소거 횟수를 가진 블록을 선택할 확률을 증가시킬 수 있다. 조건 (C) 하에서, 소거 시간이 미리 결정된 시간을 초과하는 공백 상태 블록들 만을 정렬해야 하므로, 처리 부하가 가장 낮다. 조건 (A) 및 (B) 하에서는, 가장 오래된 소거 시간을 가진 블록순으로 미리 결정된 개수/미리 결정된 비율의 블록들이 항상 추출되며, 조건 (C)에서는, 미리 결정된 시간 보다 더 오래된 소거 시간을 가지는 블록들이 추출된다. 따라서, 조건 (C) 하에서, 소거 간격은 항상 미리 결정된 간격이 되므로, 이에 따라 소거 횟수의 비교 후보의 수가 감소될 수 있다.

[0160] 이후에, 선택기(32C)는 선택기(32B)에 의해 추출된 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 할당 블록으로서 선택한다(단계 S93). 이 할당 블록에 대응하는 할당 블록 번호는 블록 제어기(30)에 공급된다. 또한, 상기 할당 블록에 대응하는 할당 블록 정보는 평준화부(35)에 공급된다.

[0161] 위에서 상세히 설명한 바와 같이, 본 실시형태에서는, 외부로부터 공급되는 데이터를 기록하는 할당 블록을 선택할 때, 공백 상태 블록들 중에서 오래된 소거 시간과 작은 소거 횟수를 가지는 블록을 할당 블록으로서 선택할 수 있다. 이는 양호한 유지 특성을 가지는 블록에 외부로부터의 데이터를 기록할 수 있어, NAND 플래시 메모리(10)의 서비스 수명을 연장시킬 수 있다.

[0162] [제 3 실시형태]

[0163] 제 3 실시형태는 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리의 또 다른 일례를 개시 한다. 즉, 오래된 소거 시간 및 작은 소거 횟수를 가지는 블록을 할당 블록으로서 선택한다.

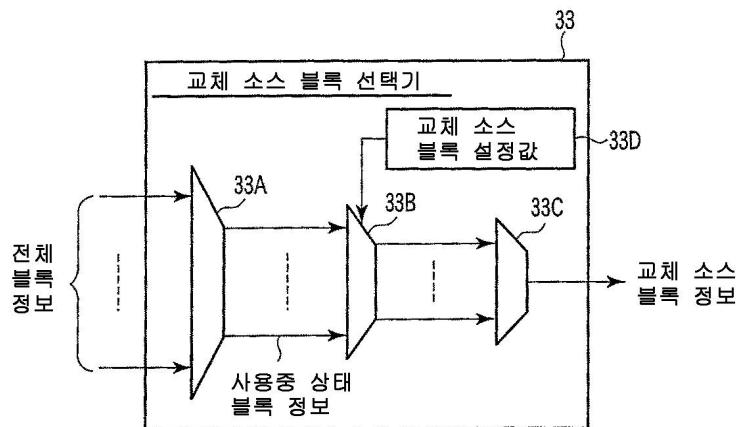

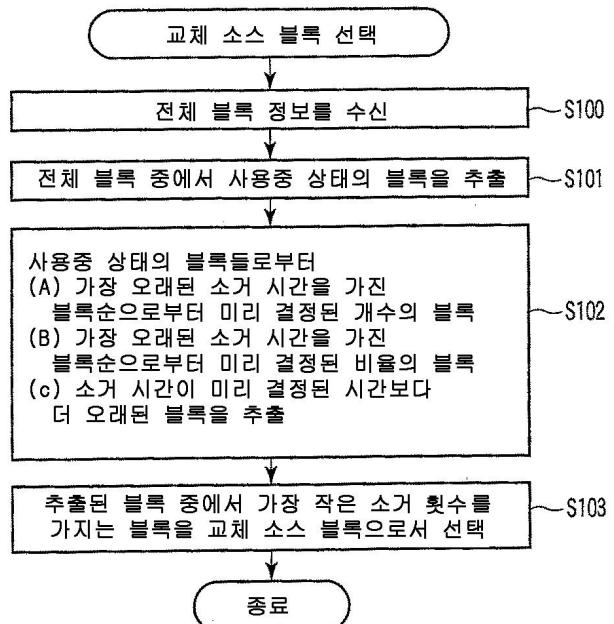

[0164] 도 21은 제 3 실시형태에 따른 교체 소스 블록 선택기(33)의 배열을 나타내는 블록도이다. 도 22는 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리를 나타내는 흐름도이다.

[0165] 교체 소스 블록 선택기(33)는, 3 개의 선택기(33A 내지 33C) 및 교체 소스 블록 설정값을 기억하는 기억부(33D)를 가진다. 교체 소스 블록 선택기(33)는 블록 제어기(30)로부터 전체 블록 정보를 수신한다(단계 S100). 이 전체 블록 정보는 선택기(32A)에 공급된다. 선택기(32A)는 전체 블록의 상태를 체크하고, 전체 블록 중에서 사용중 상태 블록들을 추출한다(단계 S101). 그 후, 선택기(32A)는 사용중 상태 블록들에 대응하는 블록 정보(사용중 상태 블록 정보)를 선택기(33B)에 공급한다.

[0166] 선택기(33B)는 사용중 상태 블록 정보로부터 교체 소스 블록 설정값에 의해 설정된 조건을 충족하는 블록 정보를 추출한다(단계 S102). 교체 소스 블록 설정값은,

(A) 가장 오래된 소거 시간을 가진 블록으로부터 시작하는 미리 결정된 개수의 블록들

[0168] (B) 가장 오래된 소거 시간을 가진 블록으로부터 시작하는 미리 결정된 비율의 블록들

[0169] (C) 소거 시간이 미리 결정된 시간 보다 더 오래된 블록들

[0170] 중 하나이다.

[0171] 조건 (A) 내지 (C) 중 임의의 하나는 교체 소스 블록 설정값으로서 선택될 수 있다. 예를 들어, 교체 소스 블록 설정값으로서 조건 (A)를 이용하면, 선택기(33B)는 사용중 상태 블록들로부터 가장 오래된 소거 시간을 가진 블록순으로 미리 결정된 개수의 블록들을 추출한다. 그 후, 선택기(33B)는 추출된 블록들에 대응하는 블록 정보를 선택기(32C)에 보낸다.

[0172] 조건 (A) 및 (B) 하에서, 사용중 상태 블록들은, 소거 시간순으로 정렬되고, 가장 오래된 소거 시간을 가지는 블록순으로 미리 결정된 개수/미리 결정된 비율의 블록들을 탐색한다. 따라서, 단계 S102에서 선택되는 블록들의 개수를 증가시킬 수 있기 때문에, 단계 S103에서 작은 소거 횟수를 가진 블록을 선택할 확률을 증가시킬 수 있다. 조건 (C) 하에서는, 소거 시간이 미리 결정된 시간을 초과하는 사용중 상태 블록들 만을 정렬해야 하므로, 처리 부하가 가장 낮다. 또한, 조건 (A) 및 (B) 하에서는, 가장 오래된 소거 시간을 가진 블록순으로 미리 결정된 개수/미리 결정된 비율의 블록들이 항상 추출되며, 조건 (C)에서는, 미리 결정된 시간 보다 더 오래된 소거 시간을 가지는 블록들이 추출된다. 따라서, 조건 (C) 하에서, 소거 간격은 항상 미리 결정된 간격이 되므로, 이에 따라 소거 횟수의 비교 후보의 수가 감소될 수 있다.

[0173] 이후에, 선택기(32C)는 선택기(32B)에 의해 추출된 블록들 중에서 가장 작은 소거 횟수를 가지는 블록을 교체 소스 블록으로서 선택한다(단계 S103). 이 교체 소스 블록에 대응하는 교체 소스 블록 정보를 평준화부(35)에 공급된다.

[0174] 위에서 상세히 설명한 바와 같이, 본 실시형태에서는, 평준화에 사용될 교체 소스 블록을 선택할 때, 사용중 상태 블록들 중에서 오래된 소거 시간과 작은 소거 횟수를 가지는 블록을 교체 소스 블록으로서 선택할 수 있다. 이는 빈번하게 재기록되지 않는 데이터를 기억하며 양호한 유지 특성을 가지는 블록을 교체 소스 블록으로서 선택하여, NAND 플래시 메모리(10)의 서비스 수명을 연장시킬 수 있다.

[0175] [제 4 실시형태]

[0176] 제 4 실시형태는 단기간 재기록 검출 처리의 또 다른 일례를 개시한다. 제 4 실시형태에서, 단기간 재기록 검출 처리는 이분 탐색법을 이용하여 수행된다.

[0177] 도 23은 제 4 실시형태에 따른 단기간 재기록 검출기(34)의 배열을 나타내는 블록도이다. 단기간 재기록 검출기(34)는 선택기(34A), 정렬부(34B), 탐색 리스트(34C), 판정부(34D), 집중 계수 임계값을 기억하는 기억부(34E) 및 정보 출력부(34F)를 구비한다.

[0178] 판정부(34D)는 이분 탐색법을 이용함으로써 탐색 리스트(34C)에서 탐색 대상 블록을 선택한다. 그 후, 판정부(34D)는 이 탐색 대상 블록에 대하여 단기간 재기록 검출에 사용될 집중 계수를 산출하고, 이 집중 계수가 집중 계수 임계값을 초과하는지 여부를 판정한다. 판정 결과에 기초하여, 블록들은 탐색 리스트(34C)로부터 제외되고, 하나의 탐색 대상 블록으로 좁혀진다. 마지막 탐색 대상 블록을 이용함으로써, 소거 시간이 급격하게 변하는 경계를 탐색한다.

[0179] 기억부(34E)에 기억되는 집중 계수 임계값은 데이터가 빈번하게 재기록되는 블록들의 범위를 특정하는데 사용되며, NAND 플래시 메모리(10)의 서비스 수명(또는 데이터 유지 기간)을 연장시키는 정도를 나타내는 기준에 기초하여 설정된다. 집중 계수 임계값이 감소되는 경우에 단기간 재기록 검출의 가능성성이 증가하며, 그 임계값이 증가되는 경우에 단기간 재기록 검출의 가능성성이 감소된다.

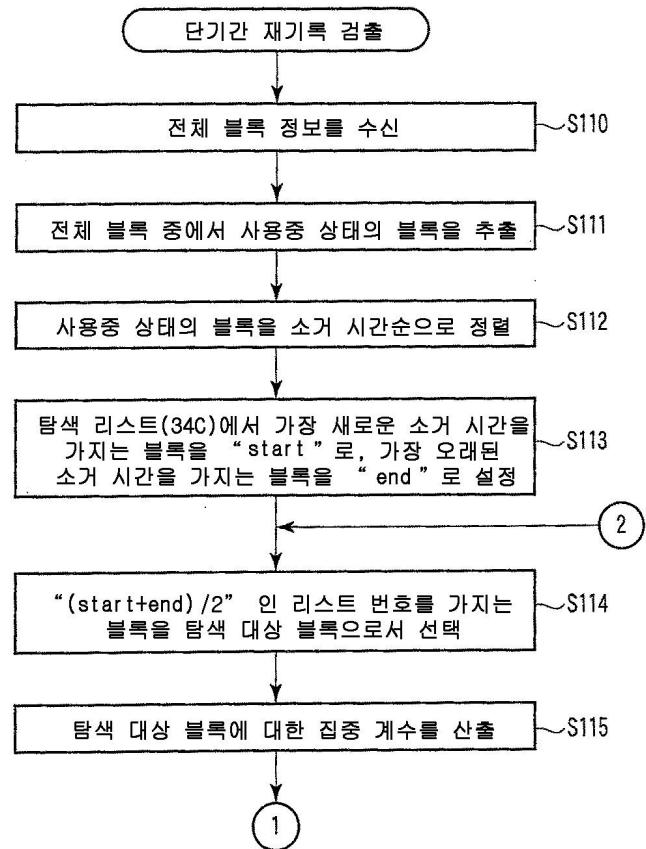

[0180] 도 24 및 도 25는 단기간 재기록 검출기(34)에 의해 수행되는 단기간 재기록 검출 처리를 나타내는 흐름도이다.

[0181] 먼저, 단기간 재기록 검출기(34)는 블록 제어기(30)로부터 전체 블록 정보를 수신한다(단계 S110). 이 전체 블록 정보는 선택기(34A)에 공급된다. 이 선택기(34A)는 전체 블록의 상태를 체크하고, 전체 블록 중에서 사용중 상태 블록을 추출한다(단계 S111). 그 후, 선택기(34A)는 사용중 상태 블록들에 대응하는 블록 정보(사용중 상태 블록 정보)를 정렬부(34B)에 보낸다.

[0182] 정렬부(34B)는 사용중 상태 블록 정보에 포함되는 소거 시간을 체크하고, 사용중 상태 블록들을 소거 시간순으로 정렬한다(단계 S112). 정렬부(34B)에 의해 정렬된 블록 정보는 탐색 리스트(34C)에 배치되며, 리스트 번호는 가장 새로운 소거 시간을 가지는 블록순으로 블록들에 부여된다.

[0183] 이후에, 판정부(34D)는 탐색 리스트(34C)에서 가장 새로운 소거 시간을 가지는 블록을 "start"로서 설정하고, 가장 오래된 소거 시간을 가지는 블록을 "end"로서 설정한다(단계 S113). 그 후, 판정부(34D)는 리스트 번호 "(start + end)/2" 를 가지는 블록을 탐색 대상 블록으로서 선택한다(단계 S114).

[0184] 이 후에, 판정부(34D)는 탐색 대상 블록에 대한 집중 계수를 산출한다(단계 S115). 이 집중 계수는, 집중 계수 = 현재 시각 - 리스트 번호 - 소거 시간

[0185] 예 의해 주어진다.

[0186] 집중 계수에 사용되는 현재 시각은 예를 들어, 소거 시간 측정부(31)로부터 단기간 재기록 검출기(34)에 공급된다. 현재 시각으로서, 예를 들어 소거 횟수 카운터(31A)의 카운트값을 이용할 수 있다.

[0187] 그 후, 판정부(34D)는 산출된 집중 계수가 집중 계수 임계값을 초과하는지 여부를 판정한다(단계 S116). 집중 계수가 집중 계수 임계값을 초과하면, 판정부(34D)는 탐색 대상 블록을 "end"로서 설정한다(단계 S117). 이후에, 판정부(34D)는 탐색 리스트(34C)로부터 "end"의 소거 시간 보다 더 오래된 소거 시간을 가지는 블록들을 제외한다(단계 S117).

[0188] 한편, 단계 S116에서, 집중 계수가 집중 계수 임계값을 초과하지 않는다고 판정되면, 판정부(34D)는, 탐색 대상 블록의 소거 시간 다음으로 가장 오래된 소거 시간을 가지는 블록을 "start"로서 설정한다(단계 S119). 그 후에, 판정부(34D)는 "start"의 소거 시간보다 더 새로운 소거 시간을 가지는 블록들을 탐색 리스트(34C)로부터 제외한다(단계 S120).

[0189] 단계 S118 또는 단계 S120에서 미리 결정된 블록들이 탐색 리스트(34C)로부터 제외된 이후에, 판정부(34D)는 2개 이상의 블록들이 탐색 리스트(34C)에 남아 있는지를 판정한다(단계 S121). 탐색 리스트(34C)에 2개 이상의 블록이 남아 있으면, 판정부(34D)는 단계 S114로 리턴하고 탐색 대상 블록을 다시 선택한다.

[0190] 단계 S121에서 2개 이상의 블록이 탐색 리스트(34C)에 남아있지 않다고 판정되면, 판정부(34D)는 탐색 리스트(34C)에 남겨진 마지막 블록을 탐색 대상 블록으로서 선택한다. 그 후, 판정부(34D)는 이 탐색 대상 블록에 대하여 집중 계수(= 현재 시각 - 리스트 번호 - 소거 시간)을 산출한다.

[0191] 이후에, 판정부(34D)는 산출된 집중 계수가 집중 계수 임계값을 초과하는지 여부를 판정한다(단계 123). 집중 계수가 집중 계수 임계값을 초과하면, 판정부(34D)는 탐색 대상 블록 번호를 정보 출력부(34F)에 보낸다. 이 탐색 대상 블록 번호를 이용함으로써, 정보 출력부(34F)는 전체 블록들 중에서 탐색 대상 블록의 소거 시간 보다 더 새로운 소거 시간을 가지는 블록들의 범위를 산출한다(단계 S124). 정보 출력부(34F)는 상기 범위를 단기간 재기록 정보로서 블록 제어기(30)에 보낸다. 이 단기간 재기록 정보의 수신 시에, 블록 제어기(30)는 단기간 재기록 정보에 포함되는 블록들에 대응하는 단기간 재기록 플래그를 설정하고, 다른 블록들에 대한 단기간 재기록 플래그를 클리어한다.

[0192] 단계 S123에서 집중 계수가 집중 계수 임계값을 초과하지 않는다고 판정되면, 판정부(34D)는 단기간 재기록된 블록을 검출할 수 없다고 판정하고, 단기간 재기록 검출 처리를 종료한다.

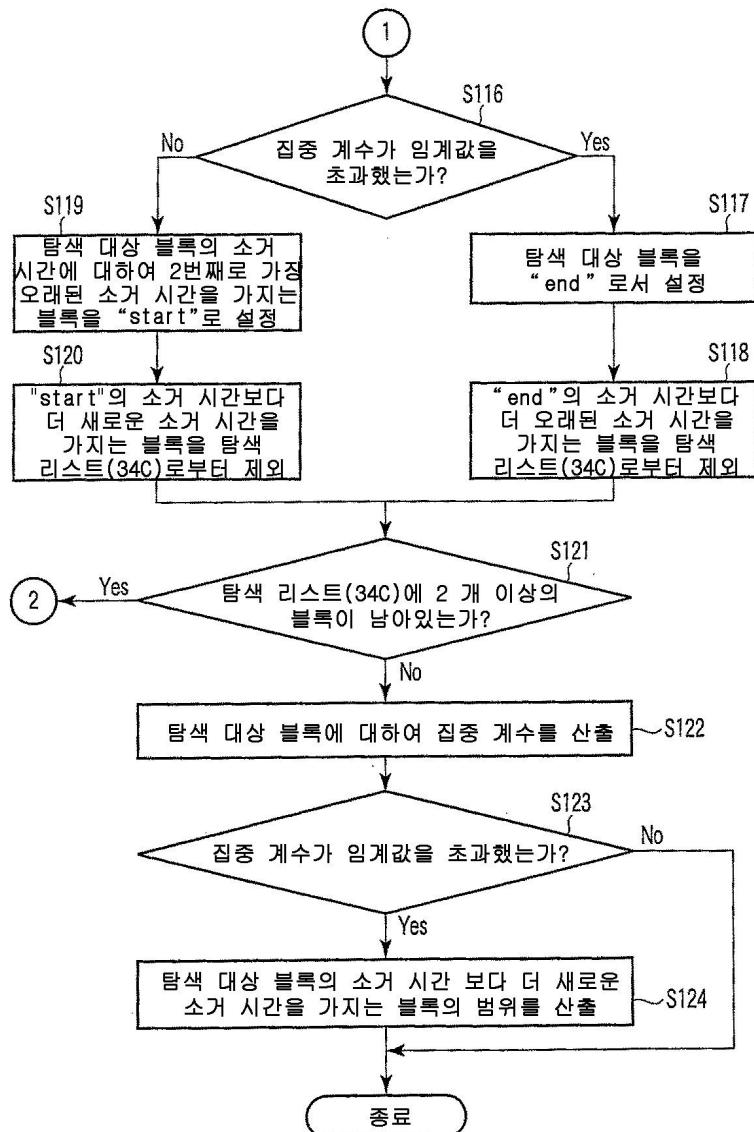

[0193] 도 26은 단기간 재기록 검출기(34)에 의해 수행되는 단기간 재기록 검출 처리의 실용예를 설명하기 위한 도면이다. NAND 플래시 메모리(10)가 12개의 블록(블록 #0 내지 블록 #11)을 포함하고, 블록 #0 내지 블록 #7은 탐색 리스트(34C)에 포함되는 사용중 상태 블록이며, 블록 #8 내지 블록 #11은 공백 상태 블록이라고 가정한다. 블록 #0 내지 블록 7은 가장 새로운 소거 시간을 가지는 블록으로 부터 소거 시간순으로 정렬된다. 이러한 블록들의 소거 시간은 도 26에 도시된 바와 같다. 탐색 리스트(34C)에 포함되는 블록 #0 내지 블록 #7은 가장 새로운 소거 시간을 가지는 블록순으로 리스트 번호를 부여 받는다.

[0194] 먼저, 탐색 리스트(34C)에서, 가장 새로운 소거 시간을 가지는 블록 #0은 "start"로서 선택되며, 가장 오래된 소거 시간을 가지는 블록 #7은 "end"로서 설정된다. 이후에, 리스트 번호 "(start + end)/2"를 가지는 블록 #3은 탐색 대상 블록으로서 선택되고, 집중 계수(= 현재 시각 - 리스트 번호 - 소거 시간)은 탐색 대상 블록 #3으로서 선택되며, 이 집중 계수가 집중 계수 임계값을 초과하는지 여부가 체크된다. 현재 시각이 "106"이며, 집중 계수 임계값이 "90"이라고 가정한다. 탐색 대상 블록 #3의 집중 계수는 "97"이며, 이 값은 임계값을 초과한다. 따라서, 탐색 대상 블록 #3이 "end"로서 설정되고, 블록 #3의 소거 시간 보다 더 오래된 소거 시간을 가지는 블록 #4 내지 #7이 탐색 리스트(34C)로부터 제외된다.

[0195] 그 후, 리스트 번호 "(start + end)/2"를 가지는 블록 #1은 탐색 대상 블록으로서 선택되고, 집중 계수는 탐색 대상 블록 #1에 대하여 산출된다. 탐색 대상 블록 #1의 집중 계수는 "0"이며, 이 값은 임계값을 초과하지 않는다. 따라서, 탐색 대상 블록 #1의 소거 시간 다음으로 오래된 소거 시간을 가지는 블록 #2는 "start"로서 설정되며, 블록 #2의 소거 시간 보다 더 새로운 소거 시간을 가지는 블록 #0 및 블록 #1은 탐색 리스트(34C)로부터

제외된다.

[0197] 그 후에, 리스트 번호 "(start + end)/2"를 가지는 블록 #2는 탐색 대상 블록으로서 선택되고, 집중 계수는 탐색 대상 블록 #2에 대하여 산출된다. 탐색 대상 블록 #2의 집중 계수는 "97"이며, 이 값은 임계값을 초과한다. 따라서, 탐색 대상 블록 #2은 "end"로서 설정되며, 블록 #2의 소거 시간보다 더 오래된 소거 시간을 가지는 블록 #3은 탐색 리스트(34C)로부터 제외된다.

[0198] 이후에, 탐색 리스트(34C)에 마지막으로 남겨지는 블록 #2는 탐색 대상 블록으로서 선택되며, 집중 계수는 탐색 대상 블록 #2에 대하여 산출된다. 탐색 대상 블록 #2의 이 집중 계수는 임계값을 초과한다. 따라서, 판정부(34D)는 탐색 대상 블록 #2의 번호를 정보 출력부(34F)로 보낸다.

[0199] 공개 상태 블록들을 포함하는 전체 블록들 중에서, 정보 출력부(34F)는, 탐색 대상 블록 #2의 소거 시간보다 더 새로운 소거 시간을 가지는 블록 #0, #1, #8 내지 #11을 산출한다. 정보 출력부(34F)는 블록 #0, #1, #8 내지 #11을 단기간 재기록 정보로서 블록 제어기(30)에 보낸다. 블록 제어기(30)는 블록 #0, #1, #8 내지 #11에 대응하는 단기간 재기록 플래그를 설정하고, 다른 블록들에 대응하는 단기간 재기록 플래그들을 클리어한다. 따라서, 블록 테이블(30B)의 정보를 업데이트한다.

[0200] 위에서 상세히 설명한 바와 같이, 본 실시형태에서는, 단기간 재기록 검출기(34)는 데이터가 빈번하게 재기록되는 블록을 특정할 수 있다. 또한, 단기간 재기록 검출 처리에서 임계값을 " $\log_2 N$ "회로 체크함으로써 탐색이 완료된다. 이는 단기간 재기록 검출의 효율을 증가시킬 수 있다.

[0201] [제 5 실시형태]

[0202] 제 5 실시형태에서, NAND 제어기(11)는 에러 체크 및 정정(ECC) 회로를 포함하고, 이 ECC 회로는 판독된 데이터에서 에러를 검출 및 정정한다. 일반적으로, 데이터 기록으로부터의 시간이 경과함에 따라 에러 수는 증가한다. 따라서, 많은 에러를 가지는 블록은 아마도 오래된 소거 시간을 가지는 블록일 것이다. 따라서, 이 실시형태에서, ECC 회로에 의해 검출된 에러 수는 교체 소스 블록 선택의 지표로서 사용된다.

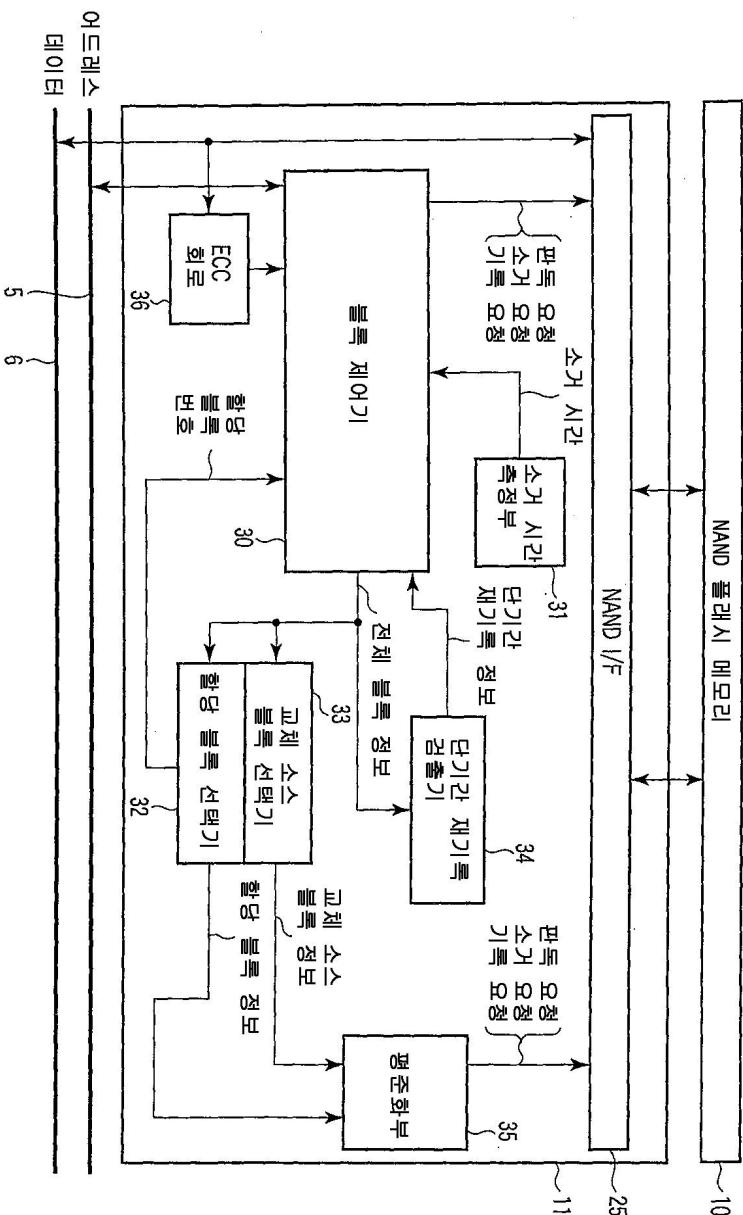

[0203] 도 27은 제 5 실시형태에 따른 NAND 제어기(11)의 배열의 일례를 나타내는 블록도이다. NAND 제어기(11)는 ECC 회로(36)를 구비한다. NAND 플래시 메모리(10)로부터 데이터를 판독하는 경우, ECC 회로(36)는 에러를 검출 및 정정한다. 또한, ECC 회로(36)는 각 블록에 대하여 검출된 에러 수를 블록 제어기(30)로 송신한다.

[0204] 도 28은 블록 제어기(30)의 배열을 나타내는 블록도이다. 상기 블록 제어기(30)에 포함되는 블록 테이블(30B)은 각 블록 번호에 대한 에러 수를 저장한다. 블록 테이블(30B)에 포함되는 에러 수는, NAND 플래시 메모리(10)로부터 데이터가 판독될 때마다(ECC 회로(36)가 에러를 정정할 때마다) 업데이트된다.

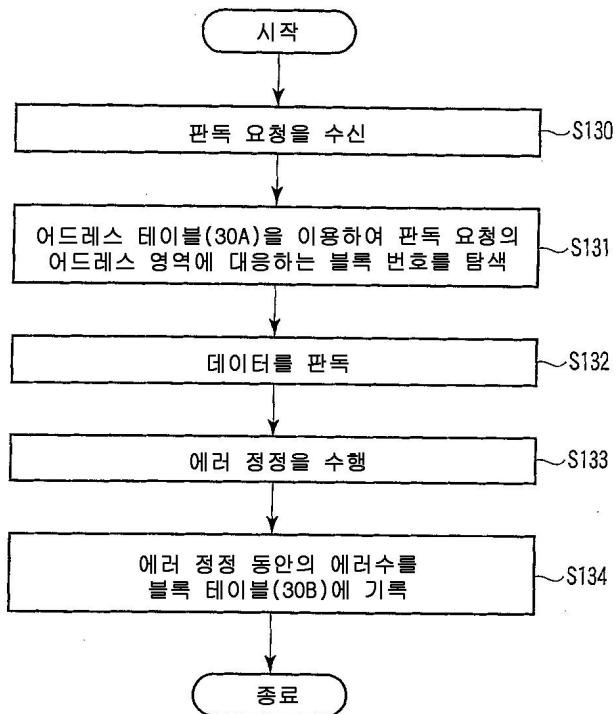

[0205] 다음으로, NAND 제어기(11)의 판독 동작을 설명한다. 도 29는 NAND 제어기(11)에 의해 수행되는 판독 동작을 나타내는 흐름도이다.

[0206] 먼저, NAND 제어기(11)는 CPU(2)로부터의 판독 요청 수신시에 판독 동작을 개시한다(단계 S130). 그 후, 블록 제어기(30)는 어드레스 테이블(30A)을 이용함으로써 판독 요청의 어드레스를 포함하는 어드레스 영역에 대응하는 블록 번호를 탐색한다(단계 S131).

[0207] 이후에, 블록 제어기(30)는 판독 요청의 블록으로부터 데이터를 판독한다(단계 S132). 즉, 블록 제어기(30)는 NAND 인터페이스 회로(25)에 판독 요청을 발행한다. 이 판독 요청에 기초하여, NAND 인터페이스 회로(25)는 NAND 플래시 메모리(10)에게 판독 요청의 블록으로부터 데이터를 판독하도록 지시한다.

[0208] 그 후에, ECC 회로(36)는 NAND 플래시 메모리(10)로부터 판독된 데이터에 대하여 에러 검출 및 정정을 수행한다(단계 S133). 에러 정정된 판독 데이터는 데이터 버스(6)를 통하여 CPU(2) 등에 공급된다. 이 에러 정정에서, ECC 회로(36)는 에러 수를 산출하고, 그 에러 수를 블록 제어기(30)로 보낸다. 블록 제어기(30)는 ECC 회로(36)로부터 에러 수를 수신하고, 그 에러 수를 블록 테이블(30B)에 기록한다. 이러한 방식으로, 블록 테이블(30B)에 포함되는 에러 수를 업데이트한다.

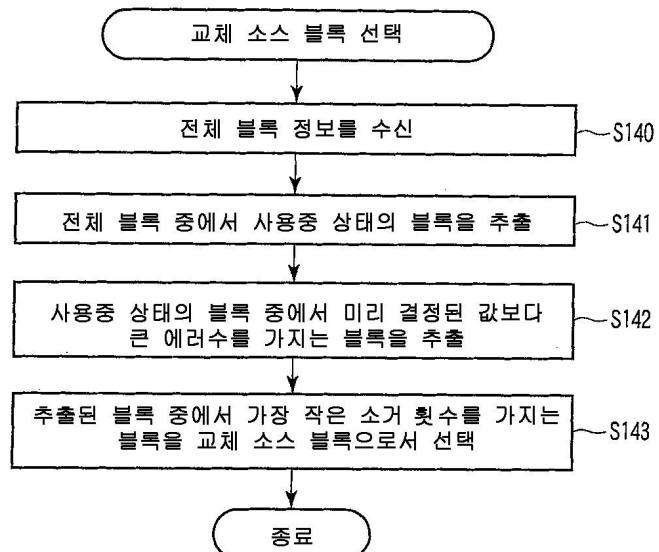

[0209] 이하에서, 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리를 설명한다. 도 30은 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리를 나타내는 흐름도이다. 교체 소스 블록 선택기(33)의 배열은 도 21에 도시된 배열과 동일하다.

[0210] 교체 소스 블록(33)은 블록 제어기로부터 전체 블록 정보를 수신한다(단계 S140). 이 전체 블록 정보는 선택기(33A)에 공급된다. 선택기(33A)는 전체 블록의 상태를 체크하고, 전체 블록으로부터 사용중 상태 블록을 추출

한다(단계 S141). 그 후, 이 선택기(33A)는 사용중 상태 블록들에 대응하는 블록 정보(사용중 상태 블록 정보)를 선택기(33B)로 보낸다.

[0211] 선택기(33B)는, 사용중 상태 블록 정보로부터, 교체 소스 블록 설정값에 의해 설정된 조건을 충족하는 블록 정보를 추출한다(단계 S142). 이 단계에서, "미리 결정된 값보다 더 큰 에러 수를 가지는 블록"은 교체 소스 블록 설정값으로서 설정된다.

[0212] 이후에, 선택기(33C)는 선택기(33B)에 의해 추출된 블록들로부터, 가장 작은 소거 횟수를 가지는 블록을 교체 소스 블록으로서 선택한다(단계 S143). 이 교체 소스 블록에 대응하는 교체 소스 블록 정보는 평준화부(35)에 공급된다.

[0213] 위에서 상세히 설명한 바와 같이, 본 실시형태에서는, 메모리 시스템(1)의 기록 처리 동안에 단기간 내에 재기록이 집중적으로 발생되는 블록을, 1회 데이터 기록되어 할당된 채로 장기간 동안 릴리즈되지 않는 블록으로 교체할 수 있다. 이는 짧은 소거 시간 간격에 의해 야기되는 블록의 소모를 억제하므로, NAND 플래시 메모리(10) 전체의 블록 소모를 평균화할 수 있다.

[0214] 또한, ECC 회로에 의해 산출된 복수의 에러 수를 가지는 블록을 교체 소스 블록으로서 선택한다. 따라서, 복수의 에러 수를 가지는 블록의 데이터가 재기록되므로, 리플레시 처리(NAND 플래시 메모리(10)에 저장되는 데이터를 관리하여, 에러 정정하고, NAND 플래시 메모리(10)에 다시 기록함)를 평준화 처리와 동시에 수행한다. 그 결과, 리플레시 처리의 횟수를 감소시킬 수 있다. 이는 리플레시에 기인하는 데이터 기록량을 감소시키는 효과를 얻을 수 있게 한다.

[0215] [실시형태]

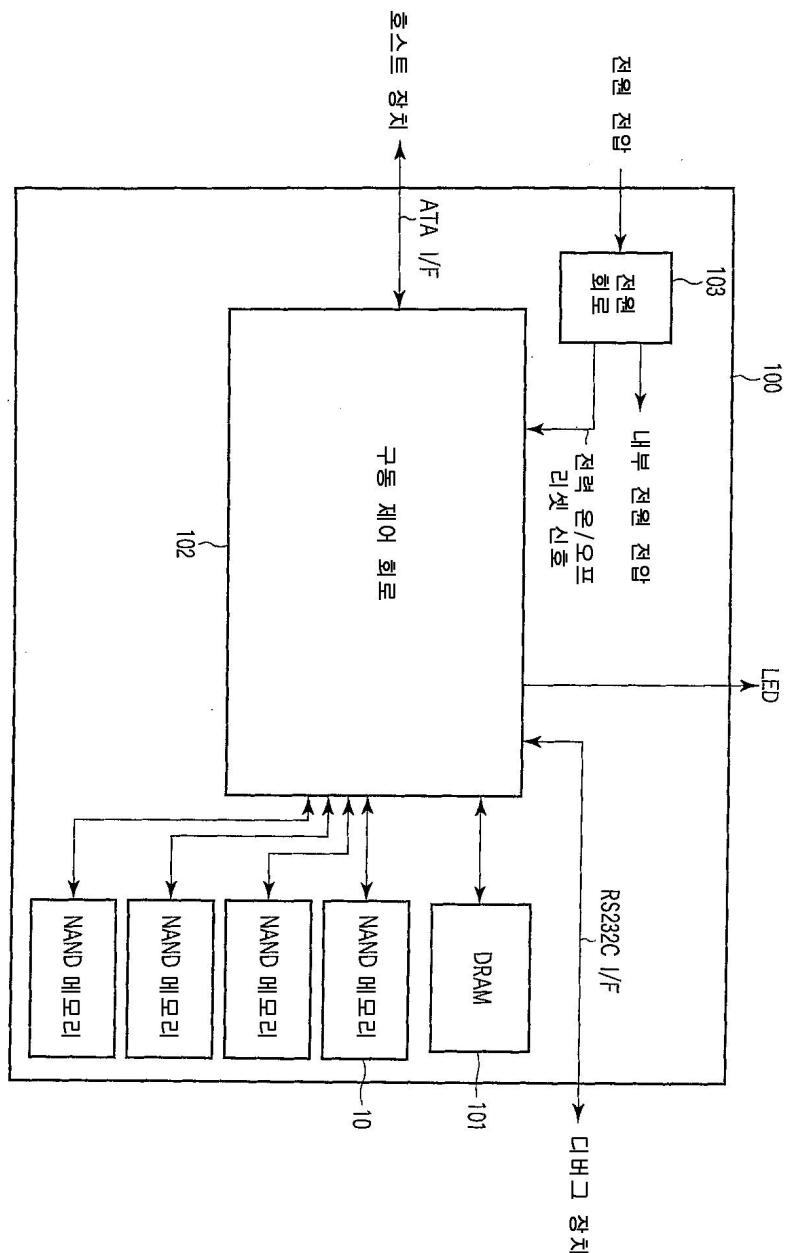

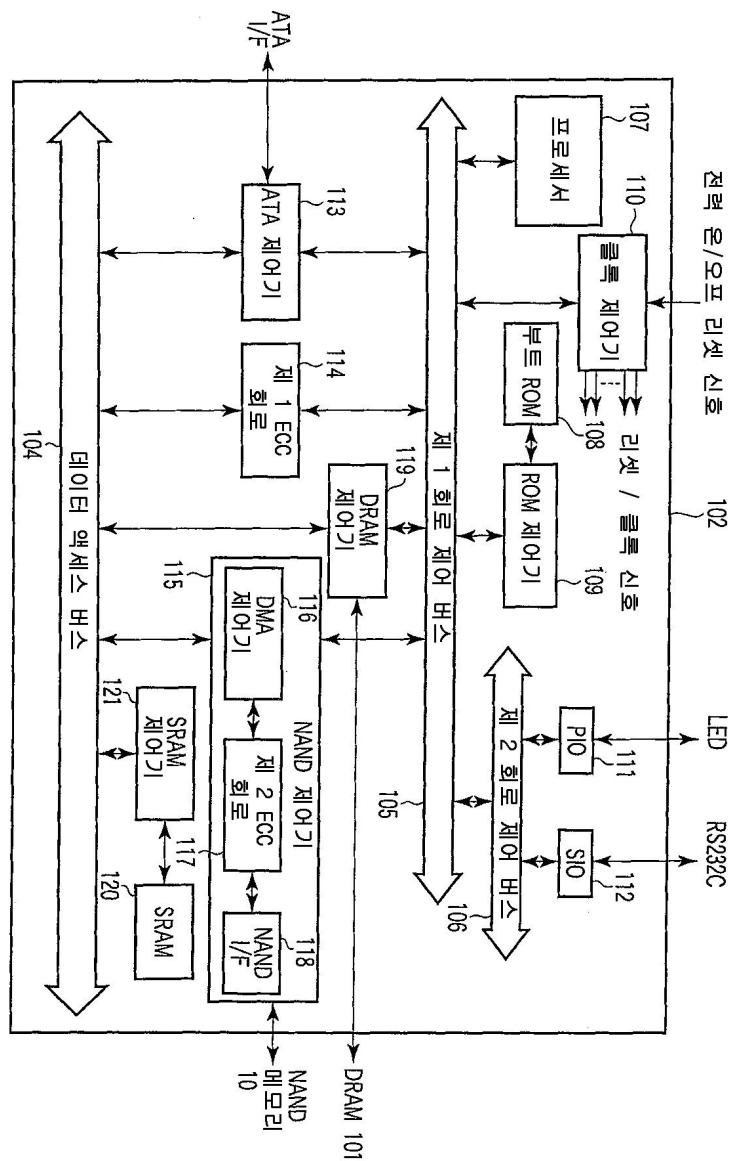

[0216] 상술된 실시형태들 각각의 메모리 시스템(1)을 고체 상태 드라이버(SSD; solid state driver)로서 구성함으로써 얻어진 실시형태를 설명한다. 도 31은 SSD(100)의 구성을 나타내는 블록도이다.

[0217] SSD(100)은, 데이터 저장용 복수의 NAND 플래시 메모리들(NAND 메모리)(10), 데이터 전송 또는 작업 영역용 DRAM(101), 상기 장치들을 제어하는 구동 제어 회로(102), 및 전원 회로(103)를 포함한다. 구동 제어 회로(102)는 SSD(100)의 외부에 제공된 상태 표시용 LED를 제어하기 위한 제어 신호를 출력한다.

[0218] SSD(100)는, ATA 인터페이스(ATA I/F)를 통하여 퍼스널 컴퓨터와 같은 호스트 장치에 데이터를 전송한다. SSD(100)는 RS-232C 인터페이스(RS232C I/F)를 통하여 디버그 장치에 데이터를 전송한다.

[0219] 전원 회로(103)는 외부 전원 전압을 공급 받아서, 이 외부 전원 전압을 이용하여 복수의 내부 전원 전압을 생성한다. 내부 전원 전압은 SSD(100)의 각 부에 공급된다. 또한, 전원 회로(103)는 외부 전원 전압의 상승 또는 하강을 감출하여, 전력 온 리셋 신호 또는 전력 오프 리셋 신호를 생성한다. 전력 온 리셋 신호 및 전력 오프 리셋 신호는 구동 제어 회로(102)에 공급된다.

[0220] 도 32는 구동 제어 회로(102)의 구성을 나타내는 블록도이다. 구동 제어 회로(102)는, 데이터 액세스 버스(104), 제 1 회로 제어 버스(105), 및 제 2 회로 제어 버스(106)를 포함한다.

[0221] 구동 제어 회로(102)의 전체를 제어하는 프로세서(107)은 제 1 회로 제어 버스(105)에 연결된다. 또한, 관리 프로그램(FW: firmware)의 부트 프로그램이 저장되는 부트 ROM(108)은 ROM 제어기(109)를 통하여 제 1 회로 제어 버스(105)에 연결된다. 또한, 전원 회로(103)로부터 전력 온 리셋 신호를 수신하여, 각 부에 리셋 신호와 클록 신호를 공급하는 클록 제어기(110)는 제 1 회로 제어 버스(105)에 연결된다.

[0222] 제 2 회로 제어 버스(106)는 제 1 회로 제어 버스(105)에 연결된다. 상태 표시용 LED에 상태 표시 신호를 공급하는 병렬 IO(PIO) 회로(111)와 RS232C 인터페이스를 제어하는 직렬 IO(SIO) 회로(112)가 제2 회로 제어 버스(106)에 연결된다.

[0223] ATA 인터페이스 제어기(ATA 제어기)(113), 제 1 에러 체크 및 정정(ECC) 회로(114), NAND 제어기(115) 및 DRAM 제어기(119)가 데이터 액세스 버스(104)와 제 1 회로 제어 버스(105) 모두에 연결된다. ATA 제어기(113)는 ATA 인터페이스를 통하여 호스트 장치에 데이터를 전송한다. 데이터 작업 영역으로서 사용되는 SRAM(120)은 SRAM 제어기(121)를 통하여 데이터 액세스 버스(104)에 연결된다.

[0224] NAND 제어기(115)는, 4개의 NAND 메모리(10)에 대하여 인터페이스 처리를 수행하는 NAND I/F(118), 제 2 ECC 회로(117), 및 NAND 메모리와 DRAM 간의 액세스 제어를 수행하는 DMA 전송 제어 DAM 제어기(116)를 포함한다.

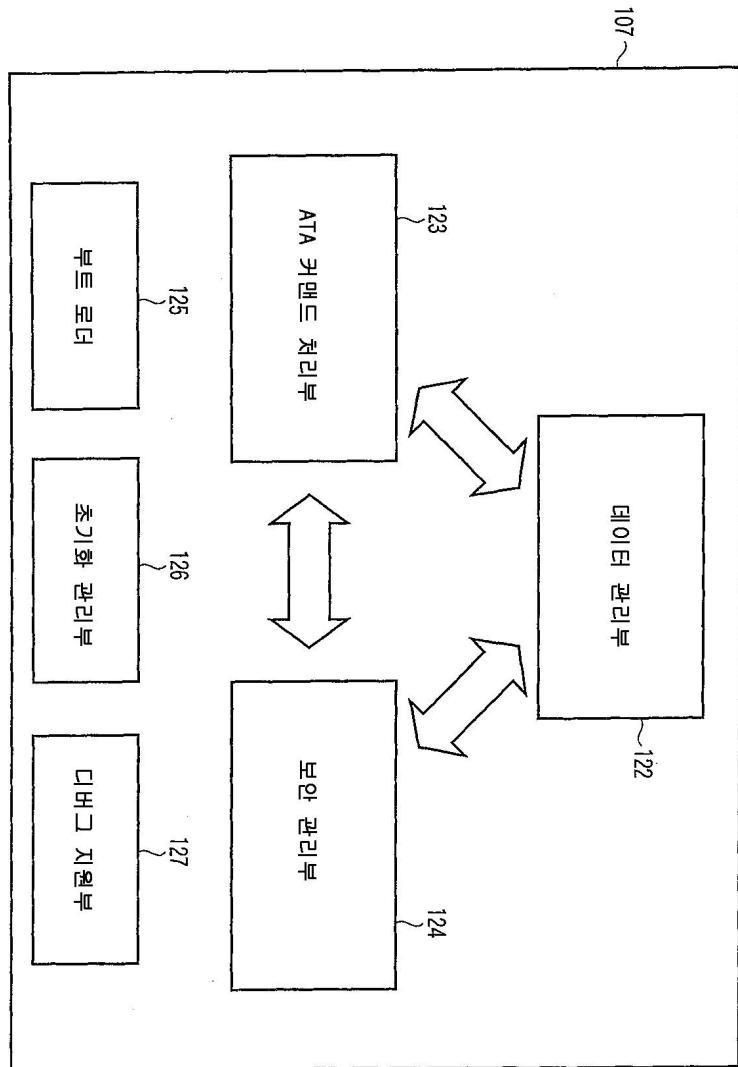

[0225] 도 33은 프로세서(107)의 구성을 나타내는 블록도이다. 프로세서(107)는, 데이터 관리부(122), ATA 커맨드 처리부(123), 보안 관리부(124), 부트 로더(125), 초기화 관리부(126), 및 디버그 지원부(127)을 포함한다.

[0226] 데이터 관리부(122)는, NAND 제어기(115)와 제 1 ECC 회로(114)를 통하여, NAND 메모리(10)와 DRAM(101) 간의 데이터 전송과 NAND 칩에 연관된 다양한 기능들을 제어한다.

[0227] ATA 커맨드 처리부(123)는, ATA 제어기(113)와 DRAM 제어기(119)를 통하여, 데이터 관리부(122)와 협동하여 데이터 전송 처리를 수행한다. 보안 관리부(124)는 데이터 관리부(122)와 ATA 커맨드 처리부(123)과 협동하여 다양한 보안 정보 항목들을 관리한다. 부트 로더(125)는, 전력 on 시에 NAND 메모리(10)로부터 SRAM(120)으로 다양한 관리 프로그램(FW)을 로딩한다.

[0228] 초기화 관리부(126)는 구동 제어 회로(102) 내의 다양한 제어기/회로를 초기화한다. 디버그 지원부(127)은 RS232C 인터페이스를 통하여 외부로부터 공급된 디버그 데이터를 처리한다.

[0229] 도 34는 상부에 SSD(100)가 탑재된 휴대용 컴퓨터(200)의 일례를 나타내는 사시도이다. 휴대용 컴퓨터(200)는 본체(201)와 디스플레이 유닛(202)을 가진다. 디스플레이 유닛(202)은 디스플레이 하우징(203)과, 디스플레이 하우징(203)에 수용된 디스플레이 장치(204)를 포함한다.

[0230] 본체(201)는, 케이싱(205), 키보드(KB)(206), 및 포인팅 장치로서 사용되는 터치 패드(207)를 포함한다. 케이싱(205)에는, 메인 회로 기판, 광 디스크장치(ODD) 유닛, 카드 슬롯, SSD(100) 등이 수용된다.

[0231] 카드 슬롯은 케이싱(205)의 주변 벽에 인접하여 제공된다. 그 주변 벽에는, 카드 슬롯과 대향하는 개구부(208)가 형성된다. 사용자는 케이싱(205)의 외부로부터 개구부(208)를 통하여 카드 슬롯에 부가적인 장치를 착탈 가능하게 삽입할 수 있다.

[0232] SSD(100)는 휴대용 컴퓨터(200)의 내부에 탑재될 수 있고, 종래의 HDD 대신에 사용되거나 또는 휴대용 컴퓨터(200)의 카드 슬롯에 삽입되어 부가적인 장치로서 사용될 수 있다.

[0233] 도 35는, SSD(100)를 이용한 휴대용 컴퓨터(200)의 시스템 구성의 일례를 나타낸다. 휴대용 컴퓨터(200)는, CPU(301), 노스 브리지(north bridge)(302), 메인 메모리(303), 비디오 제어기(304), 오디오 제어기(305), 사우스 브리지(south bridge)(309), BIOS-ROM(317), SSD(100), ODD 유닛(311), 임베딩된 제어기/키보드 제어기 IC(EC/KBC)(309), 네트워크 제어기(313) 등을 구비한다.

[0234] CPU(301)는 휴대용 컴퓨터(200)의 동작을 제어하기 위하여 사용된 프로세서이며, SSD(100)로부터 메인 메모리(303)에 로딩된 동작 시스템(OS)을 실행한다. ODD 유닛(308)이, 로딩된 광 디스크에 대하여 판독 처리 및 기록 처리 중 적어도 하나를 실행시킬 수 있을 때, CPU(301)는 처리를 실행한다.

[0235] CPU(301)는 또한, BIOS-ROM(310)에 기억된 시스템 BIOS(Basic Input Output System)을 실행한다. 시스템 BIOS는 휴대용 컴퓨터(200)의 하드웨어 구성요소를 제어하는데 사용되는 프로그램이다.

[0236] 노스 브리지(302)는 CPU(301)의 로컬 버스와 사우스 브리지(309)를 연결하는 브리지 장치이다. 노스 브리지(302)는 메인 메모리(303)에 대한 액세스를 제어하는데 사용되는 메모리 제어기를 포함된다.

[0237] 노스 브리지(302)는 AGP(accelerated graphics port) 버스에 의해 비디오 제어기(304) 및 오디오 제어기(305)와 통신하는 기능을 가진다.

[0238] 메인 메모리(303)는 일시적으로 프로그램들과 데이터를 기억하고, CPU(301)의 작업 영역으로서 기능한다. 메인 메모리(303)는, 예를 들어 DRAM으로 이루어진다.

[0239] 비디오 제어기(304)는 디스플레이 유닛(LCD)(202)를 제어하는데 사용되는 비디오 재생 제어기이다. 디스플레이 유닛(202)은 휴대용 컴퓨터(200)의 디스플레이 모니터로서 사용된다.

[0240] 오디오 제어기(305)는 휴대용 컴퓨터(200)의 스피커(311)를 제어하는데 사용되는 오디오 재생 제어기이다.

[0241] 사우스 브리지(306)는 LPC(Low Pin Count) 버스(314) 상의 장치들과, PCI(Peripheral Component Interconnect) 버스(315) 상의 장치들을 제어한다. 사우스 브리지(309)는 또한, ATA 인터페이스를 통하여 SSD(100)를 제어한다. SSD(100)는 다양한 종류의 소프트웨어와 데이터를 기억하는데 사용되는 기억 장치이다.

[0242] 휴대용 컴퓨터(200)는 섹터 단위로 SSD(100)에 액세스한다. 기록 커맨드, 판독 커맨드, 플래시 커맨드 등을, ATA 인터페이스를 통하여 SSD(100)에 공급한다.

[0243] 사우스 브리지(309)는 BIOS-ROM(310)과 ODD 유닛(311)으로의 액세스를 제어하는 기능을 가진다. EC/KBC(312)는, 전력 관리를 위한 임베딩된 제어기와, 키보드(KB)(206)와 터치 패드(207)를 제어하기 위한 키보드 제어기가 통합되는 1 칩 마이크로컴퓨터이다.

[0244] EC/KBC(309)는 사용자의 전력 버튼(312)의 동작에 따라서 휴대용 컴퓨터(200)를 온(on) 또는 오프(off)하는 기능을 가진다. 네트워크 제어기(313)는, 인터넷과 같은 외부 네트워크와 통신하는 통신 장치이다.

[0245] 상술된 실시형태의 메모리 시스템(1)은 SSD로 제한되지 않으며, SD(상표) 카드로 대표되는 메모리 카드로서 구성될 수 있다. 메모리 시스템(1)이 메모리 카드로 구성되는 경우, 메모리 시스템(1)은, 휴대용 컴퓨터 뿐만 아니라 휴대 전화, PDS, 디지털 스틸 카메라, 및 디지털 비디오 카메라와 같은 다른 다양한 전자 장치들에 적용될 수 있다.

[0246] 부가적인 이점 및 변경이 당업자에게 쉽게 발생할 수 있다. 따라서, 넓은 양태에서의 본 발명은 여기서 도시되고 기술된 특정 세부사항 및 대표적인 실시형태들로 제한되지 않는다. 따라서, 첨부된 청구범위 및 그 등가물에 의해 규정된 바와 같이 일반적인 발명의 개념의 사상 또는 범위를 벗어나지 않고 다양한 변경이 행해질 수도 있다.

### 도면의 간단한 설명

[0009] 도 1은 본 발명의 제 1 실시형태에 따른 메모리 시스템(1)을 포함하는 컴퓨터 시스템이 일례를 나타내는 개략도이다.

[0010] 도 2는 제 1 실시형태에 따른 메모리 시스템(1)의 구성을 나타내는 개략도이다.

[0011] 도 3a는 NAND 플래시 메모리에 포함되는 블록의 배열을 나타내는 회로도이다.

[0012] 도 3b는 4 레벨 데이터 기록 시스템에서 획득되는 임계값 분포의 일례를 나타내는 도면이다.

[0013] 도 4는 NAND 제어기(11)의 배열의 일례를 설명하기 위한 블록도이다.

[0014] 도 5는 블록 제어기(30) 및 소거 시간 측정부(31)의 배열을 나타내는 블록도이다.

[0015] 도 6은 NAND 제어기(11)에 의해 수행되는 일련의 기록 동작을 나타내는 흐름도이다.

[0016] 도 7은 NAND 제어기(11)에 의해 수행되는 블록 릴리즈 처리를 나타내는 흐름도이다.

[0017] 도 8은 할당 블록 선택기(32)의 배열을 나타내는 블록도이다.

[0018] 도 9는 할당 블록 선택기(32)에 의해 수행되는 할당 블록 선택 처리를 나타내는 흐름도이다.

[0019] 도 10은 NAND 제어기(11)에 의해 수행되는 블록 할당 처리를 나타내는 흐름도이다.

[0020] 도 11은 NAND 제어기(11)에 의해 수행되는 블록 소거 처리를 나타내는 흐름도이다.

[0021] 도 12는 단기간 재기록 검출기(34)의 배열을 나타내는 블록도이다.

[0022] 도 13은 단기간 재기록 검출기(34)에 의해 수행되는 단기간 재기록 검출 처리를 나타내는 흐름도이다.

[0023] 도 14는 단기간 재기록 검출 처리의 실용예를 설명하기 위한 도면이다.

[0024] 도 15는 평준화부(35)의 배열을 나타내는 블록도이다.

[0025] 도 16은 NAND 제어기(11)에 의해 수행되는 평준화 처리를 나타내는 흐름도이다.

[0026] 도 17은 교체 소스 블록 선택기(11)의 배열을 나타내는 블록도이다.

[0027] 도 18은 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리를 나타내는 흐름도이다.

[0028] 도 19는 본 발명의 제 2 실시형태에 따른 할당 블록 선택기(32)의 배열을 나타내는 블록도이다.

[0029] 도 20은 제 2 실시형태에 따른 할당 블록 선택기(32)에 의해 수행되는 할당 블록 선택 처리를 나타내는 흐름도이다.

[0030] 도 21은 본 발명의 제 3 실시형태에 따른 교체 소스 블록 선택기(33)의 배열을 나타내는 블록도이다.

[0031] 도 22는 제 3 실시형태에 따른 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스 블록 선택 처리를 나타내

는 흐름도이다.

[0032] 도 23은 본 발명의 제 4 실시형태에 따른 단기간 재기록 검출기(34)의 배열을 나타내는 블록도이다.

[0033] 도 24는 단기간 재기록 검출기(34)에 의해 수행되는 단기간 재기록 검출 처리를 나타내는 흐름도이다.

[0034] 도 25는 도 24에 후속하는 단기간 재기록 검출 처리를 나타내는 흐름도이다.

[0035] 도 26은 단기간 재기록 검출 처리의 실용예를 설명하기 위한 도면이다.

[0036] 도 27은 본 발명의 제 5 실시형태에 따른 NAND 제어기(11)의 배열의 일례를 나타내는 블록도이다.

[0037] 도 28은 블록 제어기(30)의 배열을 나타내는 블록도이다.

[0038] 도 29는 NAND 제어기(11)에 의해 수행되는 관독 동작을 나타내는 흐름도이다.

[0039] 도 30은 교체 소스 블록 선택기(33)에 의해 수행되는 교체 소스블록 선택 처리를 나타내는 흐름도이다.

[0040] 도 31은 실시형태에 따른 SSD(100)의 구성을 나타내는 블록도이다.

[0041] 도 32는 구동 제어 회로(102)의 구성을 나타내는 블록도이다.

[0042] 도 33은 프로세서(107)의 구성을 나타내는 블록도이다.

[0043] 도 34는 상부에 SSD(100)가 탑재된 휴대용 컴퓨터(200)의 일례를 나타내는 사시도이다.

[0044] 도 35는 SSD(100)를 이용한 휴대용 컴퓨터(200)의 시스템 구성의 일례를 나타내는 블록도이다.

도면

도면1

도면2

도면3a

도면3b

도면4

도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

도면11

도면12

## 도면13

## 도면14

도면15

도면16

도면17

## 도면18

## 도면19

## 도면20

## 도면21

## 도면22

도면23

## 도면24

## 도면25

## 도면26

도면27

## 도면28

## 도면29

## 도면30

도면31

### 도면32

도면33

도면34

도면35