(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5066702号

(P5066702)

(45) 発行日 平成24年11月7日(2012.11.7)

(24) 登録日 平成24年8月24日(2012.8.24)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| GO6F 13/38 | (2006.01) | GO6F 13/38 | 350  |

| GO6F 12/00 | (2006.01) | GO6F 12/00 | 545M |

| GO6F 13/10 | (2006.01) | GO6F 13/10 | 340B |

請求項の数 35 (全 50 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2002-531029 (P2002-531029)  |

| (86) (22) 出願日 | 平成13年9月24日 (2001.9.24)        |

| (65) 公表番号     | 特表2004-510252 (P2004-510252A) |

| (43) 公表日      | 平成16年4月2日 (2004.4.2)          |

| (86) 國際出願番号   | PCT/US2001/030150             |

| (87) 國際公開番号   | W02002/027519                 |

| (87) 國際公開日    | 平成14年4月4日 (2002.4.4)          |

| 審査請求日         | 平成20年9月24日 (2008.9.24)        |

| (31) 優先権主張番号  | 09/675,700                    |

| (32) 優先日      | 平成12年9月29日 (2000.9.29)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 09/675,484                    |

| (32) 優先日      | 平成12年9月29日 (2000.9.29)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                            |

|-----------|--------------------------------------------------------------------------------------------|

| (73) 特許権者 | 501082978<br>アラクリテック・インコーポレイテッド<br>アメリカ合衆国、カリフォルニア州・95<br>012, サン・ノゼ、イースト・ギッシュ<br>・ロード・234 |

| (74) 代理人  | 100098062<br>弁理士 梅田 明彦                                                                     |

| (72) 発明者  | スター, ダリル, ディー<br>アメリカ合衆国、カリフォルニア州・95<br>035, ミルピタス, フォルソム・コート<br>・446                      |

| (72) 発明者  | フィルブリック, クライヴ, エム<br>アメリカ合衆国、カリフォルニア州・95<br>125, サン・ノゼ, ロイコット・ウェイ<br>・1170                 |

最終頁に続く

(54) 【発明の名称】 インテリジェントネットワークストレージインターフェースシステム及びデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

ネットワークと記憶装置間で情報を転送するための装置であって、

ファイルシステムを動作させるCPUと、ホストメモリバスにより前記CPUに接続されたホストメモリとを有するホストコンピュータと、

前記ホストコンピュータと前記ネットワークと前記記憶装置とに接続され、前記ネットワークと記憶装置間で通信されるデータを格納するのに適したインターフェースファイルキャッシュを含むインターフェースメモリを有するインターフェース装置とを備え、

前記インターフェースファイルキャッシュが前記ファイルシステムにより制御され、

前記ホストコンピュータが、通信制御ブロックを作成しつつ前記通信制御ブロックを前記インターフェース装置へ送るように構成され、

前記インターフェース装置が、前記通信制御ブロックに従って前記ネットワークと前記ファイルキャッシュ間で前記データを通信するように構成されていることを特徴とする装置。

。

## 【請求項 2】

前記ホストコンピュータが、通信制御ブロックを作成しつつ前記通信制御ブロックを前記インターフェース装置へ送るように構成され、かつ

前記インターフェース装置が、前記通信制御ブロックに従って前記記憶装置を前記ファイルキャッシュ間で前記データを通信するように構成されていることを特徴とする請求項1に記載の装置。

**【請求項 3】**

前記データが前記ホストコンピュータに入力しないことを特徴とする請求項 1 に記載の装置。

**【請求項 4】**

前記データが、前記ネットワークと前記インターフェース装置間をファイル形式で通信され、かつ

前記データが前記インターフェース装置と前記記憶装置間をブロック形式で通信されることを特徴とする請求項 1 に記載の装置。

**【請求項 5】**

前記データがトランスポートレイヤヘッダを含むヘッダに添付され、かつ前記インターフェース装置が前記トランスポートレイヤヘッダを処理するように構成されたメカニズムを有することを特徴とする請求項 1 に記載の装置。 10

**【請求項 6】**

前記インターフェース装置が、前記ホストを有する第 1 パスを介して、または前記ホストを有しない第 2 パスを介して前記ネットワークと前記記憶装置間で前記データを転送するかどうかを選択するように構成されたメカニズムを有することを特徴とする請求項 1 に記載の装置。

**【請求項 7】**

前記インターフェース装置が、前記記憶装置に接続された S C S I コントローラを有することを特徴とする請求項 1 に記載の装置。 20

**【請求項 8】**

前記インターフェース装置が、前記記憶装置に接続されたファイバチャネルコントローラを有することを特徴とする請求項 1 に記載の装置。

**【請求項 9】**

前記インターフェース装置が、前記記憶装置に接続された R A I D コントローラを有することを特徴とする請求項 1 に記載の装置。

**【請求項 10】**

前記インターフェース装置が、前記ネットワーク及び前記記憶装置の少なくとも一方に接続されたネットワークポートを有することを特徴とする請求項 1 に記載の装置。

**【請求項 11】**

前記ホストコンピュータ、前記ネットワーク及び第 2 記憶装置に接続された第 2 インターフェース装置を更に備え、

前記第 2 インターフェース装置が、前記ネットワークと前記第 2 記憶装置間で通信されるデータを格納するのに適した第 2 インターフェースファイルキャッシュを含む第 2 インターフェースメモリを有し、

前記第 2 インターフェースファイルキャッシュが前記ファイルシステムにより制御されることを特徴とする請求項 1 に記載の装置。

**【請求項 12】**

ネットワークと記憶装置間で情報を転送するための装置であって、

ホストメモリバスによりホストメモリに接続されたプロセッサを有し、前記ホストメモリが、ネットワーク接続を定義する通信制御ブロックを作成するように前記プロセッサにより動作可能なプロトコルスタックを有するホストコンピュータと、 40

前記ホストコンピュータに接続されかつ前記ネットワークと前記記憶装置間に結合されたインターフェース装置とを備え、前記インターフェース装置が、前記通信制御ブロックを格納するのに適したインターフェースメモリと、データを前記通信制御ブロックと関連付け、それにより前記データが前記ホストコンピュータに出会うことなく前記ネットワークと前記記憶装置間で通信されるように構成されたメカニズムとを有することを特徴とする装置。

**【請求項 13】**

前記ホストコンピュータがファイルシステムを有し、かつ前記インターフェースメモリが 50

前記データを格納するのに適したファイルキャッシュを有し、前記ファイルシステムが前記データの前記ファイルキャッシュへの格納を管理することを特徴とする請求項1 2に記載の装置。

【請求項 1 4】

前記データが、トランスポートレイヤヘッダを含む少なくとも1つのパケットで前記ネットワーク上を移動し、かつ前記インターフェース装置が前記ヘッダを処理するための回路を有することを特徴とする請求項1 2に記載の装置。

【請求項 1 5】

前記トランスポートレイヤヘッダがTCPヘッダであることを特徴とする請求項1 4に記載の装置。

10

【請求項 1 6】

前記トランスポートレイヤヘッダがUDPヘッダであることを特徴とする請求項1 4に記載の装置。

【請求項 1 7】

前記インターフェース装置が入力／出力バスにより前記ホストコンピュータに接続され、かつ前記通信コントロールブロックが前記入力／出力バス上で前記インターフェース装置と前記ホストコンピュータ間を移動することを特徴とする請求項1 2に記載の装置。

【請求項 1 8】

前記インターフェース装置が更に、前記記憶装置に接続されたSCSIコントローラを有することを特徴とする請求項1 2に記載の装置。

20

【請求項 1 9】

前記インターフェース装置が更に、前記記憶装置に接続されたファイバチャネルコントローラを有することを特徴とする請求項1 2に記載の装置。

【請求項 2 0】

前記インターフェース装置が更に、前記記憶装置に接続されたRAIDコントローラを有することを特徴とする請求項1 2に記載の装置。

【請求項 2 1】

前記インターフェース装置が前記記憶装置と、少なくとも1つのネットワークポートにより前記ネットワークに接続されていることを特徴とする請求項1 2に記載の装置。

【請求項 2 2】

30

前記通信制御ブロックに対応する先のまたは後のデータが前記ホストコンピュータを通過することを特徴とする請求項1 2に記載の装置。

【請求項 2 3】

前記ホストコンピュータが、前記インターフェース装置によってアクセス可能なUDPソケットを指定するように構成され、かつ前記インターフェース装置が、前記UDPソケットに従って前記ネットワークと前記ファイルキャッシュ間で前記データを通信するように構成されていることを特徴とする請求項1 2に記載の装置。

【請求項 2 4】

ネットワークと記憶装置間で情報を転送するための装置であって、

ファイルシステムを動作させるCPUと、ホストバスにより前記CPUに接続されたホストメモリとを有し、前記ファイルシステムにより情報がファイルの階層構造として論理的に編成されるホストコンピュータと、

40

前記ホストコンピュータ、前記ネットワーク及び前記記憶装置に接続され、前記ファイルシステムの制御下で前記ネットワークと前記記憶装置間で通信されるデータを格納するのに適したインターフェースファイルキャッシュを含むインターフェスマモリを有し、前記ファイルシステムによって前記ファイルキャッシュ内の情報が前記ファイルの階層構造の一部として論理的に編成されたようにしたインターフェース装置とを備え、

前記ホストコンピュータが、前記インターフェース装置によりアクセス可能なUDPソケットを指定するように構成され、かつ、

前記インターフェース装置が、前記UDPソケットに従って前記ネットワークと前記ファ

50

イルキャッシュ間で前記データを通信するように構成されていることを特徴とする装置。

【請求項 25】

前記ホストコンピュータが、前記インターフェース装置によりアクセス可能なアプリケーションレイヤヘッダを作成するように構成され、かつ前記インターフェース装置が前記アプリケーションレイヤヘッダを前記データにプリペンドするように構成されていることを特徴とする請求項24に記載の装置。

【請求項 26】

前記ホストコンピュータが、前記インターフェース装置によりアクセス可能なリアルタイムトランSPORTプロトコルヘッダを作成するように構成され、かつ前記インターフェース装置が前記リアルタイムトランSPORTプロトコルヘッダを前記データにプリペンドするように構成されていることを特徴とする請求項24に記載の装置。

10

【請求項 27】

前記データが関連するUDPヘッダと共に格納され、かつ前記インターフェース装置が前記UDPヘッダを処理するように構成されたメカニズムを有することを特徴とする請求項24に記載の装置。

【請求項 28】

前記データが前記インターフェース装置によりUDPヘッダでプリペンドされてUDPデータグラムを作成し、かつ前記インターフェース装置が前記データグラムを複数のフラグメントに分割するように構成されたメカニズムを有することを特徴とする請求項24に記載の装置。

20

【請求項 29】

前記データが複数のフラグメントに配置され、かつ前記インターフェース装置が、UDPヘッダに対応する前記フラグメントを連結するように構成されたメカニズムを有することを特徴とする請求項24に記載の装置。

【請求項 30】

前記データが前記ホストコンピュータに入力しないことを特徴とする請求項24に記載の装置。

【請求項 31】

前記データが音声データを含むことを特徴とする請求項24に記載の装置。

【請求項 32】

30

前記データが映像データを含むことを特徴とする請求項24に記載の装置。

【請求項 33】

前記データがリアルタイム通信の一部であることを特徴とする請求項24に記載の装置。

【請求項 34】

ネットワークと記憶装置間で情報を転送するための装置であって、

ファイルシステムを動作させるCPUと、メモリバスにより前記CPUに接続されたメモリとを有するコンピュータと、

前記コンピュータ、前記ネットワーク及び前記記憶装置に接続され、前記ネットワークと記憶装置間で通信されるデータを格納するインターフェースファイルキャッシュを含むインターフェースメモリを有するインターフェース装置とを備え、

40

前記インターフェースファイルキャッシュが前記ファイルシステムにより制御され、

前記データが前記インターフェース装置と前記記憶装置間での前記データの転送の際にISCSIヘッダに添付され、

前記コンピュータが、通信制御ブロックを作成し、かつ前記通信制御ブロックを前記インターフェース装置へ送るように構成され、

前記インターフェース装置が、前記通信制御ブロックに従って前記ネットワークと前記ファイルキャッシュ間で前記データを通信するように構成されていることを特徴とする装置。

【請求項 35】

50

前記インターフェース装置がギガビットイーサネットネットワークにより前記記憶装置に接続されていることを特徴とする請求項3 4に記載の装置。

【発明の詳細な説明】

【0001】

【技術分野】

本発明は、ネットワーク通信及びストレージに関する。

【0002】

【背景技術】

過去数10年以上に亘って、ネットワークコンピューティングの利益及び進歩がコンピュータネットワークの著しい成長を促しており、これがより一層の進歩、成長及び利益に拍車をかけている。しかしながら、この成長と共に従来のネットワークデバイスを用いる上で混乱及び障害が起こっている。例えば、ネットワークに接続されたコンピュータのCPUが、そのネットワーク通信を処理するのに使用する時間の部分が増加して、他の作業に使うことができる時間が少なくなっている場合がある。特に、ネットワークとディスクドライブのようなコンピュータの記憶装置との間でファイルデータを移動させることへの要求が加速度的に増えている。従来、このようなデータはネットワーク上での移動のためにパケットに分割され、各パケットは受信コンピュータのCPUによって一度に1つのレイヤが処理される制御情報のレイヤにカプセル化される。CPUの速度が一定の割合で増加しているにも拘わらず、このファイル転送のようなネットワークメッセージのプロトコル処理は、市販の最速CPUの利用可能な処理能力の大部分を消費する場合がある。

10

【0003】

このような状況は、その主な機能がネットワーク上でファイルデータを転送することによってその接続型ディスクまたはテープドライブ上でファイルを格納しかつ検索することであるネットワークファイルサーバにとって、より一層挑戦的なものになる場合がある。ネットワーク及びデータベースが成長するにつれて、そのようなサーバに格納される情報の量が爆発的に増加し、そのようなサーバ接続型記憶装置の限界を露呈している。ホストCPUにより処理されるプロトコルの上述した問題に加えて、従来の小型コンピュータシステムインターフェース(SCSI)インターフェースのようなパラレルデータチャネルの限界が、ストレージの必要性が増加するにつれて明らかになっている。例えば、パラレルSCSIインターフェースは、サーバに接続することができるストレージデバイスの数及びストレージデバイスとサーバ間の距離を制限する。

20

【0004】

Tom Clark著の書籍「Designing Storage Area Networks」(著作権1999年)に記載されるように、サーバ接続型のパラレルSCSIストレージデバイスの限界に対する1つの解決策は、ネットワークサーバの正面にある既存のローカルエリアネットワーク(LAN)に別のファイルサーバを接続することを必要とする。このネットワーク接続型ストレージ(NAS)によって、ネットワーク上の他のサーバ及びクライアントからNASファイルサーバへのアクセスが可能になるが、元のネットワークサーバに専用の記憶容量が増加するものではない。逆に、NASは、元のネットワークサーバが様々なNASファイルサーバと通信する必要があることから、そのサーバが必要とするプロトコル処理が増える場合がある。更に、NASファイルサーバのそれぞれが、次に、プロトコル処理の負担及びストレージインターフェースの限界を被ることになる。

30

【0005】

ストレージエリアネットワーキング(SAN)が、サーバの背後に接続されたストレージデバイスのネットワークでデイジーチェーンにより接続されたSCSIストレージデバイスを置き換えることによって、ネットワーク上でのファイル転送及び記憶に対する必要性の増加に対する別の解決策を提供している。イーサネットまたはファーストイーサネットのような従来のネットワーク規格の代わりに、SANは、ファイバチャネル(FC)と呼ばれる新しいネットワーキング規格を使用する。しかしながら、それが比較的最近の導入であるため、多くの市販されているFCデバイスは互いに互換性がない。また、FCネット

40

50

トワークはサーバと記憶装置のようなネットワーク上の2点間の通信のためにバンド幅を専用にすることがあり、前記2点が通信していない時はバンド幅が無駄になる。

【0006】

今や公知のNAS及びSANは、転送されかつ格納されるデータの形によって区別することができる。NASデバイスは一般にデータファイルを別のファイルサーバまたはクライアントへ及びそこから転送するのに対し、SAN上ではデバイスレベルのデータのブロックが転送される。このため、NASデバイスは通常記憶のためにファイルとブロック間で変換するためのファイルシステムを有するが、SANはそのようなファイルシステムを持たないストレージデバイスを備えることができる。

【0007】

これに代えて、NASファイルサーバは、イーサネットSANの一部分として、サーバに専用のイーサネットベースのネットワークに接続することができる。Marc Farleyは、その書籍「Building Storage Networks」(著作権2000年)において、イーサネット上でストレージプロトコルを実行することが可能であり、それによってファイルチャネルの非互換性の問題を解消できると述べている。しかしながら、SANのようなネットワークトポジを使用することによってサーバに接続されたストレージデバイスの数の増加によって、そのサーバが実行しなければならないプロトコル処理の量が増加する。上述したように、このようなプロトコルの処理は既に最新型のサーバを乱用している。

【0008】

ファイル転送のようなネットワークメッセージの従来の処理の一例は、ネットワークデータの格納を遅くするいくつかの処理ステップを説明している。ネットワークインターフェースカード(NIC)は一般に、ホストがネットワークにアクセスできるようにする媒体アクセスコントロール(MAC)機能を提供することに加えて、ホストとネットワーク間の物理的接続を提供する。ホストに送られたネットワークメッセージのパケットがNICに到着すると、そのパケットのMACレイヤヘッダは処理されかつ前記パケットはNICにおいて巡回冗長検査(CRC)を受ける。次に前記パケットは、周辺装置相互接続(PCIE)のような入力/出力(I/O)バスを通ってホストに送られかつホストメモリに格納される。次に、CPUが、プロトコルスタックからの命令を実行することによって、前記パケットのヘッダレイヤのそれぞれを順に処理する。これには、最初に前記パケットを格納するためにホストメモリバスを通る移動と、次に各ヘッダレイヤを順に処理するためにホストメモリバスを通る移動とが必要である。そのパケットの全ヘッダレイヤが処理された後、該パケットからのペイロードデータが、前記メッセージの他の同様に処理されたペイロードパケットと共にファイルキャッシュ内にグループ分けされる。前記データは、ディスク上に格納するためのファイルブロックとして前記ファイルシステムに従ってCPUにより再アセンブリされる。全パケットが処理されかつメッセージがファイルキャッシュにファイルブロックとして再アセンブリされた後、前記ファイルは、それぞれに数個のペイロードパケットから構築することができるデータブロックにして、ホストメモリバス及びI/Oバス上をホストストレージヘディスク上で長期間格納するために、一般にI/OバスにブリッジされたSCSIバスを介して送られる。

【0009】

これに代えて、SAN上でファイルを格納するために、ファイルキャッシュの再アセンブリされたファイルがブロックでホストメモリバス及びI/Oバス上を前記SAN用に構成されたI/Oコントローラへ送られる。SANがFCネットワークである場合には、ファイルチャネルプロトコル(FCP)に従ってファイルブロックをSAN上のストレージデバイスに送ることができる特別のFCコントローラが設けられる。ファイルがNASデバイス上で格納されることになっている場合には、該ファイルはNASデバイスへ送りまたは再送することができ、これがパケットを上述したとほぼ同様に処理するが、NASデバイスのCPU、プロトコルスタック及びファイルシステムを使用し、NASデバイスの記憶装置に前記ファイルのブロックを格納する。

【0010】

10

20

30

40

50

このように、ホストに接続されたNASまたはSANでの格納のためにネットワークから該ホストに送られるファイルは、一般に前記ファイルの各メッセージパケットについてI/Oバスを通る2つの移動が必要である。更に、各パケットのヘッダレイヤの制御情報は、一時的に格納され、一度に1つのレイヤが処理されかつ次にI/Oバスへ送り戻されるので、ホストメモリバスを繰り返し通過することになる。このようなファイルをクライアントからのリクエストに応答してSAN上のストレージから検索することはまた、従来ホストCPU及びファイルシステムによる相当量の処理を必要とする。

#### 【0011】

##### 【発明の開示】

データ転送の制御をホストに残しつつ、ネットワークと記憶装置間のデータ転送を加速するためのハードウェア及び処理メカニズムを提供する、ローカルホストのためのインテリジェントネットワークインタフェースカード(INIC)のようなインタフェース装置が開示されている。このインタフェース装置は、ネットワークパケットヘッダを処理するためのハードウェア回路を有し、ネットワークと記憶装置間でのデータ転送のためのホストにより設定された専用の高速バスを使用することができる。ホストCPU及びプロトコルスタックにより、高速バス上でのデータ転送のためのプロトコル処理が回避され、ネットワーク及びストレージサブシステムの多くの要求からホストバスのバンド幅を解放する。独立ディスクの冗長アレイ(RAID)または複数のドライブからなる他の構成を有することができる記憶装置が、SCSIのようなパラレルチャネルによって、またはイーサネットもしくはファイバチャネルのようなシリアルチャネルによってインタフェース装置に接続することができ、かつインタフェース装置はPCIバスのようなI/Oバスによってローカルホストに接続することができる。追加の記憶装置を、SCSIのようなパラレルインタフェースによりローカルホストに接続することができる。

10

#### 【0012】

ファイルキャッシュがホストをバイパスすることができるデータを格納するためにインタフェース装置上に設けられ、インタフェース装置のファイルキャッシュにおけるデータの編成が、ホスト上のファイルシステムによって制御される。この構成によって、リモートホストと記憶装置間のデータ転送が、データがインタフェース装置とI/Oバス上のローカルホストの間を通過することなく、インタフェース装置の高速バス上で処理することができる。また、従来の通信プロトコル処理と対照的に、高速バスデータのための制御信号がホストメモリバス上を繰り返し移動して一時的に格納され、かつ次にホストCPUにより一度に1レイヤが処理されるということがない。従って、ホストは、ホスト制御型記憶装置上のファイル読出しありは書き込みのためのデータトラフィックの大部分に関与することから解放することができる。

20

#### 【0013】

追加のインタフェース装置をI/Oバスを介してホストに接続することができ、追加の各インタフェース装置はホストファイルシステムにより制御されるファイルキャッシュを有し、かつ追加のネットワーク接続を提供しありまたは追加の記憶装置に接続される。複数のインタフェース装置が単一のホストに接続されることによって、該ホストは複数のストレージネットワークを制御することができ、ホスト制御型ネットワークとの間のデータフローの大部分がホストプロトコル処理、I/Oバスを通る移動、ホストバスを通る移動、ホストメモリへの格納をバイパスする。ある実施例では、記憶装置がそのようなインタフェース装置にギガビットイーサネットネットワークにより接続することができ、前記欠陥なしでファイバチャネルの速度及びバンド幅を提供し、かつイーサネットベースのネットワークの大規模導入ベース及び互換性の利益が得られる。

30

#### 【0014】

##### 【発明を実施するための最良の形態】

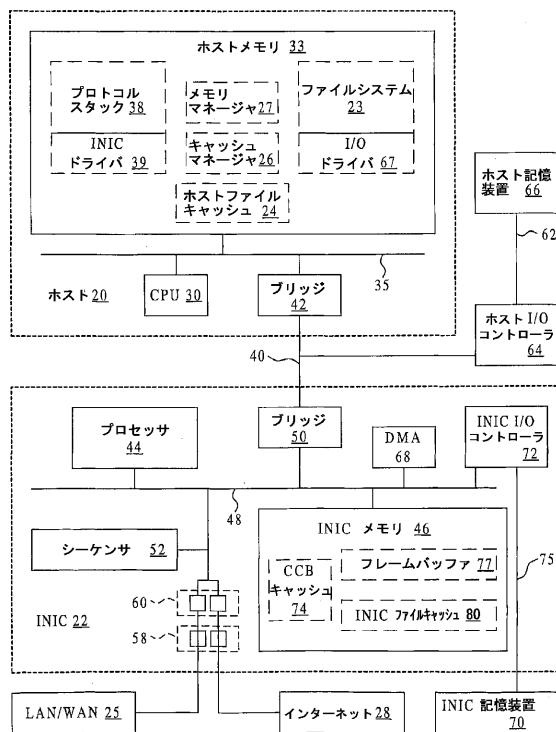

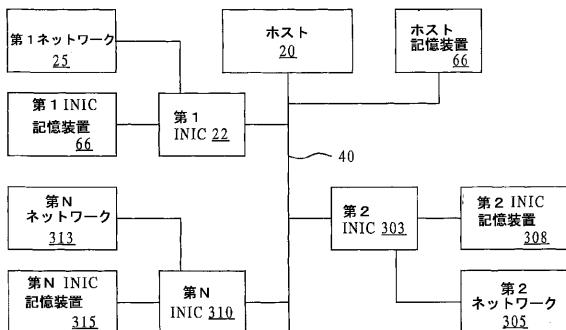

本発明によるネットワークデータ通信システムの概要が図1に示されている。ホストコンピュータ20が、ローカルまたはワイドエリアネットワーク25もしくはインターネット28のようなネットワークに接続するための1つまたは複数のポートを有することができ

40

50

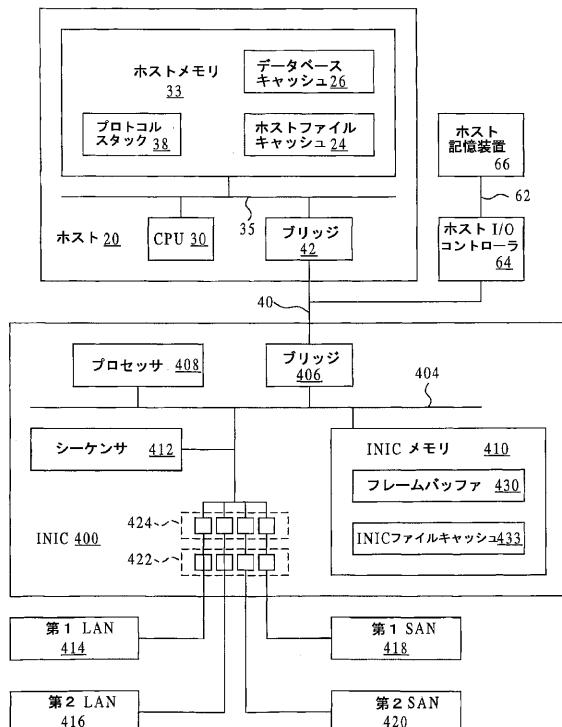

るインテリジェントネットワークインターフェースカード( I N I C ) 2 2 のようなインターフェース装置に接続されている。ホスト 2 0 は、ホストバス 3 5 によりホストメモリ 3 3 に接続された中央処理装置( C P U ) 3 0 のようなプロセッサを有し、図示しないオペレーティングシステムが、ファイルシステム 2 3 を含む様々なタスク及び装置を監督するためにメモリ 3 3 に存在する。同様にホストメモリ 3 3 に格納されているのは、ネットワーク通信を処理するためのインストラクションのプロトコルスタック 3 8 、及び I N I C 2 2 とプロトコルスタック 3 8 間を通信する I N I C ドライバ 3 9 である。キャッシュマネージャ 2 6 は、ファイルシステム 2 3 及び W i n d o w s ( 登録商標 ) N T または 2 0 0 0 の仮想メモリマネージャのような任意のメモリマネージャ 2 7 の制御下で動作して、ファイルストリームと称されるファイル部分をホストファイルキャッシュ 2 4 上に格納しあつ検索する。

#### 【 0 0 1 5 】

ホスト 2 0 は、 P C I バスのような I / O バス 4 0 によって I N I C 2 2 に接続され、これはホスト I / O ブリッジ 4 2 によりホストバス 3 5 に結合されている。前記 I N I C は、 I N I C バス 4 8 により相互に接続されたインターフェースプロセッサ 4 4 及びメモリ 4 6 を有する。 I N I C バス 4 8 は、 I N I C ・ I / O ブリッジ 5 0 を有する I / O バス 4 0 に接続されている。同様に I N I C バス 4 8 に接続されているのは、ネットワークメッセージの上位レイヤプロセッシングを行うハードウェアシーケンサ 5 2 のセット即ち集合である。 L A N / W A N 2 5 及びインターネット 2 8 への物理的接続は、従来の物理的レイヤハードウェア P H Y 5 8 によって提供される。各 P H Y 5 8 装置は、媒体アクセスコントロール( M A C ) 6 0 の対応する装置に接続され、各 M A C 装置によって、前記 I N I C と前記ネットワークの 1 つとの間に従来型のデータリンクレイヤ接続が提供される。

#### 【 0 0 1 6 】

ディスクドライブまたはディスクドライブの集合と対応するコントローラのようなホスト記憶装置 6 6 が、 S C S I アダプタのような従来の I / O コントローラ 6 4 により I / O バス 4 0 と接続することができる。パラレルデータチャネル 6 2 がコントローラ 6 4 をホスト記憶装置 6 6 に接続している。これに代えて、ホスト記憶装置 6 6 は、独立ディスクの冗長アレイ( R A I D ) とすることができます、かつ I / O コントローラ 6 4 は R A I D コントローラとすることができます。ファイルシステム 2 3 の命令下で動作する I / O ドライバ 6 7 、例えば S C S I ドライバモジュールがコントローラ 6 4 と対話して、ホスト記憶装置 6 6 へのデータの書き込み及び読み出しを行う。好ましくは、ホスト記憶装置 6 6 が、ホストメモリ 3 3 にキャッシュすることができます、ファイルシステム 2 3 を含むホスト 2 0 のオペレーティングシステムコードを有する。

#### 【 0 0 1 7 】

ディスクドライブまたはディスクドライブ及び対応するコントローラの集合のような I N I C 記憶装置 7 0 が、マッチングインターフェースコントローラ、 I N I C ・ I / O コントローラ 7 2 を介して I N I C バス 4 8 に接続され、これが次にパラレルデータチャネル 7 5 により前記 I N I C 記憶装置に接続されている。 I N I C ・ I / O コントローラ 7 2 は、 S C S I コントローラとすることができます、これはパラレルデータチャネル 7 5 により I N I C 記憶装置 7 0 に接続される。これに代えて、 I N I C 記憶装置 7 0 は R A I D システムとすることができます、かつ I / O コントローラ 7 2 を R A I D コントローラとし、多数のまたは分岐したデータチャネル 7 5 とすることができます。同様に、 I / O コントローラ 7 2 は、 I N I C 記憶装置 7 0 のための R A I D コントローラに接続された S C S I コントローラとすることができます。別の実施例では、 I N I C 記憶装置 7 0 は、ファイバチャネル( F C ) ネットワーク 7 5 に接続され、かつ I / O コントローラ 7 2 は F C コントローラである。 I N I C ・ I / O コントローラ 7 2 は I N I C バス 4 8 に接続されたように図示されているが、 I / O コントローラ 7 2 は、これに代えて I / O バス 4 0 に接続することができる。 I N I C 記憶装置 7 0 は、任意により、そこからオペレーティングシステムの核がロードされる、ホスト 2 0 のルートディスクを有することができる。 I N I C メモリ 4 6 は、 L A N / W N 2 5 のようなネットワークから受信したまたはそれに送信される

10

20

30

40

50

パケットを一時的に格納するためのフレームバッファ 77 を有する。また、I N I C メモリ 46 は、I N I C 記憶装置 70 に格納しましたはそこから検索するデータを一時的に格納するために、インターフェースファイルキャッシュ、I N I C ファイルキャッシュ 80 を有する。I N I C メモリ 46 が図 1 においてそれを簡単にするために 1 個のブロックで記載されているが、メモリ 46 は I N I C 22 の様々な位置に配置された別個の装置で形成することができ、かつダイナミックランダムアクセスメモリ (D R A M ) 、スタティックランダムアクセスメモリ (S R A M ) 、リードオンリメモリ (R O M ) 及び他の形態のメモリで構成することができる。

#### 【 0 0 1 8 】

ファイルシステム 23 は、記憶装置 66 、 70 及びファイルキャッシュ 24 、 80 の情報の編成に関する一般的な知識を有する高レベルのソフトウェアエンティティであり、ストレージアーキテクチャの特性及び性能を実行するアルゴリズムを提供する。ファイルシステム 23 は、ファイルの階層構造として、記憶装置 66 、 70 及び各ファイルキャッシュ 24 、 80 に格納されている情報を論理的に編成するが、このような論理ファイルは、記憶装置 66 または 70 の異なるディスクの本質的に異なるブロックに物理的に配置できるものである。また、ファイルシステム 23 は、記憶装置 66 、 70 及びファイルキャッシュ 24 、 80 上でのファイルデータの格納及び検索を管理する。前記ファイルシステム下でホスト 20 上で動作する I / O ドライバ 67 ソフトウェアが、各記憶装置 66 、 70 のコントローラ 64 、 72 と対話して、データのブロックを操作し、即ちそれらの記憶装置からデータブロックを読み出しましたはそれらに書き込む。ホストファイルキャッシュ 24 及び I N I C ファイルキャッシュ 80 によって、記憶装置 66 、 70 から読み出されまたはそれらに書き込まれるデータの記憶空間が提供され、前記データは記憶装置 66 、 70 の物理的ブロック形式とアプリケーションについて使用される論理的ファイル形式との間でファイルシステム 23 によりマッピングされる。ファイルに関連しつホストファイルキャッシュ 24 及び I N I C ファイルキャッシュ 80 に格納されるバイトの線形ストリームをファイルストリームと称する。ホストファイルキャッシュ 24 及び I N I C ファイルキャッシュ 80 はそれぞれ、その対応するキャッシュに保持されるファイルストリームをリストするインデックスを有する。

#### 【 0 0 1 9 】

ファイルシステム 23 は、記憶装置 66 、 70 上のファイルブロックのアドレスを決定するのに使用することができるメタデータを有し、最近アクセスされたファイルブロックのアドレスへのポインタがメタデータキャッシュにキャッシュされる。ファイルブロックへのアクセスが、例えば L A N / W A N 25 上のリモートホストにより要求されると、ホストファイルキャッシュ 24 及び I N I C ファイルキャッシュ 80 のインデックスが最初に参照されて、前記ブロックに対応するファイルストリームがそれらのキャッシュに格納されているかどうかを見る。前記ファイルストリームがファイルキャッシュ 24 または 80 に見当たらない場合には、そのブロックへのリクエストが、前記メタデータにより示された適当な記憶装置のアドレスへ送られる。1つまたは複数の従来のキャッシングアルゴリズムをファイルキャッシュ 24 及び 80 のキャッシングマネージャ 26 が用いて、前記キャッシュが空で新しいデータをキャッシングすべき場合にどのデータを捨てるべきかを選択する。I N I C ファイルキャッシュ 80 上でのファイルストリームのキャッシングによって、I N I C 記憶装置 70 に格納されたファイルブロックの I / O バス 40 及びデータチャネル 75 双方におけるトラフィックが大幅に減少する。

#### 【 0 0 2 0 】

ホスト 20 に送られたネットワークパケットが I N I C 22 に到着すると、そのパケットのヘッダがシーケンサ 52 により処理されて、前記パケットを有効にしつ該パケットのサマリまたは記述子が作成され、該サマリは前記パケットにプリペンドされかつフレームバッファ 77 に格納され、前記パケットへのポインタが 9 に記憶される。前記サマリは、前記パケットヘッダのプロトコルタイプ及びチェックサムの結果を表す状態語である。この状態語に含まれるものは、前記フレームが高速バスデータフローの対象であるかどうか

10

20

30

40

50

を示すものである。従来の方法と異なり、トランスポート及びセッションレイヤの情報を含むプロトコル情報を有する上位レイヤヘッダが、シーケンサ52のハードウェア論理により処理されて、サマリが作成される。前記シーケンサの専用論理回路によって、パケットヘッダを、該パケットがネットワークから到着するのと同様に高速で仮想的に処理することが可能になる。

#### 【0021】

次に、前記INICは、CPU30実行プロトコルスタック38によるヘッダの「低速バス」プロセッシングのために前記パケットをホストメモリ33に送るか、または「高速バス」に従って前記パケットデータを直接INICファイルキャッシュ80またはホストファイルキャッシュ24のいずれかに送るかを選択する。前記高速バスは、シーケンシャルでエラーのないメッセージ毎に複数のパケットを有するデータトライフィックの相当大部分について選択することができ、データを繰り返しコピーしたり、ホストメモリバス35を繰り返し往来するような、前記CPUによる各パケットの時間のかかるプロトコルプロセッシングが回避される。パケットがINICファイルキャッシュ80内に直接移される高速バス状況の場合、ホストバス35とI/Oバス40における追加の往来が同様に回避される。低速バスプロセッシングは、INIC22の高速バスによって従来は転送されないあらゆるパケットをホスト20により従来通り処理できるようとする。

10

#### 【0022】

ホスト20における高速バス能力を与えるためにリモートホストとの接続が最初に設定され、それにはハンドシェーク、認証及び他の接続初期化の手順を含むことができる。通信制御ブロック(CCB)が、TCP/IPまたはSPX/IPXプロトコルにより代表されるような接続ベースのメッセージのための接続初期設定手順の際にプロトコルスタック38により作成される。前記CCBは、ソース及びデスティネーションアドレス並びにポートのような接続情報を有する。TCP接続の場合、CCBは、ソース及びデスティネーション媒体アクセスコントロール(MAC)アドレス、ソース及びデスティネーションIPアドレス、ソース及びデスティネーションTCPポート、並びにスライディングウィンドウプロトコルのための送信受信ウィンドウ及びタイムのようなTCP変数からなる。接続が設定された後、前記CCBはINICドライバ39により前記ホストからINICメモリ46へ、そのメモリ46内にコマンドレジスタを書き込むことによって送られ、そこでは他のCCBと共にCCBキャッシュ74に格納することができる。また、前記INICは、前記CCBをパケットサマリと加速して突き合わせるためにキャッシュしたCCBに対応するハッシュテーブルを作成する。

20

#### 【0023】

ファイル書込みのような前記CCBに対応するメッセージを前記INOCが受け取ると、該メッセージの最初のパケットのヘッダ部分がホスト20に送られて、CPU及びプロトコルスタック38により処理される。この前記ホストに送られたヘッダ部分は、前記パケットの一定のオフセットで始まっていることが知られている、前記メッセージのセッションレイヤヘッダを有し、かつ任意により前記パケットからいくつかのデータを含んでいる。プロトコルスタック38のセッションレイヤによる前記セッションレイヤヘッダのプロセッシングによって、前記ファイルに属するものとして前記データが認識されかつ前記メッセージのサイズが表示され、これらが前記ファイルシステムにより使用されて、前記メッセージデータをホストファイルキャッシュ24またはINICファイルキャッシュ80にキャッシュするかどうか、及び選択されたファイルキャッシュ内の前記データのデスティネーションを確保するかどうかが決定される。前記ホストに送られたヘッダ部分に何らかのデータが含まれていた場合には、それは前記デスティネーションに格納される。選択された前記ファイルキャッシュの前記デスティネーションのバッファアドレスのリストがINIC22に送られて、前記CCBにまたはそれと共に格納される。また、前記CCBは、メッセージの長さ及び処理されたパケットの数並びに順序のような、前記メッセージに関する状態情報を保持し、どのユーザが関与しているか及び転送情報毎の記憶空間を含む、各プロトコルレイヤに関するプロトコル及びステータス情報を提供する。

30

40

50

## 【0024】

前記 CCB が一旦デスティネーションを示すと、該 CCB に対応するパケットの高速バスプロセッシングが可能になる。次に受け取ったパケットをシーケンサ 52 により上述したようにプロセッシングしてパケットサマリを生成した後、前記パケットサマリのハッシュが前記ハッシュテーブルと比較され、かつ必要な場合には前記 CCB キャッシュ 74 に格納された CCB と比較され、高速バス接続が設定されているメッセージに前記パッケージが属するかどうかを決定する。パケットサマリが CCB に整合すると、他の例外的な条件が存在しないと仮定して、ネットワークまたはトランスポートレイヤヘッダ無しで、前記パケットのデータがダイレクトメモリアクセス (DMA) 装置 68 により、前記 CCB により示されたファイルキャッシュ 80 またはファイルキャッシュ 24 のデスティネーションに送られる。

10

## 【0025】

前記メッセージからの全てのデータがファイルストリームとして INC ファイルキャッシュ 80 またはホストファイルキャッシュ 24 内にキャッシュされた後のいくつかの時点において、データのファイルストリームが、ファイルシステム 23 の制御下にある DMA 装置 68 により、そのファイルキャッシュから INC 記憶装置 70 またはホスト記憶装置 66 に、前記ファイルシステムの制御下で送られる。通例、ホストファイルキャッシュ 24 内にキャッシュされたファイルストリームは、INC 記憶装置 66 上に格納されるのに対し、INC ファイルキャッシュ 80 内にキャッシュされたファイルストリームは、INC 記憶装置 70 上に格納されるが、このような構成は必ずしも必要でない。ファイル転送に関する後のリクエストは、そのリクエストが同一のソース及びデスティネーション IP アドレス及びポートを含んでいると仮定して、同じ CCB により取り扱うことができ、書込みリクエストの最初のパケットは前記ホスト CPU により処理されて、前記メッセージを格納するためのホストファイルキャッシュ 24 または INC ファイルキャッシュ 80 内の位置を決定する。また、前記ファイルキャッシュをバイパスしてリモートホストから受け取ったメッセージからのデータを格納するためのデスティネーションとして INC 記憶装置 70 またはホスト記憶装置 66 上の位置を予定するように前記ファイルシステムを構成することが可能である。

20

## 【0026】

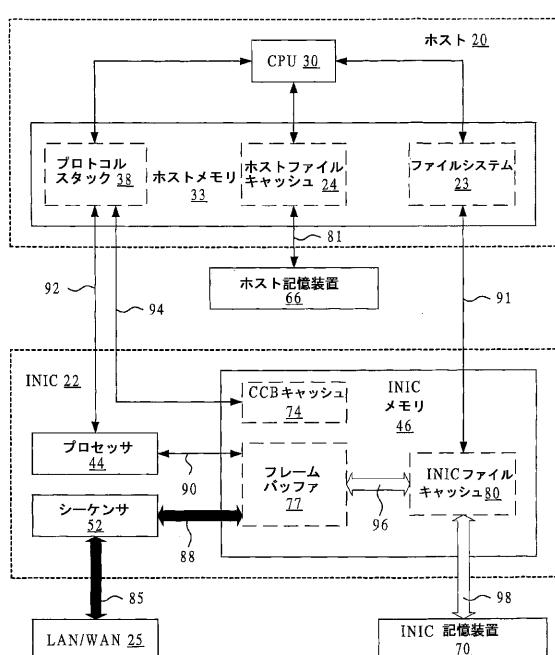

本発明の基本的な理解を促すための概要が図 2 に記載されており、同図では、各バスについての情報についての基本タイプを示すことによって、図 1 のネットワークデータ記憶システムのための情報の流れに関する主要なバスを分離している。図 2 は、細い矢印を有する基本的に制御情報からなる情報のフローパス、太く白い矢印を有する基本的にデータからなる情報のフローパス、及び太く黒い矢印を有する制御情報及びデータ双方からなる情報のフローパスを示している。ホスト 20 が基本的に制御情報の流れに関係しているのに対して、INC 記憶装置 70 は基本的にデータ転送に関連していることに注意する。

30

## 【0027】

LAN / WAN 25 のようなネットワークと INC 22 間の情報の流れは制御情報及びデータを含むことができ、従って太く黒い矢印 85 で示されている。LAN / WAN 25 のようなネットワークと INC 22 間の情報の流れ 81 の例は、ファイルの読み出しままたは書込みに加えて、接続初期設定の対話及び肯定応答のような、制御情報に含まれるようなファイルデータを含むパケットとして送られる制御情報が含まれる。シーケンサ 52 がファイル書込みからの制御情報を処理し、かつデータ及び制御情報を INC フレームバッファ 77 との間でやりとりするが、従ってそれらの転送は太く黒い矢印 88 で表されている。フレームバッファ 77 に格納されるデータに関する制御情報は、細い矢印 90 で示すようにプロセッサ 44 により処理され、かつネットワーク接続初期設定パケット及びセッションレイヤヘッダのような制御情報は、太い矢印 92 で示すように、プロトコルスタック 38 に送られる。前記ホストにより接続が設定されると、その接続に関する、CCB のような制御情報を、細い矢印 94 で示すようにホストプロトコルスタック 38 と INC メモリ 46 との間で送ることができる。INC 記憶装置 70 から読み出されまた

40

50

は書き込まれるデータの一時的な格納が、太く白い矢印 9 6、9 8 で示されるように、INIC ファイルキャッシュ 8 0 及びフレームバッファ 7 7 により行われる。INIC ファイルキャッシュ 8 0 に格納されている全てのファイルストリームの制御及び知識が、細い矢印 9 1 で示すように、ファイルシステム 2 3 によって提供される。ホスト記憶装置 6 6 がネットワークアクセス可能なデータを格納しない実施例では、ファイルシステムの情報が、矢印 8 1 で示すように、ホストファイルキャッシュ 2 4 とホスト記憶装置 6 6 との間で送られる。同図に記載されていない別の実施例では、ホスト記憶装置を備えておらず、または基本的にネットワークファイル転送のためにホスト記憶装置及びホストファイルキャッシュを用いることができる。

【0028】

10

図 2 からわかるように、ネットワークファイル読み出しまたは書き込みのデータは基本的に INIC 2 2 を通過しつつホスト 2 0 を避けており、制御情報が基本的に前記ホストと INIC 間で送られる。このネットワークと記憶装置間のファイル転送に関する制御情報の分離によって、前記ホストは、前記ネットワークと記憶装置との間で前記 INIC を流れるファイル転送を管理することが可能になり、他方前記 INIC がそれらデータ転送のための高速パスを提供し、それによってデータ処理能力が加速される。前記 INIC のデータ高速パスにより得られる処理能力の増加によって、ホスト及び INIC は、ファイルサーバとして機能することに加えて、例えば映像のような高帯域幅アプリケーションのデータベースサーバとして機能することができる。

【0029】

20

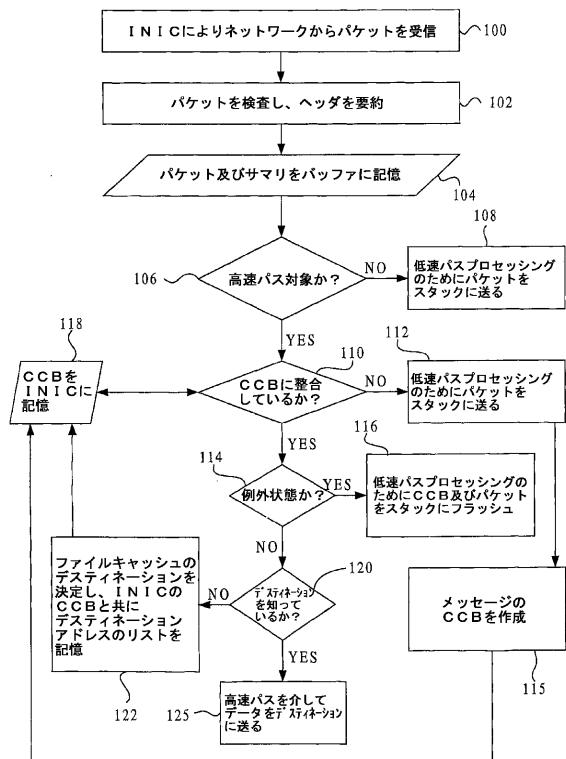

図 3 は、ネットワークから受け取ったメッセージを格納するために図 1 のシステムが実行するいくつかのステップを示している。LAN / WAN 2 5 のようなネットワークから送られたパケットは、最初に PHY 装置 5 8 により INIC 2 2 において受け取られ 1 0 0 、かつ MAC 装置 6 0 が前記パケットがホスト 2 0 にアドレス指定されていることを確認するようにリンクレイヤプロセッシングを実行する。次に、ネットワーク、前記パケットのトランスポート及び任意によりセッションレイヤヘッダがシーケンサ 5 2 により処理され 1 0 2 、それにより前記パケットが有効になりつつそれらヘッダのサマリが作成される。次に、前記サマリをパケットに追加して、フレームバッファ 7 7 の 1 つに格納する。次にプロセッサ 4 4 が、前記パケットサマリを検査することにより、前記パケットが高速パスプロセッシングの対象であるかどうかを決定する 1 0 6 。パケットが高速パスの対象であるかどうかは、単にサマリ内に示されているパケットのプロトコルによって決定することができる。パケットが高速パス対象でない場合には、そのパケットはプロトコルスタック 3 8 からの CPU 3 0 実行命令によって前記パケットのヘッダを処理するために、I/O バス 4 0 を介してホストメモリ 3 3 に送られる 1 0 8 。

【0030】

30

前記パケットは高速パス対象である場合には、前記パケットサマリが、それぞれに CCB として表される、前記カードによって取り扱われる高速バス接続の集合と前記サマリを CCB ハッシュ及び CCB キャッシュと突き合わせることによって比較する。前記サマリが前記 INIC メモリに保持されている CCB と整合しない場合には、前記パケットは、プロトコルスタックからの CPU 実行命令により前記パケットのヘッダを処理するためにホストメモリに送られる 1 1 2 。パケットが接続初期設定対話の一部分である場合には、前記パケットを用いて前記メッセージについて CCB を作成することができる 1 1 5 。前記パケットサマリがむしろ前記 INIC メモリに保持されている CCB に整合する場合には、前記プロセッサは、例えば断片化されたまたは壊れたパケットを含む例外状態を検討し、そのような例外状態が見つかった場合には、プロトコルプロセッシングのために CCB 及び前記パケットをホストプロトコルスタック 3 8 にフラッシュする。パケットサマリは CCB に整合しているが該パケットのデスティネーションが CCB で示されていない場合には、前記パケットのセッションレイヤヘッダをホストプロトコルスタック 3 8 に送って、前記ファイルシステムに従って、ホストファイルキャッシュまたは INIC ファイルキャッシュ内のデスティネーションを決定し 1 2 2 、そのデスティネーションのキャッシュ

40

50

アドレスのリストを CCB と共に INC に格納する。また、前記 INC は CCB をホスト 116 にフラッシュさせかつパケットをスタックによるプロセッシングのためにホストに送らせることになる例外状態について前記パケットサマリを検査する 114。

#### 【0031】

パケットサマリが CCB に整合しかつ該パケットのデスティネーションが該 CCB と共に格納され、かつ例外状態が存在しない場合には、前記パケットからのデータが DMA により、CCB により示されたホストファイルキャッシュまたは INC ファイルキャッシュのデスティネーションに送られる 125。この場合におけるメッセージパケットはホストプロトコルプロセッシングスタックによるヘッダのプロセッシングをバイパスし、高速バスデータ転送を提供する。パケットのデータが高速バスを介して INC ファイルキャッシュ及び INC ストレージに送られているような場合には、前記パケットはホストによるプロトコルプロセッシングを避けるだけでなく、前記 I/O バスまたはホストメモリバスを横切らないので、従来のネットワークストレージと比較して大幅に時間を節約する CPU プロセッシング及びバストラフィックが得られる。

10

#### 【0032】

##### 【発明の実施の形態】

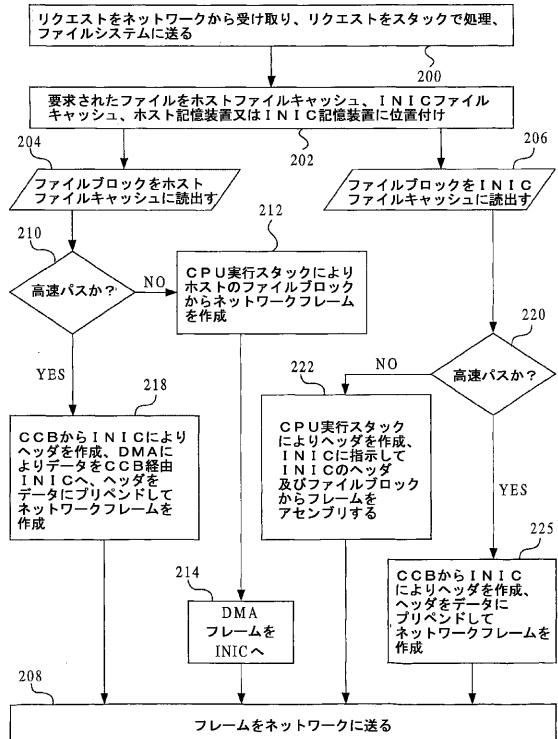

図 4 は、LAN / WAN 25 のようなネットワークからのリクエスト 200 に応答して、ホスト記憶装置 66 または INC 記憶装置 70 からファイルまたはファイルの一部分を検索するために図 1 のシステムによって実行されるいくつかのステップを示している。まず、リクエストパケットをプロトコルスタックにより処理し、それにより前記リクエストをファイルシステムに送る。前記ファイルシステムは前記リクエストに示されたファイルを、該ファイルに対応するファイルストリームが INC ファイルキャッシュまたはホストファイルキャッシュにキャッシュされているかどうかを決定すること、及び前記ファイルストリームが前記キャッシュのいずれかにも配置されていない場合には前記ファイルに対応するブロックが前記ホスト記憶装置または INC 記憶装置に格納されているかどうかを決定することを含めて、位置付けする。ファイルストリームが前記キャッシュのいずれにも配置されていないと仮定した場合、前記ファイルブロックはホストファイルキャッシュに読み取られ 204、または INC ファイルキャッシュに読み取られる 206。大抵の場合には、前記ホスト記憶装置に格納されたファイルブロックはホストファイルキャッシュ内に読み取られ、かつ INC 記憶装置に格納されたファイルブロックは INC ファイルに読み取られことになるが、このマッピングは必然ではない。例えば、ホスト記憶装置に格納されたファイルブロックを INC ファイルキャッシュ内に読み取り、それによってホストメモリバス上のトラフィックを減少させることが好ましい場合がある。

20

#### 【0033】

ファイルブロックがホストファイルキャッシュにキャッシュされていない場合には、前記ホストは前記リクエストに対応する CCB が前記 INC により保持されているかどうかを注意することによって、ファイルを高速バスプロセッシングにより送るかどうかを決定する 210。前記ホストが高速バスを使うのではなく、低速バスによって前記ファイルをホストから送ることを選択した場合、前記ホストはプロトコルスタックを実行して、ホストファイルキャッシュに保持されているデータについてヘッダを作成し、かつ次に前記ヘッダ及びチェックサムをデータに追加して、従来と同様に INC によりネットワーク上を送信するためにネットワークフレームを作成する 212。次に、INC は DMA を用いてホストから前記フレームを入手し 214、かつ次に INC は前記フレームをネットワーク上に送る 208。そうしないで前記ファイルを高速バスで送る場合には、INC プロセッサは CCB を用いてヘッダ及びチェックサムを作成し、ホストファイルキャッシュからのデータのフレームサイズのセグメントを DMA し、かつ次に前記ヘッダ及びチェックサムを前記データセグメントにプリペンドしてネットワークフレームを作成し 218、前記ホストをプロトコルプロセッシングから解放する。

30

#### 【0034】

同様にして、ファイルブロックが INC ファイルキャッシュ内にキャッシュされた場合

40

50

には、前記ホストが CCB が INIC により保持されているかどうかを注意することによって、高速バスプロセッシングにより前記ファイルを送るかどうかを決定する 220。前記ホストが高速バスを使用しないことを選択した場合 222、ホスト CPU は、ファイルロックデータについてヘッダ及びチェックサムを準備し、前記ヘッダをホストメモリに格納する。次に前記ホストは、INIC に指示して、ホストメモリからのヘッダを INIC メモリ内のデータにプリペンドすることによってネットワークフレームをアセンブリし、次に INIC によりネットワークを介して送られるメッセージフレームを作成する。この高速バスを使用しない場合でさえ、データは I/O バスを通ってホストに送られたり INIC から戻されることが無く、I/O バスまたはネットワークによりホストに接続された記憶装置上に配置されたファイルロックの送信という従来方法と比較して、I/O ト 10 ラフィックが少なくなる。その代わりに高速バスが選択された場合 225、INIC プロセッサは CCB に対応するヘッダ及びチェックサムを作成し、かつ前記ヘッダ及びチェックサムを INIC ファイルキャッシュからのデータセグメントにプリペンドしてネットワークフレームを作成し、これは次に INIC によってネットワーク上を送信される。この高速バスの場合には、前記ホストが、I/O バストラフィックから解放されることに加えて、プロトコルプロセッシング及びホストメモリバストラフィックから解放される。

#### 【0035】

図 5 は、ホスト 20 が I/O バス 40 を介して、第 1 INIC 22 に加えていくつかの I/O・INIC に接続されたネットワーク記憶システムを示している。本実施例の各 INIC は少なくとも 1 つのネットワークに接続されかつ少なくとも 1 つの記憶装置が接続されている。かくして第 2 INIC 303 は I/O バス 40 に接続され、第 2 ネットワーク 305 への前記ホストのインターフェースを提供する。第 1 INIC 22 は、上述したように実際はいくつかのネットワークに接続するためにいくつかのネットワークポートを持つことができ、同様に第 2 INIC 303 も 1 つのネットワーク 305 以外のネットワークに接続することができるが、この図面では簡単化するために、各 INIC について 1 つのネットワーク接続のみが示されている。第 2 INIC 303 は、第 2 INIC 記憶装置 308 に接続された SCSI アダプタのような I/O コントローラを有する。これに代えて、第 2 INIC 記憶装置 308 は RAID システムとすることことができ、かつ第 2 INIC 303 は RAID コントローラを有しまたはそれと接続することができる。別の実施例では、第 2 INIC 303 が、FC ネットワークループまたは FC アダプタ及びネットワークラインによって第 2 INIC 記憶装置 308 に接続された FC コントローラを有する。第 N・INIC 310 で示されるように、N 個の INIC をホスト 20 に I/O バスを介して接続することができる。第 N・INIC 310 は、第 N ネットワーク 313 及び第 N 記憶装置 315 にそれぞれ接続されたネットワークインターフェース及びストレージインターフェースを提供する回路及び制御インストラクションを有する。第 N・INIC 310 はいくつかのネットワークに接続するためにいくつかのネットワークポートを持つことができ、かつ第 2 の第 N・INIC 310 が同様に 2 以上のネットワークに接続することができる。第 N・INIC 310 のストレージインターフェース回路及び制御インストラクションは、例えば、SCSI ケーブルによって第 N・INIC 記憶装置 315 に接続された SCSI コントローラを含むことができる。これに代えて、第 N・INIC 記憶装置 315 は RAID システムとすることことができ、かつ第 N・INIC 315 は RAID コントローラを有しまたはそれに接続することができる。さらに別の実施例では、第 N・INIC 310 が、FC アダプタ及び FC ネットワークラインによって第 N・INIC 記憶装置 315 に接続された FC コントローラを有する。 20 30 40

#### 【0036】

前記ファイルシステムは、ネットワークアクセス可能ファイルが、ホスト記憶装置 66 ではなく、いずれか 1 つのネットワーク記憶装置 66、305、315 に格納されるように構成することができ、その代わりにそれはファイルシステムコード及びプロトコルスタックを含み、それらの複製が前記ホストにキャッシュされる。この構成によって、ホスト 20 はネットワークファイル転送を制御するが、それらファイル内のデータの相当大部分は 50

、前記ホストに入ることすらなく、INIC22、203、310を通じて高速バスにより転送することができる。ファイルブロックがネットワークと同じINICに接続された記憶装置との間で転送される場合には、ファイルデータは決してI/Oバスまたはホストメモリバスを横切ることがない。ファイルがネットワークと異なるINICに接続された記憶装置との間で転送される場合には、ファイルブロックはDMAによって、記憶装置に接続されたINIC上のファイルキャッシュとの間でI/Oバスを通して送ることができ、依然としてホストメモリバスを回避する。この通常は回避される最悪の場合では、データはあるINICから別のものに転送することができ、それには、2回のI/Oバス転送や従来通りの繰り返しのホストメモリバスへのアクセスではなく、それに伴うI/Oバスの転送が1回であり、同様にホストメモリバスが回避される。

10

### 【0037】

図6は、上述したINIC・I/Oコントローラ72を必要とすることなく、ネットワーク通信接続及びネットワークストレージ接続を提供するINIC400を含むネットワークストレージシステムを示している。簡潔にするために、ホスト20及び関連する要素は、図1から変更はないものとして図示されているが、これは必ずしも当てはまらない。本実施例のINICは、第1LAN414、第2LAN416、第1SAN418及び第2SAN420に接続されたネットワーク接続またはポートを有する。ネットワーク414、416、418、420のいずれかまたは全部は、イーサネット、ファーストイーサネットまたはギガビットイーサネット規格に従って動作することができる。例えば802.3z及び802.3ab規格で記述されるギガビットイーサネットは、1ギガビット/秒または10ギガビット/秒のデータ転送速度、もしくは将来的におそらくはより速い速度を提供する。SAN418、420は、TCP/IPまたはSCSIカプセル化プロトコルにおいてSCSIのようなストレージプロトコルを実行することができる。そのようなストレージプロトコルの1つが、J.Satran他によりthe Internet Engineering Task Force (IETF)のthe Internet-Draftにおいて「iSCSI (Internet SCSI)」の表題を付して2000年6月に、それより早い時期のInternet-Draftでは「SCSI/TCP (SCSI over TCP)」の表題を付して2000年2月に記載されている。イーサネットストレージと称される、このような別のプロトコルがセッションレイヤにおいてSCSIカプセル化プロトコル(SEP)を使用し、かつ基本的にTCPが使用されているWANまたはインターネット上でデータが転送されているかどうか、またはSTPが使用されるLANまたはSAN上でデータが転送されているかによって、トранスポートレイヤにおいてTCPまたはSANトранスポートプロトコル(STP)を用いることを提案している。

20

### 【0038】

ホスト20は、PCIバスのようなI/Oバス40によってINIC400に接続され、これはPCIバスインターフェースのようなINIC・I/Oブリッジ406によってINICバス404に接続されている。INIC400は、I/Oバス40によってINICメモリ410に接続された専用プロセッサ408を有する。INICメモリ410は、フレームバッファ430及びINICファイルキャッシュ433を有する。また、INICバス404には、ネットワーク、トランスポート及びセッションレイヤプロセッシングを含むネットワークメッセージのプロセッシングを提供するハードウェアシーケンサ412の集合が接続されている。LAN414、416及びSAN418、420への物理的接続は、従来の物理的レイヤハードウェアPHY422によって提供される。各PHY422装置は、媒体アクセスコントロール(MAC)424の対応する装置と接続され、MAC装置はそれぞれINIC400と1つのネットワークとの間にデータリンクレイヤ接続を提供する。

30

### 【0039】

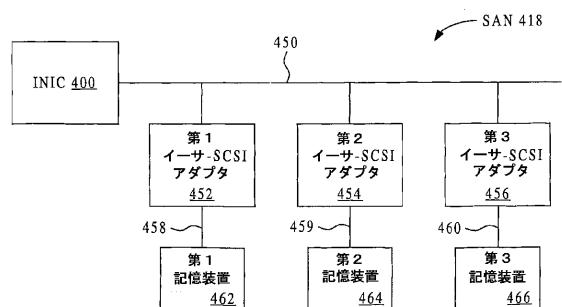

図7は、INIC400と第1イーサネット-SCSIアダプタ452、第2イーサネット-SCSIアダプタ454、及び第3イーサネット-SCSIアダプタ456との間に接続されたギガビットイーサネットライン450を有するSAN418を示している。イ

40

50

—サネット - S C S I アダプタ 452、454、456 は T C P 接続を形成しつつ遮断することができ、I N I C 400 に S C S I コマンドを送りまたはそれから受け取り、かつ 450 を介して I N I C 400 にデータを送りまたはそれから受け取ることができる。第1記憶装置 462 が第1 S C S I ケーブル 458 によって第1イーサネット - S C S I アダプタ 452 に接続されている。同様に、第2記憶装置 464 が第2 S C S I ケーブル 459 によって第2イーサネット - S C S I アダプタ 454 に接続され、かつ第3記憶装置 466 が第3 S C S I ケーブル 460 によって第3イーサネット - S C S I アダプタ 456 に接続されている。記憶装置 462、464、466 は S C S I 規格に従って各アダプタ 452、454、456 によって動作する。各記憶装置は、それぞれのアダプタにデイジーチェーン式に接続された多数のディスクドライブを含むことができる。 10

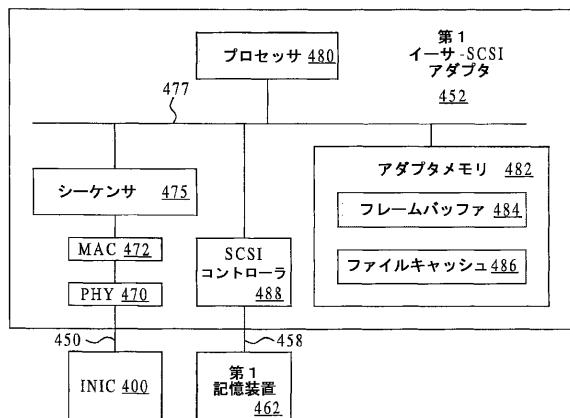

#### 【0040】

図8は、第1イーサネット - S C S I アダプタ 452 を詳細に示しており、これは本実施例において図1に示すものと類似するI N I C である。アダプタ 452 は、従来のP H Y 470 によって提供されるネットワークライン 450 との物理的レイヤ接続及び従来のM A C 472 によって提供される媒体アクセスを有する1個のネットワークポートを有する。上位レイヤプロセッシングを含むネットワークメッセージのパケットヘッダのプロセッシングは、アダプタバス 477 を介してプロセッサ 480 及びアダプタメモリ 482 に接続されたシーケンサ 475 によって提供される。アダプタメモリ 482 はフレームバッファ 484 及びファイルキャッシュ 486 を有する。また、アダプタバス 477 には S C S I コントローラが接続され、かつこれは S C S I チャネル 458 によって第1記憶装置 462 に接続されている。アダプタ 452 と I N I C 20との1つの違いは、アダプタ 452 が低速バスメッセージを処理するためにC P U 及びプロトコルスタックを有するホストに必ずしも接続されていないことである。本実施例において接続の設定は、例えば接続初期設定対話の際にアダプタ 452 に初期パケットを I N I C 400 が送ることによって、アダプタ 452 により行われ、前記パケットはシーケンサ 475 により処理されかつプロセッサ 480 に送られて C C B を作成する。ソフトウェアプロトコルスタックを実行するC P U による低速バスプロセッシングを必要とする一定の状態は、このようなアダプタ 452 と I N I C 400 間の通信環境ではなお一層起こりにくいものである。アダプタ 452 と I N I C 400 間で送られるメッセージは、S C S I / T C P 及び簡易ネットワーク管理プロトコル ( S N M P ) のような単一のまたは限られたプロトコルレイヤの集合に従って構成することができ、かつ単一のソースへまたはそれから単一のもしくは制限された数のデスティネーションに送られる。従来の通信ネットワークに複雑な状態を生じさせる変数の多くを減らすことによって、高速バスプロセッシングの使用を増やすことができ、エラープロセッシングのためのアダプタ 452 の必要性が少なくなる。アダプタ 452 は、I P 及び T C P 上でいくつかのタイプのストレージプロトコルを処理する能力を持たせることができるが、それはアダプタ 452 が、I N I C 400 に接続される代わりに、ネットワークストレージのためにそのようなプロトコルの1つを使用するホストに接続されるような場合である。ネットワーク 450 がストレージ転送に専用のS A N ではないが通信トラフィックを取り扱うような場合、低速バスパケットのためにプロトコルスタックを実行するC P U を有するホストに接続されたI N I C は、アダプタ 452 の代わりに用いることができる。 30

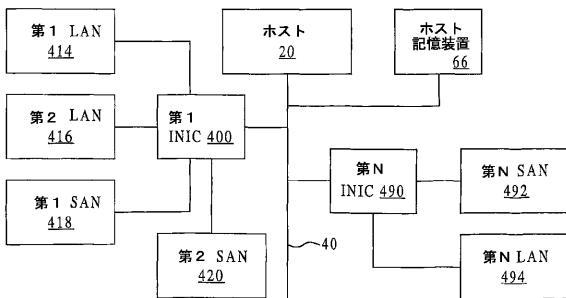

#### 【0041】

図9に示すように、I N I C 400 に類似する追加のI N I C が、I / O バス 40 を介してホスト 20 に接続され、追加の各I N I C によって追加のL A N 接続が提供されかつ / または追加のS A N に接続されている。複数のI N I C は、第N・I N I C 490 で表されており、これは第N・S A N 492 及び第N・L A N 494 に接続されている。ホスト 20 に接続された複数のI N I C によって、前記ホストは複数のストレージネットワークを制御することができ、ホスト制御ネットワークとの間で行き来するデータの流れの相当大部分がホストプロトコルプロセッシング、I / O バスを介しての移動、ホストバスを介しての移動及びホストメモリへの格納をバイパスする。 40

## 【0042】

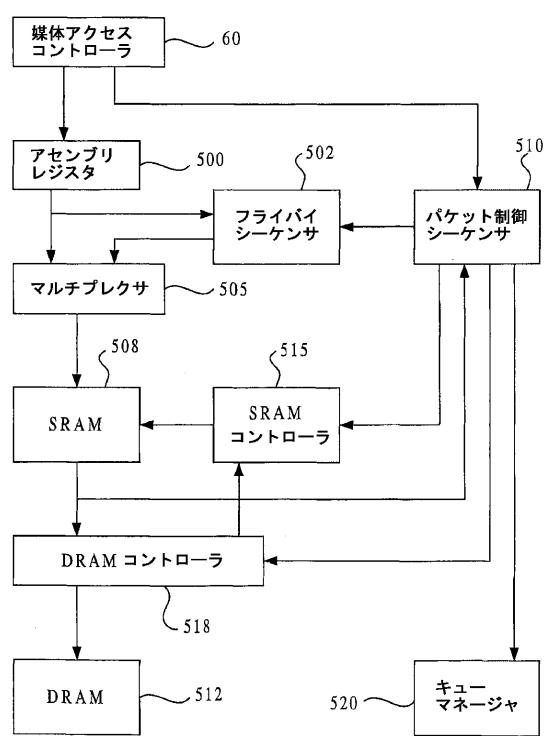

図1のI N I C 2 2がネットワーク2 5のようなネットワークから受信するメッセージパケットのプロセッシングが、図10により詳細に示されている。受け取ったメッセージパケットは、まず媒体アクセスコントローラ6 0に入り、これがネットワークへのI N I Cアクセス及びパケットの受け取りを制御しつつネットワークプロトコル管理のための統計的情報を提供することができる。そこから、データは一度に1バイトづつ、本実施例では1 2 8ビットの幅を有するアセンブリレジスタ5 0 0内に流れる。このデータは、図11に関してより詳細に説明するように、フライバイシーケンサ5 0 2によって分類され、これはパケットのバイトをそれらが近くを飛ぶごとに調査し、それらのバイトから前記パケットを要約されることになるステータスを生成する。このように作成されたステータスは、マルチブレクサ5 0 5により前記データと併合され、その結果得られたデータがS R A M 5 0 8に格納される。パケット制御シーケンサ5 1 0がフライバイシーケンサ5 0 2を監督し、媒体アクセスコントローラ6 0からの情報を調べ、データのバイトをカウントし、アドレスを生成し、かつアセンブリレジスタ5 0 0からS R A M 5 0 8及び最終的にD R A M 5 1 2へのデータの移動を管理する。パケット制御シーケンサ5 1 0は、S R A Mコントローラ5 1 5を介してS R A M 5 0 8のバッファを管理し、またデータをS R A M 5 0 8からD R A M 5 1 2のバッファに移動させる必要がある時、D R A Mコントローラ5 1 8に知らせる。前記パケットに関するデータの移動が一旦完了しつつ全データがD R A M 5 1 2のバッファに移動すると、パケットコントロールシーケンサ5 1 0は、フライバイシーケンサ5 0 2によって生成されたステータスを、パケットデータにプリペンドされるようにS R A M 5 0 8に及びD R A M 5 1 2バッファの開始部分に移動させる。次に、パケット制御シーケンサ5 1 0は、キューマネージャ5 2 0に受信バッファ記述子を受信9に入力するように要求し、これが次にプロセッサ4 4にパケットがハードウェア論理及びその要約されたステータスによって処理されたことを通知する。

## 【0043】

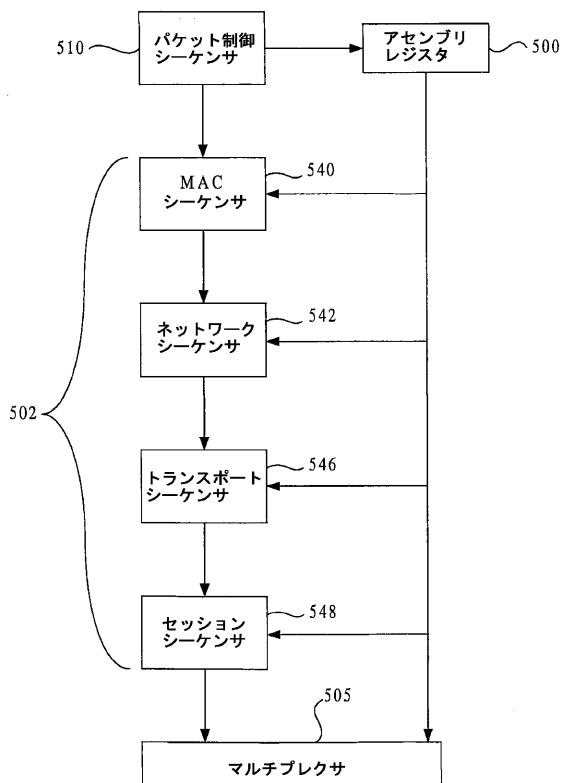

図11は、フライバイシーケンサ5 0 2がいくつかの階層を有することを示しており、各階層は一般にパケットヘッダの特定部分及び特定のプロトコルレイヤに、そのレイヤに関連するステータスを生成するために、焦点を合わせている。本実施例のフライバイシーケンサ5 0 2は、媒体アクセス制御シーケンサ5 4 0、ネットワークシーケンサ5 4 2、トランスポートシーケンサ5 4 6及びセッションシーケンサ5 4 8を有する。より上位のプロトコルレイヤに関するシーケンサを追加で設けることができる。フライバイシーケンサ5 0 2は、パケット制御シーケンサ5 1 0によってリセットされ、かつ一定のバイトがアセンブリレジスタ5 0 0から利用可能であるかをフライバイシーケンサに知らせるパケット制御シーケンサによってポインタが与えられる。媒体アクセス制御シーケンサ5 4 0は、バイト0～5を見ることによってパケットが別のホストではなくまたは別のホストに加えてホスト2 0にアドレス指定されていることを判断する。また、パケットのオフセット1 2、1 3が媒体アクセス制御シーケンサ5 4 0により処理されて、タイプフィールド、例えば前記パケットがイーサネットまたは8 0 2 . 3であるかどうかを決定する。タイプフィールドがイーサネットの場合、それらのバイトは更に前記パケットのネットワークプロトコルタイプを媒体アクセス制御シーケンサ5 4 0に知らせる。8 0 2 . 3の場合には、そうではなく、それらのバイトはフレーム全体の長さを示し、媒体アクセス制御シーケンサ5 4 0が前記パケット内に更に8バイトを調べて、ネットワークレイヤのタイプを決定することになる。

## 【0044】

大部分のパケットについて、ネットワークシーケンサ5 4 2が、受け取ったヘッダの長さが正しい長さであるかを検証し、かつネットワークレイヤのヘッドをチェックサムする。高速バスの対象について、ネットワークレイヤのヘッダは、媒体アクセス制御シーケンサ5 4 0により行われる分析から、I PまたはI P Xであることがわかる。例えば、タイプフィールドが8 0 2 . 3でありかつネットワークプロトコルがI Pであると仮定すると、ネットワークシーケンサ5 4 2は、I Pタイプを決定するために、バイト2 2で始まるこ

となるネットワークレイヤヘッダの最初のバイトを分析する。IPヘッダの最初のバイトは、ネットワークシーケンサにより処理されて、前記パケットが関連するIPタイプを決定することになる。前記パケットが例えばIPバージョン4に関するものであることを決定することで、ネットワークシーケンサ542による処理が更に行われ、該ネットワークシーケンサは前記パケットのトランスポートヘッダプロトコルを表示するためにIPヘッダ内への10バイトに配置されたプロトコルタイプをも見る。例えば、イーサネット上でのIPの場合、IPヘッダはオフセット14で始まり、かつプロトコルタイプバイトはオフセット23であり、これはネットワーク論理により処理されて、トランスポートレイヤプロトコルが例えばTCPであるかどうかを決定する。一般に20～40バイトであるネットワークレイヤヘッダの長さから、ネットワークシーケンサ542は、トランスポートレイヤヘッダを検証するためにパケットのトランスポートレイヤヘッダの開始部分を決定する。トランスポートシーケンサ546は、トランスポートレイヤヘッダ及びデータのチェックサムを生成することができ、これには、少なくともTCPの場合にIPヘッダからの情報を含むことができる。

#### 【0045】

TCPパケットの例について続けて説明すると、トランスポートシーケンサ546はまた、ヘッダのトランスポートレイヤ部分の最初のいくつかのバイトを分析して、前記パケットがNetBiosまたは別のプロトコルであるかどうかのようなメッセージについてTCPソース及びデスティネーションポートを部分的に決定する。TCPヘッダのバイト12をトランスポートシーケンサ546により処理されて、TCPヘッダの長さを決定しつつ検証する。TCPヘッダのバイト13は、認証フラグ及びプッシュフラグは別として、プロセッサにこのパケットを例外として分類せざることがある、リセット及び終了のような予期しないオプションを示すことがあるフラグを有する。TCPオフセットバイト16、17は、ハードウェア論理によって取り出されかつ格納されるチェックサムであり、前記フレームの残りの部分は該チェックサムに対して検証される。

#### 【0046】

セッションシーケンサ548は、セッションレイヤヘッダの長さを決定し、これは、NetBiosの場合にはたった4つのバイトであり、その内の2つがNetBiosペイロードデータの長さを知らせるが、これは他のプロトコルについてより大きくすることができる。また、セッションシーケンサ548を用いて、例えば、特に高速バスが有利であるような読み出しまだ書き込みとしてメッセージのタイプを分類することができる。メッセージのタイプによって、更に上位レイヤの論理プロセッシングが、パケット制御シーケンサ510及びフライバイシーケンサ502のハードウェア論理によって実行することができる。このようにして、シーケンサ52は、バイトの単一のストリームから選択したバイトの分類によってヘッダのハードウェアプロセッシングを知的に行い、パケットのステータスがオンザフライで決定された分類から構築される。全てのパケットがフライバイシーケンサ502により処理されたことをパケット制御シーケンサ510が一旦検出すると、パケット制御シーケンサ510は、フライバイシーケンサ502により生成されたステータス情報及びパケット制御シーケンサ510により生成されたあらゆるステータス情報を付け加え、かつプロセッサ44によるパケットの取り扱いに好都合なように、それらのステータス情報をパケットにプリペンド（前部に追加）する。パケット制御シーケンサ510により生成された追加のステータス情報には、媒体アクセスコントローラ60のステータス情報及び発見されたあらゆるエラー、またはアセンブリレジスタまたはDRAMバッファにおけるデータのオーバフロー、または前記パケットに関する他の様々な情報が含まれる。また、パケット制御シーケンサ510は、キューマネージャ520を介して受信バッファ9及び受信統計9への入力を記憶する。

#### 【0047】

ハードウェア論理によりパケットを処理することの利点は、従来のシーケンシャルソフトウェアプロトコルプロセッシングと対照的に、パケットを格納したり、移動したり、コピーしたり、各プロトコルレイヤヘッダを処理するためにストレージから引き抜いたりする

10

20

30

40

50

必要がなく、処理効率の大幅な増加及び各パケットについて処理時間の節約が得られる事である。パケットは、ネットワークから受け取ったレートビットで、例えば 100 ベース T 接続の場合に 100 メガビット / 秒で処理することができる。このレートで受信されかつ 60 バイトの長さを有するパケットを分類するための時間は、従って約 5 ミリ秒である。このパケットをハードウェア論理で処理しかつパケットデータを高速バスを介してそのホストデスティネーションに送るための合計時間は、CPU の割込みの減少で得られる追加の時間の節約及びホストバスバンド幅の節約を考慮することさえ無く、従来のシーケンシャルソフトウェアプロトコルプロセッシングを用いる従来の CPU が必要とするものよりも、大幅に少なくすることができる。デスティネーションが INIC キャッシュにあるような場合には、ホストバス 35 及び I/O バス 40 について追加のバンド幅の節約が得られる。

#### 【 0048 】

プロセッサ 44 は、フレームバッファ 77 に保持される各受信メッセージパケットについて、そのパケットが高速バスの対象であるかどうかを選択し、かつそうである場合には、前記パケットが属する接続について高速バスが既に接続されているかどうかを調べる。これをするために、プロセッサ 44 はまずヘッダのステータスサマリを調べて、パケットのヘッダが高速バスの対象について定義されたプロトコルからなるものであるかどうかを決定する。そうでない場合には、プロセッサ 44 は、INIC 22 内の DMA コントローラに命令して、前記パケットを低速バスプロセッシングのためのホストに送る。メッセージの低速バスプロセッシングの場合でさえ、このように INIC 22 は、メッセージタイプの検証及び決定のような初期処理を実行し、かつ検証したメッセージを少なくともホストのデータリンクレイヤに送る。

#### 【 0049 】

高速バス対象の場合、プロセッサ 44 は、ヘッダのステータスサマリが INIC により保持されている CCB と一致するかどうかを調べる。そうである場合、前記パケットからのデータは、高速バスに沿って前記ホストのデスティネーション 168 に送られる。高速バス対象のパケットサマリが INIC により保持される CCB と一致しない場合には、前記パケットは低速バスプロセッシングのために前記ホストに送られ、該メッセージの CCB を作成する。また、断片化されたメッセージや他の複雑さがある場合には高速バスが用いられないことがある。しかしながら、相当大部分のメッセージについては、INIC 高速バスによってメッセージのプロセッシングを大幅に加速することができる。このように INIC 22 は、与えられたパケットの運命を決定するためにいくつかのプロトコルレイヤのそれぞれにステートマシンを用いる従来のものと対照的に、オンザフライで集めた情報に基づいて、データをそのデスティネーションに直接送るかどうかを決定する単一のステートマシンプロセッサ 44 が提供される。

#### 【 0050 】

CCB を INIC のハッシュテーブルにキャッシングすることによって、到来するパケットを要約する語との素早い比較が行われ、パケットを高速バスを介して処理できるかどうかが決定される一方、一杯の CCB がプロセッシングのために INIC に保持される。この比較を加速する別の方法には、B - ツリーのようなソフトウェア処理またはコンテンツアドレス可能メモリ (CAM) のようなハードウェアアシストが含まれる。INIC マイクロコードまたはコンパレータ回路が CCB との整合を検出すると、DMA コントローラが前記パケットからのデータをホストメモリ 33 または INIC ファイルキャッシュ 80 のデスティネーションに CPU による割込み、プロトコルプロセッシングまたは複製なしで配置する。受信したメッセージのタイプによって、前記データのデスティネーションはホスト 20 、またはホストファイルキャッシュ 24 、INIC ファイルキャッシュ 80 のセッションレイヤ、プレゼンテーションレイヤまたはアプリケーションレイヤであったりする。

#### 【 0051 】

ファイル転送のような大きなメッセージについて最も一般的に使用されているネットワー

10

20

30

40

50

クプロトコルの1つは、TCP/IP上のサーバメッセージブロック(SMB)である。SMBは、ファイルが書き込まれるプリンタまたはディスクのような特定の動作のために必要なリソースが前記動作が行われたホストに存在するかまたはそれに関連するかもしくはファイルサーバのようなネットワークに接続された別室のホストに配置されているかどうかを決定するリダイレクタソフトウェアと協力して動作することができる。SMB及びサーバフラッシュリダイレクタは、通常トランスポートレイヤからサービスを受けることができる。本発明では、SMB及びリダイレクタはそうではなく、INICからサービスを受けることができる。この場合、大きなSMBトランザクションを受け取った時、INICバッファからDMAコントローラによってデータを送ることは、ホストが取り扱わなければならない割込みを大幅に少なくすることができる。更に、このDMAは、通常データをそのホストファイルキャッシュ24またはINICファイルキャッシュ80内のデスティネーションに移動させ、そこから次にロックでホスト記憶装置66またはINIC記憶装置70へそれぞれフラッシュされる。

#### 【0052】

SMB高速バス電送は一般に上述したSMB高速バス受信を逆にし、データのブロックがホスト記憶装置66またはINIC記憶装置70からホストファイルキャッシュ24またはINICファイルキャッシュ80へそれぞれ読み取られる一方、関連するプロトコルヘッダが、ネットワークラインを介してリモートホストへの伝送のために、INICにより前記データにプリペンドされる。カスタムハードウェア経由かつホストの繰り返し割込み無しにINICにより複数パケット及び複数TCP、IP、NetBIOS及びSMBプロトコルレイヤのプロセッシングによって、SMBメッセージをネットワークラインに伝送する速度を大幅に増加させることができる。図4に関連して上述したように、送信したファイルロックがINIC記憶装置70上に格納される場合には、ホストバス35バンド幅及びI/Oバスバンド幅40における追加の節約を得ることができる。

#### 【0053】

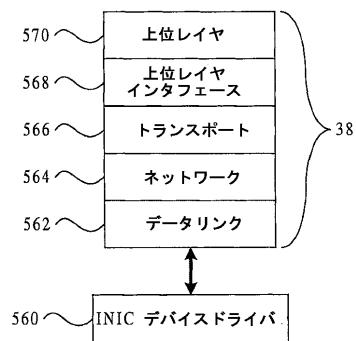

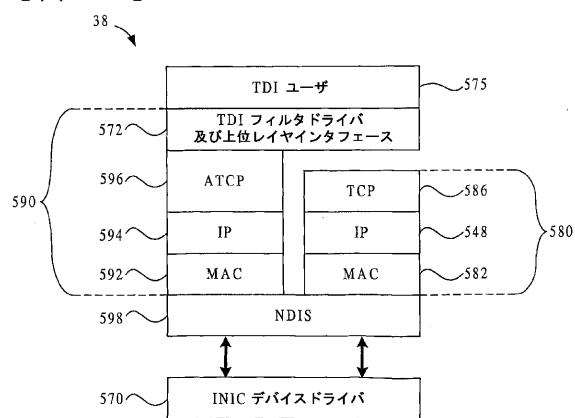

図12は、そのいずれも同図には記載されていないが、ネットワークメッセージを処理するために、INICと共にホストにより使用されるAlacritechのプロトコルスタック38を示している。INICドライバ560はINICをホストのオペレーティングシステムにリンクさせ、INICとプロトコルスタック38間で通信を送ることができる。本実施例のプロトコルスタック38はデータリンクレイヤ562、ネットワークレイヤ564、トランスポートレイヤ566、上位レイヤインタフェース568及び上位レイヤ570を有する。上位レイヤ570は、使用される特定のプロトコル及び通信されるメッセージによって、セッションレイヤ、プレゼンテーションレイヤ及び/またはアプリケーションレイヤを表すことができる。プロトコルスタック38は低速バスのパケットヘッダを処理し、接続を作りかつ壊し、INICへの高速バス接続のためにCCBを分配し、かつINICからホスト20へフラッシュされる高速バス接続のためにCCBを受け取る。上位レイヤインタフェース568は一般に、データリンクレイヤ562、ネットワークレイヤ564及びトランスポートレイヤ566により作成された接続及びステータス情報に基づいてCCBを組み立てること、及びINICデバイスドライバ560経由CCBをINICに分配すること、またはINICデバイスドライバ560経由INICからフラッシュされたCCBを受け取ることに責任を有する。

#### 【0054】

図13は、マイクロソフト(登録商標)のオペレーティングシステムと協力してネットワーク通信を処理するための複数のプロトコルスタックを有するAlacrytechのプロトコルスタック38の別の実施例を示している。従来のマイクロソフトのTCP/IPプロトコルスタック580はMACレイヤ582、IPレイヤ584及びTCPレイヤ586を有する。コマンドドライバ590がホストスタック580と協力して動作し、ネットワークメッセージを処理する。コマンドドライバ590はMACレイヤ592、IP594及びAlacrytechのTCP(APCP)レイヤ596を有する。従来のスタック580とコマンドドライバ590とが、INICデバイスドライバ570と対話するネットワークドライバ

10

20

30

40

50

インターフェース仕様(NDIS)レイヤ598を共有する。INICデバイスドライバ570は、従来のホストスタック580またはATCPドライバ590によって処理するために受信表示をソートする。PDIフィルタドライバ及び上位レイヤインターフェース572は同様に、TDIユーナ575からネットワークに送られるメッセージがコマンドドライバにかつ恐らくはINICの高速バスへ向きを変えられるか、またはホストスタックにより処理されるかを決定する。

#### 【0055】

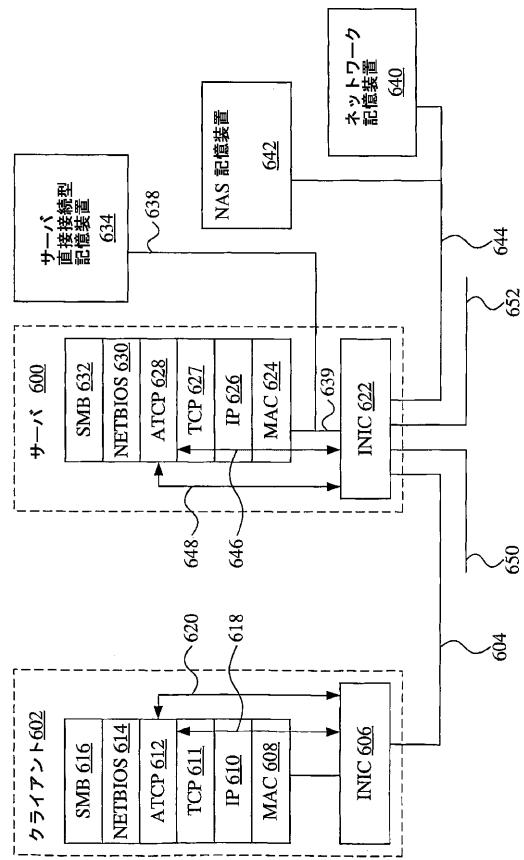

図14は、共にINICを有するサーバ600とクライアント602との間のSMBエクスチェンジを示しており、各INICは、ギガビットイーサネットコンプライアントで有り得るネットワーク604上でのデータの高速バス移動のためにその接続及びステータスを定義するCCBを有する。クライアント602はINIC606、802.3コンプライアントデータリンクレイヤ608、IPレイヤ610、TCPレイヤ611、ATCPレイヤ612、NetBIOSレイヤ614及びSMBレイヤ616を有する。前記クライアントは、通信処理のために低速バス618及び高速バス620を有する。同様に、サーバ600はINIC622、802.3コンプライアントデータリンクレイヤ624、IPレイヤ626、TCPレイヤ627、ATCPレイヤ628、NetBIOSレイヤ630及びSMBレイヤ632を有する。サーバ直接接続型記憶装置634が、SCSIチャネルのようなパラレルチャネル638上でサーバと接続される。これはINIC622にも接続されたI/Oバス639に接続されている。ネットワーク記憶装置640がネットワークライン644上でINIC622に接続され、かつNAS記憶装置642が、ギガビットイーサネットコンプライアントで有り得る同じネットワーク644に接続されている。サーバ600は、図14に示されてないファイルキャッシュとINIC622間でI/Oバス638上を通過する通信プロセッシングのための低速バス646及び高速バス648を有する。

#### 【0056】

ネットワーク記憶装置640または642とクライアント602との間で転送される、I/Oバスを通らないデータのために、サーバの制御下でINIC622によりストレージ高速バスが提供される。データはSCSI/TCPまたはISCSIのようなブロック形式に従ってINIC622とネットワーク記憶装置640との間で通信され、データはTCP/NetBIOS/SMBのようなファイル形式に従ってINIC622とNAS記憶装置642との間で送信される。いずれのストレージ高速バスについても、INIC622が、記憶装置640または642との接続を定義する別のCCBを保持することができる。以下の説明を簡便にするために、そのサーバ600とのネットワーク604での接続を定義するINIC606により保持されるCCBをクライアントCCBと称し、そのクライアント602とのネットワーク604上での接続を定義するINIC622により保持されるCCBをサーバCCBと称する。そのネットワーク記憶装置640とのネットワーク644での接続を定義するINIC622により保持されたCCBをSAN・CCBと称し、そのNAS記憶装置642とのネットワーク644上での接続を定義するINIC622により保持されたCCBをNAS・CCBと称する。追加のネットワークライン650、652を別の通信及び/またはストレージネットワークと接続することができる。

#### 【0057】

クライアント602が、ネットワーク記憶装置640上にブロックで格納されたサーバ600上の100KBファイルを読み出したいと仮定すると、前記クライアントは、ネットワーク604を通ってSMB読み出しリクエストを送ることによって開始し、前記サーバ上のそのファイルの最初の64KBを要求することができる。この要求は、例えば76バイトだけであってもよく、前記サーバ上のINIC622はメッセージのタイプ(SMB)及び比較的小さいメッセージのサイズを認識し、前記76バイトを直接ATCPフィルタレイヤ628に送り、それが前記リクエストをサーバのNetBIOS630に送信する。NetBIOS630はセッションヘッダをSMB632に送り、これが前記読み出しリ

10

20

30

40

50

クエストを処理して、要求されたデータがホストまたはINICファイルキャッシュ上に保持されているかどうかを決定する。要求されたデータがファイルキャッシュにより保持されていない場合、SMBはファイルシステムに読み出しリクエストを出して、ネットワーク記憶装置640からのデータをINIC622ファイルキャッシュ内に書き込む。

#### 【0058】

これを実行するために、ファイルシステムはINIC622に、ネットワーク記憶装置640から64KBのデータをINIC622ファイルキャッシュ内にフェッチするように指示する。次にINIC622は、前記データへのリクエストをネットワーク記憶装置640へネットワーク644で送信する。このリクエストは前記ブロックを読み取る記憶装置640への1つまたは複数のSCSIコマンドの形を取ることができ、前記コマンドには10

ISCSIまたは類似のプロトコルに従って、TCP/IPヘッダが付加されている。記憶装置640上のコントローラがそのディスクドライブから要求されたブロックを読み出し、ISCSIまたは類似のプロトコルヘッダを前記ブロックまたは該ブロックのフレームサイズの部分に付け加え、かつその結果得られるフレームをネットワーク644上でINIC622に送ることによって、前記コマンドに応答する。前記フレームはINIC622により受け取られ、INIC622シーケンサにより処理され、ストレージCCBと整合され、かつ要求された100KBファイルの一部分を形成するINICファイルキャッシュの64KBファイルストリームとして再び組立てられる。前記ファイルストリームがINIC622ファイルキャッシュ上に一旦格納されると、SMBは読み出し応答を組立てかつそのファイルストリームを示すスキヤッタギャザリストをINIC622に送り、かつ前記応答をINIC622に送って、サーバCCBに従ってネットワーク上で前記データを送る。INIC622は前記スキヤッタギャザリストを用いて、そのファイルキャッシュからデータパケットを読み出し、これは、サーバCCBに基づいてINICにより作成されたIP/TCP/NetBIOS/SMBヘッダとプリペンドされ、かつその結果のフレームをネットワーク604上に送る。前記ファイルの残りの36KBは、同様の手法で送られる。このようにして、ネットワーク記憶装置上のファイルは、サーバの制御下で、I/Oバスまたはサーバプロトコルスタックに出会うファイルからのデータ無しで転送することができる。

#### 【0059】

クライアント602により要求されたデータがNAS記憶装置642上に格納される場合には、リクエストはサーバ600からその記憶装置642へ送ることができ、これはクライアント602にアドレス指定されたヘッダを有するデータを送ることによって応答し、サーバ600がルータとして機能する。サーバ600がプロキシサーバまたはウェブキャッシュサーバとして実行されるような実施例では、NAS記憶装置からのデータをサーバ600に送ることができ、これが前記データをそのファイルキャッシュに格納して、そのデータに関する将来のリクエストに対するより早い応答を提供する。この実施例では、サーバ600上のファイルシステムが、NAS記憶装置642上のファイルデータを要求するようにINICを指示し、これがファイルデータの最初の64KBを含む多数の約1.5KBパケットを送ることによって応答する。前記ファイルデータを含むパケットはINIC622が受信し、INIC受信シーケンサにより分類されかつNAS・CCBと整合され、最初のパケットからのセッションレイヤヘッダがホストスタックにより処理され、これがファイルシステムからINIC622ファイルキャッシュのアドレスのスキヤッタギャザリストを入手して、前記パケットからのデータを格納する。前記スキヤッタギャザリストはホストスタックによりINIC622に送られ、かつNAS・CCBと共に格納され、INIC622が、NAS・CCBに対応するあらゆる蓄積パケット及びその後に続くパケットからのデータを、スキヤッタギャザリストに従ってファイルストリームとしてINIC622ファイルキャッシュ内へDMAし始める。次に、ホストファイルシステムがINIC622に指示して、クライアントCCBに基づいてヘッダを作成し、かつ前記ファイルストリームから読み出されたデータのパケットに、該データをクライアント602に送るためにヘッダをプリペンドする。前記ファイルの残りの36KBは同様の手法40

50

により送られ、かつ別のファイルストリームとしてINIC622ファイルキャッシュにキャッシュすることができる。ファイルストリームがINIC622ファイルキャッシュに保持されることによって、クライアント606のようなクライアントへの前記ファイルへの後から来るリクエストが、より早く処理することができる。

#### 【0060】

クライアント602により要求されたファイルがキャッシュに存在せず、その代わりにファイルブロックとしてサーバ接続記憶装置634上に格納されていた場合には、サーバ622ファイルシステムがホストSCSIドライバを指示して、サーバ接続記憶装置634から100KBのデータをサーバ600ファイルキャッシュ内にフェッチさせる（前記ファイルシステムはINIC622ファイルキャッシュ上のデータをキャッシュしたくないと仮定する）。次に、ホストSCSIドライバがSCSIチャネル638上で前記データへのSCSIリクエストをサーバ直接接続型記憶装置634に送る。サーバ直接接続型記憶装置634上のコントローラが、要求されたブロックをそのディスクドライブから読出し、かつ該ブロックをSCSIチャネル639上で前記SCSIドライバに送ることによって前記コマンドに応答し、これが前記ファイルシステムの命令下でキャッシュマネージャと対話して、前記ブロックをファイルストリームとしてサーバ600ファイルキャッシュに格納する。次にファイルシステムリダイレクタがSMBを指示して、前記ファイルストリームのスキッタギャザリストをINIC622に送り、これをINIC622が用いて、サーバ600ファイルストリームからデータパケットを読み出す。INIC622は、サーバCCBに基づいて作成されたヘッダで前記データパケットをプリペンドしつつ、その結果のフレームをネットワーク604上に送る。

#### 【0061】

この応答が到着したときクライアント602上でINIC606が動作し、INIC606は受け取った第1フレームからこの接続が高速バス620プロセッシング（TCP/IP、NetBIOS、CCBをマッチング）を受け取っていることを認識し、SMB616がこの第1フレームを用いてメッセージのためのバッファステージを獲得する。バッファの割り当ては、あらゆるNetBIOS/SMBヘッダを含む前記フレームの最初の192バイトをATCP高速バス620を介してクライアントNetBIOS614に直接送り、適当なヘッダをNetBIOS/SMBに与えることによって提供される。NetBIOS/SMBはこれらのヘッダを分析し、リクエストIDとの整合によって、これが元の読出し接続への応答であることを認識し、かつその中にデータが配置されるクライアントファイルキャッシュのバッファの64KリストをATCPコマンドドライバに与える。この段階ではまだ1つのフレームが到着しているが、このプロセッシングが行なわれている間により多くのフレームが到着し得る。前記クライアントバッファリストがATCPコマンドドライバ628に与えられるとすぐに、これはその転送情報をINIC606に送り、INIC606はDMAによりそれらのバッファ内に蓄積されている全てのフレームデータの送信を開始する。

#### 【0062】

クライアント602がSMBファイルをサーバ600に書き込みたい場合には、書き込みリクエストが、INIC622により保持されているCCBとマッチングするであろうネットワーク604上を送信される。ファイル書き込みの最初のパケットからのセッションレイヤヘッダがサーバSMB632により処理されて、サーバ600またはINIC622ファイルキャッシュ内にバッファが割り当てられ、それらバッファに関するアドレスのスキッタギャザリストが、高速バスプロセッシングが適当であると仮定した場合、INIC622へ戻される。SMBファイルデータを含むパケットがINIC622により受け取られ、INIC受信シーケンサにより分類されかつキューの中に配置される。INIC622プロセッサは、パケットがサーバCCBに対応していることを認識しつつ前記パケットからのデータをINIC622またはサーバ600ファイルキャッシュバッファ内にスキッタギャザリストに従ってDMAして、ファイルストリームを形成する。

#### 【0063】

10

20

30

40

50

次に、前記ファイルシステムが、前記ファイルストリームのサーバ記憶装置 634、ネットワーク記憶装置 640 または NAS 記憶装置 642 への送信を編成する。ファイルストリームをサーバ記憶装置 634 に送るために、ファイルシステムはサーバ 600 内の SCSI ドライバに命令して、前記ファイルストリームをファイルブロックとして記憶装置 634 に送る。ファイルストリームをネットワーク記憶装置 640 に送るために、ファイルシステムは INIC に命令して、SAN・CCB に基づいて ICS または類似のヘッダを作成し、それらのヘッダを前記スキヤッタギャザリストに従って前記ファイルストリームから読み出したパケットにプリペンドし、その結果のフレームをネットワーク 644 上で記憶装置 640 に送る。例えば分散ファイルキャッシュまたはプロキシサーバの実行に有用で有り得る NAS 記憶装置 642 に前記ファイルストリームを送るために、ファイルシステムリダイレクタは適当な NetBios / SMB ヘッダをプリペンドし、かつ INIC に命令して、NAS・CCB に基づいて IP / TCP ヘッダを作成し、かつそれらのヘッダを、スキヤッタギャザリストに従って前記ファイルストリームから読み出されたパケットにプリペンドし、その結果のフレームをネットワーク 644 上で記憶装置 642 に送る。

10

#### 【0064】

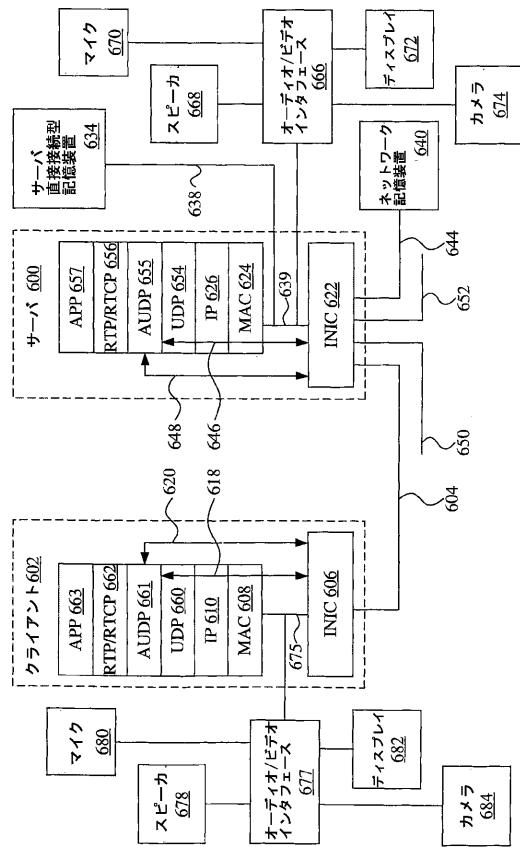

図 15 は図 14 に示すものと類似のものを示しているが、図 15 は、特にリアルタイムトランスポートプロトコル ( RTP ) 及びリアルタイムトランスポートコントロールプロトコル ( RTCP ) が関係し得る音声及び映像通信のコンテキストにおいて、本発明の ユーザデータグラムプロトコル ( UDP ) に焦点を合わせている。サーバ 600 は、図 14 に示すプロトコルレイヤに加えて、UDP レイヤ 654、AUDP レイヤ 655、RTP / RTCP レイヤ 656 及びアプリケーションレイヤ 657 を有する。同様に、クライアント 602 は、図 14 に示すプロトコルレイヤに加えて UDP レイヤ 660、AUDP レイヤ 661、RTP / RTCP レイヤ 662 及びアプリケーションレイヤ 663 を有する。図 15 に RTP / RTCP レイヤ 656、662 は図示されているが、セッション初期設定プロトコル ( SIP ) または媒体ゲートウェイコントロールプロトコル ( MGCP ) のような他のセッション及びアプリケーションプロトコルを UDP の上に用いることができる。

20

#### 【0065】

オーディオ / ビデオインターフェース ( AVI ) 666 または類似の周辺装置がサーバ 600 の I / O バス 639 に接続され、かつ AVI 666 にはスピーカ 668、マイク 670、ディスプレイ 672 及びビデオカメラで有り得るカメラ 674 が接続されている。簡単にするために 1 つのインターフェースとして図示されているが、これに変えて AVI 666 は、サウンドカードまたはビデオカードのようなそれぞれ I / O バス 639 に接続される別個のインターフェースを有することができる。別の実施例では、AVIインターフェースが I / O バスではなくホストバスに接続され、かつホスト CPU のメモリコントローラまたは I / O コントローラと一体にすることができる。AVI 666 は、音声または映像データのための一時的記憶装置として機能するメモリを有することができる。また、クライアント 602 は I / O バス 675 を有し、AVI 677 は I / O バス 675 に接続されている。AVI 677 に接続されているのは、スピーカ 678、マイク 680、ディスプレイ 682、及びビデオカメラで有り得るカメラ 684 である。簡単にするために 1 つのインターフェースとして図示されているが、これに代えて AVI 666 は、サウンドカード及びビデオカードのようなそれぞれ I / O バス 675 に接続された別個のインターフェースを有することができる。

30

40

#### 【0066】

TCP と異なり、UDP は従属性の接続を提供しない。その代わりに、UDP パケットはベストエフォートベースで送られ、かつ失われたまたは壊れたパケットは UDP より上位のレイヤがそのようなサービスを提供しない限り、再送されない。UDP は、接続を確立する必要なく IP を介してアプリケーションがデータを送る方法を提供する。しかしながら、UDP またはネットワークファイルシステム ( NFF ) 、TCP 、 RTCP 、 SIP

50

またはM G C P のような別のプロトコルによるリクエストに応答してソケットが指定され、そのソケットがU D P により送られたメッセージを受け入れることができる受信装置上のポートを割り当てる。ソケットは、ソース及びデスティネーションI P アドレス並びにソース及びデスティネーションU D P ポートを示すU D P により用いられるアプリケーションプログラミングインタフェース ( A P I ) である。

#### 【 0 0 6 7 】

U D P を介して従来どおりに通信を送るために、セッションレイヤまたはアプリケーションレイヤのヘッダを含むことができ、かつ通常約 8 K BまでのN F S デフォルトサイズのデータグラムである 6 4 K Bまでのデータグラムを、ホストコンピュータによりU D P ヘッダでプリペンドしてI P レイヤに渡す。U D P ヘッダは、ソース及びデスティネーションポート並びに任意のチェックサムを含む。イーサネット伝送の場合、U D P ダイヤグラムは、必要に応じて、I P レイヤにより約 1 . 5 K B のフラグメントに分割され、I P ヘッダでプリペンドされかつイーサネットヘッダ及びトレーラでのカプセル化のためにM A C レイヤに与えられ、かつネットワーク上に送られる。I P ヘッダは、U D P データグラムに固有のI P 識別フィールド ( I P · I D ) と、そのダイヤグラムのより多くのフラグメントが続いているかどうかを示すフラグフィールドと、前記フラグメントを正しい順序で再アセンブリするために、前記ダイヤグラムのどの 1 . 5 K B フラグメントがI P ヘッダに接続されたかを示すフラグメントオフセットフィールドを有する。

10

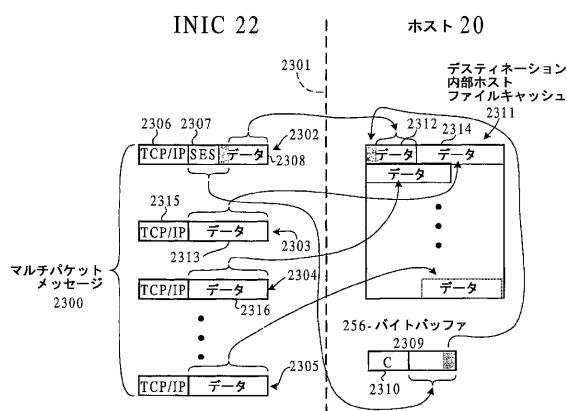

#### 【 0 0 6 8 】

クライアント 6 0 2 からサーバ 6 0 0 への高速バスU D P データ転送の場合、例えばクライアントアプリケーション 6 6 3 またはオーディオ/ビデオインタフェース 6 7 7 からのデータのファイルストリームは、ファイルシステムの命令下でI N I C 6 0 6 のメモリ上に格納することができる。アプリケーション 6 6 3 は、例えば約 8 K B を有するように前記ファイルストリームを構成することができ、それはアプリケーション 6 6 3 の命令下でI N I C 6 0 6 により獲得される上位レイヤヘッダを含むことができ、I N I C 6 0 6 により受け取られる各ファイルストリームは、指定されたソケットに従ってI N I C 6 0 6 によりU D P ヘッダでプリペンドされ、U D P データグラムを作成する。U D P データグラムは、I N I C 6 0 6 により 6 つの 1 . 5 K B メッセージフラグメントに分割され、それはそれぞれI P 及びM A C レイヤヘッダでプリペンドされて、ネットワーク 6 0 4 上に伝送されるI P パケットを作成する。

20

30

#### 【 0 0 6 9 】

I N I C 6 2 2 は、I N I C 6 0 6 から送られたイーサネットフレームをネットワーク 6 0 4 から受け取り、ヘッダをチェックサムしかつ処理して、関連するプロトコルを決定し、かつU D P 及び上位レイヤヘッダをA U D P レイヤ 6 5 5 に送って、そのU D P データグラムのパケットから前記データのデスティネーションアドレスのリストを入手する。U D P 及び上位レイヤヘッダはU D P データグラムからの最大 6 つまでのパケットの 1 つに含まれ、かつそのパケットは通常そのデータグラムからの他のパケットより先に受け取られる。前記パケットが間違った順序で到着する場合には、I N I C 6 2 2 が再アセンブリバッファ内でU D P データグラムからの前記最大 6 つのパケットを列に並ばせる。U D P データグラムに対応するパケットは、そのI P · I D に基づいて識別され、フラグメントオフセットに基づいて連結される。U D P 及び上位レイヤヘッダを含むパケットが処理されてデスティネーションアドレスが獲得された後、並べられた前記データをそれらのアドレスに書き込むことができる。U D P データグラムからの全てのパケットが来ない可能性を説明するために、I N I C 6 2 2 は、受け取ったデータの落とし込み ( dropping ) をトリガするタイマを用いることができる。

40

#### 【 0 0 7 0 】

リアルタイム音声または映像通信の場合、電気通信接続がサーバ 6 0 0 とクライアント 6 0 2 との間で最初に設定される。国際電気通信連合 ( I T U ) H . 3 2 3 規格による通信では、電気通信接続の設定が、R T P を用いたデータの流れのためにソース及びデスティネーションU D P ポートを指定するT C P ダイヤログで実行される。電気通信接続設定の

50

ための別のTCPダイヤログが、RTCPを用いたデータフローをモニタするためにソース及びデスティネーション UDP ポートを指定する。SIPによって電気通信接続を初期設定するための別のメカニズムが提供される。UDP ソケットが指定された後、本発明によるサーバ600からクライアント602への音声または映像データの伝送を開始することができる。

#### 【0071】

例えば、オーディオ/ビデオインターフェース666は、マイク670及びカメラ674からの音声及びイメージを、INIC622に利用可能なオーディオ/ビデオデータに変換する。サーバ600ファイルシステムの指示のもとで、INIC622は、 RTPヘッダを含むAVデータの8KBファイルストリームを獲得し、かつそのデータをINICファイルキャッシュに格納することができる。電気通信接続に従って、INIC622はUDPヘッダを各ファイルストリームにプリペンドすることができ、次にこれが1.5KBのフラグメントに断片化され、そのそれがIP及びイーサネットヘッダでプリペンドされて、ネットワーク604上に伝送される。これに変えて、INIC622はINICメモリ上に格納されたAVデータから1.5KBのUDPデータグラムを作成することができ、断片化を回避しかつUDP及びIP及びMACレイヤヘッダを同時に前記電気通信接続に対応するINIC622上に保持されたテンプレートから作成できるようする。また、AVデータで8KBより大きいUDPデータグラムを作成することができ、それが追加の分割を作成するが、データグラムごとにより大きなブロックのデータを転送することができる。RTPヘッダは、AVデータがオーディオ/ビデオインターフェース666によりパケット化される相対時間を表示するタイムスタンプを有する。

#### 【0072】

ホストCPUによるAVデータの従来のプロトコルプロセッシングと対照的にINIC622は、UDPヘッダ作成、IP断片化及びIPヘッダ作成のタスクをオフロードすることができ、ホストCPUの複数のプロセッシングサイクル、複数の割り込みを不要にしかつホストパストラフィックを大幅に少なくすることができる。INIC622は、複数のヘッダを1度にプリペンドすることによって、より効率的にヘッダ作成タスクを実行することができる。更に、AVデータは、最初にI/Oバス639上をプロトコルプロセッシングスタックへ送られかつ次にRTP/UDP/IPパケットとしてI/Oバス639上を送り返されるよりはむしろ、I/Oバス639上でINIC622により直接アクセスすることができる。またこれらの効率上の利点は、従来のプロトコルプロセッシングに比較して、AVデータの送信における遅れを大幅に小さくすることができる。

#### 【0073】

リアルタイム音声及び映像通信システムの対象は、通信における遅れやジッタが該システムを介して通信する人々に実質的に知覚できないことである。ジッタは、パケットを受信する遅れの変化によって生じ、これが、音や景色が記録されたテンポと比較してそれらが表示されるテンポに変動を生じさせることになる。上述したパケット化された音声及び/または映像を伝送する際の遅れを減少させる利点は、受信装置でのバッファリングを介してジッタもまた減少させるのに用いることができるが、これは遅れの減少によってジッタを円滑化するための受信装置における時間が増加するからである。AVデータを通信する際の遅れ及びジッタを更に減らすために、INIC622によりUDPデータグラムフラグメントにプリペンドされたIPまたはMACレイヤヘッダは、そのサービス分野での高品質のサービス(QoS)表示を含んでいる。この表示は、ネットワーク604により用いられて、例えば優先的にバンド幅を割り当てかつそれらのフレームについてキューに入れることによって、高QoSフレームの伝送を早めることができる。

#### 【0074】

AVデータを含むフレームがINIC606により受信されると、QoSの表示がINIC606受信論理によってフラグを立てられ、かつパケットがINIC606の高い優先順位の受信キューにバッファされる。INIC606のハードウェア論理によってパケットのヘッダを分類しかつ検証することによって、従来のIP/UDPヘッダのプロセッシ

10

20

30

40

50

ングに比較して、AVデータを受け取る際の遅れが減少する。各データグラムのUDPヘッダはAUDPレイヤに送ることができ、これが前記ヘッダを処理して、関連するソケットをアプリケーションに表示する。次に、前記アプリケーションはINIC606に指示して、そのUDPヘッダに対応するデータをオーディオ/ビデオインターフェース677のデスティネーションに送る。これに代えて、UDPデータグラムに対応する全てのフラグメントが前記受信キューに連結された後、前記データグラムをUDPヘッダ無しでファイルストリームとして前記ソケットに対応するオーディオ/ビデオインターフェース677のデスティネーションに書き込まれる。任意によって、UDPデータグラムは最初にINICメモリの別の部分に格納することができる。AVデータ及び RTPヘッダは、次にオーディオ/ビデオインターフェース677に送られ、そこで復号されてスピーカ678及びディスプレイ682で再生される。 10

#### 【0075】

AVデータフロー全体及び受信したIP/UDPパケットの大部分のプロトコルプロセッシングはINIC606により取扱うことができ、クライアント602のCPUの複数のプロフェッシングサイクルを省略してホストバストラフィック及び割り込みを大幅に減少できることに注意する。更に、INIC606の専用ハードウェア論理によって、汎用CPUよりもより効率的にヘッダを分類することができる。また、AVデータは、INIC602により、最初にI/Oバス675上でプロトコルプロセッシングスタックに送られかつ次にI/Oバス675上でオーディオ/ビデオインターフェース677に送られるのではなく、I/Oバス675上をオーディオ/ビデオインターフェース677に直接提供することができる。 20

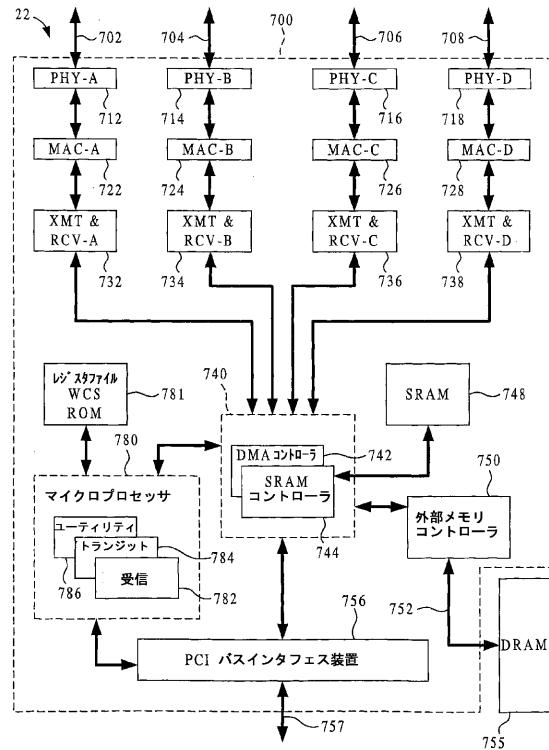

#### 【0076】

図16は、ネットワークインターフェース、ストレージコントローラ及びプロトコルプロセッサの機能を1つのASICチップ703に結合させたINIC22の図を示している。本実施例におけるINIC22は、サーバ及びネットワークストレージアプリケーションのための高速プロトコルプロセッシング用に設計された全2重4チャネル10/100メガビット毎秒(Mbps)のインテリジェントネットワークインターフェースコントローラが提供される。また、INIC22は、パーソナルコンピュータ、ワークステーション、ルータまたはTCP/IP、PPCP/IPまたはSPX/IPXプロトコルが使用されている他のホストに接続することができる。このようなINICの説明は、本願明細書の冒頭部分に挙げた関連特許出願に記載されている。 30

#### 【0077】

INIC22はネットワークコネクタによって4つのネットワークライン702、704、706、708に接続され、これらはツイストペア同軸ケーブルまたは光ファイバのような、それぞれの接続によって、米国カリフォルニア州94538、フリーモント、レイサイドパークウェイ47200のSEQ Technology Incorporatedから市販されているモデル80220/80221イーサネットメディアインタフェースアダプタのような物理的レイヤチェック712、714、716、718を介して媒体独立インターフェース(MII)を提供する多数の異なるコンジットに沿ってデータを運ぶことができる。前記ラインは好ましくは802.3コンプライアントでありかつINICに関連して4つの完全なイーサネットノード、INIC支援の10ベースT、10ベースT2、100ベースT X、100ベースF X及び100ベースT4に加えて将来のインターフェース標準を構成する。物理的レイヤの識別及び初期設定が、ホストドライバの初期設定ルーチンを介して実行される。ネットワークライン702、704、706、708とINIC22との間の接続は、MACサブレイヤの基本機能を実行し、基本的にINICがネットワークライン702、704、706、708にアクセスする時に制御する論理回路を含むMAC装置MAC-A722、MAC-B724、MAC-C726、MAC-D728によって制御される。MAC装置722、724、726、728は、無差別モード、マルチキャストモードまたはユニキャストモードで動作することができ、INICがネットワークモニタとして機能し、ブロードキャストパケット及びマルチキャス 40

トパケットを受信し、かつ各ノードについて複数のMACアドレスを実行できるようにする。また、MAC装置722、724、726、728によって、単一のネットワーク管理プロトコル(SNMP)について使用可能な統計的情報が得られる。

#### 【0078】

MAC装置722、724、726、728はそれぞれ、送受信シーケンサXMT&RCV-A732、XMT&RCV-B734、XMT&RCV-C736、XMT&RCV-D738に接続される。各送受信シーケンサは、メッセージフレームがそのシーケンサを通過する時、幾つかのプロトコルプロセッシングのステップをオンザフライで実行することができる。MAC装置と組み合わせて、送受信シーケンサ732、734、736、738は、ハードウェアにおけるデータリンク、ネットワーク、トランスポート、セッション及び適当な場合にはプレゼンテーション及びアプリケーションレイヤのプロトコルに関するパケットステータスを集めることができ、従来のシーケンシャルソフトウェアエンジンと比較してそのようなプロトコルプロセッシングのための時間を大幅に減少させることができる。送受信シーケンサ732、734、736、738はSRAM及びDMAコントローラ740に接続され、それらはDMAコントローラ742及びSRAM744を有し、これがスタティックランダムアクセスメモリ(SRAM)バッファ748を制御する。SRAM及びDMAコントローラ740は外部メモリコントロール750と対話して、外部メモリバス752を介して、I/Cチップ700の近くに配置されたダイナミックランダムアクセスメモリ(DRAM)バッファ755との間でフレームを送りかつ受信する。DRAMバッファ755は、4MB、8MB、16MBまたは32MBとして構成することができ、かつ任意によりチップ上に配置することができる。SRAM及びDMAコントローラ740は、本実施例ではINIC22とPCIインターフェースバス757との間のインターフェースを管理するPCIバスインターフェース装置(BIU)756であるI/Oブリッジに接続されている。64ビットの多重化BIU756によって、スレイブ及びマスタ機能双方についてPCIバス757との直接のインターフェースが得られる。INIC22は64ビットまたは32ビットのPCI環境で動作することができ、そのいずれの構成においても64ビットのアドレス指定をサポートする。

#### 【0079】

マイクロプロセッサ780がSRAM及びDMAコントローラ740とPCI・BIU756に接続されているマイクロプロセッサ780の命令及びレジスタファイルはSRAMの書き込み可能なオンチップコントロールストア(WCS)及びリードオンリメモリ(ROM)を有するオンチップコントロールストア780に存在する。マイクロプロセッサ780は、入力するフレームを処理し、ホストコマンドを処理し、ネットワークトラフィックを指示しかつPCIバストラフィックを指示することができるプログラマブルステートマシンを提供する。3つのプロセッサが、クロックサイクルごとに1つの命令を発しかつ完了する3段階パイプラインアーキテクチャの共有ハードウェアを用いて実行される。受信プロセッサ782は、基本的に通信を受け取るために用いられるのに対し、送信プロセッサ784は、基本的に全2重通信を容易にする目的で通信を送るために用いられ、ユーティリティプロセッサ786は、PCIレジスタのアクセスを監督しかつ制御することを含む様々な機能を提供する。

#### 【0080】

プロセッサ782、784、786のための命令がオンチップコントロールストア781に存在するので、前記3つのプロセッサの機能は容易に再定義することができ、それによってマイクロプロセッサ780は所定の環境に適応することができる。例えば、受信機能に必要なプロセッシングの量が送信またはユーティリティ機能に必要なそれを上回ることがある。そのような場合、幾つかの受信機能が送信プロセッサ784及び/またはユーティリティプロセッサ786によって実行することができる。それに代えて、追加レベルのパイプライン方式を作つて3つではなく4つまたはそれ以上の仮想プロセッサを設けることができ、その追加レベルに受信機能が指示される。

#### 【0081】

10

20

30

40

50

本実施例のINIC22は、DRAM755のテーブルに保持される最大256のCCBをサポートすることができる。また、しかしながら、順次検索を省略するためにSRAM748には順番がハッシュ状態のCCBインデックスが存在する。一旦ハッシュが生成されると、CCBがSRAMにキャッシュされ、本実施例では60までのCCBがSRAMにキャッシュされる。SRAMにキャッシュされた60のCCBの割り当ては、以下に説明するように、最小使用頻度のレジスタによって操作される。これらキャッシュの配置は、送信プロセッサ784と受信プロセッサ786との間で共有され、それによってより大きなロードを有するプロセッサがより多くのキャッシュバッファを使用することができる。また、前記シーケンサ間で共有されるべき8つのヘッダバッファ及び8つのコマンドバッファが存在する。所定のヘッダまたはコマンドバッファは、特定のCCBバッファに統計的にリンクされないが、そのリンクは各フレームごとにダイナミックだからである。

10

#### 【0082】

図17はパイプラインマイクロプロセッサ780の概観を示しており、受信、送信及びユーティリティプロセッサへの命令がクロックインクリメントI、II及びIIIによって交互に変わるそれにパイプラインの段階に対応する3つのフェーズで実行される。各フェーズは異なる機能について責任を有し、前記3つのプロセッサのそれぞれが各クロックインクリメントの際に異なるフェーズを占有する。各プロセッサは通常コントロールストア781からの異なる命令ストリームに基づいて動作し、それぞれに前記フェーズのそれぞれを通してそれ自身のプログラムカウンタ及びステータスを有する。

20

#### 【0083】

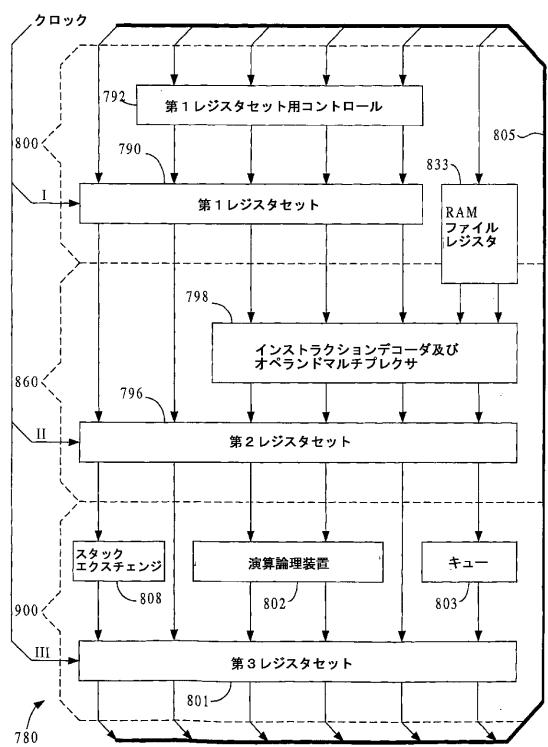

一般にパイプラインマイクロプロセッサの第1インストラクションフェーズ800は、命令を完了しつつ結果をデステイネーションオペランドに格納し、次の命令をフェッチし、かつその次の命令をインストラクションレジスタに格納する。第1のレジスタセット790によって、命令レジスタを含む多数のレジスタが提供され、かつ前記第1レジスタセットのためのコントロール792セットによって、第1レジスタセット790への記憶のためのコントロールが提供される。幾つかのアイテムがコントロール790による変更なしに第1フェーズを通過し、かつその代わりに単に第1レジスタセット790またはRAMファイルレジスタ833内にコピーされる。第2インストラクションフェーズ860はインストラクションデコーダ及びオペランドマルチプレクサ798を有し、これは一般に第1レジスタセット490のインストラクションレジスタ内に格納された命令をデコードし、かつ生成されている全てのオペランドを集め、これは次に第2のレジスタセット796のデコードレジスタに格納される。第3インストラクションフェーズ900で使用される第1レジスタセット790、第2レジスタセット796及び第3レジスタセット801は、図18A～Cにより詳細に示すように、多数の同じレジスタを有する。インストラクションデコーダ及びオペランドマルチプレクサ798は、第1フェーズ806及び第2フェーズ860の双方で動作するRAMファイルレジスタ833の2つのアドレスおよびデータポートから読み出すことができる。プロセッサ780の第3フェーズ900は、演算論理装置(ALU)902を有し、これは一般に第2レジスタセットからのオペランドについて全てのALU動作を実行し、結果を第3レジスタセット801に含まれるリザルトレジスタに格納する。スタックエクスチェンジ808がレジスタスタックを順序付けすることができ、かつキューマネージャ803がプロセッサ780のキューを編成し、その結果が第3レジスタセットに格納される。

30

#### 【0084】

インストラクションは、循環パイプライン805に示されるように第1フェーズに続き、第3フェーズが続く。全ての所定のフェーズにおける組み合わせ遅れを最小にするために、様々な機能が命令実行の3つのフェーズに渡って分散されていることに注意する。本実施例では66MHzの周波数で、各クロックインクリメントは15ナノ秒で完了し、3つの前記プロセッサのそれぞれについて1つの命令を完了するのに合計45ナノ秒を要する。インストラクションフェーズが循環する様子が図18A～Cにより詳細に示されており、各フェーズが異なる図で示されている。

40

50

【 0 0 8 5 】

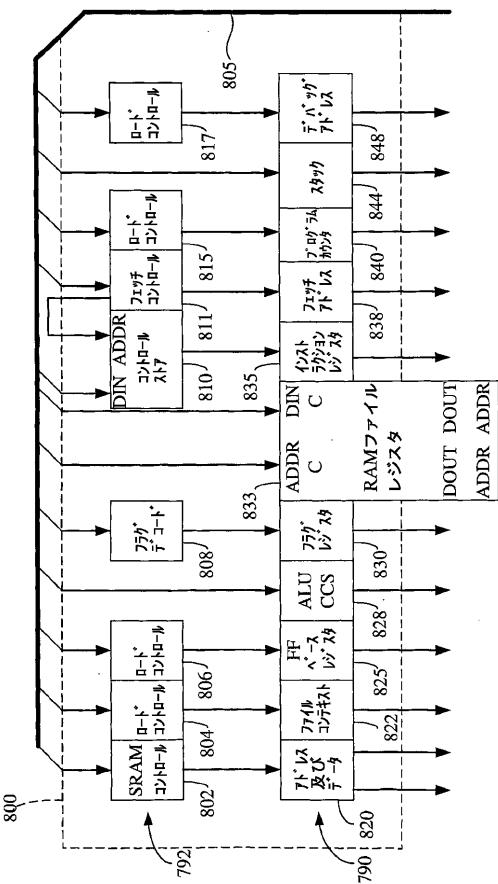

より詳細に言えば、図 18 A は、第 1 フェーズ 8 0 0 の幾つかの特定のハードウェア機能を示しており、一般に第 1 レジスタセット 7 9 0 及び関連するコントロール 7 9 2 を有する。第 1 レジスタセット 7 9 2 のコントロールには、アドレス及び書込みデータを S R A M アドレス及びデータレジスタ 8 2 0 内にロードするための論理コントロールである、 S R A M コントロール 8 2 0 を有する。従って、第 3 フェーズ 9 0 0 からの A L U 9 0 2 の出力は、 S R A M コントロール 8 0 2 によって S R A M アドレス及びデータレジスタ 8 2 0 のアドレスレジスタまたはデータレジスタ内に配置される。同様にロードコントロール 8 0 4 がコンテキストレジスタ 8 2 2 にファイルするファイルのためのコンテキストを書き込むためのコントロールを提供し、かつ別のロードコントロール 8 0 6 が、様々な雑データをフリップフロップレジスタ 8 2 5 に格納するためのコントロールを提供する。キャリービットが設定されているかどうかというような A L U 状態コードが、第 1 フェーズ 8 0 0 において実行される動作無しで、 A L U 状態コードレジスタ 8 2 8 内にロックされる。フラグレコード 8 0 8 がロックを設定するような、フラグレジスタ 8 3 0 内に格納される様々な機能を実行する。

〔 0 0 8 6 〕

RAMファイルレジスタ833は、アドレス及びデータのための1つの書き込みポートとアドレス及びデータのための2つの読み出しポートとを有し、それによって2以上のレジスタが同時に読み出すことができる。上述したように、RAMファイルレジスタ33は基本的に第1及び第2フェーズにまたがるが、それは第1フェーズ800において書き込まれかつ第2フェーズ860において読み出されるからである。コントロールストアインストラクション810によって、この図面には記載されていないコントロールストア781からの新しいデータによる前記プロセッサの再プログラミングが可能になり、前記インストラクションはインストラクションレジスタ830のみ格納される。このためのアドレスがフェッチコントロールレジスタ811において生成され、それによりどのアドレスにフェッチするかが決定され、アドレスがフェッチアドレスレジスタ838に格納される。ロードコントロール831がプログラムカウンタ840の命令を出し、これはコントロールストアのためのフェッチアドレスに良く似たように動作する。3つのレジスタからなる後入れ先出し方式のスタッカ844が、このフェーズで他の動作を受けることなく、第1レジスタセットにコピーされる。最後にデバッグアドレス848のためのロードコントロール817が任意により含まれ、それによって起こり得るエラーの修正が可能になる。

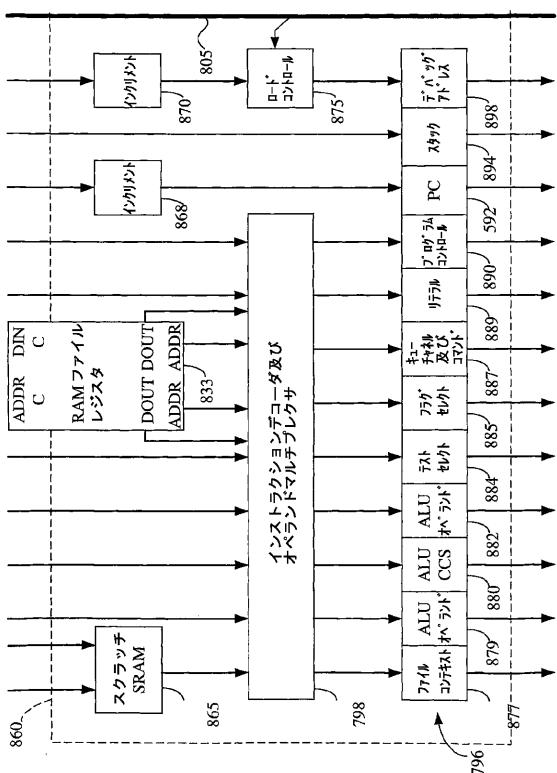

〔 0 0 8 7 〕

図18Bは、RAMファイルレジスタ833からのアドレス及びデータの読み出しを含む第2マイクロプロセッサフェーズ860を示している。スクラッチSRAM865が、最初の2つのフェーズを通過して第3で増分されるレジスタを有する、前記第1レジスタセットのSRAMアドレス及びデータレジスタ820から書き込まれる。スクラッチSRAM865は、スタック844、デバッグアドレス848、及び上述したSRAMアドレス及びデータレジスタを除いて、前記第1レジスタセットからの大部分のレジスタがそうであるように、インストラクションデコーダ及びオペランドマルチプレクサ798によって読み出される。インストラクションレコーダ及びオペランドマルチプレクサ798は、レジスタセット790の各レジスタ及びSRAM865を見て、インストラクションをデコードし、かつ次のフェーズにおける動作のためのオペランドを集め、特に以下のALU902に提供するオペランドを決定する。インストラクションデコーダ及びイペランドマルチプレクサ798の成果は、ALUオペランド879、882、ALU状態コードレジスタ880、及び本実施例では32のキューを制御することができるキューチャネル及びコマンド887レジスタを含む第2レジスタセット796の多数のレジスタに格納される。レジスタセット796のレジスタの幾つかは、デコーダ798により実質的にデコードすることなく、上述したインストラクションレジスタ835からほぼ直接にロードされ、プログラムコントロール890、リテラルフィールド889、テストセレクト884及びフラグ885が含まれる。第1フェーズ800のファイルコンテキスト822のような他のレ

ジスタは、常に第2フェーズ860のファイルコンテキスト877に格納されるが、マルチプレクサ870により集められたオペランドとして取扱うこともできる。スタックレジスタ844は、単にスタックレジスタ894にコピーされる。プログラムカウンタ840はこのフェーズで増分され868、かつレジスタ892に格納される。また、任意のデバッグアドレス848が増分され、870、かつロードコントロール875が各フェーズでのエラーを制御できるようにする目的で、この時点でパイプライン805から供給することができ、その結果がデバッグアドレス898に格納される。

#### 【0088】

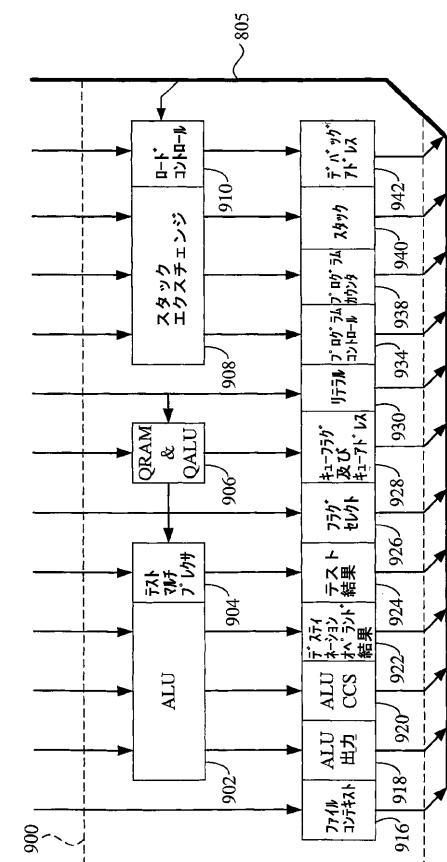

図18Cは、ALU及びキュー動作を含む第3のマイクロプロセッサフェーズ900を示している。ALU902は加算器、優先順位エンコーダ及び他の標準的な論理機能を有する。ALUの結果はレジスタALU出力918、ALU状態コード920及びデスティネーションオペランドリザルト922に格納される。ファイルコンテキストレジスタ925、フラグセレクトレジスタ926及びリテラルフィールドレジスタ930は、先のフェーズ860から単にコピーされるだけである。テストマルチプレクサが設けられて、条件付ジャンプが結果としてジャンプになるかどうかが決定され、その結果がテストリザルトレジスタ924に格納される。テストマルチプレクサ904は、そうではなくフェッチコントロール811のような類似の決定と共に第1フェーズ800で実行することができる。スタックエクスチェンジ808が、プログラムカウンタをスタック879からフェッチし、またはそのスタック上にプログラムカウンタを置くことによってスタックを上下にシフトさせ、その結果がプログラムコントロール934、プログラムカウンタ938及びスタック940レジスタに格納される。SRAMアドレスは、任意によりこのフェーズ900で増分させることができる。このフェーズでもエラーを制御できるようにするために、別のデバッグアドレス942の別のロードコントロール910をこの時点でパイプライン805から強制することができる。この図面では一体に表されているQRAM&QARU906が、キューチャネル及びコマンドレジスタ887から読み出し、SRAMに格納し、かつキューを再編成し、データのキューを管理するのに必要なようにデータ及びポインタを追加しましたは取り外し、結果をテストマルチプレクサ904及びキューフラグ及びキューアドレスレジスタ928に送る。このようにQRAM&QARU906は、従来はCPU上のソフトウェアにより順に実行されていたタスク、前記3つのプロセッサのためのキューを管理する義務を受け、代わりにキューマネージャ906によって加速されかつ実質的にパラレルなハードウェアキューイングが行なわれる。

#### 【0089】

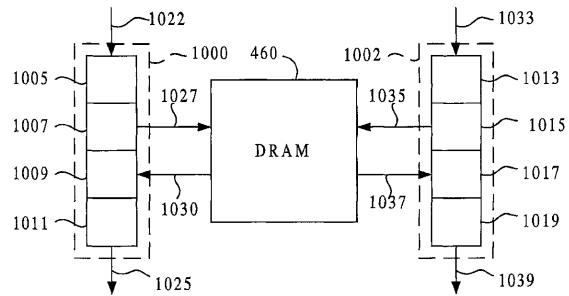

図19は、キューマネージャ906によって管理される32のハードウェアキューの内の2つを示しており、前記キューのそれぞれはSRAMヘッド、SRAM末尾及びTRAM本体内で情報を列に並べる能力をも有し、各キューの拡張及び個々の構成を可能にしている。このように、FIFO1000はSRAM記憶装置1005、1007、1009、1011を有し、それぞれが8バイトで合計32バイトを有するが、これら装置の数及び能力は、他の実施例において変えることができる。同様に、FIFO1002はSRAM記憶装置1013、1015、1017、1019を有する。SRAM装置1005、1007はFIFO1000のヘッドであり、かつ装置1009、1011はそのFIFOの末尾であるのに対し、装置113、115はFIFO1002のヘッドでありかつ装置117、119はそのFIFOの末尾である。FIFO1000の情報は矢印1022で示すように、ヘッドの装置1005または1007内に書き込むことができ、かつ矢印1025で示すように、末尾の装置1011または1009から読み出される。しかしながら、特定の項目はヘッドの装置1005または1007への書き込み及び読み出し両方を行なうことができ、または末尾の装置1009または1011への書き込み及び読み出し両方を行なうことができ、データの移動及び待ち時間を最小にする。同様に、FIFO1002の情報は一般に、矢印1033で示すように、ヘッドの装置1013または1015に書き込まれ、かつ矢印1039で示すように、末尾の装置1017または1019から読み出されるが、そうではなく、書き込まれた同じヘッドまたは末尾の装置から読み出すことが

10

20

30

40

50

できる。

【0090】

S R A M · F I F O 1 0 0 0 、 1 0 0 2 は双方共 D R A M 7 5 5 に接続されており、それら F I F O が実質的に無限に拡張して S R A M ヘッド及び末尾部分が一杯であるような状況を処理できるようにしている。例えば、 Q 0 とラベル付けされた 3 2 のキューの最初のものは、矢印 1 0 2 7 で示すように、 F I F O 7 0 0 のヘッド部分または末尾部分で待ち行列に入れられる代わりに、キューマネージャの指示下で動作する D M A 装置によって、 D R A M 7 5 5 のエントリを待ち行列に入れることができる。 D R A M 7 5 5 に格納されたエントリは、矢印 1 0 3 0 で示すように、 S R A M 装置 1 0 0 9 に戻り、その F I F O の長さ及びフォールスルーランタイムを延長させる。 S R A M から D R A M への転換は、 D R A M の方がより遅くかつ D M A の動作が別の待ち時間を生じさせることから、一般に S R A M が一杯である場合のために取っておかれる。このように Q 0 は、キューマネージャ 8 0 3 によって F I F O 1 0 0 0 及び D R A M 7 5 5 の双方に格納されたエントリで構成することができる。同様に、例えば Q 2 7 に対応する F I F O 1 0 0 0 に行きの情報は、矢印 1 0 3 5 で示すように、 D M A によって D R A M 7 5 5 内に動かすことができる。遅いとはいえコスト効果のよい D R A M 8 0 3 で待ち行列に入れる能力は、初期設定の際にユーザ定義可能なものであり、前記キューを所望のサイズに変更できるようにしている。 D R A M 7 5 5 にキューされた情報は、矢印 1 0 3 7 で示すように、 S R A M 装置 1 0 1 7 に戻される。

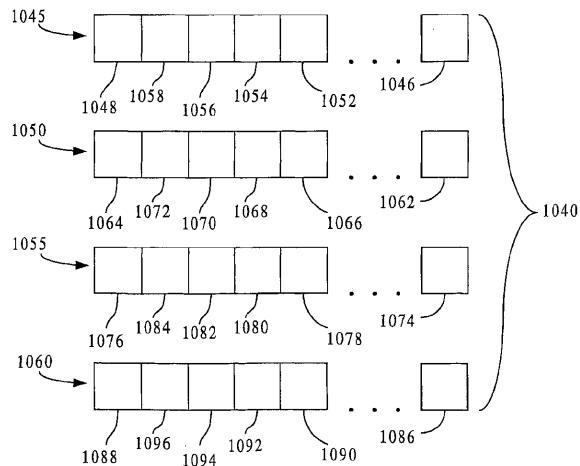

【0091】

3 2 個のハードウェアキューのそれぞれのステータスが、図 2 0 に示すように、4 つの 3 2 ビットのレジスタからなる組み 1 0 4 0 に保持されかつそれからアクセスされ、各レジスタの特定のビットが特定のキューに対応していると好都合である。前記レジスタには、 Q - O u t \_ R e a d y 1 0 4 5 、 Q - I n \_ R e a d y 1 0 5 0 、 Q - E m p t y 1 0 5 5 及び Q - F u l l 1 1 0 6 0 のラベルが付されている。特定のビットが Q - O u t \_ R e a d y レジスタ 1 0 5 0 で設定されると、そのビットに対応するキューは、読み出される準備のできた情報を有するのに対し、同じビットの Q - I n \_ R e a d y 1 0 5 2 レジスタにおける設定は、前記キューが書き込まれる準備ができていることを意味している。同様に、特定のビットの Q - E m p t y レジスタ 1 0 5 5 の肯定的設定がそのビットに対応するキューが空であることを意味するのに対し、特定のビットの Q - F u l l 1 レジスタ 1 0 6 0 における肯定的設定は、そのビットに対応するキューが一杯であることを意味する。このように Q - O u t \_ R e a d y 1 0 4 5 は、ビット 2 7 · 1 0 5 2 、 2 8 · 1 0 5 4 、 2 9 · 1 0 5 6 及び 3 0 · 1 0 5 8 を含むビット 0 · 1 0 4 6 から 3 1 · 1 0 4 8 を有する。 Q - I n \_ R e a d y 1 0 5 0 は、ビット 2 7 · 1 0 6 6 、 2 8 · 1 0 6 8 、 2 9 · 1 0 7 0 及び 3 0 · 1 0 7 2 を含めて、ビット 0 · 1 0 6 2 ~ 3 1 · 1 0 6 4 を有する。 Q - E m p t y 1 0 5 5 は、ビット 2 7 · 1 0 7 8 、 2 8 · 1 0 8 0 、 2 9 · 1 0 8 2 及び 3 0 · 1 0 8 4 を含めて、ビット 0 · 1 0 7 4 ~ 3 1 · 1 0 7 6 を有し、 Q - F u l l 1 1 0 7 0 は、ビット 2 7 · 1 0 9 0 、 2 8 · 1 0 9 2 、 2 9 · 1 0 9 4 及び 3 0 · 1 0 9 6 を含めて、ビット 0 · 1 0 8 6 ~ 3 1 · 1 0 8 8 を有する。

【0092】

F I F O 1 0 0 0 に対応する Q 0 はフリーバッファキューであり、全ての使用可能なバッファのアドレスのリストを保持している。このキューは、前記マイクロプロセッサまたは他のデバイスがフリーバッファのアドレスを必要とする時にアドレス指定され、従って一般に分かる程度の D R A M 7 5 5 を有する。従って、フリーバッファのアドレスを必要とするデバイスは、 Q - 0 を調べてそのアドレスを得ることになる。 F I F O 1 0 0 2 に対応する Q - 2 7 は、受信バッファ記述子のキューである。受け取ったフレームを受信シーケンサにより処理した後、シーケンサは Q - 2 7 に前記フレームの記述子を格納すると思われる。そのような記述子のロケーションが S R A M においてすぐに使用可能な場合には、 Q - I n \_ R e a d y 1 0 5 0 のビット 2 7 · 1 0 6 6 が設定されることになる。そうでない場合には、前記シーケンサはキューマネージャが S R A M から D R A M へ D M A の

移動を開始させるのを待たなければならず、それにより空間を解放して受信記述子を格納する。

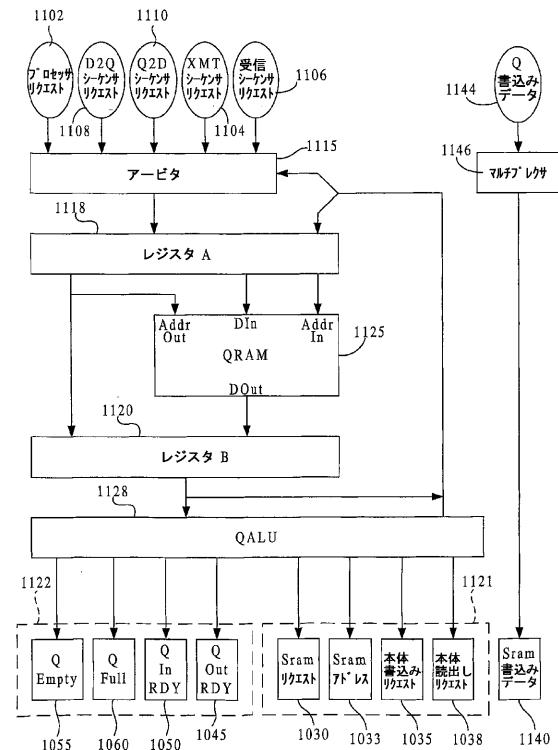

【0093】

S R A M と前記プロセッサ間、送信シーケンサと受信シーケンサ間、及び S R A M と D R A M 間におけるキューエントリの動きを管理するキューマネージャの動作が、図 21 により詳細に示されている。前記キューを利用するリクエストは、プロセッサリクエスト 1102、送信シーケンサリクエスト 1104、及び受信シーケンサリクエスト 1106 を含む。前記キューへの他のリクエストは、D R A M 対 S R A M リクエスト 1086 及び S R A M 対 D R A M リクエスト 1110 であり、これは D R A M と前記キューの S R A M ヘッド部分または末尾部分との間でデータを行ったり来たり動かす際にキューマネージャのために動作する。これら様々にリクエストのどれが次のサイクルでキューマネージャを使用することになるかを決定することは、優先順位論理アービタ 1115 によって処理される。高周波数動作を可能にするために、キューマネージャはパイプライン化され、レジスタ A 1118 及びレジスタ B 1120 によって一時的ストレージが提供されるのに対し、ステータスレジスタ 1112 は、次の更新までステータスを維持する。キューマネージャは、送受信シーケンサが要求する D M A について偶数サイクルを、プロセッサのリクエストのために奇数サイクルを確保する。デュアルコープの Q R A M 1125 が前記キューのそれぞれに関する変数、前記キューの S R A M 状態に対応するヘッドライトポインタ、ヘッドリードポインタ、テールライトポインタ及びテールリードポインタ、並びに前記キューの D R A M 状態及び前記キューのサイズに対応するボディライトポインタ及びボディリードポインタを含む各キューの変数を格納する。

【0094】

アービタ 1115 が実行すべき次の動作を選択した後 Q R A M 825 の変数は Q A L U 1128 により選択された動作に従って設置されかつ変更され、S R A M 読出しリクエスト 1130 または S R A M 書込みリクエスト 1140 が生成される。前記変数が更新されかつ更新されたステータスが Q R A M 1125 に加えてステータスレジスタ 1122 に格納される。前記ステータスはまたアービタ 1115 に供給されて、先に要求された動作が完了したという信号を送り、リクエストの重複を抑制する。ステータスレジスタ 1122 は、4 つのキューレジスタ Q - O u t \_ R e a d y 1045、Q - I n \_ R e a d y 1050、Q - E m p t y 1055 及び Q - F u l l 1106 を更新して、アクセスされた前記キューの新しいステータスを反映する。同様に、D M A を介してそのキューについて S R A M ヘッド部分及び末尾部分にアクセスしつつそれからアクセスされた S R A M アドレス 1133、ボディ書込みリクエスト 1135 及びボディ読出しリクエスト 1138 が更新される。これに代えて、Q 書込みデータ 1144 で示すように、マルチプラクサ 1146 により選択されかつ S R A M 書込みリクエスト 1140 にパイプライン化されたキューに様々な処理を書き込みたい場合がある。S R A M コントローラは、アクセスされた前記キューの末尾部分に書き込みまたはヘッド部分を読み出し、かつ応答を返すことによって、読み出し及び書込みリクエストを処理する。このようにして、様々なキューが用いられかつそれらのステータスが更新される。

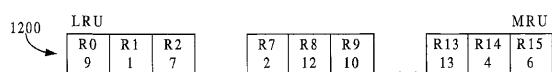

【0095】

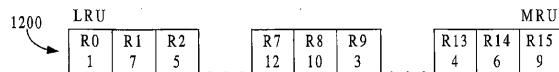

図 22 A ~ D は、どのコンテキストまたは C C B を I N I C キャッシュメモリ内に保持するかを選択するために使用される最小使用頻度レジスタ 1200 を示している本実施例の I N I C は、所定の時間で最大 60 の C C B を S R A M にキャッシュすることができ、従つて新しい C C B がキャッシュされると、古いものは多くの場合捨てなければならず、捨てられる C C B は通常このレジスタ 1200 によって、その時点で最も使用されていない C C B が選択される。本実施例では、最大 256 の C C B のハッシュテーブルが S R A M に保持されるのに対し、最大 256 の満杯の C C B が D R A M に保持される。最小使用頻度レジスタ 1200 は、R 0 ~ R 15 とラベル付けされた 16 の 4 ビットブロックを有し、そのそれぞれが S R A M キャッシュ装置に対応している。初期設定時、前記ブロックには 0 ~ 15 の番号が付され、番号 0 が前記最小使用頻度 ( L R U ) キャッシュ装置を表す

10

20

30

40

50

ブロックに任意に格納され、かつ番号 15 が最大使用頻度 (M R U) キャッシュ装置を表すブロックに格納される。図 22 A は、L R U ブロック R 0 が番号 9 を保持し、かつ M R U ブロック R 15 が番号 6 を保持する任意の時点におけるレジスタ 1200 を示している。現在 S R A M に保持されている別の C C B をキャッシュしようとする場合、L R U ブロック R 0 が読み出されこれは図 22 A において番号 9 を保持し、かつ新しい C C B が番号 9 に対応する S R A M キャッシュ装置に格納される。番号 9 に対応する新しい C C B はこの時点で最大使用頻度 C C B であるから、番号 9 が、図 22 B に示すように、M R U ブロックに格納される。他の番号は、番号 1 を L R U ブロックに残して、全て 1 レジスタ ブロックずつ左へシフトされる。番号 9 に対応して S R A M 装置に以前キャッシュされていた C C B は、速度は遅いがよりコスト効率的な D R A M に移動される。

10

#### 【 0096 】

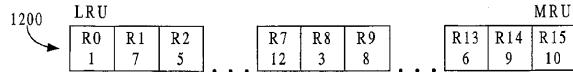

図 22 C は、使用された次の C C B がすでに S R A M にキャッシュされた結果を示している。この実施例では、番号 10 に対応する S R A M 装置に C C B がキャッシュされており、従ってその C C B を用いた後、番号 10 が M R U ブロックに格納される。以前により多く使用されていた番号 10 以外の番号のみ (レジスタ ブロック R 9 ~ R 15) が、番号 1 を L R U ブロックに残して左側へシフトされる。このようにして、I N I C は S R A M キャッシュ内に最もアクティブな C C B を保持する。

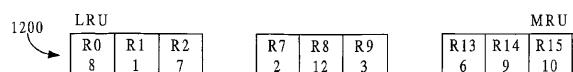

#### 【 0097 】

ある場合には、使用されている C C B は、制限されたキャッシュメモリ内に保持することが望ましくないものである。例えば、閉じつつあることが分かっているコンテキストについて C C B をキャッシュしないことが好ましく、従って他のキャッシュされた C C B を S R A M により長く留めることことができる。この場合には、デキャッシュ可能な C C B を保持するキャッシュ装置を表す番号が、M R U ブロック R 15 ではなくむしろ L R U ブロック R 0 に格納され、従ってデキャッシュ可能な C C B は、L R U ブロック R 0 に保持される番号に対応する S R A M 装置内にキャッシュされた新しい C C B の使用の直後に置き換えられることになる。図 22 D は、番号 8 (図 22 C においてブロック R 9 にあったもの) が使用されかつその後閉じることになっている C C B に対応する場合を示している。この場合、番号 8 はブロック R 9 から取り外され、かつ L R U ブロック R 0 内に格納される。先にブロック R 9 の左側に格納されていた全ての数 (R 1 ~ R 8) は、ここで 1 ブロック右側へシフトされる。

20

#### 【 0098 】

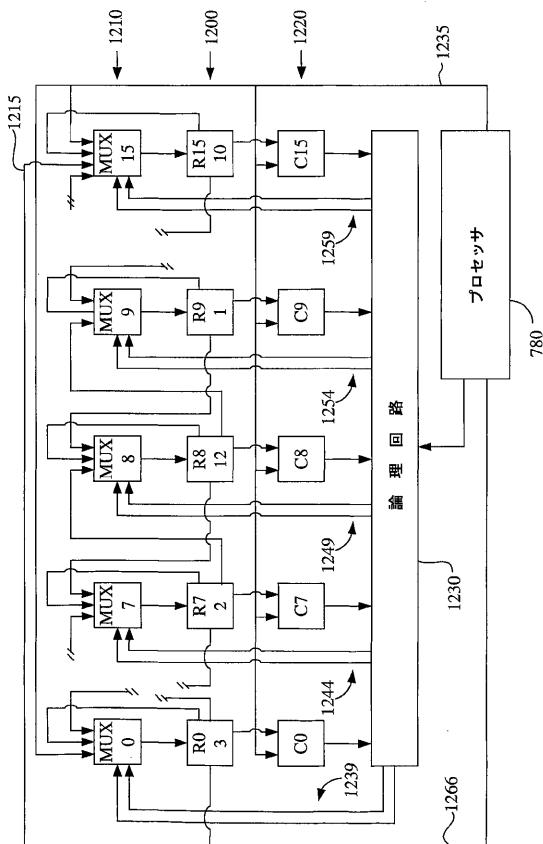

図 23 は、最小使用頻度レジスタ 1200 を動作するのに用いられる論理装置のいくつかを示している。16 個の 3 または 4 入力マルチプレクサ 1210 のアレイ、その内のマルチプレクサ MUX 0、MUX 7、MUX 8、MUX 9 及び MUX 15 のみが簡単にするために示されているが、最小使用頻度レジスタ 1200 の対応する 16 個のブロックに接続された出力を有する。例えば、MUX 0 の出力はブロック R 0 に格納され、MUX 7 の出力はブロック R 7 に格納される等である。各レジスタ ブロックの値は、ブロック番号をシフトする際に使用するために、その対応するマルチプレクサの入力及び両側に隣接するマルチプレクサの入力に接続されている。例えば、R 8 に格納される番号は MUX 7、MUX 8 及び MUX 9 の入力に供給される。MUX 0 及び MUX 15 はそれぞれ隣接するブロックを 1 つだけ有し、それらマルチプレクサの特別の入力がそれぞれ L R U 及び M R U ブロックの選択のために使用される。MUX 15 は 4 入力マルチプレクサとして図示されており、入力 1215 が R 0 に格納された番号を供給する。

30

#### 【 0099 】

16 個のコンパレータ 1220 からアレイはそれぞれ、最少使用頻度レジスタ 1200 の対応するブロックに格納された値を受け取る。また、各コンパレータは、ライン 1235 に沿ってプロセッサ 470 から信号を受け取り、それによってプロセッサ 470 により送られたものと整合する番号を有するレジスタ ブロックが、論理回路 1230 に真を出力するのに対し、他の 15 個のコンパレータが偽を出力する。論理回路 1230 が、マルチプレクサへの入力を選択しつつ従ってレジスタ ブロック 番号のシフトを制御するために、

40

50

前記マルチプレクサのそれぞれに繋がる一対の選択ラインを制御する。このように、選択ライン 1239 が MUX0 を制御し、選択ライン 1244 が MUX7 を制御し、選択ライン 1249 が MUX8 を制御し、選択ライン 1254 が MUX9 を制御し、かつ選択ライン 1259 が MUX15 を制御する。

#### 【0100】

CCB を使用しようとする時、プロセッサ 470 は、CCB が現在 16 個のキャッシュ装置の 1 つに保持されている CCB と整合するかどうかを調べる。整合が認められると、前記プロセッサは、そのキャッシュ装置に対応するロック番号、例えば番号 12 と共に信号をライン 1235 に沿って送る。コンパレータ 1220 は、そのライン 1235 からの前記信号をロック番号と比較し、かつコンパレータ C8 が前記信号に整合するロック R8 について真を出力するのに対し、他の全てのコンパレータは偽を出力する。論理回路 1230 は、プロセッサ 470 からの制御下で、選択ライン 1259 を用いて、MUX15 についてライン 1235 からの入力を選択し、番号 12 を MRU ブロック R15 に格納する。また、論理回路 1230 は、MUX15 は別にして、MUX8 及びそれより上位のマルチプレクサに関する各対の選択線に信号を送り、MUX8 及びそれより上位の各マルチプレクサへの入力として、1 ブロック右側のレジスタブロック (R9 ~ R15) に格納されていた値を選択することによって、その出力を 1 ブロック左側へシフトする。MUX8 の左側にあるマルチプレクサの出力は、一定に選択される。

10

#### 【0101】

他方、プロセッサ 470 が 16 個のキャッシュ装置の中で前記 CCB との整合を見つけることができない場合には、前記プロセッサはライン 1266 に沿って LRU ブロック R0 から読み出しを行い、LRU ブロックに対応するキャッシュを識別し、かつそのキャッシュに格納されていたデータを DRAM に書き込む。R0 に格納されていた番号、本実施例では番号 3、が MRU ブロック R15 に格納するために MUX15 への入力 1215 として選択ライン 1259 により選択される。他の 15 のマルチプレクサは、そのそれぞれのレジスタブロックに、各レジスタブロックのすぐ右側に格納されていた番号を出力する。

20

#### 【0102】

前記プロセッサが CCB を使用後にキャッシュから取り外したい場合には、MRU ブロック R15 よりもむしろ LRU ブロック R0 が、その CCB を保持するキャッシュ装置に対応する番号を置くために選択される。SRAM から取り外すために LRU ブロック R0 に置かれるべき CCB に対応する数 (例えば、ブロック R9 に保持される番号 1) は、プロセッサ 470 によりライン 1235 に沿って送られ、これはコンパレータ C9 によって整合される。前記プロセッサは論理回路 1230 に指示して、ライン 1239 で MUX0 への入力 1235 を選択することによって、番号 1 を R0 に入力させる。MUX9 への選択ライン 1254 が入力として、レジスタブロック R8 に保持されている番号を選択し、それによって R8 からの番号が R9 に格納される。R0 と R9 間の他のレジスタブロックにより保持されている番号が同様にして右側へシフトされ、R9 の右側のレジスタブロックの番号が一定のまま残される。これによって、多くのサイクルについて閉じた CCB を保持することから不十分なキャッシュメモリが解放され、それらの識別番号がレジスタブロックを介して MRU から LRU ブロックへ移動する。

30

#### 【0103】

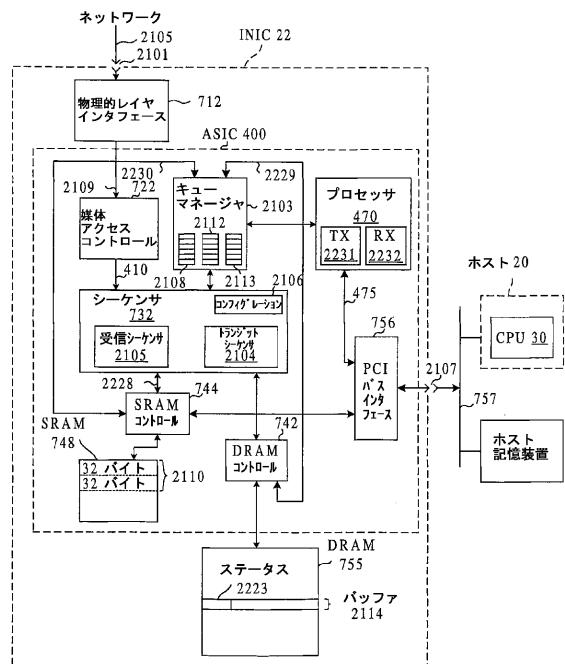

図 24 は、INIC の詳細を追加して示しており、この記載では单一のネットワークシステムに焦点を置いている。INIC22 は、PHY チップ 712、ASIC チップ 700 及び DRAM 755 を有する。PHY チップ 712 は INIC カード 22 をネットワークコネクタ 2101 を介してネットワークライン 2105 に接続している。INIC22 は、カードエッジコネクタ 2107 及び PCI バス 757 を介してホストの CPU (例えば、図 1 のホスト 20 の CPU30) に接続されている。ASIC チップ 700 は、媒体アクセスコントロール (MAC) 装置 722、シーケンサブロック 732、SRAM コントロール 744、SRAM 748、DRAM コントロール 742、キューマネージャ 803、プロセッサ 780 及び PCI バスインターフェース装置 756 を有する。シーケンサブロ

40

50

ック 732 は、送信シーケンサ 2104、受信シーケンサ 2105、及びコンフィグレーションレジスタ 2106 を有する。MAC デスティネーションアドレスはコンフィグレーションレジスタ 2106 に格納される。プロセッサ 780 により実行されるプログラムコードの一部分が ROM ( 図示せず ) に保有され、かつ一部分が書き込み可能なコントロールストア SRAM ( 図示せず ) に送られている。前記プログラムは、初期設定時にホスト 20 から書き込み可能なコントロールストア SRAM にダウンロードすることができる。

#### 【 0104 】

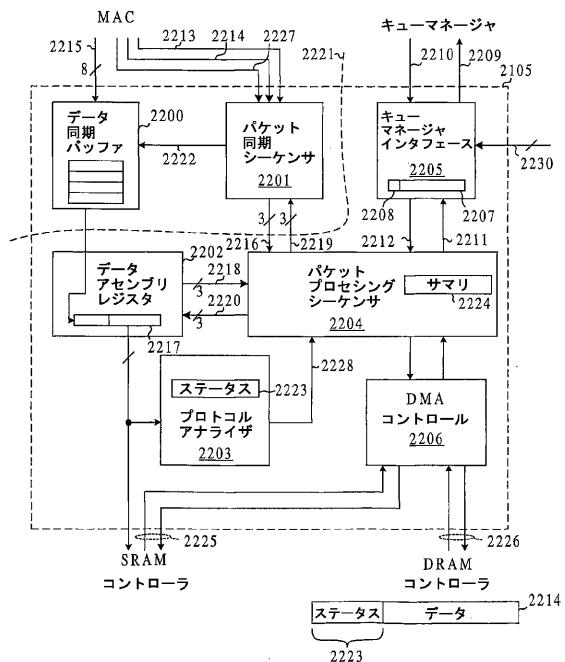

図 25 は、図 24 の受信シーケンサ 2105 のより詳細な線図である。受信シーケンサ 2105 は、データ同期バッファ 2200、パケット同期シーケンサ 2201、データアセンブリレジスタ 2202、プロトコルアナライザ 2203、パケットプロセッシングシーケンサ 2204、キューマネージャインタフェース 2205、及びダイレクトメモリアクセス ( DMA ) コントロールブロック 2206 を有する。パケット同期シーケンサ 2201 及びデータ同期バッファ 2200 は MAC 722 のネットワーク同期式クロックを利用し、受信シーケンサ 2105 の残りの部分は固定周波数のクロックを利用する。破線 2221 は、クロックのドメイン境界を示している。

#### 【 0105 】

図 24 及び図 25 の受信シーケンサ 2105 の動作について、ネットワークライン 702 からの TCP / IP パケットの NIC 22 上での受信に関連して説明する。初期設定時には、プロセッサ 780 が DRAM 755 をバッファに区分する。受信シーケンサ 2105 が DRAM 755 のバッファを用いて、到来するネットワークパケットデータを前記パケットのステータス情報と共に格納する。プロセッサ 780 は各バッファについて 32 ビットのバッファ記述子を作成する。バッファ記述子は、その関連するバッファの DRAM におけるサイズ及びロケーションを示す。プロセッサ 780 は、これらのバッファ記述子をキューマネージャ 803 に書き込むことによって、「フリーバッファキュー」 2108 上にバッファ記述子を置く。キューマネージャ 803 は、「フリーバッファキュー」 2108 を含む複数のキューを保持する。この実施例では、様々なキューのヘッド部分及び末尾部分が SRAM 748 に置かれ、前記キューの中間部分が DRAM 755 に置かれる。

#### 【 0106 】

ライン 2229 は、リクエストライン及びアドレスラインに関連するリクエストメカニズムを有する。同様にライン 2230 は、リクエストライン及びアドレスラインに関係するリクエストメカニズムを有する。キューマネージャ 803 はライン 2229、2230 を用いて、DRAM から SRAM へまたは SRAM から DRAM へキュー情報を転送するリクエストを出す。

#### 【 0107 】

受信シーケンサのキューマネージャインタフェース 2205 は、パケットプロセッシングシーケンサ 2204 による使用のために、常にフリーバッファ記述子 2207 を保持しようとする。ビット 2208 は、フリーバッファ記述子 2207 がパケットプロセッシングシーケンサ 2204 により使用可能であることを表示するレディビットである。キューマネージャインタフェース 2205 がフリーバッファ記述子を持っていない ( ビット 2208 が設定されていない ) 場合には、キューマネージャインタフェース 2205 はリクエストライン 2205 を介してキューマネージャ 803 から 1 を要求する。( リクエストライン 2209 は実際、動作がキューへの書き込みである場合、リクエスト、キュー ID、読み出し / 書込み信号及びデータを通信するバスである。 )

応答の際、キューマネージャ 803 は「フリーバッファキュー」 2108 の末尾部分からフリーバッファ記述子を検索し、次に応答ライン 2210 上の応答信号を介してキューマネージャインタフェース 2205 に知らせる。キューマネージャインタフェース 2205 が応答信号を受け取ると、キューマネージャインタフェース 2205 はフリーバッファ記述子 2207 をロードし、かつレディビット 2208 を設定する。前記フリーバッファ記述子が SRAM 748 のフリーバッファキューの末尾部分にあったことから、キューマネージャインタフェース 2205 は、実際は SRAM コントロールブロック 744 の読み出し

10

20

30

40

50

データバス 2228 からフリーバッファ記述子 2207 を受け取る。パケットプロセッシングシーケンサ 2204 は、リクエストライン 2211 を介してフリーバッファ記述子 2207 を要求する。キューマネージャインタフェース 2205 がフリーバッファ記述子 2207 を検索し、かつフリーバッファ記述子 2207 がパケットプロセッシングシーケンサによる利用が可能である場合、キューマネージャインタフェース 2205 はグラントライン 2212 を介してパケットプロセッシングシーケンサ 2204 に知らせる。この処理によって、フリーバッファ記述子はパケットプロセッシングシーケンサ 2204 による使用が可能になり、かつ受信シーケンサ 2105 が到来するパケットを処理できる状態となる。

## 【0108】

10

次に、TCP/IP パケットがネットワークコネクタ 2101 及び物理的レイヤインタフェース (PHY) 712 を介してネットワークライン 2105 から受け取られる。PHY 712 は、前記パケットを MAC 722 に媒体独立インタフェース (MII) パラレルバス 2109 を介して供給する。MAC 722 は前記パケットの処理を開始し、かつパケットの開始部分が受信されていることを示す「パケットの開始」信号をライン 2213 上にアサートする。データのバイトが MAC に受信されかつ MAC 出力 2215 において利用可能になると、MAC 722 は「データ有効」信号をライン 2214 上にアサートする。前記「データ有効」信号を受け取ると、パケット同期シーケンサ 2201 がロード信号ライン 2222 を介してデータ同期バッファ 2200 を指示し、データライン 2215 から受け取ったバイトをロードする。データ同期バッファ 2200 は 4 バイトの深さを有する。次に、パケット同期シーケンサ 2201 がデータ同期バッファの書き込みポインタを増分させる。このデータ同期バッファの書き込みポインタは、ライン 2216 を介してパケットプロセッシングシーケンサ 2204 に利用可能となる。データライン 2215 から連続するデータのバイトは、このようにしてデータ同期バッファ 2200 内に刻時される。

20

## 【0109】

ライン 2219 上で利用可能なデータ同期バッファ読出しポインタがパケットプロセッシングシーケンサ 2204 によって保持される。パケットプロセッシングシーケンサ 2204 は、ライン 2216 上のデータ同期バッファ書き込みポインタをライン 2219 上のデータ同期バッファ読出しポインタと比較することによって、データ同期バッファ 2200 においてデータが使用可能であることを決定する。

30

## 【0110】

データアセンブリレジスタ 2202 は 16 バイト長のシフトレジスタ 2217 を有する。このレジスタ 2217 は、一度に 1 バイトが順にロードされ、かつパラレルにアンロードされる。データがレジスタ 2217 にロードされると、書き込みポインタが増分される。この書き込みポインタが、ライン 2218 を介してパケットプロセッシングシーケンサ 2204 に利用可能となる。同様に、データがレジスタ 2217 からアンロードされると、パケットプロセッシングシーケンサ 2204 により保持された読出しポインタが増分される。この読出しポインタは、ライン 2220 を介してデータアセンブリレジスタ 2202 に利用可能である。従って、パケットプロセッシングシーケンサ 2204 は、ライン 2218 上の書き込みポインタをライン 2220 上の読出しポインタと比較することによって、レジスタ 2217 に利用可能な余裕があるかどうかを決定することができる。

40

## 【0111】

レジスタ 2217 に利用可能な余裕があるとパケットプロセッシングシーケンサ 2204 が決定した場合、パケットプロセッシングシーケンサ 2204 はデータアセンブリレジスタ 2202 に命令して、データ同期バッファ 2200 からデータのバイトをロードする。データアセンブリレジスタ 2202 は、ライン 2218 上のデータアセンブリレジスタ書き込みポインタを増分し、かつパケットプロセッシングシーケンサ 2204 がライン 2219 上のデータ同期バッファ読出しポインタを増分する。レジスタ 2217 にシフトされたデータは、チェックサムを検証しつつ「ステータス」情報 2223 を生成するプロトコルアナライザ 2203 によってレジスタ出力で調べられる。

50

## 【0112】

DMAコントロールブロック2206は、64バイト受信 FIFO2110を介して情報をレジスタ2217からバッファ2114へ動かす責任を有する。DMAコントロールブロック2206は、64バイトのSRAM748を用いて受信 FIFO2110を2つの32バイトピンポンバッファとして実行する。DMAコントロールブロック2206は、書き込みポインタ及び読み出しポインタを用いて前記受信 FIFOを実行する。転送されるべきデータがレジスタ2217において利用可能でありかつ空間が FIFO2110において利用可能であると、DMAコントロールブロック2206は、ライン2225を介してSRAMコントローラ744にSRAM書き込みリクエストをアサートする。次にSRAMコントローラ744がデータをレジスタ2217から FIFO2110へ移動させ、かつライン2225を介して応答信号をDMAコントロールブロック2206へアサートする。ここで、DMAコントロールブロック2206が受信 FIFO書き込みポインタを増分させ、かつデータアセンブリレジスタ読み出しポインタを増分させる。

## 【0113】

32バイトのデータが受信 FIFO2110に預けられていると、DMAコントロールブロック2206はライン2226を介してDRAMコントローラ742にDRAM書き込みリクエストを示す。この書き込みリクエストは、DRAMリクエストアドレスに関して「バッファロードカウント」でOR演算したフリーバッファ記述子2207と、SRAM読み出しあドレスに関する受信 FIFO読み出しポインタとから構成される。受信 FIFO読み出しポインタを用いて、DRAMコントローラ742はSRAM744に読み出しリクエストをアサートする。SRAMコントローラ744は、SRAM748の受信 FIFO2110から表示されたデータを戻しつつ応答信号をアサートすることによって、DRAMコントローラ742に応答する。DRAMコントローラ742は、前記データをDRAM書き込みデータレジスタに格納し、DRAMリクエストアドレスをDRAMアドレスレジスタに格納し、かつ応答DMAコントロールブロック2206にアサートする。次に、DMAコントロールブロック2206は、受信 FIFO読み出しポインタをデクリメントする。次に、DRAMコントローラ742は、前記データをDRAM書き込みデータレジスタからバッファ2114へ移動させる。このようにして、連続的な32バイトのチャンクからなるデータがSRAM748に格納されるので、DRAMコントロールブロック2206は、これら32バイトのチャンクからなるデータを一度にSRAM748からDRAM755のバッファ2214に移動させる。32バイトチャンクのデータをこのようにしてDRAM755に転送することによって、DRAMの比較的効率的なバーストモードを用いて、データをDRAMに書き込むことができる。

## 【0114】

パケットデータは、全てのパケットデータが受け取られるまで、ネットワークライン2105からバッファ2114へ流れ続ける。次に、MAC722は、ライン2227上に「フレーム終了」（即ちパケットの終了）信号をアサートすることによって、かつ最後のパケットステータス（MACパケットステータス）をパケット同期シーケンサ2204に示すことによって、到来するパケットが完了したことを表す。次にパケットプロセッシングシーケンサ2204が、最後にバッファ2114に転送するためにステータス2223（「プロトコルアナライザステータス」とも称する）及びMACパケットステータスをレジスタ2217へ移動させる。前記パケットの全データがバッファ2214内に置かれた後、ステータス2223及びMACパケットステータスは、図23に示すように関連するデータにプリペンドされて格納されるように、バッファ2214に転送される。

## 【0115】

全データ及びステータスがバッファ2114に転送された後、パケットプロセッシングシーケンサ2204が、フリーバッファ記述子2207、バッファロードカウント、MAC・ID及びステータスピット（「アテンションビット」とも称する）を連結することによって、サマリ2224（「受信パケット記述子」とも称する）を作成する。前記アテンションビットが1である場合、前記パケットは「高速バス対象」でなく、前記アテンション

ビットが 0 である場合には、前記パケットは「高速バス対象」となる。アテンションビットの値は、さもなければプロセッサ 780 が前記パケットが「高速バス対象」であるかどうかを決定するためにしなければならない多大な量の処理の結果を表す。例えば、アテンションビットが 0 であることは、前記パケットが TCP プロトコル及び IP プロトコルの両方を用いていることを示している。この多大な量の処理を事前にハードウェアで実行しつつ次に結果をアテンションビットにエンコードすることによって、パケットが本当の「高速バスパケット」であるかどうかに関してプロセッサ 780 が次に行なう決定が加速される。

#### 【 0116 】

次に、パケットプロセッシングシーケンサ 2204 がサマリ 2224 に関連するレディビット（図示せず）を設定し、かつサマリ 2224 をキューマネージャインタフェース 2205 に提示する。次にキューマネージャインタフェース 2205 が、「サマリキュー」2112（「受信記述子キュー」とも称する）のヘッド部分に書き込みを要求する。キューマネージャ 803 はこのリクエストを受け取り、サマリ 2224 をサマリキュー 2212 のヘッドに書き込み、かつライン 2210 を介してキューマネージャインタフェースに応答信号をアサートする。キューマネージャインタフェース 2205 が前記応答を受け取ると、キューマネージャインタフェース 2205 は、前記サマリに関連するレディビットをクリアすることによって、サマリ 2224 がサマリキュー 2212 にあることをパケットプロセッシングシーケンサ 2204 に知らせる。また、パケットプロセッシングシーケンサ 2204 は、MAC パケットステータスと MAC・ID を連結することによって、前記パケットに関する追加のステータス情報（「ベクタ」とも称する）を生成する。パケットプロセッシングシーケンサ 2204 は、このベクタに関連するレディビット（図示せず）を設定し、かつこのベクタをキューマネージャインタフェース 2205 に提示する。キューマネージャインタフェース 2205 及びキューマネージャ 803 は、上述したようにサマリ 2224 がサマリキュー 2112 のヘッドに書き込まれたのと同様にして、このベクタを協同して「ベクタキュー」2113 のヘッドに書き込む。前記パケットのベクタがベクタキュー 2113 に書き込まれると、キューマネージャインタフェース 2205 は、前記ベクタに関連するレディビットをリセットする。

#### 【 0117 】

サマリ 2224（バッファ 2114 を指すバッファ記述子を含む）が一旦サマリキュー 2112 に置かれかつパケットデータがバッファ 2144 に置かれると、プロセッサ 780 はサマリ 2224 をサマリキュー 2112 から検索して、前記「アテンションビット」を調べることができる。

#### 【 0118 】

サマリ 2224 からのアテンションビットが数字の 1 である場合、プロセッサ 780 は、前記パケットが「高速バス対象」でないと決定し、プロセッサ 780 はパケットヘッダを調べる必要がない。バッファ 2114 からのステータス 2223（最初の 16 バイト）のみが SDRAM に DMA 転送され、従ってプロセッサ 780 がこれを調べることができる。ステータス 2223 は、前記パケットがホストに転送されることになつてない種類のパケットであること（例えば、ホストが受け取るようにレジスタされていないマルチパストフレーム）を示す場合には、前記パケットは捨てられる（即ち、ホストに送られない）。ステータス 2223 が、前記パケットがホストに転送されるべきでないタイプのパケットであることを示していない場合には、パケット全体（ヘッダ及びデータ）が、「低速バス」移動及びホスト 20 のプロトコルスタックによるネットワークレイヤプロセッシングのためにホスト 20 のバッファに送られる。

#### 【 0119 】

前記アテンションビットが 0 である場合、プロセッサ 780 は、前記パケットが「高速バス対象」であることを決定する。プロセッサ 780 が前記パケットを「高速バス対象」と決定した場合、プロセッサ 780 は前記サマリからのバッファ記述子を用いて、バッファ 2114 からの最初の約 96 バイトの情報を DRAM 755 から SDRAM 748 の部分内

10

20

30

40

50

にDMA転送し、それによってプロセッサ780がこれを調べることができる。この最初の約96バイトは、IPヘッダのIPソースアドレス、IPヘッダのIPデスティネーションアドレス、TCPヘッダのTCPソースアドレス及びTCPヘッダのTCPデスティネーションアドレスと共に、ステータス2223を含む。IPヘッダのIPソースアドレス、IPヘッダのIPデスティネーションアドレス、TCPヘッダのTCPソースアドレス及びTCPヘッダのTCPデスティネーションアドレスは一緒になって、前記パケットが関連する1つの接続コンテキスト(TCB)を独自に定義する。プロセッサ780は、これらのTCP及びIPヘッダのアドレスを調べ、前記パケットの接続コンテキストを決定する。次に、プロセッサ780は、INIC22の制御下にある接続コンテキストのリストを調査し、前記パケットがINIC22の制御下で接続コンテキスト(TCB)に関連しているかどうかを決定する。

#### 【0120】

前記接続コンテキストが前記リストにない場合、前記「高速バス対象」パケットは「高速バスパケット」でないと決定される。そのような場合、パケット全体(ヘッダ及びデータ)は、ホスト20のプロトコルスタックによる「低速バス」処理のためにホスト20のバッファに転送される。

#### 【0121】