Europäisches Patentamt

European Patent Office

Office européen des brevets

(11) **EP 1 471 536 A2**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

27.10.2004 Bulletin 2004/44

(51) Int Cl.<sup>7</sup>: **G11C 11/16**, H01F 10/32, H01F 41/30

(21) Application number: 04252197.1

(22) Date of filing: 15.04.2004

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IT LI LU MC NL PL PT RO SE SI SK TR Designated Extension States:

AL HR LT LV MK

(30) Priority: 23.04.2003 KR 2003025716

(71) Applicant: Samsung Electronics Co., Ltd. Suwon-si, Gyeonggi-do (KR)

(72) Inventors:

Park, Sang-jin

Pyeongtaek-si Gyeonggi-do (KR)

Kim, Tae-wan Yongin-si, Gyeonggi-do (KR)

Lee, Jung-hyun

Yongin-si Gyeonggi-do (KR)

Park, Wan-jun Gangnam-gu Seoul (KR)

• Song, I-hun Bundang-gu Seongnam-si Gyeonggi-do (KR)

(74) Representative: Greene, Simon Kenneth

Elkington and Fife LLP, Prospect House, 8 Pembroke Road

Sevenoaks, Kent TN13 1XR (GB)

(54) Magnetic random access memory cell comprising an oxidation preventing layer and method of manufacturing the same

(57) A magnetic random access memory (MRAM) having middle oxide layers formed by a hetero-method and a method of manufacturing the same are provided. The MRAM including a magnetic tunneling junction (MTJ) formed of a lower magnetic layer, an oxidation

preventing layer, a tunneling oxide layer, and an upper magnetic layer. The tunneling oxide layer is formed by an atomic layer deposition (ALD) method, and the other material layers, particularly the oxidation preventing layer, are formed by a method other than the ALD method.

# FIG. 9

EP 1 471 536 A2

#### **Description**

**[0001]** The present invention relates to a semiconductor memory device and a method of manufacturing the same, and more particularly, to a magnetic random access memory (MRAM) comprising a middle oxide layer formed by a hetero-method and a method of manufacturing the MRAM.

**[0002]** A magnetic random access memory (MRAM) is a memory device for reading and writing data using a phenomenon that resistance values of a magnetic tunneling junction (MTJ) layer changes according to the magnetization direction of the two magnetic layers consisting the MTJ layer.

**[0003]** The MRAM can be highly integrated and can perform high-speed operations like a dynamic random access memory (DRAM) and a synchronous dynamic random access memory (SRAM) and has a non-volatile characteristic to store data for a long time without a refresh process.

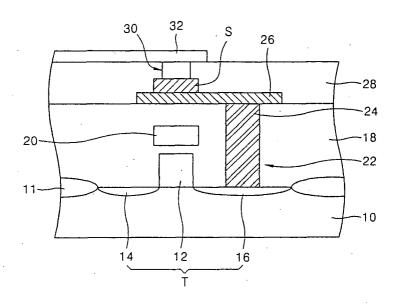

**[0004]** FIG. 1 is a cross-sectional view illustrating a general structure of an MRAM. As illustrated in FIG. 1, in general, an MRAM includes a transistor T performing a switching process and one MTJ layer S which is electrically connected to the transistor T and where data such as "0" and "1" is written.

[0005] Referring to FIG. 1, in a conventional method of manufacturing the MRAM, a gate stacking material 12, which includes a gate electrode, and the source and drain areas 14 and 16 at both sides of the gate stacking material 12 are respectively formed on a semiconductor substrate 10. The gate stacking material 12 and source and drain areas 14 and 16 together form the transistor T which performs the switching process on the semiconductor substrate 10, and a reference numeral 11 indicates a field oxide layer. Then, an interlayer insulating layer 18 covering the transistor T is formed on the semiconductor substrate 10. After forming the interlayer insulating layer 18, a data line 20 covered by the interlayer insulating layer 18 in an upper portion of the gate stacking material 12 is formed to be parallel with the gate stacking material 12. A contact hole 22 exposing the drain area 16 in the interlayer insulating layer 18 is formed. Then, the contact hole 22 is filled with a conductive plug 24, and a pad conductive layer 26 contacting the top surface of the conductive plug 24 is formed on the interlayer insulating layer 18. More specifically, the pad conductive layer 26 is formed over the data line

**[0006]** In addition, the MTJ layer S is formed on an area of the pad conductive layer 26, which corresponds to the data line 20, and a second interlayer insulating layer 28 covering the pad conductive layer 26 and the MTJ layers is formed on the material resulting from the formation of the MTJ layer S. A via hole 30 exposing an upper layer of the MTJ layer S is formed in the second interlayer insulating layer 28. A bit line 32 filling the via hole 30 is formed on the second interlayer insulating lay-

er 28 in a vertical direction to the gate electrode and the data line 20.

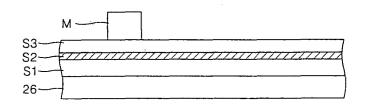

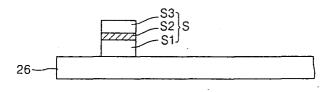

**[0007]** The MTJ layer S included in the MRAM of FIG. 1 is formed in a way shown in FIGS. 2 and 3.

[0008] That is, as shown in FIG. 2, a lower magnetic layer S1, a tunneling barrier layer S2, and an upper magnetic layer S3 are sequentially formed in a predetermined area of the pad conductive layer 26, and then, a mask pattern M, limiting an area in which the MTJ layer S will be formed, is formed on an upper magnetic layer S3

**[0009]** The tunneling barrier layer S2 is formed by depositing a metal layer such as an aluminum layer Al on the lower magnetic layer S1 and oxidizing the metal layer. In order to oxidize the metal layer, one of plasma oxidation, UV oxidation, natural oxidation, and ozone oxidation may be used.

**[0010]** Thereafter, as shown in FIG. 3, the MTJ layers are completely formed on the pad conductive layer 26 by etching the above sequentially formed material layers in reverse order to an order in which they were disposed using the mask pattern M as an etching mask, and thereafter removing the mask pattern M. One of ion milling using an argon gas, dry etching using a chlorine gas, and reactive ion etching may be used for etching the sequentially formed material layers in the reverse order. In addition, the MTJ layer S may be formed by a lift-off method.

**[0011]** Generally, the tunneling barrier layer S2 of the MRAM should be formed uniformly without defects for tunneling to be spin-dependent.

**[0012]** As described above, the tunneling barrier layer S2 of the MRAM in the conventional method is formed by oxidizing a metal layer using one of the methods of plasma oxidation, UV oxidation, natural oxidation, and ozone oxidation. However, some problems arise with the oxidation process on the metal layer.

**[0013]** In specific, when the metal layer is oxidized using the plasma oxidation method, an interface of thin layers consisting the lower magnetic layer S1, which is located under the metal layer, is damaged, and thereby, a magnetic resistance (MR) ratio of the MTJ layer S or the stability of the MRAM is lowered.

[0014] Moreover, when the metal layer is oxidized using methods aside from the plasma oxidation method, thickness uniformity of the tunneling barrier layer S2 may be changed. The change in the thickness uniformity of the tunneling barrier layer S2 along with a change in the thickness uniformity of the metal layer, which is inevitable in a manufacturing process, dramatically change the characteristics of the MRAM, for example, the MR ratio.

**[0015]** One solution to the above problems is to form the MTJ layer S of the MRAM using an atomic layer deposition (ALD) method.

**[0016]** In a case where the MTJ layer S of the MRAM is formed by the ALD method, a target material layer, that is, the tunneling barrier layer S2, having uniform

20

40

50

thickness can be formed. However, since characteristics of the interface of the target material layer and a material layer placed under the target material layer are changed, and the MR ratio is lowered.

**[0017]** According to an aspect of the present invention, there is provided an MRAM having one transistor and one MTJ layer in a unit cell, wherein the MTJ layer may be formed by sequentially stacking a lower magnetic layer, an oxidation preventing layer, a tunneling oxide layer, and an upper magnetic layer.

**[0018]** The oxidation preventing layer may be formed of an  $AIO_x$  layer and the tunneling oxide layer may be formed of one of an  $AIO_x$  layer, an  $AI_xHf_{1-x}O_y$  and, an  $Fe_3O_4$  layer.

**[0019]** The tunneling oxide layer may have a repeating structure where respective components are sequentially stacked in each atomic layer unit.

**[0020]** According to another aspect of the present invention, there is provided a method of manufacturing an MRAM having one transistor and one MTJ layer in a unit cell, wherein the MTJ layer is formed by sequentially stacking a lower magnetic layer, an oxidation preventing layer, a tunneling oxide layer, and an upper magnetic layer, and wherein the tunneling oxide layer is formed using an atomic layer deposition (ALD) method and at least the oxidation preventing layer among the above three material layers is formed using a method other than the ALD method.

**[0021]** The oxidation preventing layer may be formed of an  $AIO_x$  layer using a sputtering process. The lower and upper magnetic layers may be formed using a sputtering process and the ALD method.

[0022] The tunneling oxide layer may be formed of one of an  $AIO_x$  layer, an  $AI_xHf_{1-x}O_y$  and, an  $Fe_3O_4$  layer. [0023] As a consequence, the tunneling oxide layer is formed to have a uniform thickness that can be adjusted easily. Therefore, resistance of the MTJ layer is easily adjusted and a resistance variation between memory cells can be reduced. Moreover, a decrease in the MR ratio can be prevented by precluding any damage in the lower magnetic layer when forming the tunneling oxide layer.

**[0024]** The present invention provides a magnetic random access memory (MRAM) in which a tunneling oxide layer of a magnetic tunneling junction (MTJ) layer has a uniform thickness, which prevents a magnetic resistance (MR) ratio from being lowered due to a damaged lower layer disposed under the MTJ layer.

**[0025]** In addition, the present invention also provides a method of manufacturing the MRAM.

**[0026]** The above and other features and advantages of the present invention will become more apparent by describing in detail exemplary embodiments thereof with reference to the attached drawings in which:

FIG. 1 is a cross-sectional view illustrating a general structure of a magnetic random access memory (MRAM);

FIG. 2 is a cross-sectional view illustrating a structure and a method of forming a magnetic tunneling junction (MTJ) layer of the MRAM in FIG. 1 in accordance with the order in which the structure is formed:

FIG. 3 is a cross-sectional view sequentially illustrating an MTJ layer of the MRAM of FIG. 1;

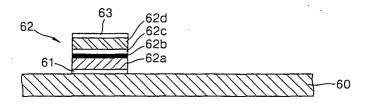

FIG. 4 is a cross-sectional view of an MRAM comprising a middle oxide layer formed by a heteromethod according to an embodiment of the present invention;

FIGS. 5 through 8 are cross-sectional views sequentially illustrating a method of forming a MTJ layer of an MRAM comprising a middle oxide layer formed by a hetero-method according to an embodiment of the present invention;

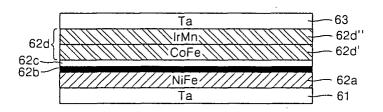

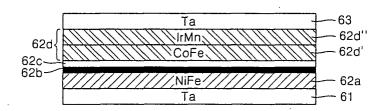

FIG. 9 is a cross-sectional view illustrating a structure of an MTJ layer which is used in an experimental example in order to measure characteristics of an MRAM comprising a middle oxide layer formed by a hetero-method according to an embodiment of the present invention;

FIG. 10 is a cross-sectional view of an MTJ layer as a control for comparison with the MTJ layer of FIG. o.

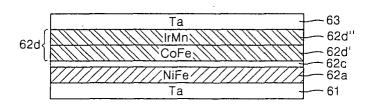

FIG. 11 is a graph illustrating resistance changes in the MTJ layer of FIG. 10 according to bias voltage; FIG. 12 is a graph illustrating a magnetic resistance (MR) ratio and a resistance of the MTJ layer of FIG. 9 according to bias voltage; and

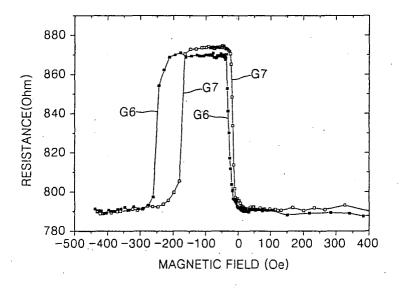

FIG. 13 is a graph illustrating resistance changes according to changes in magnetic field applied to the MTJ layer when a predetermined bias voltage is applied to the MTJ layer of FIG. 9.

[0027] The present invention will now be described more fully with reference to the attached drawings, in which exemplary embodiments thereof are shown. This invention may, however, be embodied in many different forms and should not be construed as being limited to the embodiments set forth herein; rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the concept of the invention to those skilled in the art. In the drawings, the forms of the elements are exaggerated for clarity. To facilitate understanding, identical reference numerals have been used, where possible, to designate identical elements that are common to the figures.

**[0028]** A magnetic random access memory (MRAM) according to an embodiment of the present invention will be explained.

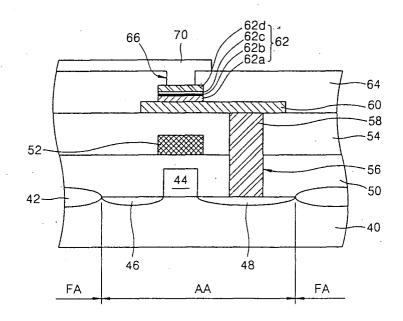

**[0029]** FIG. 4 is a cross-sectional view of a MRAM comprising middle oxide layers formed by a heteromethod according to an embodiment of the present invention.

**[0030]** Referring to FIG. 4, an active area (AA) and a field area (FA) are set up in a semiconductor substrate 40, and a field oxide layer 42 is formed in the FA. A tran-

sistor comprising a gate stacking material 44 and source and drain areas 46 and 48 is formed in the AA which is located between the two FAs. A first interlayer insulating layer 50 covering the transistor is formed on the semiconductor substrate 40 and a data line 52 corresponding to the gate stacking material 44 is formed on the first interlayer insulating layer 50.

**[0031]** The data line 52 is a magnetic field generating element for writing data to an MTJ layer 62. A magnetic field passing an MTJ layer 62 is generated around the data line 52 as a predetermined current is applied to the data line 52 to write data. In this case, the transistor is in an off-state.

[0032] A second interlayer insulating layer 54 covering the data line 52 is formed on the first interlayer insulating layer 50. A contact hole 56, which is separated a predetermined distance from the data line 52 and the gate stocking material 44, is formed on the first and second interlayer insulating layers 50 and 54. The drain area 48 of the transistor is exposed through the contact hole 56, which is filled with a conductive plug 58. A pad conductive layer 60 contacting the top of the conductive plug 58 is extended over the data line 52 on the second interlayer insulating layer 54. The pad conductive layer 60 is formed by sequentially depositing a titanium (Ti) layer and a titanium nitride (TiN) layer. The MTJ layer 62 is formed in a predetermined area of the pad conductive layer 60 corresponding to the data line 52. The MTJ layer 62 includes a seed layer (not shown), a lower magnetic layer 62a, an oxidation preventing layer 62b, a tunneling oxide layer 62c, an upper magnetic layer 62d, and a capping layer (not shown). The lower magnetic layer 62a is formed by sequentially stacking a pinning layer and a pinned layer. The seed layer may be a single or double layer. When the seed layer is a single layer, it is preferable to be a tantalum (Ta) layer. The pinning layer may be an anti-ferromagnetic layer, for example, an IrMn layer, and the pinned layer may be a ferromagnetic layer, for example a CoFe layer. The upper magnetic layer 62d may be a ferromagnetic layer (hereinafter, free ferromagnetic layer) in which a direction of magnetic polarization is freely changed according to an applied magnetic field. For example, the upper magnetic layer 62b may be formed of an NiFe layer.

**[0033]** The structures of the lower magnetic layer 62a and the upper magnetic layer 62d may be interchanged. For example, the lower magnetic layer 62a may be a free ferromagnetic layer, and the upper magnetic layer 62d may be formed by sequentially stacking a pinned layer and a pinning layer. In this case, the lower magnetic layer 62a may be a NiFe layer, and the pinned layer and the pinning layer may be a CoFe layer and an IrMn layer, respectively.

**[0034]** The capping layer is intended to contact the MT layer 62 with a bit line 70. The capping layer is formed of a metal layer having low contact resistance, for example, a Ta or Ru layer. The oxidation preventing layer 62b is intended to prevent an interface of the lower

magnetic layer 62a from being damaged, for instance, by oxidation of the interface of the lower magnetic layer 62a, when forming the tunneling oxide layer 62c. The oxidation preventing layer 62b is a first aluminum oxide layer AlO $_{\rm X}$ , for example, an Al $_{\rm 2}$ O $_{\rm 3}$  layer. The tunneling oxide layer 62c is formed by an atomic layer deposition (ALD) method, a method of which is different from that used for forming the oxidation preventing layer 62b. That is, the tunneling oxide layer 62c is preferably formed of an oxide layer having a predetermined thickness, for instance, a second aluminium oxide layer AlO $_{\rm X}$ . However, it may be an Al $_{\rm X}$ Hf $_{\rm 1-X}$ O $_{\rm Y}$  or Fe $_{\rm 3}$ O $_{\rm 4}$  layer. In addition, the second aluminium oxide layer AlO $_{\rm X}$  may be, but are not limited to, an Al $_{\rm 2}$ O $_{\rm 3}$  layer.

**[0035]** The MTJ layer 62 may be applied to not only the MRAM of FIG. 4 but also to other MRAMs, for instance an MRAM including the data line 52 placed over the MTJ layer 62 and the bit line 70 which is placed under the MTJ layer 62.

[0036] A third interlayer insulating layer 64 covering the pad conductive layer 60 and the MTJ layer 62 is formed on the second interlayer insulating layer 54. A via hole 66 exposing the MTJ layer 62 is formed on the third interlayer insulating layer 64. In addition, the bit line 70 which fills the via hole 66 and contacts the MTJ layer 62 is formed on the third interlayer insulating layer 64. The bit line 70 may be perpendicular to the data line 52 and the gate stacking material 44.

**[0037]** Next, a method of manufacturing the MRAM having the aforementioned elements will be explained with reference to FIGS. 4 through 8.

**[0038]** Referring to FIG. 4, the active area (AA) and the field area (FA) are defined in the semiconductor substrate 40 and the field oxide layer 42 for device separation is formed in the FA. The gate stacking material 44 including the gate electrode is formed on the AA. The source and drain areas 46 and 48 are formed on the AA at both sides of the gate stacking material 44. Thus, the transistor is completely formed on the semiconductor substrate 40. The transistor is in an off-state when writing data in the MTJ layer 62 and in an on-state when reading data from the MTJ layer 62.

[0039] Then, the first interlayer insulating layer 50 covering the transistor is formed on the semiconductor substrate 40. The data line 52 may be formed in a predetermined area over the gate stacking material 44 on the first interlayer insulating layer 50 and parallel to the gate stacking material 44. The data line 52 is intended to write data in the MTJ layer 62 and a predetermined current is applied thereto when writing data. The second interlayer insulating layer 54 covering the data line 52 is formed on the first interlayer insulating layer 50. Then, the contact hole 56 exposing a predetermined area of the semiconductor substrate 40 is formed in the first and second interlayer insulating layers 50 and 54. The drain area 48 of the transistor is exposed through the contact hole 56. After filling the contact hole 56 with the conductive plug 58, the pad conductive layer 60 is formed on

15

20

the second interlayer insulating layer 54. Then, the pad conductive layer 60 contacts the top surface of the conductive plug 58 and extends over the data line 52. The MTJ layer 62 is formed on a predetermined area of the pad conductive layer 60, preferably over the data line 52.

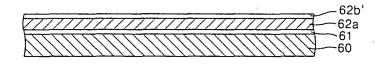

[0040] Now, specific procedures of forming the MTJ layer 62 will be explained with reference to FIGS. 5 and 8

[0041] Referring to FIG. 5, a seed layer 61 is formed on the pad conductive layer 60, and a lower magnetic layer 62a including a pinning layer and a pinned layer is formed on the seed layer 61. The layers of the lower magnetic layer 62a are formed using a sputtering method or an ion beam deposition (IBD) method. Specific examples of the respective layers of the lower magnetic layer 62a have been mentioned before and thus will be omitted.

**[0042]** Next, a metal layer 62b', which will be used as an oxide preventing layer in a subsequent process, is formed on the lower magnetic layer 62a. The metal layer 62b' may be formed of an aluminium layer Al using a sputtering method. Then, the metal layer 62b' is oxidized using a predetermined method, for instance, a plasma oxidation method. As a result, an oxidation preventing layer 62b, for example, an aluminium oxide layer AlO<sub>x</sub>, is formed on the top layer, that is the pinned layer, of the lower magnetic layer 62a as shown in FIG. 6. The oxidation preventing layer 62b is one of the middle oxide layer, which is placed between the lower magnetic layer 62a and an upper magnetic layer 62d.

**[0043]** Referring to FIG. 7, a tunneling oxide layer 62c, the upper magnetic layer 62d, and the capping layer 63 are sequentially formed on the oxide preventing layer 62b. The tunneling oxide layer 62c as one of the middle oxide layers is preferably formed by the ALD method and the upper magnetic layer 62d is preferably formed using a sputtering method.

**[0044]** Specific procedures of forming the tunneling oxide layer 62c using a second aluminium oxide layer  $AIO_X$  and the ALD method will be explained.

[0045] The semiconductor substrate 40 having the oxidation preventing layer 62b is loaded on a wafer stage of an ALD apparatus maintained at a predetermined temperature between 150°C and 500°C, preferably 400°C. Thereafter, a predetermined amount of a first precursor including a first reactive element, aluminium Al, is provided to the ALD apparatus and chemically absorbed into a surface of the oxidation preventing layer 62b. In specific, the first precursor is a compound including ligands of an aluminium and hydrocarbon series, for instance, Al(CH<sub>3</sub>)<sub>3</sub>, Al(CH<sub>2</sub>-CH<sub>2</sub>- ... -CH<sub>3</sub>)<sub>3</sub>, or a compound with one H of AI(CH<sub>2</sub>-CH<sub>2</sub>- ... -CH<sub>3</sub>)<sub>3</sub> substituted by CH<sub>2</sub>-CH<sub>2</sub>- ... -CH<sub>3</sub>. The first precursor provided to the ALD apparatus that is not chemically absorbed onto the surface of the oxidation preventing layer 62b is discharged from the ALD apparatus when the ALD apparatus is ventilated. Then, a predetermined amount of a

second precursor for oxidizing the first reaction element AI of the first precursor on the oxidation preventing layer 62b is provided to the ALD apparatus. The second precursor may be formed of one of  $\rm H_2O$  and  $\rm O_3$ , but preferably  $\rm H_2O$ .

**[0046]** Then, the first and second precursors chemically react with each other. Accordingly, a reactive byproduct  $3CH_4$  resulting from a reaction between a ligand of the first precursor  $(-CH_3)_3$  and H of the second precursor is formed as shown in a chemical reaction equation below, and the reactive by-product  $3CH_4$  is volatilized. Thus, the tunneling oxide layer 62c, that is the aluminum oxide layer  $AIO_X$ , is formed on the oxidation preventing layer 62b.

### <Chemical Reaction Equation>

$$AI(CH_3)_3(g) + 3H_2O(g) \rightarrow AI_2O_3(s) + 3CH_4(g)$$

[0047] After the aluminium oxide layer  $AIO_X$  is formed on the oxidation preventing layer 62b, volatile materials and other by-products are removed from the ALD apparatus by exhausting the ALD apparatus. The aforementioned procedure will be repeated until the aluminium oxide layer  $AIO_X$  having a desired thickness is obtained. [0048] Referring to FIG. 7, the upper magnetic layer 62 is a free ferromagnetic layer. The free ferromagnetic layer may be formed of a single ferromagnetic layer or at least two sequentially stacked ferromagnetic layers. In the former case, the free ferromagnetic layer may be formed of an NiFe layer.

[0049] After the upper magnetic layer 62d and the capping layer 63 are formed on the tunneling oxide layer 62c, a photosensitive layer (not shown) is disposed on the capping layer 63. Then, a photosensitive pattern 80, which limits an area where the MTJ layer 62 of FIG. 4 will be formed, is formed by patterning the photosensitive layer using general photolithography. The material layers 61, 62a, 62b, 62c, 62d, and 63 stacked on the pad conductive layer 60 are etched in a reverse order using the photosensitive pattern 80 as an etching mask. A dotted line of FIG. 7 indicates an etching direction. This etching procedure will be continued until the pad conductive layer 60 is exposed, and thereafter the photosensitive pattern 80 is removed by ashing and stripning

**[0050]** FIG. 8 illustrates a cross-sectional view of a resulting material after the above etching process is finished and the photosensitive pattern 80 is removed. Referring to FIG. 8, the MTJ layer 62 comprising the seed layer 61, the lower magnetic layer 62a, the middle oxide layers 62b and 62c, and the upper magnetic layer 62d is formed in a predetermined area of the pad conductive layer 60.

**[0051]** Here, referring to FIG. 4, the MTJ layer 62 is formed in a predetermined area of the pad conductive layer 60, and then, a third interlayer insulating layer 64

covering the pad conductive layer 60 and the MTJ layer 62 is formed on the second interlayer insulating layer 54. In addition, a via hole 66 exposing the MTJ layer 62 is formed in the third interlayer insulating layer 64, and thereafter, the bit line 70 filling the via hole 66 is formed on the third interlayer insulting layer 64.

#### < Experimental Example>

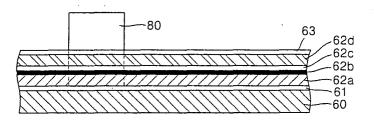

[0052] The MTJ layer of the present invention is formed as shown in FIG. 9, in order to measure characteristics of the MTJ layer, for instance, the MR ratio. Furthermore, a conventional MTJ layer is also formed as shown in FIG. 10, in order to compare the same with the MTJ layer of the present invention.

[0053] Referring to FIG. 9, the seed layer 61 in the MTJ layer according to the present invention is formed of a Ta layer using sputtering. The lower magnetic layer 62a, which is a free ferromagnetic layer, is formed of a NiFe layer using sputtering. The oxidation preventing layer 62b and the tunneling oxide layer 62c forming the middle oxide layers are formed of an AlO<sub>x</sub> layer. The oxidation preventing layer 62b is formed by oxidizing a metal layer Al after the metal layer Al is formed using a sputtering process, and the tunneling oxide layer 62c is formed by the ALD method. Furthermore, the upper magnetic layer 62d is formed by sequentially stacking a CoFe layer 62d' and a IrMn layer 62d", which act as the pinned layer and the pinning layer, respectively, using sputtering. The seed layer 61 and the capping layer may be substituted with a Ru layer.

[0054] The conventional MTJ layer of FIG. 10 is formed by removing the oxidation preventing layer 62b from the MTJ layer according to an embodiment of the present invention in FIG. 9.

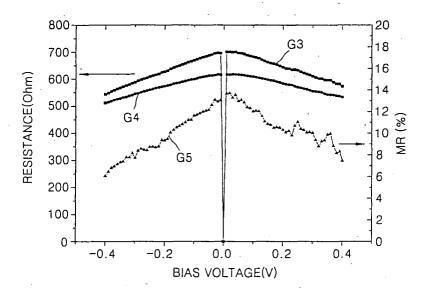

[0055] FIGS. 11 through 13 are graphs illustrating characteristics of the conventional MTJ layer and the MTJ layer of the present invention.

[0056] In specific, FIG. 11 illustrates first and second graphs G1 and G2 representing resistance changes of the conventional MTJ layer according to a bias voltage. The first graph G1 illustrates the resistance changes when magnetic directions of the upper and lower magnetic layers are the same and the second graph G2 illustrates the resistance changes when the magnetic directions of the upper and lower magnetic layers are op-

[0057] Referring to FIG. 11, the first and second graphs G1 and G2 overlap and thereby showing that the resistance of the conventional MTJ layer is the same regardless of the magnetic directions of the upper and lower magnetic layers. Therefore, the MR ratio of the conventional MTJ layer is 0%.

[0058] FIG. 12 illustrates third and fourth graphs G3 and G4 representing the resistance changes of the MTJ layer of the present invention according to bias voltage and a fifth graph G5 indicating changes in the MR ratio. In specific, the third graph G3 shows the resistance

changes when magnetic directions of the upper and lower magnetic layers are opposite and the fourth graph G4 shows the resistance changes when the magnetic directions of the upper and lower magnetic layers are the same.

10

[0059] Referring to FIG. 12, unlike the first and second graphs G1 and G2 of FIG. 11, the third and fourth graphs G4 and G5 are separated by a predetermined distance. This means that the resistance of the MTJ layer of the present invention is different according to the magnetic directions of the upper and lower magnetic layers, and thus, the MTJ layer of the present invention has a predetermined MR ratio as shown in the fifth graph G5.

[0060] Referring to the fifth graph G5, the MR ratio of the MTJ layer of the present invention is 0.13 or 13% at the predetermined bias voltage, for instance 100mV. Using the MR ratio, whether the magnetic directions of the upper and lower magnetic layers are the same or opposite can be checked. That is, it is possible to sense whether data " 1 " or "0" is recorded.

[0061] FIG. 13 illustrates sixth and seventh graphs G6 and G7 representing the resistance changes of the MTJ layer of the present invention according to changes in a magnetic field H applied to the MTJ layer when a bias voltage is fixed at a predetermined value, for instance 400mV. Although the sixth and seventh graphs G6 and G7 are to be a continuous single graph, they are illustrated separated to provide an easy explanation.

[0062] The sixth graph G6 illustrates the resistance changes of the MTJ layer of the present invention when gradually decreasing the strength of the magnetic field H which is applied to the MTJ layer H until it is "0" in order to equalize the magnetization directions of the upper and lower magnetic layers of the MTJ layers and then gradually increasing the strength of the magnetic field H in order to make the magnetization directions of the upper and lower magnetic layers opposite.

[0063] After the strength of the magnetic field H becomes "0", when the magnetic field H is strengthened in a direction opposite to the original, the magnetization directions of the upper and lower magnetic layers becomes opposite to each other. Therefore, resistance of the MTJ layer of the present invention is increased as shown in the sixth graph G6. However, when the strength of the magnetic field H is continuously increased, for instance up to near -300(Oe), the magnetization directions of the upper and lower magnetic layers of the MTJ layer of the present invention become the same again, and thus, the resistance of the MTJ layer of the present invention is decreased. A flat left portion of the sixth graph G6 illustrates this case.

[0064] The seventh graph G7 illustrates the resistance changes starting from a right end of the flat left portion in the sixth graph G6. That is, the seventh graph G7 illustrates the resistance changes of the MTJ layer of the present invention when gradually decreasing the strength of the magnetic field H applied to the MTJ layer H to "0", and then gradually increasing the strength of

50

15

20

35

40

the magnetic field H in an opposite direction after the magnetic directions of the upper and lower magnetic layers have become the same again.

**[0065]** As described above, the MRAM according to the preferred embodiments of the present invention comprises the tunneling oxide layer which is formed by the ALD method and the oxidation preventing layer which is formed using a sputtering method and located under the tunneling oxide layer. The oxidation preventing layer prevents oxidation of the interface of the lower magnetic layer when forming the tunneling oxide layer by the ALD method. Accordingly, it can prevent the MR ratio of the MTJ layer from decreasing while forming the tunneling oxide layer to a uniform thickness.

[0066] This invention may, however, be embodied in many different forms and should not be construed as being limited to the embodiments set forth herein; rather, these embodiments are provided so that this disclosure will be thorough and complete and will fully convey the concept of the invention to those skilled in the art. For example, the lower and upper magnetic layers 62a and 62d of the MTJ layer 62 including the tunneling oxide layer 62c and the oxidation preventing layer 62b may have different structures. In addition, the MTJ layer according to the exemplary embodiments of the present invention may be applied to an MRAM having the data line 52 and the bit line 70 in different structures. Also, the tunneling oxide layer 62c may be formed of a different type of oxide layer and other types of non-oxide layer playing an equivalent role. Also, the oxidation preventing layer 62b may be formed of an oxide layer differing from AlO<sub>x</sub> or non-oxide.

**[0067]** While the present invention has been particularly shown and described with reference to exemplary embodiments thereof, it will be understood by those of ordinary skill in the art that various changes in form and details may be made therein without departing from the spirit and scope of the present invention as defined by the following claims.

#### Claims

1. A magnetic random access memory (MRAM) having a transistor and

a magnetic tunneling junction (MTJ) layer in a unit cell, wherein the MTJ layer comprises a lower magnetic layer, an oxidation preventing layer, a tunneling oxide layer, and an upper magnetic layer, which are sequentially stacked.

- 2. The MRAM of claim 1, wherein the oxidation preventing layer is formed of an AlO<sub>v</sub> layer.

- 3. The MRAM of claim 2, wherein the tunneling oxide layer is formed of one of an  $AlO_x$  layer, an  $Al_xHf_{1-x}O_y$ , and a  $Fe_3O_4$  layer.

- 4. The MRAM of claim 1, 2 or 3, wherein the tunneling oxide layer is formed of one of an AlO<sub>x</sub> layer, an Al<sub>x</sub>Hf<sub>1-x</sub>O<sub>y</sub>, and a Fe<sub>3</sub>O<sub>4</sub> layer.

- 5. The MRAM of any preceding claim, wherein the tunneling oxide layer has a repeating structure where respective components are sequentially stacked on each atomic layer unit.

- 6. The MRAM of any preceding claim, wherein one of the upper and lower magnetic layers includes a free ferromagnetic layer.

- A method of manufacturing an MRAM having a transistor and a

MTJ layer in a unit cell, wherein the MTJ layer is formed by sequentially stacking a lower magnetic layer, an oxidation preventing layer, a tunneling oxide layer, and an upper magnetic layer, and wherein the tunneling oxide layer is formed by an atomic layer deposition (ALD) method and at least the oxidation preventing layer among the above three material layers is formed by a method other than the ALD method.

- **8.** The method of claim 7, wherein the oxidation preventing layer is formed using a sputtering method.

- The method of claim 7 or 8, wherein the lower magnetic layer is formed using one of the sputtering method and the ALD method.

- **10.** The method of any of claims 7 to 9, wherein the upper magnetic layer is formed using one of the sputtering method and the ALD method.

- The method of any of claims 7 to 10, wherein the oxidation preventing layer is formed of an AlO<sub>x</sub> layer.

- 12. The method of any of claims 7 to 11, wherein the tunneling oxide layer is formed of one of an  $AIO_X$  layer, an  $AI_XHf_{1-X}O_Y$ , and a  $Fe_3O_4$  layer.

- 13. The method of claim 7, wherein one of the upper and lower magnetic layers includes a free ferromagnetic layer.

55

50

# FIG. 1 (PRIOR ART)

FIG. 2 (PRIOR ART)

FIG. 3 (PRIOR ART)

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13