(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6556736号

(P6556736)

(45) 発行日 令和1年8月7日(2019.8.7)

(24) 登録日 令和1年7月19日(2019.7.19)

(51) Int.Cl.

F 1

|             |           |      |        |      |

|-------------|-----------|------|--------|------|

| HO3K 19/00  | (2006.01) | HO3K | 19/00  | 108  |

| HO3K 19/094 | (2006.01) | HO3K | 19/094 |      |

| HO3K 5/133  | (2014.01) | HO3K | 5/133  |      |

| HO2J 1/00   | (2006.01) | HO2J | 1/00   | 306D |

| HO2J 1/02   | (2006.01) | HO2J | 1/02   |      |

請求項の数 10 (全 20 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2016-546760 (P2016-546760)  |

| (86) (22) 出願日      | 平成27年1月16日 (2015.1.16)        |

| (65) 公表番号          | 特表2017-509202 (P2017-509202A) |

| (43) 公表日           | 平成29年3月30日 (2017.3.30)        |

| (86) 國際出願番号        | PCT/US2015/011762             |

| (87) 國際公開番号        | W02015/109188                 |

| (87) 國際公開日         | 平成27年7月23日 (2015.7.23)        |

| 審査請求日              | 平成29年12月21日 (2017.12.21)      |

| (31) 優先権主張番号       | 14/157,503                    |

| (32) 優先日           | 平成26年1月16日 (2014.1.16)        |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                        |

| (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                                        |

最終頁に続く

(54) 【発明の名称】電圧降下を制約することによる、パワーゲーティングされた複数のセクションのサイジング

## (57) 【特許請求の範囲】

## 【請求項 1】

ダウンストリーム回路におけるパワーゲーティングされた複数のセクションをサイジングするための方法であって、

アップストリーム回路の供給端子間で定義される前記アップストリーム回路に対応するキャパシタンスと、電圧降下制約条件とに基づいて、第1のセクションに関する供給端子間で定義される前記ダウンストリーム回路に対応するキャパシタンスを決定することと、

前記アップストリーム回路の前記キャパシタンスと、前記電圧降下制約条件と、前記第1のセクションに関する前記決定されたキャパシタンスとに基づいて、第2のセクションに関する供給端子間で定義される前記ダウンストリーム回路に対応するキャパシタンスを決定することと、

前記アップストリーム回路の前記キャパシタンスと、前記電圧降下制約条件と、前記第1のおよび第2のセクションに関する前記決定されたキャパシタンスとに基づいて、第3のセクションに関する供給端子間で定義される前記ダウンストリーム回路に対応するキャパシタンスを決定することと、

前記複数のセクションの各々に関する前記決定されたキャパシタンスに基づいて、前記第1の、第2の、および第3のセクションの各々のサイズを決定することと、

を備える、方法。

## 【請求項 2】

前記ダウンストリーム回路は、メモリを備える、請求項1に記載の方法。

10

20

**【請求項 3】**

前記第2のセクションに関する前記キャパシタンスを決定することは、前記アップストリーム回路の前記キャパシタンスと、前記第1のセクションに関する前記決定されたキャパシタンスとの合計に基づいて、前記第2のセクションに関する前記キャパシタンスを決定することを備える、請求項1に記載の方法。

**【請求項 4】**

前記第3のセクションに関する前記キャパシタンスを決定することは、前記アップストリーム回路の前記キャパシタンスと、前記第1のセクションに関する前記決定されたキャパシタンスと、前記第2のセクションに関する前記決定されたキャパシタンスとの合計に基づいて、前記第3のセクションに関する前記キャパシタンスを決定することを備える、請求項3に記載の方法。10

**【請求項 5】**

前記第1の、第2の、および第3のセクションの各々の前記サイズを決定することは、前記複数のセクションの各々に関する前記決定されたキャパシタンスを、キャパシタンス密度で割ることを備える、請求項1に記載の方法。

**【請求項 6】**

前記第1のセクションに関する前記キャパシタンスを決定することは、補正係数に基づいて、前記第1のセクションに関する前記キャパシタンスを決定することを備える、請求項1に記載の方法。

**【請求項 7】**

前記補正係数は0.8以上1より小さい値を有する、請求項6に記載の方法。20

**【請求項 8】**

前記電圧降下制約条件は0.05またはそれより小さい、請求項1に記載の方法。

**【請求項 9】**

ダウンストリーム回路におけるパワーゲーティングされた複数のセクションをサイジングするための装置であって、

アップストリーム回路の供給端子間で定義される前記アップストリーム回路に対応するキャパシタンスと、電圧降下制約条件とに基づいて、第1のセクションに関する供給端子間で定義される前記ダウンストリーム回路に対応するキャパシタンスを決定するための手段と、30

前記アップストリーム回路の前記キャパシタンスと、前記電圧降下制約条件と、前記第1のセクションに関する前記決定されたキャパシタンスとに基づいて、第2のセクションに関する供給端子間で定義される前記ダウンストリーム回路に対応するキャパシタンスを決定するための手段と、

前記アップストリーム回路の前記キャパシタンスと、前記電圧降下制約条件と、前記第1のおよび第2のセクションに関する前記決定されたキャパシタンスとに基づいて、第3のセクションに関する供給端子間で定義される前記ダウンストリーム回路に対応するキャパシタンスを決定するための手段と、

前記複数のセクションの各々に関する前記決定されたキャパシタンスに基づいて、前記第1の、第2の、および第3のセクションの各々のサイズを決定するための手段と、40

を備える、装置。

**【請求項 10】**

前記ダウンストリーム回路は、メモリを備える、請求項9に記載の装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

[0001] 本開示の複数の態様は、一般にパワーゲーティング(power gating)に関し、より具体的には、電圧降下(voltage droop)を制約することによって、パワーゲーティングされた複数のセクション(power-gated sections)をサイジング(sizing)することに関する。

**【背景技術】****【0002】**

[0002] パワー分配ネットワーク (P D N : power distribution network) は、電力供給装置 (power supply) (例えば、バッテリ) から、ダイ上の様々な回路へ電力を分配 (distribute) するために使用され得る。電力を節約するために、P D N は、パワーゲーティングを用い得、そこでは、P D N は、ある回路が非アクティブの時、その回路からの電力漏れ (power leakage) を防ぐために、電力供給装置からその回路を切断する。回路のディメンション (dimensions) が、ディープナノメートル範囲へと (into the deep nano meter range) スケールダウンされるにつれ、電力漏れは著しく増加する。故に、パワーゲーティングは、電力消費を低減し、モバイルデバイスのバッテリ寿命を延ばすために、重要性を増してきている。

10

**【発明の概要】****【0003】**

[0003] 以下は、1つ以上の実施形態の基本的な理解を提供するために、そのような実施形態の簡略化された概要を提示する。この概要是、考えられる全ての実施形態の広範な概観ではなく、全ての実施形態の重要要素や決定的要素を特定するようにも、何れかまたは全ての実施形態の範囲を定める (delineate) ようにも意図されていない。その唯一の目的は、後に提示されるより詳細な説明への前置きとして、簡略化された形式で1つ以上の実施形態のうちのいくつかの概念を提示することである。

**【0004】**

20

[0004] 第1の態様に従って、ダウンストリーム回路におけるパワーゲーティングされた複数のセクションをサイジングするための方法がここに説明される。この方法は、アップストリーム回路のキャパシタンスと、電圧降下制約条件 (a voltage-droop constraint) とに基づいて、第1のセクションに関するキャパシタンスを決定することと、アップストリーム回路のキャパシタンスと、電圧降下制約条件と、第1のセクションに関する決定されたキャパシタンスとに基づいて、第2のセクションに関するキャパシタンスを決定することと、アップストリーム回路のキャパシタンスと、電圧降下制約条件と、第1のおよび第2のセクションに関する決定されたキャパシタンスとに基づいて、第3のセクションに関するキャパシタンスを決定することと、を備える。この方法はまた、第1の、第2の、および第3のセクションの各々のサイズを、それらセクションの各々に関する決定されたキャパシタンスに基づいて決定することを備える。

30

**【0005】**

[0005] 第2の態様は、漸進的に (progressively) サイズが大きくなる複数のセクションを備える回路をパワーアップするための方法に関する。この方法は、回路をパワーアップ (powering up) するための信号を受信することと、その信号に応答して、サイズが大きくなっていく順番で、複数のセクションを連続的に (sequentially) パワーアップすることとを備える。

**【0006】**

40

[0006] 第3の態様は、漸進的にサイズが大きくなる複数のセクションを備える回路をパワーアップするための装置に関する。この装置は、回路をパワーアップするための信号を受信するための手段と、その信号に応答して、サイズが大きくなっていく順番で、複数のセクションを連続的にパワーアップするための手段とを備える。

**【0007】**

[0007] 第4の態様は、漸進的にサイズが大きくなる複数のセクションを備える回路をパワーアップするための装置に関する。この装置は、複数のスイッチを備え、ここで、それらスイッチの各々は、複数のセクションのうちのそれぞれ1つをパワーレールに選択的に接続するように構成される。この装置はまた、それらスイッチが、サイズが大きくなっていく順番で、複数のセクションを連続的にパワーアップするように、それらスイッチを連続的に閉じるように構成される電力管理デバイスを備える。

**【0008】**

50

[0008] 前述した目的および関連する目的を達成するために、1つ以上の実施形態は、以下で十分に説明され、且つ特許請求の範囲において具体的に指摘される特徴を備える。以下の説明および添付図面は、1つ以上の実施形態のある特定の例示的な態様を詳細に記載する。しかしながら、これらの態様は、様々な実施形態の原理が用いられ得る様々な方法のほんの一部しか示しておらず、説明される実施形態は、そのような態様およびそれらの同等物の全てを含むことが意図されている。

**【図面の簡単な説明】**

**【0 0 0 9】**

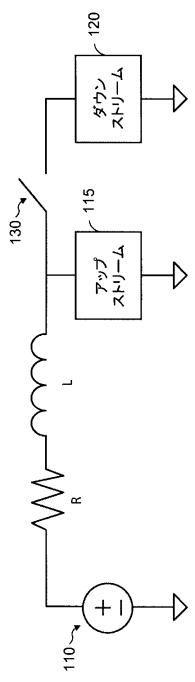

【図1】[0009] 図1は、アップストリーム回路およびダウンストリーム回路へ電力を分配するためのパワー分配ネットワーク（P D N : power distribution network）の例を示す。10

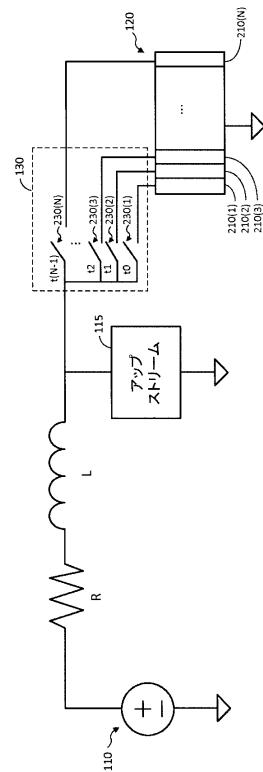

【図2】[0010] 図2は、複数の等しいサイズのセクションへ分割されたダウンストリーム回路の例を示す。

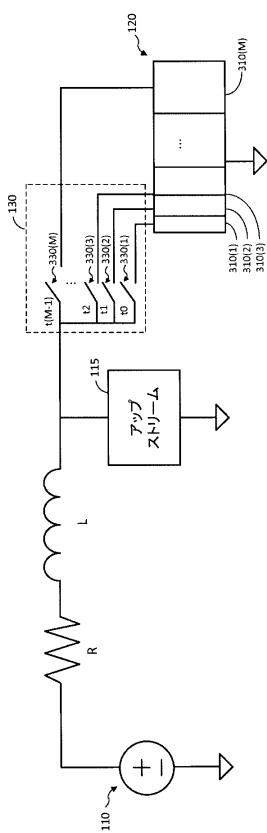

【図3】[0011] 図3は、本開示の実施形態に従って、漸進的にサイズが大きくなる複数のセクションへ分割されたダウンストリーム回路を示す。

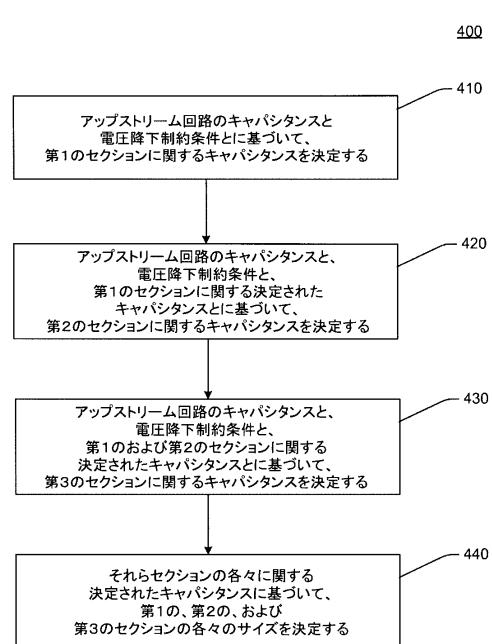

【図4】[0012] 図4は、本開示の実施形態に従って、ダウンストリーム回路におけるパワーゲーティングされた複数のセクションをサイジングするための方法を示すフローダイアグラムである。

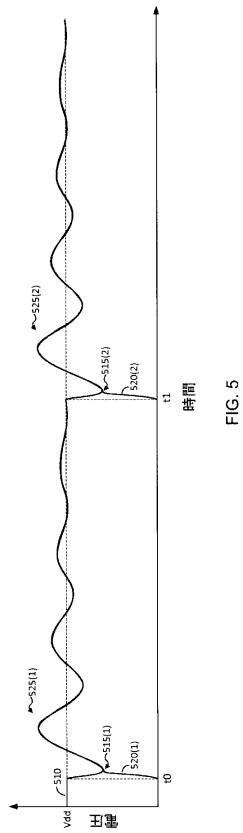

【図5】[0013] 図5は、本開示の実施形態に従って、パワーアップシーケンスの間の、アップストリーム回路およびダウンストリーム回路の2つのセクションに関する電圧波形の例を示す。20

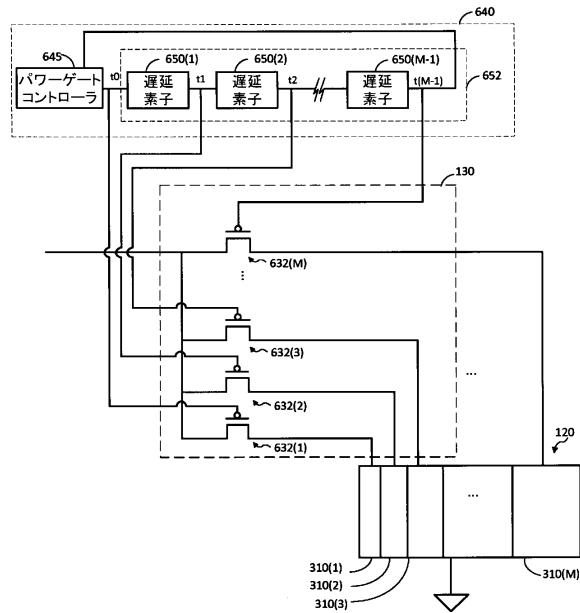

【図6】[0014] 図6は、本開示の実施形態に従って、ダウンストリーム回路の複数のセクションを連続的にパワーアップするための回路を示す。

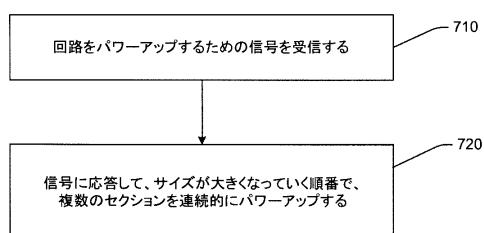

【図7】[0015] 図7は、本開示の実施形態に従って、回路の複数のセクションを連続的にパワーアップするための方法を示すフローダイアグラムである。

**【詳細な説明】**

**【0 0 1 0】**

[0016] 添付図面に関連して以下に記載される詳細な説明は、様々な構成のうちの1つの説明として意図されており、ここに説明される概念が実施され得る唯一の構成を表すようには意図されていない。詳細な説明は、様々な概念の徹底した理解を提供することを目的として特定の詳細を含む。しかしながら、これらの概念がこれらの特定の詳細なしに実施され得ることは、当業者に明らかであるだろう。いくつかの例では、そのような概念をあいまいにすることを避けるために、周知の構造およびコンポーネントはブロック図の形式で示される。30

**【0 0 1 1】**

[0017] 図1は、DC電力供給装置110からアップストリーム回路115およびダウンストリーム回路120へ電力を分配するためのパワー分配ネットワーク（P D N : power distribution network）の例を示す。図1におけるインダクタLおよびレジスタRは、それぞれ、電力供給装置110と回路115および120との間のパッケージング相互接続（packaging interconnects）ならびに基板のインダクタンスおよび抵抗をモデル化（model）する。アップストリーム回路115およびダウンストリーム回路120は、同じダイ上に配置され得る。40

**【0 0 1 2】**

[0018] P D Nは、電力を節約するためにパワーゲーティングを用い得る。この点で、P D Nは、ダウンストリーム回路120を電力供給装置110に選択的に接続するための電力スイッチ130を含む。ダウンストリーム回路120がアクティブである時、電力スイッチ130は、ダウンストリーム回路120に電力を供給するためにオンにされ（turned on）、ダウンストリーム回路120が非アクティブである時、電力スイッチ130は、電力供給装置110をダウンストリーム回路120から切断するためにオフにされる（turned off）。これにより、ダウンストリーム回路120が非アクティブである時、ダウ50

ンストリーム回路 120 からの電力漏れが低減され、電力の節約になる。

#### 【0013】

[0019] ダウンストリーム回路 120 がアクティブである時、電力スイッチ 130 を通した I R 電圧降下 (voltage drop) を最小化するために、電力スイッチ 130 が非常に低い抵抗を有することが望ましい。しかしながら、これは、電力スイッチ 130 が最初に閉じられた時にアップストリーム回路 115 における供給電圧に大きな降下 (droop) を招く可能性があり、アップストリーム回路 115 における論理に誤動作を生じさせる可能性がある。その大きな電圧降下は、ダウンストリーム回路 120 における複数のキャパシタによって引き起こされる。それらキャパシタは、ダウンストリーム回路 120 のトランジスタ中の寄生メタルラインキャパシタ (parasitic metal-line capacitors) および寄生キャパシタ (parasitic capacitors) を含み得る。ダウンストリーム回路 120 におけるそれらキャパシタは、ダウンストリーム回路 120 が非アクティブ状態から最初に覚醒される時、ほぼ全く電荷を有さない (have approximately no charge)。その結果、アップストリーム回路 115 およびダウンストリーム回路 120 が初めに電力スイッチ 130 によって接続される時、大量の電荷が、アップストリーム回路 115 におけるキャパシタからダウンストリーム回路 120 におけるキャパシタへ素早く流れ、アップストリーム回路 115 における供給電圧に降下を引き起こす。PDN は、PDN におけるインダクタンスが原因で、電圧降下を防ぐのに十分な程速く電荷を供給することができない。

10

#### 【0014】

[0020] 電圧降下のサイズは、以下の方程式によって近似され (be approximated) 得る。

20

#### 【数1】

$$Droop = \left(1 - \frac{C_{up}}{C_{up} + C_{dn}}\right) \quad (1)$$

ここで、 $C_{up}$  はアップストリーム回路 115 のキャパシタンスであり、 $C_{dn}$  はダウンストリーム回路 120 のキャパシタンスであり、Droop は電圧降下が原因のアップストリーム回路 115 における供給電圧の降下率を表す。例えば、0.10 の Droop は、供給電圧の 10 % の降下を表す。方程式 (1) は、オン抵抗がゼロである (having zero on resistance) 理想的な電力スイッチ 130 を想定している。

30

#### 【0015】

[0021] 方程式 (1) から分かるように、電圧降下は、ダウンストリーム回路 120 のキャパシタンスがアップストリーム回路 115 のキャパシタンスと比較して大きい時、大きくなる可能性がある。例えば、 $C_{up}$  と  $C_{dn}$  とがおおよそ等しい時、Droop はおよそ 0.5 (すなわち、供給電圧の 50 %) であり、それは大抵の場合には容認し難い程高い (unacceptably high)。

#### 【0016】

[0022] 電圧降下を容認可能な限界内に保つための 1 つのアプローチは、ダウンストリーム回路 120 を複数のセクション (電力ドメイン) へ分割し、全体のダウンストリーム回路 120 を一度にパワーアップする代わりに、ダウンストリーム回路 120 のそれら複数のセクションを連続的にパワーアップすることである。この点で、図 2 は、ダウンストリーム回路 120 が N 個の等しいサイズのセクション 210 (1) - 210 (N) へ分割され、電力スイッチ 130 が N 個のスイッチ 230 (1) - 230 (N) を備える例を示す。各スイッチ 230 (1) - 230 (N) は、セクション 210 (1) - 210 (N) のうちのそれぞれ 1 つを電力供給装置 110 に選択的に接続するように構成される。これにより、ダウンストリーム回路 120 の各セクション 210 (1) - 210 (N) が別々にパワーアップされることが可能になる。

40

#### 【0017】

[0023] ダウンストリーム回路 120 が非アクティブの時、電力漏れを低減するために

50

、スイッチ 230(1) - 230(N) は全て開かれる。ダウンストリーム回路 120 が非アクティブ状態から覚醒される (be awakened) ことになる時、スイッチ 230(1) - 230(N) は、ダウンストリーム回路 120 のセクション 210(1) - 210(N) を連続的にパワーアップするために連続的にオンにされる。第 1 のスイッチ 230(1) は、時間  $t_0$  においてオンにされ、第 2 のスイッチ 230(2) は、時間  $t_1$  においてオンにされ、第 3 のスイッチ 230(3) は、時間  $t_2$  においてオンにされ、N 番目のスイッチ 230(N) が時間  $t(N-1)$  においてオンにされるまで、そのように続く (and so forth)。隣接したスイッチ間の時間遅延は、複数のスイッチのうちの 1 つがオンにされる時、アップストリーム回路 115 が名目供給電圧 (nominal supply voltage) に戻って落ち着く (settle back) のに十分な時間を取るまで次のスイッチがオンにされないように、選ばれ得る。

## 【0018】

[0024] このように、ダウンストリーム回路 120 が覚醒されることになる時、スイッチ 230(1) - 230(N) は、全体のダウンストリーム回路 120 を一度にパワーアップする代わりに、ダウンストリーム回路 120 のセクション 210(1) - 210(N) を連続的にパワーアップするために、連続的にオンにされる。各セクション 210(1) - 210(N) は、ダウンストリーム回路 120 のキャパシタンスのごく一部のみを有する。したがって、スイッチ 230(1) - 230(N) がオンにされる度に、充電される (charged up) 必要があるのはダウンストリーム回路 120 のキャパシタンスのごく一部のみであり、これは格段により小さい電圧降下をもたらす。

## 【0019】

[0025] このアプローチの難点は、ダウンストリーム回路 120 のセクション 210(1) - 210(N) を連続的にパワーアップすることが、ダウンストリーム回路 120 の起動時間 (wakeup time) を増加させることである。したがって、電圧降下制約条件内にまだ留まりながらもダウンストリーム回路の起動時間を低減するために、複数のセクションのサイズを最適化するための技法が望まれることになる。

## 【0020】

[0026] 以下にさらに説明されるように、本開示の実施形態は、電圧降下制約条件内にまだ留まりながらも起動時間を低減するために、ダウンストリーム回路のパワーゲーティングされた複数のセクションをサイジングするための技法を提供する。

## 【0021】

[0027] 上の方程式 (1) は、ダウンストリームキャパシタンス  $C_{dn}$  を、アップストリームキャパシタンス  $C_{up}$  および Droop の関数として (as a function of) 表現するために、以下のように書き直され得る。

## 【数 2】

$$C_{dn} = \left( \frac{Droop * C_{up}}{1 - Droop} \right) \quad (2)$$

方程式 (2) は、方程式 (1) における Droop を電圧降下制約条件に等しいように設定することによって、所与のアップストリームキャパシタンス  $C_{up}$  および電圧降下制約条件に対するダウンストリームキャパシタンス  $C_{dn}$  を決定するために使用されることがある。例えば、0.05 の電圧降下制約条件 (すなわち、供給電圧の 5%) の場合、ダウンストリームキャパシタンス  $C_{dn}$  は、およそ  $0.05263 * C_{up}$  に等しい。

## 【0022】

[0028] 方程式 (2) は、ダウンストリーム回路 120 の各セクションに関するキャパシタンスを決定するために、以下のように、拡張されることができる。

10

20

30

40

【数3】

$$C_{dn}(n) = \left( \frac{Droop * (C_{up} + \sum_{m=1}^{m=n-1} C_{dn}(m))}{1 - Droop} \right) \quad (3)$$

ここで、 $C_{dn}(n)$ は、ダウンストリーム回路120のn番目のセクションに関するキャパシタンスであり、 $C_{up}$ は、アップストリーム回路115のキャパシタンスであり、

【数4】

$$\sum_{m=1}^{m=n-1} C_{dn}(m)$$

10

は、ダウンストリーム回路120の前の複数のセクションのキャパシタンスの合計である。したがって、前の複数のセクションのキャパシタンスは、方程式(3)におけるトータルのアップストリームキャパシタンスの一部として含まれる。これは、ダウンストリーム回路120のn番目のセクションに関するスイッチがオンにされる時間までに、ダウンストリーム回路120の前の複数のセクションが既に供給電圧に充電されているからである。その結果、前の複数のセクションのキャパシタンスにおける電荷は、n番目のセクションのキャパシタンスを充電するのを助けるために利用可能である。このように、前の複数のセクションのキャパシタンスは、n番目のセクションに対してアップストリームであり、したがって、方程式(3)におけるトータルのアップストリームキャパシタンスの一部として含まれる。

20

【0023】

[0029] 方程式(3)から分かるように、より多くのセクションがパワーアップされるにつれて、各セクションに関するキャパシタンスは漸進的に増加する。これは、方程式(3)におけるトータルのアップストリームキャパシタンス(すなわち、

【数5】

$$C_{up} + \sum_{m=1}^{m=n-1} C_{dn}(m)$$

30

)が、より多くのセクションがパワーアップされるにつれて増加するからである。このように、方程式(3)は、ダウンストリーム回路120の複数のセクションが、規定された電圧降下制約条件(例えば、0.05)内にまだ留まりながらも漸進的にサイズが大きくなることができるることを明示している。各セクションのサイズは、そのセクションに関する決定されたキャパシタンスを、ダウンストリーム回路120のキャパシタンス密度(capacitance density)(単位面積(unit area)当たりのキャパシタンス)で割ることによって計算され得る。複数のセクションは漸進的にサイズが大きくなるので、パワーアップされる必要のあるセクションの数は減少し、それにより起動時間を低減する。

【0024】

[0030] 図3は、本開示の実施形態に従って、漸進的にサイズが大きくなる複数のセクション310(1)-310(M)へ分割されたダウンストリーム回路120を示す。上述したように、事実上の(effective)アップストリームキャパシタンスは、より多くのセクションがパワーアップされるにつれて増加するので、セクション310(1)-310(M)は漸進的にサイズが大きくなる。電力スイッチ130は、M個のスイッチ330(1)-330(M)を備え、ここで、各スイッチ330(1)-330(M)は、セクション310(1)-310(M)のうちのそれぞれ1つを電力供給装置110へ選択的に接続するように構成される。

40

【0025】

[0031] ダウンストリーム回路120が非アクティブ状態から覚醒されることになる時、スイッチ330(1)-330(M)は、サイズが大きくなっていく順番で(すなわち、最も小さいセクション310(1)から最も大きなセクション310(M)へと)、ダ

50

ウンストリーム回路 120 のセクション 310(1) - 310(M) を連続的にパワーアップする。セクション 310(1) - 310(M) のサイズを漸進的に大きくすることは、等しいサイズの複数のセクションを使用することに比べて、パワーアップシーケンスの間にパワーアップされることが必要なセクションの数を低減し、したがって、ダウンストリーム回路 120 の起動時間を低減する。

#### 【0026】

[0032] 方程式(3)は、本開示の実施形態に従って、ダウンストリーム回路 120 のパワーゲーティングされたセクション 310(1) - 310(M) のサイズを決定するための反復的なプロセスにおいて使用することができる。第1の反復において、ダウンストリーム回路 120 の第1のセクション 310(1) に関するキャパシタンス  $C_{dn}(1)$  が、アップストリーム回路 115 のキャパシタンス  $C_{up}$  と電圧降下制約条件とに基づいて、方程式(3)を使用して決定される。第1の反復について、方程式(3)は、前のセクションがないので、方程式(2)に等しい。電圧降下制約条件が 0.05 である例の場合、第1のセクション 310(1) のキャパシタンス  $C_{dn}(1)$  は、おおよそ 0.05263 \*  $C_{up}$  である。第1のセクション 310(1) のキャパシタンス  $C_{dn}(1)$  が決定された後、第1のセクション 310(1) のサイズは、第1のセクション 310(1) のキャパシタンス  $C_{dn}(1)$  を、ダウンストリーム回路 120 のキャパシタンス密度(単位面積当たりのキャパシタンス)で割ることによって、決定され得る。

#### 【0027】

[0033] 第2の反復において、ダウンストリーム回路 120 の第2のセクション 310(2) に関するキャパシタンス  $C_{dn}(2)$  は、アップストリーム回路 115 のキャパシタンス  $C_{up}$  と、第1のセクション 310(1)(前のセクション)のキャパシタンス  $C_{dn}(1)$  と、電圧降下制約条件とに基づいて、方程式(3)を使用して決定される。電圧降下制約条件が 0.05 である例の場合、第2のセクション 310(2) のキャパシタンス  $C_{dn}(2)$  は、おおよそ 0.0554 \*  $C_{up}$  である。したがって、第2のセクション 310(2) のキャパシタンス  $C_{dn}(2)$  は、第1のセクション 310(1) のキャパシタンス  $C_{dn}(1)$  よりも大きい。第2のセクション 310(2) のキャパシタンス  $C_{dn}(2)$  が決定された後、第2のセクション 310(2) のサイズは、第2のセクション 310(2) のキャパシタンス  $C_{dn}(2)$  を、ダウンストリーム回路 120 のキャパシタンス密度で割ることによって、決定され得る。第2のセクション 310(2) のキャパシタンス  $C_{dn}(2)$  は、第1のセクション 310(1) のキャパシタンス  $C_{dn}(1)$  よりも大きいので、第2のセクション 310(2) のサイズは、(比較的一様な( relatively uniform) キャパシタンス密度を想定すると) 第1のセクション 310(1) のサイズよりも大きい。

#### 【0028】

[0034] 第3の反復では、ダウンストリーム回路 120 の第3のセクション 310(3) に関するキャパシタンス  $C_{dn}(3)$  は、アップストリーム回路 115 のキャパシタンス  $C_{up}$  と、第1のおよび第2のセクション 310(1) および 310(2)(前のセクション)のキャパシタンス  $C_{dn}(1)$  および  $C_{dn}(2)$  の合計と、電圧降下制約条件とに基づいて、方程式(3)を使用して決定される。電圧降下制約条件が 0.05 である例の場合、第3のセクションのキャパシタンス  $C_{dn}(3)$  は、おおよそ 0.0583 \*  $C_{up}$  である。したがって、第3のセクション 310(3) のキャパシタンス  $C_{dn}(3)$  は、第1のおよび第2のセクション 310(1) および 310(2) の各々のキャパシタンスよりも大きい。第3のセクション 310(3) のキャパシタンス  $C_{dn}(3)$  が決定された後、第3のセクション 310(3) のサイズは、第3のセクション 310(3) のキャパシタンス  $C_{dn}(3)$  を、ダウンストリーム回路 120 のキャパシタンス密度で割ることによって、決定され得る。第3のセクション 310(3) のキャパシタンス  $C_{dn}(3)$  は、第1のおよび第2のセクション 310(1) および 310(2) の各々のキャパシタンスよりも大きいので、第3のセクション 310(3) のサイズは、(比較的一様なキャパシタンス密度を想定すると) 第1のおよび第2のセクション 310(1) およ

10

20

30

40

50

び 310(2) の各々のサイズよりも大きい。

**【0029】**

[0035] 後続のセクション 310(4) - 310(M) のサイズは、追加的な反復を実行することにより決定され得、そこでは、各後続のセクションのキャパシタンスは、アップストリーム回路 115 のキャパシタンス  $C_{up}$  と、前の複数のセクションのキャパシタンスの合計と、電圧降下制約条件とに基づいて、方程式(3)を使用して決定される。各後続のセクションのサイズは、その後続のセクションに関する決定されたキャパシタンスを、キャパシタンス密度で割ることによって決定される。前の複数のセクションのキャパシタンスの合計は各反復において増加するので、キャパシタンス(およびゆえにサイズ)は、各反復において増加する。

10

**【0030】**

[0036] 反復的なプロセスは、複数のセクションのサイズの合計がダウンストリーム回路 120 の全エリアをカバーするまで続き得る。各反復は 1 つのセクションに対応するので、反復的なプロセスがストップする時、反復の数は、ダウンストリーム回路におけるセクション(電力ドメイン)の数に等しくなる。したがって、反復的なプロセスはまた、ダウンストリーム回路 120 が分割されることになるセクションの数(すなわち、M)を決定するためにも使用され得る。

**【0031】**

[0037] 反復的なプロセスによって決定される複数のセクションのサイズの合計は、ダウンストリーム回路 120 のエリアよりも若干大きいことがあり得る。例えば、セクション 310(1) - 310(M-1) のサイズの合計がダウンストリーム回路 120 のエリアよりも若干小さいことがあり得る一方で、セクション 310(1) - 310(M) のサイズの合計がダウンストリーム回路 120 のエリアよりも若干大きいことがあり得る。この場合、セクション 310(1) - 310(M) のサイズは、セクション 310(1) - 310(M) のサイズの合計をダウンストリーム回路 120 のエリアにフィットさせるために、少量だけ比例的に(proportionally) 低減され得る。

20

**【0032】**

[0038] 図 4 は、本開示の実施形態に従って、ダウンストリーム回路におけるパワーゲーティングされた複数のセクションをサイジングするための方法 400 を示す。

**【0033】**

30

[0039] ステップ 410 において、第 1 のセクションに関するキャパシタンスは、アップストリーム回路のキャパシタンスと電圧降下制約条件とに基づいて、決定される。例えば、第 1 のセクション(例えば、310(1))に関するキャパシタンス(例えば、 $C_{dn}(1)$ )は、方程式(3)を使用して決定され得る。

**【0034】**

[0040] ステップ 420 において、第 2 のセクションに関するキャパシタンスは、アップストリーム回路のキャパシタンスと、電圧降下制約条件と、第 1 のセクションに関する決定されたキャパシタンスとに基づいて、決定される。例えば、第 2 のセクション(例えば、310(2))に関するキャパシタンス(例えば、 $C_{dn}(2)$ )は、方程式(3)を使用して決定され得、そこでは、方程式(3)における実効アップストリームキャパシタンス(effective upstream capacitance)は、アップストリーム回路(例えば、アップストリーム回路 115)のキャパシタンスと第 1 のセクションに関するキャパシタンスとの合計である。

40

**【0035】**

[0041] ステップ 430 において、第 3 のセクションに関するキャパシタンスは、アップストリーム回路のキャパシタンスと、電圧降下制約条件と、第 1 のおよび第 2 のセクションに関する決定されたキャパシタンスとに基づいて、決定される。例えば、第 3 のセクション(例えば、310(3))に関するキャパシタンス(例えば、 $C_{dn}(3)$ )は、方程式(3)を使用して決定され得、そこでは、方程式(3)における実効アップストリームキャパシタンスは、アップストリーム回路(例えば、アップストリーム回路 115)

50

のキャパシタンスと第 1 のセクションおよび第 2 のセクションに関するキャパシタンスとの合計である。

#### 【 0 0 3 6 】

[0042] ステップ 440において、第 1 の、第 2 の、および第 3 のセクションの各々のサイズは、それらセクションの各々に関する決定されたキャパシタンスに基づいて、決定される。例えば、各セクションのサイズは、そのセクションに関する決定されたキャパシタンスを、ダウンストリーム回路のキャパシタンス密度で割ることによって、決定され得る。

#### 【 0 0 3 7 】

[0043] 上述したように、電圧降下を決定するための方程式(1)は、スイッチが閉じられている時に有する抵抗がゼロ(すなわち、オン抵抗ゼロ)である理想的な電力スイッチを想定する。その結果、方程式(1)は、電力供給装置 110 からの電荷の寄与なく(with no charge contribution)スイッチが閉じられる時のアップストリーム回路 115 におけるキャパシタからダウンストリームキャパシタ 120 におけるキャパシタへの電荷の即座の転送(instantaneous transfer of charge)を電圧降下の原因と想定する。方程式(1)において電力供給装置 110 からの電荷の寄与がない理由は、PDN におけるインダクタンスが、電力供給装置 110 が電荷をアップストリーム回路 115 に即座に供給することを防ぐからである。

#### 【 0 0 3 8 】

[0044] 実際には、電力スイッチは、スイッチが閉じられる時、少量の抵抗を有し得る。スイッチの抵抗およびダウンストリーム回路 120 のキャパシタンスは、ある時間期間にわたってアップストリーム回路 115 からダウンストリーム回路 120 へ電荷が転送されることを引き起こすRC時定数(an RC time constant)を形成する。これは、電力供給装置 110 に、電圧降下を低減するためにアップストリーム回路 115 に電荷を供給するための時間を与える。その結果、実際の電圧降下は、方程式(1)で予測される電圧降下よりも小さい。

#### 【 0 0 3 9 】

[0045] それでも、方程式(1)によって予測される電圧降下は、スイッチの抵抗が低い時、実際の電圧降下の良好な近似値(good approximation)を提供する。これは、スイッチの抵抗が低い時、RC時定数は、電力供給装置 110 とアップストリーム回路 115 との間のPDNインダクタンス(例えば、基板およびパッケージングインダクタンス(packaging inductance))に関連する時定数よりも格段に小さいからである。その結果、アップストリーム回路 115 からダウンストリーム回路 120 への電荷の転送は、電力供給装置 110 からアップストリーム回路 115 への電荷の転送よりも格段に速く、その場合、方程式(1)によって予測される電圧降下は、実際の電圧降下に比較的近い。

#### 【 0 0 4 0 】

[0046] 上述したように、方程式(1)は、オン抵抗がゼロの(with zero on resistance)理想的なスイッチを想定しているので、方程式(1)を使用して決定される電圧降下は、実際の電圧降下よりも小さい。方程式(1)は、以下のように、電圧降下の式に補正係数(correction factor)を乗じることによって、スイッチの抵抗を考慮に入れるよう修正され得る。

#### 【 数 6 】

$$Droop = \left(1 - \frac{C_{up}}{C_{up} + C_{dn}}\right) * f \quad (4)$$

ここで、f は補正係数である。実際の電圧降下は、方程式(1)によって決定される電圧降下より小さいので、補正係数 f は、1 より小さい。例えば、補正係数は、0.8 と 0.9 との間の値を有し得る。スイッチのオン抵抗が低いほど、スイッチはオン抵抗がゼロである理想的なスイッチにより近く近似(approximates)し、補正係数はより 1 に近くなる

10

20

30

40

50

。補正係数  $f$  は、方程式(1)を使用して決定される電圧降下を、物理デバイスおよび/または回路シミュレーションの測定値から取得された電圧降下と比較することにより決定され得る。

**【0041】**

[0047] ダウンストリームキャパシタンス  $C_{dn}$  を決定するための方程式(2)は、以下のように、方程式(4)に基づいて、修正され得る。

**【数7】**

$$C_{dn} = \left( \frac{\frac{1}{f} * Droop * C_{up}}{1 - \frac{1}{f} * Droop} \right) \quad (5)$$

10

補正係数  $f$  は 1 より小さいので、方程式(5)は、所与の電圧降下制約条件およびアップストリームキャパシタンス  $C_{up}$  に関して、方程式(2)よりも大きなダウンストリームキャパシタンス  $C_{dn}$  を決定する。ダウンストリーム回路 120 のセクションのキャパシタンスを決定するための方程式(3)は、以下のように、同様の方法で修正され得る。

**【数8】**

$$C_{dn}(n) = \left( \frac{\frac{1}{f} * Droop * (C_{up} + \sum_{m=1}^{m=n-1} C_{dn}(m))}{1 - \frac{1}{f} * Droop} \right) \quad (6)$$

20

方程式(6)は、ダウンストリーム回路 120 の各セクション 310(1) - 310(M) に関するキャパシタンス  $C_{dn}(1) - C_{dn}(M)$  を決定するために使用され得る。例えば、方程式(6)は、上で説明された方法 400 および/または反復的なプロセスにおいて使用され得る。方程式(6)は、ダウンストリーム回路 120 のセクション 310(1) - 310(M) に関して、方程式(3)よりも大きなキャパシタンス  $C_{dn}(1) - C_{dn}(M)$  を、よってそれらセクションに関してより大きなサイズを、決定する。

**【0042】**

30

[0048] 図 5 は、本開示の実施形態に従って、パワーアップシーケンスの間の、アップストリーム回路 115 に関する電圧波形 510、ならびにダウンストリーム回路 120 の第 1 の 2 つのセクション 310(1) および 310(2) に関する電圧波形 520(1) および 520(2) の例を示す。時間  $t_0$  の前には、アップストリーム回路 115 の電圧は、電力供給装置 110 の供給電圧  $V_{dd}$  におおよそ等しい。また、時間  $t_0$  の前には、ダウンストリーム回路 120 は、非アクティブであり、電力スイッチ 130 のスイッチ 330(1) - 330(M) の全ては、開かれている。その結果、第 1 のおよびセクションセクション 310(1) および 310(2) の各々の電圧は、おおよそゼロボルトである。

**【0043】**

40

[0049] 時間  $t_0$  において、第 1 のセクション 310(1) に関するスイッチ 330(1) は、第 1 のセクション 310(1) をパワーアップするために閉じられる。これによって、電荷が、アップストリーム回路 115 におけるキャパシタからスイッチ 330(1) を通して第 1 のセクション 310(1) におけるキャパシタへと素早く流れる。電荷の転送は、アップストリーム回路 115 の電圧を素早く低減し、アップストリーム回路 115 における電圧降下 515(1) をもたらす。低いオン抵抗を有するスイッチ (a switch having low on resistance) の場合、PDN のインダクタンスが電力供給装置 110 からアップストリーム回路 115 への転送電荷を遅くするので、電力供給装置 110 からの電荷は、電圧降下 515(1) にそれほどの影響を与えない。電圧降下 515(1) は、方程式(3) または(6) に従って第 1 のセクション 310(1) をサイジングすること

50

で、電圧降下制約条件（例えば、0 . 0 5）によって制限（bounded）され得る。図5に示される電圧降下515(1)のサイズは、説明し易さのために誇張されていることは理解されるべきである。

#### 【0044】

[0050] 電圧降下515(1)の後、第1のセクション310(1)およびアップストリーム回路115の電圧が発振(oscillate)し、第1のセクション310(1)およびアップストリーム回路115においてパワーレールにおける電圧リップル(a voltage ripple)525(1)を生成する。この発振は、PDNのインダクタンス、第1のセクション310(1)およびアップストリーム回路115のキャパシタンス、並びに、PDN、アップストリーム回路115および第1のセクション310(1)の抵抗によって形成されるRLC回路の共振によって引き起こされる。共振は、第1のスイッチ330(1)を閉じることからもたらされる電圧降下515(1)によってトリガされる。RLC回路の共振周波数は、以下によって近似され得る。

10

#### 【数9】

$$\omega = \frac{1}{\sqrt{LC}} \quad (7)$$

ここで、 $\omega$ は共振周波数であり、LはPDNのインダクタンスを含み、およびCは第1のセクション310(1)およびアップストリーム回路115のキャパシタンスを含む。リップル525(1)は、PDN、アップストリーム回路115および第1のセクション310(1)の抵抗によって減少させられ(dampened)、それはエネルギーを消散(dissipate)する。その結果、リップル525(1)は、時間の経過と共に消滅し(dies out over time)、第1のセクション310(1)およびアップストリーム回路115の電圧は、供給電圧Vddに近い値に落ち着く。

20

#### 【0045】

[0051] 時間t0から時間遅延後、第2のセクション310(2)に関するスイッチ330(2)は、第2のセクション310(2)をパワーアップするために時間t1において閉じられる。1つの態様では、時間遅延は、第1のセクション310(1)およびアップストリーム回路115における電圧が、(整定時間(settling time)と称される)供給電圧Vddに近い値に落ち着くために十分な時間を提供する。例えば、整定時間は、リップル525(1)の電圧スイング(swing)が名目供給電圧の2パーセントより小さい値に減少するためにかかる時間であり得る。したがって、第2のセクション310(2)に関するスイッチ330(2)が閉じられる時間までに、アップストリーム回路115および第1のセクション310(1)は、およそ供給電圧Vddまで充電されている。

30

#### 【0046】

[0052] 時間t1において、スイッチ330(2)は、第2のセクション310(2)をアップストリーム回路115および第1のセクション310(1)に接続し、これによって電荷が第1のセクション310(1)およびアップストリーム回路115におけるキャパシタから第2のセクション310(2)におけるキャパシタへと素早く流れれる。電荷の転送は、第1のセクション310(1)およびアップストリーム回路115の電圧を素早く低減し、アップストリーム回路115および第1のセクション310(1)における電圧降下515(2)をもたらす。電圧降下515(2)は、方程式(3)または(6)に従って第2のセクション310(2)をサイジングすることで、電圧制約条件（例えば、0 . 0 5）によって制限され得る。図5に示される電圧降下515(2)のサイズは、説明し易さのために誇張されていることは理解されるべきである。

40

#### 【0047】

[0053] 電圧降下515(2)の後、第1のおよび第2のセクション310(1)および310(2)、ならびにアップストリーム回路115の電圧が発振し、パワーレールにおいて電圧リップル525(2)を生成する。リップル525(2)は、時間の経過と共に消滅し、第1のおよび第2のセクション310(1)および310(2)、ならびにア

50

ップストリーム回路 115 の電圧は、供給電圧 Vdd に近い値に落ち着く。

#### 【0048】

[0054] 時間  $t_1$  からの時間遅延の後、第 3 のセクション 310(3) に関するスイッチ 330(3) は、第 3 のセクション 310(3)(図 5 に示されていない) をパワーアップするために閉じられる。時間遅延は、第 3 のセクション 310(3) に関するスイッチ 330(3) が閉じられる時間までに、アップストリーム回路 115 ならびに第 1 のおよび第 2 のセクション 310(1) および 310(2) がおおよそ供給電圧 Vdd まで充電されているように、リップル 525(2) の整定時間におおよそ等しい可能性がある。

#### 【0049】

[0055] 図 6 は、本開示の実施形態に従って、電力スイッチ 130 の例示的なインプリメンテーションを示す。この実施形態では、ダウンストリーム回路 120 のセクション 310(1) - 310(M) を連続的にパワーアップするためのスイッチ 632(1) - 632(M) は、複数の P 型金属酸化膜半導体 (PMOS) ドラッグタススイッチを備える。各 PMOS スイッチ 632(1) - 632(M) は、それぞれのゲートをハイ (high) に駆動することによって開かれ (オフにされ) 得、それぞれのゲートをロー (low) に駆動することによって閉じられ (オンにされ) 得る。図 6 は、各セクション 310(1) - 310(M) につき 1 つの PMOS スイッチ 632(1) - 632(M) を示しているが、電力スイッチ 130 は、各セクション 310(1) - 310(M) につき 2 つ以上の PMOS スイッチ 632(1) - 632(M) を備え得ることは理解されるべきである。例えば、電力スイッチ 130 は、各セクションに関して並列に接続された複数の PMOS スイッチを備え得る。

#### 【0050】

[0056] この実施形態では、スイッチ 632(1) - 632(M) は、電力管理デバイス 640 によって制御される。ダウンストリーム回路 120 が非アクティブ状態に入る場合、電力管理デバイス 640 は、電力漏れを低減するためにダウンストリーム回路 120 の各セクション 310(1) - 310(M) を、電力供給装置 110 から切断するために、スイッチ 632(1) - 632(M) の全てを開き得る。ダウンストリーム回路 120 が非アクティブ状態から覚醒される場合、電力管理デバイス 640 は、ダウンストリーム回路 120 のセクション 310(1) - 310(M) を連続的にパワーアップするために、パワーアップシーケンスの間にスイッチ 632(1) - 632(M) を連続的に閉じ (オンにし) 得る。セクション 310(1) - 310(M) は、漸進的にサイズが大きくなり得、電力管理デバイス 640 は、セクション 310(1) - 310(M) がサイズが大きくなっていく順番で (すなわち、最も小さいセクション 310(1) から最も大きなセクション 310(M) へと)、パワーアップされるように、スイッチ 632(1) - 632(M) を連続的に閉じ (オンにし) 得る。

#### 【0051】

[0057] 電力管理デバイス 640 は、遅延チェーン 652 を形成するために直列に結合された複数の遅延素子 650(1) - 650(M-1) およびパワーゲートコントローラ 645 を備える。電力管理デバイス 640 の出力は、第 1 の遅延素子 650(1) の入力および第 1 のスイッチ 632(1) のゲートに結合される。遅延素子 650(1) - 650(M-1) の各々の出力は、スイッチ 632(2) - 632(M) のうちのそれぞれ 1 つのゲートに結合される。より具体的には、第 1 の遅延素子 650(1) の出力は、第 2 のスイッチ 632(2) のゲートに結合され、第 2 の遅延素子 650(2) の出力は、第 3 のスイッチ 632(3) のゲートに結合される、等 (and so on) である。

#### 【0052】

[0058] ダウンストリーム回路 120 が非アクティブ状態から覚醒される場合、パワーゲートコントローラ 645 は、スイッチ 632(1) - 632(M) を連続的にオンにするために、時間  $t_0$  において遅延チェーン 652 にパワーアップ信号を出力する。例えば、ダウンストリーム回路 120 は、アプリケーションまたは他の回路がダウンストリーム回路 120 を使用する必要がある時、覚醒され得る。スイッチ 632(1) - 632(M)

10

20

30

40

50

) が PMOS スイッチを使用してインプリメントされる時、PMOS スイッチのゲートをローに駆動することは PMOS スイッチをオンにするので、パワーアップ信号は、低電圧信号（論理ゼロ）を備え得る。

#### 【 0 0 5 3 】

[0059] 時間  $t_0$  において、パワーアップ信号は、第 1 のセクション 310(1) をパワーアップするために第 1 のスイッチ 632(1) をオンにする。第 1 の遅延素子 650(1) は、第 1 の時間遅延だけパワーアップ信号を遅延させ、時間  $t_1$  において第 2 の遅延素子 650(2) および第 2 のスイッチ 632(2) へパワーアップ信号を出力する。したがって、第 1 の遅延素子 650(1) の出力は、時間  $t_0$  から第 1 の時間遅延後に、第 2 のスイッチ 632(2) をオンにする。第 1 の時間遅延は、第 1 のセクション 310(1) およびアップストリーム回路 115 における電圧のための整定時間におおよそ等しい可能性がある。10

#### 【 0 0 5 4 】

[0060] 第 2 の遅延素子 650(2) は、第 2 の時間遅延だけパワーアップ信号を遅延させ、時間  $t_2$  において第 3 の遅延素子（図 6 に示されていない）および第 3 のスイッチ 632(3) にパワーアップ信号を出力する。したがって、第 2 の遅延素子 650(2) の出力は、第 2 の時間遅延の後、第 3 のスイッチ 632(3) をオンにする。第 2 の時間遅延は、第 1 のおよび第 2 のセクション 310(1) および 310(2)、ならびにアップストリーム回路 115 における電圧のための整定時間におおよそ等しい可能性がある。20

#### 【 0 0 5 5 】

[0061] 一般に、各遅延素子 650(1) - 650(M-1) は、その遅延素子の時間遅延だけパワーアップ信号を遅延させる。したがって、各遅延素子 650(1) - 650(M-1) の出力は、前のスイッチがオンにされた時間から時間遅延後に、それぞれのスイッチ 632(2) - 632(M) をオンにし、ここで、時間遅延は、その遅延素子の時間遅延におおよそ等しい。各遅延素子 650(1) - 650(M-1) の時間遅延は、前の複数のセクションおよびアップストリーム回路 115 における電圧のための整定時間におおよそ等しい可能性がある。20

#### 【 0 0 5 6 】

[0062] 最後の遅延素子 650(M-1) の出力は、パワーゲートコントローラ 645 に結合され得、その場合、パワーアップ信号は、遅延素子 650(1) - 650(M-1) を通して伝播した後、パワーゲートコントローラ 645 へ戻る。この実施形態では、パワーゲートコントローラ 645 は、パワーアップ信号の戻りを、ダウンストリーム回路 120 のセクション 310(1) - 310(M) がパワーアップされたことを示すインジケーションとして扱い得る。30

#### 【 0 0 5 7 】

[0063] 1 つの実施形態では、ダウンストリーム回路 120 は、さまざまなサイズのパワーゲーティングされた複数のセクションへ分割されることができるメモリを備え得る。例えば、メモリは、多数のビット線を備え得、そこでは、各セクション 310(1) - 310(M) は、ビット線のサブセットを備える。この例では、各ビット線への電力は、別個のスイッチによって制御され得る。これは、回路設計者に、各セクションのビット線の数の選択について、ゆえに各セクションのサイズについて、柔軟性を提供する。セクションのビット線の数が多くなる程、そのセクションのサイズは大きくなる。40

#### 【 0 0 5 8 】

[0064] 各セクションのサイズは、複数の異なるサイズから選択され得、ここで、各サイズは、異なる数のビット線に対応する。この例では、セクションのサイズが決定される時（例えば、方程式(3)または(6)に基づいて）、回路設計者は、複数のサイズから、そのセクションの決定されたサイズに最も近いサイズを選択し得る。最も近いサイズが、決定されたよりサイズよりも大きい場合には、回路設計者は、電圧降下制約条件が満たされることを保証するために、決定されたサイズより小さい、最も近いサイズを選択し得る。50

**【0059】**

[0065] 図7は、本開示の実施形態に従って、漸進的にサイズが大きくなる複数のセクションを備える回路をパワーアップするための方法700を示す。

**【0060】**

[0066] ステップ710において、回路をパワーアップするための信号が受信される。例えば、信号は、パワーゲートコントローラ（例えば、パワーゲートコントローラ645）によって出力されたパワーアップ信号を備え得る。

**【0061】**

[0067] ステップ720において、信号に応答して、複数のセクションは、サイズが大きくなっていく順番で、連続的にパワーアップされる。例えば、パワーアップ信号は、複数のセクション（例えば、310(1) - 310(M)）を電力供給装置（例えば、電力供給装置110）へ接続する複数のスイッチ（例えば、スイッチ632(1) - 632(M)）を、連続的にオンにする遅延チェーン（例えば、遅延チェーン625）を伝播（propagate down）し得る。10

**【0062】**

[0068] 本開示の先の説明は、当業者が本開示を製造するまたは使用することを可能にするために提供される。本開示への様々な修正は、当業者にとって容易に明らかであろうし、ここに定義された一般的な原理は、本開示の範囲または精神から逸脱することなく、他のバリエーションにも適用され得る。したがって、本開示は、ここに説明された例に限定されるようには意図されておらず、ここに開示された原理および新規な特徴と一致する最も広い範囲を与えられるべきである。20

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

**[C1]**

ダウンストリーム回路におけるパワーゲーティングされた複数のセクションをサイジングするための方法であって、

アップストリーム回路のキャパシタンスと、電圧降下制約条件とに基づいて、第1のセクションに関するキャパシタンスを決定することと、

前記アップストリーム回路の前記キャパシタンスと、前記電圧降下制約条件と、前記第1のセクションに関する前記決定されたキャパシタンスとに基づいて、第2のセクションに関するキャパシタンスを決定することと、30

前記アップストリーム回路の前記キャパシタンスと、前記電圧降下制約条件と、前記第1のおよび第2のセクションに関する前記決定されたキャパシタンスとに基づいて、第3のセクションに関するキャパシタンスを決定することと、

前記複数のセクションの各々に関する前記決定されたキャパシタンスに基づいて、前記第1の、第2の、および第3のセクションの各々のサイズを決定することと、

を備える、方法。

**[C2]**

前記ダウンストリーム回路は、メモリを備える、C1に記載の方法。

**[C3]**

前記第2のセクションに関する前記キャパシタンスを決定することは、前記アップストリーム回路の前記キャパシタンスと、前記第1のセクションに関する前記決定されたキャパシタンスとの合計に基づいて、前記第2のセクションに関する前記キャパシタンスを決定することを備える、C1に記載の方法。40

**[C4]**

前記第3のセクションに関する前記キャパシタンスを決定することは、前記アップストリーム回路の前記キャパシタンスと、前記第1のセクションに関する前記決定されたキャパシタンスと、前記第2のセクションに関する前記決定されたキャパシタンスとの合計に基づいて、前記第3の第2のセクションに関する前記キャパシタンスを決定することを備える、C3に記載の方法。

**[C5]**

10

20

30

40

50

前記第1の、第2の、および第3のセクションの各々の前記サイズを決定することは、前記複数のセクションの各々に関する前記決定されたキャパシタンスを、キャパシタンス密度で割ることを備える、C 1に記載の方法。

## [ C 6 ]

前記第1のセクションに関する前記キャパシタンスを決定することは、補正係数に基づいて、前記第1のセクションに関する前記キャパシタンスを決定することを備える、C 1に記載の方法。

## [ C 7 ]

前記補正係数は少なくとも0.8の値を有する、C 6に記載の方法。

## [ C 8 ]

前記電圧降下制約条件は、おおよそ0.05またはそれより小さい、C 1に記載の方法。

## [ C 9 ]

漸進的にサイズが大きくなる複数のセクションを備える回路をパワーアップするための方法であって、

前記回路をパワーアップするための信号を受信することと、

前記信号に応答して、サイズが大きくなっていく順番で、前記複数のセクションを連続的にパワーアップすることと、

を備える、方法。

## [ C 10 ]

前記複数のセクションは異なるキャパシタンスを有し、前記複数のセクションを連続的にパワーアップすることは、キャパシタンスが増えていく順番で前記複数のセクションを連続的にパワーアップすることを備える、C 9に記載の方法。

## [ C 11 ]

前記回路は、前記複数のセクションに分割されたメモリを備える、C 9に記載の方法。

## [ C 12 ]

前記複数のセクションの各々は、別個のスイッチによってパワーレールに選択的に接続され、前記複数のセクションを連続的にパワーアップすることは、前記複数のスイッチを連続的に閉じることを備える、C 9に記載の方法。

## [ C 13 ]

前記複数のスイッチを連続的に閉じることは、

前記複数のセクションのうちの第1の1つに関する前記スイッチを閉じることと、

時間遅延の後に、前記複数のセクションのうちの第2の1つに関する前記スイッチを開じることと、ここにおいて、前記時間遅延は、前記複数のセクションのうちの前記第1の1つに関する前記スイッチを前記閉じることによってトリガされる前記パワーレールにおける電圧リップルの整定時間と等しいかまたはそれより長い、

を備える、C 12に記載の方法。

## [ C 14 ]

漸進的にサイズが大きくなる複数のセクションを備える回路をパワーアップするための装置であって、

前記回路をパワーアップするための信号を受信するための手段と、

前記信号に応答して、サイズが大きくなっていく順番で、前記複数のセクションを連続的にパワーアップするための手段と、

を備える、装置。

## [ C 15 ]

前記複数のセクションは異なるキャパシタンスを有し、前記複数のセクションを連続的にパワーアップするための前記手段は、キャパシタンスが増えていく順番で前記複数のセクションを連続的にパワーアップするための手段を備える、C 14に記載の装置。

## [ C 16 ]

前記回路は、前記複数のセクションに分割されたメモリを備える、C 14に記載の装置

10

20

30

40

50

。

## [ C 1 7 ]

前記複数のセクションの各々は、別個のスイッチによってパワーレールに選択的に接続され、および前記複数のセクションを連続的にパワーアップするための前記手段は、前記複数のスイッチを連続的に閉じるための手段を備える、C 1 4 に記載の装置。

## [ C 1 8 ]

前記複数のスイッチを連続的に閉じるための前記手段は、

前記複数のセクションのうちの第1の1つに関する前記スイッチを閉じるための手段と

<sup>10</sup>

時間遅延の後に、前記複数のセクションのうちの第2の1つに関する前記スイッチを閉じるための手段と、ここにおいて、前記時間遅延は、前記複数のセクションのうちの前記第1の1つに関する前記スイッチを前記閉じることによってトリガされる前記パワーレールにおける電圧リップルの整定時間と等しいかまたはそれより長い、

を備える、C 1 7 に記載の装置。

## [ C 1 9 ]

漸進的にサイズが大きくなる複数のセクションを備える回路をパワーアップするための装置であって、

複数のスイッチと、ここにおいて、前記複数のスイッチの各々は、前記複数のセクションのうちのそれぞれ1つをパワーレールに選択的に接続するように構成される、

<sup>20</sup>

前記複数のスイッチが、サイズが大きくなっていく順番で前記複数のセクションを連続的にパワーアップするように、前記複数のスイッチを連続的に閉じるように構成される、

電力管理デバイスと、

を備える、装置。

## [ C 2 0 ]

前記複数のセクションは異なるキャパシタンスを有し、前記電力管理デバイスは、前記複数のスイッチが、キャパシタンスが増えていく順番で前記複数のセクションを連続的にパワーアップするように、前記複数のスイッチを連続的に閉じるように構成される、C 1 9 に記載の装置。

## [ C 2 1 ]

前記回路は、前記複数のセクションに分割されたメモリを備える、C 1 9 に記載の装置

<sup>30</sup>

。

## [ C 2 2 ]

前記電力管理デバイスは、

遅延チェーンを形成するために直列に結合された複数の遅延素子と、各スイッチは、前記遅延チェーンに沿った異なるポイントに結合される、

前記回路が非アクティブ状態からパワーアップされることになる場合、パワーアップ信号を前記遅延チェーンへ出力するように構成されるパワーゲートコントローラと、

を備える、C 1 9 に記載の装置。

## [ C 2 3 ]

前記複数のスイッチの各々は、1つ以上のP型金属酸化膜半導体(PMOS)トランジスタを備え、前記パワーアップ信号は低電圧信号である、C 2 2 に記載の装置。

<sup>40</sup>

## [ C 2 4 ]

前記遅延素子のうちの1つの時間遅延は、前記複数のスイッチのうちの1つを閉じることによってトリガされる前記パワーレールにおける電圧リップルの整定時間と等しいかまたはそれより長い、C 2 3 に記載の装置。

【図1】

図1

FIG. 1

【図2】

図2

FIG. 2

【図3】

図3

FIG. 3

【図4】

図4

FIG. 4

【図5】

図5

【図6】

図6

【図7】

図7

---

フロントページの続き

(51)Int.Cl. F I

**G 0 6 F 1/3296 (2019.01)** G 0 6 F 1/3296

(72)発明者 コーツ、ライアン・マイケル

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 工藤 一光

(56)参考文献 特開2013-250964(JP,A)

特開2011-199094(JP,A)

特表2010-532058(JP,A)

特開2009-240153(JP,A)

米国特許出願公開第2013/0099570(US,A1)

米国特許出願公開第2008/0120514(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 0 6 F 1 / 2 6 - 1 / 3 2 9 6

H 0 2 J 1 / 0 0 - 1 / 0 2

H 0 3 K 5 / 1 3 - 5 / 1 3 4

H 0 3 K 1 9 / 0 0

H 0 3 K 1 9 / 0 9 4