(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5107680号

(P5107680)

(45) 発行日 平成24年12月26日(2012.12.26)

(24) 登録日 平成24年10月12日(2012.10.12)

(51) Int.Cl.

H01L 21/336 (2006.01)

H01L 29/78 (2006.01)

F 1

H01L 29/78 301S

請求項の数 14 (全 25 頁)

(21) 出願番号 特願2007-297639 (P2007-297639)

(22) 出願日 平成19年11月16日 (2007.11.16)

(65) 公開番号 特開2009-123997 (P2009-123997A)

(43) 公開日 平成21年6月4日 (2009.6.4)

審査請求日 平成22年2月18日 (2010.2.18)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 110001427

特許業務法人前田特許事務所

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板内に形成された素子分離領域と、

前記素子分離領域に囲まれた前記半導体基板からなり、トレンチ部を有する活性領域と、

前記活性領域上に形成されたゲート電極と、前記ゲート電極の側面上であって、平面的に見て前記ゲート電極と前記トレンチ部との間に形成された第1のサイドウォールと、前記トレンチ部内に充填され、前記活性領域におけるチャネル領域に対して応力を生じさせる第1導電型のシリコン混晶層とを有する第1導電型のMISトランジスタと、

前記トレンチ部と前記素子分離領域との間に設けられ、前記半導体基板からなる基板領域と、

前記基板領域に形成された第1導電型の不純物領域と、

前記素子分離領域上に形成されたダミーゲート電極と、前記ダミーゲート電極の側面上に形成された第2のサイドウォールとを有するマスク部とを備え、

前記基板領域上には、前記マスク部の一部が形成されていることを特徴とする半導体装置。

## 【請求項 2】

請求項1に記載の半導体装置において、

前記マスク部の一部は、前記第2のサイドウォールからなることを特徴とする半導体裝置。

10

20

置。

**【請求項 3】**

請求項1又は2に記載の半導体装置において、

前記素子分離領域は、ゲート長方向の一方に形成された第1の素子分離領域と、ゲート長方向の他方に形成された前記第1の素子分離領域よりも分離幅の広い第2の素子分離領域とを有し、

前記ダミーゲート電極は、前記第1の素子分離領域上に形成され、前記ゲート電極のゲート長よりも大きいゲート長を有する第1のダミーゲート電極と、前記第2の素子分離領域上に形成され、前記ゲート電極のゲート長と同一のゲート長を有する第2のダミーゲート電極とを有していることを特徴とする半導体装置。 10

**【請求項 4】**

請求項1～3のうちいずれか1項に記載の半導体装置において、

前記第1のサイドウォールは、断面形状がL字状の第1絶縁膜からなる第1の内側サイドウォールと、前記第1の内側サイドウォール上に形成された第2絶縁膜からなる第1の外側サイドウォールとで構成されており、

前記第2のサイドウォールは、断面形状がL字状の前記第1絶縁膜からなる第2の内側サイドウォールと、前記第2の内側サイドウォール上に形成された前記第2絶縁膜からなる第2の外側サイドウォールとで構成されていることを特徴とする半導体装置。

**【請求項 5】**

請求項1～3のうちいずれか1項に記載の半導体装置において、 20

前記第1のサイドウォールは、断面形状がL字状の第1絶縁膜からなる第1の内側サイドウォールと、前記第1の内側サイドウォール上に形成された第2絶縁膜からなる第1の外側サイドウォールとで構成されており、

前記第2のサイドウォールは、断面形状がL字状の前記第1絶縁膜からなる第2の内側サイドウォールのみで構成されていることを特徴とする半導体装置。

**【請求項 6】**

請求項1～5のうちいずれか1項に記載の半導体装置において、

前記トレンチ部の内壁全体は、前記半導体基板で構成されていることを特徴とする半導体装置。

**【請求項 7】**

請求項1～6のうちいずれか1項に記載の半導体装置において、 30

前記シリコン混晶層の上面は、前記ゲート電極直下に位置する前記半導体基板の上面の高さに比べて同等以上の高さを有することを特徴とする半導体装置。

**【請求項 8】**

請求項1～7のうちいずれか1項に記載の半導体装置において、

前記不純物領域の接合深さは、前記シリコン混晶層の底面よりも浅いことを特徴とする半導体装置。

**【請求項 9】**

請求項1～8のうちいずれか1項に記載の半導体装置において、

前記シリコン混晶層の上に金属シリサイド層が形成されていることを特徴とする半導体装置。 40

**【請求項 10】**

請求項9に記載の半導体装置において、

前記ゲート電極上に前記金属シリサイド層が形成されていることを特徴とする半導体装置。

**【請求項 11】**

請求項9又は10に記載の半導体装置において、

前記金属シリサイド層はニッケル又は白金を含むことを特徴とする半導体装置。

**【請求項 12】**

請求項1～11のうちいずれか1項に記載の半導体装置において、 50

前記第1導電型のMISトランジスタは、p型MISトランジスタであり、前記第1導電型のシリコン混晶層は、p型SiGe層であることを特徴とする半導体装置。

#### 【請求項13】

半導体基板と、

前記半導体基板内に形成された素子分離領域と、

前記素子分離領域に囲まれた前記半導体基板からなり、トレンチ部を有する活性領域と

前記活性領域上に形成されたゲート電極と、前記ゲート電極の側面上であって、平面的に見て前記ゲート電極と前記トレンチ部との間に形成された第1のサイドウォールと、前記トレンチ部内に充填され、前記活性領域におけるチャネル領域に対して応力を生じさせる第1導電型のシリコン混晶層とを有する第1導電型のMISトランジスタと、

前記トレンチ部と前記素子分離領域との間に設けられ、前記半導体基板からなる基板領域と、

前記基板領域に形成された第1導電型の不純物領域と、

前記ゲート電極上に形成された金属シリサイド層とを備え、

前記基板領域上には、マスク部が形成されており、

前記素子分離領域は、上面が前記基板領域の上面よりも高く形成されており、

前記マスク部は、前記素子分離領域の側面上に形成された第2のサイドウォールからなることを特徴とする半導体装置。

#### 【請求項14】

請求項13に記載の半導体装置において、

前記第1のサイドウォールは、断面形状がL字状の第1絶縁膜からなる第1の内側サイドウォールと、前記第1の内側サイドウォール上に形成された第2絶縁膜からなる第1の外側サイドウォールとで構成されており、

前記第2のサイドウォールは、断面形状がL字状の前記第1絶縁膜からなる第2の内側サイドウォールと、前記第2の内側サイドウォール上に形成された前記第2絶縁膜からなる第2の外側サイドウォールとで構成されていることを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、MIS(Metal Insulator Semiconductor)トランジスタを有する半導体装置及びその製造方法に関する。

##### 【背景技術】

##### 【0002】

半導体装置では、高速動作、低消費電力化、高集積化等の高性能化のため、最小加工寸法の微細化が図られてきた。最小加工寸法が65nm以下の世代では、微細化の技術的困難性が極めて高くなり、また、微細化のみによる高性能化に限界が見え始めている。

##### 【0003】

そこで、微細化によらない高性能トランジスタとして、MIS型トランジスタのチャネル領域に対して応力歪みを与えることによりキャリア移動度を向上させる、いわゆる歪みシリコントランジスタが注目されている(例えば、特許文献1、2参照)。例えば、p型MISトランジスタでは、主面の面方位が(100)面であるシリコン基板の主面上に形成されたp型MISトランジスタのチャネル領域に対して、ゲート長方向に圧縮応力を印加することにより、正孔の移動度が向上しトランジスタ駆動力が増大する。

##### 【0004】

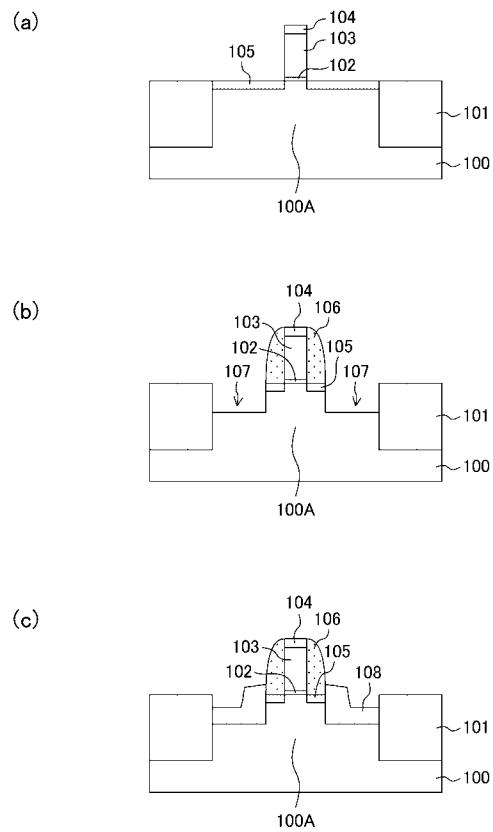

以下、従来の圧縮応力を有する半導体装置の製造方法について図13を参考しながら説明する。図13(a)~(d)は、従来の半導体装置の製造方法を示す断面図である。

##### 【0005】

まず、図13(a)に示すように、半導体基板100の上部に素子分離領域101によ

10

20

30

40

50

って囲まれ、半導体基板 100 からなる活性領域 100A を形成した後、活性領域 100A 上にゲート絶縁膜 102、ゲート電極 103 及び保護絶縁膜 104 を形成する。その後、活性領域 100A におけるゲート電極 103 の側方下の領域に p 型エクステンション領域 105 を形成する。

#### 【0006】

次に、図 13 (b) に示すように、ゲート電極 103 の側面上にサイドウォール 106 を形成した後、露出している半導体基板 100 を所望の深さまでエッチングする。これにより、活性領域 100A であって、平面的に見てサイドウォール 106 と素子分離領域 101 との間に位置する領域にトレンチ部 107 を形成する。

#### 【0007】

次に、図 13 (c) に示すように、トレンチ部 107 内に p 型 SiGe 層 108 をエピタキシャル成長させる。以降、所定の工程を経て、従来の半導体装置を製造する。

#### 【0008】

この製造方法によれば、ゲート電極 103 直下のチャネル領域に対して、ゲート長方向に圧縮応力を与える p 型 SiGe 層 108 が設けられた p 型 MIS ランジスタを有する半導体装置が製造できる。

#### 【特許文献 1】米国特許第 6 6 2 1 1 3 1 号明細書

#### 【特許文献 2】特開 2006 - 13428 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

しかしながら、前記従来の半導体装置の製造方法では、トレンチ部内に、例えば SiGe 層などの歪みを含有するシリコン混晶層を制御良く所望の厚さでエピタキシャル成長することができないという不具合がある。

#### 【0010】

すなわち、SiGe 層をエピタキシャル成長する際、トレンチ部内における素子分離領域側の側面には素子分離領域の絶縁膜が露出しており、エピタキシャル成長基板となるシリコンが存在していないため、エピタキシャル成長不良が生じ、所望の厚さで SiGe 層を形成することが困難である。

#### 【0011】

本発明は、前記従来の問題に鑑み、所望の厚さで制御良くエピタキシャル成長され、良好な特性を示すシリコン混晶層を備えた半導体装置及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0012】

上記課題を解決するために、本発明の半導体装置は、半導体基板と、前記半導体基板内に形成された素子分離領域と、前記素子分離領域に囲まれた前記半導体基板からなり、トレンチ部を有する活性領域と、前記活性領域上に形成されたゲート電極と、前記ゲート電極の側面上であって、平面的に見て前記ゲート電極と前記トレンチ部との間に形成された第 1 のサイドウォールと、前記トレンチ部内に充填され、前記活性領域におけるチャネル領域に対して応力を生じさせる第 1 導電型のシリコン混晶層とを有する第 1 導電型の MIS ランジスタと、前記トレンチ部と前記素子分離領域との間に設けられ、前記半導体基板からなる基板領域と、前記基板領域に形成された第 1 導電型の不純物領域とを備えている。

#### 【0013】

この構成によれば、活性領域に形成されたトレンチ部と素子分離領域との間に、基板領域が設けられている。これにより、活性領域に対して応力を生じさせるシリコン混晶層をトレンチ部内に例えばエピタキシャル成長により形成する場合、トレンチ部内の内壁全体は半導体基板で構成されており、素子分離領域が露出していないため、成長不良が抑制され、制御良くシリコン混晶層を形成することができる。従って、本発明の半導体装置によ

10

20

30

40

50

れば、良好な品質を有するシリコン混晶層を備え、高速に動作が可能な半導体装置を実現することができる。

#### 【0014】

また、基板領域にはシリコン混晶層と同じ導電型の不純物領域が形成されているため、MISトランジスタのソース・ドレイン領域として機能するシリコン混晶層と、半導体基板との間で、リーク電流が発生するのを抑制することができる。従って、本発明の半導体装置によれば、上記の効果に加えて、リーク電流の発生が抑制された信頼性の高い半導体装置を実現することができる。

#### 【0015】

次に、本発明の半導体装置の製造方法は、半導体基板内に形成された活性領域上に設けられた第1導電型のMISトランジスタを備えた半導体装置の製造方法であって、前記半導体基板内に前記活性領域を囲む素子分離領域を形成する工程(a)と、前記工程(a)の後、前記活性領域上に、ゲート電極と、前記ゲート電極上に形成された第1の保護絶縁膜と、前記ゲート電極の側面上に形成された第1のサイドウォールとを有するゲート部を形成する工程(b)と、前記活性領域の端部であって、前記素子分離領域と隣接する基板領域上に、マスク部を形成する工程(c)と、前記半導体基板のうち、平面的に見て前記ゲート部と前記マスク部との間に位置するトレンチ部形成領域をエッチングしてトレンチ部を形成するとともに、前記トレンチ部と前記素子分離領域との間に前記基板領域を残存させる工程(d)と、前記トレンチ部内に、前記活性領域におけるチャネル領域に対して応力を生じさせる第1導電型のシリコン混晶層を充填する工程(e)と、前記基板領域に第1導電型の不純物領域を形成する工程(f)とを備えている。10

#### 【0016】

この方法によれば、工程(c)で基板領域を覆うマスク部を形成することで、工程(d)で、トレンチ部と素子分離領域との間に基板領域を残存させてトレンチ部を形成することができる。そのため、工程(e)でトレンチ部内にシリコン混晶層をエピタキシャル成長などにより形成する際に、トレンチ部の表面に素子分離領域が露出することなく、トレンチ部の内壁全体が半導体基板で構成されることになり、トレンチ部内に良好にシリコン混晶層をエピタキシャル成長させることができる。その結果、本発明の半導体装置の製造方法を用いれば、所望の特性を示すシリコン混晶層を備え、高速で動作可能な半導体装置を製造することができる。20

#### 【発明の効果】

#### 【0017】

本発明の半導体装置及びその製造方法によれば、活性領域のチャネル領域に対して応力を生じさせるシリコン混晶層を制御良く形成することができ、半導体装置の駆動能力を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0018】

##### (第1の実施形態)

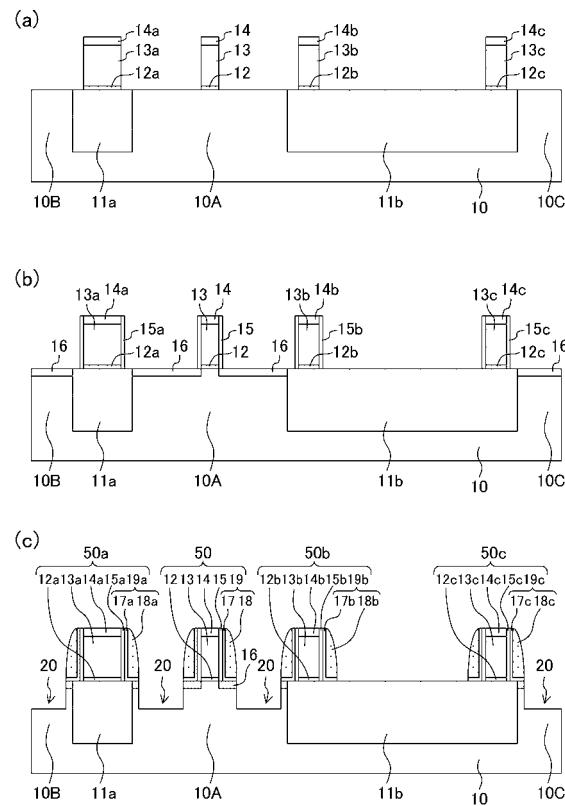

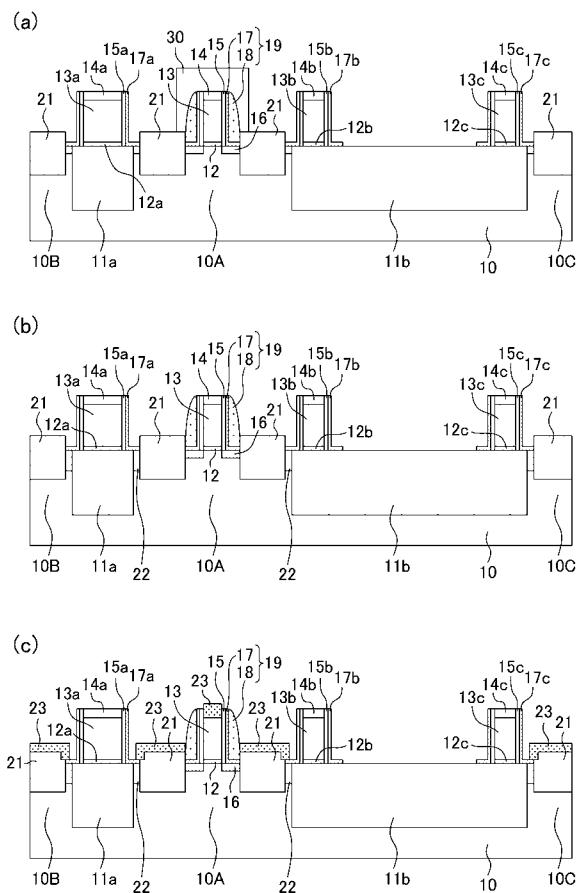

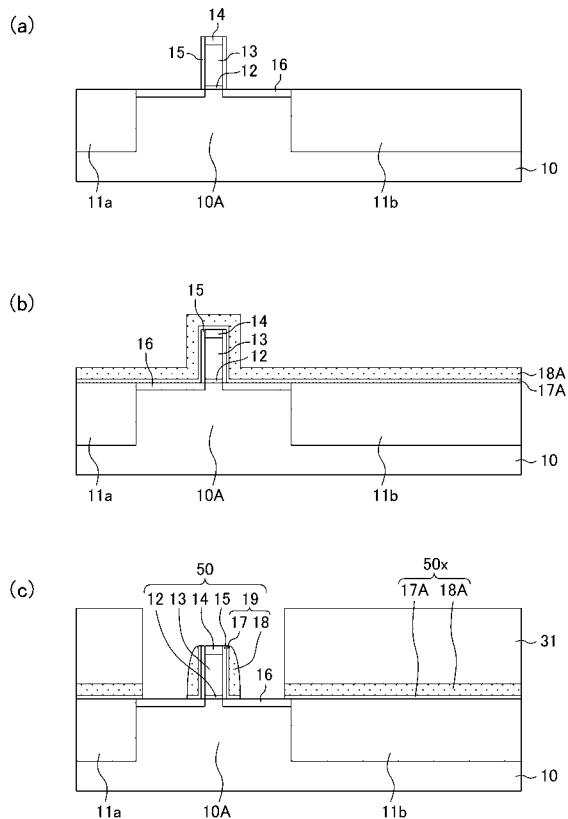

本発明の第1の実施形態に係る半導体装置の製造方法について図面を参照しながら説明する。図1(a)～(c)及び図2(a)～(c)は、本実施形態の半導体装置の製造方法を示す断面図である。40

#### 【0019】

まず、図1(a)に示すように、例えばSTI(Shallow Trench Isolation)法により、例えば面方位が(100)面の主面を持つシリコン(Si)からなる半導体基板10の上部にトレンチを形成し、該トレンチ内に絶縁膜を埋め込んで素子分離領域11a、11bを選択的に形成する。これにより、素子分離領域11a、11bによって囲まれた半導体基板10からなる活性領域10A、10B、10Cが形成される。ここで、素子分離領域11aの分離幅は、素子分離領域11bの分離幅よりも狭く、最小ルールにおけるゲート電極のゲート長の2～5倍である。50

## 【0020】

次に、リソグラフィ法及びイオン注入法により、半導体基板10に、例えばP(リン)等のn型不純物を注入して、活性領域10A、10B、10Cを含む領域にn型ウェル領域(図示せず)を形成する。その後、半導体基板10上の全面に、例えば膜厚が2nmのシリコン酸窒化膜、膜厚が100nmのポリシリコン膜、及び膜厚が30nmのシリコン酸化膜を順次形成する。その後、フォトリソグラフィ法及びドライエッチング法により、シリコン酸化膜、ポリシリコン膜及びシリコン酸窒化膜を順次パターニングして、活性領域10A上にシリコン酸窒化膜からなるゲート絶縁膜12、ポリシリコン膜からなるゲート電極13、及びシリコン酸化膜からなる保護絶縁膜14を形成する。同時に、素子分離領域11a上の中央部に、ダミーゲート絶縁膜12a、ダミーゲート電極13a及びダミー保護絶縁膜14aを形成する。一方、素子分離領域11b上の活性領域10A側の端部に、ダミーゲート絶縁膜12b、ダミーゲート電極13b及びダミー保護絶縁膜14bを形成すると共に、素子分離領域11b上の活性領域10C側の端部に、ダミーゲート絶縁膜12c、ダミーゲート電極13c及びダミー保護絶縁膜14cを形成する。なお、このとき、活性領域10B、10C上にもゲート絶縁膜、ゲート電極及び保護絶縁膜が形成されるが、ここでは図示を省略する。

## 【0021】

ここで、ダミーゲート電極13aは、ゲート長がゲート電極13のゲート長よりも大きくて素子分離領域11aの分離幅よりも狭くなるように、且つ後工程でダミーゲート電極13aの両側面上に形成されるサイドウォールの一部が平面的に見て活性領域10A、10B上にオーバーラップするように形成する。一方、ダミーゲート電極13b、13cは、ゲート長がゲート電極13のゲート長と同程度となるように、且つ後工程で形成するサイドウォールの一部が活性領域10A、10C上にオーバーラップするようにそれぞれ形成する。なお、ダミーゲート絶縁膜12a、12b、12cは必ずしも設ける必要はない。

## 【0022】

次に、図1(b)に示すように、半導体基板10上の全面に、膜厚が5nmのシリコン酸化膜を形成した後、該シリコン酸化膜をエッチバックすることにより、ゲート電極13の側面上に断面形状がI字状のオフセットスペーサ15を形成するとともに、ダミーゲート電極13a、13b、13cの側面上に断面形状がI字状のオフセットスペーサ15a、15b、15cをそれぞれ形成する。その後、活性領域10Aに、ゲート電極13及びオフセットスペーサ15をマスクにして、p型不純物であるボロンをドーズ量 $4 \times 10^{14} \text{ ions/cm}^2$ で注入してp型エクステンション領域16を形成する。このとき、活性領域10B、10Cにも同様にしてp型エクステンション領域16を形成する。

## 【0023】

次に、図1(c)に示すように、例えばCVD(Chemical Vapor Deposition)法により、半導体基板10上の全面に、例えば膜厚が5nmのシリコン酸化膜と膜厚が30nmのシリコン窒化膜とを順次堆積した後、シリコン酸化膜及びシリコン窒化膜からなる積層膜をエッチバックする。これにより、ゲート電極13の側面上に、オフセットスペーサ15を介してサイドウォール19を形成するとともに、ダミーゲート電極13a、13b、13cの側面上に、オフセットスペーサ15a、15b、15cを介してサイドウォール19a、19b、19cをそれぞれ形成する。

## 【0024】

ここで、サイドウォール19は、シリコン酸化膜からなる断面形状がL字状の内側サイドウォール17と、内側サイドウォール17上に形成されたシリコン窒化膜からなる外側サイドウォール18とでそれぞれ構成されている。同様に、サイドウォール19aは、シリコン酸化膜からなる断面形状がL字状の内側サイドウォール17aと、L字状の内側サイドウォール17a上に形成されたシリコン窒化膜からなる外側サイドウォール18aとでそれぞれ構成されている。また、サイドウォール19bは、シリコン酸化膜からなる断面形状がL字状の内側サイドウォール17bと、内側サイドウォール17b上に形成され

たシリコン窒化膜からなる外側サイドウォール 18 b とで構成されている。同様に、サイドウォール 19 c は、シリコン酸化膜からなる断面形状が L 字状の内側サイドウォール 17 c と、内側サイドウォール 17 c 上に形成されたシリコン窒化膜からなる外側サイドウォール 18 c とで構成されている。

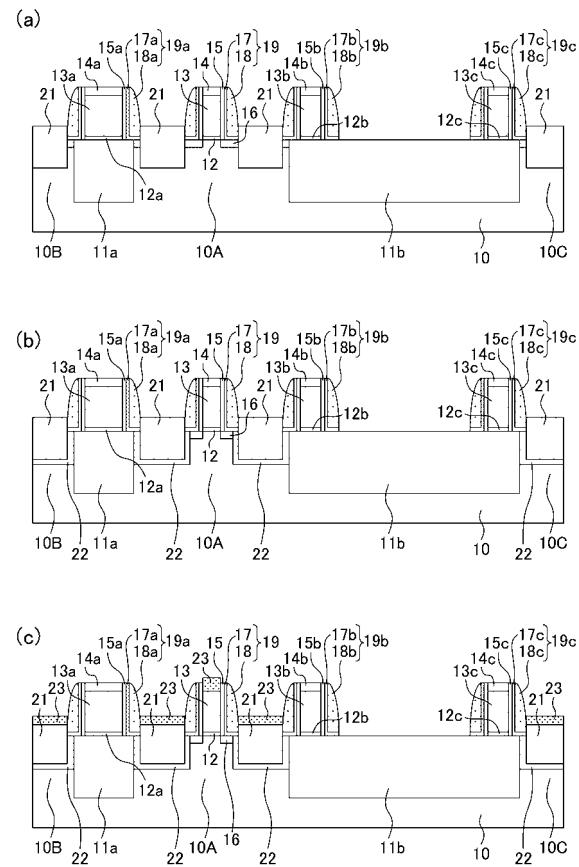

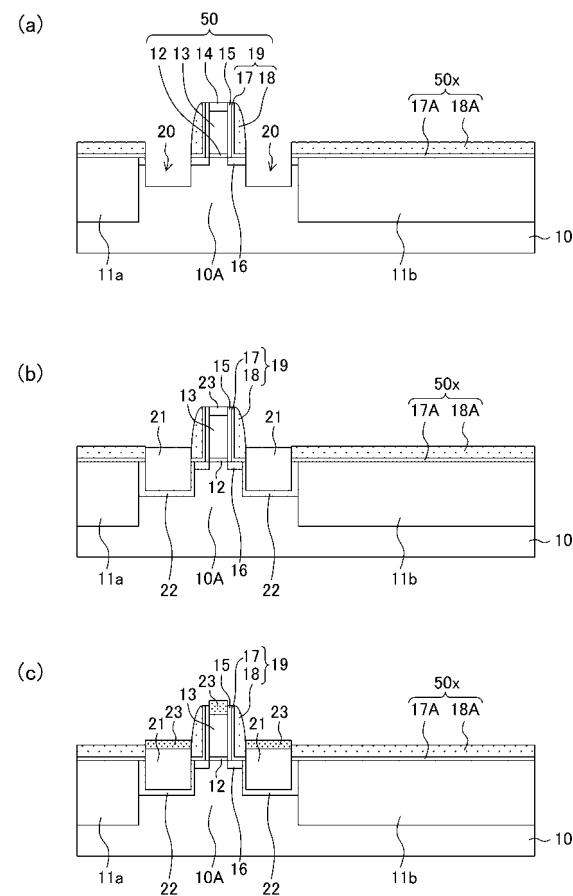

#### 【0025】

次に、ゲート絶縁膜 12、ゲート電極 13、保護絶縁膜 14、オフセットスペーサ 15、及びサイドウォール 19 を有するゲート部 50 と、ダミーゲート絶縁膜 12 a、ダミーゲート電極 13 a、ダミー保護絶縁膜 14 a、オフセットスペーサ 15 a、及びサイドウォール 19 a を有するマスク部 50 a と、ダミーゲート絶縁膜 12 b、ダミーゲート電極 13 b、ダミー保護絶縁膜 14 b、オフセットスペーサ 15 b、及びサイドウォール 19 b を有するマスク部 50 b と、ダミーゲート絶縁膜 12 c、ダミーゲート電極 13 c、ダミー保護絶縁膜 14 c、オフセットスペーサ 15 c、及びサイドウォール 19 c を有するマスク部 50 c とをマスクにして、露出している半導体基板 10 を所望の深さまでエッチングする。これにより、活性領域 10 A 内であって、平面的に見てサイドウォール 19 とサイドウォール 19 a、19 b との間に位置する領域（トレンチ部形成領域）にトレンチ部 20 を形成する。このとき、活性領域の端部であって、素子分離領域 11 a、11 b と隣接する領域（以下、「基板領域」と称する）上には、サイドウォール 19 a、19 b が形成されているため、素子分離領域 11 a、11 b とトレンチ部 20 との間には半導体基板 10 が残存する。この基板領域が残存することで、トレンチ部 20 内には素子分離領域 11 a、11 b が露出しない。このとき、活性領域 10 B、10 C にも同様にしてトレンチ部 20 が形成される。ここで、トレンチ部 20 の深さは、50 nm 程度が望ましい。

10

#### 【0026】

次に、図 2(a) に示すように、例えば MOCVD (Metal Organic Chemical Vapor Deposition) 法により、例えはシランガス ( $\text{SiH}_4$ ) 及びゲルマン ( $\text{GeH}_4$ ) ガスを、ジボラン ( $\text{B}_2\text{H}_6$ ) などの p 型ドーパントガスとともに 650 ~ 700 の温度で供給することにより、トレンチ部 20 内を充填するように p 型 SiGe 層 21 をエピタキシャル成長させる。このとき、p 型 SiGe 層 21 の上面は、ゲート電極 13 直下に位置する半導体基板 10 の上面の高さに比べて同等以上の高さになるように形成することが望ましい。この場合、ゲート電極 13 の下方に形成されるチャネル領域に対して、p 型 SiGe 層 21 が十分に応力を加えられるため、p 型 MIS ドライン領域の駆動能力をより一層高めることができる。

20

#### 【0027】

次に、図 2(b) に示すように、半導体基板 10 に熱処理を行うことにより、p 型 SiGe 層 21 中の p 型不純物を半導体基板 10 に拡散させる。これにより、活性領域 10 A における素子分離領域 11 a、11 b と p 型 SiGe 層 21 との間に位置する領域（基板領域）に p 型不純物領域 22 を形成する。このとき、活性領域 10 B、10 C にも同様にして p 型不純物領域 22 が形成される。本工程により、サイドウォール 19 の外側方下に位置する領域に、p 型 SiGe 層 21 及び p 型不純物領域 22 からなる p 型ソース・ドレイン領域が形成される。

30

#### 【0028】

ここで、図 2(b) に示す工程では、p 型 SiGe 層 21 を含む活性領域 10 A、10 B、10 C に、ゲート電極 13 及びサイドウォール 19 をマスクにして p 型不純物である例えはボロンを、ドーズ量が  $4 \times 10^{15} \text{ ions/cm}^2$  で、注入角度が  $10^\circ \sim 25^\circ$  の注入条件で斜めイオン注入した後、熱処理を行うことで p 型不純物領域 22 を形成してもよい。この場合、p 型 SiGe 層 21 中の p 型不純物のみを拡散させて p 型不純物領域 22 を形成するよりも、基板領域に対して短時間の熱処理で高濃度の p 型不純物領域 22 を確実に形成することができる。

40

#### 【0029】

次に、図 2(c) に示すように、ゲート電極 13 上に設けられた保護絶縁膜 14 を除去した後、スパッタ法等により、半導体基板 10 の上に、例えはニッケル ( $\text{Ni}$ )、コバルト

50

ト( C o )又は白金( P t )等からなる金属膜を堆積する。その後、堆積した金属膜をアニールすることにより、ゲート電極 13 及び p 型 SiGe 層 21 の各上に金属シリサイド層 23 をそれぞれ形成する。次に、半導体基板 10 上に、層間絶縁膜、コンタクトプラグ、金属配線等( 図示せず )を形成することによって、本実施形態に係る半導体装置を製造することができる。

#### 【 0030 】

本実施形態の半導体装置の製造方法の特徴は、図 1 ( c )に示す工程でゲート部 50 、及びマスク部 50 a 、 50 b 、 50 c を用いてトレンチ部 20 を形成することにある。この方法によれば、マスク部 50 a 、 50 b 、 50 c を構成するサイドウォール 19 a 、 19 b 、 19 c の一部が、活性領域の端部であって、素子分離領域 11 a 、 11 b と隣接する領域( 基板領域 )を覆うため、トレンチ部 20 と素子分離領域 11 a 、 11 b との間に、基板領域を残存させることができる。その結果、トレンチ部 20 の表面に素子分離領域 11 a 、 11 b が露出することなくトレンチ部 20 の内壁全体が半導体基板で構成されることになるため、良好にエピタキシャル成長を行うことができ、所望の特性を示す p 型 SiGe 層 21 を得ることができる。従って、本実施形態の半導体装置の製造方法によれば、良好な特性を示す p 型 SiGe 層を備え、高速で動作可能な半導体装置を製造することができる。

#### 【 0031 】

また、本実施形態の半導体装置の製造方法では、マスク部を構成するダミーゲート電極 13 a 、 13 b 、 13 c 、ダミー保護絶縁膜 14 a 、 14 b 、 14 c 、及びサイドウォール 19 a 、 19 b 、 19 c は、MIS トランジスタのゲート電極 13 、保護絶縁膜 14 、及びサイドウォール 19 と、それぞれ同一工程で形成されるため、マスク部を別途形成するための工程を増加することなく、比較的容易にトレンチ部 20 を形成することができる。

#### 【 0032 】

なお、本実施形態の半導体装置の製造方法のように、分離幅がゲート電極 13 のゲート長に対して十分に大きい素子分離領域 11 b を備えている場合は、ゲート長がゲート電極 13 のゲート長と同じであるダミーゲート電極 13 b を素子分離領域 11 b の両端部に1つずつ設けることが望ましい。これにより、ダミーゲート電極 13 b とダミーゲート電極 13 a を形成する際のマスクレイアウトパターンが比較的容易に形成できる、最適なエッチング条件を使用できるなどの効果が得られる。また、分離幅がゲート電極 13 のゲート長よりも大きく、素子分離領域 11 b の分離幅よりも小さい素子分離領域 11 a を備えている場合は、上述したように所望の領域にトレンチ部 20 が形成できるように、素子分離領域 11 a の分離幅、サイドウォール 19 a の幅を考慮して、ダミーゲート電極 13 a のゲート長を設定すればよい。なお、本実施形態の製造方法の素子分離領域 11 a 、 11 b の分離幅は一例であり、これに限定されるものではない。

#### 【 0033 】

次に、図 2 ( c )を用いて本実施形態の半導体装置の構成について簡単に説明する。なお、各構成部材の材料、膜厚、形成方法などは、上述の製造方法で述べた材料と同様である。

#### 【 0034 】

図 2 ( c )に示すように、本実施形態の半導体装置は、半導体基板 10 と、半導体基板 10 内に形成された素子分離領域 11 a 、 11 b と、素子分離領域 11 a 、 11 b に囲まれた半導体基板 10 からなり、トレンチ部を有する活性領域 10 A と、活性領域 10 A 上に形成された p 型 MIS トランジスタと、トレンチ部と素子分離領域 11 a 、 11 b の間にそれぞれ設けられ、半導体基板 10 からなる基板領域と、基板領域に形成された p 型不純物領域 22 とを備えている。

#### 【 0035 】

ここで、 p 型 MIS トランジスタは、活性領域 10 A 上に下から順に形成されたゲート絶縁膜 12 及びゲート電極 13 と、ゲート電極 13 の側面上に形成されたオフセットスペ

10

20

30

40

50

ーサ 15 と、オフセットスペーサ 15 上であって、平面的に見てゲート電極 13 とトレンチ部との間に形成されたサイドウォール 19 と、活性領域 10A におけるゲート電極 13 の側方下の領域に形成された p 型エクステンション領域 16 と、サイドウォール 19 の外側方下の領域に形成された p 型 SiGe 層 21 及び p 型不純物領域 22 からなる p 型ソース・ドレイン領域とを有している。ここで、p 型 SiGe 層 21 は、トレンチ部内に充填され、活性領域におけるチャネル領域に対して応力を生じさせる。なお、サイドウォール 19 は、断面形状が L 字状の内側サイドウォール 17 と、内側サイドウォール 17 上に形成された外側サイドウォール 18 とで構成されている。また、ゲート電極 13 及び p 型 SiGe 層 21 の上には、金属シリサイド層 23 が形成されている。

## 【0036】

10

さらに、本実施形態の半導体装置は、素子分離領域 11a、11b 上に下から順にそれぞれ形成されたダミーゲート絶縁膜 12a、12b と、ダミーゲート電極 13a、13b と、及びダミー保護絶縁膜 14a、14b と、ダミーゲート電極 13a、13b の側面上に形成されたオフセットスペーサ 15a、15b と、オフセットスペーサ 15a 上であって、基板領域を覆うように形成されたサイドウォール 19a、19b とを備えている。なお、サイドウォール 19a は、断面形状が L 字状の内側サイドウォール 17a と、内側サイドウォール 17a 上に形成された外側サイドウォール 18a とで構成されている。同様に、サイドウォール 19b は、断面形状が L 字状の内側サイドウォール 17b と、内側サイドウォール 17b 上に形成された外側サイドウォール 18b とで構成されている。

## 【0037】

20

以上の構成を備えた本実施形態の半導体装置では、活性領域 10A であって、ゲート電極 13 の両側方下に位置する領域に形成された p 型 SiGe 層 21 を備えている。この p 型 SiGe 層 21 は、Si よりも格子定数が大きい Ge を含むため、ゲート長方向に圧縮応力歪みを生じさせる。その結果、活性領域 10A 内であって、ゲート電極 13 の下側に位置するチャネル領域に p 型 SiGe 層 21 により圧縮応力が加わることで、p 型 MIS ドレインジスタの駆動力を向上させることができ、高速で動作可能な半導体装置を実現することができる。

## 【0038】

30

また、活性領域 10A の端部であって、素子分離領域 11a、11b と隣接する領域である基板領域には、p 型不純物領域 22 が形成されている。これにより、p 型ソース・ドレイン領域 ( p 型 SiGe 層 21 及び p 型不純物領域 22 ) と半導体基板 10 ( n 型ウェル領域 ( 図示せず ) )との間に生じるリーク電流の低減を図ることができる。

## 【0039】

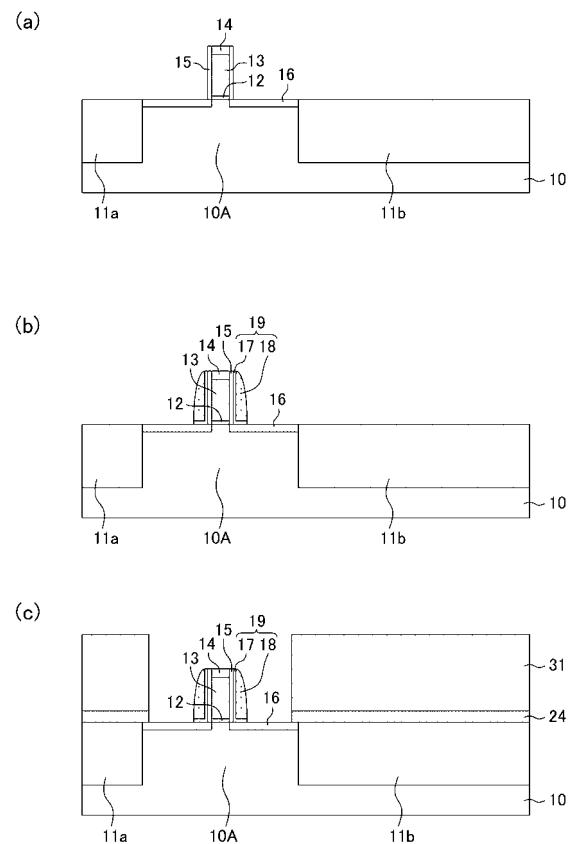

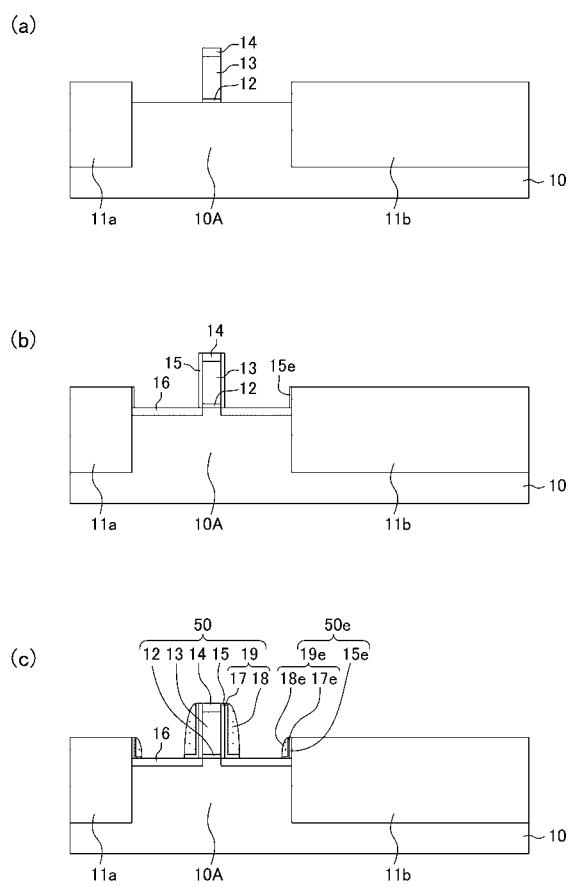

## (第 1 の実施形態の第 1 変形例)

以下、本発明の第 1 の実施形態の第 1 変形例に係る半導体装置の製造方法について図 3 を参照しながら説明する。図 3 ( a ) ~ ( c ) は、第 1 の実施形態の第 1 変形例に係る半導体装置の製造方法を示す断面図である。なお、図 3 において、図 1、図 2 に示した構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

## 【0040】

40

まず、第 1 の実施形態に係る半導体装置の製造方法と同様にして、図 1 ( a ) 及び図 1 ( b ) に示す工程を行うことで、p 型エクステンション領域 16 が形成された図 1 ( b ) に示す構成を得る。

## 【0041】

次に、図 3 ( a ) に示すように、半導体基板 10 上に、ゲート電極 13、及び後工程でトレンチ部を形成するトレンチ部形成領域の一部を覆い、且つ、活性領域 10A、10B、10C の端部であって、素子分離領域 11a、11b と隣接する領域を露出させる開口部を有するレジスト 30 を形成する。その後、レジスト 30 をマスクにして、活性領域 10A、10B、10C に、p 型不純物である例えはボロンをドーズ量が  $4 \times 10^{15}$  cm<sup>-2</sup> の注入条件でイオン注入する。次いで、レジスト 30 を除去した後、注入した不純物を活性化するための熱処理を行って、p 型不純物領域 22 を形成する。この p 型

50

不純物領域 22 は、半導体基板 10 からなり、後工程で形成する p 型 SiGe 層と素子分離領域 11a、11b との間に位置する領域に形成されれば良い。

#### 【 0042 】

次に、図 3 (b) に示すように、図 1 (c) に示す工程と同様な方法によって、サイドウォール 19、19a、19b、19c を形成する。その後、ゲート絶縁膜 12、ゲート電極 13、保護絶縁膜 14、オフセットスペーサ 15、及びサイドウォール 19 を有するゲート部 50 と、ダミーゲート絶縁膜 12a、ダミーゲート電極 13a、ダミー保護絶縁膜 14a、オフセットスペーサ 15a、及びサイドウォール 19a を有するマスク部 50a と、ダミーゲート絶縁膜 12b、ダミーゲート電極 13b、ダミー保護絶縁膜 14b、オフセットスペーサ 15b、及びサイドウォール 19b を有するマスク部 50b と、ダミーゲート絶縁膜 12c、ダミーゲート電極 13c、ダミー保護絶縁膜 14c、オフセットスペーサ 15c、及びサイドウォール 19c を有するマスク部 50c とをマスクにして、露出している半導体基板 10 を所望の深さまでエッチングすることで、トレンチ部 20 を形成する。このとき、素子分離領域 11a、11b とトレンチ部 20 との間には、p 型不純物領域 22 が形成された半導体基板 10 が残存するため、トレンチ部 20 の表面に素子分離領域 11a、11b が露出することなく、トレンチ部 20 の内壁全体は半導体基板 10 で構成される。

10

#### 【 0043 】

次に、図 3 (c) に示すように、例えば MOCVD 法により、トレンチ部 20 内を充填するように p 型 SiGe 層 21 をエピタキシャル成長させる。なお、本変形例の製造方法では、イオン注入により形成された p 型不純物領域 22 の接合深さが、トレンチ部 20 に形成された p 型 SiGe 層 21 の底面よりも浅くなっている。続いて、ゲート電極 13 上に設けられた保護絶縁膜 14 を除去した後、ゲート電極 13 及びソース・ドレイン領域となる p 型 SiGe 層 21 の上に金属シリサイド層 23 をそれぞれ形成する。その後、半導体基板 10 上に、層間絶縁膜、コンタクトプラグ、金属配線等（図示せず）を形成することによって、本変形例に係る半導体装置を製造することができる。

20

#### 【 0044 】

本変形例に係る半導体装置の製造方法では、第 1 の実施形態の半導体装置の製造方法と同様にして、トレンチ部 20 を形成する際に、マスク部 50a、50b、50c を構成するサイドウォール 19a、19b、19c の一部が、活性領域の端部であって、素子分離領域 11a、11b と隣接する領域（基板領域）を覆うため、トレンチ部 20 と素子分離領域 11a、11b との間に、基板領域を残存させることができる。その結果、トレンチ部 20 の内壁全体が半導体基板で構成されることになるため、良好にエピタキシャル成長を行うことができ、所望の特性を示す p 型 SiGe 層 21 を得ることができる。従って、本変形例の半導体装置の製造方法によれば、良好な特性を示す p 型 SiGe 層を備え、高速で動作可能な半導体装置を製造することができる。

30

#### 【 0045 】

また、本変形例の半導体装置の製造方法では、p 型不純物領域 22 は、p 型 SiGe 層 21 におけるゲート電極 13 側の側方（サイドウォール 19 の下方）には形成されず、p 型 SiGe 層 21 と素子分離領域 11a、11b との間に位置する半導体基板 10 の領域のみに形成される。この場合、図 2 (c) に示す第 1 の実施形態の半導体装置に比べて、短チャネル効果の抑制を図ることができる。その結果、本変形例の半導体装置の製造方法を用いれば、リーク電流が抑制されるとともに、短チャネル効果による MIS トランジスタの特性の劣化が軽減され、信頼性の高い半導体装置を実現することができる。

40

#### 【 0046 】

また、本変形例の半導体装置の製造方法では、p 型不純物領域 22 は、p 型 SiGe 層 21 を形成する前にイオン注入することにより形成される。このため、第 1 の実施形態の製造方法のように、p 型 SiGe 層 21 を形成した後、該 p 型 SiGe 層 21 に含まれる p 型不純物を熱処理で拡散することで p 型不純物領域を形成する場合に比べて、本変形例の半導体装置の製造方法では、短時間の熱処理で高濃度の p 型不純物領域 22 を比較的容

50

易に形成することができる。

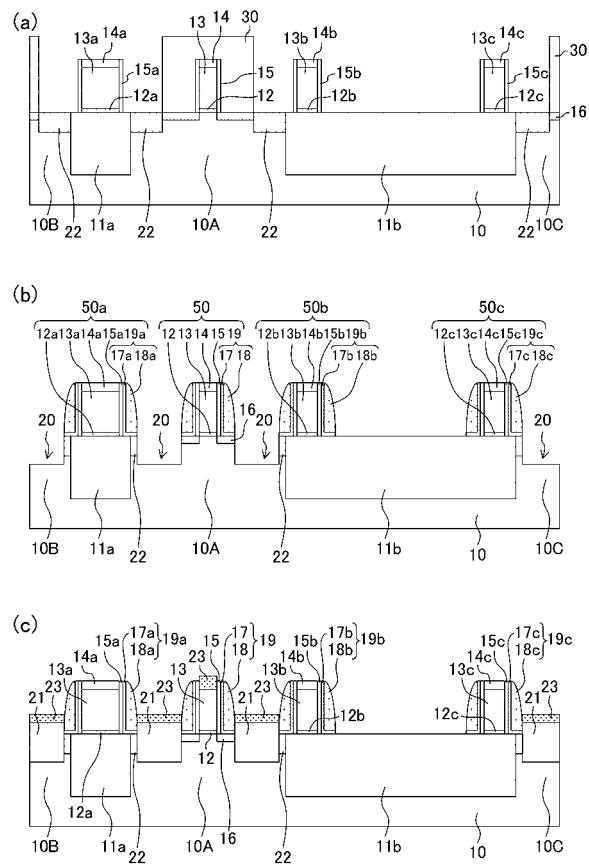

#### 【0047】

(第1の実施形態の第2変形例)

以下、本発明の第1の実施形態の第2変形例に係る半導体装置の製造方法について図4を参照しながら説明する。図4(a)～(c)は、第2変形例に係る半導体装置の製造方法である。なお、図4において、図1、図2に示した構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

#### 【0048】

まず、第1の実施形態に係る半導体装置の製造方法と同様にして、図1(a)及び図1(b)に示す工程を行うことで、p型エクステンション領域16が形成された図1(b)に示す構成を得る。

10

#### 【0049】

次に、図4(a)に示すように、図1(c)に示すサイドウォールの形成と同様な方法によって、ゲート電極13の側面上にオフセットスペーサ15を介してサイドウォール19を形成するとともに、ダミーゲート電極13a、13b、13cの側面上にオフセットスペーサ15a、15b、15cを介してサイドウォール19a、19b、19cを形成する。

#### 【0050】

次に、図4(b)に示すように、半導体基板10上に、ゲート電極13、サイドウォール19、及び後の工程でトレンチ部を形成するトレンチ部形成領域の一部を覆い、且つ、活性領域10A、10B、10Cの端部であって、素子分離領域11a、11bと隣接する領域(基板領域)を露出させる開口部を有するレジスト30を形成する。その後、レジスト30をマスクにして、活性領域10A、10B、10Cに、p型不純物である例えはボロンをドーズ量が $4 \times 10^{15}$ ions/cm<sup>2</sup>で、注入角度が10°～25°の注入条件で斜めイオン注入する。次に、レジスト30を除去した後、注入した不純物を活性化するための熱処理を行って、p型不純物領域22を形成する。このp型不純物領域22は、後工程で形成するp型SiGe層と、素子分離領域11a、11bとの間に位置する半導体基板10からなる領域に形成されれば良い。

20

#### 【0051】

次に、図4(c)に示すように、図1(c)に示すトレンチ部20の形成と同様な方法によって、ゲート絶縁膜12、ゲート電極13、保護絶縁膜14、オフセットスペーサ15、及びサイドウォール19を有するゲート部50と、ダミーゲート絶縁膜12a、ダミーゲート電極13a、ダミー保護絶縁膜14a、オフセットスペーサ15a、及びサイドウォール19aを有するマスク部50aと、ダミーゲート絶縁膜12b、ダミーゲート電極13b、ダミー保護絶縁膜14b、オフセットスペーサ15b、及びサイドウォール19bを有するマスク部50bと、ダミーゲート絶縁膜12c、ダミーゲート電極13c、ダミー保護絶縁膜14c、オフセットスペーサ15c、及びサイドウォール19cを有するマスク部50cとをマスクにして、露出している半導体基板10を所望の深さまでエッチングすることで、トレンチ部20を形成する。このとき、素子分離領域11a、11bとトレンチ部20との間には、p型不純物領域22が形成された半導体基板10が残存するため、トレンチ部20の表面に素子分離領域11a、11bが露出することなく、トレンチ部20の内壁全体は半導体基板10で構成される。

30

40

#### 【0052】

続いて、図示は省略するが、例えはMOCVD法により、トレンチ部20内を充填するようにp型SiGe層21をエピタキシャル成長させる。次に、ゲート電極13上に設けられた保護絶縁膜14を除去した後、ゲート電極13及びp型SiGe層21の上に金属シリサイド層23をそれぞれ形成する。その後、半導体基板10上に、層間絶縁膜、コンタクトプラグ、金属配線等(図示せず)を形成することによって、本変形例に係る半導体装置を製造することができる。

#### 【0053】

本変形例の半導体装置及びその製造方法によれば、図4(c)に示す工程でトレンチ部20と素子分離領域11a、11bとの間には、p型不純物領域22が形成された基板領域が設けられている。これにより、トレンチ部20の内壁全体は半導体基板10で構成されるため、トレンチ部20内にエピタキシャル成長により制御良くp型SiGe層21を形成することができる。従って、良好な品質を有するp型SiGe層21を備えた半導体装置を実現することができ、第1の実施形態及び第1変形例の半導体装置及びその製造方法と同様な効果を得ることができる。

#### 【0054】

##### (第1の実施形態の第3変形例)

以下、本発明の第1の実施形態の第3変形例に係る半導体装置の製造方法について、図5を参照しながら説明する。図5(a)～(c)は、第3変形例に係る半導体装置の製造方法である。なお、図5において、図1、図2に示した構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

#### 【0055】

まず、第1の実施形態に係る半導体装置の製造方法と同様にして、図1(a)～(c)、図2(a)に示す工程を順次行って、p型SiGe層21が形成された図2(a)に示す構成を得る。

#### 【0056】

次に、図5(a)に示すように、半導体基板10上に、ゲート電極13、オフセットスペーサ15、サイドウォール19、及びp型SiGe層21の一部を覆うレジスト30を形成する。その後、レジスト30をマスクにして、サイドウォール19a、19b、19cを構成する外側サイドウォール18a、18b、18cをそれぞれ除去する。

#### 【0057】

次に、図5(b)に示すように、レジスト30を除去した後、活性領域10A、10B、10Cに、p型不純物であるボロンをドーズ量が $4 \times 10^{15}$ ions/cm<sup>2</sup>の注入条件でイオン注入する。その後、注入したp型不純物を活性化するための熱処理を行って、p型不純物領域22を形成する。なお、本変形例では、レジスト30を除去した後、ボロンのイオン注入を行ったが、レジスト30をマスクにしてボロンのイオン注入を行ってp型不純物領域22を形成してもよい。あるいは、レジスト30を除去した後、再度半導体基板10上にゲート電極13、オフセットスペーサ15、サイドウォール19、及びp型SiGe層21の一部を覆うレジストを形成し、該レジストをマスクにしてボロンのイオン注入を行ってp型不純物領域22を形成してもよい。

#### 【0058】

次に、図5(c)に示すように、ゲート電極13上に設けられた保護絶縁膜14を除去した後、ゲート電極13及びp型SiGe層21の上に金属シリサイド層23をそれぞれ形成する。その後、半導体基板10上に、層間絶縁膜、コンタクトプラグ、金属配線等(図示せず)を形成することによって、本変形例に係る半導体装置を製造することができる。

#### 【0059】

本変形例の半導体装置及びその製造方法によれば、第1の実施形態、及びその第1変形例、第2変形例と同様に、トレンチ部20と素子分離領域11a、11bとの間には、基板領域が設けられている。これにより、トレンチ部20の内壁全体は半導体基板10で構成されるため、図5(a)に示す工程で、トレンチ部20内に制御良くp型SiGe層21をエピタキシャル成長させることができる。従って、本変形例の半導体装置及びその製造方法によれば、良好な品質を有するp型SiGe層21を備え、高速に動作可能な半導体装置を実現することができる。

#### 【0060】

なお、本変形例では、図5(a)に示す工程において、内側サイドウォール17a、17b、17cを残存させたが、必ずしも残存させる必要はなく、内側サイドウォール17a、17b、17cを全て除去する、又は、内側サイドウォール17a、17b、17c

10

20

30

40

50

のうち半導体基板 10 に接している部分を除去してもよい。この場合、p 型不純物を注入しやすくなるため、より確実に p 型不純物領域 22 を形成することができる。

#### 【0061】

また、本変形例では、図 5 (a) に示す工程において、ゲート電極 13 の側面上に設けられた外側サイドウォール 18 は残存させたが、必ずしも残存させる必要はなく、外側サイドウォール 18a、18b、18c とともに外側サイドウォール 18 も除去してもよい。この場合、図 5 (b) に示す工程において、半導体基板 10 上にゲート電極 13、オフセットスペーサ 15、内側サイドウォール 17、及び p 型 SiGe 層 21 の一部を覆うレジストを形成し、該レジストをマスクにしてボロンのイオン注入を行って p 型不純物領域 22 を形成すれば良い。

10

#### 【0062】

なお、第 1 の実施形態及びその各変形例の製造方法では、ゲート電極 13 上に設けられた保護絶縁膜 14 は、p 型 SiGe 層 21 を形成する際にゲート電極 13 上でもエピタキシャル成長が起こるのを防止するために設けられている。従って、保護絶縁膜 14 の除去工程は、必ずしも金属シリサイド層 23 の形成直前で行う必要はなく、p 型 SiGe 層 21 を形成した後であれば、金属シリサイド層 23 を形成するまでのどの工程でも保護絶縁膜 14 を除去することができる。

#### 【0063】

##### (第 2 の実施形態)

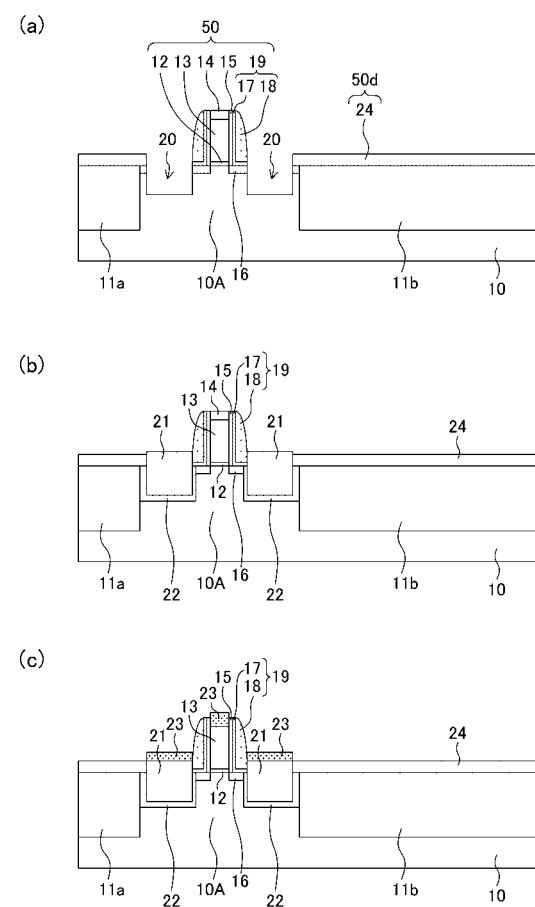

本発明の第 2 の実施形態に係る半導体装置の製造方法について図面を参照しながら説明する。図 6 及び図 7 は、本実施形態に係る半導体装置の製造方法を示す断面図である。なお、第 1 の実施形態（図 1、図 2）の構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

20

#### 【0064】

まず、図 6 (a) に示すように、例えば STI (Shallow Trench Isolation) 法により、例えば面方位が (100) 面の主面を持つシリコン (Si) からなる半導体基板 10 の上部にトレンチを形成し、該トレンチ内に絶縁膜を埋め込んで素子分離領域 11a、11b を選択的に形成する。これにより、素子分離領域 11a、11b によって囲まれた半導体基板 10 からなる活性領域 10A が形成される。

#### 【0065】

次に、リソグラフィ法及びイオン注入法により、半導体基板 10 に、例えば P (リン) 等の n 型不純物を注入して、n 型ウェル領域（図示せず）を形成する。その後、半導体基板 10 上の全面に、例えば膜厚が 2 nm のシリコン酸化膜、膜厚が 100 nm のポリシリコン膜、及び膜厚が 30 nm のシリコン酸化膜を順次形成する。その後、フォトリソグラフィ法及びドライエッティング法により、シリコン酸化膜、ポリシリコン膜及びシリコン酸化膜を順次パターニングして、活性領域 10A 上にシリコン酸化膜からなるゲート絶縁膜 12、ポリシリコン膜からなるゲート電極 13、及びシリコン酸化膜からなる保護絶縁膜 14 を形成する。

30

#### 【0066】

次に、半導体基板 10 上の全面に、膜厚が 5 nm のシリコン酸化膜を形成した後、該シリコン酸化膜をエッチバックすることにより、ゲート電極 13 の側面上に断面形状が I 字状のオフセットスペーサ 15 を形成する。その後、活性領域 10A に、ゲート電極 13 及びオフセットスペーサ 15 をマスクにして、p 型不純物であるボロンをドーズ量  $4 \times 10^{14} \text{ ions/cm}^2$  で注入して p 型エクステンション領域 16 を形成する。

40

#### 【0067】

次に、図 6 (b) に示すように、例えば CVD 法により、例えば膜厚が 5 nm のシリコン酸化膜と膜厚が 30 nm のシリコン窒化膜とを順次堆積した後、シリコン酸化膜及びシリコン窒化膜からなる積層膜をエッチバックすることで、ゲート電極 13 の側面上に、オフセットスペーサ 15 を介してサイドウォール 19 を形成する。ここで、サイドウォール 19 は、シリコン酸化膜からなる断面形状が L 字状の内側サイドウォール 17 と、L 字状

50

の内側サイドウォール 17 上に形成されたシリコン窒化膜からなる外側サイドウォール 18 とで構成されている。

#### 【 0 0 6 8 】

次に、図 6 ( c ) に示すように、例えば CVD 法により、半導体基板 10 上の全面に、例えば膜厚が 30 nm のシリコン酸化膜からなる保護膜 24 を堆積する。その後、保護膜 24 上に、保護膜 24 のうち、ゲート電極 13 、サイドウォール 19 、及び後工程でトレンチ部を形成するトレンチ部形成領域の上に設けられた部分を露出させる開口部を有し、且つ、保護膜 24 のうち、素子分離領域 11a 、 11b 上、及び、素子分離領域 11a 、 11b と活性領域 10A との境界位置から活性領域 10A 側に所定の距離だけ離れた位置までに亘る領域上に設けられた部分を覆うレジスト 31 を形成する。次いで、レジスト 31 をマスクにして保護膜 24 をエッチングする。これにより、トレンチ部形成領域を露出させる開口部を有し、且つ、活性領域 10A の端部であって、素子分離領域 11a 、 11b との境界領域（基板領域）を覆う保護膜 24 を形成する。なお、本実施形態では、素子分離領域 11a 、 11b の全面を覆うようにレジスト 31 を形成したが、所定の位置に開口部を有し、且つ、基板領域の上方に形成された保護膜 24 を覆っていれば、必ずしも素子分離領域 11a 、 11b 上にレジスト 31 を形成する必要はない。

10

#### 【 0 0 6 9 】

次に、図 7 ( a ) に示すように、レジスト 31 を除去した後、ゲート絶縁膜 12 、ゲート電極 13 、保護絶縁膜 14 、オフセットスペーサ 15 、及びサイドウォール 19 を有するゲート部 50 と、保護膜 24 からなるマスク部 50d とをマスクにして、露出している半導体基板 10 を所望の深さまでエッチングする。これにより、活性領域 10A におけるサイドウォール 19 と保護膜 24 との間に位置する領域（トレンチ部形成領域）にトレンチ部 20 を形成する。このとき、活性領域 10A の端部であって、素子分離領域 11a 、 11b と隣接する領域（基板領域）上には保護膜 24 が形成されているため、素子分離領域 11a 、 11b とトレンチ部 20 との間には半導体基板 10 が残存する。これにより、トレンチ部 20 内には素子分離領域 11a 、 11b が露出することなく、トレンチ部 20 の内壁全体は半導体基板 10 で構成される。

20

#### 【 0 0 7 0 】

次に、例えば MOCVD (Metal Organic Chemical Vapor Deposition) 法により、例えばシランガス (SiH<sub>4</sub>) 及びゲルマン (GeH<sub>4</sub>) ガスを、ジボラン (B<sub>2</sub>H<sub>6</sub>) などの p 型ドーパントガスとともに 650 ~ 700 の温度で供給することにより、トレンチ部 20 内を充填するように p 型 SiGe 層 21 をエピタキシャル成長させる。このとき、p 型 SiGe 層 21 の上面は、ゲート電極 13 直下に位置する半導体基板 10 の上面の高さに比べて同等以上の高さになるように形成することが望ましい。この場合、ゲート電極 13 の下方に形成されるチャネル領域に対して、p 型 SiGe 層 21 が十分に応力ができるので、p 型 MIS ツランジスタの駆動能力をより一層高めることができる。

30

#### 【 0 0 7 1 】

続いて、半導体基板 10 に熱処理を行うことにより、p 型 SiGe 層 21 中の p 型不純物を半導体基板 10 に拡散させる。これにより、活性領域 10A における素子分離領域 11a 、 11b と p 型 SiGe 層 21 との間に位置する領域（基板領域）に p 型不純物領域 22 を形成する。本工程により、サイドウォール 19 の外側方下に位置する領域に、p 型 SiGe 層 21 及び p 型不純物領域 22 からなる p 型ソース・ドレイン領域が形成される。

40

#### 【 0 0 7 2 】

ここで、上述の工程では、p 型 SiGe 層 21 を形成した後に、p 型 SiGe 層 21 を含む活性領域 10A に、ゲート電極 13 及びサイドウォール 19 をマスクにして p 型不純物である例えはボロンを、ドーズ量が  $4 \times 10^{15}$  ions/cm<sup>2</sup> で、注入角度が 10 ° ~ 25 ° の注入条件で斜めイオン注入した後、熱処理を行うことで p 型不純物領域 22 を形成してもよい。この場合、p 型 SiGe 層 21 中の p 型不純物のみを拡散させて p 型

50

不純物領域 2 2 を形成するよりも、基板領域に短時間の熱処理で高濃度の p 型不純物領域 2 2 を確実に形成することができる。

#### 【 0 0 7 3 】

次に、図 7 ( c ) に示すように、ゲート電極 1 3 上に設けられた保護絶縁膜 1 4 を除去した後、スパッタ法等により、半導体基板 1 0 の上に、例えばニッケル ( N i )、コバルト ( C o ) 又は白金 ( P t ) 等からなる金属膜を堆積する。その後、堆積した金属膜をアニールすることにより、ゲート電極 1 3 及び p 型 S i G e 層 2 1 の各上に金属シリサイド層 2 3 をそれぞれ形成する。ここで、p 型 S i G e 層 2 1 の形成後であれば、保護膜 2 4 を除去して、p 型不純物領域 2 2 上にも金属シリサイド層 2 3 を形成してもよい。次に、半導体基板 1 0 上に、層間絶縁膜、コンタクトプラグ、金属配線等 ( 図示せず ) を形成することによって、本実施形態に係る半導体装置を製造することができる。10

#### 【 0 0 7 4 】

本実施形態の半導体装置の製造方法の特徴は、図 7 ( a ) に示す工程でゲート部 5 0 及びマスク部 5 0 d を用いてトレンチ部 2 0 を形成することにある。この方法によれば、マスク部 5 0 d を構成する保護膜 2 4 の一部が、活性領域の端部であって、素子分離領域 1 1 a、1 1 b と隣接する領域 ( 基板領域 ) を覆うため、トレンチ部 2 0 と素子分離領域 1 1 a、1 1 bとの間に、基板領域を残存させることができる。その結果、トレンチ部 2 0 の内壁全体が半導体基板で構成されるため、良好にエピタキシャル成長を行うことができ、所望の特性を示す p 型 S i G e 層 2 1 を得ることができる。従って、本実施形態の半導体装置の製造方法によれば、良好な特性を示す p 型 S i G e 層を備え、高速で動作可能な半導体装置を製造することができる。20

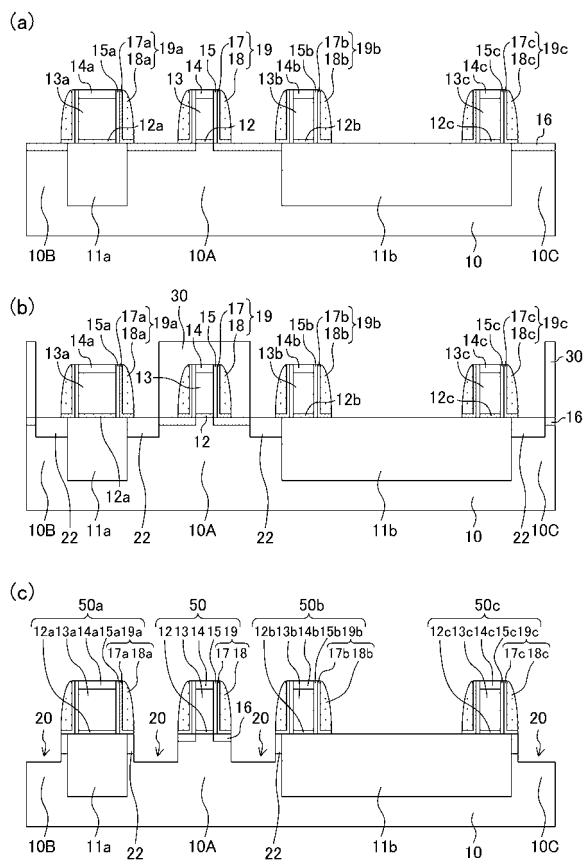

#### 【 0 0 7 5 】

##### ( 第 2 の実施形態の変形例 )

以下、本発明の第 2 の実施形態変形例に係る半導体装置の製造方法について図 8 を参照しながら説明する。図 8 ( a ) ~ ( c ) は、本実施形態の変形例に係る半導体装置の製造方法を示す断面図である。なお、図 8 において、図 6 、図 7 に示した構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

#### 【 0 0 7 6 】

まず、第 2 の実施形態に係る半導体装置の製造方法と同様にして、図 6 ( a )、( b ) に示す工程を行うことで、サイドウォール 1 9 が形成された図 6 ( b ) に示す構成を得る。30

#### 【 0 0 7 7 】

次に、図 8 ( a ) に示すように、活性領域 1 0 A に、ゲート電極 1 3 、オフセットスペーサ 1 5 、及びサイドウォール 1 9 をマスクにして p 型不純物であるボロンを、ドーズ量  $4 \times 1 0^{14}$  ions / cm<sup>2</sup> の注入条件でイオン注入した後、熱処理を行って p 型不純物領域 2 2 を形成する。

#### 【 0 0 7 8 】

次に、図 8 ( b ) に示すように、図 6 ( c ) 及び図 7 ( a ) と同様な方法によって、素子分離領域 1 1 a、1 1 b 及び p 型不純物領域 2 2 の一部上に、トレンチ部形成領域を露出させる開口部を有し、且つ、活性領域の端部であって、素子分離領域 1 1 a、1 1 b との境界領域 ( 基板領域 ) を覆う保護膜 2 4 を形成する。その後、ゲート絶縁膜 1 2 、ゲート電極 1 3 、保護絶縁膜 1 4 及びサイドウォール 1 9 を有するゲート部 5 0 と、保護膜 2 4 からなるマスク部 5 0 d をマスクにして、露出している半導体基板 1 0 を所望の深さまでエッチングしてトレンチ部 2 0 を形成する。40

#### 【 0 0 7 9 】

次に、図 8 ( c ) に示すように、例えば M O C V D 法により、トレンチ部 2 0 内を充填するように p 型 S i G e 層 2 1 をエピタキシャル成長させる。その後、ゲート電極 1 3 上に設けられた保護絶縁膜 1 4 を除去した後、ゲート電極 1 3 及びソース・ドレイン領域となる p 型 S i G e 層 2 1 の上に金属シリサイド層 2 3 をそれぞれ形成する。ここで、p 型 S i G e 層 2 1 を形成した後であれば、保護膜 2 4 を除去して p 型不純物領域 2 2 上にも50

金属シリサイド層 23 を形成してもよい。次に、半導体基板 10 上に、層間絶縁膜、コンタクトプラグ、金属配線等(図示せず)を形成することによって、本変形例に係る半導体装置を製造することができる。

#### 【0080】

本変形例の製造方法では、第2の実施形態の製造方法と同様にして、図8(b)に示す工程で、ゲート部 50 及びマスク部 50d を用いてトレンチ部 20 を形成する。この方法によれば、マスク部 50d を構成する保護膜 24 の一部が、活性領域の端部であって、素子分離領域 11a、11b と隣接する領域(基板領域)を覆うため、トレンチ部 20 と素子分離領域 11a、11bとの間に、基板領域を残存させることができる。その結果、トレンチ部 20 の内壁全体が半導体基板で構成されるため、良好にエピタキシャル成長を行うことができ、所望の特性を示す p型 SiGe 層 21 を得ることができる。従って、本変形例の製造方法によれば、良好な品質を有する p型 SiGe 層 21 を備え、高速に動作可能な半導体装置を実現することができる。10

#### 【0081】

なお、本変形例の製造方法では、図8(a)に示す工程において、ゲート電極 13 及びサイドウォール 19 をマスクにして p型不純物領域 22 を形成したが、第1の実施形態の第1変形例～第3変形例と同様な方法によって p型不純物領域 22 を形成しても良い。すなわち、第1の実施形態の第1変形例における図3(a)に示す工程と同様にして、図6(a)の工程の後で図6(b)の工程の前に、ゲート電極 13 及びオフセットスペーサ 15、並びにトレンチ部形成領域の一部を覆うレジストを注入マスクに用いて p型不純物領域 22 を形成する方法を用いてもよい。また、第1の実施形態の第2変形例における図4(b)に示す工程と同様にして、図6(b)の工程の後で、図7(a)の工程の前、好ましくは図6(c)の工程の前に、ゲート電極 13、オフセットスペーサ 15、サイドウォール 19 及びトレンチ部形成領域の一部を覆うレジストを注入マスクに用いて p型不純物領域 22 を形成する方法を用いてもよい。あるいは、第1の実施形態の第3変形例における図5(a)、図5(b)に示す工程と同様にして、図7(b)の工程で p型 SiGe 層 21 を形成した後で、図7(c)の工程の前に、半導体基板 10 上に、ゲート電極 13、オフセットスペーサ 15、サイドウォール 19 及び p型 SiGe 層 21 の一部を覆うレジストを注入マスクに用いて p型不純物領域 22 を形成する方法であってもよい。これらの方法を用いても、本変形例の製造方法と同様な効果を得ることができる。2030

#### 【0082】

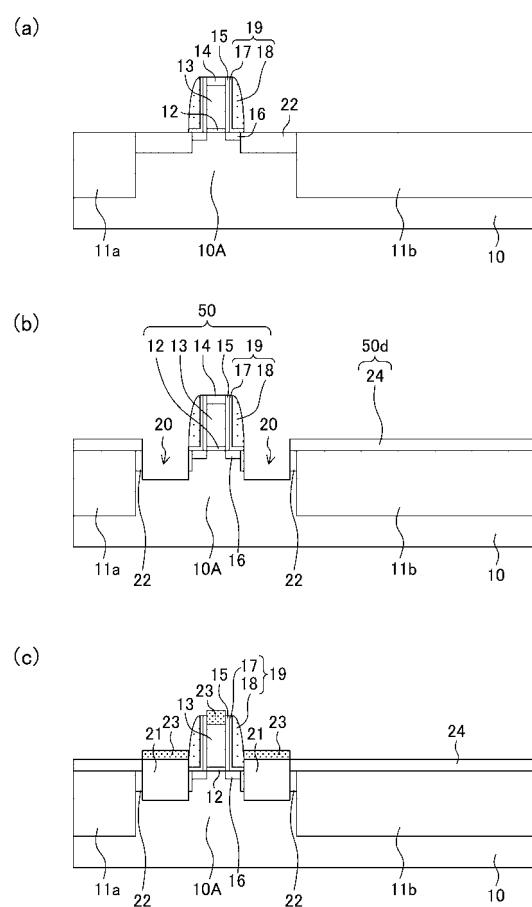

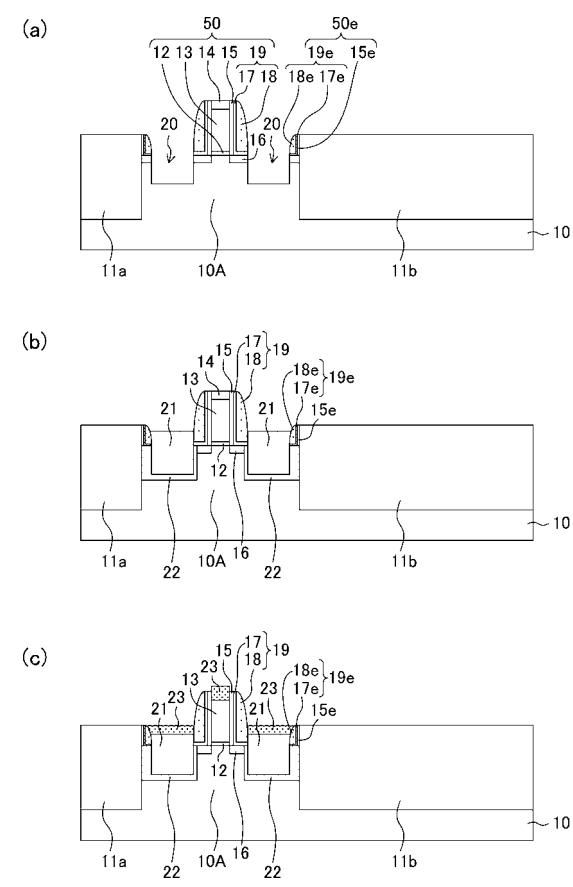

##### (第3の実施形態)

本発明の第3の実施形態に係る半導体装置の製造方法について図面を参照しながら説明する。図9及び図10は、本実施形態の半導体装置の製造方法を示す断面図である。なお、第1の実施形態(図1、図2)の構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

#### 【0083】

まず、図9(a)に示すように、第2の実施形態における図6(a)に示す工程と同様な方法によって、半導体基板 10 における素子分離領域 11a、11b に囲まれた活性領域 10A 上にゲート絶縁膜 12、ゲート電極 13 及び保護絶縁膜 14 を形成する。次に、ゲート電極 13 の側面上にオフセットスペーサ 15 を形成した後、活性領域 10A におけるゲート電極 13 の側方に p型エクステンション領域 16 を形成する。40

#### 【0084】

次に、図9(b)に示すように、例えば CVD 法により、半導体基板 10 上の全面に、例えば膜厚が 5 nm のシリコン酸化膜からなる第1絶縁膜 17A と、膜厚が 30 nm のシリコン窒化膜からなる第2絶縁膜 18A とを順次堆積する。

#### 【0085】

次に、図9(c)に示すように、第2絶縁膜 18A 上に、第2絶縁膜 18A のうち、ゲート電極 13、サイドウォール 19、及び後工程でトレンチ部を形成するトレンチ部形成領域の上に設けられた部分を露出させる開口部を有し、且つ、第2絶縁膜 18A のうち、50

素子分離領域 11a、11b 上、及び、素子分離領域 11a、11b と活性領域 10A と境界位置から活性領域 10A 側に所定の距離だけ離れた位置までに亘る領域上に設けられた部分を覆うレジスト 31 を形成する。その後、レジスト 31 をマスクにして第 2 絶縁膜 18A 及び第 1 絶縁膜 17A を順次エッティングする。これにより、ゲート電極 13 の側面上にオフセットスペーサ 15 を介してサイドウォール 19 を形成すると共に、素子分離領域 11a、11b 上、及び、活性領域 10A の端部であって、素子分離領域 11a、11b との境界領域（基板領域）上を覆い、第 1 絶縁膜 17A と第 2 絶縁膜 18A とからなるマスク部 50x を形成する。

#### 【0086】

次に、図 10 (a) に示すように、レジスト 31 を除去した後、ゲート絶縁膜 12、ゲート電極 13、保護絶縁膜 14、オフセットスペーサ 15、及びサイドウォール 19 を有するゲート部 50 と、第 1 絶縁膜 17A 及び第 2 絶縁膜 18A からなるマスク部 50x とをマスクにして、露出している半導体基板 10 を所望の深さまでエッティングする。これにより、活性領域 10A 内であって、平面的に見てサイドウォール 19 とマスク部 50x（第 1 絶縁膜 17A 及び第 2 絶縁膜 18A）との間に位置する領域（トレンチ部形成領域）にトレンチ部 20 を形成する。このとき、活性領域 10A の端部であって、素子分離領域 11a、11b と隣接する領域（基板領域）上にはマスク部 50x が形成されているため、素子分離領域 11a とトレンチ部 20 との間、及び、素子分離領域 11b とトレンチ部 20 との間には半導体基板 10 が残存する。このため、トレンチ部 20 内には素子分離領域 11a、11b が露出することなく、トレンチ部 20 の内壁全体は、半導体基板 10 で構成される。10

#### 【0087】

次に、図 10 (b) に示すように、第 2 の実施形態における図 7 (b) に示す工程と同様にして、トレンチ部 20 内を充填するように p 型 SiGe 層 21 をエピタキシャル成長させる。その後、半導体基板 10 に熱処理を行うことにより、p 型 SiGe 層 21 中の p 型不純物を半導体基板 10 に拡散させる。これにより、活性領域 10A において、素子分離領域 11a と p 型 SiGe 層 21 との間に位置する領域、及び、素子分離領域 11b と p 型 SiGe 層 21 との間に位置する領域に p 型不純物領域 22 を形成する。このとき、熱処理を行う前に、p 型 SiGe 層 21 を含む活性領域 10A に、ゲート電極 13 及びサイドウォール 19 をマスクにして p 型不純物であるボロンをイオン注入した後、熱処理を行って p 型不純物領域 22 を形成してもよい。この場合、短時間の熱処理で高濃度の p 型不純物領域 22 を比較的容易に形成することができる。20

#### 【0088】

次に、図 10 (c) に示すように、ゲート電極 13 上の保護絶縁膜 14 を除去した後、スパッタ法等により、半導体基板 10 の上に、例えはニッケル (Ni)、コバルト (Co) 又は白金 (Pt) 等からなる金属膜を堆積し、堆積した金属膜をアニールすることにより、ゲート電極 13 及び p 型 SiGe 層 21 の上に金属シリサイド層 23 をそれぞれ形成する。その後、半導体基板 10 上に、層間絶縁膜、コンタクトプラグ、金属配線等（図示せず）を形成することによって、本実施形態に係る半導体装置を製造することができる。30

#### 【0089】

本実施形態の半導体装置の製造方法の特徴は、第 2 の実施形態の半導体装置の製造方法と同様にして、基板領域を覆うマスク部 50x を用いてトレンチ部 20 を形成することにある。これにより、素子分離領域 11a、11b が露出することなくトレンチ部 20 が形成されるため、トレンチ部 20 内に制御良く p 型 SiGe 層 21 をエピタキシャル成長させることができる。また、本実施形態の半導体装置の製造方法では、マスク部 50x が MIS トランジスタのサイドウォール 19 と同一工程で形成されるため、複雑な工程を用いることなく、良好な品質を有する p 型 SiGe 層 21 を備え、高速に動作可能な半導体装置を比較的容易に製造することができる。40

#### 【0090】

なお、本実施形態の製造方法では、図 10 (b) に示す工程において、p 型 SiGe 層50

21に含まれる不純物の拡散またはp型不純物のイオン注入によってp型不純物領域22を形成したが、第1の実施形態の第1変形例～第3変形例の製造方法と同様な方法によってp型不純物領域22を形成しても良い。

#### 【0091】

##### (第4の実施形態)

本発明の第4の実施形態に係る半導体装置の製造方法について図面を参照しながら説明する。図11および図12は、本実施形態の半導体装置の製造方法を示す断面図である。なお、第1の実施形態(図1、図2)の構成部材と同一の構成部材には同一の符号を付すことにより詳細な説明は省略する。

#### 【0092】

まず、図11(a)に示すように、例えばSTI法により、例えば面方位が(100)面の主面を持つシリコン(Si)からなる半導体基板10の上部にトレンチを形成し、該トレンチ内に絶縁膜が埋め込んで素子分離領域11a、11bを選択的に形成する。これにより、素子分離領域11a、11bによって囲まれた半導体基板10からなる活性領域10Aが形成される。このとき、上面が活性領域10Aの上面よりも、例えば30nm程度高くなるように素子分離領域11a、11bを形成し、活性領域10Aと素子分離領域11a、11bとの境界に段差を設ける。このとき、例えば、活性領域10A上にシリコン酸化膜及びシリコン窒化膜からなる膜厚50nmの保護膜を形成した状態で、CMP法を用いてトレンチ内に絶縁膜を埋め込み、その後、活性領域10A上の保護膜を除去することによって、活性領域10Aと素子分離領域11a、11bとの境界に所望の段差を設けることができる。あるいは、素子分離領域11a、11bを形成した後、活性領域10Aの上部をエッティングして、活性領域10Aと素子分離領域11a、11bとの境界に所望の段差を設けてもよい。続いて、n型ウェル領域(図示せず)を形成した後、活性領域10A上にシリコン酸窒化膜からなるゲート絶縁膜12、ポリシリコン膜からなるゲート電極13及びシリコン酸化膜からなる保護絶縁膜14を形成する。

#### 【0093】

次に、図11(b)に示すように、半導体基板10上の全面にシリコン酸化膜を形成した後、シリコン酸化膜をエッチバックすることにより、ゲート電極13の側面上に断面形状がI字状のオフセットスペーサ15を形成するとともに、素子分離領域11a、11bの側面上に断面形状がI字状のオフセットスペーサ15eを形成する。このとき、オフセットスペーサ15eは必ずしも形成する必要はない。その後、活性領域10Aにおけるゲート電極13の側方下の領域にp型エクステンション領域16を形成する。

#### 【0094】

次に、図11(c)に示すように、例えばCVD法により、半導体基板10上の全面に、シリコン酸化膜及びシリコン窒化膜を順次堆積した後、シリコン酸化膜及びシリコン窒化膜からなる積層膜をエッチバックすることにより、ゲート電極13の側面上にオフセットスペーサ15を介してサイドウォール19を形成するとともに、素子分離領域11a、11bの側面上にはオフセットスペーサ15eを介してサイドウォール19eを形成する。ここで、サイドウォール19は、シリコン酸化膜からなる断面形状がL字状の内側サイドウォール17と、内側サイドウォール17上に形成されたシリコン窒化膜からなる外側サイドウォール18とで構成されている。同様に、サイドウォール19eは、シリコン酸化膜からなる断面形状がL字状の内側サイドウォール17eと、内側サイドウォール17e上に形成されたシリコン窒化膜からなる外側サイドウォール18eとで構成されている。

#### 【0095】

次に、図12(a)に示すように、ゲート絶縁膜12、ゲート電極13、保護絶縁膜14、オフセットスペーサ15、及びサイドウォール19を有するゲート部50と、オフセットスペーサ15e及びサイドウォール19eを有するマスク部50eとをマスクにして、露出している半導体基板10を所望の深さまでエッティングする。これにより、活性領域10Aの端部であって、平面的に見てサイドウォール19とサイドウォール19eとの間

10

20

30

40

50

の領域（トレンチ部形成領域）にトレンチ部20を形成する。このとき、活性領域10Aの端部であって、素子分離領域11a、11bと隣接する領域（基板領域）上にはマスク部50eが形成されているため、素子分離領域11aとトレンチ部20との間、及び、素子分離領域11bとトレンチ部20との間には、半導体基板10が残存する。このため、トレンチ部20内には素子分離領域11a、11bが露出することなく、トレンチ部20の内壁全体は半導体基板10で構成される。

#### 【0096】

次に、図12（b）に示すように、第2の実施形態における図7（b）に示す工程と同様にして、トレンチ部20内を充填するようにp型SiGe層21をエピタキシャル成長させる。その後、半導体基板10に熱処理を行うことにより、p型SiGe層21中のp型不純物を半導体基板10に拡散させる。これにより、活性領域10Aにおける、素子分離領域11a、11bとp型SiGe層21との間に位置する領域にp型不純物領域22を形成する。このとき、熱処理を行う前に、p型SiGe層21を含む活性領域10Aに、ゲート電極13及びサイドウォール19をマスクにしてp型不純物であるボロンをイオン注入した後、熱処理を行ってp型不純物領域22を形成してもよい。10

#### 【0097】

次に、図12（c）に示すように、ゲート電極13上の保護絶縁膜14を除去した後、スパッタ法等により、半導体基板10の上に、例えばニッケル（Ni）、コバルト（Co）又は白金（Pt）等からなる金属膜を堆積し、堆積した金属膜をアニールすることにより、ゲート電極13及びp型SiGe層21の各上部に金属シリサイド層23を形成する。20その後、半導体基板10上に、層間絶縁膜、コンタクトプラグ、金属配線等（図示せず）を形成することによって、本実施形態に係る半導体装置を製造することができる。

#### 【0098】

本実施形態の半導体装置の製造方法によれば、第2の実施形態及びその変形例と同様にして、活性領域10Aの端部であって、素子分離領域11a、11bとの境界領域（基板領域）を覆うマスク部50eを用いてトレンチ部20を形成する。これにより、素子分離領域11a、11bが露出することなくトレンチ部が形成されるので、トレンチ内に制御良くp型SiGe層21をエピタキシャル成長させることができる。また、本実施形態の半導体装置の製造方法では、素子分離領域11a、11bの上面を半導体基板10の上面よりも高くして段差を設けることで、MISトランジスタのサイドウォール19形成時に段差部分に自己整合的にマスク部50eを形成することができる。その結果、本実施形態の半導体装置を用いれば、良好な品質を有するp型SiGe層21を備え、高速に動作可能な半導体装置を比較的容易に製造することができる。30

#### 【0099】

なお、本実施形態の製造方法では、図12（b）に示す工程において、p型SiGe層21からの拡散またはp型不純物のイオン注入によってp型不純物領域22を形成したが、第1の実施形態の第1変形例～第3変形例と同様な方法によってp型不純物領域22を形成してもよい。

#### 【0100】

なお、本発明に係る第1～第4の実施形態及びその各変形例では、p型MISトランジスタを用いて説明したが、n型MISトランジスタであっても、例えばシリコン混晶層として、p型SiGe層の代わりにn型SIC層を用いれば、本発明の半導体装置およびその製造方法と同様な効果を得ることができる。40

#### 【産業上の利用可能性】

#### 【0101】

本発明の半導体装置及びその製造方法は、半導体装置の高性能化に有用である。

#### 【図面の簡単な説明】

#### 【0102】

【図1】（a）～（c）は、本発明の第1の実施形態の半導体装置の製造方法を示す断面図である。50

【図2】(a)～(c)は、第1の実施形態の半導体装置の製造方法を示す断面図である。

【図3】(a)～(c)は、第1の実施形態の第1変形例に係る半導体装置の製造方法を示す断面図である。

【図4】(a)～(c)は、第1の実施形態の第2変形例に係る半導体装置の製造方法を示す断面図である。

【図5】(a)～(c)は、第1の実施形態の第3変形例に係る半導体装置の製造方法を示す断面図である。

【図6】(a)～(c)は、第2の実施形態の半導体装置の製造方法を示す断面図である。

10

【図7】(a)～(c)は、第2の実施形態の半導体装置の製造方法を示す断面図である。

【図8】(a)～(c)は、第2の実施形態の変形例に係る半導体装置の製造方法を示す断面図である。

【図9】(a)～(c)は、第3の実施形態の半導体装置の製造方法を示す断面図である。

【図10】(a)～(c)は、第3の実施形態の半導体装置の製造方法を示す断面図である。

20

【図11】(a)～(c)は、第4の実施形態の半導体装置の製造方法を示す断面図である。

【図12】(a)～(c)は、第4の実施形態の半導体装置の製造方法を示す断面図である。

【図13】(a)～(c)は、従来の半導体装置の製造方法を示す断面図である。

#### 【符号の説明】

##### 【0103】

|                                     |              |    |

|-------------------------------------|--------------|----|

| 1 0                                 | 半導体基板        |    |

| 1 0 A、1 0 B、1 0 C                   | 活性領域         |    |

| 1 1 a、1 1 b                         | 素子分離領域       |    |

| 1 2                                 | ゲート絶縁膜       |    |

| 1 2 a、1 2 b、1 2 c                   | ダミーゲート絶縁膜    | 30 |

| 1 3                                 | ゲート電極        |    |

| 1 3 a、1 3 b、1 3 c                   | ダミーゲート電極     |    |

| 1 4                                 | 保護絶縁膜        |    |

| 1 4 a、1 4 b、1 4 c                   | ダミー保護絶縁膜     |    |

| 1 5                                 | オフセットスペーサ    |    |

| 1 5 a、1 5 b、1 5 c                   | オフセットスペーサ    |    |

| 1 6                                 | p型エクステンション領域 |    |

| 1 7、1 7 a、1 7 b、1 7 c               | 内側サイドウォール    |    |

| 1 7 A                               | 第1絶縁膜        |    |

| 1 8、1 8 a、1 8 b、1 8 c               | 外側サイドウォール    | 40 |

| 1 8 A                               | 第2絶縁膜        |    |

| 1 9、1 9 a、1 9 b、1 9 c               | サイドウォール      |    |

| 2 0                                 | トレンチ部        |    |

| 2 1                                 | p型SiGe層      |    |

| 2 2                                 | p型不純物領域      |    |

| 2 3                                 | 金属シリサイド層     |    |

| 2 4                                 | 保護膜          |    |

| 3 0、3 1                             | レジスト         |    |

| 5 0                                 | ゲート部         |    |

| 5 0 a、5 0 b、5 0 c、5 0 d、5 0 e、5 0 x | マスク部         | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 図 9 】

【 図 1 0 】

【図 1 1】

【 図 1 2 】

【図13】

---

フロントページの続き

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 鈴木 健

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 鈴木 純

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 瀧内 健夫

(56)参考文献 特開2007-110098(JP,A)

特開2007-220808(JP,A)

特開2001-244437(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/78