# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**G09G 3/20** (2006.01) **G11C 19/18** (2006.01) H01L 27/02 (2006.01) H01L 27/12 (2006.01)

(52) CPC특허분류 G09G 3/20 (2013.01)

G11C 19/184 (2013.01)

(21) 출원번호 10-2023-0076717(분할)

(22) 출원일자 2023년06월15일 심사청구일자 2023년06월15일

(62) 원출원 특허 10-2022-0121533

> 2022년09월26일 원출원일자 2022년09월26일 심사청구일자

(30) 우선권주장

JP-P-2011-222990 2011년10월07일 일본(JP)

(43) 공개일자

(11) 공개번호

10-2023-0095890 2023년06월29일

가부시키가이샤 한도오따이 에네루기 켄큐쇼

(71) 출원인

일본국 가나가와켄 아쓰기시 하세 398

(72) 발명자

사카쿠라 마사유키

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내

고토 유우고

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내 (뒷면에 계속)

(74) 대리인

장훈

전체 청구항 수 : 총 3 항

#### (54) 발명의 명칭 **반도체 장치**

#### (57) 요 약

[과제] 정전 파괴에 의한 제조 수율의 저하를 방지할 수 있는 반도체 장치.

[해결수단] 복수의 화소를 선택하기 위한 신호를 주사선에 공급하는 주사선 구동 회로가, 상기 신호를 생성하는 시프트 레지스터를 가지고 있고, 상기 시프트 레지스터에 있어서, 복수의 트랜지스터의 게이트 전극으로서 기능 하는 하나의 도전막을 복수로 분할하고, 상기 분할된 도전막끼리를, 분할된 도전막과 상이한 층에 형성된 도전막 에 의해, 전기적으로 접속하는 구성을 가진다. 상기 복수의 트랜지스터에는, 시프트 레지스터의 출력 측의 트랜 지스터가 포함되는 것으로 한다.

#### 대 표 도 - 도1

#### (52) CPC특허분류

H01L 27/0248 (2013.01) H01L 27/1225 (2013.01) H01L 27/124 (2013.01)

G09G 2300/0809 (2013.01)

G09G 2310/0267 (2013.01)

G09G 2310/0286 (2013.01)

(72) 발명자

#### 미야케 히로유키

일본 243-0036 가나가와켄 아쓰기시 하세 398 가부 시키가이샤 한도오따이 에네루기 켄큐쇼 내

#### 구로사키 다이스케

일본 243-0036 가나가와켄 아쓰기시 하세 398 가부 시키가이샤 한도오따이 에네루기 켄큐쇼 내

#### 명세서

### 청구범위

#### 청구항 1

제 1 트랜지스터 내지 제 10 트랜지스터를 갖고,

상기 제 1 트랜지스터 내지 상기 제 10 트랜지스터는 동일한 채널형이고,

상기 제 1 트랜지스터에서는, 소스 또는 드레인의 한쪽이 제 1 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 제 2 배선에 전기적으로 접속되고,

상기 제 2 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 2 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 제 3 배선에 전기적으로 접속되고,

상기 제 3 트랜지스터에서는, 소스 또는 드레인의 한쪽이 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 7 트랜지스터의 게이트에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 4 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 7 트랜지스터의 게이트에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 제 5 배선에 전기적으로 접속되고,

상기 제 5 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 6 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 7 트랜지스터의 소스 또는 드레인의 한쪽에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 8 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 9 트랜지스터의 소스 또는 드레인의 한쪽에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 9 트랜지스터에서는, 소스 또는 드레인의 다른쪽이 제 6 배선에 전기적으로 접속되고,

상기 제 10 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되는 반도체 장치에 있어서,

상기 제 1 트랜지스터의 게이트로서의 기능을 갖는 제 1 도전층은 제 2 도전층을 통하여 상기 제 3 트랜지스터의 게이트로서의 기능을 갖는 제 3 도전층에 전기적으로 접속되고,

상기 제 2 배선은 상기 제 1 트랜지스터 내지 상기 제 10 트랜지스터를 갖는 회로로부터 출력되는 신호를 전달하는 기능을 갖고,

상기 제 6 배선에는 펄스를 갖는 신호가 입력되는, 반도체 장치.

#### 청구항 2

제 1 트랜지스터 내지 제 10 트랜지스터를 갖고,

상기 제 1 트랜지스터 내지 상기 제 10 트랜지스터는 동일한 채널형이고,

상기 제 1 트랜지스터에서는, 소스 또는 드레인의 한쪽이 제 1 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 제 2 배선에 전기적으로 접속되고,

상기 제 2 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 2 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 제 3 배선에 전기적으로 접속되고,

상기 제 3 트랜지스터에서는, 소스 또는 드레인의 한쪽이 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 7 트랜지스터의 게이트에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의

게이트에 전기적으로 접속되고,

상기 제 4 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 7 트랜지스터의 게이트에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 제 5 배선에 전기적으로 접속되고,

상기 제 5 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 6 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 7 트랜지스터의 소스 또는 드레인의 한쪽에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 8 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 9 트랜지스터의 소스 또는 드레인의 한쪽에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 9 트랜지스터에서는, 소스 또는 드레인의 다른쪽이 제 6 배선에 전기적으로 접속되고,

상기 제 10 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되는 반도체 장치에 있어서,

상기 제 1 트랜지스터의 게이트로서의 기능을 갖는 제 1 도전층은 제 2 도전층을 통하여 상기 제 3 트랜지스터의 게이트로서의 기능을 갖는 제 3 도전층에 전기적으로 접속되고,

상기 제 1 트랜지스터의 채널 길이에 대한 채널 폭의 비는 상기 제 3 트랜지스터의 채널 길이에 대한 채널 폭의 비보다도  $\exists$ 고.

상기 제 2 배선은 상기 제 1 트랜지스터 내지 상기 제 10 트랜지스터를 갖는 회로로부터 출력되는 신호를 전달하는 기능을 갖고,

상기 제 6 배선에는 펄스를 갖는 신호가 입력되는, 반도체 장치.

#### 청구항 3

제 1 트랜지스터 내지 제 10 트랜지스터를 갖고,

상기 제 1 트랜지스터 내지 상기 제 10 트랜지스터는 동일한 채널형이고,

상기 제 1 트랜지스터에서는, 소스 또는 드레인의 한쪽이 제 1 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 제 2 배선에 전기적으로 접속되고,

상기 제 2 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 2 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 제 3 배선에 전기적으로 접속되고,

상기 제 3 트랜지스터에서는, 소스 또는 드레인의 한쪽이 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 7 트랜지스터의 게이트에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 4 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 7 트랜지스터의 게이트에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 제 5 배선에 전기적으로 접속되고,

상기 제 5 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 또한, 소스 또는 드레인의 다른쪽이 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 6 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 7 트랜지스터의 소스 또는 드레인의 한쪽에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 8 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 4 배선에 전기적으로 접속되고, 소스 또는 드레인의 다른쪽이 상기 제 9 트랜지스터의 소스 또는 드레인의 한쪽에 전기적으로 접속되고, 또한, 게이트가 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제 9 트랜지스터에서는, 소스 또는 드레인의 다른쪽이 제 6 배선에 전기적으로 접속되고,

상기 제 10 트랜지스터에서는, 소스 또는 드레인의 한쪽이 상기 제 1 트랜지스터의 게이트에 전기적으로 접속되는 반도체 장치에 있어서,

상기 제 1 트랜지스터의 게이트로서의 기능을 갖는 제 1 도전층은 제 2 도전층을 통하여 상기 제 3 트랜지스터의 게이트로서의 기능을 갖는 제 3 도전층에 전기적으로 접속되고,

상기 제 1 도전층은 상기 제 3 도전층과 항상 도통하고 있고,

상기 제 2 배선은 상기 제 1 트랜지스터 내지 상기 제 10 트랜지스터를 갖는 회로로부터 출력되는 신호를 전달하는 기능을 갖고,

상기 제 6 배선에는 펄스를 갖는 신호가 입력되는, 반도체 장치.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은, 절연 게이트형 전계 효과 트랜지스터를 사용한 반도체 장치에 관한 것이다.

#### 배경기술

[0002] 최근, 다결정 실리콘이나 미결정 실리콘에 의해 얻어지는 높은 이동도와, 비정질 실리콘에 의해 얻어지는 균일 한 소자 특성을 겸비한 새로운 반도체 재료로서, 산화물 반도체라고 불리는, 반도체 특성을 나타내는 금속 산화물에 주목이 모이고 있다. 금속 산화물은 다양한 용도에 사용되고 있으며, 예를 들면, 잘 알려진 금속 산화물인 산화인듐은, 액정 표시 장치 등에서 투명 전극 재료로서 사용되고 있다. 반도체 특성을 나타내는 금속 산화물로서는, 예를 들면, 산화탕스텐, 산화주석, 산화인듐, 산화아연 등이 있으며, 이러한 반도체 특성을 나타내는 금속 산화물을 채널 형성 영역에 사용하는 트랜지스터가, 이미 알려져 있다(특허문헌 1 및 특허문헌 2).

#### 선행기술문헌

#### 특허문헌

[0003] (특허문헌 0001) 일본 공개특허공보 제2007-123861호

(특허문헌 0002) 일본 공개특허공보 제2007-96055호

#### 발명의 내용

#### 해결하려는 과제

- [0004] 그런데, 비정질 실리콘이나 산화물 반도체를 갖는 트랜지스터로 구성된 반도체 표시 장치는, 제 5 세대(가로 1200mm×세로 1300mm) 이상의 유리 기판에 대응할 수 있기 때문에, 생산성이 높고, 비용이 낮다고 하는 이점을 가진다. 패널이 대형화되면, 반도체 표시 장치의 화소부에 있어서, 복수의 화소에 접속된 버스 라인이라고 불리는 배선, 예를 들면 주사선이나 신호선 등의 부하가 커진다. 이로 인해, 주사선이나 신호선에 전위를 공급하는 구동 회로에는 큰 전류 공급 능력이 요구되기 때문에, 구동 회로를 구성하는 트랜지스터, 특히 출력 측에 위치하는 트랜지스터는, 그 전기적 특성에도 따르지만, 패널의 대형화에 따라 사이즈가 증대되는 경향이 있다.

- [0005] 상기 트랜지스터의 사이즈가 증대되면, 구동 회로에 있어서 트랜지스터의 게이트 전국으로서 기능하는 배선의 면적이, 레이아웃을 고려하여, 증대된다. 이로 인해, 드라이 에칭 등의 플라즈마를 사용한 제조 공정에 있어서 배선에 전하가 축적되는, 소위 안테나 효과라고 불리는 현상이 일어나기 쉬우며, 배선에 축적된 상기 전하의 방전에 의해 배선이 정전 파괴될 확률이 높아진다.

- [0006] 특히, 비정질 실리콘이나 산화물 반도체를 갖는 트랜지스터는, 다결정 실리콘이나 단결정 실리콘을 사용한 트랜 지스터에 비해, 온 전류가 작은 경향이 있다. 비정질 실리콘이나 산화물 반도체를 갖는 트랜지스터를

사용하면, 패널의 대형화는 프로세스상 가능하지만, 구동 회로의 전류 공급 능력을 만족시키기 위해 더욱 큰 사이즈의 트랜지스터를 설계할 필요가 생긴다. 따라서, 배선의 면적 증대에 의한 배선의 정전 파괴의 확률이 향상되고, 그것에 의해 제조 수율의 저하가 초래되기 쉽다.

[0007] 상기한 바와 같은 기술적 배경하, 본 발명은, 정전 파괴에 의한 제조 수율의 저하를 방지할 수 있는 반도체 장치의 제공을, 과제의 하나로 한다.

#### 과제의 해결 수단

- [0008] 본 발명의 일 형태는, 안테나 효과에 의한 도전막으로의 전하의 축적을 방지하기 위해, 복수의 트랜지스터의 게이트 전국으로서 기능하는 하나의 도전막을 복수로 분할한다. 상기 분할된 도전막은 격리되어 있다. 그리고, 상기 분할된 도전막끼리를, 분할된 도전막과 상이한 도전막에 의해, 전기적으로 접속하는 구성을 가진다. 상기 복수의 트랜지스터에는, 구동 회로의 출력 측의 트랜지스터가 포함되는 것으로 한다.

- [0009] 또는, 본 발명의 일 형태에서는, 복수의 화소를 선택하기 위한 신호를 주사선에 공급하는 주사선 구동 회로가, 상기 신호를 생성하는 시프트 레지스터를 가지고 있으며, 상기 시프트 레지스터에 있어서, 복수의 트랜지스터의 게이트 전극으로서 기능하는 하나의 도전막을 복수로 분할한다. 상기 분할된 도전막은 격리되어 있다. 그리고, 상기 분할된 도전막끼리를, 분할된 도전막과 상이한 도전막에 의해, 전기적으로 접속하는 구성을 가진다. 상기 복수의 트랜지스터에는, 시프트 레지스터의 출력 측의 트랜지스터가 포함되는 것으로 한다.

- [0010] 분할된 도전막과 상이한 도전막은, 상기 분할된 도전막과 상이한 층에 형성되어 있어도 좋다. 그리고, 상기의 상이한 층에 형성된 도전막은, 상기 복수의 트랜지스터의 소스 전극 및 드레인 전극과 동일한 층에 형성되어 있 어도 좋다.

- [0011] 또한, 본 발명의 일 형태에서는, 상기 복수의 트랜지스터가, 비정질 실리콘 또는 산화물 반도체를 활성층에 갖고 있어도 좋다.

- [0012] 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 복수의 도전막끼리를, 상이한 층에 형성된 도전막에서 전기적으로 접속함으로써, 하나의 도전막을 복수의 게이트 전극으로서 기능시키는 경우보다도, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 패널의 대형화에 의해 구동 회로의 출력 측에 위치하는 트랜지스터의 사이즈가 증대되어도, 상기 트랜지스터의 게이트 전극으로서 기능하는 도전막의 면적을 작게 억제할 수 있고, 그것에 의해, 게이트 전극을 에칭에 의해 형성하는 공정 등, 플라즈마를 사용한 제조 공정에 있어서, 안테나 효과에 의해 상기 도전막이 정전 파괴되는 것을 방지할 수 있다.

- [0013] 구체적으로, 본 발명의 일 형태에 따르는 반도체 장치는, 복수의 화소에 신호를 공급하는 구동 회로를 가진다. 상기 구동 회로는 복수의 트랜지스터를 가지며, 상기 복수의 트랜지스터 중, 신호의 출력 측의 적어도 하나의 트랜지스터와, 상기 출력 측의 트랜지스터 이외의 적어도 하나의 트랜지스터는, 서로의 게이트 전극이, 게이트 전극과 상이한 도전막에 의해, 전기적으로 접속되어 있다.

#### 박명의 효과

[0014] 본 발명의 일 형태에 따르는 반도체 장치에서는, 상기 구성에 의해, 정전 파괴에 의한 제조 수율의 저하를 방지할 수 있다.

#### 도면의 간단한 설명

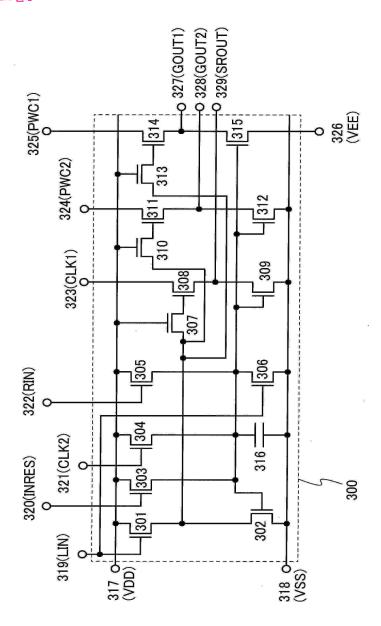

- [0015] 도 1은 본 발명의 반도체 장치의 구성을 도시하는 도면.

- 도 2는 트랜지스터의 상면도 및 단면도.

- 도 3은 트랜지스터의 상면도 및 단면도.

- 도 4는 본 발명의 반도체 장치의 구성을 도시하는 회로도.

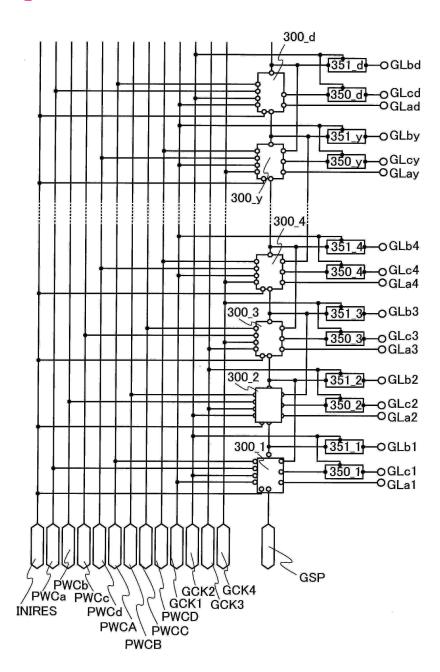

- 도 5는 시프트 레지스터의 구성을 도시하는 도면.

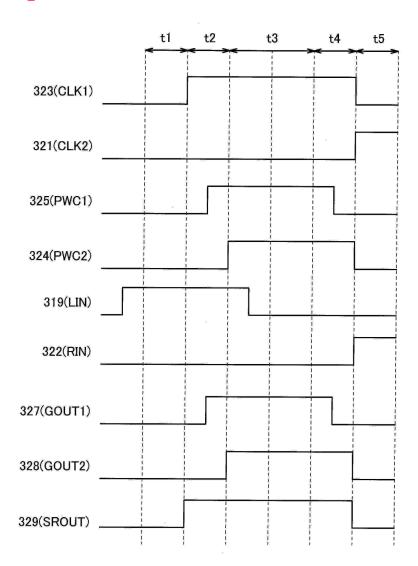

- 도 6은 펄스 출력 회로의 동작을 도시하는 타이밍 차트.

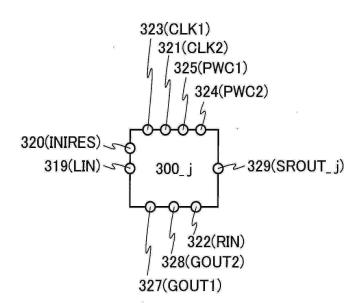

- 도 7은 제 j 펄스 발생 회로를, 모식적으로 도시하는 도면.

- 도 8은 펄스 발생 회로의 구성을 도시하는 도면.

- 도 9는 펄스 발생 회로의 구성을 도시하는 도면.

- 도 10은 펄스 발생 회로의 구성을 도시하는 도면.

- 도 11은 구동 회로와 화소의 단면도.

- 도 12는 패널의 구성을 도시하는 도면.

- 도 13은 전자 기기의 도면.

#### 발명을 실시하기 위한 구체적인 내용

- [0016] 이하에서는, 본 발명의 실시형태에 관해서 도면을 사용하여 상세하게 설명한다. 단, 본 발명은 이하의 설명으로 한정되지 않고, 본 발명의 취지 및 그 범위에서 일탈하지 않고 그 형태 및 상세를 다양하게 변경할 수 있는 것은, 당업자라면 용이하게 이해할 수 있다. 따라서, 본 발명은, 이하에 나타내는 실시형태의 기재 내용으로 한정하여 해석되는 것은 아니다.

- [0017] 또한, 본 발명은, 집적 회로, RF 태그, 반도체 표시 장치 등, 트랜지스터를 사용한 모든 반도체 장치를, 그 범주에 포함한다. 또한, 집적 회로에는, 마이크로 프로세서, 화상 처리 회로, DSP(Digital Signal Processor), 마이크로 콘트롤러를 포함하는 LSI(Large Scale Integrated Circuit), FPGA(Field Programmable Gate Array)이나 CPLD(Complex PLD) 등의 프로그래머블 논리 회로(PLD: Programmable Logic Device)가, 그 범주에 포함된다. 또한, 반도체 표시 장치에는, 액정 표시 장치, 유기 발광 소자(OLED)로 대표되는 발광 소자를 각 화소에 구비한 발광 장치, 전자 페이퍼, DMD(Digital Micromirror Device), PDP(Plasma Display Panel), FED(Field Emission Display) 등, 반도체막을 사용한 회로 소자를 구동 회로에 가지고 있는 반도체 표시 장치가, 그 범주에 포함된다.

- [0018] 또한, 본 명세서에 있어서 반도체 표시 장치란, 액정 소자나 발광 소자 등의 표시 소자가 각 화소에 형성된 패널과, 상기 패널에 콘트롤러를 포함하는 IC 등을 실장한 상태에 있는 모듈을, 그 범주에 포함한다.

- [0019] (실시형태 1)

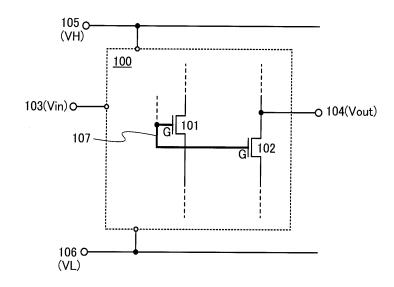

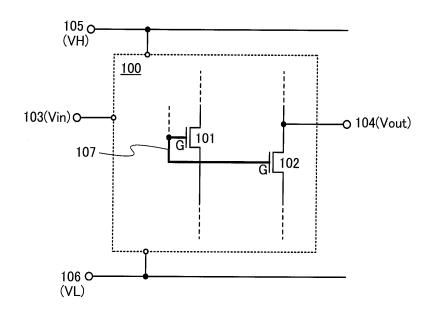

- [0020] 도 1에, 본 발명의 일 형태에 따르는 반도체 장치의, 회로 구성의 일례를 도시한다. 도 1에 도시하는 반도체 장치(100)는, 적어도 트랜지스터(101)와, 트랜지스터(102)를 포함하는 복수의 트랜지스터를 가진다.

- [0021] 반도체 장치(100)에는, 배선(105) 및 배선(106)을 개재하여, 하이 레벨의 전위(VH), 또는 로우 레벨의 전위(VL)가 주어져 있다. 도 1에서는, 배선(105)을 개재하여 전위(VH)가 반도체 장치(100)에 주어지고, 배선(106)을 개재하여 전위(VL)가 반도체 장치(100)에 주어지고 있는 경우를 예시하고 있다. 또한, 반도체 장치(100)에는, 배선(103)을 개재하여 입력 신호의 전위(Vin)가 주어진다. 반도체 장치(100)에서는, 트랜지스터(101) 및 트랜지스터(102)를 포함하는 복수의 트랜지스터가, 전위(Vin)에 따라 스위칭을 행한다. 그리고, 전위(VH) 또는 전위(VL)의 어느 한쪽이 상기 스위칭에 의해 선택되고, 선택된 전위가 출력 신호의 전위(Vout)로서, 반도체 장치(100)로부터 배선(104)을 개재하여 출력된다.

- [0022] 트랜지스터(102)는 그 소스 단자 또는 드레인 단자의 한쪽이, 배선(104)에 접속되어 있다. 즉, 트랜지스터 (102)는, 반도체 장치(100)의 출력 측에 위치하고, 배선(104)으로의 전위(Vout)의 출력을 제어하는 기능을 가진다. 그리고, 본 발명의 일 형태에서는, 트랜지스터(101)의 게이트 전극(G로 나타낸다)과, 트랜지스터(102)의 게이트 전극(G로 나타낸다)이, 상기 게이트 전극과는 상이한 배선(107)에 의해, 전기적으로 접속되어 있다.

- [0023] 또한, 본 명세서에 있어서 접속이란, 특별히 언급하지 않는 경우, 전기적인 접속과 직접적인 접속의 양쪽을 의미하고 있으며, 전류, 전압 또는 전위가, 공급 가능, 또는 전송 가능한 상태에 상당한다. 따라서, 접속하고 있는 상태란, 직접 접속하고 있는 상태를 반드시 가리키는 것은 아니고, 전류, 전압 또는 전위가, 공급 가능, 또는 전송 가능하도록, 배선, 도전막, 저항, 다이오드, 트랜지스터 등의 소자를 개재하여 간접적으로 접속하고 있는 상태도, 그 범주에 포함한다.

- [0024] 또한, 트랜지스터의 소스 단자란, 활성층의 일부인 소스 영역, 또는 활성층에 접속된 소스 전극을 의미한다. 마찬가지로, 트랜지스터의 드레인 단자란, 활성층의 일부인 드레인 영역, 또는 활성층에 접속된 드레인 전극을 의미한다.

- [0025] 트랜지스터가 갖는 소스 단자와 드레인 단자는, 트랜지스터의 극성 및 각 전극에 주어지는 전위의 고저에 의해,

그 호칭이 바뀐다. 일반적으로, n채널형 트랜지스터에서는, 낮은 전위가 주어지는 전극이 소스 단자라고 불리고, 높은 전위가 주어지는 전극이 드레인 단자라고 불린다. 또한, p채널형 트랜지스터에서는, 낮은 전위가 주어지는 전극이 드레인 단자라고 불리고, 높은 전위가 주어지는 전극이 소스 단자라고 불린다. 본 명세서에서는, 편의상, 소스 단자와 드레인 단자가 고정되어 있는 것으로 가정하고, 트랜지스터의 접속 관계를 설명하는 경우가 있지만, 실제로는 상기 전위의 관계에 따라 소스 단자와 드레인 단자의 호칭이 바뀐다.

- [0026] 또한, 복수의 화소에 접속된 버스 라인이라고 불리는 부하가 큰 배선, 예를 들면 주사선이나 신호선 등에, 반도체 장치(100)로부터 출력되는 전위(Vout)를 공급하는 경우, 상기 전위(Vout)의 출력을 제어하는 트랜지스터 (102)에는, 큰 전류 공급 능력이 요구된다. 이로 인해, 상기 트랜지스터(102)의 채널 폭(W)은, 트랜지스터 (101)의 채널 폭(W)보다도, 큰 값으로 설계하는 것이 바람직하다.

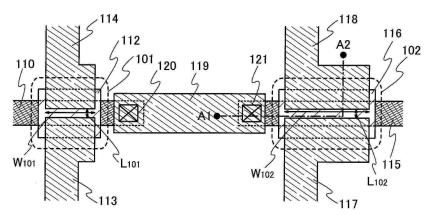

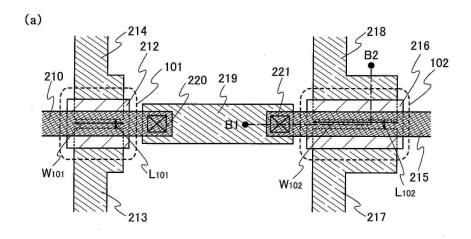

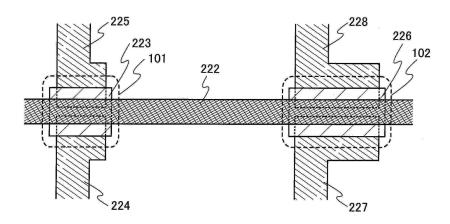

- [0027] 도 2a에, 도 1에 도시한 트랜지스터(101) 및 트랜지스터(102)의 상면도를, 일례로서 도시한다. 단, 도 2a에서는, 트랜지스터(101) 및 트랜지스터(102)의 레이아웃을 명확히 하기 위해, 게이트 절연막(111)을 생략한 상면도를 도시한다. 또한, 도 2a에 도시한 트랜지스터(102)의, 일점 쇄선 A1-A2에 있어서의 단면도의 일례를 도 2b에 도시한다.

- [0028] 도 2a에서는, 트랜지스터(101)가, 게이트 전극으로서 기능하는 도전막(110)과, 도전막(110) 위의 게이트 절연막(111)과, 게이트 절연막(111) 위에 있어서 도전막(110)과 중첩되는 위치에 형성된 반도체막(112)과, 반도체막(112) 위에 있어서 소스 전극 또는 드레인 전극으로서 기능하는 도전막(113) 및 도전막(114)을 가진다.

- [0029] \*또한, 도 2a 및 도 2b에서는, 트랜지스터(102)가, 게이트 전극으로서 기능하는 도전막(115)과, 도전막(115) 위의 게이트 절연막(111)과, 게이트 절연막(111) 위에 있어서 도전막(115)과 중첩되는 위치에 형성된 반도체막(116)과, 반도체막(116) 위에 있어서 소스 전극 또는 드레인 전극으로서 기능하는 도전막(117) 및 도전막(118)을 가진다.

- [0030] 그리고, 본 발명의 일 형태에서는, 출력 측에 위치하는 트랜지스터(102)쪽이, 트랜지스터(101)보다도 전류 공급 능력이 높다. 따라서, 본 발명의 일 형태에서는, 도 2a에 도시하는 바와 같이, 트랜지스터(102)의 채널 길이 (L<sub>102</sub>)에 대한 채널 폭(W<sub>102</sub>)의 비를, 트랜지스터(101)의 채널 길이(L<sub>101</sub>)에 대한 채널 폭(W<sub>101</sub>)의 비보다도, 큰 값으로 설계하는 것이 바람직하다. 구체적으로, 채널 길이(L<sub>102</sub>)에 대한 채널 폭(W<sub>102</sub>)의 비는, 채널 길이(L<sub>101</sub>)에 대한 채널 폭(W<sub>101</sub>)의 비의 2배 이상, 보다 바람직하게는 3배 이상인 것이 바람직하다.

- [0031] 또한, 도전막(110)과 도전막(115)은, 격리되어 있다. 또한, 본 명세서에 있어서 격리란, 물리적으로 떨어져 존 재하는 것을 의미한다. 그리고, 도 2a 및 도 2b에서는, 도전막(110)과 도전막(115)이, 배선으로서 기능하는 도 전막(119)을 개재하여, 전기적으로 접속되어 있다. 구체적으로, 도전막(110)과 도전막(115)은, 게이트 절연막(111)에 형성된 개구부(120) 및 개구부(121)를 개재하여, 도전막(119)에 접속되어 있다.

- [0032] 또한, 도 2a 및 도 2b에 도시하는 도전막(110)과 도전막(115)은, 절연 표면 위에 형성된 하나의 도전막을, 에칭 등에 의해 원하는 형상으로 가공함으로써, 형성할 수 있다. 그리고, 도전막(113) 및 도전막(114)과, 도전막(117) 및 도전막(118)과, 도전막(119)은, 개구부(120) 및 개구부(121)를 덮도록 게이트 절연막(111) 위에 형성된 하나의 도전막을, 에칭 등에 의해 원하는 형상으로 가공함으로써, 형성할 수 있다. 즉, 도전막(119)은, 도전막(110) 및 도전막(115)과, 상이한 층에 형성되어 있다.

- [0033] 도 2a 및 도 2b에 도시하는 바와 같이, 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 도전막(110) 및 도전막(115)을, 도전막(110) 및 도전막(115)과 상이한 층에 형성된 도전막(119)에 의해 전기적으로 접속하고 있다.

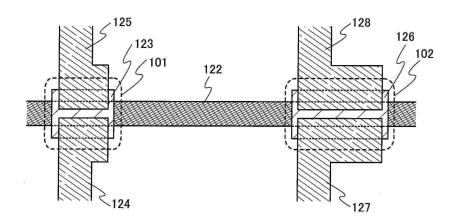

- [0034] 비교예로서, 도 2c에, 도 1에 도시한 트랜지스터(101) 및 트랜지스터(102)의 상면도의, 다른 일례로서 나타낸다. 단, 도 2c에서는, 트랜지스터(101) 및 트랜지스터(102)의 레이아웃을 명확히 하기 위해서, 게이트 절연막을 생략한 상면도를 도시한다.

- [0035] \*도 2c에서는, 트랜지스터(101)가, 게이트 전극으로서 기능하는 도전막(122)과, 도전막(122) 위의 게이트 절연막과, 게이트 절연막 위에 있어서 도전막(122)과 중첩되는 위치에 형성된 반도체막(123)과, 반도체막(123) 위에 있어서 소스 전극 또는 드레인 전극으로서 기능하는 도전막(124) 및 도전막(125)을 가진다.

- [0036] 또한, 도 2c에서는, 트랜지스터(102)가, 게이트 전극으로서 기능하는 도전막(122)과, 도전막(122) 위의 게이트 절연막과, 게이트 절연막 위에 있어서 도전막(122)과 중첩되는 위치에 형성된 반도체막(126)과, 반도체막(126)

위에 있어서 소스 전극 또는 드레인 전극으로서 기능하는 도전막(127) 및 도전막(128)을 가진다.

- [0037] 즉, 도 2c에서는, 트랜지스터(101)와 트랜지스터(102)가, 도전막(122)을 공유하고 있으며, 도전막(122)이 트랜지스터(101)의 게이트 전극 및 트랜지스터(102)의 게이트 전극으로서 기능한다. 따라서, 도 2c의 경우, 게이트 전극으로서 기능하는 도전막(122)의 면적이, 도 2a 및 도 2b에 있어서 게이트 전극으로서 기능하는 도전막(110) 및 도전막(115)의 각 면적보다도, 커진다.

- [0038] 따라서, 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 도전막(110) 및 도전막(115)의 각 면적을 비교예의 도전막(122)의 면적에 비해 작게 억제할 수 있기 때문에, 도전막(110) 및 도전막(115)을 에칭으로 제작할때에, 도전막(110) 및 도전막(115)의 각각에 축적되는 전하량을 작게 억제하는, 즉, 안테나 효과를 저감시킬 수있다. 따라서, 본 발명의 일 형태에서는, 도전막(110) 및 도전막(115)을 에칭으로 제작할때에, 비교예에비해, 상기 전하의 방전에 의한 도전막(110) 및 도전막(115)의 정전 파괴를 일어나기 어렵게 할 수 있다.

- [0039] 또한, 본 발명의 일 형태에서는, 도전막(110) 및 도전막(115) 위의 반도체막(112) 및 반도체막(116)을 에칭으로 제작할 때에도, 안테나 효과에 의한 도전막(110) 및 도전막(115)의 정전 파괴를 일어나기 어렵게 할 수 있다.

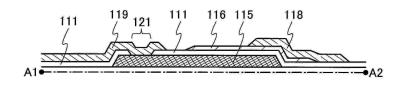

- [0040] 이어서, 도 3a에, 도 1에 도시한 트랜지스터(101) 및 트랜지스터(102)의 상면도의, 도 2a와 상이한 일례를 도시한다. 단, 도 3a에서는, 트랜지스터(101) 및 트랜지스터(102)의 레이아웃을 명확히 하기 위해서, 게이트 절연 막(211)을 생략한 상면도를 도시한다. 또한, 도 3a에 도시한 트랜지스터(102)의, 일점 쇄선 B1-B2에 있어서의 단면도의 일례를, 도 3b에 도시한다.

- [0041] 도 3a에서는, 트랜지스터(101)가, 소스 전극 또는 드레인 전극으로서 기능하는 도전막(213) 및 도전막(214)과, 도전막(213) 및 도전막(214) 위의 반도체막(212)과, 반도체막(212) 위의 게이트 절연막(211)과, 게이트 절연막(211) 위에 있어서 반도체막(212)과 중첩되는 위치에 형성된, 게이트 전극으로서 기능하는 도전막(210)을 가진다.

- [0042] 또한, 도 3a 및 도 3b에서는, 트랜지스터(102)가, 소스 전극 또는 드레인 전극으로서 기능하는 도전막(217) 및 도전막(218)과, 도전막(217) 및 도전막(218) 위의 반도체막(216)과, 반도체막(216) 위의 게이트 절연막(211)과, 게이트 절연막(211) 위에 있어서 반도체막(216)과 중첩되는 위치에 형성된, 게이트 전극으로서 기능하는 도전막(215)을 가진다.

- [0043] 그리고, 본 발명의 일 형태에서는, 출력 측에 위치하는 트랜지스터(102)쪽이, 트랜지스터(101)보다도 전류 공급 능력이 높다. 따라서, 본 발명의 일 형태에서는, 도 3a에 도시하는 바와 같이, 트랜지스터(102)의 채널 길이 (L<sub>102</sub>)에 대한 채널 폭(W<sub>102</sub>)의 비를, 트랜지스터(101)의 채널 길이(L<sub>101</sub>)에 대한 채널 폭(W<sub>101</sub>)의 비보다도, 큰 값으로 설계하는 것이 바람직하다. 구체적으로, 채널 길이(L<sub>102</sub>)에 대한 채널 폭(W<sub>102</sub>)의 비는, 채널 길이(L<sub>101</sub>)에 대한 채널 폭(W<sub>101</sub>)의 비의 2배 이상, 보다 바람직하게는 3배 이상인 것이 바람직하다.

- [0044] 또한, 도전막(210)과 도전막(215)은, 격리되어 있다. 그리고, 도 3a 및 도 3b에서는, 도전막(210)과 도전막(215)이, 배선으로서 기능하는 도전막(219)을 개재하여, 전기적으로 접속되어 있다. 구체적으로, 도전막(210)과 도전막(215)은, 게이트 절연막(211)에 형성된 개구부(220) 및 개구부(221)를 개재하여, 도전막(219)에 접속되어 있다.

- [0045] 또한, 도 3a 및 도 3b에 도시하는 도전막(210)과 도전막(215)은, 개구부(220) 및 개구부(221)를 덮도록 게이트 절연막(211) 위에 형성된 하나의 도전막을, 에칭 등에 의해 원하는 형상으로 가공함으로써, 형성할 수 있다. 그리고, 도전막(213) 및 도전막(214)과, 도전막(217) 및 도전막(218)과, 도전막(219)은, 절연 표면 위에 형성된 하나의 도전막을, 에칭 등에 의해 원하는 형상으로 가공함으로써, 형성할 수 있다. 즉, 도전막(219)은, 도전막(210) 및 도전막(215)과, 상이한 층에 형성되어 있다.

- [0046] 도 3a 및 도 3b에 도시하는 바와 같이, 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 도전막(210) 및 도전막(215)을, 도전막(210) 및 도전막(215)과 상이한 층에 형성된 도전막(219)에 의해 전기적으로 접속하고 있다.

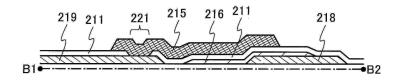

- [0047] 비교예로서, 도 3c에, 도 1에 도시한 트랜지스터(101) 및 트랜지스터(102)의 상면도의, 다른 일례로서 도시한다. 단, 도 3c에서는, 트랜지스터(101) 및 트랜지스터(102)의 레이아웃을 명확히 하기 위해서, 게이트 절연막을 생략한 상면도를 도시한다.

- [0048] \*도 3c에서는, 트랜지스터(101)가, 소스 전극 또는 드레인 전극으로서 기능하는 도전막(224) 및 도전막(225)과, 도전막(224) 및 도전막(225) 위의 반도체막(223)과, 반도체막(223) 위의 게이트 절연막과, 게이트 절연막 위에 있어서 반도체막(223)과 중첩되는 위치에 형성된, 게이트 전극으로서 기능하는 도전막(222)을 가진다.

- [0049] 또한, 도 3c에서는, 트랜지스터(102)가, 소스 전극 또는 드레인 전극으로서 기능하는 도전막(227) 및 도전막(228)과, 도전막(227) 및 도전막(228) 위의 반도체막(226)과, 반도체막(226) 위의 게이트 절연막과, 게이트 절연막 위에 있어서 반도체막(226)과 중첩되는 위치에 형성된, 게이트 전극으로서 기능하는 도전막(222)을 가진다.

- [0050] 즉, 도 3c에서는, 트랜지스터(101)와 트랜지스터(102)가, 도전막(222)을 공유하고 있으며, 도전막(222)이 트랜지스터(101)의 게이트 전극 및 트랜지스터(102)의 게이트 전극으로서 기능한다. 따라서, 도 3c의 경우, 게이트 전극으로서 기능하는 도전막(222)의 면적이, 도 3a 및 도 3b에 있어서 게이트 전극으로서 기능하는 도전막(210) 및 도전막(215)의 각 면적보다도, 커진다.

- [0051] 따라서, 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 도전막(210) 및 도전막(215)의 각 면적을 비교예의 도전막(222)의 면적에 비해 작게 억제할 수 있기 때문에, 도전막(210) 및 도전막(215)을 에칭으로 제작할때에, 도전막(210) 및 도전막(215)의 각각에 축적되는 전하량을 작게 억제하는, 즉, 안테나 효과를 저감시킬 수있다. 따라서, 본 발명의 일 형태에서는, 도전막(210) 및 도전막(215)을 에칭으로 제작할때에, 비교예에비해, 상기 전하의 방전에 의한 도전막(210) 및 도전막(215)의 정전 파괴를 일어나기 어렵게 할 수 있다.

- [0052] 또한, 본 발명의 일 형태에서는, 도전막(210) 및 도전막(215) 위의 각종 도전막을 에칭으로 원하는 형상으로 가공할 때에도, 안테나 효과에 의한 도전막(210) 및 도전막(215)의 정전 파괴를 일어나기 어렵게 할 수 있다.

- [0053] 이어서, 본 발명의 일 형태에 따르는 반도체 장치의 하나인, 펼스 발생 회로의 구성에 관해서 설명한다. 도 4에, 본 발명의 일 형태에 따르는 반도체 장치가 갖는, 펄스 발생 회로의 일례를 도시한다.

- [0054] 도 4에 도시하는 펄스 발생 회로(300)는, 트랜지스터(301) 내지 트랜지스터(315)와, 용량 소자(316)를 가진다. 트랜지스터(302)는, 도 1에서 도시한 트랜지스터(101)에 상당한다. 트랜지스터(309), 트랜지스터(312), 또는 트랜지스터(315)는, 도 1에서 도시한 트랜지스터(102)에 상당한다. 또한, 펄스 발생 회로(300)는, 배선(317) 내지 배선(326)으로부터 각종 전위가 주어지고, 배선(327) 내지 배선(329)에 전위를 출력하는 구성을 가지고 있다.

- [0055] 상기 펄스 발생 회로(300)를 복수단 접속시킴으로써, 시프트 레지스터를 구성할 수 있다.

- [0056] 구체적으로, 트랜지스터(301) 내지 트랜지스터(315)가 n채널형인 경우, 배선(317)에는 하이 레벨의 전위(VDD)가 주어지고, 배선(318)에는 로우 레벨의 전위(VSS)가 주어지고, 배선(326)에는 로우 레벨의 전위(VEE)가 주어진다. 전위(VEE)는 전위(VSS)와 동일한 전위이거나, 그것보다 높은 전위인 것이 바람직하다. 또한, 배선 (319)에는 전위(LIN)가 주어지고, 배선(320)에는 전위(INRES)가 주어지고, 배선(321)에는 전위(CLK2)가 주어지고, 배선(322)에는 전위(RIN)가 주어지고, 배선(323)에는 전위(CLK1)가 주어지고, 배선(324)에는 전위(PWC2)가 주어지고, 배선(325)에는 전위(PWC1)가 주어진다.

- [0057] 또한, 펄스 발생 회로(300)로부터 출력되는 전위(GOUT1)는, 배선(327)에 주어진다. 펄스 발생 회로(300)로부터 출력되는 전위(GOUT2)는, 배선(328)에 주어진다. 펄스 발생 회로(300)로부터 출력되는 전위(SROUT)는, 배선 (329)에 주어진다.

- [0058] 전위(LIN), 전위(RIN), 전위(CLK2), 및 전위(INRES)는, 도 1에 도시하는 반도체 장치(100)에 있어서의 전위 (Vin)에 상당한다. 전위(GOUT1), 전위(GOUT2), 및 전위(SROUT)는, 도 1에 도시하는 반도체 장치(100)에 있어서의 전위(Vout)에 상당한다. 전위(VSS), 전위(VEE), 전위(PWC1), 전위(PWC2), 및 전위(CLK1)는, 도 1에 도시하는 반도체 장치(100)에 있어서의 전위(VH) 또는 전위(VL)에 상당한다.

- [0059] 구체적으로, 트랜지스터(301)는, 그 게이트 전극이 배선(319)에 접속되어 있다. 또한, 트랜지스터(301)는, 그소스 단자 및 드레인 단자의 한쪽이 배선(317)에, 다른쪽이 트랜지스터(302)의 소스 단자 및 드레인 단자의 한쪽에, 각각 접속되어 있다. 트랜지스터(302)는, 그 게이트 전극이 트랜지스터(315)의 게이트 전극에 접속되어 있다. 또한, 트랜지스터(302)는, 그소스 단자 및 드레인 단자의 다른쪽이, 배선(318)에 접속되어 있다. 트랜지스터(303)는, 그게이트 전극이 배선(320)에 접속되어 있다. 또한, 트랜지스터(303)는, 그소스 단자 및 드레인 단자의 한쪽이 배선(317)에, 다른쪽이 트랜지스터(302)의 게이트 전극에, 각각 접속되어 있다. 트랜지스터(304)는, 그게이트 전극이 배선(321)에 접속되어 있다. 또한, 트랜지스터(304)는, 그소스 단자 및 드레인

단자의 한쪽이 배선(317)에, 다른쪽이 트랜지스터(302)의 게이트 전극에, 각각 접속되어 있다. 트랜지스터 (305)는, 그 게이트 전극이 배선(322)에 접속되어 있다. 또한, 트랜지스터(305)는, 그 소스 단자 및 드레인 단 자의 한쪽이 배선(317)에, 다른쪽이 트랜지스터(302)의 게이트 전극에, 각각 접속되어 있다. 트랜지스터(306) 는, 그 게이트 전극이 배선(319)에 접속되어 있다. 또한, 트랜지스터(306)는, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(302)의 게이트 전극에, 다른쪽이 배선(318)에, 각각 접속되어 있다. 트랜지스터(307)는, 그 게이트 전극이 배선(317)에 접속되어 있다. 또한, 트랜지스터(307)는, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(301)의 소스 단자 및 드레인 단자의 다른쪽에, 다른쪽이 트랜지스터(308)의 게이트 전극에, 각각 접 속되어 있다. 트랜지스터(308)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(323)에, 다른쪽이 배선(329)에, 각각 접속되어 있다. 트랜지스터(309)는, 그 게이트 전극이 트랜지스터(302)의 게이트 전극에 접속되어 있다. 또한, 트랜지스터(309)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(329)에, 다른쪽이 배선(318)에, 각각 접 속되어 있다. 트랜지스터(310)는, 그 게이트 전극이 배선(317)에 접속되어 있다. 또한, 트랜지스터(310)는, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(301)의 소스 단자 및 드레인 단자의 다른쪽에, 다른쪽이 트 랜지스터(311)의 게이트 전극에, 각각 접속되어 있다. 트랜지스터(311)는, 그 소스 단자 및 드레인 단자의 한 쪽이 배선(324)에, 다른쪽이 배선(328)에, 각각 접속되어 있다. 트랜지스터(312)는, 그 게이트 전극이 트랜지 스터(302)의 게이트 전극에 접속되어 있다. 또한, 트랜지스터(312)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(328)에, 다른쪽이 배선(318)에, 각각 접속되어 있다. 트랜지스터(313)는, 그 게이트 전극이 배선(317)에 접속되어 있다. 또한, 트랜지스터(313)는, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(301)의 소스 단 자 및 드레인 단자의 다른쪽에, 다른쪽이 트랜지스터(314)의 게이트 전극에, 각각 접속되어 있다. 트랜지스터 (314)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(325)에, 다른쪽이 배선(327)에, 각각 접속되어 있다. 트 랜지스터(315)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(327)에, 다른쪽이 배선(326)에, 각각 접속되어 있다. 용량 소자(316)는, 한쪽의 전극이 트랜지스터(302)의 게이트 전극에, 다른쪽의 전극이 배선(318)에, 각 각 접속되어 있다.

- [0060] 또한, 도 4에서는, 출력 측의 트랜지스터(315)의 소스 단자 및 드레인 단자의 다른쪽이 배선(326)에 접속되어 있지만, 본 발명은 이 구성으로 한정되지 않는다. 출력 측의 트랜지스터(315)의 소스 단자 및 드레인 단자의 다른쪽이, 배선(318)에 접속되어 있어도 좋다. 단, 출력 측의 트랜지스터(315)는 사이즈가 크기 때문에, 트랜지스터(315)가 노멀리 온이면, 드레인 전류가, 다른 트랜지스터에 비해 크다. 따라서, 트랜지스터(315)가 노멀리 온이면, 트랜지스터(315)의 소스 단자 및 드레인 단자의 다른쪽이 배선(318)에 접속되어 있는 경우, 배선 (318)의 전위가 상기 드레인 전류에 의해 상승하고, 출력 전위인 전위(GOUT1)의 진폭이 작아져 버리는 현상이 생기기 쉽다. 그러나, 도 4에 도시하는 바와 같이, 출력 측의 트랜지스터(315)의 소스 단자 및 드레인 단자의 다른쪽이 배선(318)이 아니라 배선(326)에 접속되어 있으면, 트랜지스터(315)가 노멀리 온이었다고 하고, 그것에 의해, 배선(326)의 전위가 상승하였다고 해도, 상기 트랜지스터의 게이트 전국에 전위를 공급하기 위한 배선 (318)의 전위는, 배선(326)의 전위의 상승과는 관계없다. 따라서, 트랜지스터(315)의 드레인 전류에 의해 배선 (326)의 전위가 상승하면, 트랜지스터(315)의 게이트 전압이 음의 값을 갖는 임계값 전압에 근접하기 때문에, 트랜지스터(315)가 노멀리 온이라도 오프로 할 수 있다.

- [0061] 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(309), 트랜지스터(312), 및 트랜지스터 (315)의 적어도 하나와, 트랜지스터(302)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 도전막을 개재 하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(309), 트랜지스터(312), 트랜지스터(315), 및 트랜지스터(302)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다.

- [0062] 또한, 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 2개의 도전막이, 상기 2개의 도전막과 상이한 하나의 도전막을 개재하여, 전기적으로 접속되어 있는 구성으로 한정되지 않는다. 예를 들면, 게이트 전극으로서 기능하는 2개의 도전막이, 상기 2개의 도전막과 상이한 복수의 도전막을 개재하여 전기적으로 접속되어 있어도 좋다. 이 경우, 상기 복수의 도전막의 적어도 하나가, 게이트 전극으로서 기능하는 2개의 도전막과 상이한 층에 형성되어 있는 것으로 한다.

- [0063] 또한, 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 복수의 도전막과, 상기 복수의 도전막을 전기적으로 접속하기 위한 도전막 사이에, 절연막이 형성되어 있는 구성으로 한정되지 않는다. 본 발명의 일 형태에서는, 게이트 전극으로서 기능하는 복수의 도전막과, 상기 복수의 도전막을 전기적으로 접속하기 위한 도전막이, 상이한 제작 공정에 있어서 제작되어 있으면 좋다. 따라서, 게이트 전극으로서 기능하는 복수의 도전막과, 상

기 복수의 도전막을 전기적으로 접속하기 위한 도전막 사이에, 절연막이 형성되어 있지 않아도 좋다.

- [0064] (실시형태 2)

- [0065] 본 실시형태에서는, 도 4에 도시한 펄스 발생 회로(300)를 복수단 접속시킴으로써 구성되는 시프트 레지스터에 관해서 설명한다.

- [0066] 도 5에 도시하는 시프트 레지스터는, 펄스 발생 회로(300\_1) 내지 펄스 발생 회로(300\_y)(y는 자연수)와, 더미의 펄스 발생 회로(300\_d)를 가진다. 펄스 발생 회로(300\_1) 내지 펄스 발생 회로(300\_y)는, 각각, 도 4에 도시한 펄스 발생 회로(300)와 동일한 구성을 가진다. 또한, 펄스 발생 회로(300\_d)는, 전위(RIN)가 주어지는 배선(322)과 접속되어 있지 않은 점, 및, 트랜지스터(305)를 갖지 않는 점에 있어서, 도 4에 도시한 펄스 발생 회로(300)와 구성이 상이하다.

- [0067] 또한, 도 5에 도시한 시프트 레지스터에 있어서, 펄스 발생 회로(300\_j)(j는, y 이하의 자연수)에 접속된 배선 (319) 내지 배선(325), 배선(327) 내지 배선(329)의 위치를, 도 7에 모식적으로 도시한다. 도 5와 도 7로부터 알 수 있는 바와 같이, 펄스 발생 회로(300\_j)의 배선(319)에는, 전단의 펄스 발생 회로(300\_j-1)의 배선(329)으로부터 출력된 전위(SROUTj-1)가, 전위(LIN)로서 주어진다. 단, 1단째의 펄스 발생 회로(300\_1)의 배선(319)에는, 스타트 펄스 신호(GSP)의 전위가 주어지는 구성으로 한다.

- [0068] 또한, 펄스 발생 회로(300\_j)에 접속된 배선(322)에는, 1개 후단의 펄스 발생 회로(300\_j+1)의 배선(329)으로부터 출력된 전위(SROUTj+1)가, 전위(RIN)로서 주어진다. 단, y단째의 펄스 발생 회로(300\_y)의 배선(322)에는, 펄스 발생 회로(300\_d)의 배선(329)으로부터 출력된 SROUTd가, 전위(RIN)로서 주어지는 구성으로 한다.

- [0069] 배선(321) 및 배선(323)에는, 클록 신호(GCK1) 내지 클록 신호(GCK4) 중, 어느 2개의 클록 신호의 전위가, 각각 주어진다. 구체적으로, 펄스 발생 회로(300\_4m+1)에서는, 클록 신호(GCK1)의 전위가, 전위(CLK1)로서 배선 (323)에 주어지고, 클록 신호(GCK2)의 전위가, 전위(CLK2)로서 배선(321)에 주어진다. 펄스 발생 회로 (300\_4m+2)에서는, 클록 신호(GCK2)의 전위가, 전위(CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK3)의 전위가, 전위(CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK3)의 전위가, 전위 (CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK4)의 전위가, 전위(CLK2)로서 배선(321)에 주어진다. 펄스 발생 회로(300\_4m+3)에서는, 클록 신호(GCK3)의 전위가, 전위 (CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK4)의 전위가, 전위(CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK1)의 전위가, 전위(CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK1)의 전위가, 전위(CLK1)로서 배선(323)에 주어지고, 클록 신호(GCK2)의 전위가, 전위(CLK2)로서 배선(321)에 주어진다. 단, m은, 펄스 발생 회로(300)의 총수가 y인 것을 충족시키는, 임의의 정수로 한다.

- [0070] 또한, 배선(324) 및 배선(325)에는, 펄스폭 제어 신호(PWCA) 내지 펄스폭 제어 신호(PWCD)와, 펄스폭 제어 신호 (PWCa) 내지 펄스폭 제어 신호(PWCd) 중, 어느 2개의 펄스폭 제어 신호의 전위가, 각각 주어진다. 구체적으로, 펄스 발생 회로(300\_4m+1)에서는, 펄스폭 제어 신호(PWCa)의 전위가, 전위(PWC1)로서 배선(325)에 주어지고, 펄스폭 제어 신호(PWCA)의 전위가, 전위(PWC2)로서 배선(324)에 주어진다. 펄스 발생 회로(300\_4m+2)에서는, 펄스폭 제어 신호(PWCb)의 전위가, 전위(PWC1)로서 배선(325)에 주어지고, 펄스폭 제어 신호(PWCB)의 전위가, 전위(PWC2)로서 배선(324)에 주어진다. 펄스 발생 회로(300\_4m+3)에서는, 펄스폭 제어 신호(PWCc)의 전위가, 전위(PWC1)로서 배선(325)에 주어지고, 펄스 발생 회로(300\_4m+4)에서는, 펄스폭 제어 신호(PWCC)의 전위가, 전위(PWC1)로서 배선(325)에 주어지고, 펄스폭 제어 신호(PWCC)의 전위가, 전위(PWC1)로서 배선(325)에 주어지고, 펄스폭 제어 신호(PWC0)의 전위가, 전위(PWC2)로서 배선(325)에 주어지고, 펄스폭 제어 신호(PWC0)의 전위가, 전위(PWC2)로서 배선(324)에 주어진다. 펄스 발생 회로(300\_d)에서는, 펄스폭 제어 신호(PWCa)의 전위가, 전위(PWC1)로서 배선(325)에 주어지고, 펄스폭 제어 신호(PWCA)의 전위가, 전위(PWC2)로서 배선(324)에 주어진다.

- [0071] 펼스 발생 회로(300\_j)에 접속된 배선(327)의 전위(GOUT1)는, 주사선(GLaj)에 주어진다.

- [0072] 펄스 발생 회로(300\_j)에 접속된 배선(329)의 전위(SROUT\_j)는, 인버터(351\_j)에 의해 그 극성이 반전되고, 주사선(GLbj)에 주어진다. 구체적으로, 인버터(351\_4m+1)는, 클록 신호(GCK2)가 입력되어 있고, 클록 신호(GCK2)의 전위가 로우 레벨일 때에, 전위(SROUT\_4m+1)의 극성을 반전시켜, 주사선(GLb4m+1)에 준다. 인버터(351\_4m+2)는, 클록 신호(GCK3)가 입력되어 있고, 클록 신호(GCK3)의 전위가 로우 레벨일 때에, 전위(SROUT\_4m+2)의 극성을 반전시켜, 주사선(GLb4m+2)에 준다. 인버터(351\_4m+3)는, 클록 신호(GCK4)가 입력되어 있고, 클록 신호(GCK4)의 전위가 로우 레벨일 때에, 전위(SROUT\_4m+3)의 극성을 반전시켜, 주사선(GLb4m+3)에 준다. 인버터(351\_4m+4)는, 클록 신호(GCK1)가 입력되어 있고, 클록 신호(GCK1)의 전위가 로우 레벨일 때에, 전위(SROUT\_4m+4)의 극성을 반전시켜, 주사선(GLb4m+4)에 준다. 인버터(351\_d)는, 클록 신호(GCK2)가 입력되

어 있고, 클록 신호(GCK2)의 전위가 로우 레벨일 때에, 전위(SROUT\_d)의 극성을 반전시켜, 주사선(GLbd)에 준다.

- [0073] 또한, 펄스 발생 회로(300\_j)에 접속된 배선(328)의 전위(GOUT2)는, 인버터(350\_j)에 의해 그 극성이 반전되어, 주사선(GLcj)에 주어진다. 구체적으로, 인버터(350\_4m+1)는, 클록 신호(GCK2)가 입력되어 있고, 클록 신호(GCK2)의 전위가 로우 레벨일 때에, 전위(GOUT2)의 극성을 반전시켜, 주사선(GLc4m+1)에 준다. 인버터(350\_4m+2)는, 클록 신호(GCK3)가 입력되어 있고, 클록 신호(GCK3)의 전위가 로우 레벨일 때에, 전위(GOUT2)의 극성을 반전시켜, 주사선(GLc4m+2)에 준다. 인버터(350\_4m+3)는, 클록 신호(GCK4)가 입력되어 있고, 클록 신호(GCK4)의 전위가 로우 레벨일 때에, 전위(GOUT2)의 극성을 반전시켜, 주사선(GLc4m+3)에 준다. 인버터(350\_4m+4)는, 클록 신호(GCK1)가 입력되어 있고, 클록 신호(GCK1)의 전위가 로우 레벨일 때에, 전위(GOUT2)의 극성을 반전시켜, 주사선(GLc4m+4)에 준다. 인버터(350\_d)는, 클록 신호(GCK2)가 입력되어 있고, 클록 신호(GCK2)의 전위가 로우 레벨일 때에, 전위(GOUT2)의 극성을 반전시켜, 주사선(GLcd)에 준다.

- [0074] 이어서, 도 4에 도시한 펄스 발생 회로(300)의 동작에 관해서, 도 6에 도시한 타이밍 차트를 사용하여 설명한다. 또한, 모든 기간을 통해, 전위(INRES)는 로우 레벨인 것으로 한다.

- [0075] 도 6에 도시하는 바와 같이, 기간(t1)에 있어서, 배선(323)에 주어지는 전위(CLK1)는 로우 레벨, 배선(321)에 주어지는 전위(CLK2)는 로우 레벨, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위는 로우 레벨, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위는 로우 레벨, 배선(319)에 주어지는 전위(LIN)는 하이 레벨, 배선(322)에 주어지는 전위(RIN)는 로우 레벨이 된다.

- [0076] 따라서, 기간(t1)에 있어서, 필스 발생 회로(300)에서는, 배선(325)에 주어지는 필스폭 제어 신호(PWC1)의 전위 (로우 레벨)가, 전위(GOUT1)로서 배선(327)에 주어진다. 또한, 배선(324)에 주어지는 필스폭 제어 신호(PWC2)의 전위(로우 레벨)가, 전위(GOUT2)로서 배선(328)에 주어진다. 또한, 배선(323)에 주어지는 전위(CLK1)(로우 레벨)가, 전위(SROUT)로서 배선(329)에 주어진다.

- [0077] 이어서, 도 6에 도시하는 바와 같이, 기간(t2)에 있어서, 배선(323)에 주어지는 전위(CLK1)는 하이 레벨, 배선 (321)에 주어지는 전위(CLK2)는 로우 레벨, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위는 로우 레벨 로부터 변화되어 하이 레벨, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위는 로우 레벨, 배선(319)에 주어지는 전위(LIN)는 하이 레벨, 배선(322)에 주어지는 전위(RIN)는 로우 레벨이 된다.

- [0078] 따라서, 기간(t2)에 있어서, 펄스 발생 회로(300)에서는, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위 (로우 레벨로부터 변화되어 하이 레벨)가, 전위(GOUT1)로서 배선(327)에 주어진다. 또한, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위(로우 레벨)가, 전위(GOUT2)로서 배선(328)에 주어진다. 또한, 배선(323)에 주어지는 전위(CLK1)(하이 레벨)가, 전위(SROUT)로서 배선(329)에 주어진다.

- [0079] 이어서, 도 6에 도시하는 바와 같이, 기간(t3)에 있어서, 배선(323)에 주어지는 전위(CLK1)는 하이 레벨, 배선 (321)에 주어지는 전위(CLK2)는 로우 레벨, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위는 하이 레벨, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위는 하이 레벨, 배선(319)에 주어지는 전위(LIN)는 하이 레벨로부터 변화되어 로우 레벨, 배선(322)에 주어지는 전위(RIN)는 로우 레벨이 된다.

- [0080] 따라서, 기간(t3)에 있어서, 펄스 발생 회로(300)에서는, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위 (하이 레벨)가, 전위(GOUT1)로서 배선(327)에 주어진다. 또한, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위(하이 레벨)가, 전위(GOUT2)로서 배선(328)에 주어진다. 또한, 배선(323)에 주어지는 전위(CLK1)(하이 레벨)가, 전위(SROUT)로서 배선(329)에 주어진다.

- [0081] 이어서, 도 6에 도시하는 바와 같이, 기간(t4)에 있어서, 배선(323)에 주어지는 전위(CLK1)는 하이 레벨, 배선 (321)에 주어지는 전위(CLK2)는 로우 레벨, 배선(325)에 주어지는 펼스폭 제어 신호(PWC1)의 전위는 하이 레벨 로부터 변화되어 로우 레벨, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위는 하이 레벨, 배선(319)에 주어지는 전위(LIN)는 로우 레벨, 배선(322)에 주어지는 전위(RIN)는 로우 레벨이 된다.

- [0082] 따라서, 기간(t4)에 있어서, 펄스 발생 회로(300)에서는, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위 (하이 레벨로부터 변화되어 로우 레벨)가, 전위(GOUT1)로서 배선(327)에 주어진다. 또한, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위(하이 레벨)가, 전위(GOUT2)로서 배선(328)에 주어진다. 또한, 배선(323)에 주어지는 전위(CLK1)(하이 레벨)가, 전위(SROUT)로서 배선(329)에 주어진다.

- [0083] 이어서, 도 6에 도시하는 바와 같이, 기간(t5)에 있어서, 배선(323)에 주어지는 전위(CLK1)는 로우 레벨, 배선

(321)에 주어지는 전위(CLK2)는 하이 레벨, 배선(325)에 주어지는 펄스폭 제어 신호(PWC1)의 전위는 로우 레벨, 배선(324)에 주어지는 펄스폭 제어 신호(PWC2)의 전위는 로우 레벨, 배선(319)에 주어지는 전위(LIN)는 로우 레벨, 배선(322)에 주어지는 전위(RIN)는 하이 레벨이 된다.

- [0084] 따라서, 기간(t5)에 있어서, 펼스 발생 회로(300)에서는, 배선(326)에 주어지는 전위(VEE)(로우 레벨)가, 전위 (GOUT1)로서 배선(327)에 주어진다. 또한, 배선(318)에 주어지는 전위(VSS)(로우 레벨)가, 전위(GOUT2)로서 배선(328)에 주어진다. 또한, 배선(318)에 주어지는 전위(VSS)(로우 레벨)가, 전위(SROUT)로서 배선(329)에 주어 진다.

- [0085] 본 발명의 일 형태에서는, 실시형태 1에서 설명한 바와 같이, 출력 측의 트랜지스터에 상당하는 트랜지스터 (309), 트랜지스터(312), 및 트랜지스터(315)의 적어도 하나와, 트랜지스터(302)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 도전막을 개재하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(309), 트랜지스터(312), 트랜지스터(315), 및 트랜지스터(302)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다. 따라서, 상기 시프트 레지스터를 사용한, 본 발명의 일 형태에 따르는 반도체 장치는, 정전 파괴에 의한 제조 수율의 저하가 일어나기 어렵다.

- [0086] 본 실시형태는, 다른 실시형태와 적절히 조합하여 실시하는 것이 가능하다.

- [0087] (실시형태 3)

- [0088] 본 발명의 일 형태에 따르는 반도체 장치가 갖는, 펄스 발생 회로의 구성예에 관해서 설명한다.

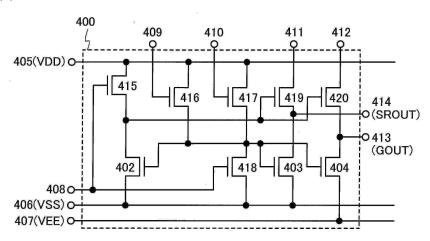

- [0089] 도 8a에 도시하는 펄스 발생 회로(400)는, 트랜지스터(402) 내지 트랜지스터(404)와, 트랜지스터(415) 내지 트랜지스터(420)를 가진다. 상기 펄스 발생 회로(400)를 복수단 접속시킴으로써, 시프트 레지스터를 구성할 수 있다.

- [0090] 트랜지스터(402)는, 그 게이트 전극이 트랜지스터(403) 및 트랜지스터(404)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(406)에, 다른쪽이 트랜지스터(420)의 게이트 전극에 접속되어 있다. 트랜지스터(403)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(406)에 접속되고, 다른쪽이 배선(414)에 접속되어 있다. 트랜지스터(404)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(407)에 접속되고, 다른쪽이 배선(413)에 접속되어 있다.

- [0091] 또한, 트랜지스터(415)는 그 게이트 전극이 배선(408)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(420)의 게이트 전극에 접속되고, 다른쪽이 배선(405)에 접속되어 있다. 트랜지스터(416)는, 그 게이트 전극이 배선(409)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(402), 트랜지스터(403), 및 트랜지스터(404)의 게이트 전극에 접속되고, 다른쪽이 배선(405)에 접속되어 있다. 트랜지스터(417)는, 그 게이트 전극이 배선(410)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(402), 트랜지스터(403), 및 트랜지스터(404)의 게이트 전극에 접속되고, 다른쪽이 배선(405)에 접속되어 있다. 트랜지스터(418)는, 그 게이트 전극이 배선(408)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(406)에 접속되고, 다른쪽이 트랜지스터(402), 트랜지스터(403), 및 트랜지스터(404)의 게이트 전극에 접속되어 있다. 트랜지스터(419)는, 그 게이트 전극이 트랜지스터(420)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(414)에 접속되고, 다른쪽이 배선(411)에 접속되고, 다른쪽이 배선(412)에 접속되어 있다.

- [0092] 트랜지스터(402) 내지 트랜지스터(404)와, 트랜지스터(415) 내지 트랜지스터(420)가 n채널형인 경우, 구체적으로, 배선(405)에는 전위(VDD)가 주어지고, 배선(406)에는 전위(VSS)가 주어지고, 배선(407)에는 전위(VEE)가 주어진다. 또한, 배선(408) 내지 배선(412)에는, 클록 신호 등의 각종 신호의 전위가 주어진다. 그리고, 배선(413)으로부터 전위(GOUT)가, 배선(414)으로부터 전위(SROUT)가 출력된다.

- [0093] 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(403), 및 트랜지스터(404)의 적어도 하나와, 트랜지스터(402)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(403), 트랜지스터(404), 및 트랜지스터(402)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다. 따라서, 상기 필스 발생 회로(400)를 시프트 레지스터 등에 사용한, 본 발명의 일 형

태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0094] 또는, 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(420)와, 트랜지스터(419)는, 서로의 게이트 전국이, 상기 게이트 전국과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있어도 좋다. 상기 구성에 의해, 상기 펄스 발생 회로(400)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0095] 또한, 도 8a에서는, 출력 측의 트랜지스터(404)의 소스 단자 및 드레인 단자의 한쪽이 배선(407)에 접속되어 있지만, 본 발명은 이 구성으로 한정되지 않는다. 출력 측의 트랜지스터(404)의 소스 단자 및 드레인 단자의 한쪽이, 배선(406)에 접속되어 있어도 좋다. 단, 도 8a에 도시하는 바와 같이, 출력 측의 트랜지스터(404)의 소스 단자 및 드레인 단자의 한쪽이 배선(406)이 아니라 배선(407)에 접속되어 있으면, 트랜지스터(404)가 노멀리온이라도, 트랜지스터(404)를 오프로 해야 할 때에 오프로 할 수 있다.

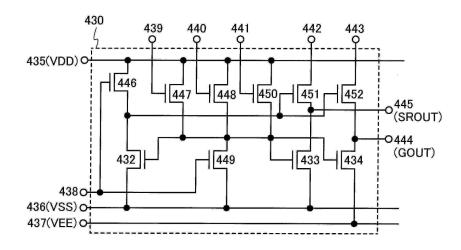

- [0096] 도 8b에 도시하는 펄스 발생 회로(430)는, 트랜지스터(432) 내지 트랜지스터(434)와, 트랜지스터(446) 내지 트랜지스터(452)를 가진다. 상기 펄스 발생 회로(430)를 복수단 접속시킴으로써, 시프트 레지스터를 구성할 수 있다.

- [0097] 트랜지스터(432)는, 그 게이트 전극이 트랜지스터(433) 및 트랜지스터(434)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(436)에 접속되고, 다른쪽이 트랜지스터(451) 및 트랜지스터(452)의 게이트 전극에 접속되어 있다. 트랜지스터(433)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(436)에 접속되고, 다른쪽이 배선(445)에 접속되어 있다. 트랜지스터(434)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(437)에 접속되고, 다른쪽이 배선(444)에 접속되어 있다.

- [0098] 또한, 트랜지스터(446)는, 그 게이트 전극이 배선(438)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(451) 및 트랜지스터(452)의 게이트 전극에 접속되고, 다른쪽이 배선(435)에 접속되어 있다. 트랜지스터(447)는, 그 게이트 전극이 배선(439)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(432), 트랜지스터(433), 및 트랜지스터(434)의 게이트 전극에 접속되고, 다른쪽이 배선(435)에 접속되어 있다. 트랜지스터(448)는, 그 게이트 전극이 배선(440)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(432), 트랜지스터(433), 및 트랜지스터(434)의 게이트 전극에 접속되고, 다른쪽이 배선(435)에 접속되어 있다. 트랜지스터(449)는, 그 게이트 전극이 배선(438)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(436)에 접속되고, 다른쪽이 트랜지스터(432), 트랜지스터(433), 및 트랜지스터(433), 및 트랜지스터(434)의 게이트 전극에 접속되어 있다. 트랜지스터(450)는, 그 게이트 전극이 배선(441)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(432), 트랜지스터(451)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(442)에 접속되어 있다. 트랜지스터(451)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(444)에 접속되고, 다른쪽이 배선(442)에 접속되어 있다. 트랜지스터(452)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(444)에 접속되고, 다른쪽이 배선(443)에 접속되어 있다.

- [0099] 트랜지스터(432) 내지 트랜지스터(434)와, 트랜지스터(446) 내지 트랜지스터(452)가 n채널형인 경우, 구체적으로, 배선(435)에는 전위(VDD)가 주어지고, 배선(436)에는 전위(VSS)가 주어지고, 배선(437)에는 전위(VEE)가 주어진다. 또한, 배선(438) 내지 배선(443)에는, 클록 신호 등의 각종 신호의 전위가 주어진다. 그리고, 배선(444)으로부터 전위(GOUT)가, 배선(445)으로부터 전위(SROUT)가 출력된다.

- [0100] 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(433), 및 트랜지스터(434)의 적어도 하나와, 트랜지스터(432)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(433), 트랜지스터(434), 및 트랜지스터(432)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다. 따라서, 상기 펄스 발생 회로(430)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0101] 또는, 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(452)와, 트랜지스터(451)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있어도좋다. 상기 구성에 의해, 상기 펼스 발생 회로(430)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0102] 또한, 도 8b에서는, 출력 측의 트랜지스터(434)의 소스 단자 및 드레인 단자의 한쪽이 배선(437)에 접속되어 있

지만, 본 발명은 이 구성으로 한정되지 않는다. 출력 측의 트랜지스터(434)의 소스 단자 및 드레인 단자의 한쪽이, 배선(436)에 접속되어 있어도 좋다. 단, 도 8b에 도시하는 바와 같이, 출력 측의 트랜지스터(434)의 소스 단자 및 드레인 단자의 한쪽이 배선(436)이 아니라 배선(437)에 접속되어 있으면, 트랜지스터(434)가 노멀리온이라도, 트랜지스터(434)를 오프로 해야 할 때에 오프로 할 수 있다.

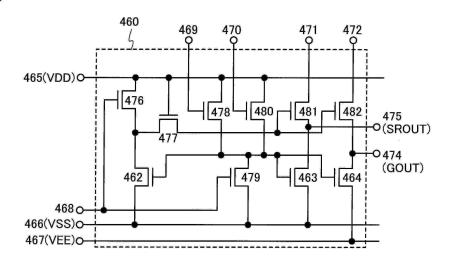

- [0103] 도 9a에 도시하는 펄스 발생 회로(460)는, 트랜지스터(462) 내지 트랜지스터(464)와, 트랜지스터(476) 내지 트랜지스터(482)를 가진다. 상기 펄스 발생 회로(460)를 복수단 접속시킴으로써, 시프트 레지스터를 구성할 수 있다.

- [0104] 트랜지스터(462)는, 그 게이트 전극이 트랜지스터(463) 및 트랜지스터(464)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(466)에 접속되고, 다른쪽이 트랜지스터(477)의 소스 단자 및 드레인 단자의 한쪽에 접속되어 있다. 트랜지스터(463)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(466)에 접속되고, 다른쪽이 배선(475)에 접속되어 있다. 트랜지스터(464)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(467)에 접속되고, 다른쪽이 배선(474)에 접속되어 있다.

- [0105] 또한, 트랜지스터(476)는, 그 게이트 전극이 배선(468)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(477)의 소스 단자 및 드레인 단자의 한쪽에 접속되고, 다른쪽이 배선(465)에 접속되어 있다. 트랜지스터(477)는, 그 게이트 전극이 배선(465)에 접속되고, 그 소스 단자 및 드레인 단자의 다른쪽이 트랜지스터 (481) 및 트랜지스터(482)의 게이트 전극에 접속되어 있다. 트랜지스터(478)는, 그 게이트 전극이 배선(469)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(462), 트랜지스터(463), 및 트랜지스터(464)의 게이트 전극에 접속되고, 다른쪽이 배선(465)에 접속되어 있다. 트랜지스터(479)는, 그 게이트 전극이 배선(468)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(466)에 접속되고, 다른쪽이 트랜지스터(462), 트랜지스터(463), 및 트랜지스터(464)의 게이트 전극에 접속되어 있다. 트랜지스터(480)는, 그 게이트 전극이 배선 (470)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(462), 트랜지스터(463), 및 트랜지스터(464)의 게이트 전극에 접속되고, 다른쪽이 배선(471)에 접속되어 있다. 트랜지스터(481)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(471)에 접속되어 있다. 트랜지스터(482)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(474)에 접속되고, 다른쪽이 배선(472)에 접속되어 있다.

- [0106] 트랜지스터(462) 내지 트랜지스터(464)와, 트랜지스터(476) 내지 트랜지스터(482)가 n채널형인 경우, 구체적으로, 배선(465)에는 전위(VDD)가 주어지고, 배선(466)에는 전위(VSS)가 주어지고, 배선(467)에는 전위(VEE)가 주어진다. 또한, 배선(468) 내지 배선(472)에는, 클록 신호 등의 각종 신호의 전위가 주어진다. 그리고, 배선(474)으로부터 전위(GOUT)가, 배선(475)으로부터 전위(SROUT)가 출력된다.

- [0107] 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(463), 및 트랜지스터(464)의 적어도 하나와, 트랜지스터(462)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(463), 트랜지스터(464), 및 트랜지스터(462)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다. 따라서, 상기 펄스 발생 회로(460)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0108] 또는, 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(482)와, 트랜지스터(481)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있어도 좋다. 상기 구성에 의해, 상기 펄스 발생 회로(460)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0109] 또한, 도 9a에서는, 출력 측의 트랜지스터(464)의 소스 단자 및 드레인 단자의 한쪽이 배선(467)에 접속되어 있지만, 본 발명은 이 구성으로 한정되지 않는다. 출력 측의 트랜지스터(464)의 소스 단자 및 드레인 단자의 한쪽이, 배선(466)에 접속되어 있어도 좋다. 단, 도 9a에 도시하는 바와 같이, 출력 측의 트랜지스터(464)의 소스 단자 및 드레인 단자의 한쪽이 배선(466)이 아니라 배선(467)에 접속되어 있으면, 트랜지스터(464)가 노멀리온이라도, 트랜지스터(464)를 오프로 해야 할 때에 오프로 할 수 있다.

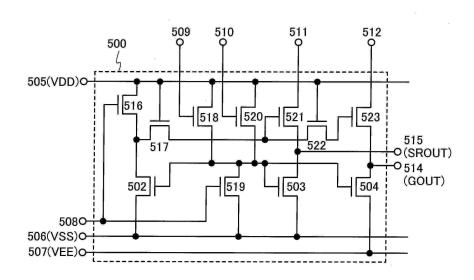

- [0110] 도 9b에 도시하는 펄스 발생 회로(500)는, 트랜지스터(502) 내지 트랜지스터(504)와, 트랜지스터(516) 내지 트랜지스터(523)를 가진다. 상기 펄스 발생 회로(500)를 복수단 접속시킴으로써, 시프트 레지스터를 구성할 수 있다.

- [0111] 트랜지스터(502)는, 그 게이트 전극이 트랜지스터(503) 및 트랜지스터(504)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(506)에 접속되고, 다른쪽이 트랜지스터(517)의 소스 단자 및 드레인 단자의 한쪽에 접속되어 있다. 트랜지스터(503)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(506)에 접속되고, 다른쪽이 배선(515)에 접속되어 있다. 트랜지스터(504)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(507)에 접속되고, 다른쪽이 배선(514)에 접속되어 있다.

- [0112] 또한, 트랜지스터(516)는, 그 게이트 전극이 배선(508)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(517)의 소스 단자 및 드레인 단자의 한쪽에 접속되고, 다른쪽이 배선(505)에 접속되어 있다. 트랜지스터(517)는, 그 게이트 전극이 배선(505)에 접속되고, 그 소스 단자 및 드레인 단자의 다른쪽이 트랜지스터(521)의 게이트 전극에 접속되어 있다. 트랜지스터(518)는, 그 게이트 전극이 배선(509)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(502), 트랜지스터(503), 및 트랜지스터(504)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 비선(506)에 접속되고, 다른쪽이 트랜지스터(502), 트랜지스터(519)는, 그 게이트 전극이 배선(508)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(506)에 접속되고, 다른쪽이 트랜지스터(502), 트랜지스터(503), 및 트랜지스터(504)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(502), 트랜지스터(503), 및 트랜지스터(504)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(515)에 접속되고, 다른쪽이 배선(511)에 접속되어 있다. 트랜지스터(521)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(515)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(521)의 게이트 전극에 접속되고, 그 다른쪽이 배선(514)에 접속되고, 다른쪽이 배선(512)에 접속되어 있다. 트랜지스터(523)는, 그 소스 단자 및 드레인 단자의 한쪽이 백건(514)에 접속되고, 다른쪽이 배선(512)에 접속되어 있다.

- [0113] 트랜지스터(502) 내지 트랜지스터(504)와, 트랜지스터(516) 내지 트랜지스터(523)가 n채널형인 경우, 구체적으로, 배선(505)에는 전위(VDD)가 주어지고, 배선(506)에는 전위(VSS)가 주어지고, 배선(507)에는 전위(VEE)가 주어진다. 또한, 배선(508) 내지 배선(512)에는, 클록 신호 등의 각종 신호의 전위가 주어진다. 그리고, 배선(514)으로부터 전위(GOUT)가, 배선(515)으로부터 전위(SROUT)가 출력된다.

- [0114] 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(503), 및 트랜지스터(504)의 적어도 하나와, 트랜지스터(502)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(503), 트랜지스터(504), 및 트랜지스터(502)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다. 따라서, 상기 펄스 발생 회로(500)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0115] 또한, 도 9b에서는, 출력 측의 트랜지스터(504)의 소스 단자 및 드레인 단자의 한쪽이 배선(507)에 접속되어 있지만, 본 발명은 이 구성으로 한정되지 않는다. 출력 측의 트랜지스터(504)의 소스 단자 및 드레인 단자의 한쪽이, 배선(506)에 접속되어 있어도 좋다. 단, 도 9b에 도시하는 바와 같이, 출력 측의 트랜지스터(504)의 소스 단자 및 드레인 단자의 한쪽이 배선(506)이 아니라 배선(507)에 접속되어 있으면, 트랜지스터(504)가 노멀리온이라도, 트랜지스터(504)를 오프로 해야 할 때에 오프로 할 수 있다.

- [0116] 도 10에 도시하는 펄스 발생 회로(530)는, 트랜지스터(532) 내지 트랜지스터(534)와, 트랜지스터(546) 내지 트랜지스터(553)를 가진다. 상기 펄스 발생 회로(530)를 복수단 접속시킴으로써, 시프트 레지스터를 구성할 수 있다.

- [0117] 트랜지스터(532)는, 그 게이트 전극이 트랜지스터(533) 및 트랜지스터(534)의 게이트 전극에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(536)에 접속되고, 다른쪽이 트랜지스터(552)의 소스 단자 및 드레인 단자의 한쪽에 접속되어 있다. 트랜지스터(533)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(536)에 접속되고, 다른쪽이 배선(545)에 접속되어 있다. 트랜지스터(534)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(537)에 접속되고, 다른쪽이 배선(544)에 접속되어 있다.

- [0118] 또한, 트랜지스터(546)는, 그 게이트 전극이 배선(538)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(532)의 소스 단자 및 드레인 단자의 한쪽에 접속되고, 다른쪽이 배선(535)에 접속되어 있다. 트랜지스터(547)는, 그 게이트 전극이 배선(539)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(532), 트랜지스터(533), 및 트랜지스터(534)의 게이트 전극에 접속되고, 다른쪽이 배선(535)에 접속되어 있다. 트랜지스터(548)는, 그 게이트 전극이 배선(540)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스

터(532), 트랜지스터(533), 및 트랜지스터(534)의 게이트 전극에 접속되고, 다른쪽이 배선(535)에 접속되어 있다. 트랜지스터(549)는, 그 게이트 전극이 배선(538)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 배선(536)에 접속되고, 다른쪽이 트랜지스터(532), 트랜지스터(533), 및 트랜지스터(534)의 게이트 전극에 접속되어 있다. 트랜지스터(550)는, 그 게이트 전극이 배선(535)에 접속되고, 그 소스 단자 및 드레인 단자의 한쪽이 트랜지스터(552)의 소스 단자 및 드레인 단자의 한쪽에 접속되고, 그 다른쪽이 트랜지스터(551)의 게이트 전극에 접속되어 있다. 트랜지스터(551)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(545)에 접속되고, 다른쪽이 배선(541)에 접속되어 있다. 트랜지스터(552)는, 그 게이트 전극에 배선(535)에 접속되고, 그 소스 단자 및 드레인 단자의 다른쪽이 트랜지스터(553)의 게이트 전극에 접속되어 있다. 트랜지스터(553)는, 그 소스 단자 및 드레인 단자의 다른쪽이 트랜지스터(553)의 게이트 전극에 접속되어 있다. 트랜지스터(553)는, 그 소스 단자 및 드레인 단자의 한쪽이 배선(544)에 접속되고, 다른쪽이 배선(542)에 접속되어 있다.

- [0119] 트랜지스터(532) 내지 트랜지스터(534)와, 트랜지스터(546) 내지 트랜지스터(553)가 n채널형인 경우, 구체적으로, 배선(535)에는 전위(VDD)가 주어지고, 배선(536)에는 전위(VSS)가 주어지고, 배선(537)에는 전위(VEE)가 주어진다. 또한, 배선(538) 내지 배선(542)에는, 클록 신호 등의 각종 신호의 전위가 주어진다. 그리고, 배선(544)으로부터 전위(GOUT)가, 배선(545)으로부터 전위(SROUT)가 출력된다.

- [0120] 본 발명의 일 형태에서는, 출력 측의 트랜지스터에 상당하는 트랜지스터(533), 및 트랜지스터(534)의 적어도 하나와, 트랜지스터(532)는, 서로의 게이트 전극이, 상기 게이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있다. 상기 구성에 의해, 트랜지스터(533), 트랜지스터(534), 및 트랜지스터(532)의 모든 게이트 전극이 하나의 도전막으로 구성되어 있는 경우에 비해, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있다. 따라서, 게이트 전극으로서 기능하는 도전막의, 안테나 효과에 의한 정전 파괴를, 일어나기 어렵게 할 수 있다. 따라서, 상기 펄스 발생 회로(530)를 시프트 레지스터 등에 사용한, 본 발명의 일 형태에 따르는 반도체 장치의, 정전 파괴에 의한 제조 수율의 저하를 일어나기 어렵게 할 수 있다.

- [0121] 또한, 도 10에서는, 출력 측의 트랜지스터(534)의 소스 단자 및 드레인 단자의 한쪽이 배선(537)에 접속되어 있지만, 본 발명은 이 구성으로 한정되지 않는다. 출력 측의 트랜지스터(534)의 소스 단자 및 드레인 단자의 한쪽이, 배선(536)에 접속되어 있어도 좋다. 단, 도 10에 도시하는 바와 같이, 출력 측의 트랜지스터(534)의 소스 단자 및 드레인 단자의 한쪽이 배선(536)이 아니라 배선(537)에 접속되어 있으면, 트랜지스터(534)가 노멀리온이라도, 트랜지스터(534)를 오프로 해야 할 때에 오프로 할 수 있다.

- [0122] 본 실시형태는, 다른 실시형태와 적절히 조합하여 실시하는 것이 가능하다.

- [0123] (실시형태 4)

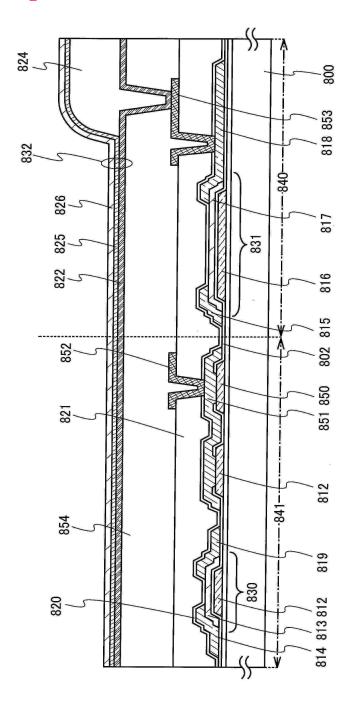

- [0124] OLED를 사용한 발광 장치를 예로 들어, 본 발명의 일 형태에 따르는 반도체 표시 장치의, 화소와 구동 회로의 단면 구조에 관해서, 도 11을 사용하여 설명한다. 도 11에, 화소(840)와 구동 회로(841)의 단면도를 일례로서 도시한다.

- [0125] 도 11에 있어서, 화소(840)는, 발광 소자(832)와, 발광 소자(832)로의 전류의 공급을 제어하는 트랜지스터(83 1)를 가진다. 화소(840)는, 상기 발광 소자(832) 및 트랜지스터(831) 외에, 화상 신호의 화소(840)로의 입력을 제어하는 트랜지스터나, 화상 신호의 전위를 유지하는 용량 소자 등, 각종 반도체 소자를 갖고 있어도 좋다.

- [0126] 또한, 도 11에 있어서, 구동 회로(841)는 트랜지스터(830)를 가진다. 구체적으로 트랜지스터(830)는, 구동 회로(841)의 일부에 상당하는 시프트 레지스터가 갖는, 출력 측의 트랜지스터에 상당한다. 구동 회로(841)는, 상기 트랜지스터(830) 외에, 트랜지스터나 용량 소자 등의 각종 반도체 소자를 갖고 있어도 좋다.

- [0127] 트랜지스터(831)는, 절연 표면을 갖는 기판(800) 위에, 게이트 전국으로서 기능하는 도전막(816)과, 도전막 (816) 위의 게이트 절연막(802)과, 도전막(816)과 중첩되는 위치에 있어서 게이트 절연막(802) 위에 형성된 반도체막(817)과, 소스 단자 또는 드레인 단자로서 기능하고, 반도체막(817) 위에 위치하는 도전막(815) 및 도전막(818)을 가진다. 도전막(816)은 주사선으로서도 기능한다.

- [0128] 트랜지스터(830)는, 절연 표면을 갖는 기판(800) 위에, 게이트 전극으로서 기능하는 도전막(812)과, 도전막(812) 위의 게이트 절연막(802)과, 도전막(812)과 중첩되는 위치에 있어서 게이트 절연막(802) 위에 형성된 반도체막(813)과, 소스 단자 또는 드레인 단자로서 기능하고, 반도체막(813) 위에 위치하는 도전막(814) 및 도전막(819)을 가진다.

- [0129] 또한, 절연 표면을 갖는 기판(800) 위에 형성된 도전막(850)은, 트랜지스터(830)와는 상이한 트랜지스터의 게이 트 전극으로서 기능한다. 그리고, 도전막(812) 및 도전막(850)은, 도전막(812) 및 도전막(850) 위의 게이트 절

연막(802)에 형성된 개구부를 개재하여, 게이트 절연막(802) 위의 도전막(851)에 접속되어 있다.

- [0130] 또한, 도전막(814), 도전막(815), 도전막(818), 도전막(819), 도전막(851) 위에는, 절연막(820) 및 절연막(821)이, 순차적으로 적충되도록 형성되어 있다. 그리고, 절연막(821) 위에는, 도전막(852) 및 도전막(853)이 형성되어 있다. 도전막(852) 및 도전막(853)은, 절연막(820) 및 절연막(821)에 형성된 개구부를 개재하여, 도전막(851) 및 도전막(818)에, 각각 접속되어 있다.

- [0131] 또한, 도전막(852) 및 도전막(853) 위에는 절연막(854)이 형성되어 있다. 그리고, 절연막(854) 위에는, 양국으로서 기능하는 도전막(822)이 형성되어 있다. 도전막(822)은, 절연막(854)에 형성된 개구부를 개재하여, 도전막(853)에 접속되어 있다.

- [0132] 또한, 도전막(822)의 일부가 노출되는 개구부를 가진 절연막(824)이, 절연막(854) 위에 형성되어 있다. 도전막 (822)의 일부 및 절연막(854) 위에는, EL층(825)과, 음극으로서 기능하는 도전막(826)이, 순차적으로 적층되도 록 형성되어 있다. 도전막(822)과, EL층(825)과, 도전막(826)이 중첩되어 있는 영역이, 발광 소자(832)에 상당한다.

- [0133] 또한, 본 발명의 일 형태에서는, 트랜지스터(830) 및 트랜지스터(831)는, 비정질, 미결정, 다결정 또는 단결정 인, 실리콘 또는 게르마늄 등의 반도체가 반도체막에 사용되고 있어도 좋고, 산화물 반도체 등의 와이드 갭 반도체가 반도체막에 사용되고 있어도 좋다.

- [0134] 트랜지스터(830) 및 트랜지스터(831)의 반도체막에, 비정질, 미결정, 다결정 또는 단결정인, 실리콘 또는 게르마늄 등의 반도체가 사용되는 경우, 1 도전성을 부여하는 불순물 원소를 상기 반도체막에 첨가하고, 소스 영역 또는 드레인 영역으로서 기능하는 불순물 영역을 형성한다. 예를 들면, 인 또는 비소를 상기 반도체막에 첨가함으로써, n형의 도전성을 갖는 불순물 영역을 형성할 수 있다. 또한, 예를 들면, 붕소를 상기 반도체막에 첨가함으로써, p형의 도전성을 갖는 불순물 영역을 형성할 수 있다.

- [0135] 트랜지스터(830) 및 트랜지스터(831)의 반도체막에, 산화물 반도체가 사용되는 경우, 도판트를 상기 반도체막에 첨가하고, 소스 영역 또는 드레인 영역으로서 기능하는 불순물 영역을 형성해도 좋다. 도판트의 첨가는, 이온 주입법을 사용할 수 있다. 도판트는, 예를 들면 헬륨, 아르곤, 크세논 등의 희가스나, 질소, 인, 비소, 안티몬 등의 15쪽 원소 등을 사용할 수 있다. 예를 들면, 질소를 도판트로서 사용한 경우, 불순물 영역 중의 질소 원자의 농도는,  $5 \times 10^{19}$ /cm² 이상  $1 \times 10^{22}$ /cm² 이하인 것이 바람직하다.

- [0136] 또한, 실리콘 반도체로서는, 플라즈마 CVD법 등의 기상 성장법 또는 스퍼터링법으로 제작된 비정질 실리콘, 비정질 실리콘을 레이저 어닐링 등의 처리에 의해 결정화시킨 다결정 실리콘, 단결정 실리콘 웨이퍼에 수소 이온 등을 주입하여 표층부를 박리한 단결정 실리콘 등을 사용할 수 있다.

- [0137] 또한, 산화물 반도체로서는, 적어도 인듐(In) 또는 아연(Zn)을 포함하는 것이 바람직하다. 특히 In과 Zn을 포함하는 것이 바람직하다. 또한, 상기 산화물을 사용한 트랜지스터의 전기적 특성의 불균일을 감소시키기 위한스테빌라이저로서, 이들 외에 갈륨(Ga)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 주석(Sn)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 알루미늄(Al)을 갖는 것이 바람직하다.

- [0138] 또한, 다른 스테빌라이저로서, 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨 (Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 툴륨(Tm), 이테르븀 (Yb), 루테튬(Lu) 중 어느 1종 또는 복수종을 포함하고 있어도 좋다.

- [0139] 예를 들면, 산화물 반도체로서, 산화인듐, 산화주석, 산화아연, 2원계 금속의 산화물인 In-Zn계 산화물, Sn-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, 3원계 금속의 산화물인 In-Ga-Zn계 산화물(IGZO라고도 표기한다), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, 4원계 금속의 산화물인 In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Hf-Al-Zn계 산화물을 사용할 수 있다. 또한, 상기 산화물 반도체는, 규소를 포함하고 있어도 좋다.

- [0140] 또한, 예를 들면, In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 포함하는 산화물이라는 의미이며, In과 Ga와 Zn의 비

율은 상관없다. 또한, In과 Ga와 Zn 이외의 금속 원소를 포함하고 있어도 좋다. In-Ga-Zn계 산화물은, 무전계일 때의 저항이 충분히 높고 오프 전류를 충분히 작게 하는 것이 가능하며, 또한, 이동도도 높기 때문에, 반도체 장치에 사용하는 반도체 재료로서는 적합하다.

- [0141] 예를 들면, In:Ga:Zn=1:1:1(=1/3:1/3:1/3) 또는 In:Ga:Zn=2:2:1(=2/5:2/5:1/5)의 원자비의 In-Ga-Zn계 산화물이나 그 조성 근방의 산화물을 사용할 수 있다. 또는, In:Sn:Zn=1:1:1(=1/3:1/3:1/3), In:Sn:Zn=2:1:3(=1/3:1/6:1/2) 또는 In:Sn:Zn=2:1:5(=1/4:1/8:5/8)의 원자비의 In-Sn-Zn계 산화물이나 그 조성 근방의 산화물을 사용하면 좋다.

- [0142] 예를 들면, In-Sn-Zn계 산화물에서는 비교적 용이하게 높은 이동도가 얻어진다. 그러나, In-Ga-Zn계 산화물에 서도, 벌크내 결함 밀도를 저감시킴으로써 이동도를 높일 수 있다.

- [0143] 또한, 전자 공여체(도너)가 되는 수분 또는 수소 등의 불순물이 저감되고, 또한 산소 결손이 저감됨으로써 고순도화된 산화물 반도체는, i형(진성 반도체) 또는 i형에 매우 가깝다. 이로 인해, 상기 산화물 반도체를 사용한트랜지스터는, 오프 전류가 현저하게 낮다고 하는 특성을 가진다. 또한, 산화물 반도체의 밴드 갭은, 2eV이상, 바람직하게는 2.5eV이상, 보다 바람직하게는 3eV이상이다. 수분 또는 수소 등의 불순물 농도가 충분히 저감되고, 또한 산소 결손이 저감됨으로써 고순도화된 산화물 반도체막을 사용함으로써, 트랜지스터의 오프 전류를 낮출 수 있다.

- [0144] 구체적으로, 고순도화된 산화물 반도체를 반도체막에 사용한 트랜지스터의 오프 전류가 낮은 것은, 여러 가지실험에 의해 증명할 수 있다. 예를 들면, 채널 폭이  $1 \times 10^6 \mu$ 에이고 채널 길이가  $10 \mu$ 에인 소자라도, 소스 단자와 드레인 단자간의 전압(드레인 전압)이 1 V에서 10 V의 범위에 있어서, 오프 전류가, 반도체 파라미터 애널라이저의 측정 한계 이하, 즉  $1 \times 10^{-13} A$  이하라는 특성을 얻을 수 있다. 이 경우, 오프 전류를 트랜지스터의 채널 폭으로 나눈 수치에 상당하는 오프 전류는,  $100 \times 10^{-12} A$  이하인 것을 알 수 있다. 또한, 용량 소자와 트랜지스터를 접속하여, 용량 소자에 유입 또는 용량 소자로부터 유출되는 전하를 상기 트랜지스터로 제어하는 회로를 사용하여, 오프 전류의 측정을 행하였다. 상기 측정에서는, 상기 트랜지스터에 고순도화된 산화물 반도체막을 채널형성 영역에 사용하여, 용량 소자의 단위 시간당 전하량의 추이로부터 상기 트랜지스터의 오프 전류를 측정하였다. 그 결과, 트랜지스터의 소스 단자와 드레인 단자간의 전압이 3 V인 경우에, 수십  $y A/\mu m$ 라는, 더욱 낮은 오프 전류가 얻어지는 것을 알 수 있었다. 따라서, 고순도화된 산화물 반도체막을 채널 형성 영역에 사용한 트랜지스터는, 오프 전류가, 결정성을 갖는 실리콘을 사용한 트랜지스터에 비해 현저하게 낮다.

- [0145] 또한, 특별히 언급하지 않는 한, 본 명세서에서 오프 전류란, n채널형 트랜지스터에 있어서는, 드레인 단자를 소스 단자와 게이트 전극보다도 높은 전위로 상태에 있어서, 소스 단자의 전위를 기준으로 했을 때의 게이트 전극의 전위가 0 이하일 때에, 소스 단자와 드레인 단자 사이에 흐르는 전류를 의미한다. 또는, 본 명세서에서 오프 전류란, p채널형 트랜지스터에 있어서는, 드레인 단자를 소스 단자와 게이트 전극보다도 낮은 전위로 한 상태에 있어서, 소스 단자의 전위를 기준으로 했을 때의 게이트 전극의 전위가 0 이상일 때에, 소스 단자와 드레인 단자 사이에 흐르는 전류를 의미한다.

- [0146] 또한, 예를 들면, 산화물 반도체막은, In(인듐), Ga(갈륨), 및 Zn(아연)을 포함하는 타깃을 사용한 스퍼터링법 에 의해 형성할 수 있다. In-Ga-Zn계 산화물 반도체막을 스퍼터링법으로 성막하는 경우, 바람직하게는, 원자수비가 In:Ga:Zn=1:1:1, 4:2:3, 3:1:2, 1:1:2, 2:1:3, 또는 3:1:4로 나타내는 In-Ga-Zn계 산화물의 타깃을 사용한다. 상기의 원자수비를 갖는 In-Ga-Zn계 산화물의 타깃을 사용하여 산화물 반도체막을 성막함으로써, 다결정 또는 CAAC(C Axis Aligned Crystal)이 형성되기 쉬워진다. 또한, In, Ga, 및 Zn을 포함하는 타깃의 상대 밀도는 90% 이상 100% 이하, 바람직하게는 95% 이상 100% 미만이다. 상대 밀도가 높은 타깃을 사용함으로써, 성막한 산화물 반도체막은 치밀한 막이 된다.

- [0147] 또한, 산화물 반도체로서 In-Zn계 산화물의 재료를 사용하는 경우, 사용하는 타깃 중의 금속 원소의 원자수비는, 원자수비로, In:Zn=50:1 내지 1:2(몰수비로 환산하면 In<sub>2</sub>O<sub>3</sub>:Zn0=25:1 내지 1:4), 바람직하게는 In:Zn=20:1 내지 1:1(몰수비로 환산하면 In<sub>2</sub>O<sub>3</sub>:Zn0=10:1 내지 1:2), 더욱 바람직하게는 In:Zn=1.5:1 내지 15:1 (몰수비로 환산하면 In<sub>2</sub>O<sub>3</sub>:Zn0=3:4 내지 15:2)로 한다. 예를 들면, In-Zn계 산화물인 산화물 반도체막의 형성에 사용하는 타깃은, 원자수비가 In:Zn:O=X:Y:Z일 때, Z>1.5X+Y로 한다. Zn의 비율을 상기 범위 내로 함으로써, 이동도의 향상을 실현할 수 있다.

- [0148] 또한, 산화물 반도체막은, 단결정, 다결정(폴리크리스탈이라고도 한다.) 또는 비정질 등의 상태를 취한다.

- [0149] 바람직하게는, 산화물 반도체막은, CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)막으로 한다.

- [0150] CAAC-OS막은, 완전한 단결정이 아니며, 완전한 비정질도 아니다. CAAC-OS 막은, 비정질상에 결정부 및 비정질부를 갖는 결정-비정질 혼상 구조의 산화물 반도체막이다. 또한, 상기 결정부는, 1변이 100nm 미만인 입방체내에 들어가는 크기인 경우가 많다. 또한, 투과형 전자 현미경(TEM: Transmission Electron Microscope)에 의한 관찰상에서는, CAAC-OS막에 포함되는 비정질부와 결정부의 경계는 명확하지는 없다. 또한, TEM에 의해 CAAC-OS막에는 입계(그레인 바운더리라고도 한다.)는 확인할 수 없다. 이로 인해, CAAC-OS막은, 입계에 기인하는 전자 이동도의 저하가 억제된다.

- [0151] CAAC-OS막에 포함되는 결정부는, c축이 CAAC-OS막의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향으로 정렬되고, 또한 ab면에 수직한 방향에서 볼 때 삼각 형상 또는 육각 형상의 원자 배열을 가지고, c축에 수직한 방향에서 볼 때 금속 원자가 충상 또는 금속 원자와 산소 원자가 충상으로 배열되어 있다. 또한, 상이한 결정부간에, 각각 a축 및 b축의 방향이 상이해도 좋다. 본 명세서에 있어서, 단순히 수직이라고 기재하는 경우, 85°이상 95°이하의 범위도 포함되는 것으로 한다. 또한, 단순히 평행이라고 기재하는 경우, -5°이상 5°이하의 범위도 포함되는 것으로 한다.

- [0152] 또한, CAAC-OS막에 있어서, 결정부의 분포가 일정하지 않아도 좋다. 예를 들면, CAAC-OS막의 형성 과정에 있어 서, 산화물 반도체막의 표면측에서부터 결정 성장 시키는 경우, 피형성면의 근방에 대해 표면의 근방에서는 결정부가 차지하는 비율이 높아지는 경우가 있다. 또한, CAAC-OS막에 불순물을 첨가함으로써, 상기 불순물 첨가 영역에 있어서 결정부가 비정질화되는 경우도 있다.

- [0153] CAAC-OS막에 포함되는 결정부의 c축은, CAAC-OS막의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향으로 정렬되기 때문에, CAAC-OS막의 형상(피형성면의 단면 형상 또는 표면의 단면 형상)에 따라서는 서로 상이한 방향을 향하는 경우가 있다. 또한, 결정부의 c축의 방향은, CAAC-OS막이 형성되었을 때의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향이 된다. 결정부는, 성막함으로써, 또는 성막후에 가열 처리 등의 결정화 처리를 행함으로써 형성된다.

- [0154] CAAC-OS막을 사용한 트랜지스터는, 가시광이나 자외광의 조사에 의한 전기적 특성의 변동을 저감시키는 것이 가능하다. 따라서, 상기 트랜지스터는, 신뢰성이 높다.

- [0155] CAAC-OS막은, 예를 들면, 다결정인 산화물 반도체 스퍼터링용 타깃을 사용하여, 스퍼터링법에 의해 성막한다. 상기 스퍼터링용 타깃에 이온이 충돌하면, 스퍼터링용 타깃에 포함되는 결정 영역이 a-b면으로부터 벽개하고, a-b면에 평행한 면을 갖는 평판상 또는 펠렛상의 스퍼터링 입자로서 박리하는 경우가 있다. 이 경우, 상기 평판상의 스퍼터링 입자가, 결정 상태를 유지한 채 기판에 도달함으로써, CAAC-OS막을 성막할 수 있다.

- [0156] 또한, CAAC-OS막을 성막하기 위해서, 이하의 조건을 적용하는 것이 바람직하다.

- [0157] 성막시의 불순물 혼입을 저감시킴으로써, 불순물에 의해 결정 상태가 붕괴되는 것을 억제할 수 있다. 예를 들면, 성막실 내에 존재하는 불순물 농도(수소, 물, 이산화탄소 및 질소 등)를 저감시키면 좋다. 또한, 성막 가스 중의 불순물 농도를 저감시키면 좋다. 구체적으로는, 노점이 -80℃ 이하, 바람직하게는 -100℃ 이하인 성막 가스를 사용한다.

- [0158] 또한, 성막시의 기판 가열 온도를 높임으로써, 기판 도달후에 스퍼터링 입자의 마이그레이션이 일어난다. 구체적으로는, 기판 가열 온도를 100℃ 이상 740℃ 이하, 바람직하게는 200℃ 이상 500℃ 이하로 하여 성막한다. 성막시의 기판 가열 온도를 높임으로써, 평판상의 스퍼터링 입자가 기판에 도달한 경우, 기판 위에서 마이그레이션이 일어나 스퍼터링 입자의 평평한 면이 기판에 부착된다.

- [0159] 또한, 성막 가스 중의 산소 비율을 높이고, 전력을 최적화함으로써 성막시의 플라즈마 대미지를 경감시키면 바람직하다. 성막 가스 중의 산소 비율은, 30체적%이상, 바람직하게는 100체적%로 한다.

- [0160] 스퍼터링용 타깃의 일례로서, In-Ga-Zn-O 화합물 타깃에 관해서 이하에 나타낸다.

- [0161] InO<sub>x</sub> 분말, GaO<sub>y</sub> 분말 및 ZnO<sub>z</sub> 분말을 소정의 mol수비로 혼합하고, 가압 처리후, 1000℃ 이상 1500℃ 이하의 온도로 가열 처리를 함으로써 다결정인 In-Ga-Zn-O 화합물 타깃으로 한다. 또한, X, Y 및 Z는 임의인 정수이다. 여기에서, 소정의 mol수비는, 예를 들면, InO<sub>x</sub> 분말, GaO<sub>y</sub> 분말 및 ZnO<sub>z</sub> 분말이, 2:2:1, 8:4:3, 3:1:1, 1:1:1, 4:2:3 또는 3:1:2이다. 또한, 분말의 종류, 및 그 혼합하는 mol수비는, 제작하는 스퍼터링용 타깃에 따라 적절히 변경하면 좋다.

- [0162] 본 실시형태는, 다른 실시형태와 적절히 조합하여 실시하는 것이 가능하다.

- [0163] (실시형태 5)

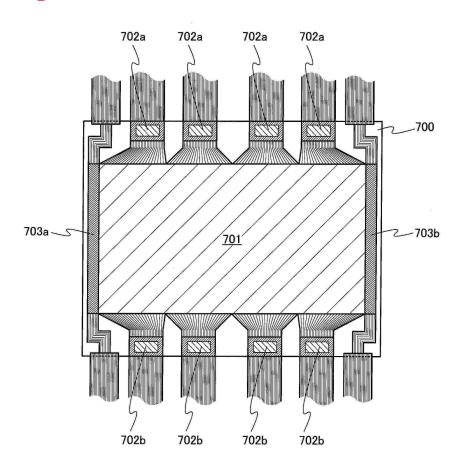

- [0164] 본 실시형태에서는, 반도체 표시 장치의 일 형태에 상당하는, 패널의 일례에 관해서 설명한다. 도 12에 도시하는 패널은, 기판(700)과, 기판(700) 위의 화소부(701), 신호선 구동 회로(702a), 신호선 구동 회로(702b), 주사선 구동 회로(703a), 및 주사선 구동 회로(703b)를 가진다.

- [0165] 화소부(701)는 복수의 화소를 가지고, 각 화소에는, 표시 소자와, 상기 표시 소자의 동작을 제어하는 단수 또는 복수의 트랜지스터가 형성되어 있다. 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)는, 각 화소에 접속된 주사선으로의 전위의 공급에 의해, 화소부(701)가 갖는 화소를 선택한다. 신호선 구동 회로(702a) 및 신호선 구동 회로(702b)는, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)에 의해 선택된 화소로의 화상 신호의 공급을 제어한다.

- [0166] 또한, 도 12에서는, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)에 의해, 화소부(701)의 양단으로부터 각 주사선으로의 전위의 공급이 행해지는 경우를 예시하고 있다. 상기 구성에 의해, 화소부(701)가 대형화됨으로써 주사선이 길어져도, 화소부(701) 내에 있어서 주사선의 배선 저항에 기인하는 전위 강하가 일어나는 것을 방지할 수 있다.

- [0167] 또한, 신호선 구동 회로(702a) 및 신호선 구동 회로(702b)에 의한, 화소로의 화상 신호의 공급은, 신호선을 개재하여 행해진다. 도 12에서는, 신호선 구동 회로(702a)에 의해, 홀수번째의 신호선을 개재하여, 화소로의 화상 신호의 공급이 행해지고, 신호선 구동 회로(702b)에 의해, 짝수번째의 신호선을 개재하여, 화소로의 화상 신호의 공급이 행해지는 경우를 예시하고 있다.

- [0168] 또한, 도 12에서는, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)가 화소부(701)와 함께 기판(700) 위에 형성되어 있고, 칩에 형성된 신호선 구동 회로(702a) 및 신호선 구동 회로(702b)가, TAB(Tape AutomatedBonding)법을사용하여 기판(700)에 실장되어 있는 경우를 예시하고 있다. 칩에 형성된 주사선 구동 로(703a) 및 주사선 구동 회로(703b)가, 기판(700)에 실장되어 있어도 좋고, 또는, 신호선 구동 희로(702a) 및 신호선 구동 회로(702b)가 화소부(701)와 함께 기판(700) 위에 형성되어 있어도 좋다. 또한, 칩의 실장도, TAB 법에 한정되지 않는다. 칩이 FPC(Flexible Printed Circuit) 등을 사용하여, 기판(700)에 실장되어 있어도 좋다.

- [0169] 주사선은, 복수의 화소에 접속되어 있기 때문에, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)에는 큰 전류 공급 능력이 요구된다. 따라서, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)가 갖는 펄스 출력 회로의 출력 측에 위치하는 트랜지스터는, 사이즈를 크게 할 필요가 있다. 특히 화소부(701)의 화소수가 증가하면, 또는 화소부(701)의 면적이 증대되면, 주사선의 배선 저항의 증대, 또는 주사선에 접속되어 있는 부하의 증대가 초래되기 때문에, 보다 큰 전류 공급 능력을 만족시키기 위해, 상기 트랜지스터의 사이즈를 더욱 크게 할 필요가 생긴다. 그리고, 상기 트랜지스터의 사이즈가 커지면, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)에 있어서 복수의 트랜지스터의 게이트 전극으로서 기능하는 도전막의 면적이 증대되어 버려, 안테나 효과에 의한 상기 배선의 정전 과괴가 일어나기 쉬워진다. 그러나, 본 발명의 일 형태에서는, 복수의 게이트 전극이, 상기 제이트 전극과 상이한 층에 형성된 도전막을 개재하여, 전기적으로 접속되어 있다. 따라서, 게이트 전극으로서 기능하는 각 도전막의 면적을 작게 억제할 수 있기 때문에, 화소부(701)의 화소수가 증가해도, 또는 화소부(701)의 면적이 증대되어도, 안테나 효과에 의한 정전 과괴를 일어나기 어렵게 할 수 있다.

- [0170] 또한, 본 실시형태에서는, 주사선 구동 회로(703a) 및 주사선 구동 회로(703b)에, 본 발명의 일 형태에 따르는 구성을 적용한 경우에 관해서 설명했지만, 본 발명의 일 형태에서는, 신호선 구동 회로(702a) 및 신호선 구동 회로(702b)에, 본 발명의 일 형태에 따르는 구성을 적용해도 좋다.

- [0171] 본 실시형태는, 다른 실시형태와 적절히 조합하여 실시하는 것이 가능하다.

- [0172] (실시형태 6)

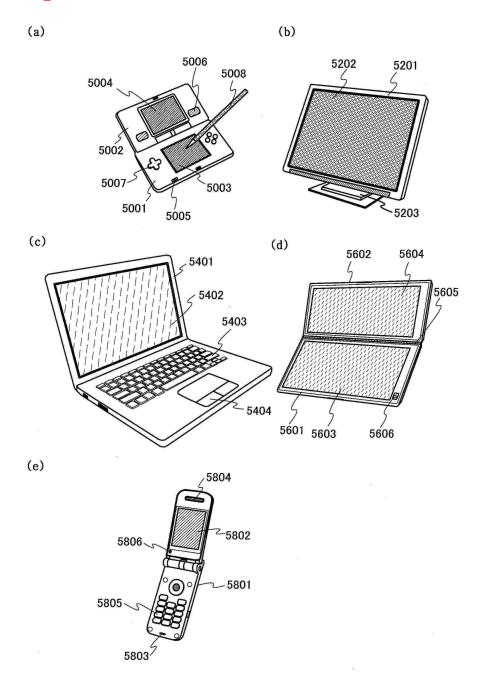

- [0173] 본 발명의 일 형태에 따르는 반도체 장치는, 표시 기기, 퍼스널 컴퓨터, 기록 매체를 구비한 화상 재생 장치(대 표적으로는 DVD: Digital Versatile Disc 등의 기록 매체를 재생하여, 그 화상을 표시할 수 있는 디스플레이를 갖는 장치)에 사용할 수 있다. 그 밖에, 본 발명의 일 형태에 따르는 반도체 장치를 사용할 수 있는 전자 기기 로서, 휴대 전화, 휴대형을 포함하는 게임기, 휴대 정보 단말, 전자 서적, 비디오 카메라, 디지털 스틸 카메라 등의 카메라, 고글형 디스플레이(헤드 마운트 디스플레이), 네비게이션 시스템, 음향 재생 장치(카 오디오, 디

지털 오디오 플레이어 등), 복사기, 팩시밀리, 프린터, 프린터 복합기, 현금 자동 입출금기(ATM), 자동 판매기 등을 들 수 있다. 이들 전자 기기의 구체적인 예를 도 13에 도시한다.

- [0174] 도 13a는 휴대형 게임기이며, 하우징(5001), 하우징(5002), 표시부(5003), 표시부(5004), 마이크로폰(5005), 스피커(5006), 조작 키(5007), 스타일러스(5008) 등을 가진다. 휴대형 게임기의 구동 회로, 또는, 표시부 (5003) 또는 표시부(5004)에, 본 발명의 일 형태에 따르는 반도체 장치를 사용함으로써, 제조 수율이 높은 휴대형 게임기를 제공할 수 있다. 또한, 도 13a에 도시한 휴대형 게임기는, 2개의 표시부(5003)와 표시부(5004)를 가지고 있지만, 휴대형 게임기가 갖는 표시부의 수는, 이것으로 한정되지 않는다.

- [0175] 도 13b는 표시 기기이며, 하우정(5201), 표시부(5202), 지지대(5203) 등을 가진다. 표시 기기의 구동 회로, 또는, 표시부(5202)에 본 발명의 일 형태에 따르는 반도체 표시 장치를 사용함으로써, 제조 수율이 높은 표시 기기를 제공할 수 있다. 또한, 표시 기기에는, 퍼스널 컴퓨터용, TV 방송 수신용, 광고 표시용 등의 모든 정보표시용 표시 기기가 포함된다.

- [0176] 도 13c는 노트형 퍼스널 컴퓨터이며, 하우징(5401), 표시부(5402), 키보드(5403), 포인팅 디바이스(5404) 등을 가진다. 노트형 퍼스널 컴퓨터의 구동 회로, 또는, 표시부(5402)에 본 발명의 일 형태에 따르는 반도체 표시 장치를 사용함으로써, 제조 수율이 높은 노트형 퍼스널 컴퓨터를 제공할 수 있다.

- [0177] 도 13d는 휴대 정보 단말이며, 제 1 하우징(5601), 제 2 하우징(5602), 제 1 표시부(5603), 제 2 표시부(5604), 접속부(5605), 조작 키(5606) 등을 가진다. 제 1 표시부(5603)는 제 1 하우징(5601)에 형성되어 있고, 제 2 표시부(5604)는 제 2 하우징(5602)에 형성되어 있다. 그리고, 제 1 하우징(5601)과 제 2 하우징(5602)은, 접속부(5605)에 의해 접속되어 있고, 제 1 하우징(5601)과 제 2 하우징(5602) 사이의 각도는, 접속부(5605)에 의해 가동으로 되어 있다. 제 1 표시부(5603)에 있어서의 영상의 전환을, 접속부(5605)에 있어서의 제 1 하우징(5601)과 제 2 하우징(5602) 사이의 각도에 따라, 전환하는 구성으로 하여도 좋다. 또한, 제 1 표시부(5603) 및 제 2 표시부(5604)의 적어도 한쪽에, 위치 입력 장치로서의 기능이 부가된 반도체 표시 장치를 사용하도록 해도 좋다. 또한, 위치 입력 장치로서의 기능은, 반도체 표시 장치에 터치 패널을 형성함으로써 부가할 수 있다. 또는, 위치 입력 장치로서의 기능은, 포토 센서라고도 불리는 광전 변환 소자를 반도체 표시 장치의 화소부에 형성함으로써도, 부가할 수 있다. 휴대 정보 단말의 구동 회로, 또는, 제 1 표시부(5603) 또는 제 2 표시부(5604)에 본 발명의 일 형태에 따르는 반도체 장치를 사용함으로써, 제조 수율이 높은 휴대 정보 단말을 제공할 수 있다.

- [0178] 도 13e는 휴대 전화이며, 하우징(5801), 표시부(5802), 음성 입력부(5803), 음성 출력부(5804), 조작 키 (5805), 수광부(5806) 등을 가진다. 수광부(5806)에 있어서 수신한 광을 전기 신호로 변환함으로써, 외부의 화상을 받아 들일 수 있다. 휴대 전화의 구동 회로, 또는, 표시부(5802)에 본 발명의 일 형태에 따르는 반도체 장치를 사용함으로써, 제조 수율이 높은 휴대 전화를 제공할 수 있다.

- [0179] 본 실시형태는, 다른 실시형태와 적절히 조합하여 실시할 수 있다.

#### 부호의 설명

- [0180] 100 반도체 장치

- 101 트랜지스터

- 102 트랜지스터

- 103 배선

- 104 배선

- 105 배선

- 106 배선

- 107 배선

- 110 도전막

- 111 게이트 절연막

- 112 반도체막

- 113 도전막

- 114 도전막

- 115 도전막

- 116 반도체막

- 117 도전막

- 118 도전막

- 119 도전막

- 120 개구부

- 121 개구부

- 122 도전막

- 123 반도체막

- 124 도전막

- 125 도전막

- 126 반도체막

- 127 도전막

- 128 도전막

- 210 도전막

- 211 게이트 절연막

- 212 반도체막

- 213 도전막

- 214 도전막

- 215 도전막

- 216 반도체막

- 217 도전막

- 218 도전막

- 219 도전막

- 220 개구부

- 221 개구부

- 222 도전막

- 223 반도체막

- 224 도전막

- 225 도전막

- 226 반도체막

- 227 도전막

- 228 도전막

- 300 펄스 발생 회로

- 301 트랜지스터

- 302 트랜지스터

- 303 트랜지스터

- 304 트랜지스터

- 305 트랜지스터

- 306 트랜지스터

- 307 트랜지스터

- 308 트랜지스터

- 309 트랜지스터

- 310 트랜지스터

- 311 트랜지스터

- 312 트랜지스터

- 313 트랜지스터

- 314 트랜지스터

- 315 트랜지스터

- 316 용량 소자

- 317 배선

- 318 배선

- 319 배선

- 320 배선

- 321 배선

- 322 배선

- 323 배선

- 324 배선

- 325 배선

- 326 배선

- 327 배선

- 328 배선

- 329 배선

- 350 인버터

- 351 인버터

- 400 펄스 발생 회로

- 402 트랜지스터

- 403 트랜지스터

- 404 트랜지스터

- 405 배선

- 406 배선

- 407 배선

- 408 배선

- 409 배선

- 410 배선

- 411 배선

- 412 배선

- 413 배선

- 414 배선

- 415 트랜지스터

- 416 트랜지스터

- 417 트랜지스터

- 418 트랜지스터

- 419 트랜지스터

- 420 트랜지스터

- 430 펄스 발생 회로

- 432 트랜지스터

- 433 트랜지스터

- 434 트랜지스터

- 435 배선

- 436 배선

- 437 배선

- 438 배선

- 439 배선

- 440 배선

- 441 배선

- 442 배선

- 443 배선

- 444 배선

- 445 배선

- 446 트랜지스터

- 447 트랜지스터

- 448 트랜지스터

- 449 트랜지스터

- 450 트랜지스터

- 451 트랜지스터

- 452 트랜지스터

- 460 펄스 발생 회로

- 462 트랜지스터

- 463 트랜지스터

- 464 트랜지스터

- 465 배선

- 466 배선

- 467 배선

- 468 배선

- 469 배선

- 470 배선

- 471 배선

- 472 배선

- 474 배선

- 475 배선

- 476 트랜지스터

- 477 트랜지스터

- 478 트랜지스터

- 479 트랜지스터

- 480 트랜지스터

- 481 트랜지스터

- 482 트랜지스터

- 500 펄스 발생 회로

- 502 트랜지스터

- 503 트랜지스터

- 504 트랜지스터

- 505 배선

- 506 배선

- 507 배선

- 508 배선

- 509 배선

- 510 배선

- 511 배선

- 512 배선

- 514 배선

- 515 배선

- 516 트랜지스터

- 517 트랜지스터

- 518 트랜지스터

- 519 트랜지스터

- 520 트랜지스터

- 521 트랜지스터

- 522 트랜지스터

- 523 트랜지스터

- 530 펄스 발생 회로

- 532 트랜지스터

- 533 트랜지스터

- 534 트랜지스터

- 535 배선

- 536 배선

- 537 배선

- 538 배선

- 539 배선

- 540 배선

- 541 배선

- 542 배선

- 544 배선

- 545 배선

- 546 트랜지스터

- 547 트랜지스터

- 548 트랜지스터

- 549 트랜지스터

- 550 트랜지스터

- 551 트랜지스터

- 552 트랜지스터

- 553 트랜지스터

- 700 기판

- 701 화소부

- 702a 신호선 구동 회로

- 702b 신호선 구동 회로

- 703a 주사선 구동 회로

- 703b 주사선 구동 회로

- 800 기판

- 802 게이트 절연막

- 812 도전막

- 813 반도체막

- 814 도전막

- 815 도전막

- 816 도전막

- 817 반도체막

- 818 도전막

- 819 도전막

- 820 절연막

- 821 절연막

- 822 도전막

- 824 절연막

- 825 EL층

- 826 도전막

- 830 트랜지스터

- 831 트랜지스터

- 832 발광 소자

- 840 화소

- 841 구동 회로

- 850 도전막

- 851 도전막

- 852 도전막

- 853 도전막

- 854 절연막

- 5001 하우징

- 5002 하우징

- 5003 표시부

- 5004 표시부

- 5005 마이크로폰

- 5006 스피커

- 5007 조작 키

- 5008 스타일러스

- 5201 하우징

- 5202 표시부

- 5203 지지대

- 5401 하우징

- 5402 표시부

- 5403 키보드

- 5404 포인팅 디바이스

- 5601 하우징

- 5602 하우징

- 5603 표시부

- 5604 표시부

- 5605 접속부

- 5606 조작 키

- 5801 하우징

- 5802 표시부

- 5803 음성 입력부

- 5804 음성 출력부

- 5805 조작 키

- 5806 수광부

# (b)

# (c)

(b)

(c)

(a)

(b)

(a)

(b)