(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3991230号

(P3991230)

(45) 発行日 平成19年10月17日(2007.10.17)

(24) 登録日 平成19年8月3日(2007.8.3)

(51) Int.C1.

F 1

H O 1 L 21/8246 (2006.01)

H O 1 L 27/105 (2006.01)

H O 1 L 27/10 4 4 4 C

請求項の数 5 (全 10 頁)

(21) 出願番号 特願2004-34597 (P2004-34597)

(22) 出願日 平成16年2月12日 (2004.2.12)

(65) 公開番号 特開2005-228852 (P2005-228852A)

(43) 公開日 平成17年8月25日 (2005.8.25)

審査請求日 平成16年12月14日 (2004.12.14)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100090387

弁理士 布施 行夫

(74) 代理人 100090398

弁理士 大渕 美千栄

(72) 発明者 木島 健

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 瀧内 健夫

最終頁に続く

(54) 【発明の名称】強誘電体キャパシタ及びその形成方法、ならびに強誘電体メモリ

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に下部電極、強誘電体膜、及び上部電極を順次積層して強誘電体キャパシタを形成する方法であって、

ダイヤモンドライカーボン(DLC)からなる誘電体膜を形成し、該誘電体膜の所与の領域に対してフッ素をイオン注入して、当該領域を導電体化することにより前記下部電極及び上部電極の少なくとも一方を形成する、強誘電体キャパシタの形成方法。

## 【請求項2】

基板上に下部電極、強誘電体膜、及び上部電極を順次積層して強誘電体キャパシタを形成する方法であって、

ダイヤモンドライカーボン(DLC)のフッ素化合物からなる導電体膜を形成し、該導電体膜の所与の領域に対して窒素をイオン注入して、当該領域を誘電体化することにより前記下部電極及び上部電極の少なくとも一方を形成する、強誘電体キャパシタの形成方法。

## 【請求項3】

基板上に下部電極、強誘電体膜、及び上部電極を順次積層して強誘電体キャパシタを形成する方法であって、

I n<sub>2</sub>-x S n O<sub>3</sub> (ITO)からなる導電体膜を形成し、該導電体膜の所与の領域に対してアンチモンをイオン注入して、当該領域を誘電体化することにより前記下部電極及び上部電極の少なくとも一方を形成する、強誘電体キャパシタの形成方法。

**【請求項 4】**

請求項1～3のいずれかに記載の形成方法により形成された、強誘電体キャパシタ。

**【請求項 5】**

請求項4に記載の強誘電体キャパシタを含む、強誘電体メモリ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、強誘電体キャパシタ及びその製造方法、ならびに強誘電体メモリに関する。

**【背景技術】****【0002】**

強誘電体メモリ（F e R A M）は、キャパシタ部分に強誘電体を用い、その自発分極によりデータを保持するものである。キャパシタは、主としてドライエッチングが適用されて所望の形状にパターニング形成される。

**【0003】**

しかし、エッチング工程は、キャパシタの電極材料や強誘電体膜に加工ダメージを与えるため、キャパシタの特性に望ましからぬ影響を与えることが懸念されている。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

本発明は上記事情に鑑みてなされたものであり、その目的は、加工ダメージを低減することができる強誘電体キャパシタの形成方法を提供することにある。また、本発明の他の目的は、加工ダメージが少なく良好な特性を有する強誘電体キャパシタ、およびこれを含む強誘電体メモリを提供することにある。

20

**【課題を解決するための手段】****【0005】**

(1) 本発明は、基板上に下部電極、強誘電体膜、及び上部電極を順次積層して強誘電体キャパシタを形成する方法であって、誘電体膜を形成し、その後該誘電体膜の所与の領域にイオンビームを照射あるいは所定元素のイオン注入を行って該領域を導電体化することにより前記下部電極及び上部電極の少なくとも一方を形成する強誘電体キャパシタの形成方法に関するものである。

30

**【0006】**

本発明によれば、キャパシタの電極形成に際し、まず誘電体膜を形成してから所望の領域のみを導電体化して下部電極あるいは上部電極を形成する。誘電体膜の導電体化は、イオンビームを照射することや所定元素のイオン注入により実現される。すなわち、本発明では、誘電体膜の特定の領域のみを導電体化させてエッチングレスで所望パターンの強誘電体キャパシタを形成することができ、キャパシタ構成部材の加工ダメージを低減することができる。

**【0007】**

(2) 本発明の形成方法では、ダイヤモンドライクカーボン（D L C）からなる誘電体膜を形成し、該誘電体膜の所与の領域に対してイオンビームを照射して、該領域を導電体化することにより前記下部電極及び上部電極の少なくとも一方を形成してもよい。

40

**【0008】**

ダイヤモンドライクカーボン（D L C）は、天然ダイヤモンドと同じ炭素のS P 3結合と、グラファイトと同じ炭素のS P 2結合と、水素との結合とを含むアモルファス構造を有する炭素化合物である。D L Cは、高硬度、低磨耗、低摩擦、表面平滑性に優れた低誘電率（ $r = \sim 2$ ）の誘電体である。このD L Cに対してイオンビームなどの高エネルギーを与えると、結合が破壊されて低抵抗の導電体となる。すなわち、この態様によれば、D L C膜の所望の領域にイオンビームを照射することによって、エッチングレスで所望パターンの下部電極や上部電極の作りこみを行うことが可能となる。

**【0009】**

50

(3) 本発明の形成方法では、ダイヤモンドライクカーボン(DLC)からなる誘電体膜を形成し、該誘電体膜の所与の領域に対してフッ素をイオン注入して、当該領域を導電体化することにより前記下部電極及び上部電極の少なくとも一方を形成してもよい。 DLCは、フッ素イオンが添加されることにより、低抵抗化して導電体として用いることができる。すなわち、この態様によれば、DLC膜の所望の領域にフッ素をイオン注入することによって、エッチングレスで所望パターンの下部電極や上部電極の作りこみを行うことが可能となる。

#### 【0010】

(4) 本発明は、基板上に下部電極、強誘電体膜、及び上部電極を順次積層して強誘電体キャパシタを形成する方法であって、導電体膜を形成し、その後該導電体膜の所与の領域に所定元素のイオン注入を行って該領域を誘電体化することにより前記下部電極及び上部電極の少なくとも一方を形成する強誘電体キャパシタの形成方法に関するものである。10

#### 【0011】

本発明によれば、キャパシタの電極形成に際し、まず導電体膜を形成してから所望の領域のみを誘電体化して下部電極あるいは上部電極を形成する。導電体膜の誘電体化は、所定元素のイオン注入により実現される。すなわち、本発明では、導電体膜の特定の領域のみを誘電体化させてエッチングレスで所望パターンの強誘電体キャパシタを形成することができ、キャパシタ構成部材の加工ダメージを低減することができる。

#### 【0012】

(5) 本発明の形成方法では、ダイヤモンドライクカーボン(DLC)のフッ素化合物からなる導電体膜を形成し、該導電体膜の所与の領域に対して窒素をイオン注入して、当該領域を誘電体化することにより前記下部電極及び上部電極の少なくとも一方を形成してもよい。 DLCのフッ素化合物は導電体であるが、これに窒素イオンが添加されることにより、誘電体として用いることができる。すなわち、この態様によれば、DLCのフッ素化合物膜の所望の領域に窒素をイオン注入することによって、エッチングレスで所望パターンの下部電極や上部電極の作りこみを行うことが可能となる。20

#### 【0013】

(6) 本発明の形成方法では、 $In_{2-x}Sn_xO_3$ (ITO)からなる導電体膜を形成し、該導電体膜の所与の領域に対してアンチモンをイオン注入して、当該領域を誘電体化することにより前記下部電極及び上部電極の少なくとも一方を形成してもよい。 ITOは、酸化インジウム( $In_2O_3$ )にスズ(Sn)をドープしたものであり、スズはインジウムの置換位置に入りて $In_{2-x}Sn_xO_3$ を形成する。 ITOは、導電体であるが、これにアンチモン(Sn)が添加されると誘電体として用いることができる。また、ITOは耐熱性やPZT系強誘電体との格子整合性に優れ、キャパシタの電極材料に適している。すなわち、この態様によれば、ITO膜の所望の領域にアンチモンをイオン注入することによってエッチングレスで所望パターンの下部電極や上部電極の作りこみを行うことが可能となる。30

#### 【0014】

(7) 本発明は、上記いずれかに記載の形成方法により形成された強誘電体キャパシタに関するものである。40

#### 【0015】

(8) 本発明は、上記強誘電体キャパシタを含む強誘電体メモリに関するものである。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、本発明に好適な実施の形態について、図面を参照しながら説明する。

#### 【0017】

##### 1. 第1の強誘電体キャパシタの形成方法

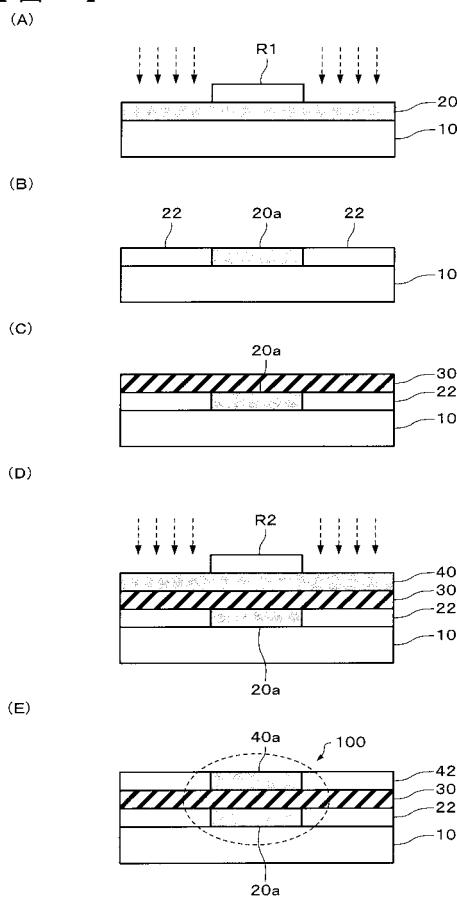

図1(A)～図1(E)は、本発明の実施の形態に係る第1の強誘電体キャパシタの形成工程例を模式的に示す断面図である。

#### 【0018】

本実施の形態の第1の強誘電体キャパシタの形成方法では、まず、基板10の上に下部電極20aを形成する(図1(A), (B)参照)。基板10は、例えば、シリコンなどの半導体基板やSOI基板などを用いることができる。下部電極20aは、ダイヤモンドライクカーボン(DLC)のフッ素化合物(DLCF)や、 $In_{2-x}Sn_xO_3$ (ITO)といった導電性酸化物から形成される導電体膜20からなる。導電体膜20は、例えば、CVD法、スプレーバイロシス法、真空蒸着法、電子ビーム蒸着法、スパッタ法、イオンビームスパッタ法、イオンプレーティング法、イオンアシスト蒸着法などの各種の成膜方法を用いて形成する。

#### 【0019】

下部電極20aのより具体的な形成方法は、まず基板10上に導電体膜20を形成して、導電体膜20のうち下部電極20aとする領域上にレジストR1を形成する。そして、所定の元素、例えば、DLCFの場合は窒素(N)、ITOの場合はアンチモン(Sb)を導電体膜20に対してイオン注入することにより、イオン注入された領域が誘電体化(比抵抗が $\sim 10^6$  cmへと変化)して所望のパターン形状の下部電極20aをエッチングレスで得ることができる。なお、レジストR1は、イオン注入が終了した後に除去される。

#### 【0020】

次に、下部電極20aの上に強誘電体膜30を形成する(図1(C)参照)。強誘電体膜30は、PZTやPZTにNbを加えたPZTNなどのペロブスカイト構造強誘電体材料や、SBTやBITなどのBi層状ペロブスカイト構造強誘電体材料などからなる。成膜方法としては、溶液塗布法、スパッタ法、CVD法などが挙げられる。

#### 【0021】

次に、強誘電体膜30の上に上部電極40aを形成する(図1(D), (E)参照)。具体的には、下部電極20aの場合と同様に、導電体膜40を形成し、続いて導電体膜40の下部電極20aとの対向領域の上にレジストR2を形成する。そして、導電体膜40に対して所定の元素を下部電極20aを形成する場合と同様にイオン注入して導電体膜40のレジストR2に被覆されていない領域を誘電体化する。これにより、所望のパターン形状の上部電極40aをエッチングレスで得ることができる。第1の強誘電体キャパシタの形成方法では、以上のようにして強誘電体キャパシタ100を得ることができる。

#### 【0022】

以上に述べたように、本実施の形態によれば、誘電体膜20, 40の特定の領域のみを誘電体化させてエッチングレスで所望のパターン形状の下部電極20a及び上部電極40aを有する強誘電体キャパシタ100を形成することができ、キャパシタ構成部材の加工ダメージの低減を図ることができる。

#### 【0023】

##### 2. 第2の強誘電体キャパシタの形成方法

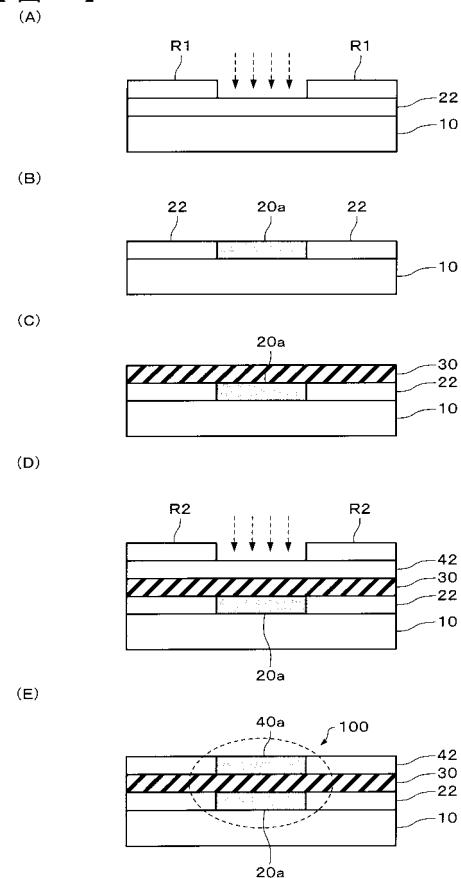

図2(A)～図2(E)は、本発明の実施の形態に係る第2の強誘電体キャパシタの形成工程例を模式的に示す断面図である。図2(A)～図2(E)においては、図1(A)～図1(E)に示す各部材と実質的に同一の機能を有する部材には同一の符号を付し、以下では詳細な説明を省略する。

#### 【0024】

本実施の形態の第2の強誘電体キャパシタの形成方法では、まず、基板10の上に下部電極20aを形成する(図2(A), (B)参照)。下部電極20aは、ダイヤモンドライクカーボン(DLC)のフッ素化合物(DLCF)や、カーボン(C)から形成される導電体膜20からなる。導電体膜20は、例えば、CVD法、スプレーバイロシス法、真空蒸着法、電子ビーム蒸着法、スパッタ法、イオンビームスパッタ法、イオンプレーティング法、イオンアシスト蒸着法などの各種の成膜方法を用いて形成する。

#### 【0025】

本実施の形態における下部電極20aのより具体的な形成方法は、まず基板10上にダイヤモンドライクカーボン(DLC)からなる誘電体膜22を形成して、誘電体膜22の

10

20

20

30

40

50

うち下部電極 20a とする領域を露出させるように誘電体膜 22 上にレジスト R1 を形成する。そして、所定の元素としてフッ素 (F) を誘電体膜 22 に対してイオン注入することにより、イオン注入された領域が低抵抗化 ( $\sim 10^{-2}$  cm) して導体化することにより所望のパターン形状の下部電極 20a をエッチングレスで得ることができる。なお、レジスト R1 は、イオン注入が終了した後に除去される。また、DLC は、イオンビームなどの高エネルギーを与えると、結合が破壊されて低抵抗 ( $6 \times 10^{-3}$  cm) のカーボン (C) からなる導電体へと変質する。このため、本実施の形態では、DLC からなる誘電体膜 22 にイオン注入を行う代わりに、イオンビームなどのエネルギー線を照射して導電体化してもよい。この場合、イオンビーム加工ではレジストを用いないマスクレスでの直接描画が可能であるため、レジスト塗布工程などを省略することができ、工程数の削減を図ることができる。また、DLC の比抵抗は、 $10^9$  cm とカーボンに比して非常に大きいものであるため、イオンビーム照射によって DLC を導体化すれば、導電体膜 20 と誘電体膜 22 との導電性の差を大きく得ることができる。10

#### 【0026】

次に、下部電極 20a の上に強誘電体膜 30 を形成し (図 2 (C) 参照)、強誘電体膜 30 の上に上部電極 40a を形成する (図 2 (D), (E) 参照)。具体的には、下部電極 20a の場合と同様に、誘電体膜 42 を形成し、続いて誘電体膜 42 の下部電極 20a との対向領域を露出させるように、誘電体膜 42 の上にレジスト R2 を形成する。そして、誘電体膜 42 に対して所定の元素としてフッ素をイオン注入あるいはイオンビームを照射して誘電体膜 40 のレジスト R2 に被覆されていない領域を導電体化する。これにより、所望のパターン形状の上部電極 40a をエッチングレスで得ることができる。第 2 の強誘電体キャパシタの形成方法では、以上のようにして強誘電体キャパシタ 100 を得ることができる。20

#### 【0027】

以上に述べたように、本実施の形態によれば、誘電体膜 22, 42 の特定の領域のみを導電体化させてエッチングレスで所望パターンの下部電極 20a 及び上部電極 40a を有する強誘電体キャパシタ 100 を形成することができ、キャパシタ構成部材の加工ダメージの低減を図ることができる。

#### 【0028】

##### 3. 強誘電体メモリおよびそのメモリセルアレイの形成方法

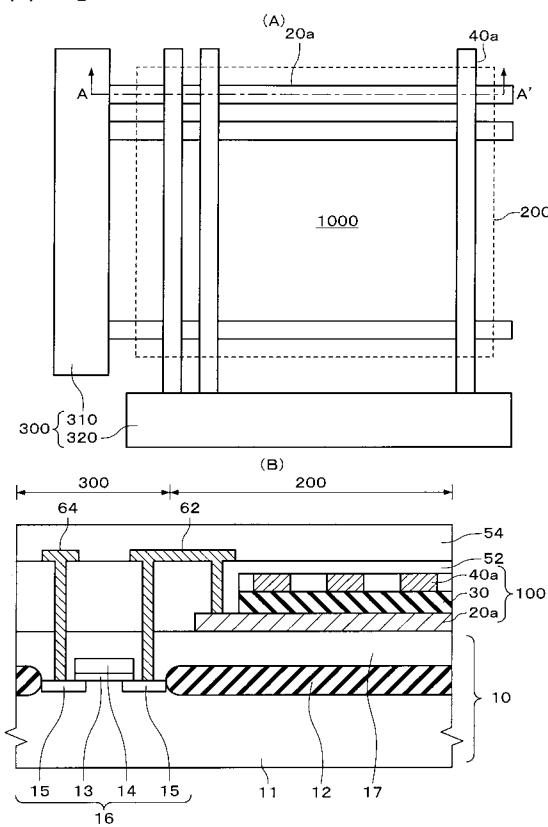

図 3 (A) 及び図 3 (B) は、上記形成方法により得られた強誘電体キャパシタを用いたメモリセルアレイを有する強誘電体メモリ 1000 を模式的に示す図である。なお、図 3 (A) は、強誘電体メモリ 1000 の平面的形状を示すものであり、図 3 (B) は、図 3 (A) における A-A' 断面を示すものである。30

#### 【0029】

強誘電体メモリ 1000 は、図 3 (A) に示すように、メモリセルアレイ 200 と、周辺回路部 300 とを有する。そして、メモリセルアレイ 200 と周辺回路部 300 とは、異なる層に形成されている。また、周辺回路部 300 は、メモリセルアレイ 200 に対して半導体基板 11 上の異なる領域に配置されている。なお、周辺回路 300 の具体例としては、Yゲート、センスアンプ、入出力バッファ、Xアドレスデコーダ、Yアドレスデコーダ、又はアドレスバッファを挙げることができる。40

#### 【0030】

メモリセルアレイ 200 は、行選択のための下部電極 20a (ワード線) と、列選択のための上部電極 40a (ビット線) とが交叉するように配列されている。また、下部電極 20a 及び上部電極 40a は、複数のライン状の信号電極から成るストライプ形状を有する。なお、信号電極は、下部電極 20a がビット線、上部電極 40a がワード線となるように形成することができる。この下部電極 20a および上部電極 40a は、上記実施の形態に係る形成方法を用いて形成されているため、加工ダメージが少ない。

#### 【0031】

そして、図 3 (B) に示すように、下部電極 20a と上部電極 40a との間には、強誘

10

20

30

40

50

電体膜 30 が配置されている。メモリセルアレイ 200 では、この下部電極 20a と上部電極 40aとの交叉する領域において、メモリセルとして機能する強誘電体キャパシタ 100 が構成される。なお、強誘電体膜 30 は、少なくとも下部電極 20a と上部電極 40aとの交叉する領域の間に配置されていればよい。

#### 【0032】

さらに、強誘電体メモリ 1000 は、下部電極 20a、強誘電体膜 30、及び上部電極 40a を覆うように、第 2 の層間絶縁膜 52 が形成されている。さらに、配線層 62、64 を覆うように第 2 の層間絶縁膜 52 の上に絶縁性の保護層 54 が形成されている。

#### 【0033】

周辺回路部 200 は、図 3 (A) に示すように、メモリセル 200 に対して選択的に情報の書き込み若しくは読み出しを行うための各種回路を含み、例えば、下部電極 20a を選択的に制御するための第 1 の駆動回路 310 と、上部電極 40a を選択的に制御するための第 2 の駆動回路 320 と、その他にセンスアンプなどの信号検出回路 (図示省略) とを含んで構成される。

#### 【0034】

また、周辺回路部 300 は、図 3 (B) に示すように、半導体基板 10 上に形成された MOS トランジスタ 16 を含む。MOS トランジスタ 16 は、ゲート絶縁膜 13、ゲート電極 14、及びソース / ドレイン領域 15 を有する。各 MOS トランジスタ 16 間は、素子分離領域 12 によって分離されている。この MOS トランジスタ 16 が形成された半導体基板 10 上には、第 1 の層間絶縁膜 17 が形成されている。そして、周辺回路部 300 とメモリセルアレイ 200 とは、配線層 62 によって電気的に接続されている。

#### 【0035】

次に、強誘電体メモリ 1000 における書き込み、読み出し動作の一例について述べる。

#### 【0036】

まず、読み出し動作においては、選択されたメモリセルのキャパシタに読み出し電圧が印加される。これは、同時に ‘0’ の書き込み動作を兼ねている。このとき、選択されたビット線を流れる電流又はビット線をハイインピーダンスにしたときの電位をセンスアンプにて読み出す。そして、非選択のメモリセルのキャパシタには、読み出し時のクロストークを防ぐため、所定の電圧が印加される。

#### 【0037】

書き込み動作においては、‘1’ の書き込みの場合は、選択されたメモリセルのキャパシタに分極状態を反転させる書き込み電圧が印加される。‘0’ の書き込みの場合は、選択されたメモリセルのキャパシタに分極状態を反転させない書き込み電圧が印加され、読み出し動作時に書き込まれた ‘0’ 状態を保持する。このとき、非選択のメモリセルのキャパシタには書き込み時のクロストークを防ぐために、所定の電圧が印加される。

#### 【0038】

この強誘電体メモリ 1000 によれば、上記実施の形態の形成方法により強誘電体キャパシタ 100 がエッティングレスで形成されているため、品質の向上および歩留まりの向上を図ることができる。

#### 【0039】

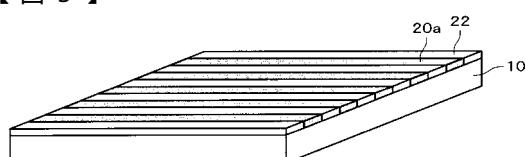

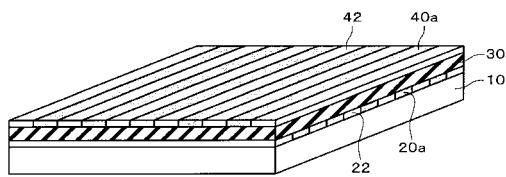

次に、本実施の形態の強誘電体キャパシタの形成方法を適用したメモリセルアレイ 200 の形成方法について図 4 ~ 図 8 を参照しながら説明する。

#### 【0040】

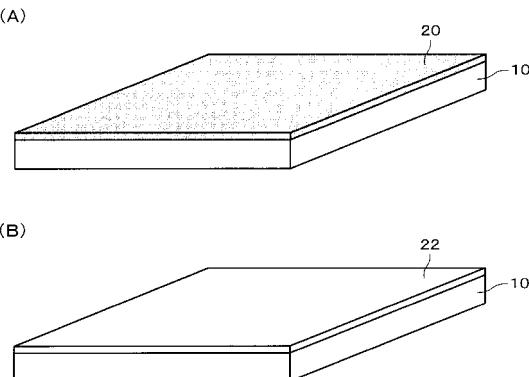

まず、基板 10 上に導電体膜 20 あるいは誘電体膜 22 を形成する (図 4 (A), 図 4 (B) 参照)。そして、図 1 (A), (B) あるいは図 2 (A), (B) で説明した手法に従い、導電体膜 20 あるいは誘電体膜 22 の上にストライプパターンでレジストを形成し、導電体膜 20 あるいは誘電体膜 22 に対してイオン注入あるいはイオンビームの照射を行って、ストライプパターンの下部電極 20a を形成する (図 5 参照)。

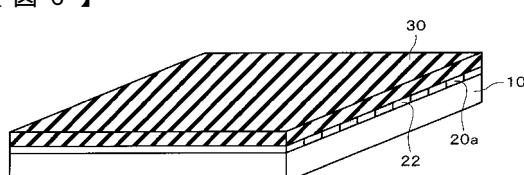

#### 【0041】

次に、下部電極 20a を被覆するように強誘電体膜 30 を形成し (図 6 参照)、下部電

10

20

30

40

50

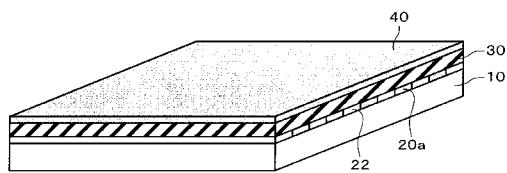

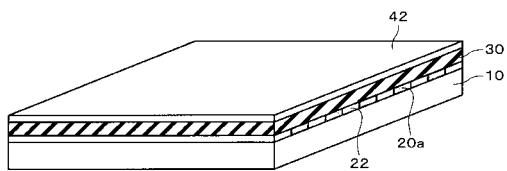

極 20 a の場合と同様に、強誘電体膜 30 の上に導電体膜 40 あるいは誘電体膜 42 を形成する（図 7（A），（B）参照）。最終的には、図 1（D），（E）あるいは図 2（D），（E）で説明した手法に従い、導電膜 40 あるいは誘電体膜 42 の上に下部電極 20 a と交差するようなストライプパターンでレジストを形成し、導電体膜 40 あるいは誘電体膜 42 に対してイオン注入あるいはイオンビームの照射を行って、下部電極 20 a と交差する上部電極 40 a を形成する。このようにして、メモリセルアレイ 200 を得ることができる。

#### 【0042】

以上のように、図 3（A），（B）に示すような電極間の密度が高い単純マトリクス型（クロスポイント型）メモリに本実施の形態の第 1 あるいは第 2 の強誘電体キャパシタの形成方法を適用すれば、下部電極 20 a と上部電極 40 a の形成をエッチングレス化することにより、加工ダメージの少ない品質の高いメモリセルアレイ 200 を得ることができる。また、本実施の形態の強誘電体メモリ 1000 のように電極間距離が高密度化した場合でも、低誘電率の DLC (DLCN を含む) を下部電極 20 a 及び上部電極 40 a の形成の際の誘電体膜として用いることで寄生容量を抑制することができる。

#### 【0043】

以上に本発明に好適な実施の形態について説明したが、本発明は上述したものに限られるものではなく、発明の要旨の範囲内で種々の変形態様により実施することができる。

#### 【図面の簡単な説明】

#### 【0044】

【図 1】本実施の形態に係る第 1 の強誘電体キャパシタの形成工程例を示す断面図。

【図 2】本実施の形態に係る第 2 の強誘電体キャパシタの形成工程例を示す断面図。

【図 3】本実施の形態に係る強誘電体メモリを示す平面図及び断面図。

【図 4】本実施の形態に係る強誘電体メモリのメモリセルアレイの一形成工程を示す斜視図。

【図 5】本実施の形態に係る強誘電体メモリのメモリセルアレイの一形成工程を示す斜視図。

【図 6】本実施の形態に係る強誘電体メモリのメモリセルアレイの一形成工程を示す斜視図。

【図 7】本実施の形態に係る強誘電体メモリのメモリセルアレイの一形成工程を示す斜視図。

【図 8】本実施の形態に係る強誘電体メモリのメモリセルアレイの一形成工程を示す斜視図。

#### 【符号の説明】

#### 【0045】

10 基板、20 a 下部電極、30 強誘電体膜、40 a 上部電極、20, 40 導体膜、22, 42 誘電体膜、100 強誘電体キャパシタ、200 メモリセルアレイ、300 周辺回路部、1000 強誘電体メモリ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(A)

(B)

【図8】

---

フロントページの続き

(56)参考文献 特開平05-036847(JP,A)

特開平10-261712(JP,A)

特開平10-041300(JP,A)

特開2003-243622(JP,A)

特開平04-067633(JP,A)

特開平10-209152(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205

H01L 21/768

H01L 21/8246

H01L 27/105