RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 524 713**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 82 05781**

(54) Transistor à effet de champ du type planar à grille supplémentaire enterrée et procédé de réalisation d'un tel transistor.

(51) Classification internationale (Int. Cl. 3). H 01 L 29/76, 21/20, 21/283.

(22) Date de dépôt..... 2 avril 1982.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 40 du 7-10-1983.

(71) Déposant : Société dite : THOMSON-CSF, société anonyme. — FR.

(72) Invention de : Paul Robert Jay et Christian Rumelhard.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Philippe Guilguet, Thomson-CSF, SCPI,

173, bd Haussmann, 75360 Paris Cedex 08.

TRANSISTOR A EFFET DE CHAMP DU TYPE PLANAR A GRILLE

SUPPLEMENTAIRE ENTERREE ET PROCEDE DE

REALISATION D'UN TEL TRANSISTOR

L'invention concerne un transistor à effet de champ du type plan ou "planar" comportant une grille dans le plan commun aux 3 électrodes et une grille supplémentaire enterrée.

5 Cette grille supplémentaire peut être raccordée à la première de façon permanente, par une connexion de résistance nulle ou quasi-nulle ; elle peut aussi être utilisée en grille auxiliaire, comme dans un transistor de type "bigrille".

On connaît des transistors à effet de champ à deux grilles :

10 - du type planar, où les deux grilles sont disposées en parallèle dans le même plan ;

- du type à canal horizontal avec grille supplémentaire (placée sous le dispositif), qui a été proposé par J.C. VOKES et al dans la revue "Electronic Letters" Année 1979 Vol.15, pages 627 - 629.

15 On connaît aussi des transistors à canal vertical ou P.B.T (permeable base transistor) dans lesquels le contrôle du courant est effectué par une grille présentant des mailles enterrées dans le matériau semiconducteur.

Or, chacune de ces solutions présente des inconvénients dont les principales sont :

20 - pour les transistors planar, l'augmentation de la résistance d'accès aux grilles à partir de la source ou du drain, en raison de l'espacement supplémentaire nécessaire pour loger les deux électrodes parallèles de grille entre source et drain, cette résistance supplémentaire étant particulièrement gênante en très haute fréquence ;

25 - pour le transistor de VOKES, il faut supprimer le substrat pour pouvoir déposer la deuxième grille sur la face arrière et résoudre un problème difficile d'alignement.

- pour le transistor à canal vertical, la technologie de fabrication particulièrement délicate et complexe.

L'invention vise à remédier à ces inconvénients.

Le transistor à effet de champ selon l'invention est du type comportant des électrodes de source, grille et drain disposées sensiblement sur une même face d'une plaquette semiconductrice. Il est caractérisé en ce qu'il comporte en outre une électrode de grille supplémentaire accessible par la même face que les électrodes précédentes et constituée d'au moins un barreau noyé dans le matériau semiconducteur constituant la plaquette.

L'invention sera mieux comprise, et d'autres caractéristiques apparaîtront, au moyen de la description qui suit, et des dessins qui l'accompagnent, parmi lesquels :

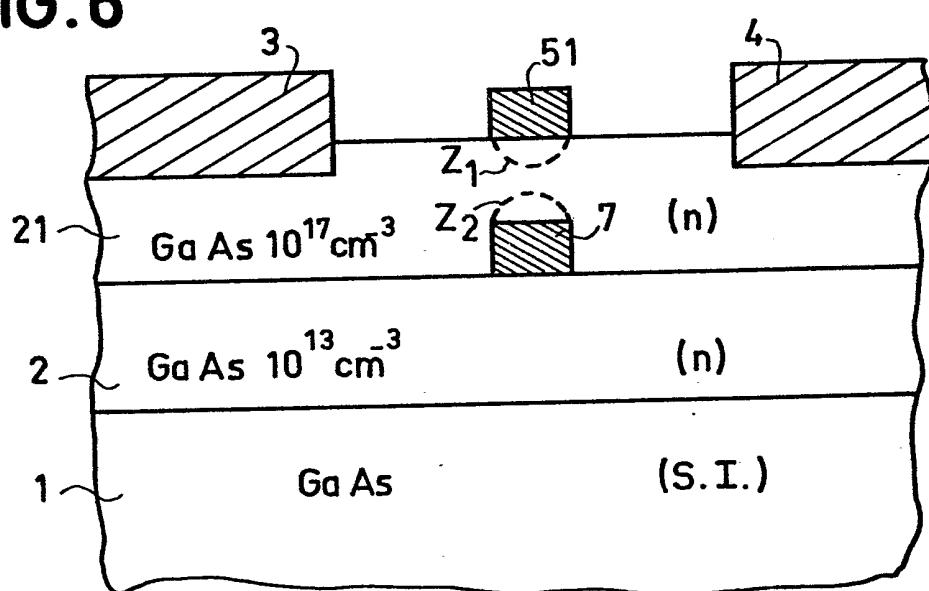

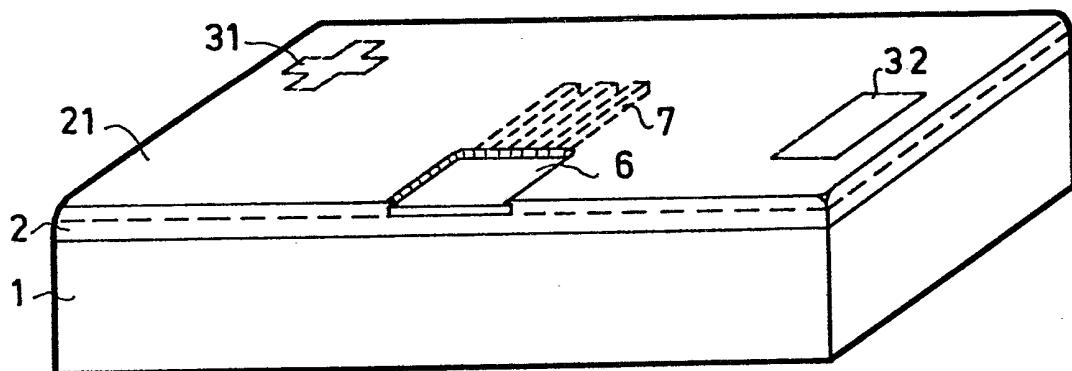

La figure 1 est une représentation simplifiée à trois dimensions d'un transistor selon l'invention ;

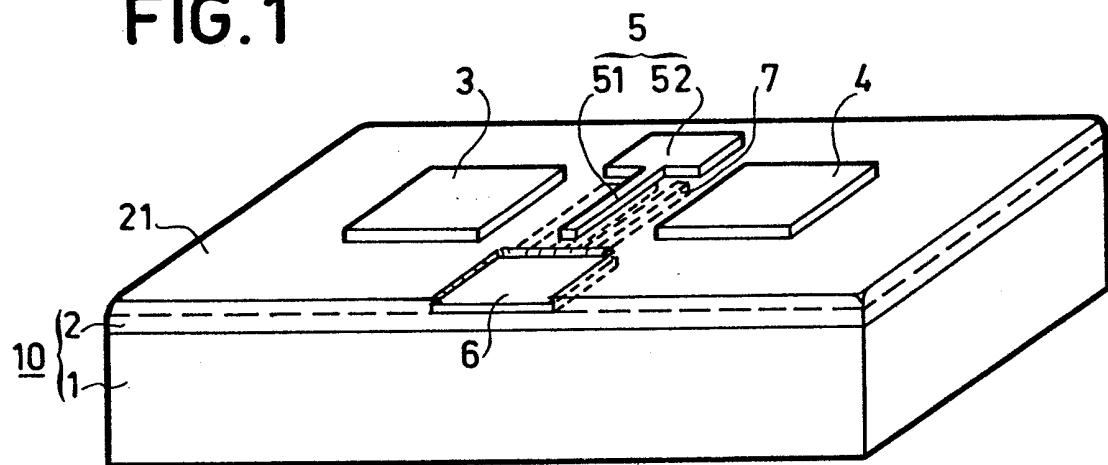

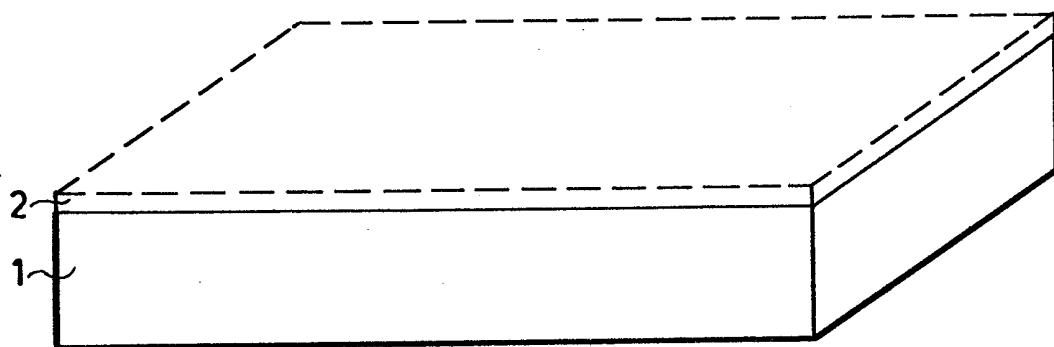

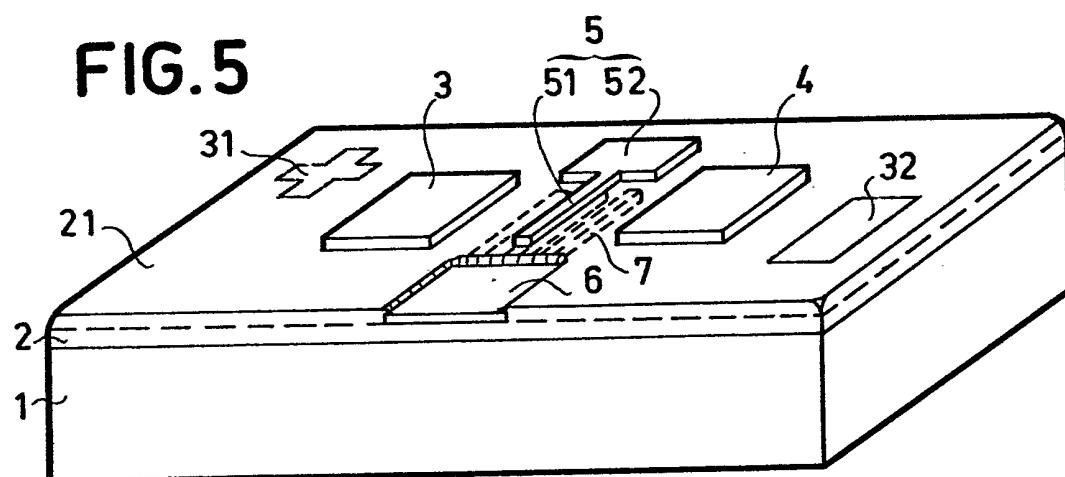

Les figures 2 à 5 représentent des étapes de fabrication de ce transistor.

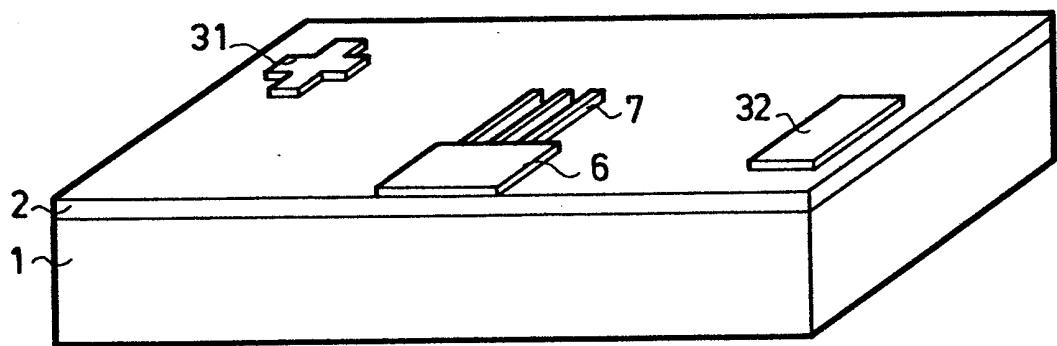

La figure 6 est une coupe transversale d'un transistor selon l'invention.

La plaquette ou fragment de plaquette semiconductrice 10, sur la figure 1, comporte un substrat 1 en matériau semiconducteur par exemple du type des composés III-V, soit, typiquement, l'arséniure de gallium. Une couche épitaxiale 2 de forte résistivité, est déposée sur le substrat 1 et supporte une électrode de grille constituée d'un plot 6 de raccordement et de barreaux ou doigts 7 en continuité métallique avec le plot 6, les barreaux étant parallèles et situés dans l'espace destiné à devenir l'intervalle source - drain du transistor.

Les dimensions du plot 6 sont, au minimum, de 50 microns sur 50 microns, et les doigts 7 ont une largeur d'environ 0,5 micron.

Sur la couche 2, on a fait croître par épitaxie une couche 21 de type n, dopée par exemple à  $10^{17}$  atomes d'impureté par centimètre cube. Dans le cas des dimensions indiquées pour le plot 6 et les doigts 7, seul le plot 6 n'est pas recouvert par la couche 21 qui présente par exemple 0,3 micron d'épaisseur.

Enfin le transistor comporte une source 3, une grille 5 et un drain 4, comme un transistor à effet de champ classique. La grille 5 comporte un doigt 51 et un plot de raccordement 52.

Pour fabriquer un transistor conforme à l'invention, on utilise un procédé comportant les étapes suivantes :

Dans une première étape, on dépose par épitaxie (figure 2) une couche monocristalline 2 sur un substrat 1, en matériau constitué par exemple par de l'arsénure de gallium de très grande résistivité, dit pour cette raison "semi-isolant", mais pouvant être aussi constitué par un autre composé III-V de très grande résistivité. Par épitaxie en phase gazeuse, par exemple, on fait croître le monocristal pour former une couche 2 de forte résistivité et d'épaisseur de l'ordre de 5 microns, par exemple en Ga As dopé n à  $10^{13} \text{ cm}^{-3}$ .

Dans une deuxième étape (figure 3), on réalise des dépôts en métal réfractaire, tel que le tungstène, d'une épaisseur de 500 à 1000 angströms selon des dessins prédéterminés, en procédant par masquage préalable et découpage du masque par photolithographie, pour obtenir, par exemple, un dépôt rectangulaire 6 de dimensions 50 par 50 microns. En outre on forme au moins un dépôt allongé 7 raccordé au dépôt 6 et formant un doigt de largeur 0,5 micron dont la longueur est égale à la "largeur" de grille à constituer pour la grille dite "supplémentaire". En outre, on forme deux repères 31 et 32 de dessins très différents, et de dimensions minimales égales à environ 15 à 20 microns dans les deux sens. Ces repères sont situés par exemple aux deux extrémités d'une diagonale du rectangle constitué par la surface supérieure du dispositif.

Dans une troisième étape (figure 4), on fait à nouveau croître le matériau par épitaxie de façon à constituer une couche 21 de même type de conductivité (n par exemple) que la couche 2 et de plus faible résistivité, par exemple en dopant l'arsénure de gallium à  $10^{17} \text{ atomes par cm}^3$ . La croissance du matériau ne peut se produire au moins au début de l'étape, à l'endroit même des métallisations. Mais lorsqu'une certaine épaisseur de couche épitaxiale est formée 3000 angströms par exemple, il se forme des ponts de matériaux, notamment par dessus les dépôts 7 de faible largeur (0,5 micron). Au contraire le dépôt 6 et les repères 31 et 32 demeurent en grande partie découverts laissant notamment accessible pour le raccordement électrique la grille dite supplémentaire.

Dans une quatrième étape (figure 5), à l'aide d'un masque obtenu par photolithographie, on forme, par dépôts successifs de métaux tels que le nickel, le germanium et l'or, des contacts ohmiques 3 et 4, dans des zones

prédéterminées située de part et d'autre de la région de grille du transistor à effet de champ, afin de réaliser les électrodes de source et de drain.

Dans une cinquième étape, (voir figure 5), on forme, par une méthode analogue à celle de l'étape précédente, mais en utilisant un métal de nature 5 à former un contact de type Schottky, par exemple de l'aluminium, un dépôt métallique comportant un plot 52 et un prolongement digital 51, recouvrant la grille enterrée (6,7).

Sur la figure 6, on a représenté le cas d'une grille enterrée à un seul barreau 7, situé au droit du doigt 51. On a tracé en trait interrompu les 10 limites des régions désertes  $Z_1$  et  $Z_2$  de la couche semiconductrice 21, au voisinage des doigts de grille 51 et 7, lorsque des potentiels égaux sont appliqués aux deux grilles. On voit que le canal conducteur du transistor à effet de champ présente un étranglement entre les deux grilles, ce qui présente des avantages certains, notamment celui de limiter la consom- 15 mation de courant circulant entre source et drain.

REVENDICATIONS

1. Transistor à effet de champ, d'un type comportant des électrodes de source, de grille et de drain disposées sensiblement sur une même face d'une plaquette semiconductrice, caractérisé en ce qu'il comporte en outre une électrode de grille supplémentaire accessible par la même face que les électrodes précédentes et constituées par au moins un barreau métallique noyé dans le matériau semiconducteur de la plaquette.

5

2. Transistor à effet de champ selon la revendication 1, caractérisé en ce que la grille supplémentaire comporte une partie non recouverte de matériau semiconducteur et un seul barreau métallique, la grille normale comportant un doigt disposé à la surface de la plaquette parallèlement audit barreau et au droit de celui-ci.

10

3. Transistor à effet de champ selon la revendication 2, caractérisé en ce qu'il comporte des repères métalliques situés à la même profondeur par rapport à la surface de la plaquette que la grille supplémentaire et présentant une partie dénudée.

15

4. Procédé de fabrication d'un transistor selon la revendication 1, caractérisé en ce qu'il comporte les étapes suivantes :

- a) formation d'une couche épitaxiale de forte résistivité sur une plaquette semiconductrice en matériau semiconducteur de forte résistivité ;

20

- b) réalisation, sur la couche formée à l'étape (a), de dépôts en métal réfractaire de très faible épaisseur, de façon à constituer la grille supplémentaire et deux repères de dessins différents ;

- c) formation d'une couche épitaxiale de faible résistivité par rapport à la couche formée à l'étape (a) et d'épaisseur assez faible pour recouvrir les parties étroites de la grille supplémentaire tout en laissant à nu au moins une partie de cette grille et des repères ;

25

- d) dépôt de contacts ohmiques de source et de drain ;

- e) dépôt d'une grille Schottky sur la couche épitaxiale formée à l'étape (c) au droit des parties noyées de la grille supplémentaire.

5. Procédé selon la revendication 4, caractérisé en ce que la plaquette semiconductrice est en arsénure de gallium semi-isolant, la couche épita-

xiale formée à l'étape (a) est dopée n à  $10^{13} \text{ cm}^{-3}$ , les dépôts réalisés à l'étape (b) sont en tungstène d'une épaisseur de 500 à 1000 angströms, et la couche épitaxiale formée à l'étape (c), est dopée n à  $10^{17} \text{ cm}^{-3}$ , et d'une épaisseur ne dépassant pas 3000 angströms.

1/2

**FIG.1****FIG.2****FIG.3**

2/2

**FIG. 4****FIG. 5****FIG. 6**