(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6039107号

(P6039107)

(45) 発行日 平成28年12月7日(2016.12.7)

(24) 登録日 平成28年11月11日(2016.11.11)

(51) Int.Cl.

F 1

|                      |                  |        |       |      |

|----------------------|------------------|--------|-------|------|

| <b>G06F 12/06</b>    | <b>(2006.01)</b> | GO6F   | 12/06 | 515H |

| <b>G06F 12/00</b>    | <b>(2006.01)</b> | GO6F   | 12/06 | 525C |

| <b>G 11 C 11/413</b> | <b>(2006.01)</b> | GO6F   | 12/00 | 550E |

|                      |                  | G 11 C | 11/34 | A    |

請求項の数 15 (全 21 頁)

(21) 出願番号 特願2015-551844 (P2015-551844)

(86) (22) 出願日 平成26年1月7日 (2014.1.7)

(65) 公表番号 特表2016-507826 (P2016-507826A)

(43) 公表日 平成28年3月10日 (2016.3.10)

(86) 國際出願番号 PCT/US2014/010546

(87) 國際公開番号 WO2014/110051

(87) 國際公開日 平成26年7月17日 (2014.7.17)

審査請求日 平成28年9月5日 (2016.9.5)

(31) 優先権主張番号 13/736,268

(32) 優先日 平成25年1月8日 (2013.1.8)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】 インテリジェントな電流／電力消費最小化を伴う、向上した動的メモリ管理

## (57) 【特許請求の範囲】

## 【請求項 1】

動的メモリ管理を実行する方法であって、

複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて低電力状態電流／電力消費を取得することと、

前記揮発性メモリデバイスの第1のセットから前記揮発性メモリデバイスの第2のセットにデータをコピーすることと、ここにおいて、揮発性メモリデバイスの前記第2のセットは、揮発性メモリデバイスの前記第1のセットよりも低い低電力状態電流／電力消費を有する、

電力消費を低減するために揮発性メモリデバイスの前記第1のセットをパワーダウン状態に置くことと 10

を備える方法。

## 【請求項 2】

ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの前記第1のセットを前記パワーダウン状態に切り替えるかを決定することをさらに備える、請求項1に記載の方法。

## 【請求項 3】

前記低電力状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせる、請求項1に記載の方法。 20

**【請求項 4】**

電力消費を低減するために揮発性メモリデバイスの前記第2のセットを電力節約状態に置くことをさらに備える、請求項1に記載の方法。

**【請求項 5】**

前記電力節約状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせる、請求項4に記載の方法。

**【請求項 6】**

前記低電力状態電流／電力消費は、漏れ電流／電力消費と、動的電力消費とを含む、請求項1に記載の方法。

10

**【請求項 7】**

前記メモリデバイス間の温度ばらつきを補償することと、

前記複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて前記低電力状態電流／電力消費を正規化することと

をさらに備える、請求項1に記載の方法。

**【請求項 8】**

前記揮発性メモリデバイスの前記第1のセットと、前記揮発性メモリデバイスの前記第2のセットとは、同じメモリバスチャネルに結合された、請求項1に記載の方法。

**【請求項 9】**

前記複数の揮発性メモリデバイスの各々の内の各メモリバンクについて低電力状態電流／電力消費を取得することと、

20

メモリデバイスの前記第2のセット中の同じメモリデバイス内でデータをメモリバンクの第1のセットからメモリバンクの第2のセットにコピーすることと、ここにおいて、メモリバンクの前記第2のセットは、メモリバンクの前記第1のセットよりも低い低電力状態電流／電力消費を有する、

メモリバンクの前記第1のセットをパワーダウン状態に置くことと

をさらに備える、請求項1に記載の方法。

**【請求項 10】**

複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて低電力状態電流／電力消費を取得するための手段と、

30

前記揮発性メモリデバイスの第1のセットから前記揮発性メモリデバイスの第2のセットにデータをコピーするための手段と、ここにおいて、揮発性メモリデバイスの前記第2のセットは、揮発性メモリデバイスの前記第1のセットよりも低い低電力状態電流／電力消費を有する、

電力消費を低減するために揮発性メモリデバイスの前記第1のセットをパワーダウン状態に置くための手段と

を備える電子デバイス。

**【請求項 11】**

ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの前記第1のセットを前記パワーダウン状態に切り替えるかを決定するための手段をさらに備える、および/または

40

前記低電力状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせる、請求項10に記載のデバイス。

**【請求項 12】**

処理回路は、

電力消費を低減するために揮発性メモリデバイスの前記第2のセットを電力節約状態に置くための手段をさらに構成され、好みしくは、

前記電力節約状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせ

50

る、請求項10に記載のデバイス。

【請求項13】

前記メモリデバイス間の温度ばらつきを補償するための手段と、

前記複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて前記低電力状態電流／電力消費を正規化するための手段と

をさらに備える、請求項10に記載のデバイス。

【請求項14】

前記複数の揮発性メモリデバイスの各々の内の各メモリバンクについて低電力状態電流／電力消費を取得するための手段と、

メモリデバイスの前記第2のセット中の同じメモリデバイス内でデータをメモリバンクの第1のセットからメモリバンクの第2のセットにコピーするための手段と、ここにおいて、メモリバンクの前記第2のセットは、メモリバンクの前記第1のセットよりも低い低電力状態電流／電力消費を有する、

メモリバンクの前記第1のセットをパワーダウン状態に置くための手段と

をさらに備える、請求項10に記載のデバイス。

【請求項15】

少なくとも1つのプロセッサによって実行されたとき、請求項1-10のいずれかの方法を実行することを前記少なくとも1つのプロセッサに行わせる、命令が記憶されたプロセッサ可読記憶媒体。

【発明の詳細な説明】

【技術分野】

【0001】

[0001]本開示は、動的メモリ管理(DMM)が実現されるメモリデバイスにおいて、電流／電力消費を低減または最小化することに関する。

【背景技術】

【0002】

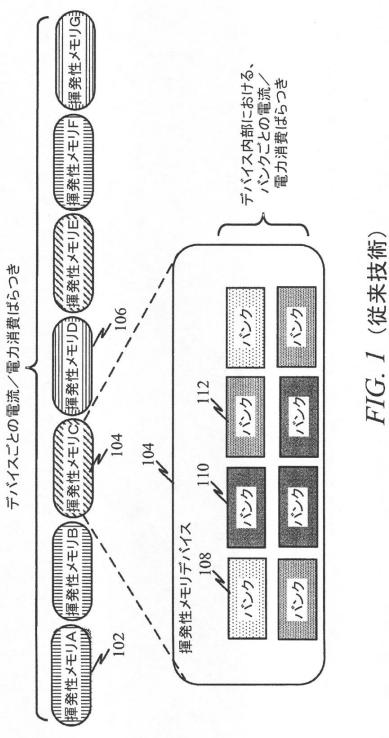

[0002]図1は、メモリデバイス間、ならびにメモリデバイス中のバンク間の、低電力状態電流／電力消費のばらつきを示す。一実施例では、複数の揮発性メモリデバイス102、104、および106、そのようなものはランダムアクセスメモリ(RAM)デバイス(たとえばRAM部品)が、より大きい回路または電子デバイスの一部として備わる場合がある。各揮発性メモリデバイス104は、たとえば単一のシリコンダイ内で、複数のメモリバンク108、110、および112として構成される場合がある。シリコン製造プロセスの性質のせいで、部品ごとの電力ばらつき(たとえば、デバイスごとの電力ばらつき)、および各メモリデバイス内のバンクごとの電力ばらつきがあることがある。すなわち、各揮発性メモリデバイスが、異なる低電力状態消費(たとえば、漏れ電流、動的電力消費など)を呈することがあり、各メモリバンクもまた、異なる低電力状態消費を呈することがある。

【0003】

[0003]いくつかの処理システムは、遊休時にいくつかのメモリデバイスの電力使用を低減することを含み得る電力管理または節約を実現しようと努める。動的メモリ管理(DMM)は、そのようなシステムの1つである。

【0004】

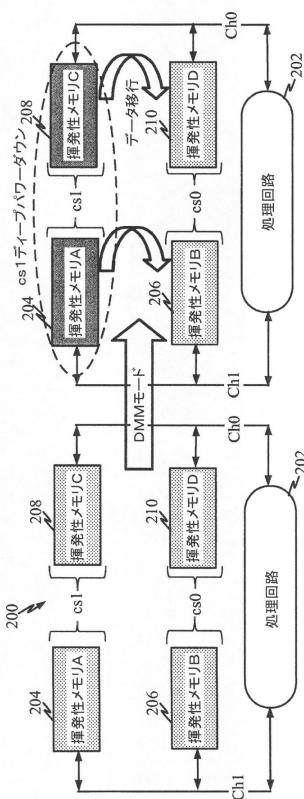

[0004]図2は、従来の動的メモリ管理(DMM)方式を示す。ここで、処理回路202は、デュアルチャネルCh0およびCh1(たとえば、チャネル0およびチャネル1)上で、複数の揮発性メモリデバイス204、206、208、210(たとえばRAM×32)に結合されてよい。長い遊休(たとえば、一晩中、鞄の中など)の期間中、利用可能な揮発性メモリは動的に低減される(たとえば遮断される)。上段の揮発性メモリデバイス204および208中のメモリページは、可能ならフラッシュされるか、そうでない場合は下段の揮発性メモリデバイス206および210に移行される。ここでは、DMMモードに入ったとき、データが、チップセレクト1(cs1)上の第1の複数の揮発性メモリ

10

20

30

40

50

リデバイス 204 および 208 から、チップセレクト 0 (cs0) 上の第 2 の複数の揮発性メモリデバイス 206 および 210 に移行されることを認識することができる。チップセレクト cs1 によって制御されるメモリデバイス（すなわち、上段の揮発性メモリデバイス 204 および 208）中に、アクティブなメモリページ（たとえば、メモリのブロックまたはセグメント）がなくなった後は、チップセレクト cs1 に結合されたこれらのメモリデバイス 204 および 208 は、ディープパワーダウン状態に遷移されて、電力が節約される。しかし、このアプローチは、パワーダウンされているメモリデバイス 204 および 208、ならびに / またはアクティブに維持されるメモリデバイス 206 および 210 の、効率（たとえば低電力状態電流）を考慮しない。

## 【0005】

10

[0005]したがって、従来の動的メモリ管理アプローチをさらに改善するために、揮発性メモリデバイスに対するより効率的な電力管理方法が必要とされている。

## 【発明の概要】

## 【0006】

[0006]複数の揮発性メモリデバイスと、処理回路とを備える、電子デバイス。処理回路は、動的メモリ管理を実行するように構成されてよい。複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて、低電力状態電流 / 電力消費が、取得、計算、または推定される。一実施例では、処理回路に結合された電力管理デバイスが、複数の揮発性メモリデバイスの各々についての低電力状態電流 / 電力消費を確認するように構成されてよい。次いで、データが揮発性メモリデバイスの第 1 のセットから揮発性メモリデバイスの第 2 のセットにコピーまたは転送されてよく、揮発性メモリデバイスの第 2 のセットは、揮発性メモリデバイスの第 1 のセットよりも低い低電力状態電流 / 電力消費を有する。次いで、揮発性メモリデバイスの第 1 のセットが電力消費を低減するためにパワーダウン状態に置かれてよい。

20

## 【0007】

[0007]同様に、揮発性メモリデバイスの第 2 のセットが電力消費を低減するために電力節約状態に置かれてよい。

## 【0008】

30

[0008]不揮発性記憶デバイスもまた処理回路に結合されてよく、この不揮発性記憶デバイスは、複数の揮発性メモリデバイスの各々についての低電力状態電流 / 電力消費を記憶する。

## 【0009】

[0009]低電力状態は、揮発性メモリデバイスの第 2 のセット中のデータを維持することができ、パワーダウン状態は、揮発性メモリデバイスの第 1 のセット中のデータを失わせる。電力節約状態は、揮発性メモリデバイスの第 2 のセット中のデータを維持することができ、パワーダウン状態は、揮発性メモリデバイスの第 1 のセット中のデータを失わせる。

## 【0010】

[0010]一実施例では、低電力状態は、電力節約状態であってよい。低電力状態電流 / 電力消費は、漏れ電流 / 電力消費と、動的電力消費とを含んでよい。

40

## 【0011】

[0011]一実施例では、処理回路は、ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの第 1 のセットをパワーダウン状態に切り替えるかを決定するように構成されてよい。

## 【0012】

[0012]複数の揮発性メモリデバイスは、1つまたは複数のチャネル中で構成されてよく、揮発性メモリデバイスの第 1 のセットおよび第 2 のセットは、チャネル単位で決定される。データは、同じチャネル中のメモリデバイス間でコピーされてよい。

## 【0013】

[0013]一実施例では、複数の揮発性メモリデバイスの各々についての低電力状態電流 /

50

電力消費は、製造段階の間または初期化段階の間に確認される。

**【0014】**

[0014]いくつかの実装形態では、処理回路は、(a)メモリデバイス間の温度ばらつきを補償すること、および/または(b)複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて低電力状態電流/電力消費を正規化すること、を行うようにさらに構成されてよい。

**【0015】**

[0015]別の様によれば、処理回路は、(a)複数の揮発性メモリデバイスのうちの各揮発性メモリデバイス内の各メモリバンクについて低電力状態電流/電力消費を取得すること、(b)メモリデバイスの第2のセット中の同じメモリデバイス内でデータをメモリバンクの第1のセットからメモリバンクの第2のセットにコピーすること、ここにおいて、メモリバンクの第2のセットがメモリバンクの第1のセットよりも低い低電力状態電流/電力消費を有する、および/または(c)メモリバンクの第1のセットをパワーダウン状態に置くこと、によって、動的メモリ管理を実行するようにさらに構成されてよい。

10

**【0016】**

[0016]同様に、動的メモリ管理を実行する方法が提供される。複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて、低電力状態電流/電力消費が取得される。次いで、データが揮発性メモリデバイスの第1のセットから揮発性メモリデバイスの第2のセットにコピーまたは転送され、揮発性メモリデバイスの第2のセットは、揮発性メモリデバイスの第1のセットよりも低い低電力状態電流/電力消費を有する。ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの第1のセットをパワーダウン状態に切り替えるかが決定されてよい。次いで、揮発性メモリデバイスの第1のセットが電力消費を低減するためにパワーダウン状態に置かれてよい。

20

**【0017】**

[0017]揮発性メモリデバイスの第2のセットが電力消費を低減するために電力節約状態に置かれてよい。

**【0018】**

[0018]一様によれば、複数の揮発性メモリデバイスの各々の内の各メモリバンクについて、低電力状態電流/電力消費が取得されてよい。次いで、メモリデバイスの第2のセット中の同じメモリデバイス内で、データがメモリバンクの第1のセットからメモリバンクの第2のセットにコピーされ、メモリバンクの第2のセットは、メモリバンクの第1のセットよりも低い低電力状態電流/電力消費を有する。次いで、メモリバンクの第1のセットはパワーダウン状態に置かれてよい。

30

**【0019】**

[0019]以下に示される詳細な説明が図面とともに読まれるとき、様々な特徴、性質、および利点が明らかになるであろう。図面全体を通して、同じ参照文字は対応するものを識別する。

**【図面の簡単な説明】**

**【0020】**

**【図1】** [0020]メモリデバイス間、ならびにメモリデバイス中のバンク間の、低電力状態電流/電力消費のばらつきを示す図。

40

**【図2】** [0021]従来の動的メモリ管理(DMM)方式を示す図。

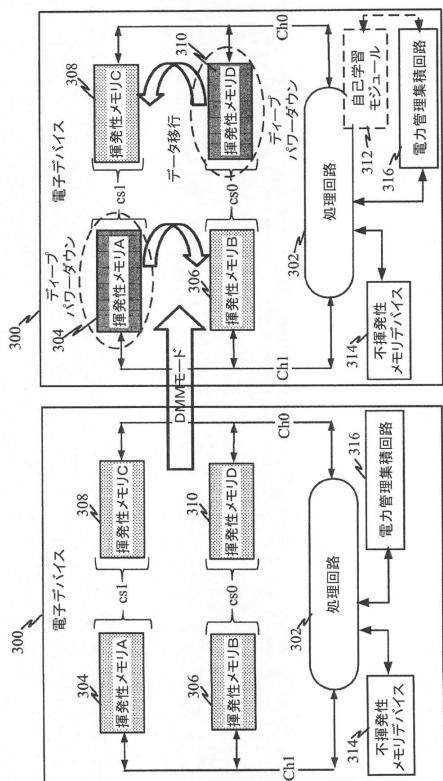

**【図3】** [0022]どのメモリデバイスがパワーダウンされることになるか、およびどのメモリデバイスが電力節約状態(たとえばセルフリフレッシュ状態)に置かれることが可能かを決定する際に、各メモリデバイスの全体的な低電力状態電流/電力消費が考慮される、第1の向上した動的メモリ管理技法を示す図。

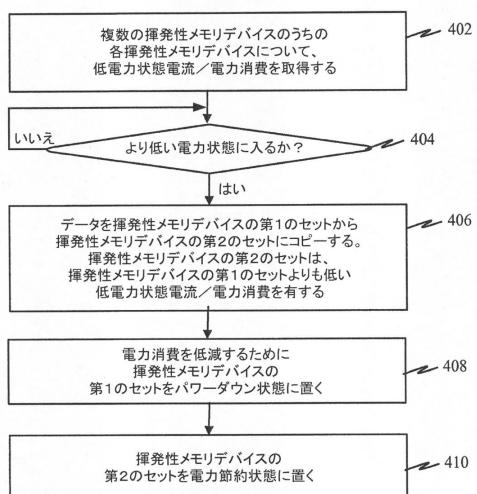

**【図4】** [0023]最高の低電力状態電流/電力消費を有する揮発性メモリデバイスよりも、最低の低電力状態電流/電力消費を有する揮発性メモリデバイスの方を選択することによって動的メモリ管理(DMM)を実行するための、処理回路によって実現される方法を示す図。

50

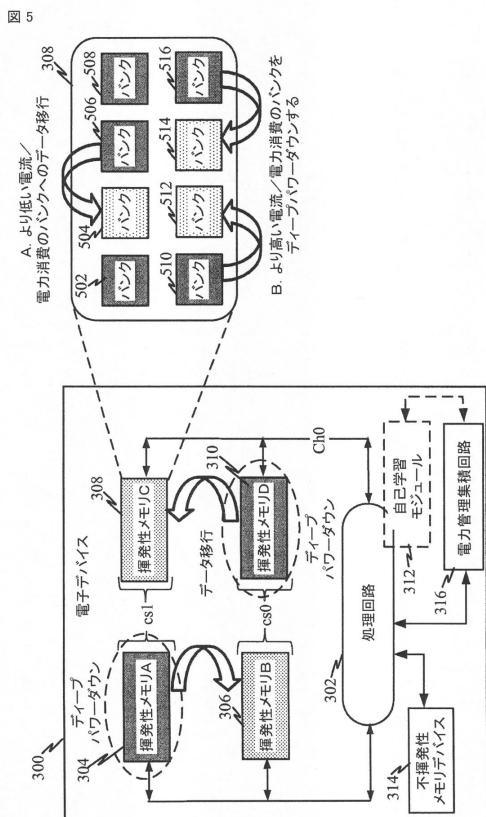

【図5】[0024]どのメモリバンクがパワーダウンされることになるか、およびどのメモリバンクが電力節約状態（たとえばセルフリフレッシュ状態）に置かれることが可能かを決定する際に、メモリデバイスの各バンクの低電力状態電流／電力消費が考慮される、第2の向上した動的メモリ管理技法を示す図。

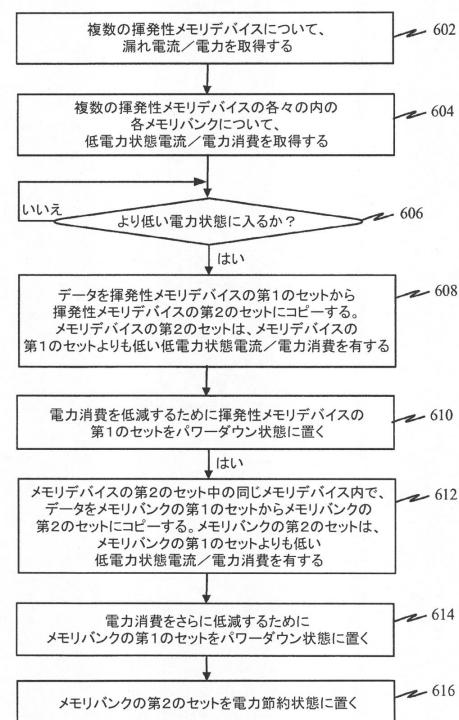

【図6】[0025]最低の低電力状態電流／電力消費を有するメモリバンクを選択することによって動的メモリ管理（DMM）を実行するための、処理回路によって実現される方法を示す図。

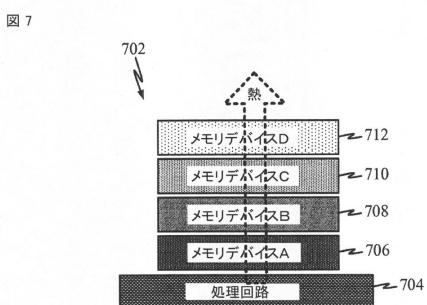

【図7】[0026]メモリデバイスおよび／またはバンクについての低電力状態電流／電力消費を測る際に、熱分散が考慮され得ることを示す図。

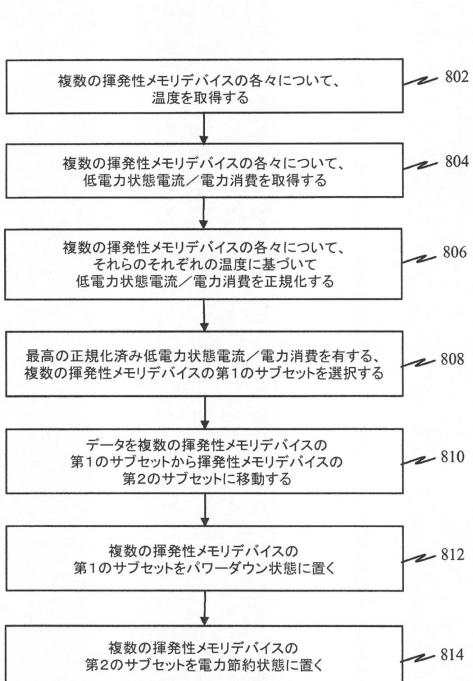

【図8】[0027]各メモリデバイスについての、および／または各メモリデバイス内の各メモリバンクについての低電力状態電流／電力消費がどのように確認され得るかについての実施例を示す図。 10

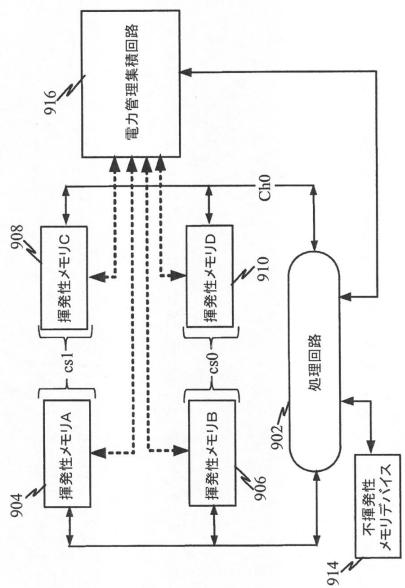

【図9】[0028]各メモリデバイスについての、および／または各メモリデバイス内の各メモリバンクについての低電力状態電流／電力消費がどのように確認され得るかについての実施例を示す図。

#### 【発明を実施するための形態】

##### 【0021】

[0029]以下の説明では、本開示の様々な態様の完全な理解をもたらすために、具体的な詳細が提供される。しかし、これらの具体的な詳細がなくてもこれらの態様が実践され得ることは、当業者には理解されるであろう。たとえば、態様を不必要に詳細にして不明瞭にするのを回避するために、回路がブロック図で示されることがある。他の事例では、本開示の態様を不明瞭にしないために、よく知られている回路、構造、および技法は詳細に図示されないことがある。 20

##### 【0022】

###### 概観

[0030]第1の向上した動的メモリ管理技法が提供されるが、この技法では、電力節約状態の間に各システムの中で最低の低電力状態電流／電力消費（たとえば、漏れ電流／電力消費、および／または動的消費）の揮発性メモリデバイスを決定および使用するためのメカニズムが、動的メモリ管理に追加される。電力節約状態に入る前に、システム中のメモリデバイスの、電流漏れ／電力特性、および／または動的電力消費特性が確認されてよい。次いで、電力節約状態に入ることが決定されると、データが、電流／電力消費のより大きい（たとえば特定のチャネル中で）メモリデバイスから、電流／電力消費のより低いメモリデバイスに移行される。 30

##### 【0023】

[0031]第2の向上した動的メモリ管理技法もまた提供されるが、この技法では、より低い電流／電力消費のメモリバンク（アクティブな揮発性メモリデバイス内の）が、動的メモリ管理の間に使用されるように選択される。電力節約状態に入る前に、システム中のいくつかまたはすべてのメモリデバイス中の各バンクの電流／電力消費特性が確認されてよい。次いで、電力節約状態に入ることが決定されると、1つまたは複数のメモリデバイスが、アクティブに留まるように選択される。選択された1つまたは複数のメモリデバイスの各々の内で、データが、電流／電力消費のより大きい（たとえば特定のチャネル中で）1つまたは複数のバンクから、電流／電力消費のより低い1つまたは複数のバンクに移行される。 40

##### 【0024】

メモリデバイスの電流／電力消費に基づく、第1の例示的な向上した動的メモリ管理技法

[0032]図3は、第1の向上した動的メモリ管理技法を示すが、この技法では、どのメモリデバイスがパワーダウンされることになるか、およびどのメモリデバイスが電力節約状態（たとえばセルフリフレッシュ状態）に置かれることが可能かを決定する際に、各メモリデバイスの全体的な低電力状態電流／電力消費が考慮される。そのような電力節約状態（たとえばセルフリフレッシュ状態）は、そのようなメモリデバイス中のデータを維持す 50

る（たとえば記憶されたままにする）のに十分な電力を使用する場合があることに留意されたい。対照的に、パワーダウン状態（たとえばパワーオフ状態）は、そのようなメモリデバイスに記憶されたデータを失わせる場合がある。この実施例では、電子デバイス 300（たとえば、デスクトップおよび／またはラップトップコンピュータ、ワイヤレス電話機、モバイル電話機、スマートフォン、ディジタルアシスタント、ディジタル音楽プレーヤ、ディジタルタブレット、パーソナルディジタルアシスタント、メモリモジュール、メモリサブシステム、メモリパッケージオンパッケージデバイスなど）が、処理回路 302（たとえばアプリケーションプロセッサ）と、1つまたは複数のメモリデバイス 304、306、308、および 310 を備えてよい。メモリデバイス 304、306、308、および 310 は、メモリバスに結合されてよく、メモリバスを介して処理回路 302 と通信する。メモリデバイス 304、306、308、および 310 はまた、メモリバス内の種々のチャネル（Ch0 および Ch1）中で構成されてよく、したがって、データが第 1 のチャネル（Ch0）または第 2 のチャネル（Ch1）上でメモリデバイスにルーティングされることが可能である。各メモリデバイス 304、306、308、および 310 は、チップセレクト（cs）線に結合されてよく、したがって、特定のチャネルに結合された個々のメモリデバイスが、選択および／または選択解除されることが可能である（たとえば、それにより、選択されたデバイスに対するデータ書き込みまたはデータ読み取りはできるが、選択解除されたデバイスからはできない）。

#### 【0025】

[0033] 処理回路 302 は、自己学習プロセスを実施するように適合されたソフトウェアおよび／またはハードウェアモジュール 312 を備えてよく、この自己学習プロセスにより、電流／電力消費特性が確認されるかまたは他の方法で取得される。たとえば、「確認」ステップでは、処理回路 302 および／またはソフトウェア／ハードウェアモジュール 312 は、本明細書で説明され、および／または図 4、6、8 に示される方法をたとえば使用して、漏れ電流／電力特性、および／または動的電流／電力特性を、計算、決定、および／または推定することができ、次いで、そのような漏れ電流／電力特性、および／または動的電流／電力特性を、メモリ（たとえば、揮発性または不揮発性メモリ）に記憶することができる。「取得」ステップでは、処理回路 302 および／またはソフトウェア／ハードウェアモジュール 312 は単に、たとえば「確認」ステップによってあらかじめメモリ（たとえば、揮発性または不揮発性メモリ）に記憶された漏れ電流／電力特性、および／または動的電流／電力特性を、読み取るかまたは取り出すだけでよい。漏れ電流／電力特性、および／または動的電流／電力特性を確認する一実施例では、処理回路 302 は、各メモリデバイスをオンにして、セルフリフレッシュモードにおけるそのメモリ電力を測定する（たとえば、セルフリフレッシュモードの間に各メモリデバイスによって消費された電流／電力を測定する）ことができる。この情報は、たとえば、不揮発性メモリデバイス 314（たとえば、電気的に消去可能プログラム可能な読み取り専用メモリまたは EEPROM（登録商標））に記録されてよい。一実施例では、生産の終わりに工場でメモリデバイスごとの電流／電力消費ばらつきの学習を行える 1 回限りのテストが実行されてよい。処理回路 302 および／または電力管理 IC（PMIC）316 に組み込まれた、自動化ソフトウェア／ハードウェアが、各メモリデバイス 304、306、308、および 310 の低電力状態電流／電力消費を確認するこれらの機能を実行することができる。さらに他の実装形態では、各メモリデバイスについての低電力状態電流／電力消費特性は、外部テストデバイスを使用して（たとえば、製造またはテスト段階の間に）確認され、次いで不揮発性メモリデバイス 314 に記憶されてよい。

#### 【0026】

[0034] 一実施例では、低電力状態電流／電力消費は、メモリデバイスが「セルフリフレッシュ」状態などの電力節約状態のときに、メモリデバイスの電力を測定することによって確認されてよい。この低電力状態の電力／電流消費は、漏れ電流／電力消費（たとえば、メモリデバイスもしくはセル中のトランジスタから漏れる電流）、および／または、動的電力消費（たとえば、メモリデバイスがほとんど常にスリープモードにある間に各メモリデバイスに記憶されたデータを失わせる場合がある）。この実施例では、電子デバイス 300 が、処理回路 302 と、1つまたは複数のメモリデバイス 304、306、308、および 310 を備えてよい。メモリデバイス 304、306、308、および 310 は、メモリバスに結合されてよく、メモリバスを介して処理回路 302 と通信する。メモリデバイス 304、306、308、および 310 はまた、メモリバス内の種々のチャネル（Ch0 および Ch1）中で構成されてよく、したがって、データが第 1 のチャネル（Ch0）または第 2 のチャネル（Ch1）上でメモリデバイスにルーティングされることが可能である。各メモリデバイス 304、306、308、および 310 は、チップセレクト（cs）線に結合されてよく、したがって、特定のチャネルに結合された個々のメモリデバイスが、選択および／または選択解除されることが可能である（たとえば、それにより、選択されたデバイスに対するデータ書き込みまたはデータ読み取りはできるが、選択解除されたデバイスからはできない）。

リアドレ스を定期的に読み取るメモリデバイス内部のコントローラによって消費される電力)の両方を含み得る。一実施例では、低電力状態は、メモリデバイスがその中に記憶されたデータを依然として保持することができる状態である場合がある。対照的に、パワーダウン状態(たとえばパワーオフ状態)は、そのようなメモリデバイスに記憶されたデータを失わせる場合がある。

#### 【0027】

[0035]処理回路302が第1の向上した動的メモリ管理モードに入ったとき、処理回路302は、データを、最高／最大の低電力状態電流／電力消費を有する揮発性メモリデバイス304および310から、最低の／より低い低電力状態電流／電力消費を有する揮発性メモリデバイス306および308に移行または移動する。データが移行された後、最高の／より高い電流／電力消費を有する揮発性メモリデバイス304および310は、オフにされるかまたはパワーダウン(たとえばパワーオフ)状態に置かれてよい。この実施例では、より低い低電力状態電流／電力消費の揮発性メモリデバイス308および306は、異なるチップセレクト線上にある。しかし、様々な構成で、より低い電流／電力消費の揮発性メモリデバイスは両方とも、同じチップセレクト線(たとえば、c<sub>s</sub>0もしくはc<sub>s</sub>1)に結合されてもよく、またはチップセレクト線c<sub>s</sub>0とc<sub>s</sub>1の両方の組合せに結合されてもよい。

#### 【0028】

[0036]図4は、最高の低電力状態電流／電力消費を有する揮発性メモリデバイスよりも、最低の低電力状態電流／電力消費を有する揮発性メモリデバイスの方を選択することによって動的メモリ管理(DMM)を実行するための、処理回路によって実現される方法を示す。複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて、低電力状態電流／電力消費が取得／確認される(402)。この、各揮発性メモリデバイスについての低電力状態電流／電力消費は、事前に確認されてもよい(たとえば、製造、テスト、または電源投入の段階で)。処理回路は、より低い電力状態に入るべき(たとえば、プロセッサが非アクティブであるなどのせいで)であるかどうか確認することができる(404)。入るべきである場合は、データが揮発性メモリデバイスの第1のセットから揮発性メモリデバイスの第2のセットに移行／コピーされ、揮発性メモリデバイスの第2のセットは、揮発性メモリデバイスの第1のセットよりも低い低電力状態電流／電力消費を有する(406)。すなわち、第2のセット中の個々の揮発性メモリデバイスは、第1のセット中の個々の揮発性メモリデバイスよりも低い低電力状態電流／電力消費を有するものとして、あらかじめ識別されている。次いで処理回路は、電力消費を低減するために揮発性メモリデバイスの第1のセットをパワーダウン状態(たとえばパワーオフ状態)に置くことができる(408)。第2のセット中の揮発性メモリデバイスの選択は、実装されているメモリ構造に部分的に依存することがある。たとえば、揮発性メモリデバイスがデュアルチャネルアーキテクチャで構成されている場合、各チャネルからの少なくとも1つのメモリデバイスが選択されなければならないであろう。したがって、揮発性メモリデバイスの第1のセットおよび揮発性メモリデバイスの第2のセットは、複数のメモリデバイスからチャネル単位で選択されてよい。たとえば、第1のチャネルについては、メモリデバイスの第2のセットは、メモリデバイスの第1のセットよりも低い低電力状態電流／電力消費を有し、この場合、すべてのメモリデバイスは第1のチャネルに結合されている。メモリデバイスの第2のセットはまた、電力節約状態(たとえばセルフリフレッシュモード)に置かれてよい(410)。そのような電力節約状態(たとえばセルフリフレッシュ状態)は、メモリデバイスのそのような第2のセット中のデータを維持する(たとえば記憶されたままにする)のに十分な電力を使用する場合がある。対照的に、パワーダウン状態は、メモリデバイスの第1のセットに記憶されたデータを失わせる場合がある。したがって、電力節約状態／モードは、パワーダウン状態(たとえばパワーオフ状態)よりも多くの電力を消費することがある。様々な実装形態で、メモリデバイスについての電流／電力消費が取得される低電力状態は、電力節約状態であってもよく、または異なる電力状態であってもよい。

10

20

30

40

50

## 【0029】

メモリデバイス内のメモリバンク電流 / 電力消費に基づく、第 2 の例示的な向上した動的メモリ管理技法

[0037] 図 5 は、第 2 の向上した動的メモリ管理技法を示すが、この技法では、どのメモリバンクがパワーダウンされることになるか、およびどのメモリバンクが電力節約状態（たとえばセルフリフレッシュ状態）に置かれることが可能かを決定する際に、メモリデバイスの各バンクの低電力状態電流 / 電力消費が考慮される。そのような電力節約状態（たとえばセルフリフレッシュ状態）は、そのようなメモリバンク中のデータを維持する（たとえば記憶されたままにする）のに十分な電力を使用する場合があることに留意されたい。対照的に、パワーダウン状態は、そのようなメモリバンクに記憶されたデータを失わせる場合がある。処理回路 302 中の自己学習モジュール 312 が自己学習プロセスを実施することができ、このプロセスで、自己学習モジュール 312 は、1つまたは複数のメモリデバイスについて、ならびに1つまたは複数のメモリデバイス 304、306、308、および 310 内のメモリバンク 502、504、506、508、510、512、514、および 516 について、バンクごとの低電力状態電流 / 電力消費ランキングまたはプロファイルを取得する。処理回路 302 が第 2 の向上した動的メモリ管理モードを開始したとき、データが、より高い電流 / 電力消費のメモリデバイスからより低い電流 / 電力消費のメモリデバイスに移行 / コピーされ、また、より低い電流 / 電力消費のメモリデバイス内で、より高い電流 / 電力消費のメモリバンクからより低い電流 / 電力消費のバンクに移行 / コピーされる。たとえば、揮発性メモリデバイス A304 および D310 からのデータが、揮発性メモリデバイス B306 および C308 にそれぞれ移行 / 移動され、揮発性メモリデバイス A304 および D310 は、パワーオフされるかまたは電力低下状態に置かれてよい。次いで、揮発性メモリデバイス B306 および C308 内で、より高い電流 / 電力消費のバンク 506、510、および 516 からのデータが、より低い電流 / 電力消費のバンク 504、512、および 514 にそれぞれ移行 / 転送される。次いで、より高い電流 / 電力消費のメモリバンクはオフにされて電力が節約されてよい。たとえば、より高い電流 / 電力消費のバンク 506、510、および 516 は、次いで、パワーオフされるかまたは電力低下状態に置かれてよい。一実施例では、最低必要セルフリフレッシュレートおよび / または電圧は、アクティブなメモリバンクに応じて異なるので、アクティブな / 選択されたメモリバンク（たとえば、より低い電流 / 電力消費のメモリバンク）のセルフリフレッシュレートおよび / または電圧が下げられてよい。すなわち、より高い電流 / 電力消費のメモリバンク 506、510、および 516 をオフにすることで、アクティブな / 選択されたメモリバンク 502、504、508、512、および 514 に対するセルフリフレッシュ期間を増大させることおよび / または電圧を下げることが許容される。

## 【0030】

[0038] 図 6 は、最低の低電力状態電流 / 電力消費を有するメモリバンクを選択することによって動的メモリ管理（DMM）を実行するための、処理回路によって実現される方法を示す。図 4 の方法と同様、この方法も、最低の低電力状態電流 / 電力消費を有するメモリデバイスを確認および選択する。複数の揮発性メモリデバイスについて、低電力状態電流 / 電力消費が取得 / 確認される（602）。追加で、各メモリデバイス内の各メモリバンクについての低電力状態電流 / 電力消費もまた取得 / 確認される（604）。この、各揮発性メモリデバイスについての低電力状態電流 / 電力消費は、事前に確認されてもよい（たとえば、製造、テスト、または電源投入の段階で）。いくつかの実装形態では、処理回路内の電力管理回路が、メモリデバイスについての電流および / または電力消費情報を取得 / 確認するステップを実行することができる。追加で、そのような低電力状態電流 / 電力消費情報は、処理回路に結合された不揮発性記憶デバイスにあらかじめ記憶されてもよい。

## 【0031】

[0039] 処理回路は、より低い電力状態に入るべき（たとえば、プロセッサが非アクティ

10

20

30

40

50

ブであるなどのせいで)であるかどうか確認することができる(606)。入るべきである場合は、データが揮発性メモリデバイスの第1のセットから揮発性メモリデバイスの第2のセットに移行/コピーされ、揮発性メモリデバイスの第2のセットは、揮発性メモリデバイスの第1のセットよりも低い低電力状態電流/電力消費を有する(608)。すなわち、第2のセット中の個々の揮発性メモリデバイスは、第1のセット中の個々の揮発性メモリデバイスよりも低い低電力状態電流/電力消費を有するものとして、あらかじめ識別されている。次いで処理回路は、電力消費を低減するために揮発性メモリデバイスの第1のセットをパワーダウン状態(たとえば、電力低下状態またはパワーオフ状態)に置くことができる(610)。

## 【0032】

10

[0040]最低の低電力状態電流/電力消費のメモリデバイスにデータが移行された後は、同じメモリデバイス内でデータがメモリバンクの第1のセットからメモリバンクの第2のセットにコピー/移行され、メモリバンクの第2のセットは、メモリバンクの第1のセットよりも低い低電力状態電流/電力消費を有する(612)。次いで、電力消費をさらに低減するためにメモリバンクの第1のセットはパワーダウン(たとえばパワーオフ)状態に置かれてよい(614)(たとえばディープパワーダウン状態)。

## 【0033】

20

[0041]いくつかの実装形態では、最低電力消費のメモリデバイスが識別された後は、これらの最低電力消費のメモリデバイスについてのバンク電力消費のみが、測定、推定、または確認されてよい。すなわち、パワーダウンされる(オフにされる)ことになるメモリデバイス中のバンクについての電力消費は、測定、推定、または確認される必要はない。

## 【0034】

[0042]追加で、別の様様によれば、パワーダウンされることになる揮発性メモリデバイスから、電力節約状態(たとえば、データが維持されるセルフリフレッシュ)に置かれることになる揮発性メモリデバイスにデータがコピーまたは転送されるとき、データは、最低電力のデバイスにコピーされた後でより高い電力のバンクからより低い電力のバンクに移動されるのではなく、最低電力のバンクに直接に転送されてもよい。

## 【0035】

30

[0043]メモリデバイスの第2のセットは、電力節約状態(たとえばセルフリフレッシュモード)に置かれてよい(616)。そのような電力節約状態(たとえばセルフリフレッシュ状態)は、メモリバンクのそのような第2のセット中のデータを維持する(たとえば記憶されたままにする)のに十分な電力を使用する場合がある。対照的に、パワーダウン状態は、メモリバンクの第1のセットに記憶されたデータを失わせる場合がある。したがって、電力節約状態/モードは、パワーダウン状態(たとえばパワーオフ状態)よりも多くの電力を消費することがある。

## 【0036】

メモリデバイス/バンクの電流/電力消費を確認するための考慮事項

[0044]図7は、メモリデバイスおよび/またはバンクについての低電力状態電流/電力消費を測る際に、熱分散が考慮され得ることを示す。いくつかのメモリデバイスは、1つまたは複数の温度センサを備えることがあり、それにより、処理回路はそれらの温度を確認することができる(たとえば、メモリデバイスのパッケージオンパッケージスタック全体にわたって)。

40

## 【0037】

[0045]この実施例では、電子デバイス702が処理回路704を備えてよく、処理回路704の上には、複数のメモリデバイス706、708、710、および712が積み重なっている。温度監視を使用して、メモリデバイスの電力消費の比較が同じ温度点で実行されるのを確実にすることができる。図示のように、処理回路704からの熱が、異なる複数のメモリデバイス706、708、710、712にわたって種々のレートで分散されることがあり、それにより、温度差が生み出され、デバイスの電力消費に影響を及ぼす可能性がある。たとえば、処理回路704に最も近いメモリデバイスA706は、処理回

50

路 7 0 4 から最も遠いメモリデバイス D 7 1 2 よりも熱くなることがある。したがって、一態様は、ほぼ同じ温度における各メモリデバイス 7 0 6、7 0 8、7 1 0、および 7 1 2 についての低電力状態電流 / 電力消費を確認しようと努めることができる。別の特徴では、各メモリデバイス 7 0 6、7 0 8、7 1 0、および 7 1 2 についての低電力状態電流 / 電力消費が温度が記録されてよく、次いで、どのメモリデバイスが最低の低電力状態電流 / 電力消費を有するかを決定する前に、各メモリデバイス 7 0 6、7 0 8、7 1 0、および 7 1 2 の低電力状態電流 / 電力消費が温度について正規化されてよい。

#### 【 0 0 3 8 】

[0046]図 8 は、様々な温度の複数のメモリデバイスについての低電力状態電流 / 電力消費を確認するための、処理回路中で動作する方法を示す。複数の揮発性メモリデバイスの各々について、温度が取得 / 確認されてよい(8 0 2)。複数の揮発性メモリデバイスの各々について、低電力状態電流 / 電力消費(たとえば、漏れ電流消費および / または動的電力消費)が取得 / 確認されてよい(8 0 4)。いくつかの実装形態では、各デバイスについて、低電力状態電流 / 電力消費と温度とが同時に取得されてもよい。このように、温度および低電力状態電流 / 電力消費がデバイスごとに取得されてよい。

10

#### 【 0 0 3 9 】

[0047]複数の揮発性メモリデバイスの各々について、それらのそれぞれの温度に基づいて低電力状態電流 / 電力消費が正規化されてよい(8 0 6)。最高の正規化済み低電力状態電流 / 電力消費を有する、複数の揮発性メモリデバイスの第 1 のサブセットが選択されてよい(8 0 8)。次いで、データが複数の揮発性メモリデバイスの第 1 のサブセットから揮発性メモリデバイスの第 2 のサブセットに移動、コピー、および / または移行されてよい(8 1 0)。次いで、複数の揮発性メモリデバイスの第 1 のサブセットがパワーダウン(たとえばパワーオフ)状態に置かれてよい(8 1 2)。追加で、複数の揮発性メモリデバイスの第 2 のサブセットが電力節約状態(たとえばセルフリフレッシュ状態)に置かれてよい。そのような電力節約状態(たとえばセルフリフレッシュ状態)は、メモリバンクのそのような第 2 のセット中のデータを維持する(たとえば記憶されたままにする)のに十分な電力を使用する場合がある。対照的に、パワーダウン状態は、メモリバンクの第 1 のセットに記憶されたデータを失わせる場合がある。したがって、電力節約状態 / モードは、パワーダウン状態(たとえばパワーオフ状態)よりも多くの電力を消費することができる。いくつかの実装形態では、処理回路内の電力管理回路が、メモリデバイスについての電流 / 電力消費情報を取得 / 確認するステップを実行することができる。

20

#### 【 0 0 4 0 】

[0048]代替実装形態では、最低の正規化済み低電力状態電流 / 電力消費を有する、複数の揮発性メモリデバイスの第 2 のサブセットが選択されてよい。次いで、データが複数の揮発性メモリデバイスの第 1 のサブセットから揮発性メモリデバイスの第 2 のサブセットに移動、コピー、および / または移行されてよい。

30

#### 【 0 0 4 1 】

[0049]図 9 は、各メモリデバイスについての、および / または各メモリデバイス内の各メモリバンクについての低電力状態電流 / 電力消費がどのように確認され得るかについての実施例を示す。自己学習プロセスの間(たとえば、製造、初期化、またはブートアップ段階の間)に、処理回路 9 0 2 が、各メモリデバイス 9 0 4、9 0 6、9 0 8、および 9 1 0(たとえば RAM × 3 2)を 1 つずつオンにして、そのメモリデバイスについての低電力状態電流 / 電力消費を評価することができる。この低電力状態電流 / 電力消費は、いくつかの方法で確認されることが可能である。第 1 の実施例では、電力管理集積回路 9 1 6(PMIC)の一部である電流感知回路が、この目的で使用されてよい。このアプローチが使用される場合、PMIC 9 1 6 と処理回路 9 0 2 とが通信して、メモリデバイス測定結果(たとえば低電力状態電流 / 電力消費特性)を処理回路 9 0 2 に報告することができる。第 2 の実施例では、生産プロセスの間に、内蔵の感知抵抗器が、外部プローブ / ツールとともに使用されてよい。このアプローチが使用される場合、外部ツールは、メモリデバイス測定結果(たとえば低電力状態電流 / 電力消費特性)を、外部コネクタまたはイ

40

50

ンターフェースによって処理回路 902 に送ることができる。

#### 【0042】

[0050] 処理回路 902 は、メモリデバイス低電力状態電流 / 電力消費比較テーブルを、不揮発性メモリデバイス 914（たとえば、EEPROM または不揮発性メモリ）中で維持することができる。デュアルチャネルメモリアーキテクチャの場合、動的メモリ管理の間にメモリ内容を維持するのに使用されることになるデフォルトメモリデバイスとして、2 つの最低低電力状態電流 / 電力消費のメモリデバイスが設定されてよい。

#### 【0043】

[0051] バンクごとの電力ゲーティングが利用可能な場合（たとえば、個々のメモリバンクがパワーオフされることが可能な場合）、各バンクを 1 つずつオンにすることによって、自己学習プロセスの間に各メモリバンクについて低電力状態電流 / 電力消費情報が同様に取得されてよい。10

#### 【0044】

[0052] 各図に示される構成要素、ステップ、特徴、および / もしくは機能のうちの 1 つもしくは複数は、単一の構成要素、ステップ、特徴、もしくは機能に再構成および / もしくは結合されてもよく、または複数の構成要素、ステップ、もしくは機能において具体化されてもよい。本明細書に開示される新規な特徴を逸脱することなく、追加の要素、構成要素、ステップ、および / または機能が加えられてもよい。各図に示される装置、デバイス、および / または構成要素は、各図で説明される方法、特徴、またはステップのうちの 1 つまたは複数を実行するように構成され得る。本明細書で説明される新規なアルゴリズムもまた、効率的にソフトウェアにおいて実現されることおよび / またはハードウェアに組み込まれることが可能である。20

#### 【0045】

[0053] また、実施形態は、フローチャート、流れ図、構造図、またはブロック図として描かれるプロセスとして説明される場合があることにも留意されたい。フローチャートは動作を連続的なプロセスとして記述する場合があるが、動作の多くは、並行してまたは同時に実行されることも可能である。加えて、動作の順序は再構成され得る。プロセスは、その動作が完了したときに終了する。プロセスは、メソッド、関数、プロシージャ、サブルーチン、サブプログラムなどに対応する場合がある。プロセスが関数に対応するとき、その終了は、関数が呼出し元関数またはメイン関数に戻ることに対応する。30

#### 【0046】

[0054] さらに、記憶媒体は、データを記憶するための 1 つまたは複数のデバイスを表す場合があり、これらのデバイスは、読み専用メモリ (ROM)、ランダムアクセスメモリ (RAM)、磁気ディスク記憶媒体、光学記憶媒体、フラッシュメモリデバイス、ならびに / または、情報を記憶するための他の機械可読媒体、プロセッサ可読媒体、および / もしくはコンピュータ可読媒体を含む。「機械可読媒体」、「コンピュータ可読媒体」、および / または「プロセッサ可読媒体」という用語は、以下のものに限定されないが、命令および / またはデータを記憶、収録、または搬送することのできる、持運び可能なまたは固定の記憶デバイス、光学記憶デバイス、および他の様々な媒体などの、非一時的な媒体を含む。よって、本明細書で説明される様々な方法は、「機械可読媒体」、「コンピュータ可読媒体」、および / または「プロセッサ可読媒体」に記憶されて 1 つまたは複数のプロセッサ、マシン、および / またはデバイスによって実行されることが可能な命令および / またはデータによって、完全にまたは部分的に実現され得る。40

#### 【0047】

[0055] さらに、実施形態は、ハードウェア、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、またはこれらの任意の組合せによって実現され得る。ソフトウェア、ファームウェア、ミドルウェア、またはマイクロコードにおいて実現されるときは、必要なタスクを実行するためのプログラムコードまたはコードセグメントは、記憶媒体や他の記憶装置など、機械可読媒体に記憶され得る。プロセッサが、必要なタスクを実行することができる。コードセグメントは、プロシージャ、関数、サブプログラム、プログラ50

ム、ルーチン、サブルーチン、モジュール、ソフトウェアパッケージ、クラス、または、命令もしくはデータ構造もしくはプログラムステートメントの任意の組合せ、を表す場合がある。コードセグメントは、情報、データ、引数、パラメータ、またはメモリ内容の引渡しおよび／または受領によって、別のコードセグメントまたはハードウェア回路に結合される場合がある。情報、引数、パラメータ、データなどは、メモリ共有、メッセージ引渡し、トークン引渡し、ネットワーク送信など、任意の適切な手段を介して、引渡し、転送、または送信されることが可能である。

#### 【 0 0 4 8 】

[0056]本明細書に開示される例との関連で説明される様々な例示的な論理ブロック、モジュール、回路、要素、および／または構成要素は、本明細書で説明される機能を実行するように設計された、汎用プロセッサ、デジタル信号プロセッサ（D S P）、特定用途向け集積回路（A S I C）、フィールドプログラマブルゲートアレイ（F P G A）もしくは他のプログラム可能ロジック構成要素、ディスクリートゲートもしくはトランジスタロジック、ディスクリートハードウェア構成要素、またはこれらの任意の組合せを用いて、実現または実行され得る。汎用プロセッサはマイクロプロセッサであってよいが、代替として、プロセッサは、任意の従来型プロセッサ、コントローラ、マイクロコントローラ、または状態機械であってもよい。プロセッサはまた、計算構成要素の組合せ、たとえば、D S Pとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、D S Pコアと併用される1つもしくは複数のマイクロプロセッサ、または他の任意のそのような構成として実現され得る。10

#### 【 0 0 4 9 】

[0057]本明細書に開示される実施例に関連して説明される方法またはアルゴリズムは、ハードウェアにおいて直接に、またはプロセッサによって実行可能なソフトウェアモジュールにおいて、または両方の組合せにおいて、処理ユニット、プログラミング命令、または他の指令の形で具体化されてよく、単一のデバイスに含まれても複数のデバイスにわたって分散されてもよい。ソフトウェアモジュールは、R A Mメモリ、フラッシュメモリ、R O Mメモリ、E P R O Mメモリ、E E P R O Mメモリ、レジスタ、ハードディスク、取り外し可能ディスク、C D - R O M、または当技術分野で知られている他の任意の形の記憶媒体の中に存在し得る。記憶媒体はプロセッサに結合されてよく、それにより、プロセッサは記憶媒体に対して情報を読み書きすることができる。代替として、記憶媒体はプロセッサに統合されてもよい。20

#### 【 0 0 5 0 】

[0058]本明細書に開示される実施形態に関連して説明される様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実現され得ることは、当業者ならさらに理解するであろう。このハードウェアとソフトウェアの交換可能性をはっきりと例示するために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップが、一般にそれらの機能の点から上述された。そのような機能がハードウェアとして実現されるかソフトウェアとして実現されるかは、特定の適用例と、システム全体に課される設計制約とに依存する。30

#### 【 0 0 5 1 】

[0059]本明細書で説明される本発明の様々な特徴は、本発明を逸脱することなく種々のシステム中で実現され得る。前述の実施形態は例にすぎず、本発明を限定するものとして解釈されるべきではないことに留意されたい。実施形態の説明は、例示的なものとし、特許請求の範囲を限定するものとはしない。したがって、本教示は、他のタイプの装置にも容易に適用されることが可能であり、当業者には多くの代替、修正、および変形が明らかであろう。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

#### 【 C 1 】

複数の揮発性メモリデバイスと、

10

20

30

40

50

- 前記複数の揮発性メモリデバイスに結合された処理回路と

を備える電子デバイスであって、前記処理回路は、

- 前記複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて低電力状態

電流 / 電力消費を取得することと、

- 前記揮発性メモリデバイスの第1のセットから前記揮発性メモリデバイスの第2のセッ

トにデータをコピーすることと、ここにおいて、揮発性メモリデバイスの前記第2のセッ

トは、揮発性メモリデバイスの前記第1のセットよりも低い低電力状態電流 / 電力消費を

有する、

- 電力消費を低減するために揮発性メモリデバイスの前記第1のセットをパワーダウン状

態に置くことと、によって動的メモリ管理を実行するように構成された、電子デバイス。

- [C 2] 10

- 前記処理回路は、

- ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの前記第1のセットを

前記パワーダウン状態に切り替えるかを決定するようにさらに構成された、C 1に記載の

デバイス。

- [C 3]

- 前記低電力状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前

記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせる

、C 1に記載のデバイス。

- [C 4] 20

- 前記処理回路は、

- 電力消費を低減するために揮発性メモリデバイスの前記第2のセットを電力節約状態に

置くようにさらに構成された、C 1に記載のデバイス。

- [C 5]

- 前記電力節約状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、

前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせ

る、C 4に記載のデバイス。

- [C 6]

- 前記低電力状態は前記電力節約状態である、C 4に記載のデバイス。

- [C 7] 30

- 前記低電力状態電流 / 電力消費は、漏れ電流 / 電力消費と、動的電力消費とを含む、C

1に記載のデバイス。

- [C 8]

- 前記複数の揮発性メモリデバイスは1つまたは複数のチャネル中で構成され、揮発性メ

モリデバイスの前記第1のセットおよび第2のセットはチャネル単位で決定される、C 1

に記載のデバイス。

- [C 9]

- 前記データは同じチャネル中のメモリデバイス間でコピーされる、C 8に記載のデバイ

ス。

- [C 10] 40

- 前記複数の揮発性メモリデバイスの各々についての前記低電力状態電流 / 電力消費は、

製造段階の間または初期化段階の間に確認される、C 1に記載のデバイス。

- [C 11]

- 前記処理回路に結合され、前記複数の揮発性メモリデバイスの各々についての前記低電

力状態電流 / 電力消費を確認するように構成された電力管理デバイスをさらに備える、C

1に記載のデバイス。

- [C 12]

- 前記処理回路は、

- 前記メモリデバイス間の温度ばらつきを補償することと、

- 前記複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて前

- 50

記低電力状態電流 / 電力消費を正規化することと、を行うようにさらに構成された、 C 1 に記載のデバイス。

[ C 1 3 ]

前記処理回路に結合された不揮発性記憶デバイスをさらに備え、前記不揮発性記憶デバイスは、前記複数の揮発性メモリデバイスの各々についての前記低電力状態電流 / 電力消費を記憶する、 C 1 に記載のデバイス。

[ C 1 4 ]

前記処理回路は、

前記複数の揮発性メモリデバイスのうちの各揮発性メモリデバイス内の各メモリバンクについて低電力状態電流 / 電力消費を取得することと、

10

メモリデバイスの前記第 2 のセット中の同じメモリデバイス内でデータをメモリバンクの第 1 のセットからメモリバンクの第 2 のセットにコピーすることと、ここにおいて、メモリバンクの前記第 2 のセットは、メモリバンクの前記第 1 のセットよりも低い低電力状態電流 / 電力消費を有する、

メモリバンクの前記第 1 のセットをパワーダウン状態に置くことと、によって動的メモリ管理を実行するようにさらに構成された、 C 1 に記載のデバイス。

[ C 1 5 ]

動的メモリ管理を実行する方法であって、

複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて低電力状態電流 / 電力消費を取得することと、

20

前記揮発性メモリデバイスの第 1 のセットから前記揮発性メモリデバイスの第 2 のセットにデータをコピーすることと、ここにおいて、揮発性メモリデバイスの前記第 2 のセットは、揮発性メモリデバイスの前記第 1 のセットよりも低い低電力状態電流 / 電力消費を有する、

電力消費を低減するために揮発性メモリデバイスの前記第 1 のセットをパワーダウン状態に置くことと

を備える方法。

[ C 1 6 ]

ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの前記第 1 のセットを前記パワーダウン状態に切り替えるかを決定することをさらに備える、 C 1 5 に記載の方法。

30

[ C 1 7 ]

前記低電力状態は、揮発性メモリデバイスの前記第 2 のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第 1 のセット中のデータを失わせる、 C 1 5 に記載の方法。

[ C 1 8 ]

電力消費を低減するために揮発性メモリデバイスの前記第 2 のセットを電力節約状態に置くことをさらに備える、 C 1 5 に記載の方法。

[ C 1 9 ]

前記電力節約状態は、揮発性メモリデバイスの前記第 2 のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第 1 のセット中のデータを失わせる、 C 1 8 に記載の方法。

40

[ C 2 0 ]

前記低電力状態電流 / 電力消費は、漏れ電流 / 電力消費と、動的電力消費とを含む、 C 1 5 に記載の方法。

[ C 2 1 ]

前記メモリデバイス間の温度ばらつきを補償することと、

前記複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて前記低電力状態電流 / 電力消費を正規化することと

をさらに備える、 C 1 5 に記載の方法。

50

## [ C 2 2 ]

前記揮発性メモリデバイスの前記第1のセットと、前記揮発性メモリデバイスの前記第2のセットとは、同じメモリバスチャネルに結合された、C 1 5に記載の方法。

## [ C 2 3 ]

前記複数の揮発性メモリデバイスの各々の内の各メモリバンクについて低電力状態電流 / 電力消費を取得することと、

メモリデバイスの前記第2のセット中の同じメモリデバイス内でデータをメモリバンクの第1のセットからメモリバンクの第2のセットにコピーすることと、ここにおいて、メモリバンクの前記第2のセットは、メモリバンクの前記第1のセットよりも低い低電力状態電流 / 電力消費を有する、

10

メモリバンクの前記第1のセットをパワーダウン状態に置くことと

をさらに備える、C 1 5に記載の方法。

## [ C 2 4 ]

複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて低電力状態電流 / 電力消費を取得するための手段と、

前記揮発性メモリデバイスの第1のセットから前記揮発性メモリデバイスの第2のセットにデータをコピーするための手段と、ここにおいて、揮発性メモリデバイスの前記第2のセットは、揮発性メモリデバイスの前記第1のセットよりも低い低電力状態電流 / 電力消費を有する、

電力消費を低減するために揮発性メモリデバイスの前記第1のセットをパワーダウン状態に置くための手段と、

を備える電子デバイス。

20

## [ C 2 5 ]

ある期間にわたる非アクティブの後でいつ揮発性メモリデバイスの前記第1のセットを前記パワーダウン状態に切り替えるかを決定するための手段をさらに備える、C 2 4に記載のデバイス。

## [ C 2 6 ]

前記低電力状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせる、C 2 4に記載のデバイス。

30

## [ C 2 7 ]

前記処理回路は、

電力消費を低減するために揮発性メモリデバイスの前記第2のセットを電力節約状態に置くための手段をさらに構成された、C 1に記載のデバイス。

## [ C 2 8 ]

前記電力節約状態は、揮発性メモリデバイスの前記第2のセット中のデータを維持し、前記パワーダウン状態は、揮発性メモリデバイスの前記第1のセット中のデータを失わせる、C 2 7に記載のデバイス。

## [ C 2 9 ]

前記メモリデバイス間の温度ばらつきを補償するための手段と、

40

前記複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて前記低電力状態電流 / 電力消費を正規化するための手段と、

をさらに備える、C 2 4に記載のデバイス。

## [ C 3 0 ]

前記複数の揮発性メモリデバイスの各々の内の各メモリバンクについて低電力状態電流 / 電力消費を取得するための手段と、

メモリデバイスの前記第2のセット中の同じメモリデバイス内でデータをメモリバンクの第1のセットからメモリバンクの第2のセットにコピーするための手段と、ここにおいて、メモリバンクの前記第2のセットは、メモリバンクの前記第1のセットよりも低い低電力状態電流 / 電力消費を有する、

50

メモリバンクの前記第1のセットをパワーダウン状態に置くための手段と

をさらに備える、C 2 4に記載のデバイス。

[ C 3 1 ]

命令が記憶されたプロセッサ可読記憶媒体であって、少なくとも1つのプロセッサによ

つて実行されたとき、

複数の揮発性メモリデバイスのうちの各揮発性メモリデバイスについて低電力状態電流

/ 電力消費を取得することと、

前記揮発性メモリデバイスの第1のセットから前記揮発性メモリデバイスの第2のセッ

トにデータをコピーすることと、ここにおいて、揮発性メモリデバイスの前記第2のセッ

トは、揮発性メモリデバイスの前記第1のセットよりも低い低電力状態電流 / 電力消費を

有する、

10

電力消費を低減するために揮発性メモリデバイスの前記第1のセットをパワーダウン状

態に置くことと、を前記少なくとも1つのプロセッサに行わせる、プロセッサ可読記憶媒

体。

[ C 3 2 ]

前記少なくとも1つのプロセッサによって実行されたとき、

前記メモリデバイス間の温度ばらつきを補償することと、

前記複数の揮発性メモリデバイスの各々について、それらに対応する温度に基づいて前

記低電力状態電流 / 電力消費を正規化することと、を前記少なくとも1つのプロセッサに

さらに行わせる、C 3 1に記載の機械可読記憶媒体。

20

[ C 3 3 ]

前記少なくとも1つのプロセッサによって実行されたとき、

前記複数の揮発性メモリデバイスの各々の内の各メモリバンクについて低電力状態電流

/ 電力消費を取得することと、

メモリデバイスの前記第2のセット中の同じメモリデバイス内でデータをメモリバンク

の第1のセットからメモリバンクの第2のセットにコピーすることと、ここにおいて、メ

モリバンクの前記第2のセットは、メモリバンクの前記第1のセットよりも低い低電力状

態電流 / 電力消費を有する、

メモリバンクの前記第1のセットをパワーダウン状態に置くことと、を前記少なくとも

1つのプロセッサにさらに行わせる、C 3 1に記載の機械可読記憶媒体。

30

【 四 1 】

图 1

FIG. 1 (従来技術)

【図2】

2

FIG. 2 (従来技術)

( 3 )

3

FIG. 3

( 4 )

図 4

FIG. 4

【図5】

【図6】

FIG. 5

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

図9

FIG. 9

---

フロントページの続き

(72)発明者 パク、ヘ・ジュン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ホフマン、リチャード・ジェラルド

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 リ、ヨン・ジュ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 後藤 彰

(56)参考文献 特表2016-500186(JP,A)

特開2014-81688(JP,A)

特開2013-250791(JP,A)

米国特許出願公開第2008/0040563(US,A1)

米国特許出願公開第2011/0252180(US,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00

G06F 12/06

G11C 11/413