(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6600318号

(P6600318)

(45) 発行日 令和1年10月30日 (2019.10.30)

(24) 登録日 令和1年10月11日 (2019.10.11)

(51) Int.Cl.

F 1

|             |           |            |       |   |

|-------------|-----------|------------|-------|---|

| HO1L 21/822 | (2006.01) | HO1L 27/04 | 27/04 | R |

| HO1L 27/04  | (2006.01) | HO1L       | 21/90 | C |

| HO1L 21/768 | (2006.01) | HO1L       | 21/88 | K |

| HO1L 21/321 | (2006.01) | HO1L       | 27/04 | A |

| HO1L 21/76  | (2006.01) | HO1L       | 27/04 | P |

請求項の数 20 (全 24 頁) 最終頁に続く

(21) 出願番号 特願2016-569994 (P2016-569994)

(86) (22) 出願日 平成27年5月27日 (2015.5.27)

(65) 公表番号 特表2017-517154 (P2017-517154A)

(43) 公表日 平成29年6月22日 (2017.6.22)

(86) 國際出願番号 PCT/US2015/032690

(87) 國際公開番号 WO2015/183964

(87) 國際公開日 平成27年12月3日 (2015.12.3)

審査請求日 平成30年5月10日 (2018.5.10)

(31) 優先権主張番号 14/287,434

(32) 優先日 平成26年5月27日 (2014.5.27)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ合同会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】ウェルレジスタ及びポリシリコンレジスタ

## (57) 【特許請求の範囲】

## 【請求項1】

集積回路であって、

頂部表面に半導体材料を含む基板と、

前記基板の前記頂部表面に配置される、シャロートレンチアイソレーション(STI)プロセスによって形成されるフィールド酸化物と、

前記フィールド酸化物の下の前記半導体材料に配置されるウェルレジスタと、

前記ウェルレジスタの端部に近接して前記フィールド酸化物を介して配置されるレジスタヘッドアクティブエリアと、

前記ウェルレジスタのためのエリアにおいて前記フィールド酸化物を介して配置されるレジスタダミーアクティブエリアであって、前記基板の上に電気的接続がなく、10%～80%の密度を有する、前記レジスタダミーアクティブエリアと、

を含む、集積回路。

## 【請求項2】

請求項1に記載の集積回路であって、

前記レジスタダミーアクティブエリアが20%～50%の密度を有する、集積回路。

## 【請求項3】

請求項1に記載の集積回路であって、

前記レジスタダミーアクティブエリアにおける重くドープされたダミー拡散された領域であって、前記ウェルレジスタにおける平均ドーピング密度の少なくとも10倍の平均ド

10

20

ーピング密度を有する、前記重くドープされたダミー拡散された領域を更に含む、集積回路。

**【請求項 4】**

請求項 3 に記載の集積回路であって、

前記重くドープされたダミー拡散された領域が、前記ウェルレジスタと同じ導電型を有する、集積回路。

**【請求項 5】**

請求項 1 に記載の集積回路であって、

前記レジスタヘッドアクティブエリアと前記レジスタダミーアクティブエリアとの頂部表面上の金属シリサイド層を更に含む、集積回路。

10

**【請求項 6】**

請求項 1 に記載の集積回路であって、

前記レジスタダミーアクティブエリアが複数の矩形として構成され、そのため、前記矩形の各々が、前記ウェルレジスター一方の側の付近から前記ウェルレジスタの反対側の付近まで延在する、集積回路。

**【請求項 7】**

集積回路を形成する方法であって、

頂部表面に半導体材料を含む基板を提供することと、

前記基板の上に化学機械研磨 (C M P) ストップ層を形成することと、

前記 C M P ストップ層の上に S T I マスクを形成することであって、前記 S T I マスクが前記集積回路のアクティブエリアのためのエリアを覆い、前記アクティブエリアが、ウェルレジスタのためのエリアにおけるレジスタヘッドアクティブエリアを含み、かつ、前記ウェルレジスタのための前記エリアにおけるレジスタダミーアクティブエリアを含み、前記レジスタダミーアクティブエリアが 10 % ~ 80 % の密度を有する、前記 S T I マスクを形成することと、

20

前記基板に 250 ナノメートル ~ 500 ナノメートルの深さの S T I トレンチを形成するに、前記 S T I マスクにより露出されるエリアにおいて、前記 C M P ストップ層を取り除き、前記基板の前記半導体材料の一部を取り除くことと、

前記 S T I トレンチ内と、前記アクティブエリアの上の前記 C M P ストップ層の上とに、トレンチ充填誘電性材料の層を形成することであって、前記トレンチ充填誘電性材料が前記 S T I トレンチを充填する、前記トレンチ充填誘電性材料の層を形成することと、

30

C M P プロセスにより前記 C M P ストップ層まで下に前記トレンチ充填誘電性材料を平坦化することであって、前記 C M P プロセスが、前記 C M P ストップ層の上から前記トレンチ充填誘電性材料の全てを取り除き、かつ、前記レジスタヘッドアクティブエリアと前記レジスタダミーアクティブエリアとから如何なる前記半導体材料も取り除かない、前記平坦化することと、

前記 C M P ストップ層の残りの部分を取り除くことであって、前記 S T I トレンチ内の前記トレンチ充填誘電性材料が前記集積回路のフィールド酸化物を形成する、前記 C M P ストップ層の残りの部分を取り除くことと、

前記フィールド酸化物を介して、前記ウェルレジスタのための前記エリアにおける前記フィールド酸化物の下の前記基板の前記半導体材料内にウェルドーパントを注入することと、

40

前記ウェルレジスタを形成するために前記ウェルドーパントを活性化するようにウェルアニールプロセスにおいて前記基板を加熱することと、

前記レジスタヘッドアクティブエリアを介する前記ウェルレジスタへの電気的接続を提供するためにコンタクトを形成することであって、前記基板の上の前記レジスタダミーアクティブエリアに電気的接続がない、前記コンタクトを形成することと、

を含む、方法。

**【請求項 8】**

請求項 7 に記載の方法であって、

50

前記レジスタダミーアクティブエリアが 20 % ~ 50 % の密度を有する、方法。

【請求項 9】

請求項 7 に記載の方法であって、

前記レジスタダミーアクティブエリアを露出させるために、前記基板と前記フィールド酸化物との上にダミー領域注入マスクを形成することと、

前記ダミー領域注入マスクが適所に置かれる一方で、ソース / ドレインドーパントを前記レジスタダミーアクティブエリアに注入することと、

その後、前記ダミー領域注入マスクを取り除くことと、

前記レジスタダミーアクティブエリアにおける重くドープされたダミー拡散された領域を形成するために、前記ソース / ドレインドーパントを活性化するためにアニールオペレーションを実施することであって、前記重くドープされたダミー拡散された領域が、前記ウェルレジスタにおける平均ドーピング密度の少なくとも 10 倍の平均ドーピング密度を有する、前記アニールオペレーションを実施することと、

を更に含む、方法。

【請求項 10】

請求項 9 に記載の方法であって、

前記重くドープされたダミー拡散された領域が、前記ウェルレジスタと同じ導電型を有する、方法。

【請求項 11】

請求項 7 に記載の方法であって、

前記レジスタヘッドアクティブエリアと前記レジスタダミーアクティブエリアとの頂部表面上に耐火性金属の層を形成することと、

前記レジスタヘッドアクティブエリアと前記レジスタダミーアクティブエリアとの前記頂部表面に金属シリサイドの層を形成するために前記基板を加熱することと、

その後、未反応の耐火性金属を前記耐火性金属の層から取り除くことと、

を更に含む、方法。

【請求項 12】

請求項 7 に記載の方法であって、

前記レジスタダミーアクティブエリアが複数の矩形として構成され、そのため、前記矩形の各々が、前記ウェルレジスタの一方の側の付近から前記ウェルレジスタの反対側の付近まで延在する、方法。

【請求項 13】

集積回路であって、

頂部表面に半導体材料を含む基板と、

前記基板の前記頂部表面に配置される、S T I プロセスによって形成されるフィールド酸化物と、

前記フィールド酸化物の上に配置されるポリシリコンレジスタであって、C M P 平坦化されたポリシリコンの層から形成される、前記ポリシリコンレジスタと、

前記ポリシリコンレジスタのためのエリアにおける前記フィールド酸化物を介して配置されるレジスタダミーアクティブエリアであって、前記基板の上に電気的接続がなく、10 % ~ 80 % の密度を有する、前記レジスタダミーアクティブエリアと、

含む、集積回路。

【請求項 14】

請求項 13 に記載の集積回路であって、

前記レジスタダミーアクティブエリアが、前記ポリシリコンレジスタの下に延在しない、集積回路。

【請求項 15】

請求項 13 に記載の集積回路であって、

前記レジスタダミーアクティブエリアが、前記ポリシリコンレジスタの下に延在し、前記レジスタダミーアクティブエリアの頂部表面で誘電体層によって前記ポリシリコンレジ

10

20

30

40

50

スタから分離される、集積回路。

【請求項 16】

請求項 13 に記載の集積回路であって、

前記レジスタダミーアクティブエリアが 20 % ~ 50 % の密度を有する、集積回路。

【請求項 17】

集積回路を形成する方法であって、

頂部表面に半導体材料を含む基板を提供することと、

前記基板の上に CMP ストップ層を形成することと、

前記 CMP ストップ層の上に STI マスクを形成することであって、前記 STI マスクが前記集積回路のアクティブエリアのためのエリアを覆い、前記アクティブエリアがポリシリコンレジスタのための前記エリアにおけるレジスタダミーアクティブエリアを含み、前記レジスタダミーアクティブエリアが 10 % ~ 80 % の密度を有する、前記 STI マスクを形成することと、

前記基板に 250 ナノメートル ~ 500 ナノメートルの深さの STI トレンチを形成するため、前記 STI マスクにより露出されたエリアにおいて、前記 CMP ストップ層を取り除き、前記基板の前記半導体材料の一部を取り除くことと、

前記 STI トレンチ内と、前記アクティブエリアの上の前記 CMP ストップ層の上と/or、トレンチ充填誘電性材料の層を形成することであって、前記トレンチ充填誘電性材料が前記 STI トレンチを充填する、前記トレンチ充填誘電性材料の層を形成することと、

CMP プロセスにより前記トレンチ充填誘電性材料を前記 CMP ストップ層まで下に平坦化することであって、前記 CMP プロセスが、前記 CMP ストップ層の上から前記トレンチ充填誘電性材料の全てを取り除き、前記レジスタダミーアクティブエリアから如何なる前記半導体材料も取り除かない、前記平坦化することと、

前記 CMP ストップ層の残りの部分を取り除くことであって、前記 STI トレンチ内の前記トレンチ充填誘電性材料が前記集積回路のフィールド酸化物を形成する、前記 CMP ストップ層の残りの部分を取り除くことと、

前記フィールド酸化物と前記レジスタダミーアクティブエリアとの上にポリシリコンの層を形成することと、

CMP 平坦化されたポリシリコン層を形成するために CMP プロセスを用いてポリシリコンの前記層を平坦化することと、

前記 CMP 平坦化されたポリシリコン層の上に、前記ポリシリコンレジスタを画定するポリシリコンエッチングマスクを形成することと、

前記ポリシリコンレジスタを形成するために前記ポリシリコンエッチングマスクの外側のエリアにおける前記 CMP 平坦化されたポリシリコン層からポリシリコンを取り除くことと、

前記ポリシリコンレジスタへの電気的接続を提供するためにコンタクトを形成することであって、前記レジスタダミーアクティブエリアには前記基板の上に電気的接続がない、前記コンタクトを形成することと、

を含む、方法。

【請求項 18】

請求項 17 に記載の方法であって、

前記レジスタダミーアクティブエリアが前記ポリシリコンレジスタの下に延在しない、方法。

【請求項 19】

請求項 17 に記載の方法であって、

前記レジスタダミーアクティブエリアが、前記ポリシリコンレジスタの下に延在し、前記レジスタダミーアクティブエリアの頂部表面で誘電体層により前記ポリシリコンレジスタから分離される、方法。

【請求項 20】

請求項 17 に記載の方法であって、

10

20

30

40

50

前記レジスタダミーアクティブエリアが20%～50%の密度を有する、方法。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、概して集積回路に関し、更に特定して言えば、集積回路におけるレジスタに関する。

【背景技術】

【0002】

シャロートレンチアイソレーション (STI) プロセスによりつくられるフィールド酸化物を含む集積回路は、化学機械研磨 (CMP) プロセスを用いる酸化物平坦化工程を含む。 CMP プロセスは、レジスタエリアなどの低アクティブエリア密度の大きなエリアをオーバーポリッシュし、これらのエリアにおいて予測不要な厚みプロファイルを備えた薄いフィールド酸化物を生成する。オーバーポリッシュされたフィールド酸化物の下につくられたウェルレジスタは、薄いフィールド酸化物を通過する一層多くの注入されたドーパントに起因して低い不規則な抵抗を有する。別の CMP プロセスを用いてポリシリコンが平坦化されている、オーバーポリッシュされたフィールド酸化物上の多結晶シリコン (ポリシリコン) のレジスタは、高い不規則な厚みを有しがちであり、これにより、低い可変抵抗、及び抵抗の温度依存における望ましくない変動が生じる。

10

【発明の概要】

【0003】

20

記載される例において、集積回路が、STI フィールド酸化物を有するウェルレジスタと、ウェルレジスタにおけるレジスタダミーアクティブエリアとを含む。 STI マスクが形成され、これは、ウェルレジスタのためのエリアにおけるレジスタヘッドアクティブエリア及びレジスタダミーアクティブエリアを覆う。 STI トレンチが、 STI マスクにより露出されたエリアにおいてエッチングされ、トレンチ充填誘電性材料で充填される。トレンチ充填誘電性材料は、 CMP プロセスによりアクティブエリアの上から取り除かれて、 STI トレンチにおいて STI フィールド酸化物が残される。その後、ウェルレジスタを形成するためにウェルレジスタエリアにおいて基板にドーパントが注入される。

【0004】

30

他の例において、集積回路が、ポリシリコンレジスタのためのエリアにおける STI フィールド酸化物においてレジスタダミーアクティブエリアを有するポリシリコンレジスタを含む。ポリシリコンの層が、フィールド酸化物の上に形成され、 CMP プロセスにより平坦化される。ポリシリコンエッチングプロセスが、ポリシリコンレジスタを残して、ポリシリコンエッチングマスクにより露出されたエリアにおいてポリシリコンを取り除く。

【図面の簡単な説明】

【0005】

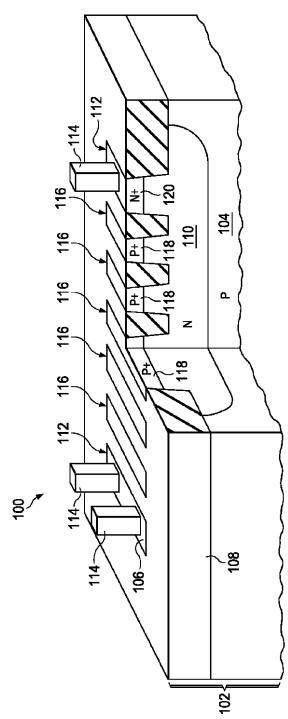

【図1】ウェルレジスタを含む例示の集積回路の断面である。

【0006】

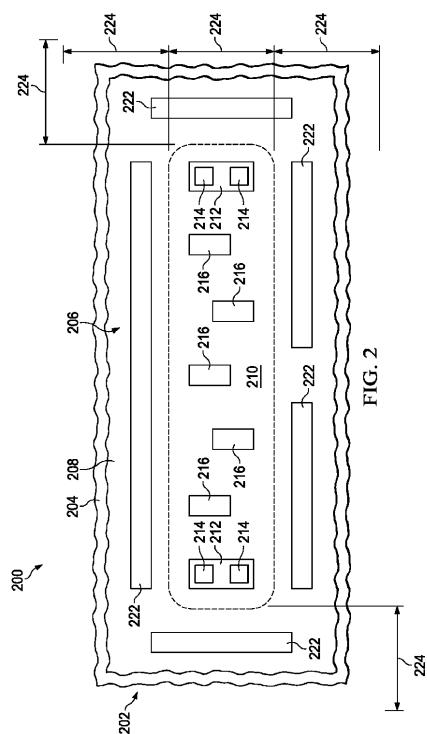

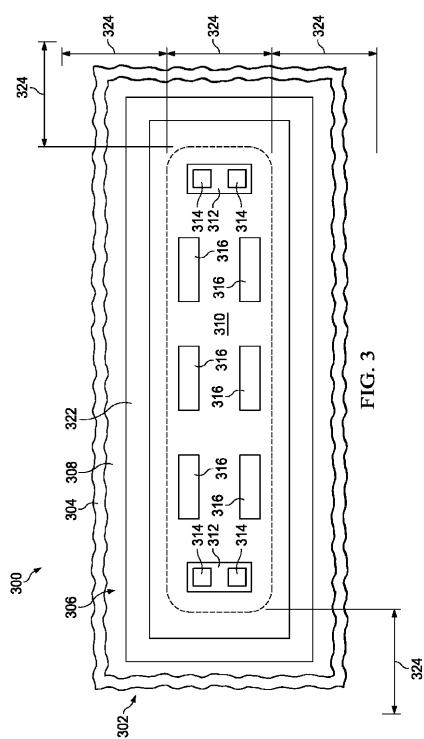

【図2】ウェルレジスタを含む例示の集積回路の上面図である。

【図3】ウェルレジスタを含む例示の集積回路の上面図である。

40

【0007】

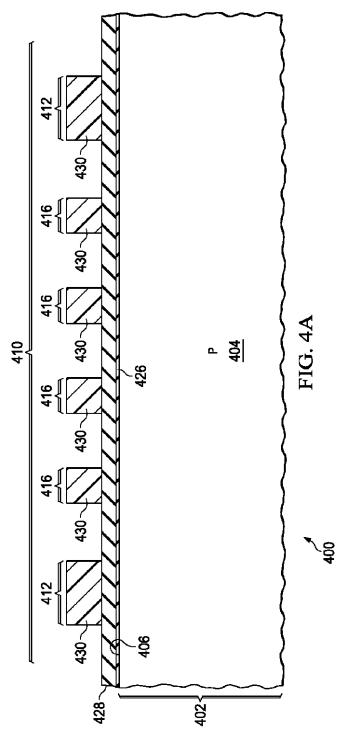

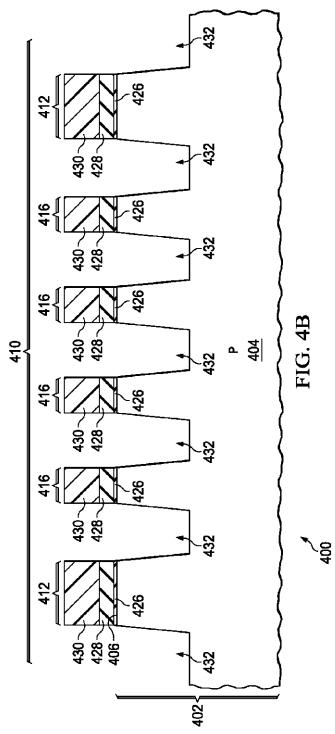

【図4A】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

【図4B】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

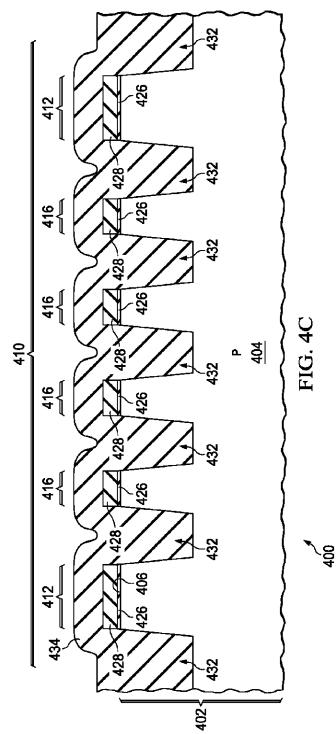

【図4C】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

【図4D】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

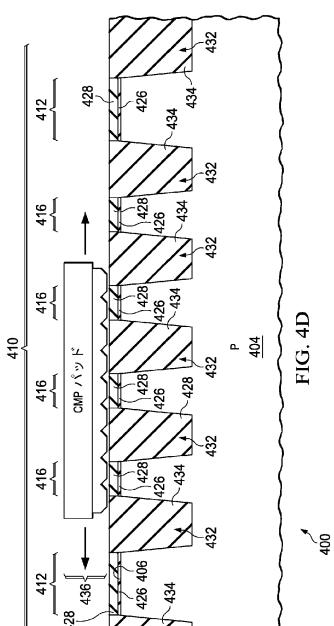

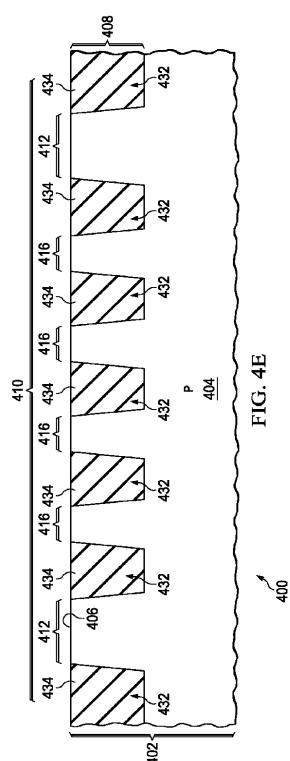

【図4E】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

50

ある。

【図4F】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

【図4G】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

【図4H】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

【図4I】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

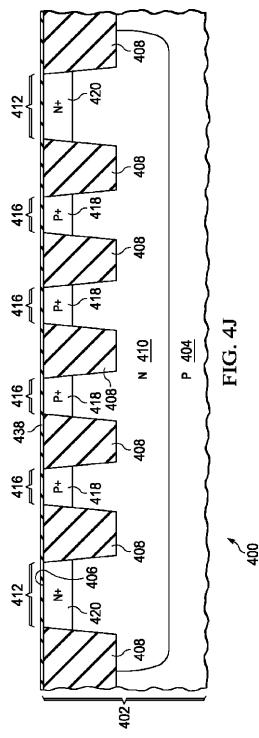

【図4J】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。 10

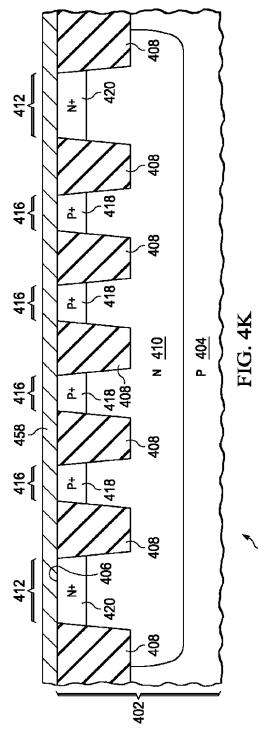

【図4K】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

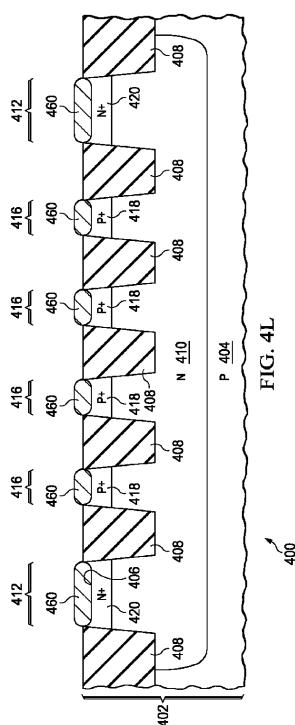

【図4L】製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。

【0008】

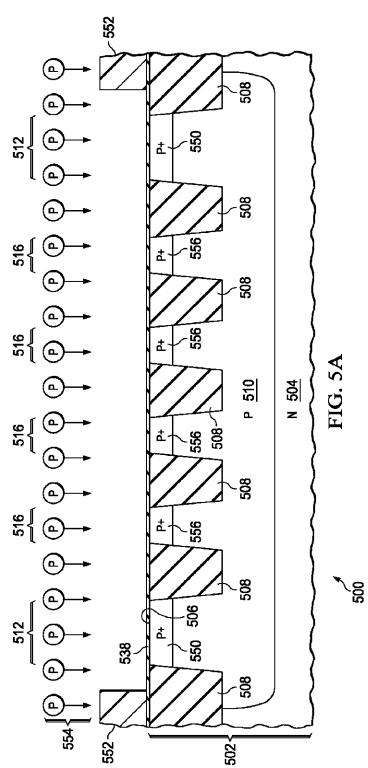

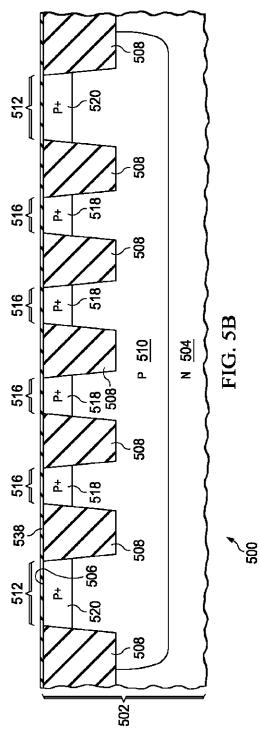

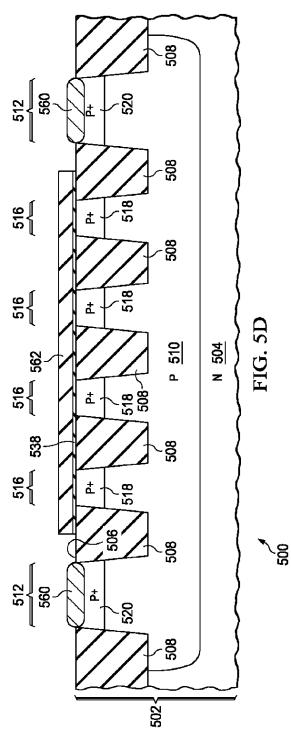

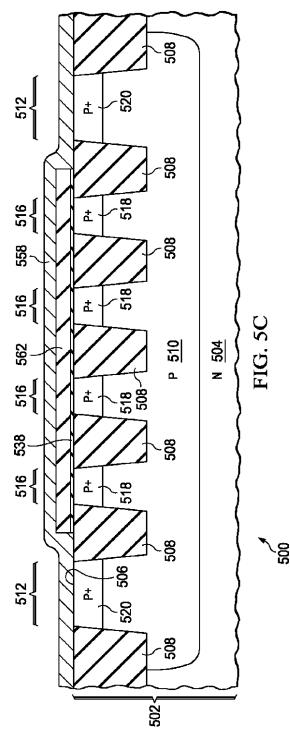

【図5A】製造の連続的段階で示した、ウェルレジスタを含む別の例示の集積回路の断面図である。

【図5B】製造の連続的段階で示した、ウェルレジスタを含む別の例示の集積回路の断面図である。 20

【図5C】製造の連続的段階で示した、ウェルレジスタを含む別の例示の集積回路の断面図である。

【図5D】製造の連続的段階で示した、ウェルレジスタを含む別の例示の集積回路の断面図である。

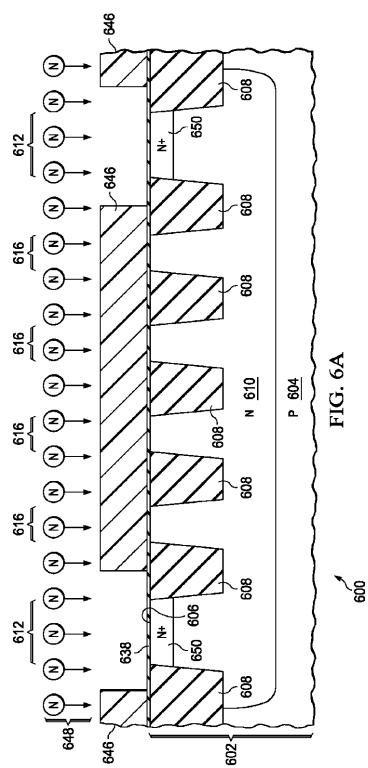

【0009】

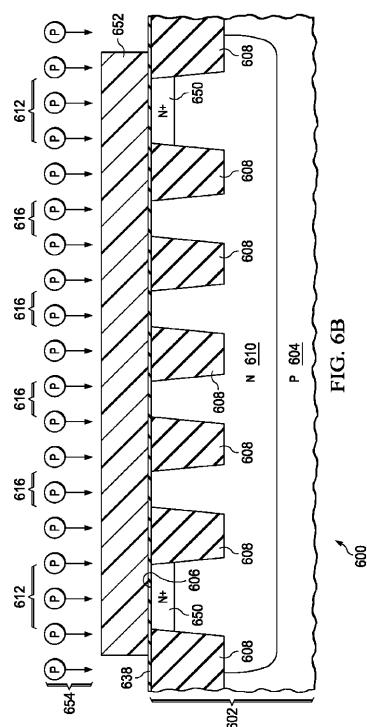

【図6A】製造の連続的段階で示した、ウェルレジスタを含む更なる例示の集積回路の断面図である。

【図6B】製造の連続的段階で示した、ウェルレジスタを含む更なる例示の集積回路の断面図である。 30

【図6C】製造の連続的段階で示した、ウェルレジスタを含む更なる例示の集積回路の断面図である。

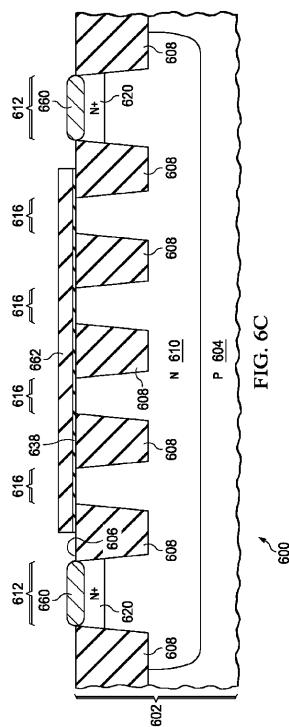

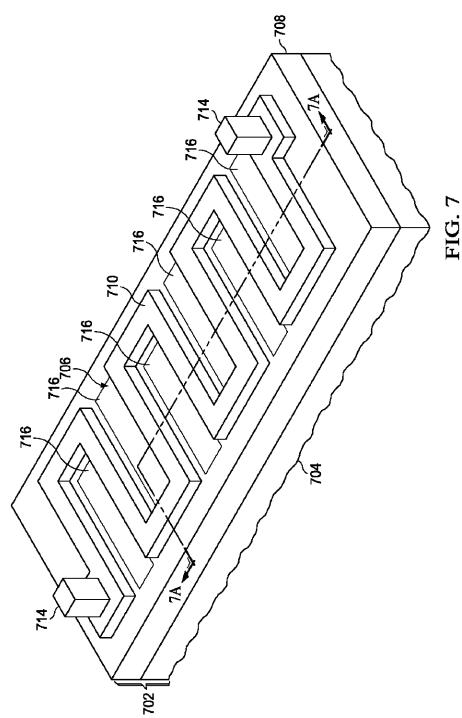

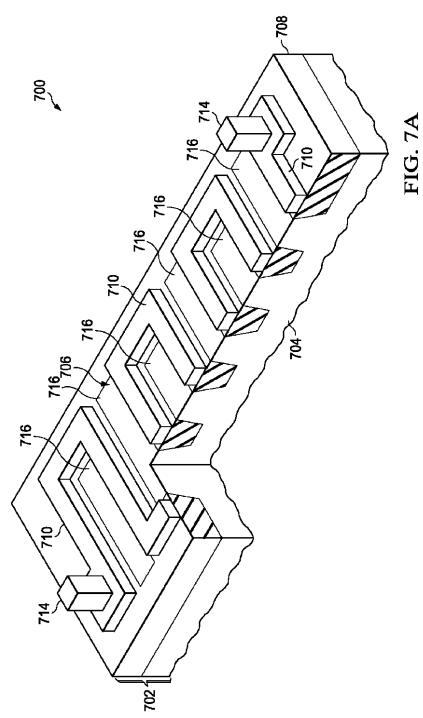

【0010】

【図7】ポリシリコンレジスタを含む例示の集積回路を示す。

【図7A】図7の集積回路の断面を示す。

【0011】

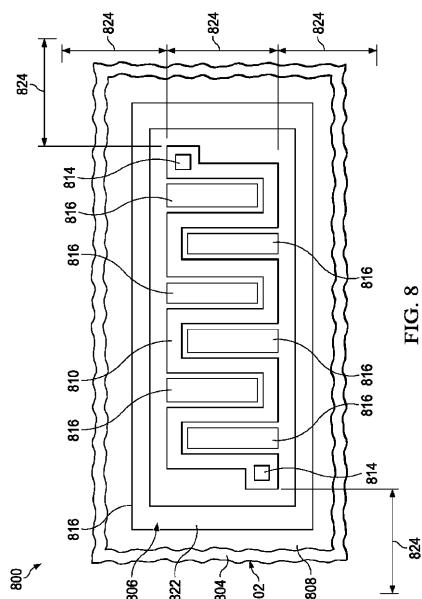

【図8】ポリシリコンレジスタを含む例示の集積回路の上面図である。

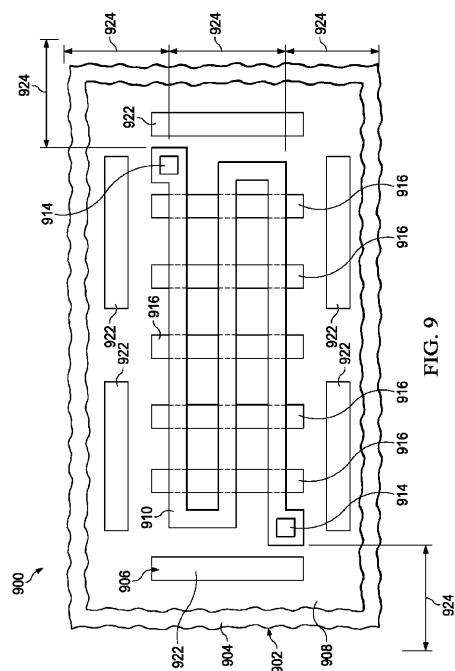

【図9】ポリシリコンレジスタを含む例示の集積回路の上面図である。

【0012】

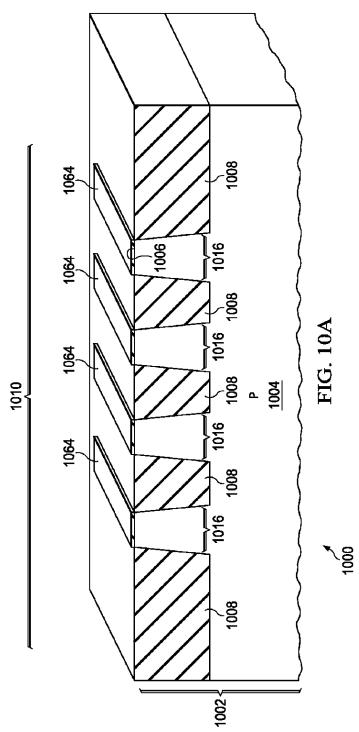

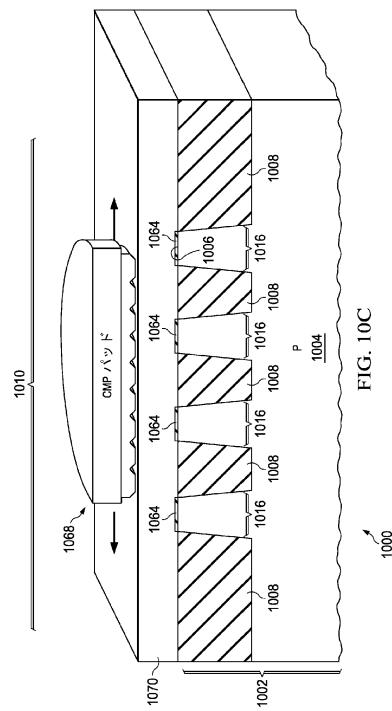

【図10A】製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。 40

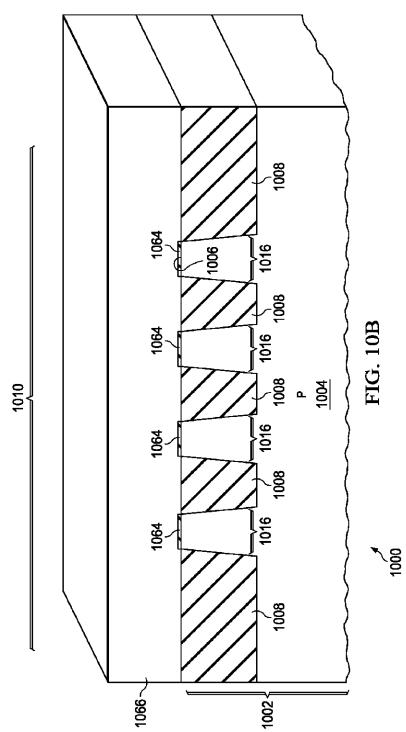

【図10B】製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。

【図10C】製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。

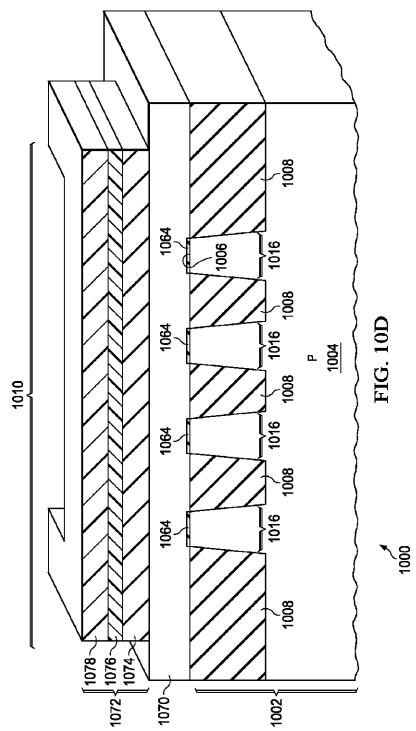

【図10D】製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。

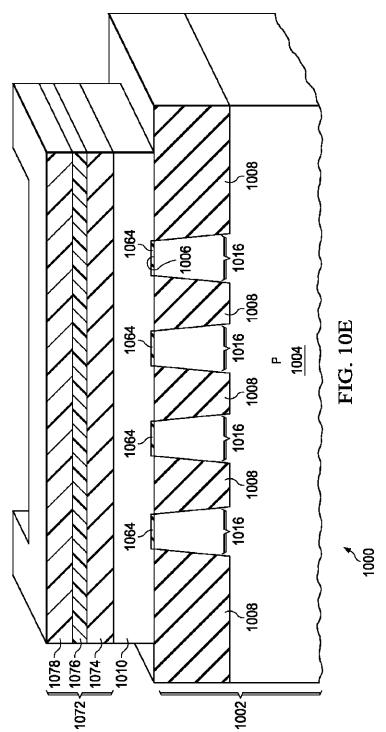

【図10E】製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。

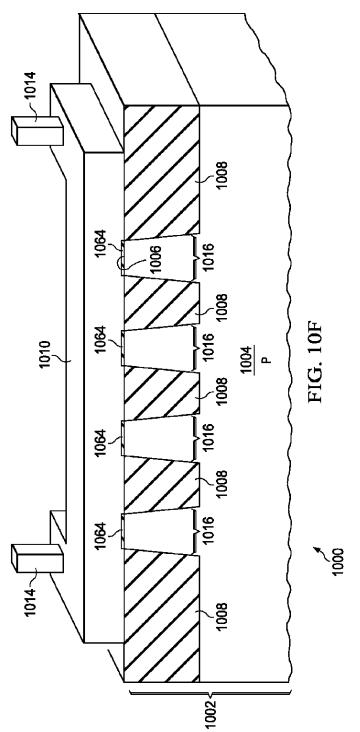

【図10F】製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。 50

## 【発明を実施するための形態】

## 【0013】

図面は一定の縮尺で描いてはいない。図1は、ウェルレジスタを含む例示の集積回路の断面である。集積回路100が基板102上に形成され、基板102は、基板102の頂部表面106まで延在する半導体材料104を含む。この例は、p型半導体材料104について説明される。STIプロセスによって形成されるフィールド酸化物108が、基板102の頂部表面106において配置される。n型ウェルレジスタ110が、フィールド酸化物108の下の基板102の半導体材料104内に配置される。ウェルレジスタ110における例示の平均ドーピング密度は、 $1 \times 10^{17} \text{ cm}^{-3} \sim 5 \times 10^{18} \text{ cm}^{-3}$ であり得る。レジスタヘッドアクティブエリア112が、ウェルレジスタ110の端部に近接してフィールド酸化物108を介して配置される。コンタクト114が、場合によって金属シリサイド(図1には示していない)の層を介して、レジスタヘッドアクティブエリア112への電気的接続を成すように形成される。フィールド酸化物108は、ウェルレジスタ110のためのエリアにおいてフィールド酸化物108を介してレジスタダミーアクティブエリア116が配置されるように、形成される。レジスタダミーアクティブエリア116には基板102の上に電気的接続がない。この例では、レジスタダミーアクティブエリアは複数の矩形として構成されて、各矩形が、ウェルレジスタの一つの側の付近からウェルレジスタの反対側の付近まで延在するようとする。レジスタダミーアクティブエリア116の密度は10%~80%である。重くドープされたダミー拡散された領域118が、任意選択で、レジスタダミーアクティブエリア116に形成され得る。ダミー拡散された領域118における平均ドーピング密度は、ウェルレジスタ110における平均ドーピング密度の少なくとも10倍である。この例では、ダミー拡散された領域118はp型であり、そのため、ダミー拡散された領域118は、ウェルレジスタ110とは反対の導電型を有する。重くドープされたレジスタヘッドコンタクト領域120が、ウェルレジスタ110と同じ導電型を有するレジスタヘッドアクティブエリア112において形成され得る。10%~80%の密度でウェルレジスタ110のためのエリアにおいてレジスタダミーアクティブエリア116を形成することは、STIプロセスの間のフィールド酸化物108のオーバーポリッシュを防止し得、フィールド酸化物の所望の厚みを有利に提供し、そのため、ウェルレジスタ110のための所望の抵抗を提供する。この例の一つのバージョンにおいて、レジスタダミーアクティブエリア116の密度は20%~50%であり、所望の厚みに一層近いフィールド酸化物108の厚みを有利に提供する。更なるバージョンにおいて、レジスタダミーアクティブエリア116の密度は30%~35%であり、フィールド酸化物108のための厚みの範囲を更に一層有利に狭める。レジスタダミーアクティブエリア116の横方向の寸法及び間隔を調節することによって、ウェルレジスタ110のインスタンスの抵抗が調整され得る。ドーパント及び導電型の適切な変化を施したこの例に従って、n型基板においてp型ウェルレジスタが形成され得る。更に、p型ウェルレジスタの下の、埋め込み層又はディープウェルなどの、隔離n型構造を形成することにより、p型ウェルレジスタがp型基板に形成され得る。同様に、p型隔離構造を用いてn型基板にn型ウェルレジスタが形成され得る。

## 【0014】

図2及び図3は、ウェルレジスタを含む例示の集積回路の上面図である。図2を参照すると、集積回路200が基板202上に形成され、基板202は、基板202の頂部表面206まで延在する半導体材料204を含む。STIプロセスによって形成されるフィールド酸化物208が、基板202の頂部表面206において配置される。フィールド酸化物208の下の半導体材料204にウェルレジスタ210が配置される。レジスタヘッドアクティブエリア212が、ウェルレジスタ210の端部に近接してフィールド酸化物208を介して配置される。コンタクト214が、レジスタヘッドアクティブエリア212への電気的接続を成すように形成される。フィールド酸化物208は、レジスタダミーアクティブエリア216がウェルレジスタ210のためのエリアにおいてフィールド酸化物208を介して配置されるように形成される。この例では、レジスタダミーアクティブエ

10

20

30

40

50

リア 216 は、ウェルレジスタ 210 の抵抗に対する影響を最小化する一方で、フィールド酸化物 208 の所望の厚みを提供するためにレジスタダミーアクティブエリア 216 の所望の密度を維持するように構成され得る。任意選択の周囲ダミーアクティブエリア 222 が、ウェルレジスタ 210 のためのエリアの全ての側部で、及びその外側で、フィールド酸化物 208 を介して配置され得る。存在する場合、周囲ダミーアクティブエリア 222 は、ウェルレジスタ 210 の幅 224 内にある。周囲ダミーアクティブエリア 222 は、図 2 に示すように区分され得る。周囲ダミーアクティブエリア 222 をウェルレジスタ 210 の幅 224 内に形成することが、フィールド酸化物 208 の厚みのための一層タイトなプロセス範囲を有利に提供し得る。

## 【0015】

10

図 3 を参照すると、集積回路 300 が基板 302 上に形成され、基板 302 は、基板 302 の頂部表面 306 まで延在する半導体材料 304 を含む。STI プロセスによって形成されるフィールド酸化物 308 が、基板 302 の頂部表面 306 において配置される。フィールド酸化物 308 の下の半導体材料 304 にウェルレジスタ 310 が配置される。レジスタヘッドアクティブエリア 312 が、ウェルレジスタ 310 の端部に近接してフィールド酸化物 308 を介して配置される。コンタクト 314 が、レジスタヘッドアクティブエリア 312 への電気的接続を成すように形成される。フィールド酸化物は、ウェルレジスタ 310 のためのエリアにおけるフィールド酸化物 308 を介してレジスタダミーアクティブエリア 316 が配置されるように、形成される。この例では、レジスタダミーアクティブエリア 316 は、ウェルレジスタ 310 の抵抗に対する一層大きな調整能力を提供するようにウェルレジスタ 310 における電流フローに平行に構成され得、一方で、フィールド酸化物 308 の所望の厚みを提供するためにレジスタダミーアクティブエリア 316 の所望の密度を維持する。任意選択の周囲ダミーアクティブエリア 322 が、ウェルレジスタ 310 のためのエリアを継続的に囲むフィールド酸化物 308 を介して配置され得る。存在する場合、周囲ダミーアクティブエリア 322 は、ウェルレジスタ 310 の幅 324 内にある。ウェルレジスタ 310 の幅 324 内にウェルレジスタ 310 を継続的に囲むように周囲ダミーアクティブエリア 322 を形成することが、フィールド酸化物 308 の厚みのための一層タイトなプロセス範囲を有利に提供し得る一方で、レジスタダミーアクティブエリア 316 の密度を低減することは、ウェルレジスタ 310 の全体的なエリアを低減するために望ましい場合がある。

20

## 【0016】

30

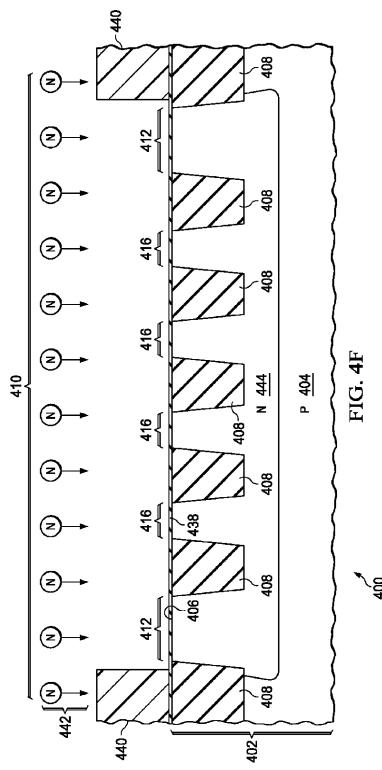

図 4A ~ 図 4L は、製造の連続的段階で示した、ウェルレジスタを含む例示の集積回路の断面図である。図 4A を参照すると、集積回路 400 が基板 402 上に形成され、基板 402 は、基板 402 の頂部表面 406 まで延在する半導体材料 404 を含む。この例では、半導体材料 404 は p 型である。5 ナノメートル ~ 25 ナノメートルの厚みの二酸化シリコンのパッド酸化物層 426 が、テトラエトキシシラン (TEOS) としても知られているオルトけい酸テトラエチルを用いるプラズマエンハンスト化学気相成長 (PECVD) プロセスなどにより、半導体材料 404 におけるシリコンの熱酸化により又は堆積により、基板 402 の頂部表面 406 の上に形成される。50 ナノメートル ~ 200 ナノメートルの厚みのシリコン窒化物の CMP ストップ層 428 が、700 でのシラン又はジクロロシラン及びアンモニアを用いる低圧化学気相成長 (LPCVD) プロセスなどにより、パッド酸化物層 426 の上に形成される。STI マスク 430 が、ウェルレジスタ 410 のためのエリアにおけるレジスタヘッドアクティブエリア 412 のためのエリア及びレジスタダミーアクティブエリア 416 のためのエリアを含み、集積回路 400 におけるアクティブエリアのためのエリアを覆うように CMP ストップ層 428 の上に形成される。STI マスク 430 は、フォトリソグラフィプロセスを用いて形成されるフォトレジストを含み得、任意選択で、反射防止層及び / 又はハードマスク層を含み得る。

40

## 【0017】

図 4B を参照すると、STI トレンチエッチングプロセスが、STI マスク 430 によ

50

り露出されたエリアにおいて CMP ストップ層 428 及びパッド酸化物層 426 を取り除き、STI マスク 430 により露出されたエリアにおいて、STI トレンチ 432 を 250 ナノメートル～500 ナノメートルの深さ形成するために半導体材料 404 内へエッチングする。STI マスク 430 はその後、アッシングプロセスなどにより取り除かれ、その後、硫酸及び過酸化水素の水溶性混合物を用いるウェット洗浄工程が続く。二酸化シリコンの層（図 4B には示していない）が、STI マスク 430 が取り除かれた後、半導体材料 404 におけるシリコンの熱酸化により STI トレンチ 432 の側壁上に形成され得る。

#### 【0018】

図 4C を参照すると、トレンチ充填誘電性材料 434 の層が、STI トレンチ 432 内に、及び、レジスタヘッドアクティブエリア 412 のためのエリア及びレジスタダミーアクティブエリア 416 のためのエリアの上の、CMP ストップ層 428 の上に形成される。トレンチ充填誘電性材料 434 は、STI トレンチ 432 を充填する。トレンチ充填誘電性材料 434 は、主として二酸化シリコンを含み得、シリコン窒化物又はシリコンオキシナイトライドの層を含み得る。トレンチ充填誘電性材料 434 は、単一の層に又は幾つかの層に形成され得る。プランケットエッチングプロセスが、CMP ストップ層 428 の上のトレンチ充填誘電性材料 434 の厚みを低減するために幾つかの層の形成の間に実施され得る。トレンチ充填誘電性材料 434 は、450 での、シラン及び酸素を用いる常圧化学気相成長（APCVD）プロセス、500 での、ジクロロシラン及び酸素を用いる準大気圧化学気相成長（SACVD）プロセス、高密度プラズマ（HDP）プロセス、又は、高アスペクト比プロセス（HARP）としても知られているオゾンベースの熱化学気相成長（CVD）プロセスなど、種々のプロセスにより形成され得る。トレンチ充填誘電性材料 434 はその後、窒素又は酸素雰囲気において少なくとも 30 分間 900 ～ 1100 での熱アニールを用いて濃密化され得る。

#### 【0019】

図 4D を参照すると、トレンチ充填誘電性材料 434 は、CMP パッド 436 により図 4D において概略で示される、CMP プロセス 436 によって CMP ストップ層 428 まで下に平坦化される。レジスタヘッドアクティブエリア 412 及びレジスタダミーアクティブエリア 416 の上のトレンチ充填誘電性材料 434 は、ウェルレジスタ 410 のためのエリアにおけるトレンチ充填誘電性材料 434 のオーバーポリッシュを効果的に防止するために CMP パッド 436 に対する充分な抵抗を提供する。この例では、ウェルレジスタ 410 のためのエリアにおける CMP ストップ層 428 の上の全てのトレンチ充填誘電性材料 434 が CMP プロセス 436 により取り除かれ、如何なる半導体材料 404 も CMP プロセス 436 によってレジスタヘッドアクティブエリア 412 及びレジスタダミーアクティブエリア 416 から取り除かれない。

#### 【0020】

図 4E を参照すると、集積回路 400 のためのフィールド酸化物 408 を提供するために STI トレンチ 432 におけるトレンチ充填誘電性材料 434 を残して、図 4D の CMP ストップ層 428 の残りの部分が取り除かれ。また、図 4E に示すように、パッド酸化物層 426 は任意で取り除かれ得る。CMP ストップ層 428 は、155 のリン酸の水溶液により取り除かれ得る。パッド酸化物層 426 は、フッ化水素酸の希釀緩衝水溶液により取り除かれ得る。

#### 【0021】

図 4F を参照すると、5 ナノメートル～15 ナノメートルの厚みの、二酸化シリコンのパッド酸化物 438 の第 2 の層が、基板 402 の上に形成され得る。パッド酸化物 438 の第 2 の層は、PECVD プロセスにより、図 4F に示すように、基板 402 及びフィールド酸化物 408 の上に二酸化シリコンのプランケット層を堆積することにより形成され得る。代替として、パッド酸化物 438 の第 2 の層は、基板 402 の頂部表面 406 における半導体材料 404 におけるシリコンの熱酸化により、レジスタヘッドアクティブエリア 412 及びレジスタダミーアクティブエリア 416 を含む集積回路 400 のアクティブ

10

20

30

40

50

エリアの上に形成され得る。ウェル注入マスク 440 が、ウェルレジスタ 410 のためのエリアを露出させるために基板 402 及びフィールド酸化物 408 の上に形成される。ウェル注入マスク 440 は、p チャネル金属酸化物半導体 (PMOS) トランジスタの下の n 型ウェルなど、集積回路 400 における他の n 型ウェルのためのエリアを露出させ得、集積回路 400 の製造コスト及び製造複雑性を有利に低減する。n 型ドーパント 442 (リンなど) が、基板 102 の半導体材料 404 におけるウェル注入された領域 444 を形成するためにウェル注入マスク 440 により露出されたエリアにおける基板 402 に注入される。n 型ドーパント 442 は、 $1 \times 10^{13} \text{ cm}^{-2} \sim 1 \times 10^{14} \text{ cm}^{-2}$  のドーズ量及び 400 keV ~ 700 keV のエネルギーで注入され得る。ウェル注入された領域 444 は、フィールド酸化物 408 の下に延在する。ウェル注入マスク 440 はその後、図 4B の STI マスク 430 を参照して説明したように取り除かれる。

#### 【0022】

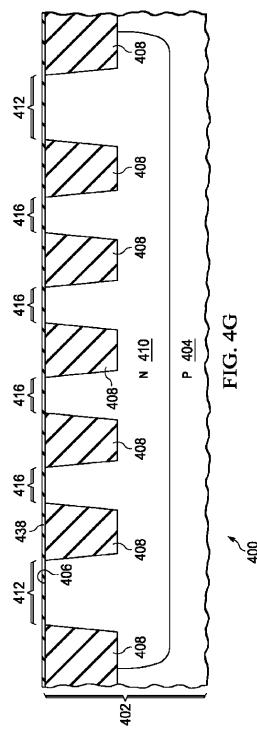

図 4G を参照すると、ウェルアニールプロセスが実施され、このプロセスは、ウェルレジスタ 410 を形成するために図 4F のウェル注入された領域 444 における注入された n 型ドーパント 442 を拡散及び活性化する。この例の一つのバージョンにおいて、ウェルアニールプロセスは、30 分 ~ 2 時間の 800 ~ 900 でのファーネルアニールを含み得る。代替のバージョンにおいて、ウェルアニールは、20 秒 ~ 60 秒間の 1025 ~ 1060 での高速サーマルプロセッサアニールを含み得る。ウェルレジスタ 410 のシート抵抗が、100 オーム / 平方 ~ 1000 オーム / 平方であり得る。

#### 【0023】

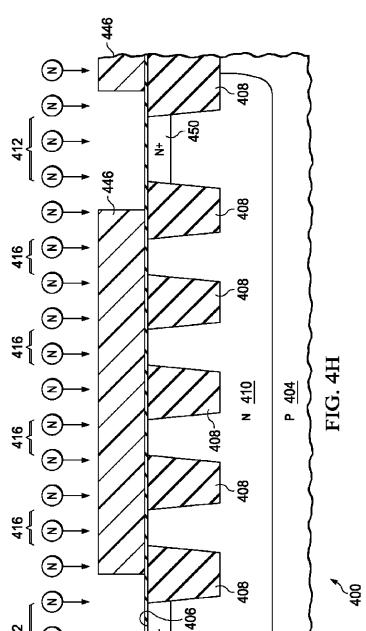

図 4H を参照すると、コンタクト注入マスク 446 が、レジスタヘッドアクティブエリア 412 を露出させるために集積回路 400 の既存の頂部表面の上に形成される。この例では、コンタクト注入マスク 446 は、レジスタダミーアクティブエリア 416 を覆う。コンタクト注入マスク 446 はまた、集積回路 400 の n チャネル金属酸化物半導体 (NMOS) トランジスタにおける n チャネルソース / ドレイン (NSD) 領域のためのエリアを露出させ得、集積回路 400 の製造コスト及び製造複雑性を有利に低減する。コンタクト注入された領域 450 を形成するために、n 型ドーパント 448 (リン及び / 又は砒素など) がレジスタヘッドアクティブエリア 412 に注入され、コンタクト注入された領域 450 は、基板 402 の頂部表面 406 から 100 ナノメートル ~ 300 ナノメートルの深さまで延在する。コンタクト注入された領域 450 は、フィールド酸化物 408 ほど深く延在しない。n 型ドーパント 448 は、 $1 \times 10^{15} \text{ cm}^{-2} \sim 5 \times 10^{16} \text{ cm}^{-2}$  のドーズ量及び 30 keV ~ 80 keV のエネルギーで注入され得る。コンタクト注入マスク 446 は、その後、図 4B の STI マスク 430 を参照して説明したように取り除かれる。

#### 【0024】

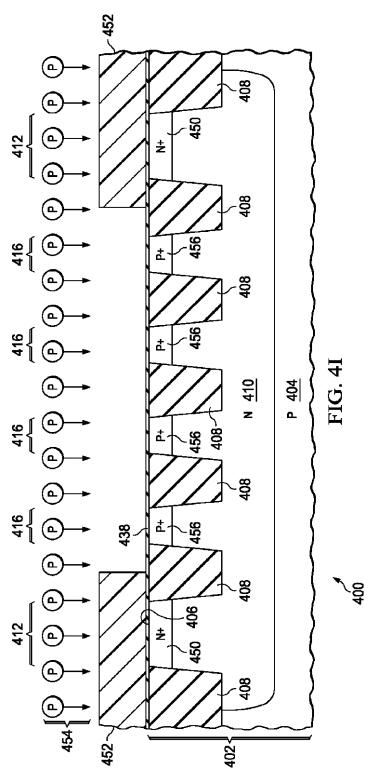

図 4I を参照すると、レジスタダミーアクティブエリア 416 を露出させるために及びレジスタヘッドアクティブエリア 412 を覆うために、ダミー領域注入マスク 452 が、集積回路 400 の既存の頂部表面の上に形成される。ダミー領域注入マスク 452 はまた、集積回路 400 の PMOS トランジスタにおける p チャネルソース / ドレイン (PSD) 領域のためのエリアを露出させ得、集積回路 400 の製造コスト及び製造複雑性を有利に低減する。p 型ドーパント 454 (ボロンなど) が、ダミー注入された領域 456 を形成するためにレジスタダミーアクティブエリア 416 に注入され、ダミー注入された領域 456 は、基板 402 の頂部表面 406 から 100 ナノメートル ~ 300 ナノメートルの深さまで延在する。ダミー注入された領域 456 は、フィールド酸化物 408 ほど深く延在しない。p 型ドーパント 454 は、 $1 \times 10^{15} \text{ cm}^{-2} \sim 5 \times 10^{16} \text{ cm}^{-2}$  のドーズ量及び 5 keV ~ 15 keV のエネルギーで注入され得る。ダミー領域注入マスク 452 はその後、図 4B の STI マスク 430 を参照して説明したように取り除かれる。

#### 【0025】

図 4J を参照すると、アニールオペレーションが実施され、このオペレーションは、レジスタヘッドアクティブエリア 412 において n 型レジスタヘッドコンタクト領域 420

10

20

30

40

50

を形成するためにコンタクト注入された領域 450において図4Hの注入されたn型ドーパント448を活性化し、レジスタダミーアクティブエリア416においてp型ダミー拡散された領域418を形成するためにダミー注入された領域456における図4Iの注入されたp型ドーパント454を活性化する。アニールオペレーションは、10秒～30秒間の985～1025での高速サーマルプロセッサアニールを含み得る。ダミー拡散された領域418もレジスタヘッドコンタクト領域420も、フィールド酸化物408ほど深く延在しない。

#### 【0026】

図4Kを参照すると、誘電性材料（レジスタヘッドアクティブエリア412の及び場合によってはレジスタダミーアクティブエリア416上の、頂部表面406上の、図4Jのパッド酸化物438の第2の層など）が、フッ化水素酸の希釈緩衝水溶液などにより、及びその後続く、Siconiエッチなどの順次ドライエッチなどにより取り除かれる。耐火性金属458の層が、レジスタヘッドアクティブエリア412上に、及び場合によっては、露出される場合にレジスタダミーアクティブエリア416上に、形成される。例えば、耐火性金属458の層は、白金、チタン、コバルト、ニッケル、又はモリブデンを含み得、5ナノメートル～50ナノメートルの厚みであり得、任意選択でキャップ層を含み得る。耐火性金属458の層は、スパッタリングにより又は有機金属化学気相成長（MOCVD）プロセスにより形成され得る。

#### 【0027】

図4Lを参照すると、図4Kの耐火性金属458の層における耐火性金属が基板402の頂部表面406におけるレジスタヘッドアクティブエリア412及びレジスタダミーアクティブエリア416におけるシリコンと反応するように、基板402が加熱されて、レジスタヘッドアクティブエリア412及びレジスタダミーアクティブエリア416の頂部において金属シリサイド層460が形成される。金属シリサイド層460を形成するために必要とされる温度は、耐火性金属458の層における特定の耐火性金属に依存する。その後、耐火性金属458の層における未反応の耐火性金属が、硫酸及び過酸化水素の混合を用いるウェットエッティングプロセスなどにより取り除かれる。金属シリサイド層460及びレジスタヘッドコンタクト領域420は、ウェルレジスタ410への低抵抗接続を有利に提供する。レジスタダミーアクティブエリア416上に金属シリサイド層460を形成することは、シリサイドブロック層を含まない製造シーケンスのための製造コスト及び製造複雑性を低減し得る。集積回路400の製造が、金属シリサイド層460の上のプレメタル誘電体（PMD）層の形成と、金属シリサイド層460及びレジスタヘッドコンタクト領域420を介するウェルレジスタ410への電気的接続を成すための、PMD層を介するコンタクトの形成で継続される。

#### 【0028】

図5A～図5Dは、製造の連続的段階で示した、ウェルレジスタを含む別の例示の集積回路の断面図である。図5Aを参照すると、集積回路500が基板502上に形成され、基板502は、基板502の頂部表面506まで延在する半導体材料504を含む。この例では、半導体材料504はn型である。フィールド酸化物508が、図4A～図4Eを参照して説明したように、基板502に形成される。集積回路500は、レジスタヘッドアクティブエリア512及びレジスタダミーアクティブエリア516を含む。図4Fのパッド酸化物438の第2の層に対応するパッド酸化物538の層が、基板502の上に形成される。p型ウェルレジスタ510が、注入されるドーパントを適切に変更して、図4F及び図4Gを参照して説明したように、フィールド酸化物508の下の半導体材料504に形成される。組み合わされたコンタクト／ダミー注入マスク552が、レジスタヘッドアクティブエリア512及びレジスタダミーアクティブエリア516を露出させるために集積回路500の既存の頂部表面の上に形成される。組み合わされたコンタクト／ダミー注入マスク552はまた、集積回路500におけるPMOSトランジスタにおいてPSD領域のためのエリアを露出させ得、集積回路500の製造コスト及び製造複雑性を有利に低減する。p型ドーパント554（ボロンなど）が、レジスタヘッドアクティブエリア

10

20

30

40

50

512においてコンタクト注入された領域550を形成するために及びレジスタダミーアクティブエリア516においてダミー注入された領域556を形成するために、図4Iを参照して説明したように、レジスタヘッドアクティブエリア512及びレジスタダミーアクティブエリア516に注入される。コンタクト注入された領域550及びダミー注入された領域556は、図4Iのダミー注入された領域456に類似する特性を有し得る。組み合わされたコンタクト/ダミー注入マスク552はその後取り除かれる。

【0029】

図5Bを参照すると、アニールオペレーションが実施され、このオペレーションは、レジスタヘッドアクティブエリア512におけるp型レジスタヘッドコンタクト領域520を形成するためにコンタクト注入された領域550において、及びレジスタダミーアクティブエリア516におけるp型ダミー拡散された領域518を形成するためにダミー注入された領域556において、図5Aの注入されたp型ドーパント554を活性化する。このアニールオペレーションは、図4Jを参照して説明したように実施され得る。

【0030】

図5Cを参照すると、誘電性材料（シリコン窒化物及び/又は二酸化シリコンなど）のシリサイドブロック層562が、パッド酸化物538の層の上に形成される。エッチングマスクが、シリサイドブロック層562及びパッド酸化物538の層の上に形成され、エッチングマスクは、レジスタヘッドアクティブエリア512を露出させ、レジスタダミーアクティブエリア516を覆う。エッチングプロセスが、エッチングマスクにより露出されたエリアにおいてシリサイドブロック層562及びパッド酸化物538の層を取り除く。エッチングマスクはその後取り除かれる。レジスタヘッドアクティブエリア512は、図4Kを参照して説明したように洗浄され、一方で、レジスタダミーアクティブエリア516は、シリサイドブロック層562及びパッド酸化物538の層により覆われている。耐火性金属558の層が、集積回路500の既存の頂部表面上に形成される。耐火性金属558の層は、レジスタヘッドアクティブエリア512上に形成され、シリサイドブロック層562及びパッド酸化物538の層によりレジスタダミーアクティブエリア516から分離される。耐火性金属558の層は、図4Kを参照して説明する組成及び厚みを有し得る。

【0031】

図5Dを参照すると、図5Cの耐火性金属558の層における耐火性金属が、図4Lを参照して説明したように、基板502頂部表面506におけるレジスタヘッドアクティブエリア512におけるシリコンと反応するように基板502が加熱されて、レジスタヘッドアクティブエリア512の頂部において金属シリサイド層560が形成される。その後、耐火性金属558の層における未反応の耐火性金属が取り除かれる。集積回路500の製造が、PMD層の形成、及び金属シリサイド層560及びレジスタヘッドコンタクト領域520を介するウェルレジスタ510へのコンタクトの形成で継続される。金属シリサイドがレジスタダミーアクティブエリア516上に形成しないようにすることが、レジスタダミーアクティブエリア上の金属シリサイドを備えるインスタンスに比して、ウェルレジスタ510のインスタンスのためのより均一な抵抗値を有利に提供し得る。

【0032】

図6A～図6Cは、製造の連続的段階で示した、ウェルレジスタを含む更なる例示の集積回路の断面図である。図6Aを参照すると、集積回路600が基板602上に形成され、基板602は、基板602の頂部表面606まで延在する半導体材料604を含む。この例では、半導体材料604はp型である。フィールド酸化物608が、図4A～図4Eを参照して説明したように、基板602に形成される。集積回路600は、レジスタヘッドアクティブエリア612及びレジスタダミーアクティブエリア616を含む。図4Fのパッド酸化物638の第2の層に対応するパッド酸化物638の層が、基板602の上に形成される。n型ウェルレジスタ610が、図4F及び図4Gを参照して説明したように、フィールド酸化物608の下の半導体材料604に形成される。コンタクト注入マスク646が、レジスタヘッドアクティブエリア612を露出させるために集積回路600の

10

20

30

40

50

既存の頂部表面の上に形成される。この例では、コンタクト注入マスク 646 は、レジスタダミーアクティブエリア 616 を覆う。コンタクト注入マスク 646 はまた、集積回路 600 の NMOS トランジスタにおける NSD 領域のためのエリアを露出させ得る。n 型ドーパント 648 (リン及び / 又は砒素など) が、図 4H を参照して説明したように、コンタクト注入された領域 650 を形成するためにレジスタヘッドアクティブエリア 612 に注入される。コンタクト注入マスク 646 はその後取り除かれる。

【0033】

図 6B を参照すると、PSD マスク 652 が、レジスタヘッドアクティブエリア 612 及びレジスタダミーアクティブエリア 616 両方を覆うように、集積回路 600 の既存の頂部表面の上に形成される。PSD マスク 652 は、集積回路 600 の PMOS トランジスタにおける PSD 領域のためのエリアを露出させる。p 型ドーパント 654 (ボロンなど) が、PSD マスク 652 により露出されたエリアにおいて基板 602 に注入される。レジスタヘッドアクティブエリア 612 及びレジスタダミーアクティブエリア 616 には、実質的に p 型ドーパント 654 がない。PSD マスク 652 はその後取り除かれる。レジスタダミーアクティブエリア 616 には実質的に、ウェルレジスタ 610 を形成する際に用いられるドーピング以外、ドーピングがない。

【0034】

図 6C を参照すると、アニールオペレーションが実施され、このオペレーションは、レジスタヘッドアクティブエリア 612 における n 型レジスタヘッドコンタクト領域 620 を形成するためにコンタクト注入された領域 650 における図 6A の注入された n 型ドーパント 648 を活性化する。シリサイドブロック層 662 が、図 5C を参照して説明したように、レジスタヘッドアクティブエリア 612 を露出させるために基板 602 の上のパッド酸化物 638 の層を用いて形成及びパターニングされ、レジスタダミーアクティブエリア 616 を覆う。金属シリサイド層 660 が、図 5C 及び図 5D を参照して説明したように、レジスタヘッドアクティブエリア 612 の頂部表面において形成される。レジスタダミーアクティブエリア 616 における余分のドーピングなしにウェルレジスタ 610 を形成することは、レジスタダミーアクティブエリアにおける余分のドーピングを備えたインスタンスに比して、ウェルレジスタ 610 のインスタンスのためのより均一な抵抗値を有利に提供し得る。

【0035】

図 7 は、ポリシリコンレジスタを含む例示の集積回路を示す。集積回路 700 が基板 702 上に形成され、基板 702 は、基板 702 の頂部表面 706 まで延在する半導体材料 704 を含む。STI プロセスによって形成されるフィールド酸化物 708 が、基板 702 の頂部表面 706 において配置される。ポリシリコンレジスタ 710 が、フィールド酸化物 708 の上に配置される。ポリシリコンレジスタ 710 は、CMP プロセスにより平坦化されたポリシリコンの層から形成される。フィールド酸化物 708 は、ポリシリコンレジスタ 710 のためのエリアにおけるフィールド酸化物 708 を介してレジスタダミーアクティブエリア 716 が配置されるように、形成される。基板 702 の頂部表面 706 の上のレジスタダミーアクティブエリア 716 には電気的接続が成されない。レジスタダミーアクティブエリア 716 の密度は 10% ~ 80% である。ポリシリコンレジスタ 710 のためのエリアにおいて 10% ~ 80% の密度でレジスタダミーアクティブエリア 716 を形成することは、STI プロセスの間のフィールド酸化物 708 のオーバーポリッシュを防止し得、ポリシリコンレジスタ 710 における平坦化されたポリシリコンの所望の厚みを有利に提供し、これにより、ポリシリコンレジスタ 710 のための所望の抵抗が提供される。この例の一つのバージョンにおいて、レジスタダミーアクティブエリア 716 の密度は 20% ~ 50% であり、所望の厚みに一層近いフィールド酸化物 708 の厚みを有利に提供する。更なるバージョンにおいて、レジスタダミーアクティブエリア 716 の密度は 25% ~ 30% であり、フィールド酸化物 708 のための厚みの範囲を更に一層有利に狭める。ポリシリコンレジスタ 710 への電気的接続を提供するために、コンタクト 714 が、ポリシリコンレジスタ 710 上に形成される。図 7A は、レジスタダミーアク

10

20

30

40

50

ティプエリア 716 をより明確に示す、図 7 の集積回路の断面である。

【0036】

図 8 及び図 9 は、ポリシリコンレジスタを含む例示の集積回路の上面図である。図 8 を参考すると、集積回路 800 が基板 802 上に形成され、基板 802 は、基板 802 の頂部表面 806 まで延在する半導体材料 804 を含む。STI プロセスによって形成されるフィールド酸化物 808 が、基板 802 の頂部表面 806 の基板 802 において配置される。ポリシリコンレジスタ 810 が、フィールド酸化物 808 の上のポリシリコンの CMP 平坦化された層から形成される。コンタクト 814 が、ポリシリコンレジスタ 810 への電気的接続を成すように形成される。フィールド酸化物 808 は、ポリシリコンレジスタ 810 のためのエリアにおけるフィールド酸化物 808 を介してレジスタダミーアクティブエリア 816 が配置されるように、形成される。この例では、レジスタダミーアクティブエリア 816 はポリシリコンレジスタ 810 の下に延在せず、これにより、ポリシリコンレジスタ 810 上の静電性負荷が有利に低減され得る。任意選択の周囲ダミーアクティブエリア 822 が、ポリシリコンレジスタ 810 のためのエリアの周りに継続的にフィールド酸化物 808 を介して配置され得る。存在する場合、周囲ダミーアクティブエリア 822 は、ポリシリコンレジスタ 810 の幅 824 内にある。ポリシリコンレジスタ 810 の幅 824 内にポリシリコンレジスタ 810 を継続的に囲むように周囲ダミーアクティブエリア 822 を形成することが、フィールド酸化物 808 の厚みのための一層タイトなプロセス範囲を有利に提供し得、一方、レジスタダミーアクティブエリア 816 の密度を低減する。レジスタダミーアクティブエリア 816 の密度を低減することは、ポリシリコンレジスタ 810 の全体的なエリアを低減するために望ましい場合がある。

【0037】

図 9 を参考すると、集積回路 900 が基板 902 上に形成され、基板 902 は、基板 902 の頂部表面 906 まで延在する半導体材料 904 を含む。STI プロセスによって形成されるフィールド酸化物 908 が、基板 902 の頂部表面 906 において配置される。ポリシリコンレジスタ 910 が、フィールド酸化物 908 の上にポリシリコンの CMP 平坦化された層から形成される。コンタクト 914 が、ポリシリコンレジスタ 910 への電気的接続を成すように形成される。フィールド酸化物 908 は、ポリシリコンレジスタ 910 のためのエリアにおいてフィールド酸化物 908 を介してレジスタダミーアクティブエリア 916 が配置されるように、形成される。この例では、レジスタダミーアクティブエリア 916 はポリシリコンレジスタ 910 の下に延在し、これにより、レジスタダミーアクティブエリア 916 の密度が増大され得、フィールド酸化物 908 のオーバーポリッシュが有利に低減される。任意選択の周囲ダミーアクティブエリア 922 が、ポリシリコンレジスタ 910 のためのエリアの周りにフィールド酸化物 908 を介して配置され得る。周囲ダミーアクティブエリア 922 は、図 9 に示すように区分され得る。存在する場合、周囲ダミーアクティブエリア 922 は、ポリシリコンレジスタ 910 の幅 924 内にある。

【0038】

図 10A ~ 図 10F は、製造の連続的段階で示した、ポリシリコンレジスタを含む例示の集積回路の断面図である。図 10A を参考すると、集積回路 1000 が基板 1002 上に形成され、基板 1002 は、基板 1002 の頂部表面 1006 まで延在する半導体材料 1004 を含む。この例では、半導体材料 1004 は p 型である。フィールド酸化物 1008 が、図 4A ~ 4E を参照して説明したように、基板 1002 の頂部表面 1006 において STI プロセスにより形成される。フィールド酸化物 1008 は、ポリシリコンレジスタ 1010 のためのエリアにおけるフィールド酸化物 1008 を介してレジスタダミーアクティブエリア 1016 が配置されるように、形成される。レジスタダミーアクティブエリア 1016 の上に誘電体層 1064 が配置される。誘電体層 1064 は、集積回路の NMOS 及び PMOS トランジスタのゲート誘電体層と同時に形成され得る。誘電体層は、フィールド酸化物 1008 の上に延在し得る。

【0039】

10

20

30

40

50

図10Bを参照すると、フィールド酸化物1008及び誘電体層1064の上にポリシリコン1066の層が形成される。ポリシリコン1066の層は、580～650でシランを熱分解することなどにより、コンフォーマルプロセスにより形成され得る。ポリシリコン1066の層は、シランと一緒に、ホスフィン、アルシン、又はボロン三塩化物などのドーパントガスを含むことによる形成の間、インサイチド-ピングされ得る。代替として、ポリシリコン1066の層は、イオン注入による形成の後ドープされ得る。インサイチド-ピングは、ポリシリコン1066の層の厚みに関係なく、一定の平均ドーピング密度を生成し得る。イオン注入は、厚みに関係なく、ポリシリコン1066の層におけるドーパントの一定の総ドーズ量を生成し得る。

## 【0040】

図10Cを参照すると、図10Bのポリシリコン1066の層は、CMPパッド1068により図10Cにおいて概略で示されるCMPプロセス1068によって平坦化されて、所望の厚みのCMP平坦化されたポリシリコン層1070が形成される。例えば、CMPプロセス1068は、ポリシリコン形成プロセスのコンフォーマル性に起因するポリシリコン1066の層から任意の表面トポロジーを取り除くために用いられ得る。ポリシリコンレジスタ1010のためのエリアにおいてレジスタダミーアクティブエリア1016を備えるフィールド酸化物1008を形成することは、STIプロセスの間のオーバーポリッシュを低減することによってフィールド酸化物1008のための所望の厚みを提供し、これにより、CMP平坦化されたポリシリコン層1070のための所望の厚みが有利に提供される。オーバーポリッシュされたフィールド酸化物は、一層薄いフィールド酸化物を生成し得、これはその後、望ましくなく一層厚いCMP平坦化されたポリシリコン層を生成し得る。

## 【0041】

図10Dを参照すると、ポリシリコンエッチングマスク1072が、ポリシリコンレジスタ1010を画定するためにCMP平坦化されたポリシリコン層1070の上に形成される。ポリシリコンエッチングマスク1072はまた、集積回路1000におけるNMOs及びPMOSトランジスタのゲートのためのエリアを覆い得る。ポリシリコンエッチングマスク1072は、シリコン窒化物又は非晶質炭素のハードマスク層1074、底部反射防止膜(BARC)と称されるスピンドルコートされた有機材料の反射防止層1076、及び/又はフォトリソグラフィプロセスによって形成されるフォトトレジスト層1078を含み得る。

## 【0042】

図10Eを参照すると、ポリシリコンエッチングプロセスが、ポリシリコンレジスタ1010を形成するためにポリシリコンエッチングマスク1072によって露出されたエリアにおいてCMP平坦化されたポリシリコン層1070からポリシリコンを取り除く。ポリシリコンエッチングプロセスの間、フォトトレジスト層1078及び反射防止層1076の一部又は全てが取り除かれ得る。ポリシリコンエッチングマスク1072の如何なる残りの部分も、その後取り除かれる。

## 【0043】

図10Fを参照すると、ポリシリコンレジスタへの電気的接続を成すためにポリシリコンレジスタ1010上にコンタクト1014が形成される。金属シリサイド(図10Fには示していない)が、ポリシリコンレジスタ1010への電気的接続を改善するために、コンタクト1014の下のポリシリコンレジスタ1010上のエリア上に形成され得る。

## 【0044】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、他の実施例が可能である。

10

20

30

40

【図1】

FIG. 1

【 図 2 】

FIG. 2

【図3】

FIG. 3

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図4C】

FIG. 4C

【図4D】

FIG. 4D

【図4E】

FIG. 4E

【図4F】

FIG. 4F

【図4G】

FIG. 4G

【図4H】

FIG. 4H

【図4I】

FIG. 4I

【図4】

FIG. 4J

### 【図4-L】

FIG. 4L

【図4K】

FIG. 4K

### 【図5A】

FIG. 5A

【図 5 B】

FIG. 5B

### 【図 5 D】

FIG. 5D

【図5C】

FIG. 5C

### 【図 6 A】

FIG. 6A

【図 6 B】

FIG. 6B

【図6C】

FIG. 6C

【 四 7 】

FIG. 7

【図7A】

FIG. 7A

【 四 8 】

FIG. 8

【 図 9 】

FIG. 9

【図10A】

FIG. 10A

【 図 1 0 B 】

FIG. 10B

【図 10C】

FIG. 10C

【図 10D】

FIG. 10D

【図 10E】

FIG. 10E

【図 10F】

FIG. 10F

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 21/76

L

(72)発明者 ステファン キース ハインリッヒ バルナ

アメリカ合衆国 7 5 0 9 4 テキサス州 マーフィー, フォールブルック ドライブ 1 2 5

(72)発明者 ダグラス ピー バーレット

アメリカ合衆国 7 7 4 9 8 テキサス州 シュガーランド, ベイ トゥリー ドライブ 1 3

8 0 7

(72)発明者 アルWIN ジエイ ツアオ

アメリカ合衆国 7 5 0 4 4 テキサス州 ガーランド, パーム デザート 7 0 1

審査官 辻 勇貴

(56)参考文献 米国特許第0 7 1 4 1 8 3 1 (U S , B 1)

米国特許出願公開第2 0 1 3 / 0 2 0 3 2 2 6 (U S , A 1)

特開2 0 0 6 - 2 6 9 5 7 3 (J P , A)

米国特許第0 7 4 0 3 0 9 4 (U S , B 2)

(58)調査した分野(Int.Cl. , DB名)

H 0 1 L 2 1 / 3 2 1

H 0 1 L 2 1 / 7 6

H 0 1 L 2 1 / 7 6 8

H 0 1 L 2 1 / 8 2 2

H 0 1 L 2 7 / 0 4