(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6154880号

(P6154880)

(45) 発行日 平成29年6月28日(2017.6.28)

(24) 登録日 平成29年6月9日(2017.6.9)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 29/786 (2006.01) | HO 1 L 29/78 6 1 8 A |

| HO 1 L 21/336 (2006.01) | GO 2 F 1/1368        |

| GO 2 F 1/1368 (2006.01) | HO 5 B 33/14 A       |

| HO 1 L 51/50 (2006.01)  | HO 5 B 33/14 Z       |

| HO 5 B 33/14 (2006.01)  | HO 5 B 33/10         |

請求項の数 2 (全 30 頁) 最終頁に続く

|              |                                                                  |

|--------------|------------------------------------------------------------------|

| (21) 出願番号    | 特願2015-225539 (P2015-225539)                                     |

| (22) 出願日     | 平成27年11月18日 (2015.11.18)                                         |

| (62) 分割の表示   | 特願2013-262465 (P2013-262465)<br>の分割<br>原出願日 平成20年8月6日 (2008.8.6) |

| (65) 公開番号    | 特開2016-76715 (P2016-76715A)                                      |

| (43) 公開日     | 平成28年5月12日 (2016.5.12)                                           |

| 審査請求日        | 平成27年12月15日 (2015.12.15)                                         |

| (31) 優先権主張番号 | 特願2007-212904 (P2007-212904)                                     |

| (32) 優先日     | 平成19年8月17日 (2007.8.17)                                           |

| (33) 優先権主張国  | 日本国 (JP)                                                         |

| (31) 優先権主張番号 | 特願2007-212903 (P2007-212903)                                     |

| (32) 優先日     | 平成19年8月17日 (2007.8.17)                                           |

| (33) 優先権主張国  | 日本国 (JP)                                                         |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 手塚 祐朗<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 古野 誠<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 鳥海 聰志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】表示装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上にゲート電極を形成する第1の工程と、

前記ゲート電極上にゲート絶縁膜を形成する第2の工程と、

前記ゲート絶縁膜上にプラズマCVD法を用いて微結晶半導体膜を形成する第3の工程

と、を有し、

前記第3の工程は、

真空排気が行なわれた反応室内に前記基板を搬入し、

前記基板を搬入した後に前記微結晶半導体膜を形成することによって行われ、

前記微結晶半導体膜の形成は、珪素気体の流量に対する水素の流量比の増減を繰り返すことによって行われ、

前記微結晶半導体膜の形成は、前記基板の温度を100以上300以下に加熱して行われ、

前記微結晶半導体膜の成膜処理は、第1の期間と第2の期間を有し、

前記第2の期間は、前記第1の期間の後であり、

前記第1の期間において、アルゴン及びヘリウムが供給され、

前記第2の期間において、アルゴンが供給されず、ヘリウムが供給されることを特徴とする表示装置の作製方法。

## 【請求項 2】

請求項1において、

前記微結晶半導体膜の形成は、第1の高周波電源と第2の高周波電源とを用いてプラズマを生成し、プラズマCVD法を用いて行われ、

前記第1の高周波電源が供給する第1の高周波電力と、前記第2の高周波電源が供給する第2の高周波電力とは周波数が異なることを特徴とする表示装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の作製方法に関し、特に画素部に薄膜トランジスタを用いた表示装置及びその作製方法に関する。

【背景技術】

10

【0002】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。薄膜トランジスタには、チャネル領域を形成する半導体が非晶質シリコンで形成されるものと、多結晶シリコンで形成されるものがある。

【0003】

また、上記2種類の半導体の他にも、微結晶シリコン半導体でチャネル領域を形成するTFTが知られている（特許文献1及び特許文献2参照）。微結晶シリコンは、非晶質シリコンと同様にプラズマCVD法により作製される。例えば、プラズマCVD法による微結晶シリコン膜の作製方法として、30MHz以上のVHF（Very High Frequency）帯の高周波を利用する発明が開示されている（特許文献3参照）。

20

【0004】

一般的に、微結晶半導体膜をチャネル形成領域とするボトムゲート型の薄膜トランジスタを形成する場合、ゲート絶縁膜界面には非晶質構造を有する半導体膜が薄く形成され、薄膜トランジスタの電気特性に影響を及ぼすおそれがある。この問題を解決するため、例えば、特許文献4では、半導体膜の成膜速度を異ならせ成膜初期において成長速度を遅くし、その後成膜速度を高くする方法が提案されている。

【0005】

30

ところで液晶パネルは、マザーガラスと呼ばれる大面積ガラス基板上で複数枚のパネルを加工した後、最終的にテレビやパーソナルコンピュータの画面に合わせた寸法に分断して製造されている。1枚のマザーガラスから複数枚のパネルを取り出すようにして、パネル1枚当たりのコストを低減するためである。液晶テレビの市場では、画面サイズ（パネルサイズ）の大型化と販売価格の低下が急激に進んでいる。大画面化と低価格化に対応して生産性を向上するために、ここ数年、マザーガラスの大型化が進められている。

【0006】

第1世代と呼ばれる1991年頃の代表的なガラス基板のサイズは300mm×400mmであった。その後、マザーガラスのサイズは、第2世代（400mm×500mm）、第3世代（550mm×650mm）、第4世代（730mm×920mm）第5世代（1000mm×1200mm）、第6世代（2450mm×1850mm）、第7世代（1870mm×2200mm）、第8世代（2000mm×2400mm）、第9世代（2450mm×3050mm）、第10世代（2850mm×3050mm）と一途に大型化が図られている。

40

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4-242724号公報

【特許文献2】米国特許5,591,987号

【特許文献3】特許第3201492号公報

【特許文献4】特開平7-94749

50

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

しかしながら、成膜速度を低下させて微結晶半導体膜を形成する場合には、成膜速度の低下により反応室中に存在する酸素(O)等の不純物元素等が成膜される膜中に取り込まれやすく、酸素等が取り込まれることによって結晶化が阻害され、そのような微結晶半導体膜で形成された薄膜トランジスタの電気特性が低下するという問題がある。

**【0009】**

マザーガラス、即ちガラス基板が大面積化すると、そのガラス基板に微結晶シリコン膜を形成するためにプラズマCVD装置の電極面積も大型化することとなる。この場合、反応室の内壁の面積も大きくなるため、微結晶シリコン膜の成膜中に不純物元素が膜中に取り込まれやすくなる。

10

**【0010】**

また、ガラス基板の大きさが第6世代を超える当たりから、プラズマCVD装置の電極の大きさが、高周波電源の周波数の波長に近くなってくる。例えば、27MHzの電源周波数の場合、波長は1100mmであり、60MHzでは500mm、120MHzでは250mmとなる。このような場合、表面定在波の影響が顕著に現れるようになり、プラズマCVD装置の反応室内のプラズマ密度分布が不均一になり、ガラス基板に形成される薄膜の膜質や厚さの面内均一性が損なわれるといったことが問題となる。

20

**【0011】**

上述した問題に鑑み、本発明は、大面積の基板を用いた場合でも電気特性が高く信頼性のよい薄膜トランジスタ及び当該薄膜トランジスタを有する表示装置を提供することを課題とする。

**【課題を解決するための手段】****【0012】**

本発明の表示装置の作製方法の一は、基板上にゲート電極を形成する工程と、ゲート電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程とを有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成するものであって、反応室の圧力を一旦 $10^{-5}$ Pa以下とした後、基板の温度を100以上200以下として水素及び珪素気体を導入し、ゲート絶縁膜表面に形成される反応生成物に水素プラズマを作用させてエッティング(除去)を行いながら成膜を行うことによって、微結晶半導体膜を形成する。

30

**【0013】**

また、本発明の表示装置の作製方法の一は、基板上にゲート電極を形成する工程と、ゲート電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程とを有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成する工程であって、反応室の圧力を一旦 $10^{-5}$ Pa以下とした後、基板の温度を100以上200以下として水素及び希ガスを導入し、ゲート絶縁膜の表面に水素プラズマ及び希ガスプラズマを作用させた後、珪素気体を導入し、ゲート絶縁膜表面に形成される反応生成物に水素プラズマを作用させてエッティング(除去)を行いながら成膜を行うことによって、微結晶半導体膜を形成する。

40

**【0014】**

また、本発明の表示装置の作製方法の一は、基板上にゲート電極を形成する工程と、ゲート電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程とを有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成

50

されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成する工程であって、反応室の圧力を一旦  $10^{-5}$  Pa 以下とした後、基板の温度を 100 以上 200 以下として水素及び珪素気体を導入し、HF 帯 (3 MHz ~ 30 MHz、代表的には 13.5 6 MHz) の第 1 の高周波電力と、VHF 帯 (30 MHz ~ 300 MHz 程度まで) の第 2 の高周波電力を重畠して印加することによりプラズマの生成を行い、ゲート絶縁膜表面に形成される反応生成物に水素プラズマを作用させて除去しつつ成膜を行うことによって、微結晶半導体膜を形成する。

【0015】

また、本発明の表示装置の作製方法の一は、基板上にゲート電極を形成する工程と、ゲート電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマ CVD 法を用いて微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程とを有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成する工程であって、反応室の圧力を一旦  $10^{-5}$  Pa 以下とした後、基板の温度を 100 以上 200 以下として水素及び希ガスを導入し、HF 帯の第 1 の高周波電力と、VHF 帯の第 2 の高周波電力を重畠して印加することによりプラズマの生成を行い、ゲート絶縁膜の表面に水素プラズマ及び希ガスプラズマを作用させた後、珪素気体を導入し、ゲート絶縁膜表面に形成される反応生成物に水素プラズマを作用させて除去しつつ成膜を行うことによって、微結晶半導体膜を形成する。

【0016】

また、本発明の表示装置の作製方法の一は、珪素気体を導入する前に希ガスの導入を停止又は希ガスの流量比を低減することを特徴とする。

【0017】

また、本発明の表示装置の作製方法の一は、珪素気体の導入後、所定の期間経過後に希ガスの導入を停止又は希ガスの流量比を低減することを特徴とする。

【0018】

また、本発明の表示装置の作製方法の一は、微結晶半導体膜の膜中の酸素濃度を  $1 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下にすることを特徴とする。

【0019】

また、表示装置としては、発光装置や液晶表示装置を含む。発光装置は発光素子を含み、液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 EL (Electro Luminescence)、有機 EL 等が含まれる。

【0020】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む IC 等を実装した状態にあるモジュールとを含む。

【発明の効果】

【0021】

本発明により、電気特性が高く信頼性の高い薄膜トランジスタ及び当該薄膜トランジスタを有する表示装置を作製することができる。

【図面の簡単な説明】

【0022】

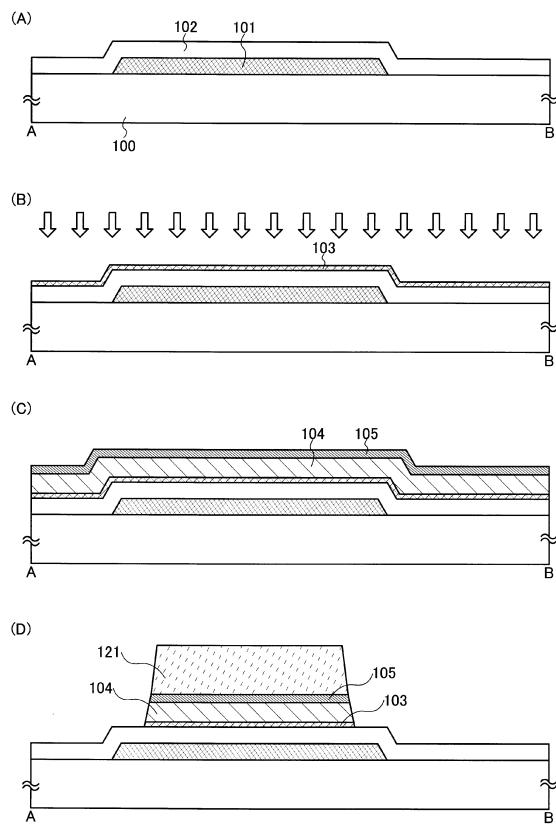

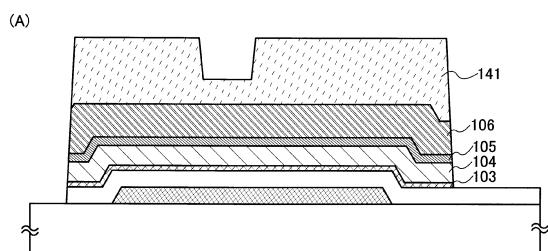

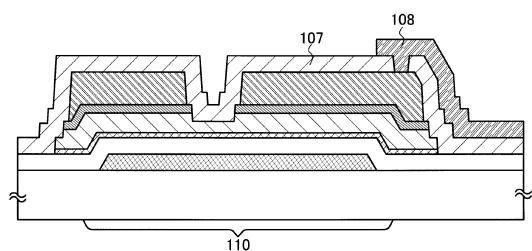

【図 1】本発明の表示装置の作製方法の一例を示す図。

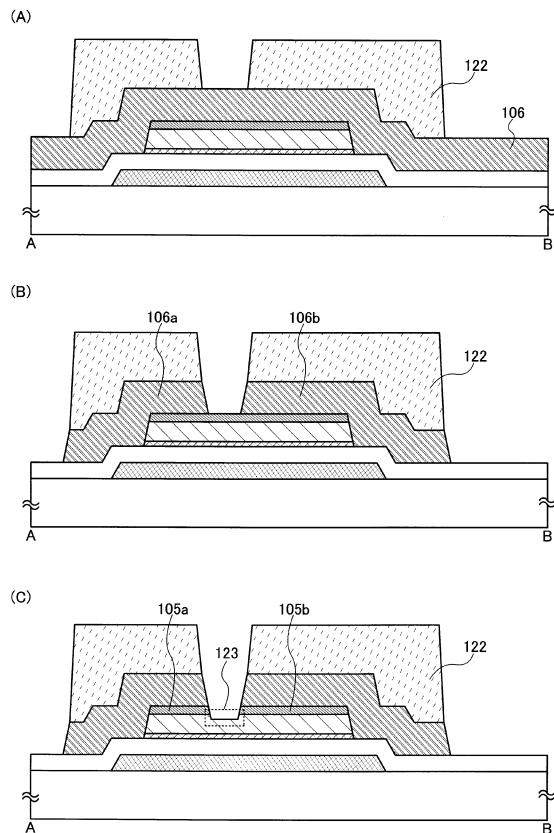

【図 2】本発明の表示装置の作製方法の一例を示す図。

【図 3】本発明の表示装置の作製方法の一例を示す図。

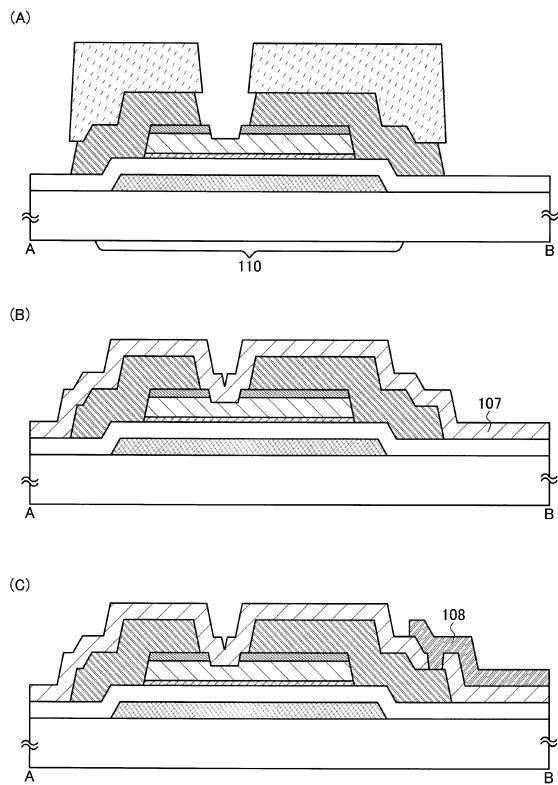

【図 4】本発明の表示装置の作製方法の一例を示す図。

【図 5】本発明の表示装置の作製方法の一例を示す図。

【図 6】本発明の表示装置の作製方法の一例を示す図。

【図 7】本発明の表示装置の作製方法の一例を示す図。

【図 8】本発明の表示装置の作製方法の一例を示す図。

10

20

30

40

50

【図9】本発明の表示装置の作製方法の一例を示す図。

【図10】本発明の表示装置の作製方法の一例を示す図。

【図11】本発明の表示装置の作製に用いるプラズマCVD装置の一例を示す図。

【図12】本発明の表示装置の作製に用いるプラズマCVD装置の一例を示す図。

【図13】本発明の表示装置の使用形態の一例を示す図。

【図14】本発明の表示装置の使用形態の一例を示す図。

【図15】本発明の表示装置の作製方法の一例を示す図。

【図16】本発明の表示装置の使用形態の一例を示す図。

【図17】本発明の表示装置の使用形態の一例を示す図。

【図18】本発明の表示装置の作製に用いるプラズマCVD装置の一例を示す図。

10

【発明を実施するための形態】

【0023】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態および詳細を変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0024】

(実施の形態1)

20

本実施の形態では、ボトムゲート型の薄膜トランジスタ(TFT)を有する表示装置の作製方法に関して図面を参照して説明する。以下の説明では、nチャネル型の薄膜トランジスタについて説明する。

【0025】

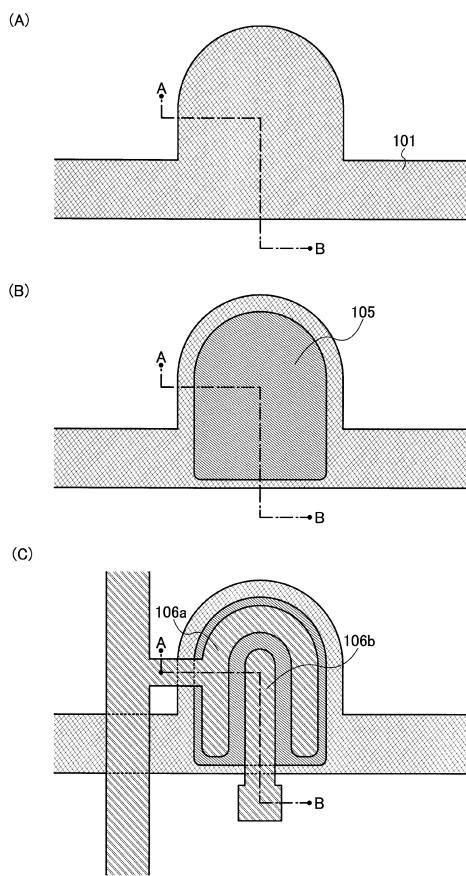

まず、基板100上にゲート電極101を形成し、当該ゲート電極101上にゲート絶縁膜を形成する(図1(A)、図5(A)参照)。

【0026】

基板100は、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、若しくはアルミニノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。

30

【0027】

ゲート電極101は、チタン、モリブデン、クロム、タンタル、タングステン、アルミニウムなどの金属またはその合金を用いて形成する。ゲート電極101は、スパッタリング法や真空蒸着法で基板100上に導電膜を形成し、当該導電膜上にフォトリソグラフィ技術またはインクジェット法によりレジストマスクを形成し、当該マスクを用いて導電膜をエッチングすることで形成することができる。なお、ゲート電極101の密着性向上と下地への不純物元素の拡散を防ぐバリアメタルとして、上記金属の窒化物膜を、基板100及びゲート電極101の間に設けてもよい。

40

【0028】

ゲート絶縁膜102は、CVD法やスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、または窒化酸化珪素膜で形成することができる。ここでは、ゲート絶縁膜102として、酸化珪素膜または酸化窒化珪素膜と、窒化珪素膜または窒化酸化珪素膜との順に積層して形成する。なお、ゲート絶縁膜を2層とせず、基板側から窒化珪素膜または窒化酸化珪素膜と、酸化珪素膜または酸化窒化珪素膜と、窒化珪素膜または窒化酸化珪素膜との順に3層積層して形成してもよい。また、ゲート絶縁膜を、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、または窒化酸化珪素膜の単層で形成してもよい。

【0029】

なお、酸化窒化珪素膜とは、その組成として、窒素よりも酸素の含有量が多いものであつ

50

て、濃度範囲として酸素が 55 ~ 65 原子%、窒素が 1 ~ 20 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものという。また、窒化酸化珪素膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が 15 ~ 30 原子%、窒素が 20 ~ 35 原子%、Si が 25 ~ 35 原子%、水素が 15 ~ 25 原子% の範囲で含まれるものという。

#### 【0030】

次に、ゲート絶縁膜 102 上に微結晶構造を有する微結晶半導体膜 103（例えば、微結晶シリコン膜）を形成する（図 1（B）参照）。

#### 【0031】

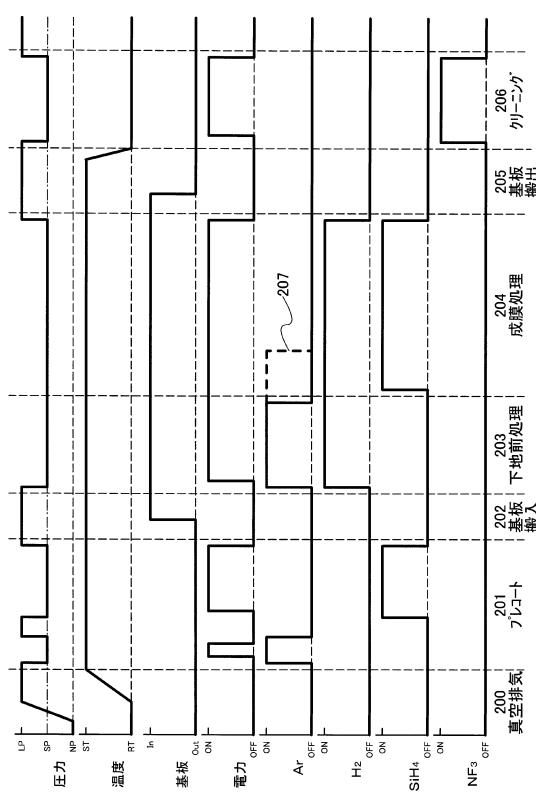

微結晶半導体膜 103 は、プラズマ CVD 法により反応生成物を堆積させることにより形成する。以下に、図 4 を参照して微結晶シリコン膜を成膜する工程の一例に関して説明する。なお、図 4 の説明は反応室を大気圧から真空排気 200 する段階から示されており、その後に行われるプレコート 201、基板搬入 202、下地前処理 203、成膜処理 204、基板搬出 205、クリーニング 206 の各処理が時系列的に示されている。

10

#### 【0032】

まず、反応室内を所定の真空度まで真空排気する。本実施の形態では、一旦超高真空（10<sup>-5</sup> Pa 以下）とし反応室内の酸素（O）等の不純物元素を極力低減する。真空度として 10<sup>-5</sup> Pa よりも低い圧力の超高真空排気する場合には、ターボ分子ポンプによる排気を行い、さらにクライオポンプを使って真空排気する。また、反応室を加熱処理して内壁からの脱ガス処理を行うことが好ましい。また、基板を加熱するヒータも動作させて温度を安定化させる。基板の加熱温度は 100 以上 300 以下、好ましくは 100 以上 200 以下で行う。

20

#### 【0033】

プレコート 201 は、反応室の内壁に吸着した気体（酸素及び窒素などの大気成分、若しくは反応室のクリーニングに使用したエッチングガス）を除去するためにアルゴンなどの希ガスを導入してプラズマ処理を行うことが好ましい。この処理により到達真空度を上げることができる。反応室の内壁を基板上に堆積されるべき膜と同種の膜で被覆する処理が含まれている。本形態は微結晶シリコン膜を形成する工程を示し、内壁被覆膜としてシリコン膜を形成する処理が行われる。プレコート 201 はシランガスが導入された後、高周波電力を印加してプラズマを生成する。シランガスは酸素、水分等と反応するので、シランガスを流し、さらにシランプラズマを生成することで反応室の酸素、水分を除去することができる。

30

#### 【0034】

プレコート 201 の後、基板搬入 202 を行う。微結晶シリコン膜が堆積されるべき基板は、真空排気されたロード室に保管されているので、基板を搬入したとしても真空度が著しく悪化することはない。

#### 【0035】

下地前処理 203 は、微結晶シリコン膜を形成する場合において、特に有効な処理であり行うことが好ましい。すなわち、ガラス基板上に設けられたゲート絶縁膜の表面上に微結晶シリコン膜をプラズマ CVD 法で成膜する場合には、不純物や格子不整合などの要因により堆積初期段階において堆積された反応生成物（半導体膜）には非晶質層が形成されてしまう。この非晶質層の厚さを極力低減し、可能であれば無くすために下地前処理 203 を行うことが好ましい。

40

#### 【0036】

下地前処理 203 としては希ガスプラズマ処理、水素プラズマ処理若しくはこの両者の併用により行うことが好ましい。希ガスプラズマ処理としては、アルゴン、クリプトン、キセノンなど質量数の大きい希ガス元素を用いることが好ましい。表面に付着した酸素、水分、有機物、金属元素などをスパッタリングの効果で除去するためである。水素プラズマ処理は、水素ラジカルにより、表面に吸着した前記不純物の除去と、絶縁膜若しくは非晶質シリコン膜に対するエッチング作用により清浄表面を形成するのに有効である。また、

50

希ガスプラズマ処理と水素プラズマ処理を併用することにより微結晶核生成を促進する作用も実現される。

【0037】

微結晶シリコン膜を形成する成膜処理204は、下地前処理203に続いて行われる処理である。微結晶シリコン膜は、水素及び珪素気体（水素化珪素気体又はハロゲン化珪素気体）を混合してプラズマにより成膜する。珪素気体は水素で10倍から2000倍に希釈される。

【0038】

ここでは、成膜の初期段階にゲート絶縁膜102表面に形成される半導体膜に水素プラズマを作用させて除去（エッティング）しつつ成膜を行い、微結晶半導体膜を形成する。つまり、 $\text{SiH}_3$ ラジカルの堆積による膜成長反応と、水素ラジカルによるエッティング反応とを競争的に起こさせて微結晶構造を含む半導体膜を形成する。

10

【0039】

また、微結晶半導体膜の結晶性を向上させるため、微結晶半導体膜の膜中の酸素濃度を $1 \times 10^{17} \text{ atoms/cm}^3$ 以下とするように形成を行うことが好ましい。膜中の酸素濃度は、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）を用いて測定することができる。

【0040】

本実施の形態では、成膜の初期段階にゲート絶縁膜102に堆積される半導体膜を水素プラズマ処理で除去（エッティング）しつつ成膜を行うことにより、ゲート絶縁膜102上に形成される結晶核生成を促進させ、当該結晶核を利用して微結晶半導体膜を形成する。そのため、不純物や格子不整合などの要因により堆積初期段階において堆積された半導体膜に非晶質層が形成された場合であっても、この非晶質層の厚さを極力低減し、ゲート絶縁膜102により近く微結晶半導体膜を形成することが可能となる。

20

【0041】

また、本実施の形態では、ゲート絶縁膜102表面に形成された半導体膜を除去しつつ成膜を行うので成膜速度が遅くなるが、成膜前に反応室の圧力を一旦超高真空（ $10^{-5} \text{ Pa}$ 以下）とし反応室内の水分や酸素（O）等の吸着不純物の不純物元素を低減した後に成膜を行うことによって、成膜速度を遅くした場合であっても膜中への酸素（O）等の不純物元素の取り込み（半導体膜の酸化等）を低減し、結晶化の阻害を抑制することができる。その結果、ゲート絶縁膜102により近く結晶性が高い半導体膜を形成することができる。

30

【0042】

なお、水素プラズマ処理は、珪素気体の流量に対する水素の流量比を調整することによって行う。例えば、成膜が進につれ、珪素気体の流量に対する水素の流量比が小さくなるように珪素気体の流量を増加させる。成膜開始時には水素の流量：珪素気体の流量を2000：1程度にしておき、成膜終了時には50：1程度になるまで徐々に珪素気体の流量を増加（水素の流量を減少）させ微結晶半導体膜を形成することができる。

【0043】

また、珪素気体の流量に対する水素の流量比の増減を繰り返して、水素プラズマ処理を繰り返して行ってもよい。この場合、半導体膜の堆積と半導体膜の除去（エッティング）を繰り返し行うことによって、ゲート絶縁膜102上に形成される結晶核生成を促進させることができる。

40

【0044】

また、図4中の破線207で示すように、微結晶シリコン膜の成膜初期段階においてアルゴンなどの希ガスを供給し続ける期間を設けてもよい。成膜の初期段階にゲート絶縁膜102表面に堆積される半導体膜に、アルゴンプラズマを作用させて表面の改質を行い、表面に吸着した水分や不純物の除去を行うことによって、微結晶核の生成を促進させることができる。

【0045】

50

また、基板の加熱温度は100以上300以下、好ましくは100以上200以下で行う。微結晶シリコン膜の成長表面を水素で不活性化し、微結晶シリコンの成長を促進するためには100以上200以下で成膜を行うことが好ましい。

【0046】

微結晶半導体膜103は、周波数が数十MHz～数百MHzの高周波プラズマCVD装置、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。

【0047】

他にも、HF帯(3MHz～30MHz、代表的には13.56MHz)とVHF帯(30MHz～300MHz程度まで)の高周波電力を重畠印加して生成されるプラズマを利用して成膜やプラズマ処理をしてもよい。表面定在波を引き起こさない第1の高周波電力を供給してプラズマを生成するとともに、VHF帯に属する第2の高周波電力を供給してプラズマの高密度化を図ることで長辺が2000mmを超える大面積基板に均質で膜質の良い薄膜を形成することが可能となる。

10

【0048】

プラズマ処理を行う際に、プレコート201の処理をしておくことで、微結晶シリコン膜中に反応室を構成する金属を不純物として取り込んでしまうのを防ぐことができる。すなわち、反応室内をシリコンで被覆しておくことで、反応室内がプラズマにより食刻されるのを防ぐことができ、微結晶シリコン膜中に含まれる不純物濃度を低減することができる。

20

【0049】

成膜処理204においては、反応ガスにヘリウムを加えても良い。ヘリウムは24.5eVとすべての気体中で最も高いイオン化エネルギーを持ち、そのイオン化エネルギーよりも少し低い、約20eVの準位に準安定状態があるので、放電持続中においては、イオン化にはその差約4eVしか必要としない。そのため放電開始電圧も全ての気体中最も低い値を示す。このような特性から、ヘリウムはプラズマを安定的に維持することができる。また、均一なプラズマを形成することができるので、微結晶シリコン膜を堆積する基板の面積が大きくなてもプラズマ密度の均一化を図る効果を奏する。

【0050】

微結晶シリコンの成膜が終了した後、シラン、水素などの反応ガス及び高周波電力の供給を止めて基板搬出205を行う。引き続き別基板に対して成膜処理を行う場合には、基板搬入202の段階に戻り同じ処理が行われる。反応室内に付着した被膜や粉末を除去するには、クリーニング206を行う。

30

【0051】

クリーニング206はNF<sub>3</sub>、SF<sub>6</sub>に代表されるエッティングガスを導入してプラズマエッティングを行う。また、ClF<sub>3</sub>のようにプラズマを利用しなくてもエッティングが可能なガスを導入して行う。クリーニング206においては基板加熱用のヒータを切って、温度を下げるが好ましい。エッティングによる反応副生成物の生成を抑えるためである。クリーニング206の終了後はプレコート201に戻り、以下同様の処理を行えば良い。

40

【0052】

また、本実施の形態で成膜する微結晶半導体膜103は、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5～20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520.6cm<sup>-1</sup>よりも低波数側に、シフトしている。即ち、481cm<sup>-1</sup>以上520.6cm<sup>-1</sup>以下の間に微結晶シリコンのラマンスペクトルのピークがある。

【0053】

50

また、薄膜トランジスタのチャネル形成領域として機能する微結晶半導体膜に対しては、p型を付与する不純物元素を、成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物元素としては、代表的にはホウ素であり、トリメチルボロン( $\text{C H}_3\text{)}_3\text{B}$ 、 $\text{B}_2\text{H}_6$ 、 $\text{B F}_3$ などの不純物気体を1 ppm ~ 1000 ppm、好ましくは1 ~ 100 ppmの割合で水素化珪素に混入させると良い。そしてボロンの濃度を、例えば $1 \times 10^{14} \sim 6 \times 10^{16}$  atoms/cm<sup>3</sup>とするといい。トリメチルボロンは、反応室の内壁等に付着した場合であってもクリーニングにより容易に除去できるためトリメチルボロンを用いることが好ましい。ボロンの濃度を制御することによって、i型又はp型の微結晶半導体膜を形成することができる。

## 【0054】

10

また、微結晶半導体膜103は、0 nmより厚く50 nm以下、好ましくは0 nmより厚く20 nm以下で形成する。微結晶半導体膜103は、後に形成される薄膜トランジスタのチャネル形成領域として機能する。微結晶半導体膜の厚さを上記の範囲内とすることと、後に形成される薄膜トランジスタは、完全空乏型とすることができます。

## 【0055】

また、微結晶半導体膜103は成膜速度が非晶質半導体の成膜速度の1/10 ~ 1/100と遅いため、膜厚を薄くすることでスループットを向上させることができます。

## 【0056】

20

次に、微結晶半導体膜103上に、バッファー層として機能する非晶質半導体膜104(例えば、非晶質シリコン膜)、一導電型を付与する不純物が添加された半導体膜105を順に形成する(図1(C)参照)。

## 【0057】

なお、ゲート絶縁膜102、微結晶半導体膜103及び非晶質半導体膜104は連続的に形成することが好ましい。さらには、ゲート絶縁膜102、微結晶半導体膜103、非晶質半導体膜104、及び一導電型を付与する不純物が添加された半導体膜105を連続的に形成することが好ましい。ゲート絶縁膜102、微結晶半導体膜103、及び非晶質半導体膜104を大気に触れさせることなく連続成膜することで、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができるので、薄膜トランジスタ特性のばらつきを低減することができる。

## 【0058】

30

また、非晶質半導体膜104は、微結晶半導体膜103を形成した後、水素及び珪素気体の流量をさらに制御し、水素を減少、珪素気体を増加させ、珪素気体の流量に対する水素の流量比を小さくすることで微結晶半導体膜上に連続的に形成してもよい。非晶質半導体膜104を形成する工程は、より水素の流量を減少させ、珪素気体(水素化珪素気体、又はハロゲン化珪素気体)のみで行ってもよい。この場合、微結晶半導体膜103の成長表面を大気に触れさせることなく、微結晶半導体膜103上に非晶質半導体膜104を形成することができる。

## 【0059】

40

バッファー層として機能する非晶質半導体膜104は、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ などの水素化珪素を用いて、プラズマCVD法により形成することができる。また、上記水素化珪素に、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して非晶質半導体を形成することができる。水素化珪素の流量の1倍以上20倍以下、好ましくは1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素を用いて、水素を含む非晶質半導体を形成することができる。また、上記水素化珪素と窒素またはアンモニアとを用いることで、窒素を含む非晶質半導体を形成することができる。また、上記水素化珪素と、フッ素、塩素、臭素、またはヨウ素を含む気体( $\text{F}_2$ 、 $\text{Cl}_2$ 、 $\text{Br}_2$ 、 $\text{I}_2$ 、 $\text{HF}$ 、 $\text{HCl}$ 、 $\text{HBr}$ 、 $\text{HI}$ 等)を用いることで、フッ素、塩素、臭素、またはヨウ素を含む非晶質半導体を形成することができる。なお、水素化珪素の代わりに、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ 等を用いることができる。

## 【0060】

50

また、非晶質半導体膜104は、ターゲットに非晶質半導体を用いて水素、または希ガスでスパッタリングして非晶質半導体膜を形成することができる。このとき、アンモニア、窒素、またはN<sub>2</sub>Oを雰囲気中に含ませることにより、窒素を含む非晶質半導体膜を形成することができる。また、雰囲気中にフッ素、塩素、臭素、またはヨウ素を含む気体(F<sub>2</sub>、Cl<sub>2</sub>、Br<sub>2</sub>、I<sub>2</sub>、HF、HCl、HBr、HI等)を含ませることにより、フッ素、塩素、臭素、またはヨウ素を含む非晶質半導体を形成することができる。

#### 【0061】

非晶質半導体膜104は、結晶粒を含まない非晶質半導体で形成することが好ましい。このため、周波数が数十MHz～数百MHzの高周波プラズマCVD法、またはマイクロ波プラズマCVD法で形成する場合は、結晶粒を含まない非晶質半導体となるように、成膜条件を制御することが好ましい。また、非晶質半導体膜104は、n型の電気伝導性を示す非晶質半導体(例えば、非晶質シリコン膜)で形成してもよい。

10

#### 【0062】

非晶質半導体膜104は、後のソース領域及びドレイン領域の形成プロセスにおいて、一部エッチングされる場合があるが、そのときに、非晶質半導体膜104の一部が残存する厚さで形成することが好ましい。代表的には、100nm以上500nm以下、好ましくは200nm以上300nm以下の厚さで形成することが好ましい。薄膜トランジスタに高い電圧(例えば15V程度)を印加する表示装置、代表的には液晶表示装置において、バッファー層として機能する非晶質半導体膜104の膜厚を上記範囲に示すように厚く形成すると、耐圧が高くなり、薄膜トランジスタに高い電圧が印加されても、薄膜トランジスタが劣化することを回避することができる。非晶質半導体膜104を上記の膜厚の範囲で形成することにより、非晶質半導体膜104は微結晶半導体膜103より厚く形成される。

20

#### 【0063】

微結晶半導体膜103の表面に、非晶質半導体膜、更には水素、窒素、またはハロゲンを含む非晶質半導体膜を形成することで、微結晶半導体膜103に含まれる結晶粒の表面の自然酸化を防止することが可能である。特に、非晶質半導体と微結晶粒が接する領域では、結晶格子の歪に由来し、亀裂が入りやすい。この亀裂が酸素に触れると結晶粒は酸化され、酸化珪素が形成される。しかしながら、微結晶半導体膜103の表面にバッファー層として機能する非晶質半導体膜104を形成することで、微結晶半導体膜103に含まれる微結晶粒の酸化を防ぐことができる。また、バッファー層を形成することで、後にソース領域及びドレイン領域を形成する際に発生するエッチング残渣が微結晶半導体に混入することを防ぐことができる。

30

#### 【0064】

また、非晶質半導体膜104は、非晶質半導体を用いて形成するため、または、水素、窒素、若しくはハロゲンを含む非晶質半導体で形成するため、非晶質半導体のエネルギーギヤップが微結晶半導体に比べて大きく(非晶質半導体のエネルギーギヤップは1.6～1.8eV、微結晶半導体のエネルギーギヤップは1.1～1.5eV)、抵抗が高く、移動度が低くなる。このため、後に形成される薄膜トランジスタにおいて、ソース領域及びドレイン領域と、微結晶半導体膜103との間に形成される非晶質半導体膜104は高抵抗領域として機能し、微結晶半導体膜103を構成する微結晶半導体がチャネル形成領域として機能する。

40

#### 【0065】

一導電型を付与する不純物が添加された半導体膜105は、nチャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてリンを添加すれば良く、水素化珪素にPH<sub>3</sub>などの不純物気体を加えれば良い。また、pチャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてボロンを添加すれば良く、水素化珪素にトリメチルボロン(C<sub>2</sub>H<sub>3</sub>)<sub>3</sub>B、B<sub>2</sub>H<sub>6</sub>などの不純物気体を加えれば良い。一導電型を付与する不純物が添加された半導体膜105は、微結晶半導体、または非晶質半導体で形成することができる。一導電型を付与する不純物が添加された半導体膜105は2nm以上

50

50 nm以下の厚さで形成する。一導電型を付与する不純物が添加された半導体膜の膜厚を、薄くすることでスループットを向上させることができる。

【0066】

次に、一導電型を付与する不純物が添加された半導体膜105上にマスク121を形成し、当該マスク121を用いて微結晶半導体膜103、非晶質半導体膜104及び導電型を付与する不純物が添加された半導体膜105をエッティングする(図1(D)、図5(B)参照)。この後、マスク121を除去する。

【0067】

マスク121は、フォトリソグラフィ技術又はインクジェット法により形成する。

【0068】

次に、エッティングにより残存した半導体膜105及びゲート絶縁膜102上に導電膜106を形成し、当該導電膜106上にマスク122を形成する(図2(A)参照)。

【0069】

導電膜106は、アルミニウム、若しくは銅、シリコン、チタン、ネオジム、スカンジウム、モリブデンなどの耐熱性向上元素若しくはヒロック防止元素が添加されたアルミニウム合金の単層または積層で形成することが好ましい。また、半導体膜105と接する側の膜を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で形成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としても良い。更には、アルミニウムまたはアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で挟んだ積層構造としてもよい。例えば、導電膜106として、モリブデン膜とアルミニウム膜とモリブデン膜を順に3層積層した構造とすることができる。また、導電膜106として、チタン膜とアルミニウム膜とチタン膜を順に3層積層した構造とすることができる。

【0070】

導電膜106は、スパッタリング法や真空蒸着法で形成する。また、導電膜106は、銀、金、銅などの導電性ナノペーストを用いてスクリーン印刷法、インクジェット法等を用いて吐出し焼成して形成しても良い。

【0071】

マスク122は、マスク121と同様に形成することができる。

【0072】

なお、本実施の形態では、図1(C)において、微結晶半導体膜103、非晶質半導体膜104及び半導体膜105をパターニングした後に導電膜106を形成する場合を示しているが、図1(C)の工程を省略し、微結晶半導体膜103、非晶質半導体膜104、半導体膜105及び導電膜106を連続して順に積層させた後にマスク122を形成してもよい。この場合、マスク121を形成しなくてよいため、工程を簡略化することができる。

【0073】

次に、マスク122を用いて導電膜106をエッティングして分離することにより、ソース電極106a及びドレイン電極106bを形成する(図2(B)、図5(C)参照)。

【0074】

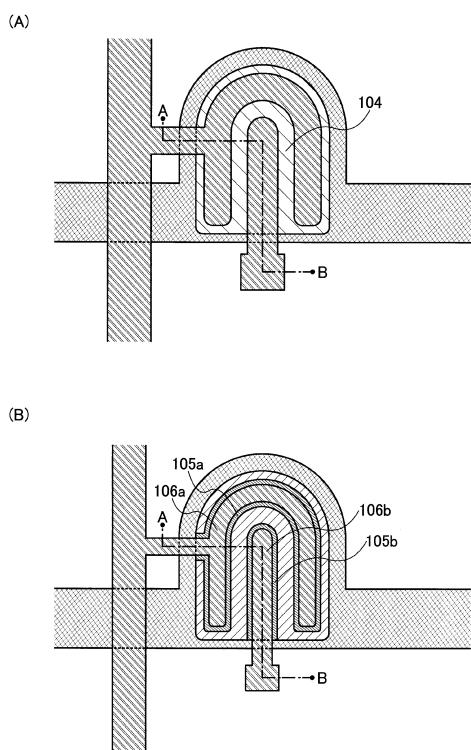

次に、マスク122を用いて導電型を付与する不純物が添加された半導体膜105及びバッファー層として機能する非晶質半導体膜104をエッティングして、ソース領域105a及びドレイン領域105b、ソース電極106a及びドレイン電極106bを形成する(図2(C)、図6(A)参照)。なお、バッファー層として機能する非晶質半導体膜104は一部のみがエッティングされたものであり、微結晶半導体膜103の表面を覆っている。ここでは、ソース領域105aとドレイン領域105bの間に位置する非晶質半導体膜104の表面に凹部が形成される。また、このとき、ソース領域105a及びドレイン領域105bの端部とソース電極106a及びドレイン電極106bの端部はほぼ一致している。

【0075】

10

20

30

40

50

次に、ソース電極 106a 及びドレイン電極 106b の一部をエッチングする（図 3（A）

）、図 6（B）参照）。

#### 【0076】

ここでは、マスク 122 を用いて、ウエットエッチングすると、ソース電極 106a 及び

ドレイン電極 106b の端部が選択的にエッチングされる。その結果、ソース電極 106

a 及びドレイン電極 106b の端部と、ソース領域 105a 及びドレイン領域 105b の

端部はそれぞれ一致せずずれており、ソース電極 106a 及びドレイン電極 106b の端

部の外側に、ソース領域 105a 及びドレイン領域 105b の端部が形成される。

#### 【0077】

この後、マスク 122 を除去する。また、ソース電極 106a 又はドレイン電極 106b

は、それぞれソース配線またはドレイン配線としても機能する。 10

#### 【0078】

ソース領域 105a とソース電極 106a の端部、ドレイン領域 105b とドレイン電極

106b の端部がそれぞれ一致せずずれた形状となることで、ソース電極 106a とドレ

イン電極 106b との端部の距離が離れるため、ソース電極 106a とドレイン電極 10

6b 間のリーク電流やショートを防止することができる。また、ソース領域 105a とソ

ース電極 106a の端部、ドレイン領域 105b とドレイン電極 106b の端部がそれ

ぞれ一致せずずれた形状となることで、ソース電極 106a 及びドレイン電極 106b 、ソ

ース領域 105a 及びドレイン領域 105b の端部に電界が集中せず、ゲート電極 101

と、ソース電極 106a 及びドレイン電極 106b との間でのリーク電流を防止する

ことができる。このため、信頼性が高く、且つ耐圧の高い薄膜トランジスタを作製する

ことができる。 20

#### 【0079】

以上の工程により、チャネルエッチ型の薄膜トランジスタ 110 を形成することができる

。

#### 【0080】

本実施の形態で示す薄膜トランジスタは、非晶質半導体膜 104 の一部には凹部（溝）が

形成されており、当該凹部以外の領域がソース領域 105a 及びドレイン領域で覆われる

。即ち、非晶質半導体膜 104 に形成される凹部 123 により、ソース領域 105a 及び

ドレイン領域 105b の距離が離れているため、ソース領域 105a 及びドレイン領域 1

05b の間でのリーク電流を低減することができる。また、非晶質半導体膜 104 の一部

をエッチングすることにより凹部 123 を形成するため、ソース領域 105a 及びドレ

イン領域 105b の形成工程において発生するエッチング残渣を除去することができるため

、残渣を介してソース領域 105a 及びドレイン領域 105b にリーク電流（寄生チャネ

ル）が発生することを回避することができる。 30

#### 【0081】

また、チャネル形成領域として機能する微結晶半導体とソース領域 105a 及びドレイン

領域 105b との間に、バッファー層が形成されている。また、微結晶半導体の表面がバ

ッファー層で覆われている。高抵抗で形成されたバッファー層は、微結晶半導体と、ソ

ース領域 105a 及びドレイン領域 105b との間にまで延在しているため、薄膜トランジ

スタにリーク電流が発生することを低減することができると共に、高い電圧の印加による

劣化を低減することができる。また、微結晶半導体の表面に水素で表面が終端された非晶

質半導体がバッファー層として形成されているため、微結晶半導体の酸化を防止するこ

とが可能であると共に、ソース領域 105a 及びドレイン領域 105b の形成工程に発生す

るエッチング残渣が微結晶半導体に混入することを防ぐことができる。 40

#### 【0082】

また、ソース電極及びドレイン電極の端部と、ソース領域及びドレイン領域の端部は一致

せずずれた形状となることで、ソース電極及びドレイン電極の端部の距離が離れるため、

ソース電極及びドレイン電極間のリーク電流やショートを防止することができる。

#### 【0083】

10

20

30

40

50

次に、ソース電極 106a 及びドレイン電極 106b、ソース領域 105a 及びドレイン領域 105b、非晶質半導体膜 104 及びゲート絶縁膜 102 上に絶縁膜 107 を形成する（図 3（B）参照）。絶縁膜 107 は、ゲート絶縁膜 102 と同様に形成することができる。なお、絶縁膜 107 は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。

#### 【0084】

次に、絶縁膜 107 にコンタクトホールを形成し、当該コンタクトホールにおいてドレイン電極 106b に接する画素電極 108 を形成する（図 3（C）、図 7 参照）。

#### 【0085】

画素電極 108 は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITO と示す）、インジウム亜鉛酸化物、酸化珪素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

10

#### 【0086】

また、画素電極 108 として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が 10000 / 以下、波長 550 nm における透光率が 70% 以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が 0.1 · cm 以下であることが好ましい。

20

#### 【0087】

導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの 2 種以上の共重合体などがあげられる。

#### 【0088】

以上の工程により、薄膜トランジスタ 110 を画素部に有する表示装置を形成することができる。なお、本実施の形態では、n チャネル型の薄膜トランジスタを形成する場合を示したが、これに限らず、p チャネル型の薄膜トランジスタも一導電型を付与する不純物が添加された半導体膜 105 を p 型とすることによって同様に形成することができる。

30

#### 【0089】

本実施の形態で示した薄膜トランジスタ 110 は、作製工程数が少なく、コスト削減が可能である。また、チャネル形成領域として機能する微結晶半導体膜 103 を微結晶半導体で構成することにより  $1 \sim 20 \text{ cm}^2 / \text{V} \cdot \text{sec}$  の電界効果移動度を得ることができる。従って、本実施の形態では、薄膜トランジスタ 110 を画素部の画素のスイッチング用素子として適用する例を示したが、これに限らず走査線（ゲート線）側の駆動回路等を形成する素子として利用することができる。

#### 【0090】

本実施の形態は、他の実施の形態に記載した構成や作製方法と組み合わせて実施することが可能である。

40

#### 【0091】

##### （実施の形態 2）

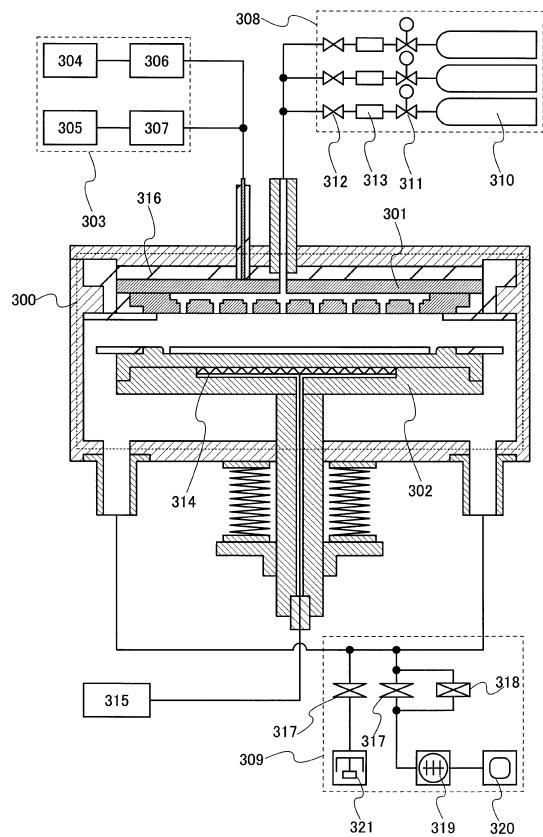

本実施の形態では、上記実施の形態 1 において微結晶半導体膜の成膜に用いたプラズマ CVD 装置の一構成例に関して図 11 を参照して説明する。具体的に、本実施の形態では、複数の高周波電力が印加されるプラズマ CVD 装置の一構成例に関して説明する。

#### 【0092】

反応室 300 はアルミニウム又はステンレスなど剛性のある素材で形成され、内部を真空排気できるように構成されている。反応室 300 には第 1 の電極 301 と第 2 の電極 302 が備えられている。

#### 【0093】

第 1 の電極 301 には高周波電力供給手段 303 が連結され、第 2 の電極 302 は接地電

50

位が与えられ、基板を載置できるように構成されている。第1の電極301は絶縁材316により反応室300の内壁と絶縁分離され、高周波電力が漏洩しないように構成されている。なお、図11では、第1の電極301と第2の電極302について容量結合型(平行平板型)の構成を示しているが、異なる二以上の高周波電力を印加して反応室300の内部にプラズマを生成できるものであれば、誘導結合型など他の構成を適用することもできる。

【0094】

高周波電力供給手段303は、第1の高周波電源304と第2の高周波電源305、及びそれらに対応して第1の整合器306と第2の整合器307が含まれている。第1の高周波電源304と第2の高周波電源305から出力される高周波電力は、共に第1の電極301に供給される。第1の整合器306又は第2の整合器307の出力側には、一方の高周波電力が流入しないように帯域通過フィルタを設けても良い。

10

【0095】

第1の高周波電源304が供給する高周波電力は、概ね波長として10m以上の高周波が適用され、HF帯である3MHzから30MHz、代表的には13.56MHzの周波数が適用される。第2の高周波電源305が供給する高周波電力は、VHF帯の周波数であり概ね波長が10m未満の高周波が適用され、30MHz～300MHzの高周波電力が適用される。

【0096】

すなわち、第1の高周波電源304が供給する高周波電力の波長は、第1の電極301の1辺の長さの3倍以上を有し、第2の高周波電源305が供給する高周波電力の波長は、それよりも短い波長を適用する。表面定在波を引き起こさない高周波電力を第1の電極301に供給してプラズマを生成するとともに、VHF帯に属する高周波電力を供給してプラズマの高密度化を図ることで長辺が2000mmを超える大面積基板に均質で膜質の良い薄膜を形成することが可能となる。

20

【0097】

第1の電極301はガス供給手段308にも連結されている。ガス供給手段308は、反応ガスが充填されるシリンドラ310、圧力調整弁311、ストップバルブ312、マスフローコントローラ313などで構成されている。反応室300内において、第1の電極301は基板と対抗する面がシャワー板状に加工され、複数の細孔が設けられている。反応ガスは、第1の電極301の内部の中空構造からこの細孔を通って反応室300に供給される。

30

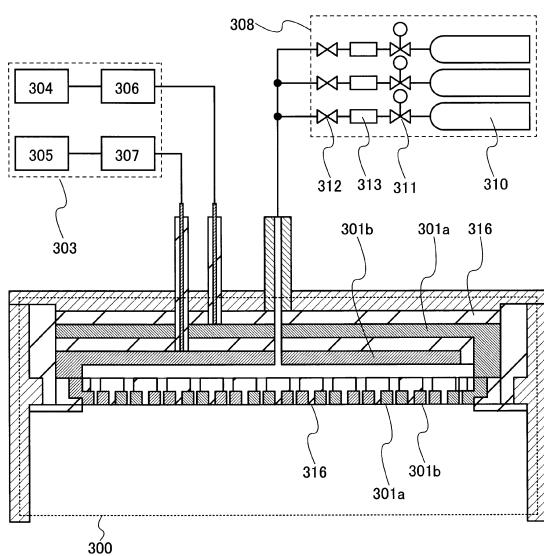

【0098】

図12は第1の電極301の他の構成を示す。第1の電極301は、第1の高周波電源304から高周波電力が供給される第1の電極301aと、第2の高周波電源305から高周波電力が供給される第1の電極301bに分離されている。第1の電極301aと第1の電極301bは基板と対抗する面は細孔が設けられると共に、櫛歯状にかみ合うように構成され、隣接するもの同士は接触しないように絶縁材316で分離されている。図12に示す構成は、図11で示す第1の電極301と置き換えることが可能であり、同様な効果を得ることができる。

40

【0099】

反応室300に接続される排気手段309は真空排気と、反応ガスを流す場合において反応室300内を所定の圧力に保持するように制御する機能が含まれている。排気手段309の構成としては、バタフライバルブ317、コンダクタンスバルブ318、ターボ分子ポンプ319、ドライポンプ320などが含まれる。バタフライバルブ317とコンダクタンスバルブ318を並列に配置する場合には、バタフライバルブ317を閉じてコンダクタンスバルブ318を動作させることで、反応ガスの排気速度を制御して反応室300の圧力を所定の範囲に保つことができる。また、コンダクタンスの大きいバタフライバルブ317を開くことで高真空排気が可能となる。

【0100】

50

真空度として  $10^{-5}$  Pa よりも低い圧力の超高真空排気する場合には、クライオポンプ 321 を併用することが好ましい。その他、到達真空度として超高真空まで排気する場合には、反応室 300 の内壁を鏡面加工し、内壁からのガス放出を低減するためにベーキング用のヒータを設けても良い。

【0101】

ヒータコントローラ 315 により温度制御される基板加熱ヒータ 314 は第 2 の電極 302 に設けられている。基板加熱ヒータ 314 は第 2 の電極 302 内に設けられる場合、熱伝導加熱方式が採用され、シースヒータなどで構成される。第 1 の電極 301 と第 2 の電極 302 の間隔は適宜変更できるように、第 2 の電極 302 の高さ調節ができるように可動式となる構成が含まれる。

10

【0102】

本形態に係るプラズマ CVD 装置の反応室を用いることで、酸化シリコン膜、窒化シリコン膜に代表される絶縁膜、微結晶シリコン膜、非晶質シリコン膜に代表される半導体膜、その他 TFT 及び光電変換装置などで使用される各種薄膜の形成が可能となる。特に長辺が 2000 mm を超える大面積基板に前記薄膜を形成する場合において有用である。

【0103】

なお、上記実施の形態 1 においては、微結晶半導体膜 103 の形成に本実施の形態で示したプラズマ CVD 装置を用いる場合について説明したが、これに限られず、反応ガスを替えれば各種薄膜を形成することができる。半導体膜としては、非晶質シリコン膜、非晶質シリコンゲルマニウム膜、非晶質シリコンカーバイト膜、微結晶シリコンゲルマニウム膜、微結晶シリコンカーバイト膜などの成膜に本実施の形態で示したプラズマ装置を適用することができる。絶縁膜としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜などの成膜に本実施の形態で示したプラズマ装置を適用することができる。

20

【0104】

本実施の形態は、他の実施の形態に記載した構成や作製方法と組み合わせて実施することが可能である。

【0105】

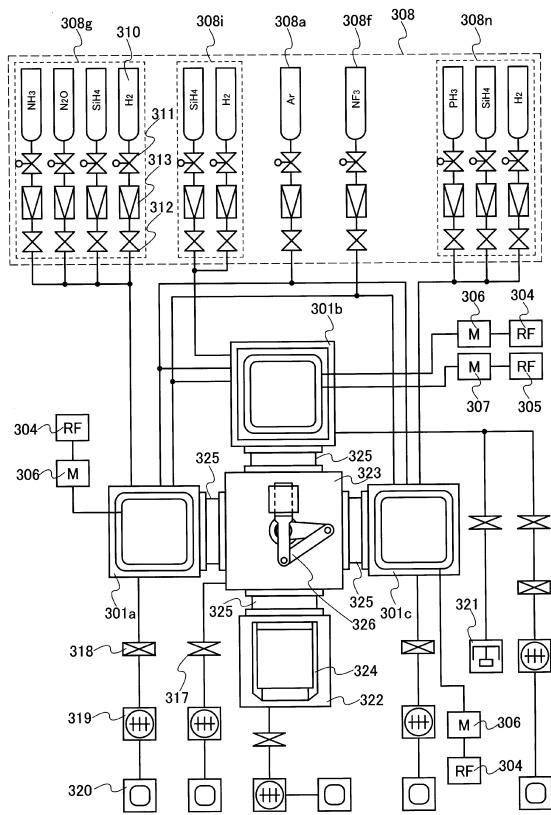

(実施の形態 3)

本実施の形態では、上記実施の形態 2 で示される反応室が適用されるプラズマ CVD 装置の一例として、複数の膜（ここでは、TFT を構成するゲート絶縁膜及び半導体膜）の成膜に適した構成の一例に関して、図 18 を参照して説明する。

30

【0106】

図 18 は複数の反応室を備えたマルチ・チャンバ・プラズマ CVD 装置の一例を示す。この装置は共通室 323 と、ロード / アンロード室 322、第 1 反応室 300a、第 2 反応室 300b、第 3 反応室 300c を備えた構成となっている。ロード / アンロード室 322 のカセット 324 に装填される基板は、共通室 323 の搬送機構 326 によって各反応室に搬出入される枚葉式の構成である。共通室 323 と各室の間にはゲートバルブ 325 が備えられ、各反応室で行われる処理が、相互に干渉しないように構成されている。

40

【0107】

各反応室は形成する薄膜の種類によって区分されている。例えば、第 1 反応室 300a はゲート絶縁膜などの絶縁膜を成膜し、第 2 反応室 300b はチャネルを形成する微結晶半導体層を成膜し、第 3 反応室 300c はソース及びドレインを形成する一導電型の不純物半導体層を成膜する反応室として充当される。勿論、反応室の数はこれに限定されるわけではなく、必要に応じて任意に増減することができる。また、一の反応室で一の膜を成膜するようにしても良いし、一の反応室で複数の膜を成膜するように構成しても良い。

【0108】

各反応室には排気手段としてターボ分子ポンプ 319 とドライポンプ 320 が接続されている。排気手段はこれらの真空ポンプの組み合わせに限定されるものではなく、概略  $10^{-1}$  Pa から  $10^{-5}$  Pa の真空度にまで排気できるものであれば他の真空ポンプを適用

50

することができる。また、微結晶半導体膜を形成する第2反応室300bは超高真空まで真空排気するものとして、クライオポンプ321が連結されている。排気手段と各反応室との間にはバタフライバルブ317が設けられており、これによって真空排気を遮断させることができ、コンダクタンスバルブ318によって排気速度を制御して、それぞれの反応室の圧力を調節することができる。

【0109】

ガス供給手段308は半導体材料ガス若しくは希ガスなどプロセスに用いるガスが充填されるシリンド310、ストップバルブ312、マスフローコントローラ313などで構成されている。ガス供給手段308gは第1反応室300aに接続され、ゲート絶縁膜を成膜するためのガスを供給する。ガス供給手段308iは第2反応室300bに接続され、微結晶半導体膜用のガスを供給する。ガス供給手段308nは第3反応室300cに接続され、例えば、n型半導体膜用のガスを供給する。ガス供給手段308aはアルゴンを供給し、ガス供給手段308fは反応室内のクリーニングに用いるエッティングガスを供給する系統であり、これらは各反応室共通のラインとして構成されている。

10

【0110】

各反応室にはプラズマを形成するための高周波電力供給手段が連結されている。高周波電力供給手段303は高周波電源と整合器が含まれる。この場合、実施の形態2と同様に、第1の高周波電源304と第2の高周波電源305、第1の整合器306と第2の整合器307で構成することにより、均一性の良い薄膜を形成することができる。プラズマCV-D装置の構成を、各種ガラス基板のサイズ(第1世代と呼ばれる300mm×400mm、第3世代の550mm×650mm、第4世代の730mm×920mm、第5世代の1000mm×1200mm、第6世代の24500mm×1850mm、第7世代の1870mm×2200mm、第8世代の2000mm×2400mm、第9世代の2450×3050mm、第10世代の2850mm×3050mmなど)に合わせれば、どのようなサイズの基板に対しても均一性の良い薄膜を形成することができる。

20

【0111】

本形態で示すように、図18で示す反応室を複数個用い、共通室で連結することにより複数の異なる層を大気に触れさせることなく連続して積層することが可能となる。

【0112】

本実施の形態は、他の実施の形態に記載した構成や作製方法と組み合わせて実施することが可能である。

30

【0113】

(実施の形態4)

本実施の形態では、上記実施と異なる薄膜トランジスタを有する表示装置の作製方法について図面を参照して説明する。具体的には、多階調マスクを用いた作製方法について説明する。

【0114】

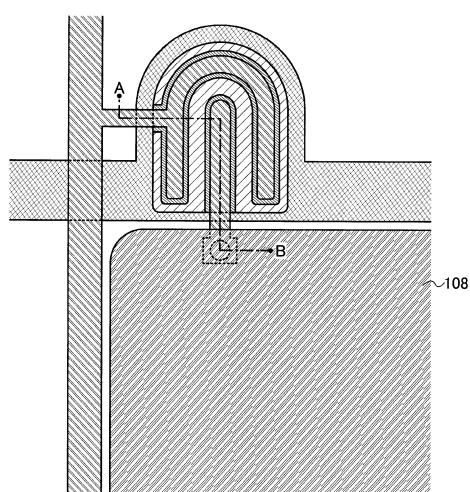

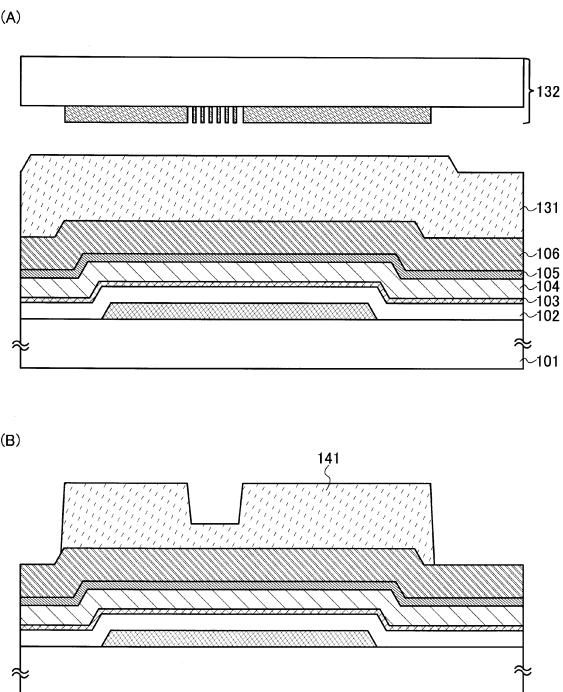

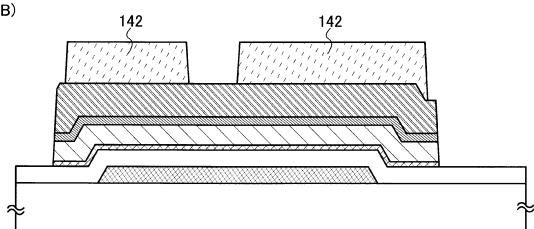

まず、基板100上に、ゲート電極101、ゲート絶縁膜102、微結晶構造を有する微結晶半導体膜103、バッファー層として機能する非晶質半導体膜104、一導電型を付与する不純物が添加された第3の半導体膜105及び導電膜106を順に積層して形成した後、導電膜106上にレジスト131を形成する。続いて、多階調マスク132を用いてレジスト131に光を照射し、当該レジスト131を露光する(図8(A)参照)。

40

【0115】

レジスト131は、ポジ型レジストまたはネガ型レジストを用いることができる。ここでは、ポジ型レジストを用いて示す。

【0116】

ここで、多階調マスク132を用いた露光について、図15を参照して説明する。

【0117】

多階調マスクとは、露光部分、中間露光部分、及び未露光部分に3つの露光レベルを行うことが可能なマスクであり、一度の露光及び現像工程により、複数(代表的には二種類)

50

の厚さの領域を有するレジストマスクを形成することが可能である。このため、多階調マスクを用いることで、フォトマスクの枚数を削減することが可能である。

【0118】

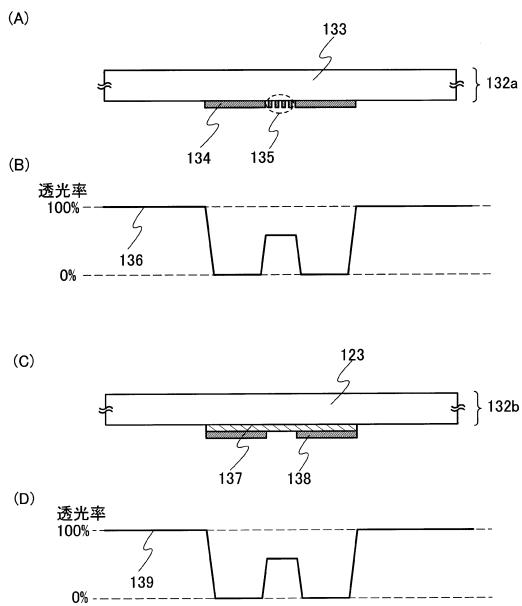

多階調マスクの代表例としては、図15(A)に示すようなグレートーンマスク132a、図15(C)に示すようなハーフトーンマスク132bがある。

【0119】

グレートーンマスク132aは、図15(A)に示すように、透光性を有する基板133及びその上に形成される遮光部134並びに回折格子135で構成される。遮光部134においては、光の透過率が0%である。一方、回折格子135はスリット、ドット、メッシュ等の光透過部の間隔を、露光に用いる光の解像度限界以下の間隔とすることにより、光の透過量を制御することができる。なお、回折格子135は、周期的なスリット、ドット、メッシュ、または非周期的なスリット、ドット、メッシュどちらも用いることができる。

【0120】

透光性を有する基板133は、石英等の透光性を有する基板を用いることができる。遮光部134及び回折格子135は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。

【0121】

グレートーンマスク132aに露光光を照射した場合、図15(B)に示すように、遮光部134においては、光透過率136は0%であり、遮光部134及び回折格子135が設けられていない領域では光透過率136は100%である。また、回折格子135においては、10~70%の範囲で調整可能である。回折格子135における光の透過量の調整は、回折格子のスリット、ドット、またはメッシュの間隔及びピッチの調整により可能である。

【0122】

ハーフトーンマスク132bは、図15(C)に示すように、透光性を有する基板133及びその上に形成される半透過部137並びに遮光部138で構成される。半透過部137は、MoSiN、MoSi、MoSiO、MoSiON、CrSiなどを用いることができる。遮光部138は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。

【0123】

ハーフトーンマスク132bに露光光を照射した場合、図15(D)に示すように、遮光部138においては、光透過率139は0%であり、遮光部138及び半透過部137が設けられていない領域では光透過率139は100%である。また、半透過部137においては、10~70%の範囲で調整可能である。半透過部137に於ける光の透過率の調整は、半透過部137の材料により調整により可能である。

【0124】

多階調マスクを用いて露光した後、現像することで、図8(B)に示すように、膜厚の異なる領域を有するレジストマスク141を形成することができる。

【0125】

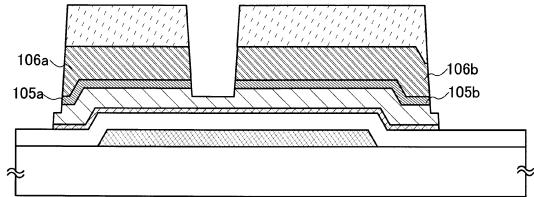

次に、レジストマスク141により、微結晶半導体膜103、バッファー層として機能する非晶質半導体膜104、一導電型を付与する不純物が添加された第3の半導体膜105及び導電膜106をエッティングし分離する(図9(A)参照)。

【0126】

次に、レジストマスク141をアッシングする。この結果、レジストの面積が縮小し、厚さが薄くなる。このとき、膜厚の薄い領域のレジスト(ゲート電極101の一部と重疊する領域)は除去され、図9(B)に示すように、分離されたレジストマスク142を形成することができる。

【0127】

次に、レジストマスク141を用いて、一導電型を付与する不純物が添加された半導体膜

10

20

30

40

50

105及びバッファー層として機能する非晶質半導体膜104をエッチングして、ソース領域105a及びドレイン領域105b、ソース電極106a及びドレイン電極106bを形成する(図9(C)参照)。なお、バッファー層として機能する非晶質半導体膜104は一部のみがエッチングされたものであり、微結晶半導体膜103の表面を覆っている。ここでは、ソース領域105aとドレイン領域105bの間に位置する非晶質半導体膜104の表面に凹部が形成される。

**【0128】**

次に、ソース電極106a及びドレイン電極106b、ソース領域105a及びドレイン領域105b、非晶質半導体膜104及びゲート絶縁膜102上に絶縁膜107を形成する。続けて、絶縁膜107にコンタクトホールを形成し、当該コンタクトホールにおいてドレイン電極106bに接する画素電極108を形成する(図10参照)。

10

**【0129】**

以上の工程により、薄膜トランジスタ110を画素部に有する表示装置を形成することができる。

**【0130】**

本実施の形態は、他の実施の形態に記載した構成や作製方法と組み合わせて実施することが可能である。

**【0131】**

(実施の形態5)

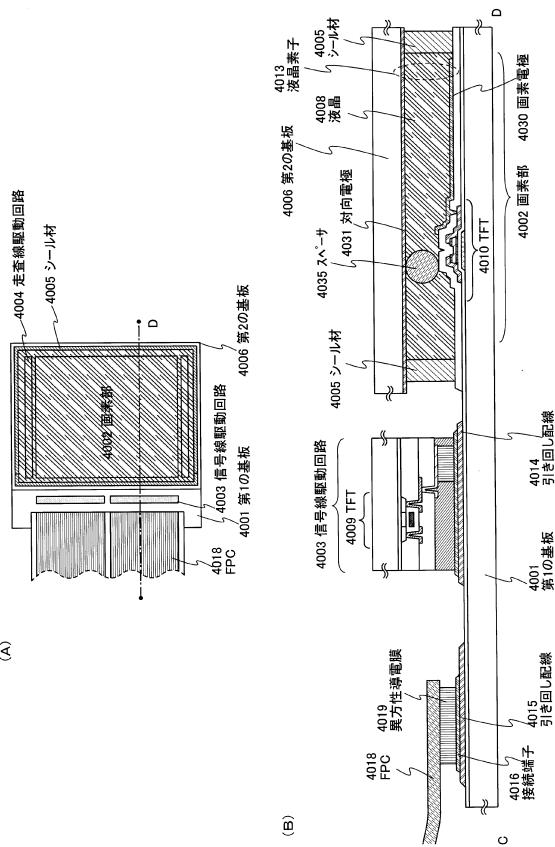

本実施の形態では、上記実施の形態で示した表示装置の一形態として液晶表示パネルについて図16を参照して説明する。図16(A)は、第1の基板4001上に形成された薄膜トランジスタ4010及び液晶素子4013を第2の基板4006との間にシール材4005によって封止したパネルの上面図であり、図16(B)は、図16(A)のC-Dにおける断面を示している。

20

**【0132】**

本実施の形態で示す液晶表示パネルは、第1の基板4001上に設けられた画素部4002と走査線駆動回路4004を囲むようにして、シール材4005が設けられている。また、画素部4002と走査線駆動回路4004の上に第2の基板4006が設けられている。そのため、画素部4002と走査線駆動回路4004は、第1の基板4001とシール材4005と第2の基板4006によって、液晶4008と共に封止されている。

30

**【0133】**

また、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体膜で形成された薄膜トランジスタ4009を具備する信号線駆動回路4003が実装されている。なお、本実施の形態では、多結晶半導体膜を用いた薄膜トランジスタ4009を有する信号線駆動回路4003を、第1の基板4001に貼り合わせる例について説明するが、単結晶半導体を用いたトランジスタで信号線駆動回路4003を形成し、貼り合わせるようにも良い。

**【0134】**

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、薄膜トランジスタを複数有しており、図16(B)では、画素部4002に含まれる薄膜トランジスタ4010を例示している。薄膜トランジスタ4010は、上記実施の形態1、2で示した薄膜トランジスタに相当する。また、走査線駆動回路4004を構成するトランジスタを薄膜トランジスタ4010と同様の構成で設けることができる。

40

**【0135】**

また、画素電極4030は、薄膜トランジスタ4010と電気的に接続されている。そして液晶素子4013を構成する対向電極4031は、第2の基板4006上に形成されている。画素電極4030と対向電極4031と液晶4008とが重なっている部分が、液晶素子4013に相当する。

**【0136】**

なお、第1の基板4001、第2の基板4006としては、ガラス、金属(代表的にはス

50

テンレス)、セラミックス、プラスチックを用いることができる。プラスチックとしては、F R P (F i b e r g l a s s - R e i n f o r c e d P l a s t i c s) 板、P V F (ポリビニルフルオライド) フィルム、ポリエスチルフィルム、ポリエスチルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをP V F フィルムやポリエスチルフィルムで挟んだ構造のシートを用いることもできる。

【0137】

また、球状のスペーサ 4035 は、画素電極 4030 と対向電極 4031 との間の距離(セルギャップ)を制御するために設けられている。なお、球場のスペーサ 4035 の代わりに絶縁膜を選択的にエッチングすることで得られるスペーサを用いていても良い。

【0138】

また、別途形成された信号線駆動回路 4003 と、走査線駆動回路 4004 または画素部 4002 に与えられる各種信号及び電位は、引き回し配線 4014、4015 を介して、F P C 4018 から供給されている。

【0139】

本実施の形態では、接続端子 4016 が、画素電極 4030 と同じ導電膜により形成されている。また、引き回し配線 4014、4015 は、薄膜トランジスタ 4010 のソース電極及びドレイン電極と同じ導電膜で形成されている。

【0140】

接続端子 4016 は、F P C 4018 が有する端子と、異方性導電膜 4019 を介して電気的に接続されている。

10

【0141】

なお、図示していないが、本実施の形態に示した液晶表示装置は配向膜、偏光板を有し、更にカラーフィルタや遮蔽膜を有していても良い。

【0142】

また、図 16 では、信号線駆動回路 4003 を別途形成し、第 1 の基板 4001 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

【0143】

本実施の形態で説明した液晶表示装置は、T N (T w i s t e d N e m a t i c) 型、V A (V e r t i c a l A l i g n m e n t) 型又は横電界方式の液晶表示装置とすることができる。

30

【0144】

V A 型の液晶表示装置とは、液晶パネルの液晶分子の配列を制御する方式の一種である。V A 型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。本実施の形態では、特に画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されている。これをマルチドメイン化あるいはマルチドメイン設計という。

【0145】

横電界方式は、セル内の液晶分子に対して水平方向に電界を加えることで液晶を駆動して階調表現する方式である。この方式によれば、視野角を約 180 度にまで広げることができる。

40

【0146】

本実施の形態は、他の実施の形態に記載した構成と組み合わせて実施することが可能である。

【0147】

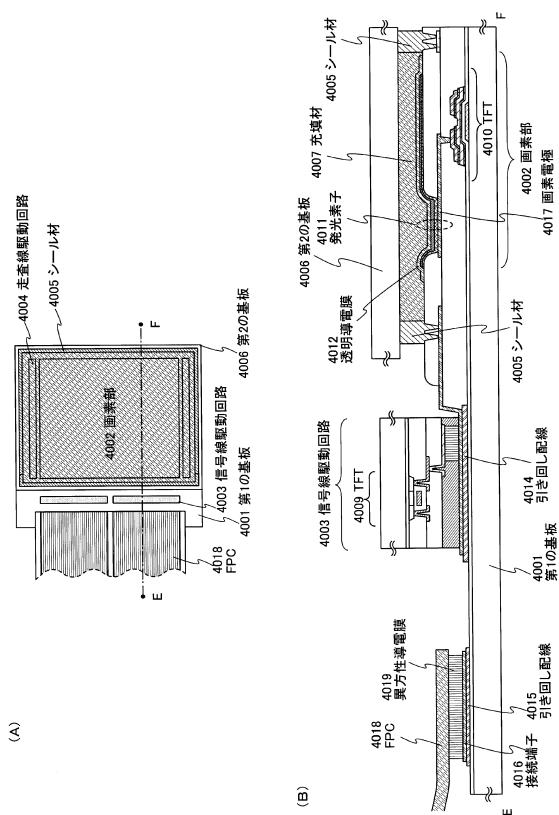

(実施の形態 6)

本実施の形態では、上記実施の形態で示した表示装置の一形態として発光表示パネルについて図 17 を参照して説明する。図 17 (A) は、第 1 の基板 4001 上に形成された薄膜トランジスタ 4010 及び発光素子 4011 を第 2 の基板 4006 との間にシール材 4

50

005によって封止したパネルの上面図であり、図17(B)は、図17(A)のE-Fにおける断面を示している。

【0148】

本実施の形態では、エレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0149】

本実施の形態で示す発光表示パネルは、第1の基板4001上に設けられた画素部4002と走査線駆動回路4004を囲むようにして、シール材4005が設けられている。また、画素部4002と走査線駆動回路4004の上に第2の基板4006が設けられている。そのため、画素部4002と走査線駆動回路4004は、第1の基板4001とシール材4005と第2の基板4006によって、充填材4007と共に密封されている。

10

【0150】

また、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体膜で形成された薄膜トランジスタ4009を具備する信号線駆動回路4003が実装されている。なお、本実施の形態では、多結晶半導体膜を用いた薄膜トランジスタ4009を有する信号線駆動回路4003を、第1の基板4001に貼り合わせる例について説明するが、単結晶半導体を用いたトランジスタで信号線駆動回路を形成し、貼り合わせるようにも良い。

20

【0151】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、薄膜トランジスタを複数有しており、図17(B)では、画素部4002に含まれる薄膜トランジスタ4010を例示している。薄膜トランジスタ4010は、上記実施の形態1、2で示した薄膜トランジスタに相当する。また、走査線駆動回路4004を構成するトランジスタを薄膜トランジスタ4010と同様の構成で設けることができる。

【0152】

発光素子4011を構成する画素電極4017は、薄膜トランジスタ4010のソース電極またはドレイン電極と電気的に接続されている。発光素子4011の構成は、発光素子4011から取り出す光の方向や、薄膜トランジスタ4010の極性などに合わせて、適宜変えることができる。

30

【0153】

また、別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、図17(B)に示す断面図では図示されていないが、引き回し配線4014及び4015を介して、FPC4018から供給されている。

【0154】

本実施の形態では、接続端子4016が、発光素子4011を構成する画素電極4017と同じ導電膜から形成されている。また、引き回し配線4014、4015は、薄膜トランジスタ4010のソース電極及びドレイン電極と同じ導電膜から形成されている。

40

【0155】

接続端子4016は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

【0156】

発光素子4011からの光の取り出し方向に位置する基板は、透光性を有する材料で設ける。本実施の形態では、第2の基板4006側から光を取り出すため、第2の基板4006は、ガラス板、プラスチック板、ポリエチルフィルムまたはアクリルフィルムのような透光性を有する材料で形成する。

【0157】

また、充填材4007としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹

50

脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。

【0158】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(橢円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【0159】

なお、図17では、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

10

【0160】

本実施の形態は、他の実施の形態に記載した構成と組み合わせて実施することが可能である。

【0161】

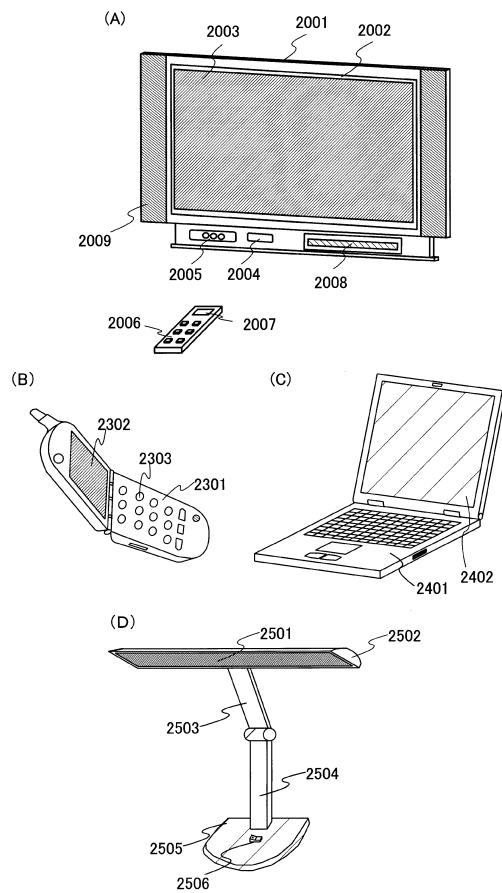

(実施の形態7)

本発明により得られる表示装置等によって、アクティブマトリクス型表示装置モジュールに用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに本発明を実施できる。

20

【0162】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パソコンコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図13に示す。

【0163】

図13(A)はテレビジョン装置である。表示モジュールを、図13(A)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付けられた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカー部2009、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。

30

【0164】

図13(A)に示すように、筐体2001に表示素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部2007が設けられていても良い。

40

【0165】

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面2003を視野角の優れた液晶表示パネルで形成し、サブ画面2008を低消費電力で表示可能な発光表示パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面2003を発光表示パネルで形成し、サブ画面2008を発光表示パネルで形成し、サブ画面2008は点滅可能とする構成としても良い。

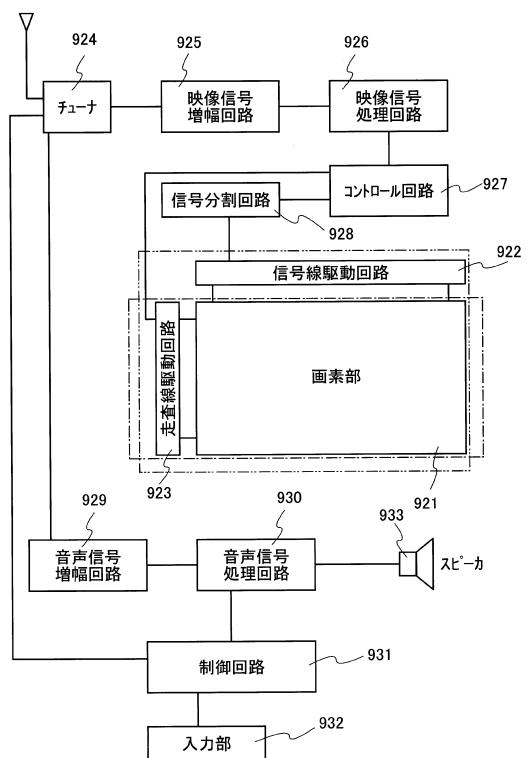

【0166】

図14はテレビ装置の主要な構成を示すブロック図を示している。表示パネル900には、画素部921が形成されている。信号線駆動回路922と走査線駆動回路923は、表

50

示パネル 900 に COG 方式により実装されていても良い。

【0167】

その他の外部回路の構成として、映像信号の入力側では、チューナ 924 で受信した信号のうち、映像信号を増幅する映像信号増幅回路 925 と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路 926 と、その映像信号をドライバ I C の入力仕様に変換するためのコントロール回路 927 などを有している。コントロール回路 927 は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路 928 を設け、入力デジタル信号を m 個に分割して供給する構成としても良い。

【0168】

チューナ 924 で受信した信号のうち、音声信号は、音声信号増幅回路 929 に送られ、その出力は音声信号処理回路 930 を経てスピーカー 933 に供給される。制御回路 931 は受信局（受信周波数）や音量の制御情報を入力部 932 から受け、チューナ 924 や音声信号処理回路 930 に信号を送出する。

【0169】

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

【0170】

図 13 (B) は携帯電話機 2301 の一例を示している。この携帯電話機 2301 は、表示部 2302、操作部 2303 などを含んで構成されている。表示部 2302 においては、上記実施の形態で説明した表示装置を適用することで、量産性を高めることができる。

【0171】

また、図 13 (C) に示す携帯型のコンピュータは、本体 2401、表示部 2402 等を含んでいる。表示部 2402 に、上記実施の形態に示す表示装置を適用することにより、量産性を高めることができる。

【0172】

図 13 (D) は卓上照明器具であり、照明部 2501、傘 2502、可変アーム 2503、支柱 2504、台 2505、電源 2506 を含む。本発明の発光装置を照明部 2501 に用いることにより作製される。なお、照明器具には天井固定型の照明器具または壁掛け型の照明器具なども含まれる。上記実施の形態に示す表示装置を適用することにより、量産性を高めることができ、安価な卓上照明器具を提供することができる。

【符号の説明】

【0173】

100 基板

101 ゲート電極

102 ゲート絶縁膜

103 微結晶半導体膜

104 非晶質半導体膜

105 半導体膜

106 導電膜

107 絶縁膜

108 画素電極

110 薄膜トランジスタ

121 マスク

122 マスク

123 凹部

131 レジスト

132 多階調マスク

133 基板

10

20

30

40

50

|       |             |    |

|-------|-------------|----|

| 1 3 4 | 遮光部         |    |

| 1 3 5 | 回折格子        |    |

| 1 3 6 | 光透過率        |    |

| 1 3 7 | 半透過部        |    |

| 1 3 8 | 遮光部         |    |

| 1 3 9 | 光透過率        |    |

| 1 4 1 | レジストマスク     |    |

| 1 4 2 | レジストマスク     |    |

| 2 0 0 | 真空排気        | 10 |

| 2 0 1 | プレコート       |    |

| 2 0 2 | 基板搬入        |    |

| 2 0 3 | 下地前処理       |    |

| 2 0 4 | 成膜処理        |    |

| 2 0 5 | 基板搬出        |    |

| 2 0 6 | クリーニング      |    |

| 2 0 7 | 破線          |    |

| 3 0 0 | 反応室         |    |

| 3 0 1 | 電極          |    |

| 3 0 2 | 電極          |    |

| 3 0 3 | 高周波電力供給手段   | 20 |

| 3 0 4 | 高周波電源       |    |

| 3 0 5 | 高周波電源       |    |

| 3 0 6 | 整合器         |    |

| 3 0 7 | 整合器         |    |

| 3 0 8 | ガス供給手段      |    |

| 3 0 9 | 排気手段        |    |

| 3 1 0 | シリンド        |    |

| 3 1 1 | 圧力調整弁       |    |

| 3 1 2 | ストップバルブ     |    |

| 3 1 3 | マスフローコントローラ | 30 |

| 3 1 4 | 基板加熱ヒータ     |    |

| 3 1 5 | ヒータコントローラ   |    |

| 3 1 6 | 絶縁材         |    |

| 3 1 7 | バタフライバルブ    |    |

| 3 1 8 | コンダクタンスバルブ  |    |

| 3 1 9 | ターボ分子ポンプ    |    |

| 3 2 0 | ドライポンプ      |    |

| 3 2 1 | クライオポンプ     |    |

| 3 2 2 | ロード／アンロード室  |    |

| 3 2 3 | 共通室         | 40 |

| 3 2 4 | カセット        |    |

| 3 2 5 | ゲートバルブ      |    |

| 3 2 6 | 搬送機構        |    |

| 9 0 0 | 表示パネル       |    |

| 9 2 1 | 画素部         |    |

| 9 2 2 | 信号線駆動回路     |    |

| 9 2 3 | 走査線駆動回路     |    |

| 9 2 4 | チューナ        |    |

| 9 2 5 | 映像信号增幅回路    |    |

| 9 2 6 | 映像信号処理回路    | 50 |

|         |           |    |

|---------|-----------|----|

| 9 2 7   | コントロール回路  |    |

| 9 2 8   | 信号分割回路    |    |

| 9 2 9   | 音声信号增幅回路  |    |

| 9 3 0   | 音声信号処理回路  |    |

| 9 3 1   | 制御回路      |    |

| 9 3 2   | 入力部       |    |

| 9 3 3   | スピーカー     |    |

| 1 0 5 a | ソース領域     |    |

| 1 0 5 b | ドレイン領域    |    |

| 1 0 6 a | ソース電極     | 10 |

| 1 0 6 b | ドレイン電極    |    |

| 1 3 2 a | グレートーンマスク |    |

| 1 3 2 b | ハーフトーンマスク |    |

| 2 0 0 1 | 筐体        |    |

| 2 0 0 2 | 表示用パネル    |    |

| 2 0 0 3 | 主画面       |    |

| 2 0 0 4 | モデム       |    |

| 2 0 0 5 | 受信機       |    |

| 2 0 0 6 | リモコン操作機   |    |

| 2 0 0 7 | 表示部       | 20 |

| 2 0 0 8 | サブ画面      |    |

| 2 0 0 9 | スピーカー部    |    |

| 2 3 0 1 | 携帯電話機     |    |

| 2 3 0 2 | 表示部       |    |

| 2 3 0 3 | 操作部       |    |

| 2 4 0 1 | 本体        |    |

| 2 4 0 2 | 表示部       |    |

| 2 5 0 1 | 照明部       |    |

| 2 5 0 2 | 傘         |    |

| 2 5 0 3 | 可変アーム     | 30 |

| 2 5 0 4 | 支柱        |    |

| 2 5 0 5 | 台         |    |

| 2 5 0 6 | 電源        |    |

| 3 0 0 a | 反応室       |    |

| 3 0 0 b | 反応室       |    |

| 3 0 0 c | 反応室       |    |

| 3 0 1 a | 電極        |    |

| 3 0 1 b | 電極        |    |

| 3 0 2 b | 電極        |    |

| 3 0 8 a | ガス供給手段    | 40 |

| 3 0 8 f | ガス供給手段    |    |

| 3 0 8 g | ガス供給手段    |    |

| 3 0 8 i | ガス供給手段    |    |

| 3 0 8 n | ガス供給手段    |    |

| 4 0 0 1 | 基板        |    |

| 4 0 0 2 | 画素部       |    |

| 4 0 0 3 | 信号線駆動回路   |    |

| 4 0 0 4 | 走査線駆動回路   |    |

| 4 0 0 5 | シール材      |    |

| 4 0 0 6 | 基板        | 50 |

|         |          |

|---------|----------|

| 4 0 0 7 | 充填材      |

| 4 0 0 8 | 液晶       |

| 4 0 0 9 | 薄膜トランジスタ |

| 4 0 1 0 | 薄膜トランジスタ |

| 4 0 1 1 | 発光素子     |

| 4 0 1 3 | 液晶素子     |

| 4 0 1 4 | 配線       |

| 4 0 1 6 | 接続端子     |

| 4 0 1 7 | 画素電極     |

| 4 0 1 8 | F P C    |

| 4 0 1 9 | 異方性導電膜   |

| 4 0 3 0 | 画素電極     |

| 4 0 3 1 | 対向電極     |

| 4 0 3 5 | スペーサ     |

| 4 0 4 1 | 薄膜トランジスタ |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

(B)

(C)

【図11】

【図12】

【図13】

【図14】

【図15】

### 【図16】

【図17】

【 図 1 8 】

---

フロントページの続き

| (51) Int.CI. |        | F I       |         |            |

|--------------|--------|-----------|---------|------------|

| H 0 5 B      | 33/10  | (2006.01) | G 0 9 F | 9/00 3 3 8 |

| G 0 9 F      | 9/00   | (2006.01) | H 0 1 L | 21/205     |

| H 0 1 L      | 21/205 | (2006.01) | C 2 3 C | 16/24      |

| C 2 3 C      | 16/24  | (2006.01) |         |            |

(72)発明者 神保 安弘

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 大力 浩二

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 市川 武宜

(56)参考文献 特開平08-148690 (JP, A)

特開昭63-215037 (JP, A)

特開平01-321625 (JP, A)

特開2007-049171 (JP, A)

特開平08-097436 (JP, A)

特開平07-094749 (JP, A)

特開2005-037849 (JP, A)

(58)調査した分野(Int.CI., DB名)

|         |             |

|---------|-------------|

| H 0 1 L | 2 1 / 3 3 6 |

| C 2 3 C | 1 6 / 2 4   |

| G 0 2 F | 1 / 1 3 6 8 |

| G 0 9 F | 9 / 0 0     |

| H 0 1 L | 2 1 / 2 0 5 |

| H 0 1 L | 2 9 / 7 8 6 |

| H 0 1 L | 5 1 / 5 0   |

| H 0 5 B | 3 3 / 1 0   |

| H 0 5 B | 3 3 / 1 4   |