## (12)发明专利

(10)授权公告号 CN 105393237 B

(45)授权公告日 2019.03.01

(21)申请号 201480041353.4

(73)专利权人 高通股份有限公司

(22)申请日 2014.07.22

地址 美国加利福尼亚州

(65)同一申请的已公布的文献号

(72)发明人 C·李 G·A·威利

申请公布号 CN 105393237 A

R·D·韦斯特费尔特

(43)申请公布日 2016.03.09

(74)专利代理机构 上海专利商标事务所有限公司 31100

(30)优先权数据

代理人 袁逸

61/857,212 2013.07.22 US

(51)Int.Cl.

14/336,977 2014.07.21 US

G06F 13/42(2006.01)

(85)PCT国际申请进入国家阶段日

H04L 7/00(2006.01)

2016.01.21

(56)对比文件

(86)PCT国际申请的申请数据

GB 2453185 A, 2009.04.01,

PCT/US2014/047586 2014.07.22

CN 101551990 A, 2009.10.07,

(87)PCT国际申请的公布数据

US 2009/0296867 A1, 2009.12.03,

W02015/013259 EN 2015.01.29

审查员 贾东曜

权利要求书2页 说明书10页 附图14页

## (54)发明名称

多相位时钟生成方法

## (57)摘要

本文中描述了用于多相位信令的系统和方法。在一个实施例中，用于接收数据的方法包括从多个导体接收码元序列(510)，以及通过检测所接收到的码元序列中的转变来生成时钟信号(520)。该方法还包括延迟所接收到的码元序列(522)，并且使用该时钟序号来捕捉经延迟的码元序列中的一个或多个码元，其中该经延迟的码元序列中的前一码元是使用该时钟信号中的基于检测到的向所接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉的(530)。

1. 一种用于接收数据的方法,包括:

从多个导体接收码元序列;

通过检测接收到的码元序列中的转变来生成时钟信号;

延迟所述接收到的码元序列;以及

用触发器来使用所述时钟信号捕捉经延迟的码元序列中的一个或多个码元,其中所述经延迟的码元序列中的前一码元是使用所述时钟信号中的基于检测到的从所述前一码元向所述接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉的,其中所述接收到的码元序列被延迟长达等于或大于所述触发器的保持时间的时间延迟,所述时间延迟小于所述触发器的建立时间。

2. 如权利要求1所述的方法,其特征在于,所述接收到的码元序列被延迟长达等于或大于所述触发器的保持时间和检测到的转变与所述时钟信号的对应边沿之间的时间延迟之和的时间延迟。

3. 如权利要求1所述的方法,其特征在于,每个码元是通过驱动至少一对所述导体并且保持至少一个所述导体不受驱动来被跨所述多个导体发送的。

4. 如权利要求3所述的方法,其特征在于,所述至少一对导体被用相反极性驱动。

5. 如权利要求3所述的方法,其特征在于,接收所述码元序列包括将每个码元转换成多个位,并且其中捕捉所述经延迟的码元序列包括使用基于在所述接收到的码元序列中所检测到的从所述前一码元向所述当前码元的转变而生成的所述时钟脉冲来捕捉所述经延迟的码元序列中的所述前一码元的所述多个位。

6. 如权利要求5所述的方法,其特征在于,将每个码元转换成多个位包括跨不同导体对检测多个差分电压,并且基于检测到的差分电压来生成所述位。

7. 一种用于接收数据的设备,包括:

用于从多个导体接收码元序列的装置;

用于通过检测接收到的码元序列中的转变来生成时钟信号的装置;

用于延迟所述接收到的码元序列的装置;以及

用于用触发器来使用所述时钟信号捕捉经延迟的码元序列中的一个或多个码元的装置,其中所述经延迟的码元序列中的前一码元是使用所述时钟信号中的基于所检测到的从所述前一码元向所述接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉的,其中所述接收到的码元序列被延迟长达等于或大于所述用于捕捉经延迟的码元序列中的一个或多个码元的装置的保持时间的时间延迟,所述时间延迟小于所述用于捕捉所述经延迟的码元序列中的一个或多个码元的装置的建立时间。

8. 如权利要求7所述的设备,其特征在于,所述接收到的码元序列被延迟长达等于或大于所述用于捕捉经延迟的码元序列中的一个或多个码元的装置的保持时间和所述用于生成时钟信号的装置的时间延迟之和的时间延迟。

9. 如权利要求7所述的设备,其特征在于,每个码元是通过驱动至少一对所述导体并且保持至少一个所述导体不受驱动来被跨所述多个导体发送的。

10. 如权利要求9所述的设备,其特征在于,所述至少一对导体被用相反极性驱动。

11. 如权利要求9所述的设备,其特征在于,所述用于接收所述码元序列的装置包括用于将每个码元转换成多个位的装置,并且其中所述用于捕捉所述经延迟的码元序列中的一

个或多个码元的装置包括用于使用基于所检测到的向所述接收到的码元序列中的所述当前码元的转变而生成的所述时钟脉冲来捕捉所述经延迟的码元序列中的所述前一码元的多个位的装置。

12. 如权利要求11所述的设备,其特征在于,所述用于将每个码元转换成多个位的装置包括用于跨不同所述导体对检测多个差分电压的装置,以及用于基于检测到的差分电压来生成所述位的装置。

13. 一种接收装置,包括:

接收机电路,其配置成从多个导体接收码元序列;

时钟恢复电路,其配置成通过检测接收到的码元序列中的转变来生成时钟信号;

延迟电路,其配置成延迟所述接收到的码元序列;以及

触发器,其配置成使用所述时钟信号来捕捉经延迟的码元序列中的一个或多个码元,其中所述触发器使用所述时钟信号中的基于所检测到的从前一码元向所述接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉所述经延迟的码元序列中的所述前一码元;

其中所述延迟电路被配置成延迟所述接收到的码元序列长达等于或大于所述触发器的保持时间的时间延迟,所述时间延迟小于所述触发器的建立时间。

14. 如权利要求13所述的装置,其特征在于,所述接收到的码元序列被延迟长达等于或大于所述触发器的保持时间和所述时钟恢复电路用以将检测到的转变转换成所述时钟信号的对应边沿所要求的时间延迟之和的时间延迟。

15. 如权利要求13所述的装置,其特征在于,每个码元是通过驱动至少一对所述导体并且保持至少一个所述导体不受驱动来被跨所述多个导体发送的。

16. 如权利要求15所述的装置,其特征在于,所述至少一对导体被用相反极性驱动。

17. 如权利要求15所述的装置,其特征在于,所述接收机电路被配置成将每个码元转换成多个位,并且所述触发器被配置成使用基于所检测到的向所述接收到的码元序列中的所述当前码元的转变所生成的所述时钟脉冲来捕捉所述经延迟的码元序列中的所述前一码元的所述多个位。

18. 如权利要求17所述的装置,其特征在于,所述接收机电路被配置成通过如下方式来将每个码元转换成多个位:跨不同所述导体对检测多个差分电压,并且基于检测到的差分电压来生成所述位。

## 多相位时钟生成方法

[0001] 相关申请

[0002] 本申请要求于2014年7月21日提交的美国非临时申请号No.14/336,977以及于2013年7月22日提交的美国临时申请号No.61/857,212的优先权,其整个说明书通过引用被纳入于此。

### 技术领域

[0003] 本公开一般涉及数据通信,并且尤其涉及多相位信令。

### 背景技术

[0004] 经常使用差分接口来传送高频信号以提供针对关键信号的共模拒斥。在传送和接收大量数据的设备(诸如存储器设备等)中,接口可能是昂贵的并且可能会消耗显著的功率。

### 发明内容

[0005] 以下给出对一个或多个实施例的简化概述以提供对此类实施例的基本理解。此概述不是所有构想到的实施例的详尽综览,并且既非旨在标识所有实施例的关键性或决定性要素亦非试图界定任何或所有实施例的范围。其唯一的目的是要以简化形式给出一个或更多个实施例的一些概念以作为稍后给出的更加具体的说明之序。

[0006] 根据一方面,本文中描述了一种用于接收数据的方法。该方法包括从多个导体接收码元序列,并且通过检测接收到的码元序列中的转变来生成时钟信号。该方法还包括延迟接收到的码元序列,以及使用该时钟信号来捕捉经延迟的码元序列中的一个或多个码元,其中该经延迟的码元序列中的前一码元是使用该时钟信号中的基于检测到的向所接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉的。

[0007] 第二方面涉及一种用于接收数据的设备。该设备包括用于从多个导体接收码元序列的装置、以及用于通过检测接收到的码元序列中的转变来生成时钟信号的装置。该设备还包括用于延迟接收到的码元序列的装置、以及用于使用该时钟信号来捕捉经延迟的码元序列中的一个或多个码元的装置,其中该经延迟的码元序列中的前一码元是使用该时钟信号中的基于检测到的向所接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉的。

[0008] 第三方面涉及一种接收系统。该接收系统包括配置成从多个导体接收码元序列的接收机电路、以及配置成通过检测所接收到的码元序列中的转变来生成时钟信号的时钟恢复电路。该接收系统还包括配置成延迟所接收到的码元序列的延迟电路、以及配置成使用该时钟信号来捕捉经延迟的码元序列中的一个或多个码元的触发器,其中该触发器使用该时钟信号中的基于检测到的向所接收到的码元序列中的当前码元的转变生成的时钟脉冲来捕捉经延迟的码元序列中的前一码元。

[0009] 为能达成前述及相关目的,这一个或多个实施例包括在下文中充分描述并在权利

要求中特别指出的特征。以下说明和所附插图详细阐述了这一个或更多个实施例的某些解说性方面。但是,这些方面仅仅是指示了可采用各个实施例的原理的各种方式中的若干种,并且所描述的实施例旨在涵盖所有此类方面及其等效方案。

## 附图说明

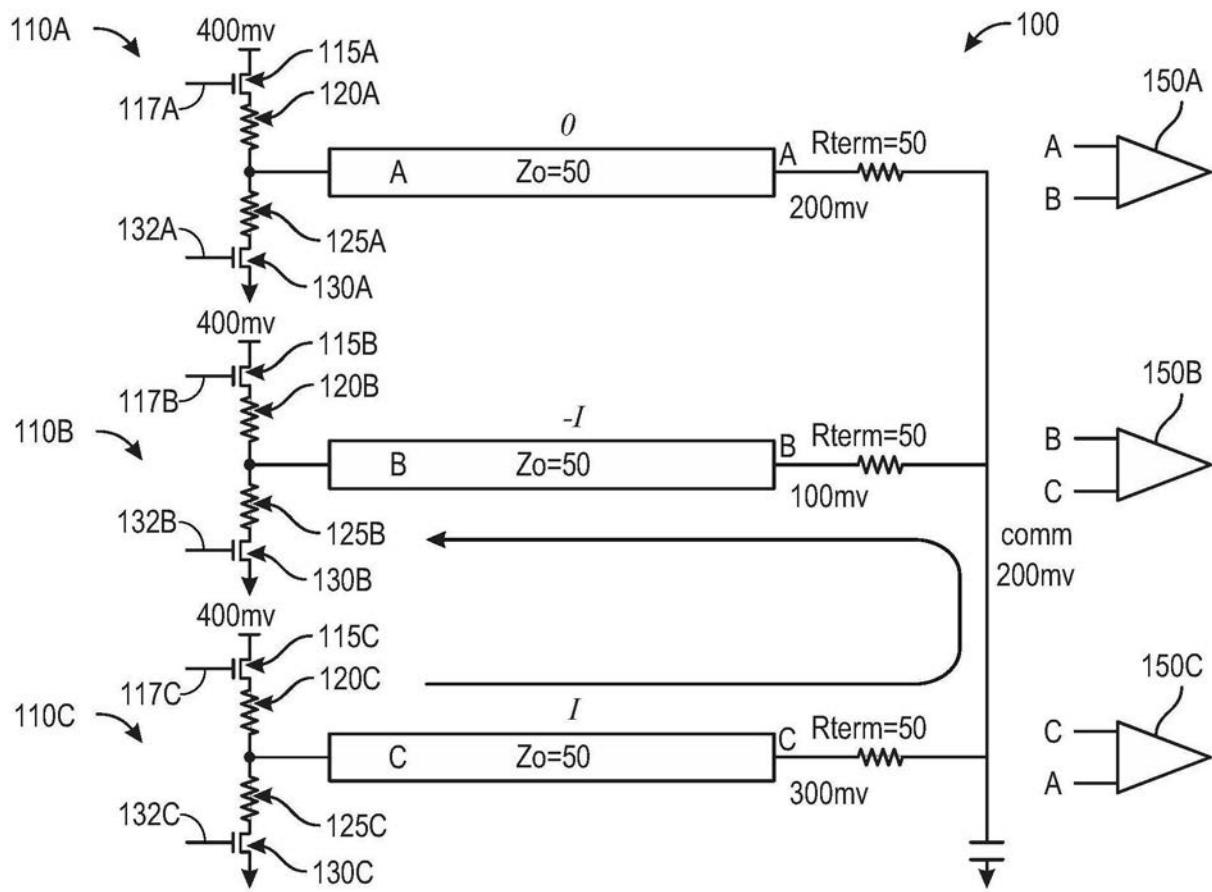

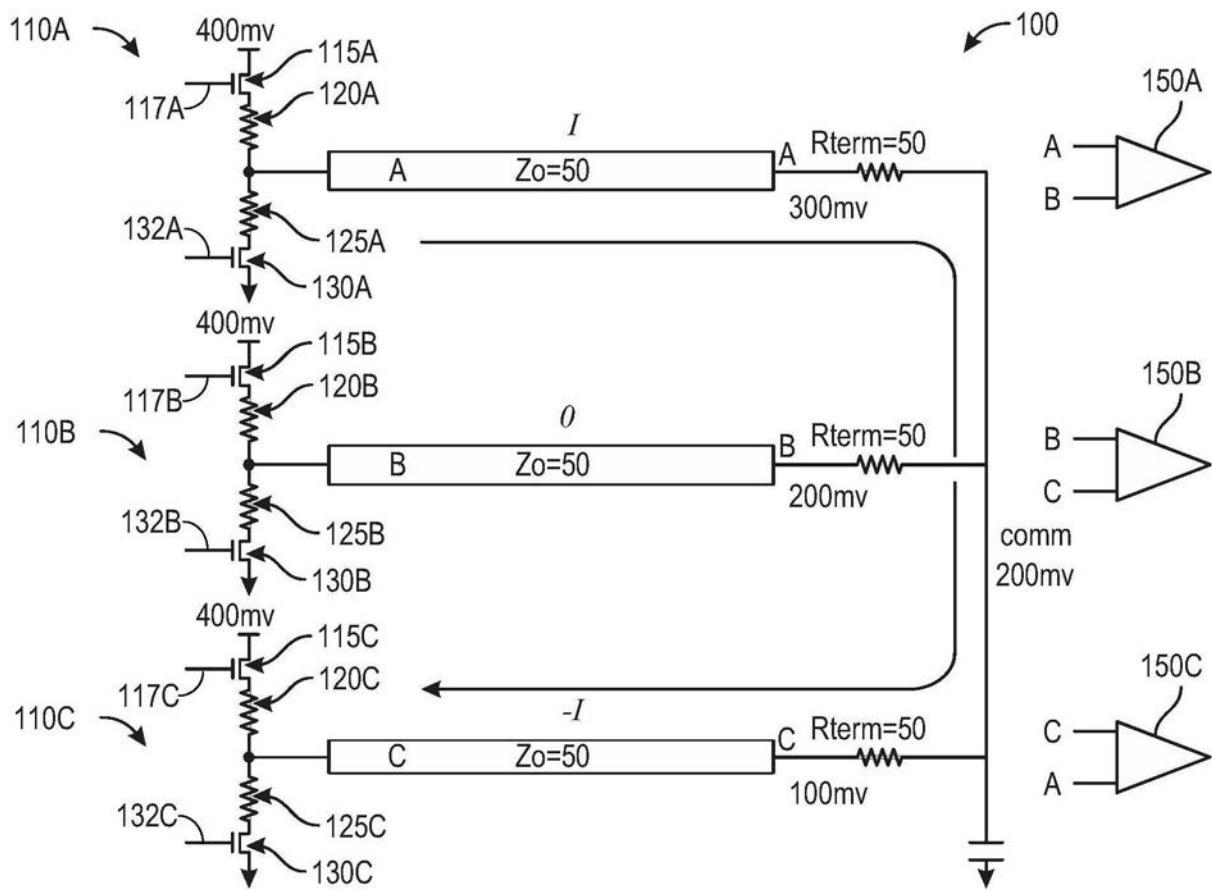

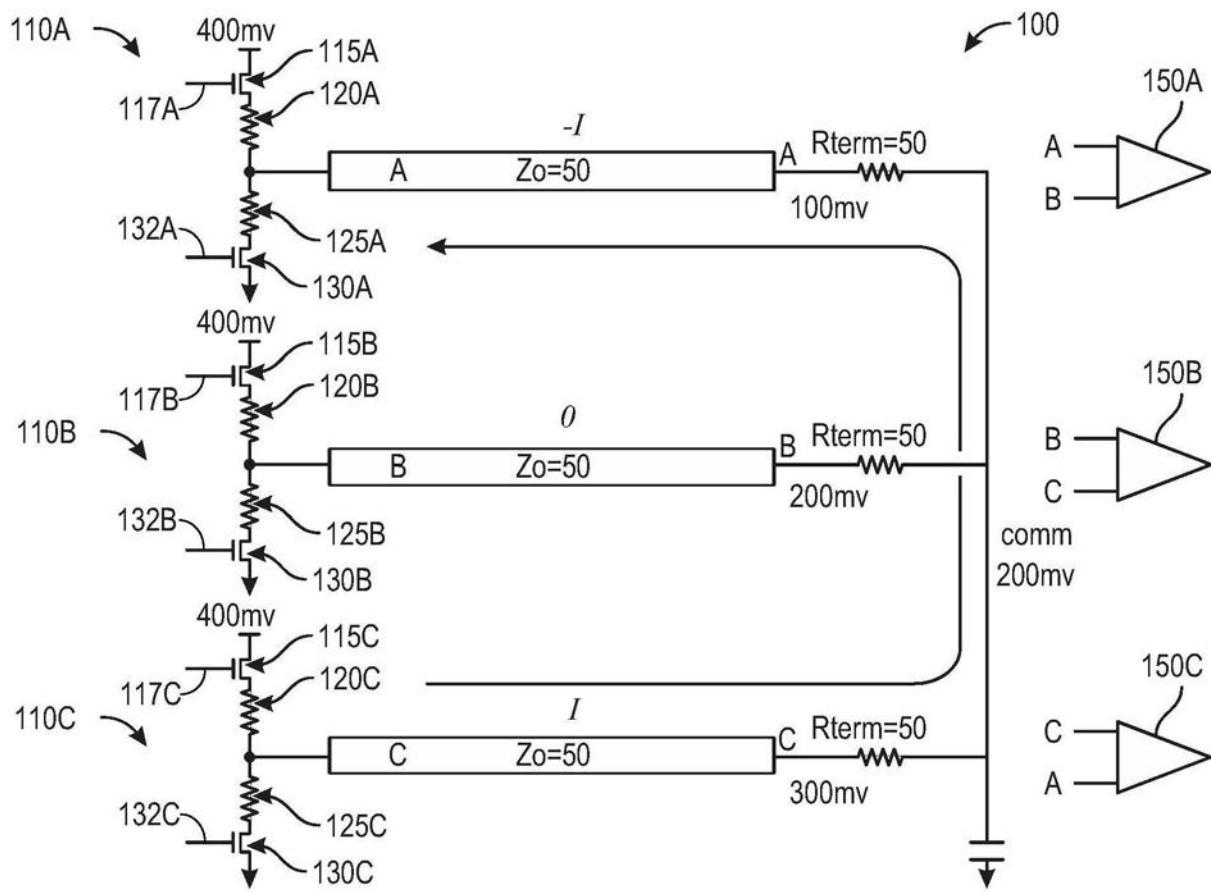

- [0010] 图1A-1F示出了被驱动成六个不同状态的示例性3相位通信系统。

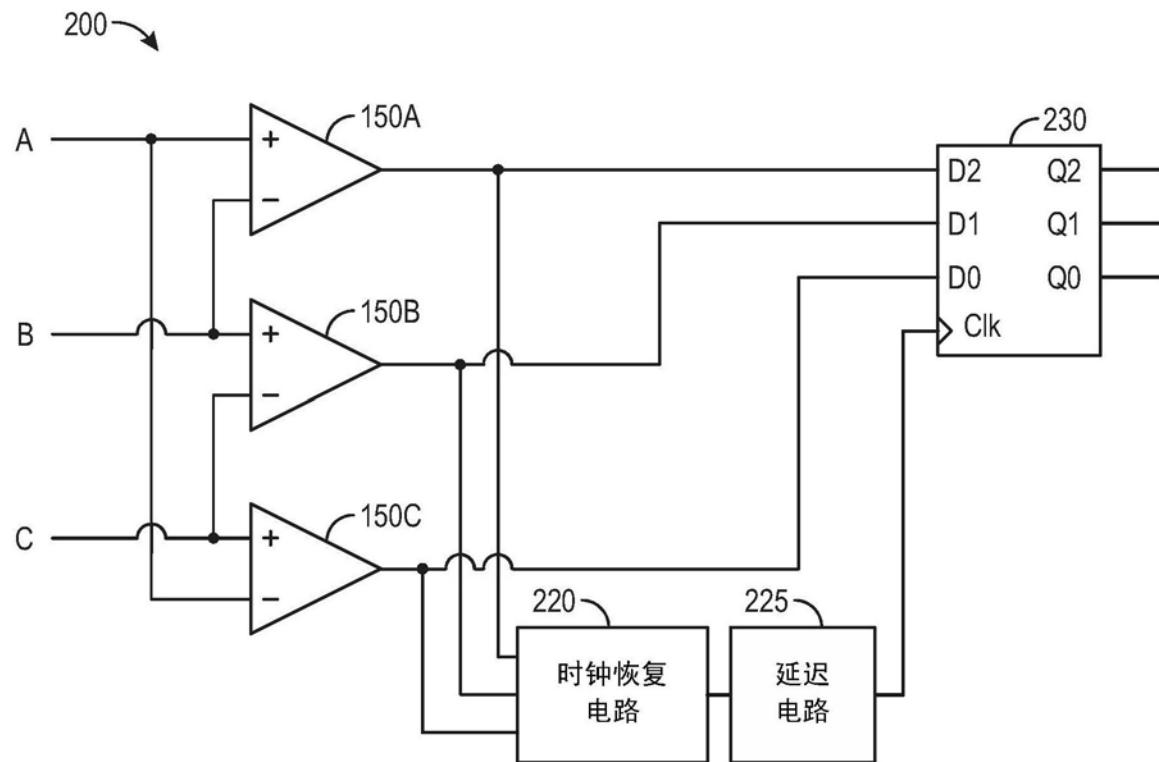

- [0011] 图2示出了根据本公开一个实施例的接收机侧系统。

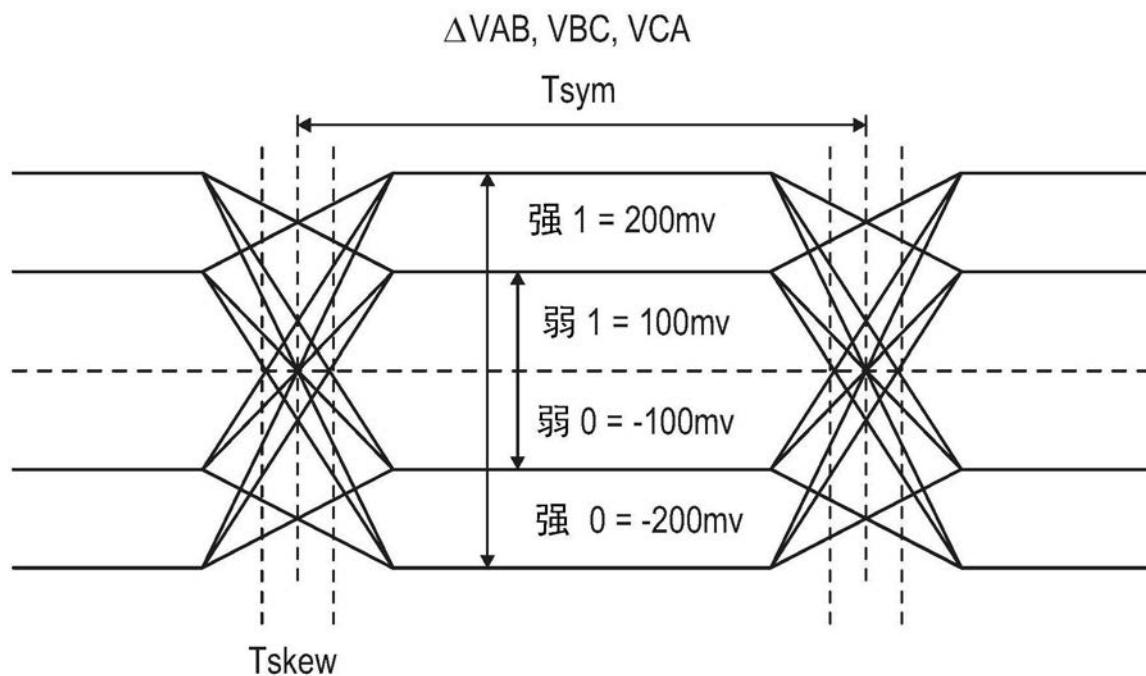

- [0012] 图3示出了根据本公开一实施例的差分电压转变的示例。

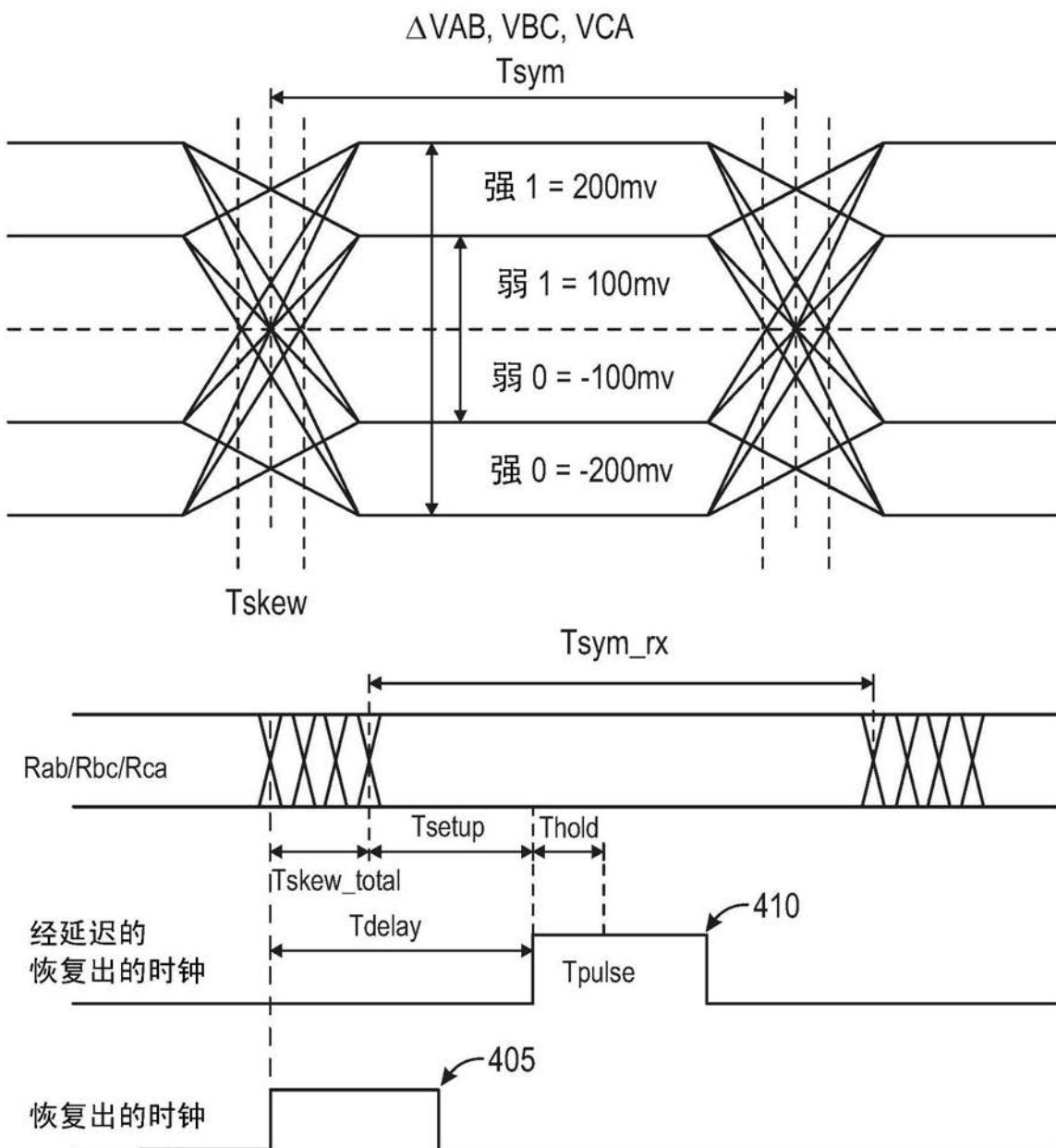

- [0013] 图4是根据本公开一实施例的解说捕捉码元的接收机输出位的时序图。

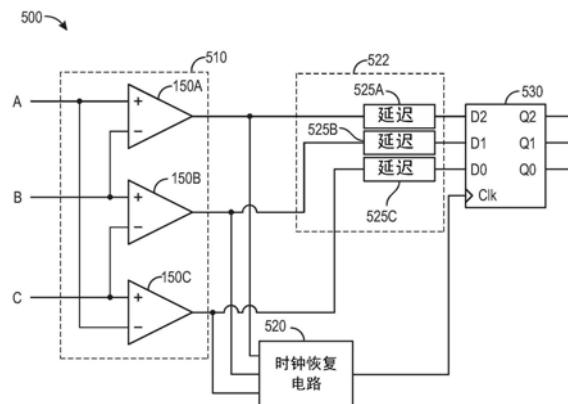

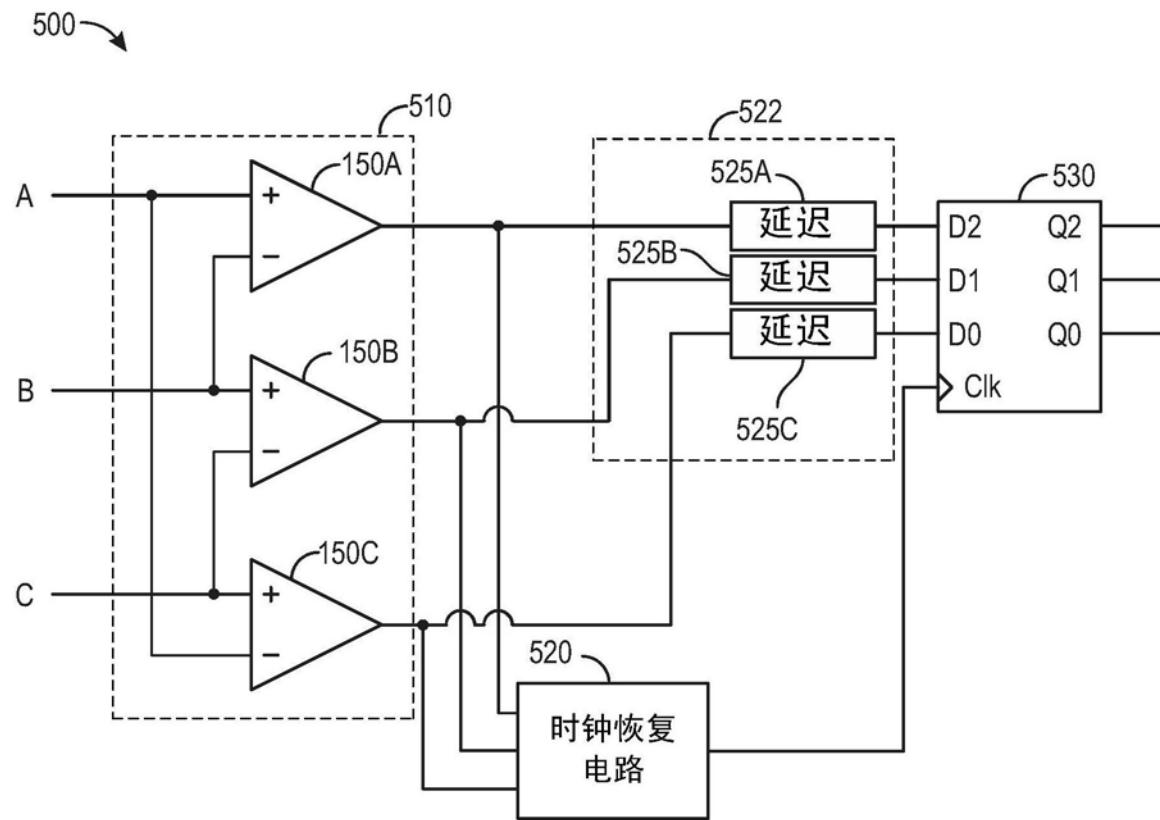

- [0014] 图5示出了根据本公开另一实施例的接收机侧系统。

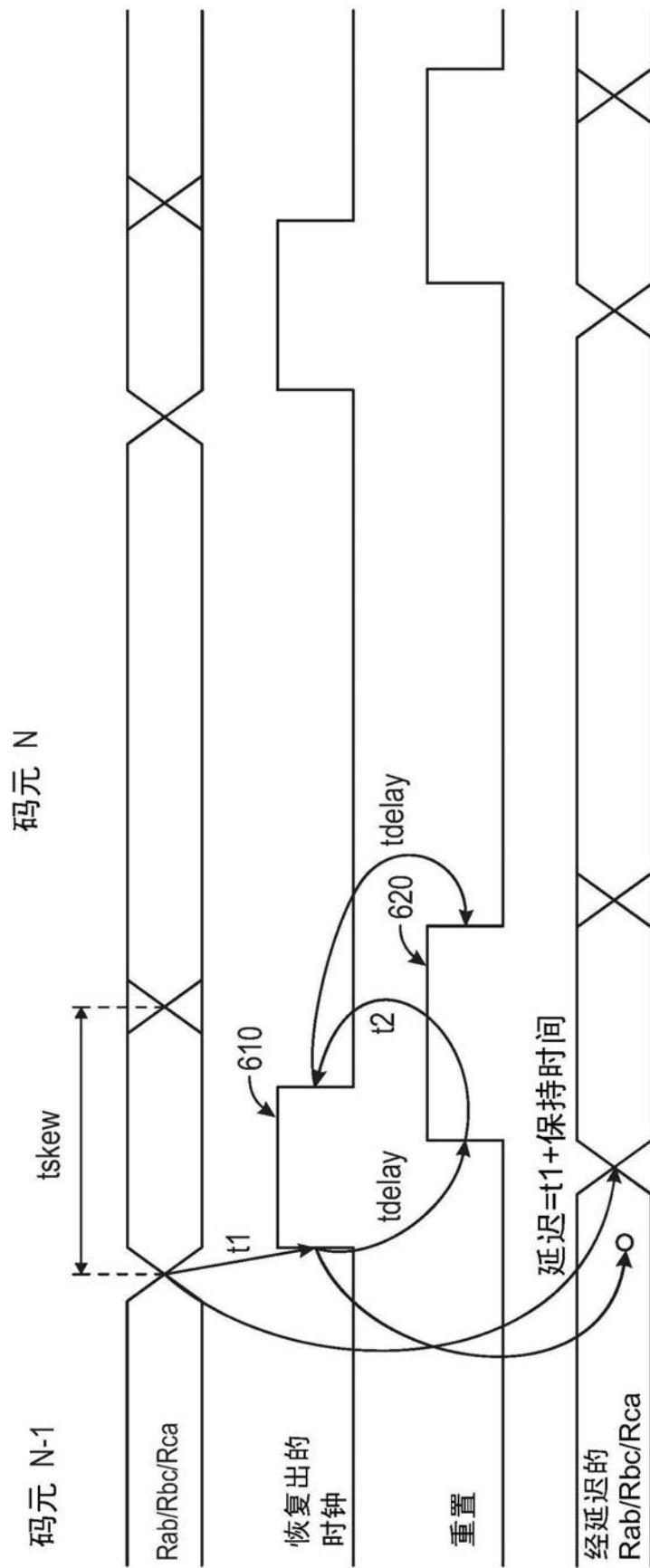

- [0015] 图6是根据本公开另一个实施例的解说捕捉码元的接收机输出位的时序图。

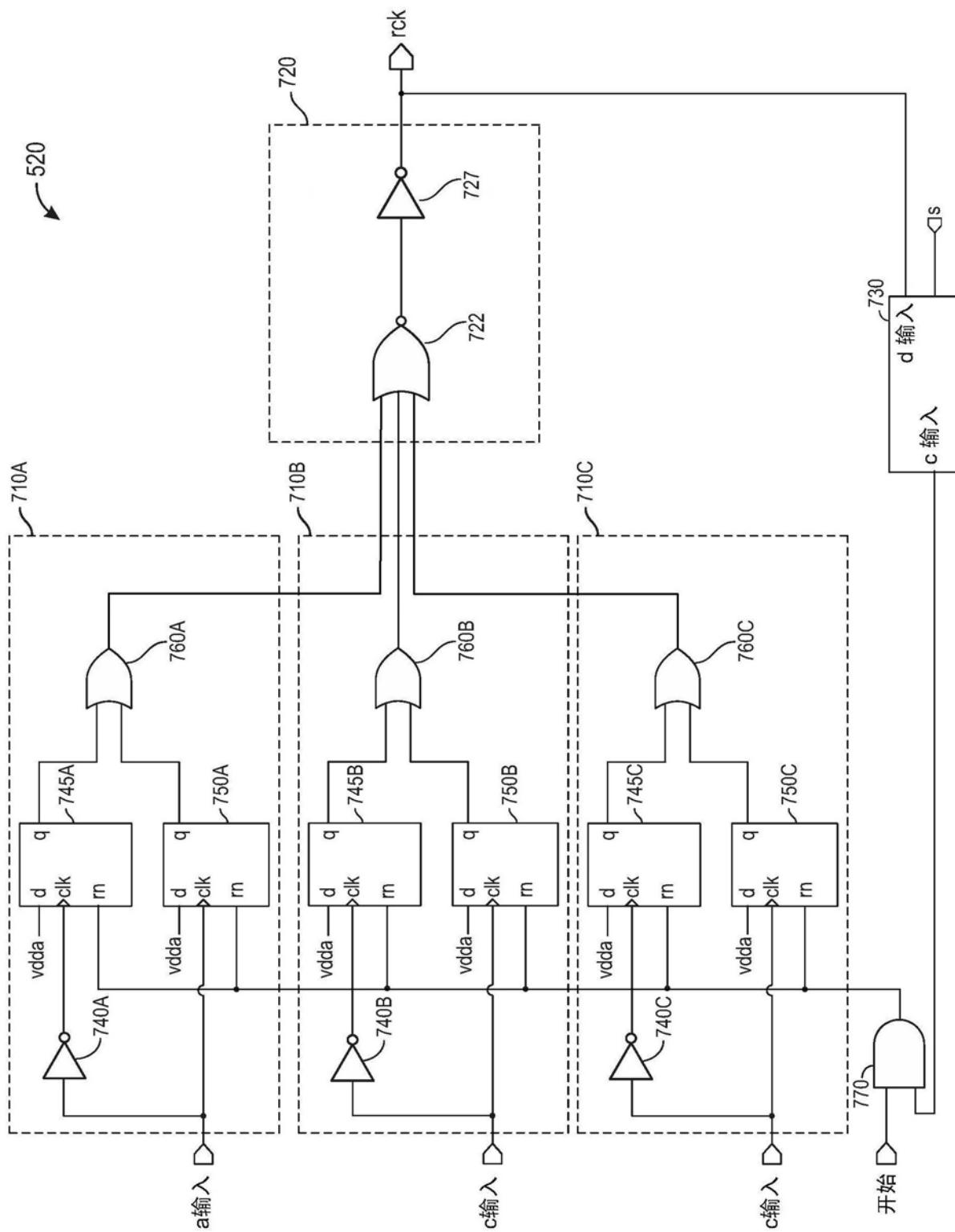

- [0016] 图7示出了根据本公开一实施例的时钟恢复电路的示例性实现。

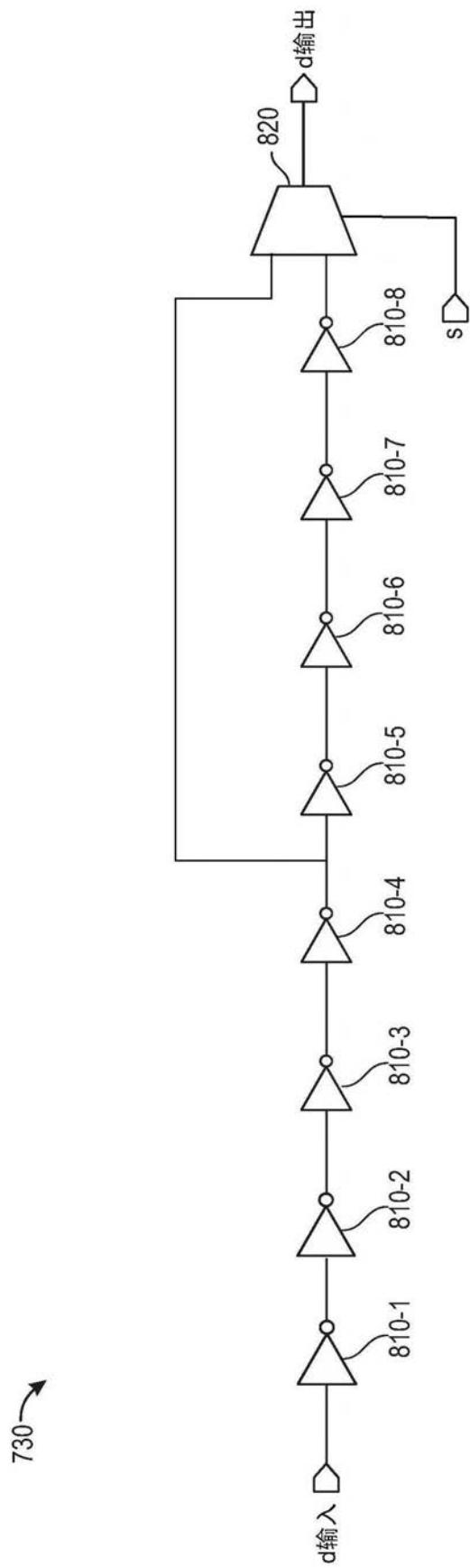

- [0017] 图8示出了根据本公开一实施例的时钟恢复电路中的延迟电路的示例性实现。

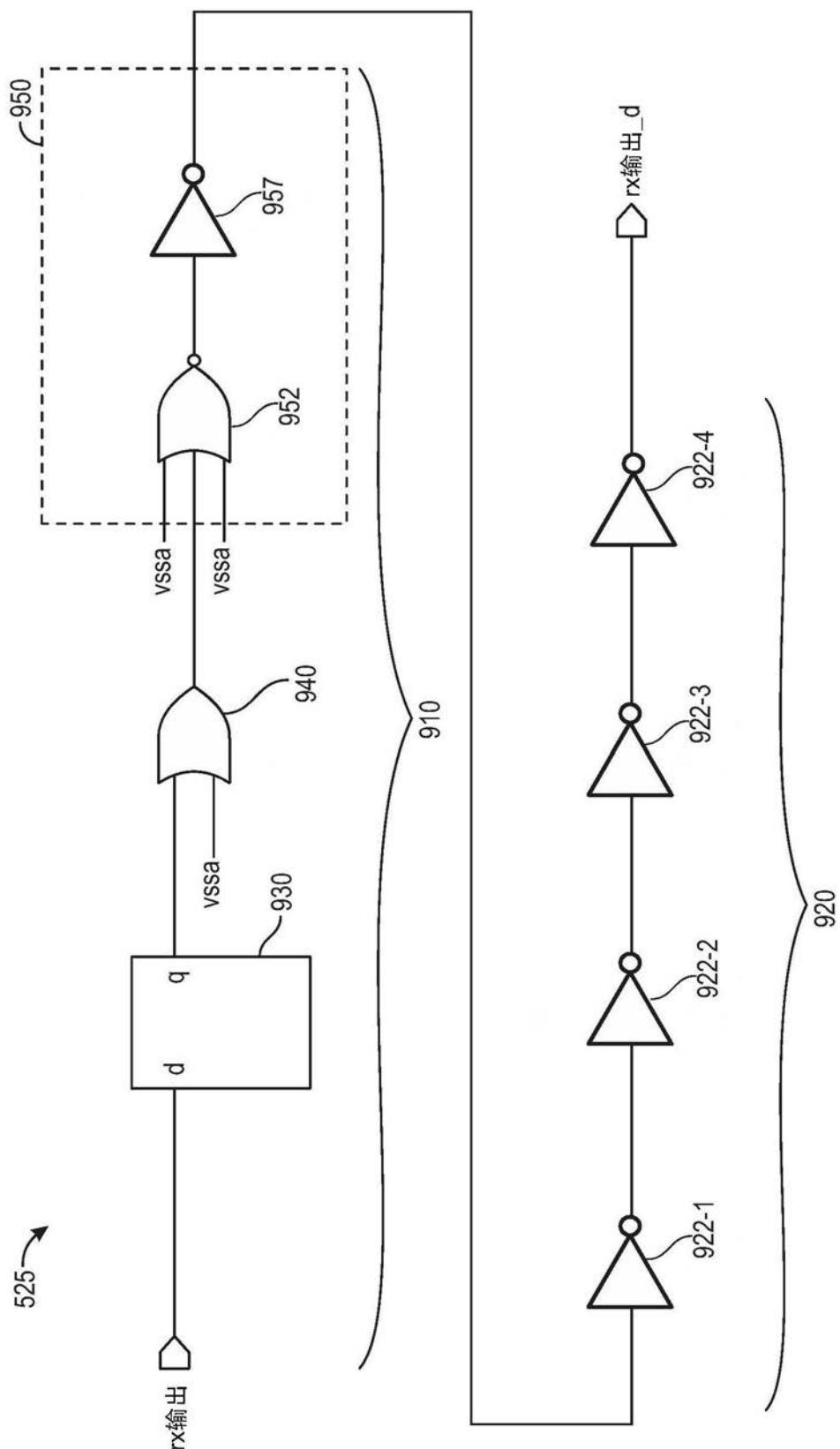

- [0018] 图9示出了根据本公开一实施例的延迟电路的示例性实现。

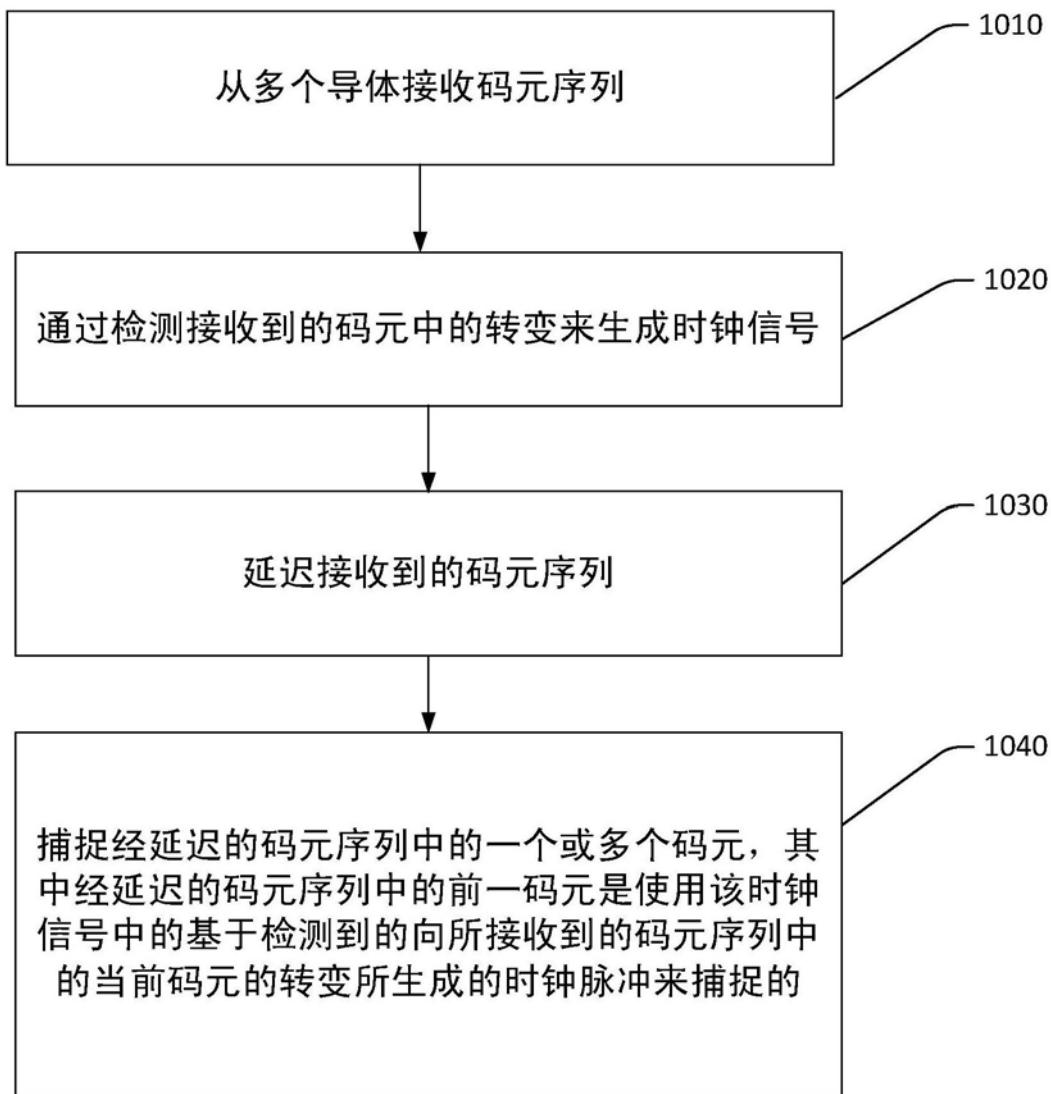

- [0019] 图10是根据本公开一实施例的解说用于接收数据的方法的流程图。

## 具体实施方式

[0020] 以下结合附图阐述的详细描述旨在作为各种配置的描述,而无意表示可实践本文中所描述的概念的仅有的配置。本详细描述包括具体细节以便提供对各种概念的透彻理解。然而,对于本领域技术人员将显而易见的是,没有这些具体细节也可实践这些概念。在一些实例中,以框图形式示出众所周知的结构与组件以避免湮没此类概念。

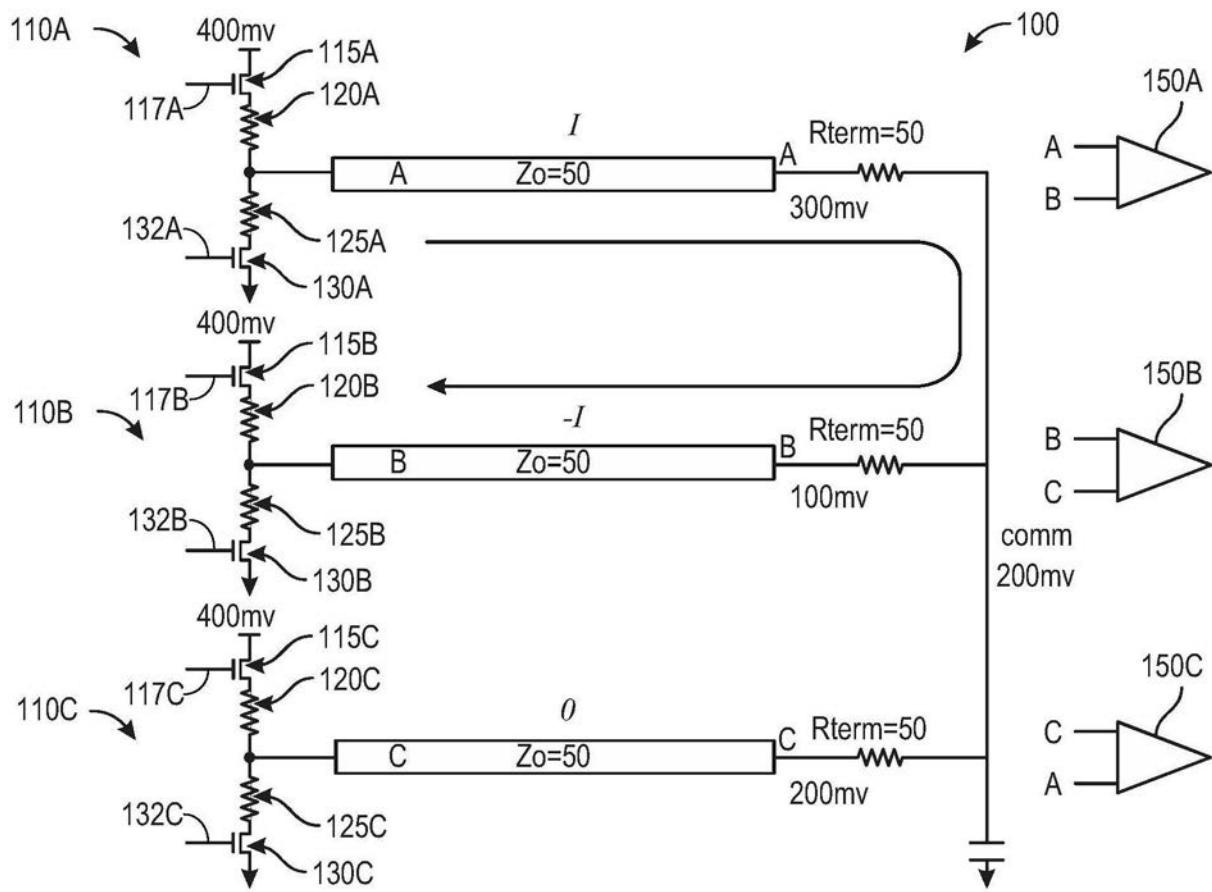

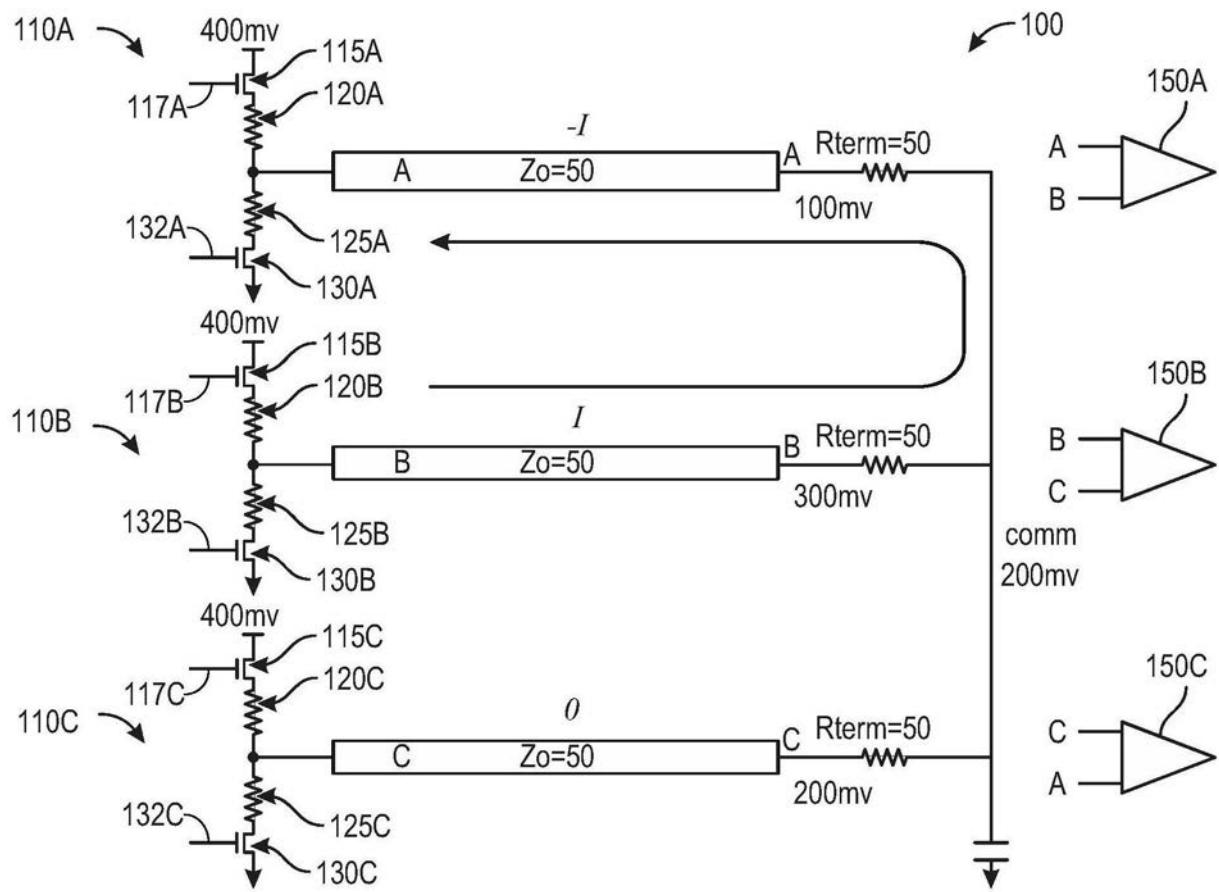

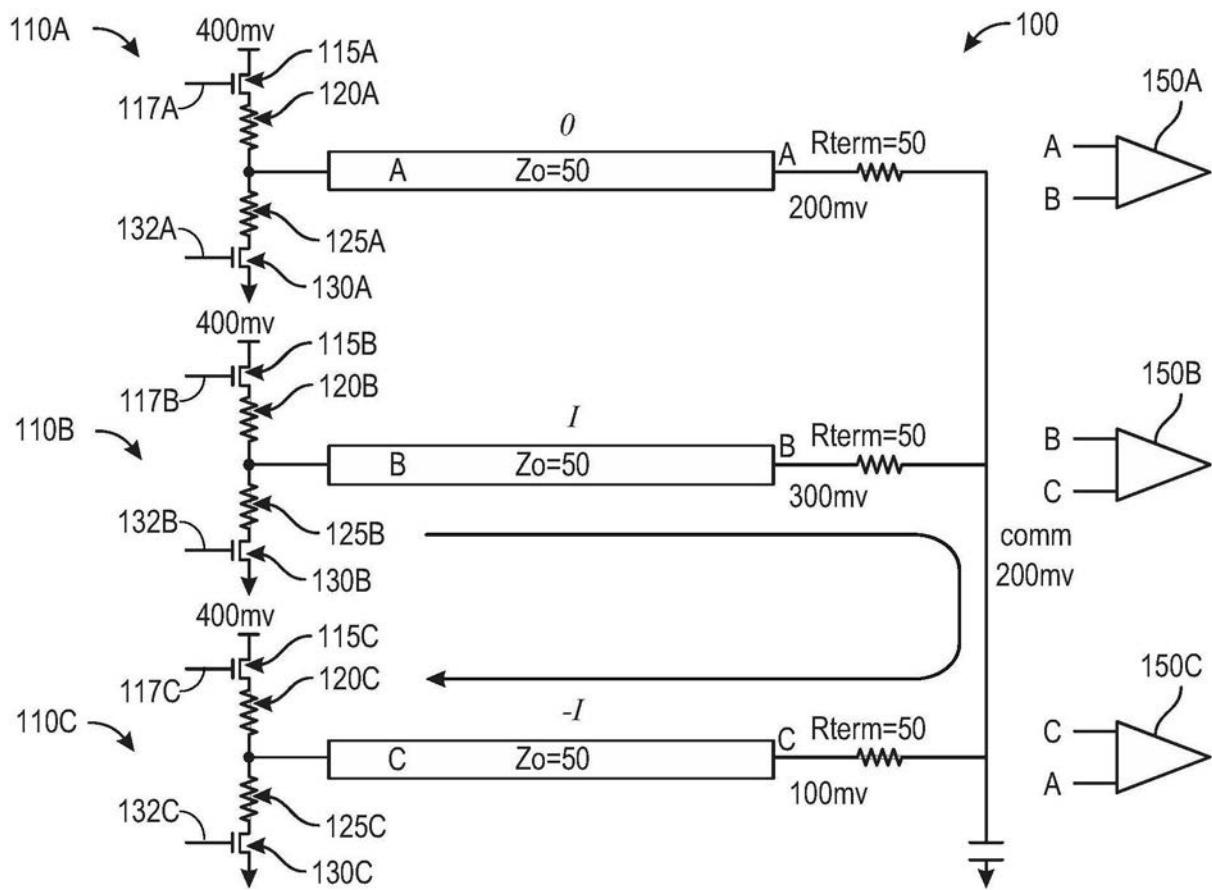

[0021] 图1A-1F示出了被配置成驱动至六个不同状态的示例性3相位通信系统100。3相位通信系统100包括标示为A、B和C的三条导线。每条导线可包括电路板上的导电迹线、集成电路(IC)上的导电迹线、传输线、或者其他类型的导体。3相位通信系统100还包括三个驱动器110A-110C。每条导线A、B和C在一端被耦合到驱动器110A-110C中的相应一者,并且在另一端被耦合到相应的终接电阻器(记为Rterm)。每个终接电阻器在一端被耦合到相应导线,并且在另一端被耦合到共同节点(记为comm)。每个终接电阻器可以具有相等的电阻。在图1A-1F中所示的示例中,每个终接电阻器具有大约 $50\Omega$ 的电阻,而每条导线A、B和C具有 $50\Omega$ 的特性阻抗。

[0022] 在一个实施例中,每个驱动器110A-110C包括上拉n型场效应晶体管(NFET)115A-115C,上拉电阻器120A-120C、下拉电阻器125A-125C、以及下拉NFET 130A-130C。对于每个驱动器110A-110C,相应的导线A、B和C被耦合在上拉电阻器120A-120C与下拉电阻器125A-125C之间。每个上拉电阻器120A-120C以及相应的上拉NFET 115A-115C的串联组合可以具有大约等于相应终接电阻器的电阻(图1A-1F中所示的示例中为 $50\Omega$ )的电阻。类似地,每个下拉电阻器125A-125C以及相应的下拉NFET 130A-130C的串联组合可以具有大约等于相应终接电阻器的电阻(图1A-1F中所示的示例中为 $50\Omega$ )。

[0023] 每个驱动器110A-110C可以配置成用正向流动电流(记为I)或负向流动电流(记为-I)驱动相应导线A、B和C,或者保持相应导线A、B和C不受驱动。为了用正电流I驱动相应导线A、B和C,上拉NFET 115A-115C被导通,并且下拉NFET 130A-130C被截止。这允许电流从

电源通过上拉NFET115A-115C和上拉电阻器120A-120C流向相应导线A、B和C。为了用负电流-I驱动相应导线A、B和C，上拉NFET 115A-115C被截止，并且下拉NFET130A-130C被导通。这允许电流从相应导线A、B和C通过下拉电阻器125A-125C和下拉NFET 130A-130C流向接地。为了保持相应导线A、B和C不受驱动，上拉NFET 115A-115C和下拉NFET 130A-130C二者都被截止。结果，几乎没有电流流过相应导线A、B和C。通过向相应门117A-117C输入逻辑一（例如，电源电压），上拉NFET 115A-115C可以被导通，且通过向相应门117A-117C输入逻辑零（例如，接地），上拉NFET 115A-115C可以被截止，并且通过向相应门132A-132C输入逻辑一（例如，电源电压），下拉NFET130A-130C可以被导通，且通过向相应门132A-132C输入逻辑零（例如，接地），下拉NFET 130A-130C可以被截止。

[0024] 在一个实施例中，驱动器110A-110C是受控的，从而在给定时间，导线A、B和C中只有两个被驱动而导线A、B和C中的另一个不受驱动。此外，这两个被驱动的导线是以相反极性被驱动的。例如，若导线A和B被驱动，那么导线A可以用正电流I被驱动，而导线B可以用负电流-I被驱动，或者反之。在该示例中，导线C是不受驱动的。

[0025] 在该示例中，有三对能够被同时驱动的不同的可能导线对：导线A和B、导线B和C，以及导线A和C。这三对导线对中的每一对可以被称为相位状态。对于每个相位状态，有两种可能的极性。例如，若导线A和B被驱动，那么导线A可以被正驱动而导线B可以被负驱动，或者导线A可以被负驱动而导线B可以被正驱动。由此，三条导线A、B和C可以具有三种不同的相位状态，其中每个相位状态有两种不同极性，结果有总共由六种可能的状态。如以下所进一步讨论的，这六种可能状态在图1A-1F中解说。

[0026] 图1A示出了第一状态，其中导线A和B被驱动，而导线C不受驱动，并且导线A被正驱动而导线B被负驱动。结果，电流通过导线A从发射机侧流向接收机侧，并且通过导线B回到发射机侧（由图1A中的电流循环表示）。几乎没有电流流过导线C。

[0027] 图1B示出了第二状态，其中导线A和B被驱动，而导线C不受驱动，并且导线B被正驱动而导线A被负驱动。结果，电流通过导线B从发射机侧流向接收机侧，并且通过导线A回到发射机侧（由图1B中的电流循环表示）。几乎没有电流流过导线C。

[0028] 图1C示出了第三状态，其中导线B和C被驱动，而导线A不受驱动，并且导线B被正驱动而导线C被负驱动。结果，电流通过导线B从发射机侧流向接收机侧，并且通过导线C回到发射机侧（由图1C中的电流循环表示）。几乎没有电流流过导线A。

[0029] 图1D示出了第四状态，其中导线B和C被驱动，而导线A不受驱动，并且导线C被正驱动而导线B被负驱动。结果，电流通过导线C从发射机侧流向接收机侧，并且通过导线B回到发射机侧（由图1D中的电流循环表示）。几乎没有电流流过导线A。

[0030] 图1E示出了第五状态，其中导线A和C被驱动，而导线B不受驱动，并且导线A被正驱动而导线C被负驱动。结果，电流通过导线A从发射机侧流向接收机侧，并且通过导线C回到发射机侧（由图1E中的电流循环表示）。几乎没有电流流过导线B。

[0031] 图1F示出了第六状态，其中导线A和C被驱动，而导线B不受驱动，并且导线C被正驱动而导线A被负驱动。结果，电流通过导线C从发射机侧流向接收机侧，并且通过导线A回到发射机侧（由图1F中的电流循环表示）。几乎没有电流流过导线B。

[0032] 三个导线A、B和C的这六种可能的状态允许发射机侧的数据位被解码成多个码元，其中每个码元对应于这六种状态中的一种。由于有6种状态，每码元可以编码 $\log_2(6) \approx$

2.585位。发射机侧的编码器(未示出)可将位编码成多个码元。对于每个码元,编码器可以控制驱动器110A-110C来将这三个导线A、B和C驱动至对应的状态以将码元传送到接收侧。

[0033] 在一个实施例中,接收机侧通过检测毗邻码元之间的状态转变来从接收到的码元中恢复时钟,并且使用恢复出的时钟来捕捉接收到的码元。为了在两个毗邻码元之间产生用于时钟恢复的状态转变,毗邻的码元需要具有不同状态。由此,从当前码元开始,下一码元可以具有不同于当前码元的状态的五种状态中的任何一种。这将每个码元的可能的状态的数目从六个状态降低到五个状态。有了5种状态,每码元可以编码 $\log_2(5) \approx 2.32$ 位。可以被用来使用三条导线A、B和C的不同可用状态来将位编码成码元的编码方案的示例在于2013年3月12日提交的题为“N-Phase Polarity Data Transfer(N相位极性数据转移)”的美国申请No.13/797,272中描述,其申请文件通过引用被纳入于此。

[0034] 在一个实施例中,在接收机侧通过检测导线A、B和C的不同对之间的差分电压来检测状态(并且由此检测码元)。在该实施例中,接收机侧包括正输入耦合到节点A且负输入耦合到节点B的第一接收机150A,正输入耦合到节点B且负输入耦合到节点C的第二接收机150B,以及正输入耦合到节点C且负输入耦合到节点A的第三接收机150C。节点A在导线A与相应终接电阻器之间,节点B在导线B与相应终接电阻器之间,并且节点C在导线C与相应终接电阻器之间。为了便于解说,接收机150A-150C与节点A、B和C之间的连接并未显式地在图1A-1F中示出。

[0035] 第一接收机150A将节点A与B之间的差分电压( $\Delta V_{AB}$ )的符号转换成位。若 $\Delta V_{AB}$ 为正,那么第一接收机150A输出位1,并且若 $\Delta V_{AB}$ 为负,那么第一接收机150B输出位0。第二接收机150B将节点B与C之间的差分电压( $\Delta V_{BC}$ )的符号转换成位。若 $\Delta V_{BC}$ 为正,那么第二接收机150B输出位1,并且若 $\Delta V_{BC}$ 为负,那么第二接收机150B输出位0。第三接收机150C将节点C与A之间的差分电压( $\Delta V_{CA}$ )的符号转换成位。若 $\Delta V_{CA}$ 为正,那么第三接收机150C输出位1,并且若 $\Delta V_{CA}$ 为负,那么第三接收机150C输出位0。如以下参考图1A-1F所进一步讨论的,接收机150A-150C的三个输出位提供了接收到的码元的数字表示。

[0036] 如以上所讨论的,图1A示出了第一状态,其中电流通过导线A从发射机侧流向接收机侧,并且通过导线B回到发射机侧,没有电流流过导线C。在图1A中所示的示例中,电源具有400mV的电压,并且每个电阻器具有相等的电阻(例如,50Ω)。结果,由于跨第一驱动器110A的上拉电阻器120A有100mV的电压降,节点A处的电压大约为300mV。由于跨节点A和B的这两个终接电阻器有200mV的电压降,节点B处的电压大约为100mV。节点C处的电压大约等于共同节点(记为comm)处的电压,因为没有电流流过导线C及其相应的终接电阻器。共同节点处的电压介于节点A和B处的电压之间的半当中,大约为200mV。由此,在第一状态中, $\Delta V_{AB}$ 为200mV, $\Delta V_{BC}$ 为-100mV,而 $\Delta V_{CA}$ 为-100mV。第一、第二和第三接收机150A-150C的输出位分别是1、0和0。

[0037] 图1B示出了第二状态,其中电流通过导线B从发射机侧流向接收机侧,并且通过导线A回到发射机侧,没有电流流过导线C。结果,节点A处的电压大约为100mV,节点B处的电压大约为300mV,并且节点C处的电压大约为200mV。由此,在第二状态中, $\Delta V_{AB}$ 为-200mV, $\Delta V_{BC}$ 为100mV,而 $\Delta V_{CA}$ 为100mV。第一、第二和第三接收机150A-150C的输出位分别是0、1和1。

[0038] 图1C示出了第三状态,其中电流通过导线B从发射机侧流向接收机侧,并且通过导线C回到发射机侧,没有电流流过导线A。结果,节点A处的电压大约为200mV,节点B处的电压

大约为300mV，并且节点C处的电压大约为100mV。由此，在第三状态中， $\Delta V_{AB}$ 为-100mV， $\Delta V_{BC}$ 为200mV，而 $\Delta V_{CA}$ 为-100mV。第一、第二和第三接收机150A-150C的输出位分别是0、1和0。

[0039] 图1D示出了第四状态，其中电流通过导线C从发射机侧流向接收机侧，并且通过导线B回到发射机侧，没有电流流过导线A。结果，节点A处的电压大约为200mV，节点B处的电压大约为100mV，并且节点C处的电压大约为300mV。由此，在第四状态中， $\Delta V_{AB}$ 为100mV， $\Delta V_{BC}$ 为-200mV，而 $\Delta V_{CA}$ 为100mV。第一、第二和第三接收机150A-150C的输出位分别是1、0和1。

[0040] 图1E示出了第五状态，其中电流通过导线A从发射机侧流向接收机侧，并且通过导线C回到发射机侧，没有电流流过导线B。结果，节点A处的电压大约为300mV，节点B处的电压大约为200mV，并且节点C处的电压大约为100mV。由此，在第五状态中， $\Delta V_{AB}$ 为100mV， $\Delta V_{BC}$ 为100mV，而 $\Delta V_{CA}$ 为-200mV。第一、第二和第三接收机150A-150C的输出位分别是1、1和0。

[0041] 图1F示出了第六状态，其中电流通过导线C从发射机侧流向接收机侧，并且通过导线A回到发射机侧，没有电流流过导线B。结果，节点A处的电压大约为100mV，节点B处的电压大约为200mV，并且节点C处的电压大约为300mV。由此，在第六状态中， $\Delta V_{AB}$ 为-100mV， $\Delta V_{BC}$ 为-100mV，而 $\Delta V_{CA}$ 为200mV。第一、第二和第三接收机150A-150C的输出位分别是0、0和1。

[0042] 由此，在该示例中，对应于被正驱动的导线的节点处的电压大约为300mv，对应于被负驱动导线的节点处的电压大约为100mv，并且对应于不受驱动的导线的节点处的电压为大约200mv。将会领会，本公开的实施例不限于以上示例，并且电源电压可以具有其他电压，并且电阻器可以具有其他电阻。一般而言，对应于被正驱动导线的节点处的电压可以记为V1，对应于被负驱动的导线的节点处的电压可以记为V2，其中V1大于V2，并且对应于不受驱动的导线的节点处的电压可以大约为(V1+V2)/2，假定了另两个节点之间的电阻器具有相等的电阻。

[0043] 由此，图1A-1F中所示的每个状态在接收机150A-150C处产生了输出位的唯一性组合。结果，接收机150A-150C的输出位能够被用于区分三个导线A、B和C的不同状态，并且因此能被用于提供接收到的码元的数字表示。这允许解码器(未示出)恢复编码在来自接收机150A-150C的输出位的码元中的位。

[0044] 通信系统100可以被用在各种应用中以提供设备之间的通信。例如，通信系统100可以被用于在片上电路(例如，存储器控制器)和存储器设备(例如，DRAM设备)之间传达数据、控制和/或地址信号。通信系统100有利地能够以一条附加导线以及一个附加驱动器为代价，来每码元传送两倍于使用单对差分导线的常规通信系统以上的位。将会领会，通信系统100不限于3条导线，并且可以包括更多的导线来增加可能状态的数目，并且因此增加吞吐量。例如，通信系统可包括6条导线，其中对于每个状态，有两对导线被驱动并且两条导线不受驱动。

[0045] 图2示出了根据一个实施例的用于捕捉接收机150A-150C的输出位的接收机侧系统200。该系统200包括触发器230、时钟恢复电路220以及延迟电路225。时钟恢复电路220被配置成通过检测接收机输出中的转变来生成时钟。例如，对于每个码元，时钟恢复电路220可以配置成检测接收机输出中关于该码元的最早的转变(1到0或0到1)，并且生成上升沿大致与所检测到的转变对齐的时钟脉冲。延迟电路225被配置成延迟来自时钟恢复电路220的

时钟，并且向触发器230的时钟输入输出经延迟的时钟。触发器230被配置成在经延迟的时钟的每个上升沿上捕捉接收机输出位，并且向解码器(未示出)输出所捕捉到的位。虽然触发器230在图2中为了便于解说而被描绘为一个触发器，但将会领会，触发器230可以包括三个触发器，每个接收机输出有一个触发器。为了使得触发器230可靠地捕捉接收机输出位，经延迟的时钟需要满足特定的定时要求，如以下参考图3和4所进一步讨论的。

[0046] 图3是示出对差分电压 $\Delta VAB$ 、 $\Delta VBC$ 和 $\Delta VCB$ 中的每一者而言可能的不同转变的时序图。每个差分电压具有四个可能的电压电平： $-200\text{mV}$ 、 $-100\text{mV}$ 、 $100\text{mV}$ 和 $200\text{mV}$ 。每当这三个导线A、B和C在状态(码元)之间转变时，每个差分电压可以从这四个电压电平中的任何一者转变到其他电压电平中的任何一者，如图3中所示。

[0047] 每个接收机150A-150C的输出在相应差分电压交越零电压点时(描绘为图3中的虚线)做出转变(1到0或0到1)如图3中所示，不是每个可能的差分电压转变都交越零电压点，并且因此不是每个差分电压转变都导致相应接收机输出的转变。然而，三条导线A、B和C的状态中的每个转变(每个码元转变)导致接收机150A-150C的三个输出中的至少一个输出的转变。

[0048] 对于诸交越零电压点的差分电压转变，交越零电压的定时各不相同。例如，从 $-100\text{mV}$ 到 $200\text{mV}$ 的差分电压转变早于从 $-100\text{mV}$ 到 $100\text{mV}$ 的差分电压转变交越零电压点，并且因此使得相应的接收机输出更早地从0转变到1。交越零电压的定时差别导致诸接收机输出的转变的定时上的不确定性。在图3中，接收机输出的转变定时中的不确定性的量由被称为Tskew的时间间隔来表示。对于给定码元，Tskew可以由接收机输出的最早可能转变和接收机输出的最晚可能转变来界定，如图3中的示例中所示。

[0049] 图4是根据一个实施例的解说针对码元的接收机输出位的捕捉的时序图。在该示例中，时钟恢复电路220被配置成检测该码元的诸接收机输出的最早转变，并且生成上升沿大致与所检测到的转变对齐的时钟脉冲405。为了定时分析的目的，最早的转变被假定为与Tskew的最左边的边界对齐。如图4中所示，时钟脉冲405随后由延迟电路225延迟达时间延迟Tdelay以成为时钟脉冲410。触发器230在经延迟的时钟脉冲410的大约上升沿处捕捉该码元的接收机输出位。

[0050] 在该示例中，Tdelay等于或大于Tskew\_total与触发器230的建立时间(记为Tsetup)之和。Tskew\_total是图3中的Tskew与由于诸导线的信道条件导致的偏斜(skew)之和。时钟脉冲410被延迟达Tskew\_total以提供计及以上所讨论的接收机输出的转变中的不确定性的定时余裕。例如，在Tskew\_total以内的这些接收机输出之一可能会比这些接收机输出中的另一个转变得更早。时钟脉冲410被进一步延迟达Tsetup以满足触发器230的建立时间要求。

[0051] 时钟脉冲410的宽度(记为Tpulse)等于或大于触发器230的最小脉冲宽度要求(记为Tmin\_pulse)。时钟脉冲410的上升沿之后的Ts sym\_rx以内剩余的时间需要大于触发器230的保持时间(记为Thold)以满足触发器230的保持时间要求。Ts sym\_rx等于Ts sym-Tskew\_total，其中Ts sym为包括了偏斜的码元周期。由此，Ts sym\_rx至少需要等于Tsetup与Thold或Tpulse中的最大值之和。

[0052] 延迟电路225中的工艺-电压-温度(PVT)差别可能会引起Tdelay中的很大差别。例如，工艺差别能够对Tdelay具有很大影响。若延迟电路225用快速晶体管(例如，快速工艺

角)制造,那么Tdelay可以更短,并且若延迟电路225用慢速晶体管(例如,慢速工艺角)制造,那么Tdelay可以更长。而且,触发器230中的PVT差别能够引起Tsetup上的差别。结果,附加的定时余裕需要被预算入码元时间周期Tsym\_rx中以计及Tdelay和Tsetup上的差别。这样做增大了码元时间周期Tsym\_rx,这降低了数据速率。

[0053] 图5示出了根据本公开另一个实施例的用于捕捉接收机150A-150C的输出位的接收机侧系统500。与之前相同,系统500检测接收机输出中的转变以生成时钟。然而,如以下进一步所讨论的,系统500延迟接收机输出,从而从这些接收机输出的向当前码元(码元N)的转变生成的时钟沿被用来捕捉(采样)前一码元(码元N-1)的诸接收机输出位。

[0054] 如以上所讨论的,接收机侧系统500包括耦合到导线A-C的接收机150A-150C。如图5中所示,接收机150A-150C可以被共同视为接收机电路510。接收机侧系统500包括触发器530、时钟恢复电路520、以及延迟电路522。如图5中所示,延迟电路522可进一步包括三个延迟电路525A-525C,其中每个延迟电路525A-525C被耦合到接收机150A-150C中的相应一者的输出。时钟恢复电路520被配置成通过检测接收机150A-150C的输出中的转变来生成时钟。例如,对于每个码元,时钟恢复电路520可以配置成检测接收机输出中关于该码元的最早转变,并且生成上升沿大致与所检测到的转变对齐的时钟脉冲。

[0055] 每个延迟电路525A-525C被配置成延迟这些接收机输出的相应一者,并向触发器530的对应数据输入输出经延迟的接收机输出。触发器530被配置成在时钟的每个上升沿上捕捉经延迟的接收机输出位,并且向解码器(未示出)输出所捕捉的位。

[0056] 在一个实施例中,延迟电路525A-525C被配置成延迟接收机输出长达约等于触发器530的保持时间与t1之和的时间延迟,其中t1约等于时钟恢复电路520在检测到接收机输出中的转变之后输出时钟沿所花的时间。如以下进一步所讨论的,延迟电路525A-525C延迟接收机输出,从而从这些接收机输出的向当前码元(码元N)的转变生成的时钟沿由触发器530使用来捕捉(采样)前一码元(码元N-1)的接收机输出位。

[0057] 图6是根据一个实施例的解说接收机侧系统500中的接收机输出位(记为Rac/Rab/Rac)的捕捉的时序图。在该示例中,时钟恢复电路520检测这些接收机输出的向当前码元(码元N)的最早转变,并且生成上升沿大致与所检测到的转变对齐的时钟脉冲610。为了定时分析的目的,最早的转变被假定为与tskew的最左边的边界对齐。如图6中所示,由于时钟恢复电路520中的传播延迟,检测到的最早转变的时间与时钟脉冲610的上升沿之间存在短延迟t1。

[0058] 延迟电路525A-525C将这些接收机输出延迟长达约等于触发器530的保持时间与t1之和的时间延迟。因为接收机输出的延迟,当触发器530接收到从检测到的在这些接收机输出中关于当前码元(码元N)的转变所生成的时钟脉冲610的上升沿时,触发器530仍然接收前一码元(码元N-1)的接收机输出位。结果,触发器530使用从这些接收机输出的向当前码元(N)的转变所生成的时钟沿来捕捉此前一码元(码元N-1)的接收机输出位。此前一码元(N-1)的接收机输出位被采样的点由图6中的开口圆来表示。

[0059] 延迟接收机输出达触发器530的保持时间帮助确保前一码元(码元N-1)的接收机输出位满足触发器530的保持时间要求,并且因此被触发器530可靠地捕捉。延迟接收机输出达t1计及在时钟恢复520处生成时钟脉冲610时的短延迟。

[0060] 触发器530的保持时间一般比建立时间和tskew小得多。结果,接收机输出的延迟

可以显著小于之前实施例中的时钟延迟。这显著降低了由于PVT导致的延迟差别，并且因此降低了需要被预算入码元时间周期Tsym\_rx的定时余裕。这些降低的定时余裕允许码元时间周期Tsym\_rx更短以达成更高的数据速率。

[0061] 图7示出了根据本公开的一实施例的时钟恢复电路520。该时钟恢复电路520包括耦合到第一接收机150A的输出的第一边沿检测电路710A，耦合到第二接收机150B的输出的第二边沿检测电路710B，以及耦合到第三接收机150C的输出的第三边沿检测电路710C。时钟恢复电路520还包括或(OR)门720和延迟电路730。在图7中所示的示例中，或门720用与反相器727串联耦合的或非(NOR)门722实现。

[0062] 每个边沿检测电路710A-710C包括第一触发器750A-750C，第二触发器745A-745C、反相器740A-740C、以及或门760A-760C。第一触发器750A-750C具有耦合到相应接收机150A-150C的输出的时钟输入，以及耦合到电源电压vdda的数据输入。第一触发器750A-750C被配置成当在时钟输入处检测到上升信号沿时，向或门760A-760C的输入之一输出1。结果，第一触发器750A-750C检测相应接收机输出中的上升转变(0到1)并且在当检测到上升转变时输出1。第二触发器745A-750C具有通过反相器740A-740C耦合到相应接收机150A-150C的输出的时钟输入，以及耦合到电源电压vdda的数据输入。第二触发器745A-750C被配置成当在时钟输入处检测到上升信号沿时，向或门760A-760C的另一输入输出1。因为反相器740A-740C将接收机输出反相，所以第二触发器745A-745C检测接收机输出中的下降转变(1到0)，并且在当下降转变被检测到时向或门760A-760C的另一输入输出1。当第一触发器750A-750C或者第二触发器745A-745C中的任一者输出1时，或门760A-760C输出1，并且因此当检测到相应接收机输出中的上升或下降转变中的任一者时输出1。由此，每个边沿检测电路710A-710C当在相应接收机输出中检测到转变(上升或下降转变)时输出1。

[0063] 或门720门具有耦合到第一边沿检测电路710A的输出的第一输入、耦合到第二边沿检测电路710B的输出的第二输入，以及耦合到第三边沿检测电路710C的输出的第三输入。结果，或门720在边沿检测电路710A-710C中的任一者输出1时输出1，并且因此当边沿检测电路710A-710C中的任一者在相应接收机输出中检测到转变时输出1。

[0064] 假定边沿检测单路710A-710C中的触发器在每个码元前被重置，则或门720在每个码元的开始处初始地输出0。当边沿检测电路710A-710C中的第一者检测到相应接收机输出中的转变并且向或门720输出1时，或门720输出1，从而在时钟恢复电路520的输出(记为rck)处生成时钟脉冲610。或门720的输出从0到1的转变对应于时钟脉冲610的上升沿。由于触发器和或门中的传播延迟，在检测到接收机输出中的第一(最早)转变与时钟脉冲610的上升沿之间有短时间延迟t1。该时间延迟在图6中由标记为t1的箭头描绘。

[0065] 时钟恢复电路520的输出通过延迟电路730被反馈到触发器745A-745C以及750A-750C的重置输入。当或门720的输出从0转变到1(上升时钟沿)时，延迟电路730在tdelay的时间延迟之后向触发器的重置输入输出重置信号620。该延迟在图6中由标记为tdelay的从时钟脉冲610的上升沿到重置信号620的开始的箭头描绘。重置信号620使得所有的触发器输出0。结果，在短延迟t2之后，或门720的输出从1转变到0。从1到0的转变对应于时钟脉冲610的下降沿。由此，如图6中所示，时钟脉冲的宽度约等于tdelay与t2之和。

[0066] 当或门的输出从1转变到0时，延迟电路730在延迟电路730的时间延迟tdelay之后结束去往这些触发器的重置输入的重置信号620。该时间延迟在图6中由标记为tdelay的从

时钟脉冲610的下降沿到重置信号620的结束的箭头描绘。在重置信号620结束之后，触发器准备好检测接收机输出中的关于下一码元的转变。

[0067] 在一方面，时钟恢复电路520满足一下定时约束：

[0068]  $t_{skew} < t_1 + t_{delay} + t_2 + t_{delay}$ .

[0069] 该约束帮助确保重置信号620在当前码元的 $t_{skew}$ 之后结束。若重置信号620在当前码元的 $t_{skew}$ 之前结束，那么接收机输出中的发生在重置信号620的结束与 $t_{skew}$ 的结束之间的转变就可能使得恢复时钟电路520为当前码元生成第二时钟脉冲，从而使得触发器530在一个码元周期中被触发两次。假定 $t_1$ 和 $t_2$ 相对于 $t_{skew}$ 而言较小，则该定时约束能够通过将延迟电路730的时间延迟 $t_{delay}$ 设置成约等于或大于 $1/2*t_{skew}$ 而被满足。在该方面， $t_{skew}$ 可包括由于信道条件导致的偏斜。延迟电路730可以用串联耦合的多个反相器或者其他类型的延迟元件来实现。

[0070] 在一个实施例中，时钟恢复电路还包括一个输入耦合到开始信号并且另一输入耦合到延迟电路730、并且输出耦合到触发器的重置输入的与(AND)门770。与门770在开始信号为1时，将延迟电路730的输出传递到触发器的重置输入，并且在开始信号为0时阻塞延迟电路730的输出去往触发器的重置输入。开始信号可以被设置成0以在时钟恢复电路520并不被在使用时禁用时钟恢复电路520以节省功率。

[0071] 图8示出了根据本公开的一实施例的延迟电路730的示例性实现。在该实施例中，延迟电路730包括串联耦合到延迟链的多个反相器810-1到810-8、以及复用器820。复用器820具有耦合到延迟链中的第四反相器810-4的输出的第一输入，以及耦合到延迟链中的最后一个反相器810-8的输出的第二输入。在选择信号(记为s)的控制下，复用器820选择性地将第四反相器810-4的输出或者最后一个反相器810-8的输出中的任一者耦合到延迟电路730的输出。这允许延迟电路730的时间延迟( $t_{delay}$ )被调节。例如，第四反相器810-4的输出可以被选择以使得 $t_{delay}$ 更短，并且最后一个反相器810-8的输出可以被选择以使得 $t_{delay}$ 更长。如以上所讨论的， $t_{delay}$ 可以被设置成约等于或者大于 $1/2*t_{skew}$ 。由此， $t_{delay}$ 可以根据 $t_{skew}$ 中的改变而被调节。为了在 $t_{delay}$ 的调解中提供更大的粒度，复用器820可以具有耦合到延迟链中的其他反相器的输出的附加的输入以允许其他反相器的输出被选择。

[0072] 在一个实施例中，复用器820可以是反相复用器820。结果，延迟电路730的输出(dout)可以相对于输入(din)被反相。在该实施例中，从延迟电路730输出的重置信号可以具有图6中所示的重置信号的相反极性，并且每个触发器745A-745C和750A-750C可以具有反相重置输入(rn)。

[0073] 图9示出了根据本公开的一实施例的延迟电路525A-525C之一的示例性实现。延迟电路525A-525C中的每一者可以使用图9中所示的延迟电路525来实现。在该示例中，延迟电路525包括用于提供以上所讨论的长达 $t_1$ 的延迟的第一部分910，以及用于提供以上所讨论的长达保持时间的延迟的第二部分920。由此，总的延迟约等于 $t_1$ 与保持时间之和。第一部分910用与时钟恢复电路520中的组件相同或类似的组件实现。这样做使得延迟电路525的第一部分910中的延迟接近匹配 $t_1$ ，其为从时钟恢复电路520在接收机输出中检测到转变的时间与时钟恢复电路520输出对应时钟沿的时间的延迟。

[0074] 延迟电路525的第一部分910包括延迟电路930、第一或门940以及第二或门950。延

迟电路930使时钟仿效于时钟恢复电路520中的触发器745A-745C和750A-750C中的一者中的Q延迟。例如，延迟电路930可包括仿效触发器的锁存器(例如，主控锁存器和从动锁存器)中的反相器的反相器。延迟电路930被解说为图9中的触发器以表达延迟电路930仿效时钟恢复电路中的触发器延迟，但是将会领会，延迟电路930严格意义上并非触发器。

[0075] 第一或门940仿效时钟恢复电路520中或门760A-760C之一中的延迟。第一或门940具有两个输入，其中一个输入被耦合到延迟电路525的信号路径，并且另一个输入被耦合到电压vssa(逻辑0)。第二或门950仿效时钟恢复电路520的或门720中的延迟。就此，第二或门950可以用串联耦合的或非门952和反相器957来实现，其中或非门952和反相器957分别对应于用以实现或门720的或非门722和反相器727。或非门952具有三个输入，其中一个输入被耦合到延迟电路525的信号路径，并且另两个输入被耦合到电压vssa(逻辑0)。

[0076] 延迟电路525的第一部分910中的组件可以被制造成接近于时钟恢复电路520中的对应组件，从而以上二者之中的组件经受大约相同的PVT差别。这允许延迟电路525的第一部分910接近匹配t1。如图9中的示例中所示，延迟电路525的第二部分920可以用串联耦合的多个反相器922-1到922-4来实现。

[0077] 图10是解说根据本公开的一实施例的用于接收数据的方法1000的流程图。方法1000可例如由图5中所示的接收机侧系统500来执行。

[0078] 在步骤1010，从多个导体接收码元序列。例如，码元序列可以由耦合到该多个导体(例如，导线A-C)的接收机(例如，接收机150A-150C)接收。

[0079] 在步骤1020，时钟信号通过检测接收到的码元序列中的转变来生成。例如，时钟信号可以由将检测到的转变转换成时钟信号的上升沿的时钟恢复电路(例如，时钟恢复电路520)生成。

[0080] 在步骤1030，接收到的码元序列被延迟。例如，接收到的码元序列可以由耦合到接收机(例如，150A-150C)的输出的延迟电路(例如，延迟电路525A-525C)延迟。

[0081] 在步骤1040，经延迟的码元序列中的一个或多个码元被使用时钟信号来捕捉，其中经延迟的码元序列中的前一码元是使用时钟信号中的基于检测到的向所接收到的码元序列中的当前码元的转变所生成的时钟脉冲来捕捉的。例如，该一个或多个码元可以由触发器(例如，触发器530)捕捉。经延迟的码元序列的延迟可以约等于或大于触发器(例如，触发器530)的保持时间和检测到的转变与时钟信号的对应沿之间的时间延迟(例如，延迟t1)之和。

[0082] 提供对本公开的先前描述是为使得本领域任何技术人员皆能够制作或使用本公开。对本公开的各种修改对本领域技术人员来说都将是显而易见的，且本文中所定义的普适原理可被应用到其他变型而不会脱离本公开的精神或范围。由此，本公开并非旨在被限定于本文中所描述的示例，而是应被授予与本文中所公开的原理和新颖特征相一致的最广范围。

图1A

图1B

图1C

图1D

图1E

图1F

图2

图3

图4

图5

图6

图7

图8

图9

1000

图10