(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-23156

(P2014-23156A)

(43) 公開日 平成26年2月3日(2014.2.3)

(51) Int.Cl.

HO4B 3/04 (2006.01)

HO4L 25/03 (2006.01)

F 1

HO 4 B 3/04

HO 4 L 25/03

HO 4 B 3/04

テーマコード(参考)

C 5KO29

C 5KO46

B

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 29 頁)

(21) 出願番号 特願2013-148220 (P2013-148220)

(22) 出願日 平成25年7月17日 (2013.7.17)

(31) 優先権主張番号 13/552,012

(32) 優先日 平成24年7月18日 (2012.7.18)

(33) 優先権主張国 米国(US)

(71) 出願人 508243639

エルエスアイ コーポレーション

アメリカ合衆国 95131 カリフォルニア、サンホセ、リッダー パーク ドライヴ 1320

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128657

弁理士 三山 勝巳

(74) 代理人 100170601

弁理士 川崎 孝

最終頁に続く

(54) 【発明の名称】 レシーバ利得適応に基づいてトランスマッタ等化係数を適応させるための方法および装置

## (57) 【要約】

【課題】 レシーバ利得適応に基づいてトランスマッタ等化係数を適応させるための方法および装置を提供する。

【解決手段】 チャネルを介してレシーバと通信するトランスマッタの等化係数は、レシーバの中の増幅器についての利得値が、増幅器の限度内にあるかどうかを決定すること、および利得値が増幅器の上限または下限を満たさない場合に、トランスマッタの等化係数に対する1つまたは複数の調整を防止することにより適応させられる。利得調整は、例えば、トランスマッタの等化係数についてのアップ要求およびダウン要求を含んでいる。1つまたは複数のイネーブル・フラグは、オプションとして、利得値が、増幅器の限度内にあるかどうかに基づいて、設定され得る。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

チャネルを介してレシーバと通信するトランスマッタの中の等化器の係数を適応させる方法であって、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定するステップと、

前記利得値が前記増幅器の前記限度を満たさないときには、前記等化器係数に対する1つまたは複数の調整を防止するステップとを備える、方法。

**【請求項 2】**

前記調整は前記等化器係数についてのアップ要求およびダウン要求を含む、請求項1に記載の方法。 10

**【請求項 3】**

前記利得値が前記増幅器の前記限度内にあるかどうかに基づいて、1つまたは複数のフラグを設定するステップをさらに備える、請求項1に記載の方法。

**【請求項 4】**

前記等化器は、送信有限インパルス応答(TX FIR)フィルタおよび可変利得増幅器のうちの1つまたは複数を備える、請求項1に記載の方法。

**【請求項 5】**

チャネルを介してレシーバと通信するトランスマッタの中の等化器の1つまたは複数の係数を適応させる装置であって、 20

メモリと、

前記メモリに結合された少なくとも1つのハードウェア・デバイスであって、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定し、そして、

前記利得値が前記増幅器の前記限度を満たさないときには、前記等化器係数に対する1つまたは複数の調整を防止する、ように動作可能である前記少なくとも1つのハードウェア・デバイスとを備える、装置。

**【請求項 6】**

前記調整は前記係数についてのアップ要求およびダウン要求を含む、請求項5に記載の装置。 30

**【請求項 7】**

前記少なくとも1つのハードウェア・デバイスは、前記利得値が前記増幅器の前記限度内にあるかどうかに基づいて、1つまたは複数のフラグを設定するようにさらに構成される、請求項5に記載の装置。

**【請求項 8】**

チャネルを介してレシーバと通信するトランスマッタの中の等化器の係数を適応させる製品であって、実行されるとときに、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定するステップと、

前記利得値が前記可変利得増幅器の前記限度を満たさないときには、前記係数に対する1つまたは複数の調整を防止するステップと、 40

を実施する1つまたは複数のプログラムを含む有形の機械読取可能記録可能媒体を備える、製品。

**【請求項 9】**

チャネルを介してレシーバと通信するトランスマッタの中の等化器の係数を適応させる集積回路であって、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定するように動作可能な利得制限回路と、

前記利得値が前記増幅器の前記限度を満たさないときには、前記係数に対する1つまたは複数の調整を防止するように動作可能な要求ゲート回路と、 50

を備える集積回路。

**【請求項 10】**

前記調整は前記係数についてのアップ要求およびダウン要求を含む、請求項 9 に記載の集積回路。

**【発明の詳細な説明】**

**【背景技術】**

**【0001】**

多数のデータ通信アプリケーションにおいては、シリアルライザおよびデシリアルライザ (serializer and de-serializer : SerDes) デバイスは、シリアル・リンクを通してパラレル・データの伝送を容易にする。パラレル・データは、レシーバに対する通信チャネルを通しての伝送の前に、トランスマッタにおけるシリアルライザによってシリアル・データに変換される。レシーバの中のデシリアルライザは、シリアル・データをパラレル・データへと変換する。レシーバに到着する信号は、通常、シンボル間干渉 (ISI : intersymbol interference)、クロストーク、エコーおよび他のノイズによって破損される。したがって、レシーバは、通常、多くの場合にいくつかの異なる等化技法を使用して、そのような歪みを補償するようにチャネルを増幅し、等化する。例えば、決定フィードバック等化 (DFE : Decision - feedback equalization) は、シンボル間干渉を取り除くために、広く使用される技法である。決定フィードバック等化器についての詳細な考察のためには、例えば、各々が参照により本明細書に組み込まれている R. Gitlin 等、Digital Communication Principles, (Plenum Press 1992 年) と、E. A. Lee および D. G. Messerschmitt, Digital Communications, (Kluwer Academic Press, 1988 年) を参照されたい。等化はまた、トランスマッタによって使用されて、伝送に先立って信号を事前に条件付ける (例えば、プリエンファシス (pre-emphasize) する) こともできる。

**【0002】**

等化には、一般に、等化パラメータを確立するためのチャネルの伝達関数の推定値が必要である。しかしながら、通信チャネルの周波数依存の信号劣化特性は、多くの場合に、時間とともに変化し、または先駆的に知られていない可能性がある。したがって、そのような環境においては、適応等化は、時間とともに等化パラメータを変化させて信号劣化を軽減するために、多くの場合に使用される。このようにして、等化は、チャネル特性、または温度や湿度などの周囲条件の変化に適応的に応答する可能性があり、かつ / またはデフォルト値から現在のチャネル特性へと適応させることができる。適応アルゴリズムは、一般的に、信号統計または信号スペクトルに従って、フィルタ係数を適応させる。例えば、最小二乗平均 (LMS : least mean square) 適応技法は、時間とともに受信された信号の観察に基づいて等化パラメータを確立するために、多くの場合に使用される。

**【0003】**

しかしながら、トランスマッタにおける等化パラメータの適応は、レシーバにおいて実行される利得の調整および / または等化に悪影響を及ぼす可能性がある (または逆も同様である)。例えば、高い減衰のチャネルの場合には、トランスマッタにおける等化器の係数が、多くの場合に、それらの上限に向かって増大され、レシーバにおける可変利得増幅器 (VGA : variable gain amplifier) が、同様にその上限に落ち着くようにさせることができ。それゆえに、VGA の出力は、送信等化器によってエンファシスされる、さらなる増大に従わることになる。結果として、データ・アイ開口部は、さらに小さくなり、レシーバにおけるジッタ耐性が、低減される。

**【先行技術文献】**

**【特許文献】**

**【0004】**

10

20

30

40

50

【特許文献 1】米国特許出願公開第 2010 / 0046598 号

【発明の概要】

【発明が解決しようとする課題】

【0005】

レシーバにおける利得適応に基づいてトランスマッタの等化係数を調整する改善された適応等化技法についての必要性が、それゆえに存在している。

【課題を解決するための手段】

【0006】

一般に、レシーバの利得適応に基づいてトランスマッタの等化係数を適応させるための方法および装置が、提供される。本発明の一実施形態によれば、チャネルを介してレシーバと通信するトランスマッタの等化係数は、レシーバの中の増幅器についての利得値が、増幅器の限度内にあるかどうかを決定すること、およびその利得値が、増幅器の限度を満たさない場合に、等化係数に対する 1 つまたは複数の調整を防止することにより、適応させられる。

【0007】

本発明の一実施形態においては、利得調整は、トランスマッタの等化係数についてのアップ要求とダウン要求とを含んでいる。例えば、上方調整要求は、利得値が、増幅器の下限を満たさない場合に、防止され得、下方調整要求は、利得値が、増幅器の上限を満たさない場合に、防止され得る。さらに、1 つまたは複数のフラグは、利得値が、増幅器の限度内にあるかどうかに基づいて、オプションとして設定され得る。トランスマッタの等化係数の調整についてのトランスマッタへの伝送は、フラグに基づいてオプションとして、イネーブルにされ、またはディスエーブルにされる。

【0008】

本発明の実施形態についてのより完全な理解は、以下の詳細な説明と、図面とを参照することにより得られるであろう。

【図面の簡単な説明】

【0009】

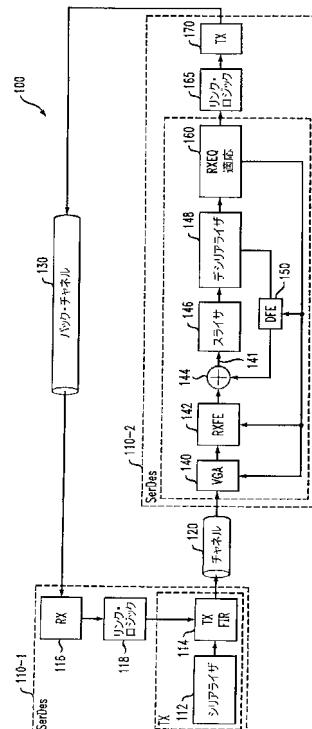

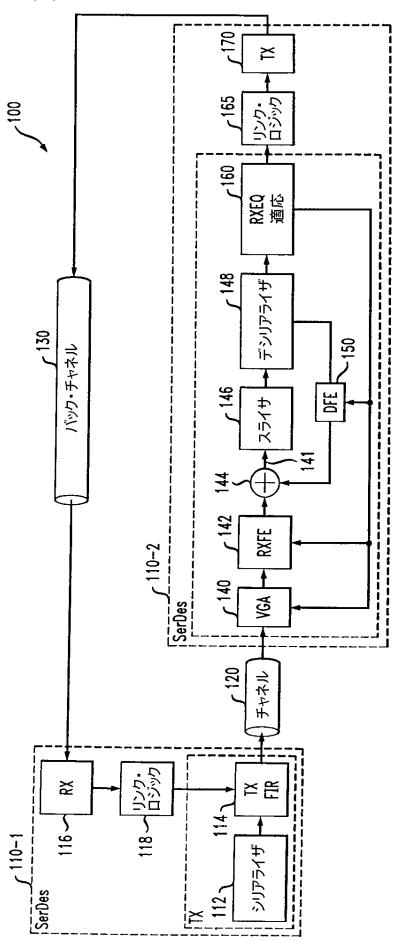

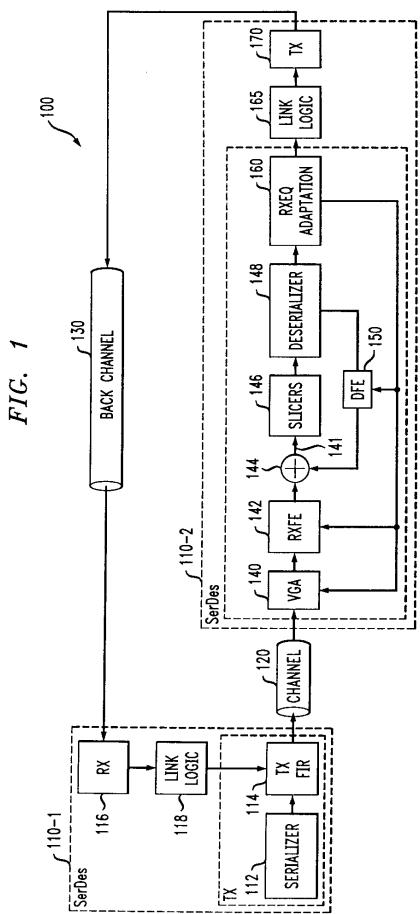

【図 1】本発明の実施形態を使用することができる通信システムのブロック図である。

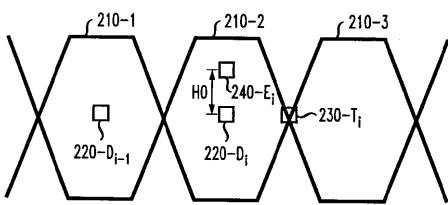

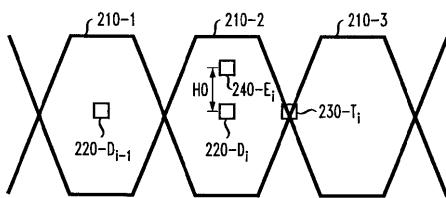

【図 2】図 1 のスライサによる、一連のデータ・アイについてのサンプリングを示す図である。

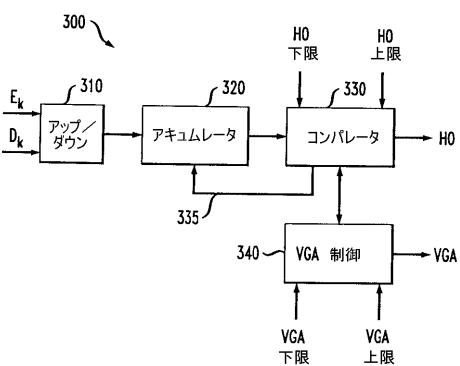

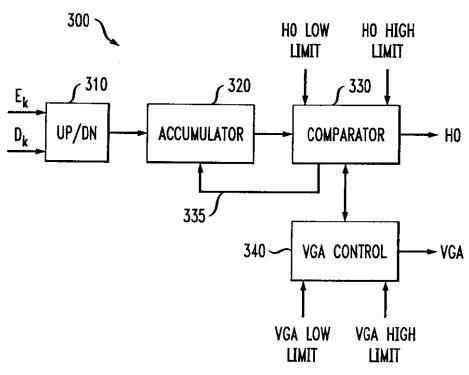

【図 3】図 2 のエラー・スライサを適応させる V G A / H 0 適応ブロックを示すブロック図である。

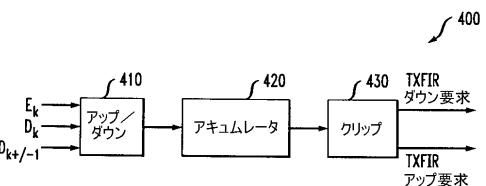

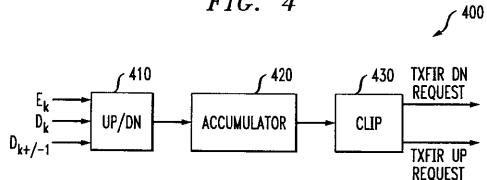

【図 4】T X F I R フィルタ係数適応ブロックを示すブロック図である。

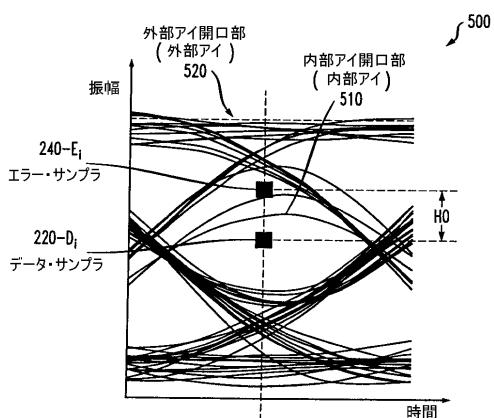

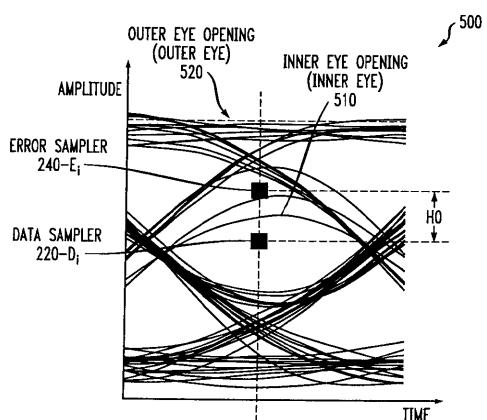

【図 5】例示のデータ・スライサおよびエラー・スライサを用いてオーバーレイされるデータ・アイ図である。

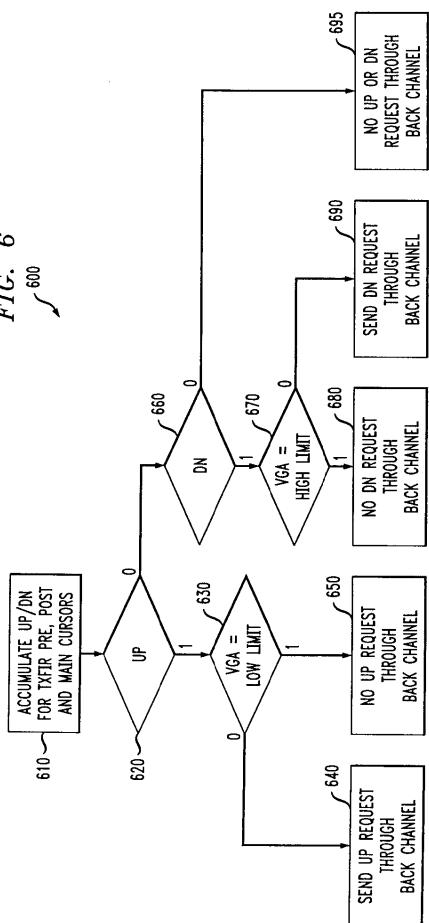

【図 6】本発明の一実施形態を組み込んでいる制限された T X F I R 適応プロセスを説明するフロー・チャートである。

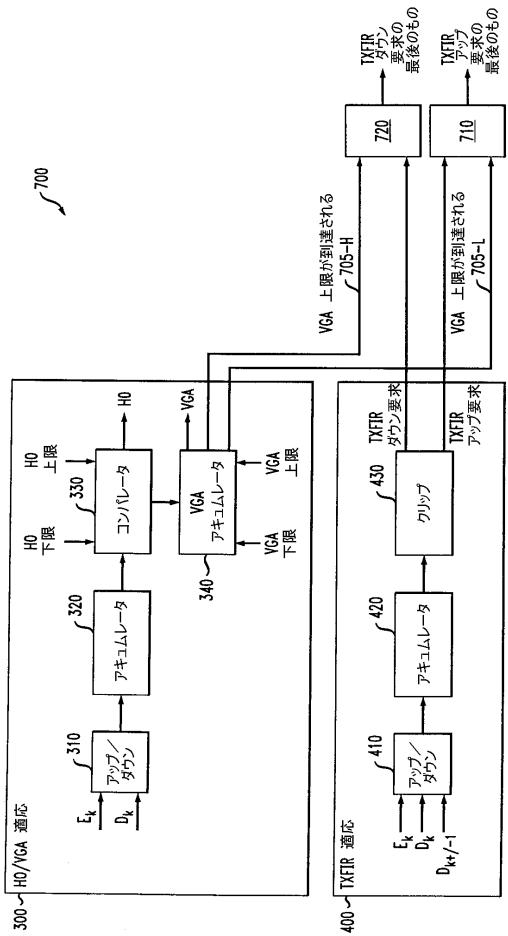

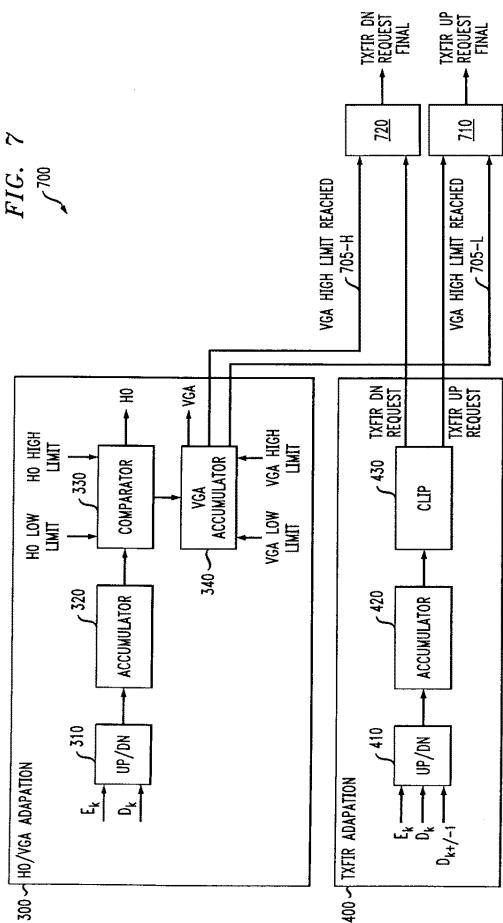

【図 7】本発明の一実施形態を組み込んでいる制限された T X F I R 適応システムのブロック図である。

【発明を実施するための形態】

【0010】

本発明の実施形態は、レシーバにおける V G A 利得適応に基づいてトランスマッタの等化係数を調整する適応等化技法においては明らかである可能性がある。上記で示されるように、トランスマッタにおける（例えば、T X F I R フィルタについての）等化係数が、それらの負の値において増大されるときに、レシーバの中の V G A は、その上限に落ち着く可能性がある。それゆえに、レシーバの中の V G A の出力は、送信等化器によるエンファシスのさらなる増大に従うこととはなくなる。結果として、データ・アイ開口部は、さらに小さくなり、またジッタ耐性は、悪化させられることになる。本発明の一実施形態によれば、トランスマッタの等化係数の適応は、等化器が、着信する受信信号を必要とされるレベルまで増幅する V G A の能力を超えることができないように制限される。一実施形態

10

20

30

40

50

においては、VGA利得適応は、監視され、またVGAが上限または下限に到達するときに、送信等化器の係数のさらなる調整は防止される。

#### 【0011】

図1は、本発明の実施形態を使用することができる通信システム100のブロック図である。図1に示されるように、通信システム100は、チャネル120を介して通信する2つのSerDesデバイス110-1および110-2を備える。図1の構成においては、SerDesデバイス110-1は、送信モードで動作しており、またSerDesデバイス110-2は、受信モードで動作している。さらに、以下でさらに論じられるように、受信SerDesデバイス110-2における適応アルゴリズムは、送信SerDesデバイス110-1についての1つまたは複数の適応等化パラメータを決定し、これらの適応等化パラメータは、バック・チャネル130を使用して受信SerDesデバイス110-2から送信SerDesデバイス110-1へと通信される。

10

#### 【0012】

上記で示されるように、パラレル・データは、受信SerDesデバイス110-2に対する通信チャネル120を通しての伝送の前に、送信SerDesデバイス110-1の中のシリアルライザ112によってシリアル・データへと変換され、この受信SerDesデバイス110-2においては、それは、デシリアルライザ148によってシリアル・データからパラレル・データへと変換される。シリアル化された送信データは、送信有限インパルス応答(TX FIR : transmit finite impulse response)フィルタ114によって事前に条件付けされて(例えば、プリエンファシスされて)、知られているやり方でチャネル120によって引き起こされる障害について補償される。TX FIRフィルタ114についての係数は、式(1)および図4に関連して以下でさらに論じられるように、受信SerDesデバイス110-2の中のレシーバ等化(RXEQ : receiver equalization)適応ブロック160の内部の適応アルゴリズムによって決定される。

20

#### 【0013】

図1に示されるように、TX FIRフィルタ114のフィルタがかけられたシリアル出力は、チャネル120に対して適用され、また受信SerDesデバイス110-2によって受信される。受信信号は、可変利得増幅器(VGA)140によって最初に増幅され、次いで、典型的には、調整可能な高域フィルタを使用してチャネル障害をさらに軽減するために、レシーバ・フロント・エンド(RXFE : receiver front end)142の中で強化される。RXFE142の出力は、加算器144に対して適用される。さらに、決定フィードバック等化器(DFE : Decision-feedback equalizer)150からのDFE補正は、フィードバックするようにして加算器144に適用されて、DFE補正された信号141を生成する。DFE補正は、チャネル120において起こるシンボル間干渉(ISI : Inter Symbol Interference)について補正する。次いで、DFE補正された信号141は、スライサ146によってサンプリングされる。図2に関連して以下でさらに論じられるように、スライサ146は、典型的には、シリアル・データと、ビット・クロックとを回復するために、各シリアル・ビット持続時間の単位間隔(UI : Unit Interval)の間に1回または複数回、シリアル・データをサンプリングする。スライサ146からのサンプリングされたシリアル・データは、次いで、デシリアルライザ148によって非シリアル化される。デシリアルライザ148からの回復されたデータは、DFE150によりフィードバック・ループの中で処理されて、DFE補正を生成する。ビット・クロックの回復と、他のタイミング課題とは、当業者にはよく知られている。

30

#### 【0014】

デシリアルライザ148からの回復されたデータはまた、受信SerDesデバイス110-2の中のRXEQ適応ブロック160の内部の1つまたは複数の適応アルゴリズムによって処理されて、VGA140と、RXFE142と、DFE150についての等化パラメータを決定する。概して、適応は、RXEQ適応ブロック160を通して、回復さ

40

れたデータと、エラー情報を使用して実行される。RXEQ適応ブロック160の内部の適応アルゴリズムは、例えば、よく知られたLMSアルゴリズム、またはゼロ・フォーシング(ZF:Zero Forcing)アルゴリズムとして実装されることもある。例示の適応アルゴリズムは、「例示の適応アルゴリズム(Exemplary Adaptation Algorithms)」と題名が付けられた節において以下でさらに論じられる。例えば、VGA140は、RXEQ適応ブロック160から利得制御信号を受信する。RXFE142と、DFE150とは、RXEQ適応ブロック160からフィルタ係数を受信する。

#### 【0015】

さらに、上記で示されるように、送信SerDesデバイス110-1の中のTXFIRフィルタ114についてのフィルタ係数の調整は、またRXEQ適応ブロック160によって決定される。例えば、RXEQ適応ブロック160は、LMSアルゴリズムを使用して、異なるTXFIR係数についてのTXFIRのアップ調整要求またはDN(ダウン)調整要求を生成することができる。RXEQ適応ブロック160によって生成されるTXFIRのアップ調整要求またはダウン調整要求は、TXFIRフィルタ114の中のメイン・カーソル、プレ・カーソル、ポスト・カーソルについてのエンファシスの量を変更し、このようにしてリモートの送信SerDesデバイス110-1を特定のチャネル120の状態に対してトレーニングする。プレ・カーソルTXFIR係数と、ポスト・カーソルTXFIR係数とは、通常、プリエンファシス(pre-emphasis)を生成する負の値である。したがって、ダウン調整要求は、プリエンファシスの量における増大を示し、またアップ調整要求は、プリエンファシスの量における低減を示す。

10

20

30

#### 【0016】

RXEQ適応ブロック160は、決定されたTXFIR係数の調整をリンク・ロジック165に対して適用し、これは、次には、係数調整要求を受信SerDesデバイス110-2の送信(TX)部分170に対して適用する。受信SerDesデバイス110-2のTX部分170は、係数についてのアップ要求またはDN(ダウン)要求をバック・チャネル130を介してSerDesデバイス110-1の受信(RX)部分116に対して送信する。リンク・ロジック118は、係数についての受信されたフィルタのアップ要求またはダウン要求をTXFIRフィルタ114に対して適用し、このようにしてプリエンファシスの量またはメイン・カーソル値を変更する。

#### 【0017】

本発明は、2つのSerDesデバイス110-1および110-2を有する通信システム100の文脈で説明されるが、本発明は、トランスマッタからレシーバへのシリアル通信を有する任意の通信システムに対して適用することもでき、またここでは、等化アップデートは、当業者には明らかになるように、レシーバからトランスマッタへと提供されることもある。

#### 【0018】

図2は、スライサ146による、DFE補正された信号141に対応する一連のデータ・アイ210-1ないし210-3についてのサンプリングを示すものである。図1のスライサ146は、2つのデータ・スライサ220-D<sub>i</sub>および220-D<sub>i+1</sub>と、遷移スライサ230-T<sub>i</sub>と、エラー・スライサ240-E<sub>i</sub>とを備える。CDRが、1つの実施形態において着信するデータに適切にロックされるときに、遷移スライサ230-T<sub>i</sub>は、レベル「0」に交差するデータ遷移の統計的中央値に揃えられ、データ・スライサ220-D<sub>i</sub>は、ゼロの垂直(電圧)オフセットを有するデータ・アイの統計的中心値に揃えられ、またエラー・スライサ240-E<sub>i</sub>は、データ・スライサ220-D<sub>i</sub>と同じタイミング・アラインメントを有するが、H0の垂直オフセットを有しており、典型的には、図5に関連して以下でさらに論じられるように、データ・レベルの統計的中央値中のエラー・スライサ240-E<sub>i</sub>をアイの中心(内側データ・アイと、外側データ・アイとの間の統計的中央値)に位置づけている。H0垂直オフセットは、VGA適応の一部分として達成され、またエラー・スライサ240-E<sub>i</sub>は、知られているやり方で、すべて

40

50

の RXEQ パラメータ、ならびにリモートの TXFIR 係数についての LMS 適応アルゴリズムにおいて使用される。データ・アイ当たりに 1 つまたは複数のエラー・スライサ 240-E<sub>i</sub> が存在していることもある。

## 【0019】

例示の適応アルゴリズム

DFE 係数、c<sub>n</sub>、についての LMS 適応アルゴリズムは、データ・アイ当たりに 1 つのエラー・スライサについての例示の場合において、以下の式によって記述され得る。

## 【0020】

## 【数 1】

10

$$Cn = \overline{(D_k \wedge Esign_k) ? \sum_0^{\infty} (D_{k-n} \wedge E_k)} : 0 \quad [1]$$

## 【0021】

式(1)において、データ・スライサ 220-D<sub>k</sub> からの現在のデータ・サンプル D<sub>k</sub> が、エラー・オフセット Esign<sub>k</sub> と同じ符号(sign)を有する場合、そのときには排他的な NOR (「XNOR」) オペレーションは、係数インデックス n によるデータ・サンプル・オフセット D<sub>k-n</sub> と、エラー・スライサ 240-E<sub>k</sub> からの現在のエラー・サンプル、E<sub>k</sub> とに対して適用され、またアップ調整またはダウン調整として係数値の中に蓄積される。

20

## 【0022】

リモートの TXFIR フィルタ 114 についての係数についての適応アルゴリズムは、プレ・カーソル適応およびポスト・カーソル適応についての対応する +1 または -1 のインデックス・オフセット n を有する式(1)によって説明される可能性もある。

## 【0023】

図 2 の VGA140 についての利得調整と、エラー・ラッチ、240-E<sub>i</sub>、についてのオフセット H0 についての適応アルゴリズムは、類似している。H0 適応と、VGA 適応との相互依存については、図 3 に関連して以下でさらに論じられる。

## 【0024】

概して、図 2 のエラー・ラッチ、240-E<sub>i</sub>、についてのオフセット H0 についての適応は、

30

## 【0025】

## 【数 2】

$$H0 = \overline{(D_k \wedge Esign_k) ? \sum_0^{\infty} (D_k \wedge E_k)} : 0 \quad [2]$$

のように記述され得る。

## 【0026】

式(2)において、データ・スライサ 220-D<sub>k</sub> からの現在のデータ・サンプル D<sub>k</sub> が、エラー・オフセット Esign<sub>k</sub> と同じ符号を有する場合、そのときには排他的な NOR 「XNOR」 オペレーションは、現在のデータ・サンプル D<sub>k</sub> と、エラー・スライサ 240-E<sub>k</sub> からの現在のエラー・サンプル、E<sub>k</sub>、とに対して適用され、またアップ調整またはダウン調整としてエラー・スライサ・オフセット値の中に蓄積される。

40

## 【0027】

等化適応技法のより詳細な考察のためには、例えば、参照により本明細書に組み込まれている「Adaptation Of A Linear Equalizer Using A Virtual Decision Feedback Equalizer (VDFE)」という名称の米国特許出願公開第 2010/0046598 号を参照されたい。

50

## 【0028】

図3は、式(2)に基づいたVGA/H0適応ブロック300を示すブロック図である。図3に示されるように、データ・スライサ220-D<sub>k</sub>からの現在のデータ・サンプルD<sub>k</sub>と、エラー・スライサ240-E<sub>k</sub>からの現在のエラー・サンプル、E<sub>k</sub>、とは、式(2)によって記述されるアップ/ダウン決定ブロック310に対して適用され、次いで、アキュムレータ320は、H0の現在のレベルに、それぞれ加算することにより、または現在のレベルから減算することにより、それらの値を蓄積する。コンパレータ330は、典型的には、全範囲のH0制御よりも狭いH0についての上限および下限を受信する。H0の限度の間の範囲は、VGA制御の1つのステップに関係づけられ、またこのステップよりも大きくすべきである。コンパレータ330が、H0制御が上限または下限のH0限度に到達していることを決定するときはいつでも、H0アキュムレータは、フィードバック経路335を使用して、(上限と下限との間の)その再スタート・レベルにリセットされ、またVGA制御340は、1だけ増分され、または減分される。例えば、H0適応がそのアキュムレータ320が、下限に到達するようにさせる場合、そのときにはチャネル120からの信号は、十分に強くはなく、また信号は、(VGA140に対して加えられる利得調整信号を増大させることにより)より高い増幅を得るべきである。この場合には、VGA利得調整信号(制御)は、1だけ増分される。

10

## 【0029】

図3に示されるアルゴリズムは、H0が、対応する下限と上限との間の安定したレベルに落ち着くまで、またはVGA制御340が、所定の下限または上限(すべての限度は、典型的にはプログラマブルである)に到達するまで、実行される。後者の場合には、VGA制御340は、対応して下限または上限において停止し、またH0は、使用可能な範囲内のどこでもそのプリセットされた限度を超えて蓄積することが許可される。この場合には、VGA増幅は、十分でない可能性があり、また垂直アイ開口部は、悪影響を受ける可能性があり、劣ったジッタ耐性をもたらす。逆に、VGA制御340が下限に到達する場合、これは、信号が十分に減衰され得ないことを意味することもあり、またRXFE142を通して、典型的には増幅の欠如ほど致命的ではない飽和を受ける可能性があるが、望ましくない非線形効果を引き起こしてしまう可能性がある。

20

## 【0030】

図4は、式(1)に基づいてリモートのTXFIRフィルタ114についてのTXFIRフィルタ係数適応ブロック400を示すブロック図である。図4に示されるように、データ・スライサ220-D<sub>k</sub>からの現在のデータ・サンプルD<sub>k</sub>、およびエラー・スライサ240-E<sub>k</sub>からの現在のエラー・サンプル、E<sub>k</sub>、ならびに対応するデータ・スライサ220からの先行のデータ・サンプル、または後続のデータ・サンプルD<sub>k+/-1</sub>は、式(1)によって記述されるアップ/ダウン決定ブロック410に適用され、次いで、アキュムレータ420は、それぞれ、現在のアキュムレータ420の値に、加算することにより、または現在のアキュムレータ420の値から減算することにより、それらの値を蓄積する。アキュムレータ420が、上限または下限に到達する場合、クリップ・ブロック430は、値をラッチし、また値は、リモートのSerdess110-1に対してバック・チャネル130を通して送信されるべきアップ要求またはダウン要求としてリンク・ロジック165へと伝えられる。このようにして、TXFIR係数値は、通信チャネル120のパラメータに合わせて調整される。

30

## 【0031】

図5は、データ・スライサ220-D<sub>i</sub>と、エラー・スライサ240-E<sub>i</sub>とを用いてオーバーレイされたデータ・アイ図500を示すものである。データ・アイは、内部アイ510とも称される内部アイ開口部510を有しており、この内部アイ開口部は、トレースが通過していない最小の開口部である。さらに、データ・アイは、外部アイ520とも称される外部アイ開口部520を有しており、この外部アイ開口部は、データ・アイの最大のものである。多数の実用的なアプリケーションにおいては、データ・スライサ220-D<sub>i</sub>は、ゼロの垂直(電圧)オフセットを伴ってデータ・アイの統計的中心値に揃えら

40

50

れ、またエラー・スライサ $240 - E_i$ は、データ・スライサ $220 - D_i$ と同じタイミング・アラインメントを有するが、ただし $H_0$ の垂直オフセットを伴っており、典型的には、アイの中心（内部アイ $510$ と、外部アイ $520$ との間の統計的中央値）におけるデータ・レベルの統計的中央の中にエラー・スライサ $240 - E_i$ を位置づけている。

#### 【0032】

##### 内部アイ $510$ と外部アイ $520$ との上の等化の影響

概して、等化は、データ・アイのサイズを開く（すなわち、データ・マージンを増大させる）ことを目指している。それにもかかわらず、等化は、外部アイ $520$ が低減する量よりも少ない量だけ内部アイ $510$ を増大させる（例えば、外部アイ $520$ は、内部アイ $510$ が開くよりももっと閉じる）ことができることが分かっている。これは、内部アイ $510$ と、外部アイ $520$ との間の統計的中央値を低減するようにさせることになり、またエラー・ラッチ $240 - E_i$ についてのオフセット・レベル $H_0$ は、より低い値に再適応されることになる。 $H_0$ レベルへの低減は、次には、図3に関連して上記で考察されるように、VGA利得調整における増大を引き起こす可能性がある。

10

#### 【0033】

外部アイ $520$ が閉じるよりも少ない程度まで内部アイ $510$ を開くようにさせるいくつかのファクタが存在している。例えば、TXFIRフィルタ $114$ は、典型的には、限られた帯域幅を有しており、また低域通過フィルタとしての役割を果たす。したがって、シリアル・データの中のより低い周波数成分は、プリエンファシス・レベルと同じ劣化を受けないようになる。

20

#### 【0034】

上記で示されるように、送信SerDes $110 - 1$ における等化パラメータの適応は、受信SerDes $110 - 2$ において実行される利得調整および／または等化に悪影響を及ぼす可能性がある（または逆もまた同様である）。例えば、高減衰チャネルの場合には、送信SerDes $110 - 1$ におけるTXFIR $114$ についての係数は、多くの場合に、それらの負の上限に向かって増大され、受信SerDes $110 - 2$ におけるVGA $140$ に、同様にその上限に落ち着くようにさせることができている。したがって、VGA $140$ の出力は、TXFIRフィルタ $114$ によるエンファシスのさらなる増大に従うことはない。結果として、データ・アイ開口部は、より小さくなり、またレシーバにおけるジッタ耐性は、低減される。

30

#### 【0035】

図6は、本発明の限られたTXFIR適応プロセス $600$ の一実施形態を説明するフロー・チャートである。限られたTXFIR適応プロセス $600$ は、例えば、RXEQ適応ブロック $160$ によって実装されることもある。概して、限られたTXFIR適応プロセス $600$ は、TXFIR $114$ が、VGA $140$ の能力を超えて、着信RX信号を必要とするレベルまで増幅することのないようにする。

#### 【0036】

図6に示されるように、限られたTXFIR適応プロセス $600$ は、最初に、ステップ $610$ 中にTXFIRフィルタ $114$ のプレ・カーソルと、ポスト・カーソルと、メイン・カーソルとについてのアップ／ダウン調整要求を蓄積する。テストが、ステップ $620$ 中に実行されて、要求が、アップ要求（プリエンファシスにおける低減は、内部アイ $510$ における低減と、外部アイ $520$ における増大とを引き起こす）であるかどうかを決定する。ステップ $620$ 中に、要求がアップ要求（例えば、01という2進値）であることが決定される場合、そのときにはさらなるテストが、ステップ $630$ 中に実行されて、VGA $140$ が、既にその下限にあるかどうかを決定する。ステップ $630$ 中に、VGA $140$ が、既にその下限にあることが決定される場合、そのときにはアップ要求は、ステップ $650$ において抑制され、またバック・チャネル $140$ を介して送信されない。しかしながら、ステップ $630$ 中に、VGA $140$ が、その下限にないことが決定される場合、そのときにはアップ要求は、ステップ $640$ 中にバック・チャネル $140$ を介して送信されることが許可される。

40

50

## 【0037】

しかしながら、ステップ620中に、要求が、アップ要求ではないことが決定された場合、そのときにはさらなるテストが、ステップ660中に実行されて、要求が、ダウン要求（例えば、11の2進値または-1の2の補数）であるかどうかを決定し、次いでさらなるテストが、ステップ670中に実行されて、VGA140が、既にその上限にあるかどうかを決定する。ステップ670中に、VGA140が、既にその上限にあることが決定される場合、そのときにはダウン要求（プリエンファシスにおける増大）は、ステップ680において抑制され、またバック・チャネル140を介して送信されない。しかしながら、ステップ670中に、VGA140が、その上限にないことが決定される場合、そのときにはダウン要求は、ステップ690中にバック・チャネル140を介して送信されることが許可される。

10

## 【0038】

最終的には、ステップ620中に、要求が、アップ要求ではないことが決定され、またステップ660中に、要求が、ダウン要求ではないことが決定された場合、そのときには要求は、ステップ695中にバック・チャネル140を通して送信されない。

## 【0039】

同じアルゴリズムが、メイン・カーソルと、プレ・カーソルと、ポスト・カーソルについて独立して実行されることに留意されたい。

## 【0040】

図7は、本発明の限られたTXFIR適応システム700の一実施形態のブロック図である。図7に示されるように、限られたTXFIR適応システム700は、図3のVGA/H0適応ブロック300と、図4のTXFIR適応ブロック400とを備える。図3のVGA/H0適応ブロック300は、それぞれVGAの上限と、下限とが、いつ到達されているかを示す2つのフラグ705-Hと705-Lとを生成するように修正されている。

20

## 【0041】

さらに、限られたTXFIR適応システム700は、それぞれアップ／ダウン要求をゲートする要求ゲート・ブロック(request gating blocks)710、720を含んでいる。図7に示されるように、要求ゲート・ブロック710は、TXFIR適応ブロック400からのアップ要求、ならびにVGA140がその下限に到達しているかどうかを示すVGAフラグ705-Lを受信する。VGA下限フラグ705-Lは、要求ゲート・ブロック710についてのディスエーブル信号としての機能を果たす。概して、要求ゲート・ブロック710により、アップ要求は、VGA140が下限の上にある限り、バック・チャネル140へと通過することができるようになる。

30

## 【0042】

同様に、要求ゲート・ブロック720は、TXFIR適応ブロック400からのダウン要求、ならびにVGA140が、その上限に到達しているかどうかを示すVGAフラグ705-Hを受信する。VGA上限フラグ705-Hは、要求ゲート・ブロック720についてのディスエーブル信号としての機能を果たす。概して、要求ゲート・ブロック720により、ダウン要求は、VGA140が、下限の下にある限り、バック・チャネル140へと通過することができるようになる。

40

## 【0043】

他の利点のうちでも、開示された例示の改善された適応等化技法は、VGA利得適応に基づいてTXFIR係数を調整し、またVGAの限度を超えてTXFIR係数を確立しない。

## 【0044】

本発明の技法のうちの少なくとも一部分は、1つまたは複数のICの形で実装されることがある。ICを形成する際に、ダイは、典型的には、半導体ウェーハの表面の上で反復されたパターンの形で製造される。ダイの各々は、本明細書において説明されるストリップライン・デバイスを含んでおり、また他の構造または回路を含むことができる。個別の

50

ダイは、ウェーハから切り出され、またはダイシングされ、次いで集積回路としてパッケージングされる。当業者なら、どのようにしてウェーハをダイシングし、またダイをパッケージングして、集積回路を製造するかを知っているであろう。そのようにして製造された集積回路は、本発明の一部分と考えられる。

【0045】

本発明によるICは、多数のアプリケーション・システムおよび／または電子システムの形で使用される可能性がある。本発明を実装するための適切なシステムは、それだけには限定されないが、通信デバイスと、ケーブル・テレビジョン信号および他の高速信号を配信するためのデバイスとを含むことができる。そのような集積回路を組み込んでいるシステムは、本発明の一部分と考えられる。本明細書において提供される本発明の教示を与えると、当業者なら、本発明の技法の他の実装形態とアプリケーションとを企図することができるであろう。10

【0046】

方法を利用して、本発明の集積回路の実施形態を形成することができる。集積回路設計は、グラフィカル・コンピュータ・プログラミング言語の形で作り出されることもあり、またコンピュータ・ストレージ媒体（ディスク、テープ、物理的ハード・ドライブ、ストレージ・アクセス・ネットワークなどにおける仮想ハード・ドライブなど）に記憶されることもある。記憶された設計は、フォトリソグラフィー・マスクの製造のための適切なフォーマット（例えば、グラフィック設計システムIII（GDSII：Graphic Design System III））へと変換されることもあり、このフォトリソグラフィー・マスクは、典型的には、ウェーハに形成される集積回路設計の複数のコピーを含んでいる。フォトリソグラフィー・マスクを利用して、エッチングされ、または他の方法で処理されるべきウェーハ（および／またはその上のレイヤ）のエリアを定める。20

【0047】

結果として得られる集積回路は、ペア・ダイとして、またはパッケージングされた形態で、生のウェーハの形態で（すなわち、複数のパッケージングされていない集積回路を有する単一のウェーハとして）製造業者によって流通させられることもある。後者の場合には、集積回路は、単一の集積回路パッケージ（例えば、マザーボードまたは他のより高レベルのキャリアに取り付けられるリードを有するプラスチック・キャリア）の形で、あるいは複数の集積回路のパッケージ（例えば、表面相互接続または埋込み相互接続のいずれかまたは両方を有するセラミック・キャリア）の形でマウントされる。いずれの場合にも、集積回路は、中間製品（例えば、マザーボード）または最終製品のいずれかの一部分として他のチップ、ディスクリート回路要素、および／または他の信号処理デバイスと一体化される可能性がある。最終製品は、集積回路を含む任意の製品とすることができます。30

【0048】

本明細書において示され、また説明される実施形態および変形形態は、本発明の原理についての単に例示的なものにすぎないこと、また様々な修正形態は、本発明の範囲および趣旨を逸脱することなく当業者によって実装され得ることを理解すべきである。

【図1】

【 図 5 】

【図2】

【 図 3 】

【 図 4 】

【 四 6 】

TX FIFOのトレ・カーネル、

ボストンカーネルにおいて

メイン/ターンを監視する

アルゴリズム

610 → アップ

620 → ダウン

630 → VGA = 下眼

640 → VGA = ダウン

650 → VGA = 上眼

660 → ダウン

670 → VGA = 上眼

680 → VGA = 下眼

690 → アップ

610 → パック・チャネルを

通じて(アップ)要求を

送信する

620 → パック・チャネルを

通じて(ダウン)要求を

送信する

630 → パック・チャネルを

通じて(ダウン)要求を

送信する

640 → パック・チャネルを

通じて(アップ)要求を

送信する

650 → パック・チャネルを

通じて(アップ)要求を

送信する

660 → パック・チャネルを

通じて(ダウン)要求を

送信する

670 → パック・チャネルを

通じて(アップ)要求を

送信する

680 → パック・チャネルを

通じて(ダウン)要求を

送信する

690 → パック・チャネルを

通じて(アップ)要求を

送信する

【図 7】

---

フロントページの続き

(72)発明者 ヴラディミア シンダロヴスキー

アメリカ合衆国 18944 ペンシルヴァニア, パーカシー, ハイランド ドライヴ 602

(72)発明者 モハメッド エス. モビン

アメリカ合衆国 18069 ペンシルヴァニア, オレフィールド, レベッカ レーン 827

(72)発明者 レーン エー. スミス

アメリカ合衆国 18040 ペンシルヴァニア, イーストン, シュイラー ドライヴ 905

Fターム(参考) 5K029 AA03 DD22 DD28 DD29 GG05 HH03 HH05

5K046 BB05 DD13 EE10 EE46 EE47 EE59 EF55

## 【外國語明細書】

## Title of the Invention

**METHODS AND APPARATUS FOR ADAPTING TRANSMITTER EQUALIZATION COEFFICIENTS BASED ON RECEIVER GAIN ADAPTATION****Background**

In many data communication applications, serializer and de-serializer (SerDes) devices facilitate the transmission of parallel data across a serial link. Parallel data is converted by the serializer at the transmitter to serial data before transmission through a communications channel to the receiver. A de-serializer in the receiver converts the serial data to parallel data. Signals arriving at the receiver are typically corrupted by intersymbol interference (ISI), crosstalk, echo and other noise. Thus, receivers typically amplify and equalize the channel to compensate for such distortions, often using a number of different equalization techniques. Decision-feedback equalization (DFE), for example, is a widely-used technique for removing intersymbol interference. For a detailed discussion of decision feedback equalizers, see, for example, R. Gitlin et al., *Digital Communication Principles*, (Plenum Press 1992) and E. A. Lee and D. G. Messerschmitt, *Digital Communications*, (Kluwer Academic Press, 1988), each incorporated by reference herein. Equalization may also be employed by the transmitter to pre-condition (e.g., pre-emphasize) the signal prior to transmission.

Equalization generally requires an estimate of the transfer function of the channel to establish the equalization parameters. The frequency-dependent signal degradation characteristics of the communications channel, however, often vary over time or may be not known a priori. Thus, in such environments, adaptive equalization is often employed to vary the equalization parameters over time to mitigate the signal degradation. In this manner, the equalization can adaptively respond to changes in channel characteristics or ambient conditions, such as temperature and humidity, and/or adapt from default values to the current channel characteristics. Adaptation algorithms typically adapt the filter coefficients in accordance with the signal statistics or the signal spectrum. For example, least mean square (LMS) adaptation techniques are often employed to establish the equalization parameters based on observations of the received signal over time.

Adaptation of the equalization parameters in the transmitter, however, may adversely impact the gain adjustments and/or equalization performed in the receiver (or vice versa). For example, in the case of high attenuation channels, it has been found that the equalizer coefficients in the transmitter are often increased towards their upper limits, causing

the variable gain amplifier (VGA) in the receiver to likewise settle to its upper limits. Thus, the output of the VGA will not follow further increases in emphasis by the transmit equalizer. As a result, the data eye opening will be smaller and jitter tolerance in the receiver is reduced.

A need therefore exists for improved adaptive equalization techniques that adjust the transmitter equalization coefficients based on the gain adaptation in the receiver.

### Summary

Generally, methods and apparatus are provided for adapting transmitter equalization coefficients based on receiver gain adaptation. According to one embodiment of the invention, equalization coefficients of a transmitter that communicates over a channel with a receiver are adapted by determining if a gain value for an amplifier in the receiver is within a limit of the amplifier; and preventing one or more adjustments to the equalization coefficients if the gain value does not satisfy the limits of the amplifier.

In one embodiment of the invention, the gain adjustments comprise up and down requests for the transmitter equalization coefficients. For example, an upward adjustment request can be prevented if the gain value does not satisfy a lower limit of the amplifier and a downward adjustment request can be prevented if the gain value does not satisfy an upper limit of the amplifier. In addition, one or more flags can optionally be set based on whether the gain value is within the limit of the amplifier. The transmission of the transmitter equalization coefficient adjustments to the transmitter can optionally be enabled or disabled based on the flags.

A more complete understanding of embodiments of the present invention will be obtained by reference to the following detailed description and drawings.

### Brief Description of the Drawings

FIG. 1 is a block diagram of a communication system in which embodiments of the invention may be employed;

FIG. 2 illustrates a sampling of a series of data eyes by the slicers of FIG. 1;

FIG. 3 is a block diagram illustrating a VGA/H0 adaptation block to adapt the error slicers of FIG. 2;

FIG. 4 is a block diagram illustrating a TXFIR filter coefficient adaptation block;

FIG. 5 illustrates a data eye diagram overlaid with exemplary data and error slicers;

FIG. 6 is a flow chart describing a limited TXFIR adaptation process that incorporates an embodiment of the present invention; and

FIG. 7 is a block diagram of a limited TXFIR adaptation system that incorporates an embodiment of the present invention.

### Detailed Description

Embodiments of the present invention can be manifest in adaptive equalization techniques that adjust the transmitter equalization coefficients based on the VGA gain adaptation in the receiver. As indicated above, when the equalization coefficients in the transmitter (e.g., for a TXFIR filter) are increased in their negative value, the VGA in the receiver may settle to its upper limits. Thus, the output of the VGA in the receiver will not follow further increases in emphasis by the transmit equalizer. As a result, the data eye opening will be smaller and the jitter tolerance will be impaired. According to one embodiment of the invention, the adaptation of the transmitter equalization coefficients is limited such that the equalizer cannot go beyond the abilities of the VGA to amplify the incoming received signal to the required level. In one embodiment the VGA gain adaptation is monitored and when the VGA reaches an upper or lower limit, further adjustments of the transmit equalizer coefficients are prevented.

FIG. 1 is a block diagram of a communication system 100 in which embodiments of the invention may be employed. As shown in FIG. 1, the communication system 100 comprises two SerDes devices 110-1 and 110-2 that communicate over a channel 120. In the configuration of FIG. 1, the SerDes device 110-1 is operating in a transmit mode and the SerDes device 110-2 is operating in a receive mode. In addition, as discussed further below, adaptation algorithms in the receive SerDes device 110-2 determine one or more adaptive equalization parameters for the transmit SerDes device 110-1, which are communicated from the receive SerDes device 110-2 to the transmit SerDes device 110-1 using a back channel 130.

As previously indicated, parallel data is converted by a serializer 112 in the transmit SerDes device 110-1 to serial data before transmission through the communications channel 120 to the receive SerDes device 110-2 where it is converted by a de-serializer 148

from serial data to parallel data. The serialized transmit data is preconditioned (e.g., pre-emphasized) by a transmit finite impulse response (TXFIR) filter 114 to compensate for impairments caused by the channel 120, in a known manner. The coefficients for the TXFIR filter 114 are determined by adaptation algorithms within a receiver equalization (RSEQ) adaptation block 160 in the receive SerDes device 110-2, as discussed further below in conjunction with equation (1) and FIG. 4.

As shown in FIG. 1, the filtered serial output of the TXFIR filter 114 is applied to the channel 120 and received by the receive SerDes device 110-2. The received signal is initially amplified by a Variable Gain Amplifier (VGA) 140, and then enhanced in a receiver front end (RXFE) 142, typically using adjustable high pass filters in order to further mitigate channel impairments. The output of RXFE 142 is applied to an adder 144. In addition, a DFE correction from a decision-feedback equalizer (DFE) 150 is applied to the adder 144 in a feedback fashion to produce a DFE corrected signal 141. The DFE correction compensates for Inter Symbol Interference (ISI) occurring in the channel 120. The DFE corrected signal 141 is then sampled by slicers 146. As discussed further below in conjunction with FIG. 2, the slicers 146 typically sample the serial data one or more times for each serial bit duration Unit Interval (UI) in order to recover the serial data and bit clock. The sampled serial data from the slicers 146 is then deserialized by deserializer 148. The recovered data from deserializer 148 is processed in a feedback loop by the DFE 150 to generate the DFE correction. The recovery of the bit clock and other timing issues are well-known to those of ordinary skill in the art.

The recovered data from deserializer 148 is also processed by one or more adaptation algorithms within the RSEQ adaptation block 160 in the receive SerDes device 110-2 to determine equalization parameters for the VGA 140, RXFE 142 and DFE 150. Generally, the adaptation is performed using recovered data and error information through the RSEQ Adaptation block 160. The adaptation algorithm within the RSEQ adaptation block 160 may be implemented, for example, as the well-known LMS or Zero Forcing (ZF) algorithms. Exemplary adaptation algorithms are discussed further below in the section entitled “Exemplary Adaptation Algorithms.” For example, the VGA 140 receives a gain control signal from the RSEQ adaptation block 160. The RXFE 142 and DFE 150 receive filter coefficients from the RSEQ adaptation block 160.

In addition, as indicated above, the filter coefficient adjustments for the TXFIR filter 114 in the transmit SerDes device 110-1 are also determined by the RXEQ adaptation block 160. For example, the RXEQ adaptation block 160 can employ the LMS algorithm to produce TXFIR UP or DN (down) adjustment requests for different TXFIR coefficients. The TXFIR UP or DN adjustment requests generated by the RXEQ adaptation block 160 change the amount of emphasis for main cursor, pre-cursors and post-cursors in the TXFIR filter 114, thus training the remote transmit SerDes device 110-1 to the conditions of the particular channel 120. Pre-cursor and post cursor TXFIR coefficients are normally negative values to create pre-emphasis. Thus, a DN adjustment request indicates an increase in the amount of pre-emphasis, and an UP adjustment request indicates a decrease in the amount of pre-emphasis.

The RXEQ adaptation block 160 applies the determined TXFIR coefficient adjustments to link logic 165, which in turn applies the coefficient adjustment requests to the transmit (TX) portion 170 of the receive SerDes device 110-2. The TX portion 170 of the receive SerDes device 110-2 transmits UP or DN (down) requests for the coefficients over the back channel 130 to the receive (RX) portion 116 of the SerDes device 110-1. Link logic 118 applies the received filter UP or DN requests for coefficients to the TXFIR filter 114 thus changing the amount of pre-emphasis or the main cursor value.

While the present invention is described in the context of the communication system 100 having two SerDes devices 110-1 and 110-2, the present invention can apply to any communication system having serial communications from a transmitter to a receiver and where equalization updates can be provided from the receiver to the transmitter, as would be apparent to a person of ordinary skill in the art.

FIG. 2 illustrates a sampling of a series of data eyes 210-1 through 210-3 corresponding to the DFE corrected signal 141 by slicers 146. The slicers 146 of FIG. 1 comprise two data slicers 220-D<sub>i</sub> and 220-D<sub>i-1</sub>, transition slicer 230-T<sub>i</sub>, and error slicer 240-E<sub>i</sub>. When the CDR is properly locked to the incoming data in one embodiment, the transition slicer 230-T<sub>i</sub> is aligned with the statistical middle of the data transitions crossing level “0,” data slicer 220-D<sub>i</sub> is aligned to the statistical center of the data eye with a vertical (voltage) offset of zero, and the error slicer 240-E<sub>i</sub> has the same timing alignment as data slicer 220-D<sub>i</sub> but with a vertical offset of H0, typically positioning the error slicer 240-E<sub>i</sub> in the statistical middle of the data levels at the center of the eye (statistical middle between inner and outer

data eyes), as discussed further below in conjunction with FIG. 5. The H0 vertical offset is achieved as a part of VGA adaptation, and the error slicer 240-E<sub>i</sub> is used in the LMS adaptation algorithm of all RXEQ parameters, as well as remote TXFIR coefficients, in a known manner. There may be one or more error slicers 240-E<sub>i</sub> per data eye.

#### Exemplary Adaptation Algorithms

The LMS adaptation algorithm for DFE coefficients,  $c_n$ , can be described by the following equation in the exemplary case of one error slicer per data eye:

$$Cn = \overline{(D_k \wedge Esign_k)} ? \sum_{n=0}^{\infty} \overline{(D_{k-n} \wedge E_k)} : 0 \quad [1]$$

In equation (1), if the current data sample  $D_k$  from data slicer 220-D<sub>k</sub> has the same sign as the error offset  $Esign_k$ , then an exclusive NOR (“XNOR”) operation is applied to the data sample offset by the coefficient index n,  $D_{k-n}$ , and the current error sample,  $E_k$ , from error slicer 240-E<sub>k</sub>, and accumulated as an UP or DOWN adjustment into the coefficient value.

The adaptation algorithm for the coefficients for the remote TXFIR filter 114 can also be described by equation (1) with a corresponding +1 or -1 index offset n for pre-cursor and post cursor adaptation.

The adaptation algorithms for the gain adjustment for the VGA 140 and the offset H0 for the error latch, 240-E<sub>i</sub>, of FIG. 2 are similar. The interdependence of H0 and VGA adaptation is discussed further below in conjunction with FIG. 3.

Generally, the adaptation for the offset H0 for the error latch, 240-E<sub>i</sub>, of FIG. 2 may be described as:

$$H0 = \overline{(D_k \wedge Esign_k)} ? \sum_{n=0}^{\infty} \overline{(D_k \wedge E_k)} : 0 \quad [2]$$

In equation (2), if the current data sample  $D_k$  from data slicer 220-D<sub>k</sub> has the same sign as the error offset  $Esign_k$ , then an exclusive NOR “XNOR” operation is applied to the current data sample  $D_k$  and the current error sample,  $E_k$ , from error slicer 240-E<sub>k</sub>, and accumulated as an UP or DOWN adjustment into the error slicer offset value.

For a more detailed discussion of equalization adaptation techniques, see, for example, United States Published Patent Application No. 20100046598, entitled “Adaptation Of A Linear Equalizer Using A Virtual Decision Feedback Equalizer (VDFE),” incorporated by reference herein.

FIG. 3 is a block diagram illustrating a VGA/H0 adaptation block 300, based on equation (2). As shown in FIG. 3, the current data sample  $D_k$  from data slicer 220-D<sub>k</sub> and

the current error sample,  $E_k$ , from error slicer 240-E<sub>k</sub> are applied to an UP/DN decision block 310 described by equation (2), and then an accumulator 320 accumulates the values by adding or subtracting, respectively, from the current level of H0. A comparator 330 receives upper and lower limits for H0 which are typically narrower than the full range of H0 control. The range between H0 limits is related to one step of VGA control, and should be greater than this step. Whenever the comparator 330 determines that H0 control reaches an upper or lower H0 limit, the H0 accumulator is reset to its restart level (between lower and upper limits) using feedback path 335 and VGA Control 340 is incremented or decremented by one. For example, if H0 adaptation causes its accumulator 320 to reach a lower limit, then the signal from the channel 120 is not strong enough, and the signal should get a higher amplification (by increasing the gain adjustment signal applied to VGA 140). In this case, the VGA gain adjustment signal (control) is incremented by one.

The algorithm shown in FIG. 3 runs until H0 settles at a steady level between the corresponding lower and upper limits or the VGA control 340 reaches a predefined low or high limit (all limits are typically programmable). In the latter case, the VGA control 340 stops at the low limit or high limit correspondingly, and H0 is allowed to accumulate beyond its preset limits anywhere within the available range. In this case, VGA amplification may not be enough, and the vertical eye opening may suffer, leading to inferior jitter tolerance. Conversely, if VGA control 340 reaches the lower limit, this may mean that the signal cannot be attenuated enough, and may suffer saturation through the RXFE 142, which is typically not as critical as the lack of amplification, but may cause undesirable non linear effects.

FIG. 4 is a block diagram illustrating a TXFIR filter coefficient adaptation block 400 for the remote TXFIR filter 114 based on equation (1). As shown in FIG. 4, the current data sample D<sub>k</sub> from data slicer 220-D<sub>k</sub> and the current error sample, E<sub>k</sub>, from error slicer 240-E<sub>k</sub>, as well as the prior or subsequent data sample D<sub>k+/-1</sub> from the corresponding data slicer 220, are applied to an UP/DN decision block 410 described by equation (1), and then an accumulator 420 accumulates the values by adding or subtracting, respectively, from the current accumulator 420 values. If the accumulator 420 reaches an upper or lower limit, the clip block 430 latches the value and the value is conveyed to the link logic 165 as UP or DN requests to be sent through the back channel 130 to the remote SerDes 110-1. In this manner, the TXFIR coefficient values are adjusted to the parameters of the communications channel 120.

FIG. 5 illustrates a data eye diagram 500 overlaid with data slicer 220-D<sub>i</sub> and error slicer 240-E<sub>i</sub>. The data eye has an inner eye opening 510, also referred to as the inner eye 510, which is the minimum opening where no traces are going through. In addition, the data eye has an outer eye opening 520, also referred to as the outer eye 520, which is the maximum of the data eye. In many practical applications, the data slicer 220-D<sub>i</sub> is aligned to the statistical center of the data eye with a vertical (voltage) offset of zero, and the error slicer 240-E<sub>i</sub> has the same timing alignment as data slicer 220-D<sub>i</sub> but with a vertical offset of H<sub>0</sub>, typically positioning the error slicer 240-E<sub>i</sub> in the statistical middle of the data levels at the center of the eye (statistical middle between inner eye 510 and outer eye 520).

#### Effect of Equalization on Inner Eye 510 and Outer Eye 520

Generally, equalization aims to open the size of the data eye (i.e., increase the data margin). Nonetheless, it has been found that equalization can increase the inner eye 510 by an amount that is smaller than the amount that the outer eye 520 decreases (e.g., outer eye 520 closes more than the inner eye 510 opens). This will cause the statistical middle between the inner eye 510 and the outer eye 520 to reduce, and the offset level H<sub>0</sub> for the error latch 240-E<sub>i</sub> will readapt to a lower value. The reduction to the H<sub>0</sub> level can in turn cause an increase in the VGA gain adjustment, as discussed above in conjunction with FIG. 3.

There are a number of factors causing the inner eye 510 to open to a lesser extent than the outer eye 520 closes. For example, the TXFIR filter 114 typically has a limited bandwidth and acts as a low pass filter. Thus, lower frequency components in the serial data will not suffer the same degradation as pre-emphasis levels.

As indicated above, adaptation of the equalization parameters in a transmit SerDes 110-1 may adversely impact the gain adjustments and/or equalization performed in a receive SerDes 110-2 (or vice versa). For example, in the case of high attenuation channels, it has been found that the coefficients for the TXFIR 114 in the transmit SerDes 110-1 are often increased towards their upper negative limits, causing the VGA 140 in the receive SerDes 110-2 to likewise settle to its upper limits. Thus, the output of the VGA 140 will not follow further increases in emphasis by the TXFIR filter 114. As a result, the data eye opening will be smaller and the jitter tolerance in the receiver is reduced.

FIG. 6 is a flow chart describing a limited TXFIR adaptation process 600 embodiment of the present invention. The limited TXFIR adaptation process 600 may be implemented, for example, by the RXEQ adaptation block 160. Generally, the limited

TXFIR adaptation process 600 prevents the TXFIR 114 from going beyond the abilities of the VGA 140 to amplify the incoming RX signal to the required level.

As shown in FIG. 6, the limited TXFIR adaptation process 600 initially accumulates UP/DN adjustment requests for the pre, post and main cursors of the TXFIR filter 114 during step 610. A test is performed during step 620 to determine if the request is an UP request (reduction in pre-emphasis causing a reduction in inner eye 510 and an increase in outer eye 520). If it is determined during step 620 that the request is an UP request (for example, a binary value of 01), then a further test is performed during step 630 to determine if the VGA 140 is already at its lower limit. If it is determined during step 630 that the VGA 140 is already at its lower limit, then the UP request is suppressed at step 650 and is not sent over the back channel 140. If, however, it is determined during step 630 that the VGA 140 is not at its lower limit, then the UP request is allowed to be sent over the back channel 140 during step 640.

If, however, it was determined during step 620 that the request is not an UP request, then a further test is performed during step 660 to determine if the request is a DN request (for example, a binary value of 11 or 2's complement of -1), then a further test is performed during step 670 to determine if the VGA 140 is already at its high limit. If it is determined during step 670 that the VGA 140 is already at its high limit, then the DN request (increase in pre-emphasis) is suppressed at step 680 and is not sent over the back channel 140. If, however, it is determined during step 670 that the VGA 140 is not at its high limit, then the DN request is allowed to be sent over the back channel 140 during step 690.

Finally, if it was determined during step 620 that the request is not an UP request and it was determined during step 660 that the request is not a DN request, then a request is not sent through the back channel 140 during step 695.

Please note that the same algorithm is run independently for the main cursor, pre- cursors, and post- cursors.

FIG. 7 is a block diagram of a limited TXFIR adaptation system 700 embodiment of the present invention. As shown in FIG. 7, the limited TXFIR adaptation system 700 comprises the VGA/H0 adaptation block 300 of FIG. 3 and the TXFIR adaptation block 400 of FIG. 4. The VGA/H0 adaptation block 300 of FIG. 3 has been modified to generate two flags 705-H and 705-L indicating when the VGA high and low limits, respectively, have been reached.

In addition, the limited TXFIR adaptation system 700 includes request gating blocks 710, 720 that gate the UP/DN requests, respectively. As shown in FIG. 7, the request gating block 710 receives the UP requests from the TXFIR adaptation block 400, as well as the VGA flag 705-L indicating whether the VGA 140 has reached its lower limit. The VGA low limit flag 705-L serves as a disable signal for the request gating block 710. Generally, the request gating block 710 will allow the UP requests to pass to the back channel 140 as long as the VGA 140 is above low limit.

Similarly, the request gating block 720 receives the DN requests from the TXFIR adaptation block 400, as well as the VGA flag 705-H indicating whether the VGA 140 has reached its upper limit. The VGA upper limit flag 705-H serves as a disable signal for the request gating block 720. Generally, the request gating block 720 will allow the DN requests to pass to the back channel 140 as long as the VGA 140 is below low limit.

Among other benefits, the disclosed exemplary improved adaptive equalization techniques adjust the TXFIR coefficients based on the VGA gain adaptation and do not establish TXFIR coefficients that are beyond the limits of the VGA.

At least a portion of the techniques of the present invention may be implemented in one or more ICs. In forming ICs, die are typically fabricated in a repeated pattern on a surface of a semiconductor wafer. Each of the die includes a stripline device described herein, and may include other structures or circuits. Individual die are cut or diced from the wafer, then packaged as integrated circuits. One skilled in the art would know how to dice wafers and package die to produce integrated circuits. Integrated circuits so manufactured are considered part of this invention.

An IC in accordance with the present invention can be employed in many application and/or electronic systems. Suitable systems for implementing the invention may include, but are not limited to, communication devices and devices for distributing cable television signals and other high speed signals. Systems incorporating such integrated circuits are considered part of this invention. Given the teachings of the invention provided herein, one of ordinary skill in the art will be able to contemplate other implementations and applications of the techniques of the invention.

Methods may be utilized to form an integrated circuit embodiment of the present invention. The integrated circuit design can be created in a graphical computer programming language, and can be stored in a computer storage medium (such as a disk,

tape, physical hard drive, or virtual hard drive such as in a storage access network). The stored design can be converted into the appropriate format (e.g., Graphic Design System II (GDSII)) for the fabrication of photolithographic masks, which typically include multiple copies of the integrated circuit design that are formed on a wafer. The photolithographic masks are utilized to define areas of the wafer (and/or the layers thereon) to be etched or otherwise processed.

The resulting integrated circuits may be distributed by the fabricator in raw wafer form (i.e., as a single wafer that has multiple unpackaged integrated circuits), as a bare die, or in packaged form. In the latter case, the integrated circuit is mounted in a single integrated circuit package (e.g., plastic carrier with leads that are affixed to a motherboard or other higher level carrier) or in a multi-integrated circuit package (e.g., ceramic carrier that has either or both surface interconnections or buried interconnections). In any case, the integrated circuit can be integrated with other chips, discrete circuit elements, and/or other signal processing devices as part of either an intermediate product (e.g., motherboard) or an end product. The end product may be any product that includes integrated circuits.

It is to be understood that the embodiments and variations shown and described herein are merely illustrative of the principles of this invention and that various modifications may be implemented by those skilled in the art without departing from the scope and spirit of the invention.

We claim:

1. A method for adapting coefficients of an equalizer in a transmitter that communicates over a channel with a receiver, comprising:

determining if a gain value for an amplifier in said receiver is within a limit of said amplifier; and

preventing one or more adjustments to said equalizer coefficients if said gain value does not satisfy said limit of said amplifier.

2. The method of claim 1, wherein said adjustments comprise up and down requests for said equalizer coefficients.

3. The method of claim 1, further comprising the step of setting one or more flags based on whether said gain value is within said limit of said amplifier.

4. The method of claim 1, wherein said equalizer comprises one or more of a transmit finite impulse response (TxFIR) filter and a variable gain amplifier.

5. An apparatus for adapting one or more coefficients of an equalizer in a transmitter that communicates over a channel with a receiver, comprising:

a memory; and

at least one hardware device, coupled to the memory, operative to:

determining if a gain value for an amplifier in said receiver is within a limit of said amplifier; and

preventing one or more adjustments to said equalizer coefficients if said gain value does not satisfy said limit of said amplifier.

6. The apparatus of claim 5, wherein said adjustments comprise up and down requests for said coefficients.

7. The apparatus of claim 5, wherein said at least one hardware device is further configured to set one or more flags based on whether said gain value is within said limit of said amplifier.

8. An article of manufacture for adapting coefficients of an equalizer in a transmitter that communicates over a channel with a receiver, comprising a tangible machine readable recordable medium containing one or more programs which when executed implement the steps of:

determining if a gain value for an amplifier in said receiver is within a limit of said amplifier; and

preventing one or more adjustments to said coefficients if said gain value does not satisfy said limit of said variable gain amplifier.

9. An integrated circuit for adapting coefficients of an equalizer in a transmitter that communicates over a channel with a receiver, comprising:

gain limit circuitry operative to:

determine if a gain value for an amplifier in said receiver is within a limit of said amplifier; and

request gating circuitry operative to:

prevent one or more adjustments to said coefficients if said gain value does not satisfy said limit of said amplifier.

10. The integrated circuit of claim 9, wherein said adjustments comprise up and down requests for said coefficients.

## ABSTRACT

Methods and apparatus are provided for adapting transmitter equalization coefficients based on receiver gain adaptation. Equalization coefficients of a transmitter that communicates over a channel with a receiver are adapted by determining if a gain value for an amplifier in the receiver is within a limit of the amplifier; and preventing one or more adjustments to the transmitter equalization coefficients if the gain value does not satisfy the upper or lower limit of the amplifier. The gain adjustments comprise, for example, up and down requests for the transmitter equalization coefficients. One or more enable flags can optionally be set based on whether the gain value is within the limit of the amplifier.

Representative Drawing: Fig. 1

**FIG. 2**

**FIG. 3**

FIG. 4

FIG. 5

FIG. 7

FIG. 6