(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5605005号

(P5605005)

(45) 発行日 平成26年10月15日(2014.10.15)

(24) 登録日 平成26年9月5日(2014.9.5)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 21/316 | (2006.01) | HO1L 21/316 | A    |

| HO1L 29/78  | (2006.01) | HO1L 29/78  | 652K |

| HO1L 29/12  | (2006.01) | HO1L 29/78  | 652T |

| HO1L 21/336 | (2006.01) | HO1L 29/78  | 658F |

| HO1L 21/304 | (2006.01) | HO1L 29/78  | 658G |

請求項の数 11 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2010-136870 (P2010-136870)

(22) 出願日

平成22年6月16日(2010.6.16)

(65) 公開番号

特開2012-4273 (P2012-4273A)

(43) 公開日

平成24年1月5日(2012.1.5)

審査請求日

平成25年1月29日(2013.1.29)

(73) 特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置

## (57) 【特許請求の範囲】

## 【請求項 1】

炭化珪素半導体装置を製造する方法であって、

炭化珪素半導体の第1の表面に第1の酸化膜を形成する工程と、

前記第1の酸化膜を除去する工程と、

前記炭化珪素半導体において前記第1の酸化膜が除去されることにより露出した第2の表面に、前記炭化珪素半導体装置を構成する第2の酸化膜を形成する工程とを備え、

前記第1の酸化膜を除去する工程と、前記第2の酸化膜を形成する工程との間ににおいて、前記炭化珪素半導体は大気が遮断された雰囲気内に配置され、

前記第1の酸化膜を除去する工程は、800以上炭化珪素の昇華温度以下で水素ガス、塩化水素ガス、フッ化硫黄ガスおよびフッ化炭素ガスからなる群から選択される少なくとも1つを含むガスを用いてエッティングする工程を含む、炭化珪素半導体装置の製造方法。

## 【請求項 2】

前記第1の酸化膜を形成する工程と、前記第1の酸化膜を除去する工程との間ににおいて、前記炭化珪素半導体は大気が遮断された雰囲気内に配置される、請求項1に記載の炭化珪素半導体装置の製造方法。

## 【請求項 3】

前記第1の酸化膜を形成する工程では、前記炭化珪素半導体の前記第1の表面に形成されたダメージ層を酸化する、請求項1または2に記載の炭化珪素半導体装置の製造方法。

10

20

## 【請求項 4】

前記第1の酸化膜を除去する工程は、酸素を含まない雰囲気で1200以上炭化珪素の昇華温度以下で前記第1の酸化膜を熱分解する工程を含む、請求項1～3のいずれか1項に記載の炭化珪素半導体装置の製造方法。

## 【請求項 5】

前記第1の酸化膜を除去する工程と前記第2の酸化膜を形成する工程との間において、前記炭化珪素半導体の温度差を500以下に保持する、請求項1～4のいずれか1項に記載の炭化珪素半導体装置の製造方法。

## 【請求項 6】

前記第2の酸化膜を形成する工程では、前記第1の酸化膜を除去する工程で用いる装置を用いて、前記第2の酸化膜を形成する、請求項5に記載の炭化珪素半導体装置の製造方法。

10

## 【請求項 7】

前記第1の酸化膜を形成する工程と、前記第1の酸化膜を除去する工程と、前記第2の酸化膜を形成する工程とのそれぞれの間において、前記炭化珪素半導体の温度差を500以下に保持する、請求項2に記載の炭化珪素半導体装置の製造方法。

## 【請求項 8】

前記第1の酸化膜を形成する工程で用いる装置と、前記第1の酸化膜を除去する工程で用いる装置と、前記第2の酸化膜を形成する工程で用いる装置とが同一である、請求項7に記載の炭化珪素半導体装置の製造方法。

20

## 【請求項 9】

炭化珪素半導体装置を製造する装置であって、炭化珪素半導体の第1の表面に第1の酸化膜を形成するための第1の形成部と、前記第1の酸化膜を除去するための除去部と、前記除去部で、前記炭化珪素半導体において前記第1の酸化膜が除去されることにより露出した第2の表面に、前記炭化珪素半導体装置を構成する第2の酸化膜を形成するための第2の形成部と、前記炭化珪素半導体を搬送可能に前記除去部と前記第2の形成部とを接続する第1の接続部とを備え、

前記第1の接続部における前記炭化珪素半導体を搬送させる領域は、大気の遮断が可能である、炭化珪素半導体装置の製造装置。

30

## 【請求項 10】

前記炭化珪素半導体を搬送可能に前記第1の形成部と前記除去部とを接続する第2の接続部をさらに備え、

前記第2の接続部における前記炭化珪素半導体を搬送させる領域は、大気の遮断が可能である、請求項9に記載の炭化珪素半導体装置の製造装置。

## 【請求項 11】

炭化珪素半導体装置を製造する装置であって、炭化珪素半導体の第1の表面に第1の酸化膜を形成するための第1の形成部と、前記第1の酸化膜を除去し、かつ前記炭化珪素半導体において前記第1の酸化膜が除去されることにより露出した第2の表面に、前記炭化珪素半導体装置を構成する第2の酸化膜を形成するための第2の形成部と、前記炭化珪素半導体を搬送可能に前記第1の形成部と前記第2の形成部とを接続する接続部とを備えた、炭化珪素半導体装置の製造装置。

40

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、炭化珪素(SiC)半導体装置の製造方法および製造装置に関し、より特定的には酸化膜を有するSiC半導体装置の製造方法および製造装置に関する。

## 【背景技術】

## 【0002】

50

従来より、半導体デバイスの製造方法において、表面に付着している付着物を除去するために洗浄を行なっている。このような洗浄方法として、たとえば、特開平6-314679号公報（特許文献1）に開示の技術が挙げられる。この特許文献1の半導体基板の洗浄方法は、以下のように行なうことが開示されている。まず、シリコン（Si）基板をオゾンを含む超純水で洗浄してSi酸化膜を形成し、このSi酸化膜の内部や表面にパーティクルおよび金属不純物を取り込む。次に、このSi基板を希フッ酸水溶液で洗浄してSi酸化膜をエッティング除去し、同時にパーティクルおよび金属不純物を除去する。

【先行技術文献】

【特許文献】

【0003】

10

【特許文献1】特開平6-314679号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、上記特許文献1に開示の洗浄方法を用いてSiC半導体装置を製造すると、以下の問題があることを本発明者は初めて明らかにした。SiC半導体装置として、たとえばMOSFET（Metal Oxide Semiconductor Field Effect Transistor：電界効果トランジスタ）を製造する場合には、たとえばSiC基板上にSiCエピタキシャル層を形成し、このエピタキシャル層の表面を洗浄し、この表面上にゲート酸化膜を形成する。仮に、エピタキシャル層の表面を上記特許文献1の洗浄方法により洗浄しても、洗浄後の表面上に不純物が付着する。この表面上にゲート酸化膜を形成しても、エピタキシャル層とゲート酸化膜との界面に不純物が存在することで、SiC半導体装置の特性が悪くなるという問題がある。

20

【0005】

したがって、本発明の目的は、特性を向上できるSiC半導体装置の製造方法およびSiC半導体装置の製造装置を提供することである。

【課題を解決するための手段】

【0006】

30

本発明者が鋭意研究した結果、上記課題は、洗浄後のエピタキシャル層を大気中またはクリーン度の低い雰囲気に配置することに起因していることを見い出した。

【0007】

そこで、本発明のSiC半導体装置の製造方法は、SiC半導体の第1の表面に第1の酸化膜を形成する工程と、第1の酸化膜を除去する工程と、SiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成する工程とを備え、第1の酸化膜を除去する工程と、第2の酸化膜を形成する工程との間において、SiC半導体は大気が遮断された雰囲気内に配置される。

【0008】

本発明のSiC半導体装置の製造方法によれば、第1の酸化膜を形成する工程において、SiC半導体の第1の表面に付着していた不純物、パーティクルなどを第1の酸化膜に取り込むことができる。第1の酸化膜を除去する工程により、SiC半導体の第1の表面に付着していた不純物、パーティクルなどを除去することで清浄化された第2の表面を形成することができる。不純物、パーティクルなどが除去されたSiC半導体を大気が遮断された雰囲気内に配置することで、大気中の不純物、パーティクルなどがSiC半導体の第2の表面に再付着することを抑制できるので、SiC半導体の第2の表面を清浄に維持することができる。第2の酸化膜を形成する工程において、清浄に維持されたSiC半導体の第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成することができるので、SiC半導体の第2の表面と第2の酸化膜との界面に存在する不純物、パーティクルなどを低減できる。したがって、特性を向上できるSiC半導体装置を製造することができる。

40

【0009】

50

上記 SiC 半導体装置の製造方法において好ましくは、第1の酸化膜を形成する工程と、第1の酸化膜を除去する工程との間において、SiC 半導体は大気が遮断された雰囲気内に配置される。

#### 【0010】

これにより、第1の酸化膜を除去した後のみでなく、第1の酸化膜を形成した後にも、不純物、パーティクルなどが再付着することを抑制できる。このため、SiC 半導体と第2の酸化膜との界面に存在する不純物、パーティクルなどをより低減できる。したがって、より特性を向上できる SiC 半導体装置を製造することができる。

#### 【0011】

上記 SiC 半導体装置の製造方法において好ましくは、第1の酸化膜を形成する工程では、SiC 半導体の第1の表面に形成されたダメージ層を酸化する。

10

#### 【0012】

これにより、第1の酸化膜を除去する工程を実施すると、SiC 半導体の第1の表面に形成されたダメージ層も併せて除去することができる。このため、SiC 半導体の特性を向上できるので、特性をより向上できる SiC 半導体を製造することができる。

#### 【0013】

上記 SiC 半導体装置の製造方法において好ましくは、第1の酸化膜を除去する工程は、酸素(O)を含まない雰囲気で 1200 以上 SiC の昇華温度以下で第1の酸化膜を熱分解する工程、および、1000 以上 SiC の昇華温度以下で水素ガス(H<sub>2</sub>)、塩化水素ガス(HCl)、フッ化硫黄ガス(SF<sub>6</sub>)およびフッ化炭素ガス(CF<sub>4</sub>)からなる群から選択される少なくとも1つを含むガスを用いてエッチングする工程の少なくとも一方を含む。

20

#### 【0014】

これにより、ウェット洗浄(液相を含む洗浄)をせずに第1の酸化膜を容易に除去できるので、ウェット洗浄による汚染を防止することができる。

#### 【0015】

上記 SiC 半導体装置の製造方法において好ましくは、第1の酸化膜を除去する工程と第2の酸化膜を形成する工程との間において、SiC 半導体の温度差を 500 以下に保持する。

#### 【0016】

30

これにより、第1の酸化膜を除去する工程と第2の酸化膜を形成する工程との間で温度が低下することを抑制することで、昇温時間を削減できるため、スループットを向上することができる。

#### 【0017】

上記 SiC 半導体装置の製造方法において好ましくは、第2の酸化膜を形成する工程では、第1の酸化膜を除去する工程で用いる装置を用いて、第2の酸化膜を形成する。

#### 【0018】

同じ装置を用いて、第1の酸化膜を除去できるとともに、第2の酸化膜を形成できるので、第1の酸化膜を除去する工程と第2の酸化膜を形成する工程との間で温度が低下することを抑制できる。これにより、第1の酸化膜を除去する工程と第2の酸化膜を形成する工程との移行により昇温時間を削減できるため、スループットを向上することができる。

40

#### 【0019】

上記 SiC 半導体装置の製造方法において好ましくは、第1の酸化膜を形成する工程と、第1の酸化膜を除去する工程と、第2の酸化膜を形成する工程とのそれぞれの間において、SiC 半導体の温度差を 500 以下に保持する。

#### 【0020】

これにより、第1の酸化膜を形成する工程、第1の酸化膜を除去する工程および第2の酸化膜を形成する工程の間で温度が低下することを抑制できるので、スループットをより向上することができる。

#### 【0021】

50

上記SiC半導体装置の製造方法において好ましくは、第1の酸化膜を形成する工程で用いる装置と、第1の酸化膜を除去する工程で用いる装置と、第2の酸化膜を形成する工程で用いる装置とが同一である。

【0022】

同じ装置を用いて、第1の酸化膜を形成し、かつ第1の酸化膜を除去し、かつ第2の酸化膜を形成できるので、第1の酸化膜を形成する工程と、第1の酸化膜を除去する工程と、第2の酸化膜を形成する工程との移行により温度が低下することを抑制できる。このため、スループットをより向上することができる。

【0023】

本発明の一の局面におけるSiC半導体装置の製造装置は、第1の形成部と、除去部と、第2の形成部と、第1の接続部とを備えている。第1の形成部は、SiC半導体の第1の表面に第1の酸化膜を形成する。除去部は、第1の酸化膜を除去する。第2の形成部は、除去部で、SiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成する。第1の接続部は、SiC半導体を搬送可能に、除去部と第2の形成部とを接続する。第1の接続部におけるSiC半導体を搬送させる領域は、大気の遮断が可能である。

10

【0024】

本発明の一の局面におけるSiC半導体の製造装置によれば、第1の形成部において、SiC半導体の第1の表面に付着していた不純物、パーティクルなどを取り込むように第1の酸化膜を形成することができる。除去部において第1の酸化膜を除去することにより、SiC半導体の第1の表面に付着していた不純物、パーティクルなどを除去することで清浄化された第2の表面を形成することができる。第1の接続部により、不純物、パーティクルなどが除去された第2の表面を有するSiC半導体を大気が遮断された雰囲気内に配置することができるので、大気中の不純物、パーティクルなどがSiC半導体の第2の表面に再付着することを抑制でき、SiC半導体の第2の表面を清浄に維持することができる。第2の形成部において、清浄に維持されたSiC半導体の第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成することができるので、SiC半導体の第2の表面と第2の酸化膜との界面に存在する不純物、パーティクルなどを低減できる。したがって、特性向上できるSiC半導体装置を製造することができる。

20

【0025】

上記一の局面におけるSiC半導体の製造装置において好ましくは、SiC半導体を搬送可能に第1の形成部と除去部とを接続する第2の接続部をさらに備え、第1の接続部におけるSiC半導体を搬送させる領域は、大気の遮断が可能である。

30

【0026】

第2の接続部により、第1の酸化膜を形成した後、および、第1の酸化膜を除去した後、不純物、パーティクルなどが再付着することを抑制できる。このため、SiC半導体と第2の酸化膜との界面に存在する不純物、パーティクルなどをより低減できる。したがって、より特性向上できるSiC半導体装置を製造することができる。

【0027】

本発明の他の局面におけるSiC半導体装置の製造装置は、第1の形成部と、第2の形成部とを備えている。第1の形成部は、SiC半導体の第1の表面に第1の酸化膜を形成する。第2の形成部は、第1の酸化膜を除去し、かつSiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成する。

40

【0028】

本発明の他の局面におけるSiC半導体の製造装置によれば、第1の形成部において、SiC半導体の第1の表面に付着していた不純物、パーティクルなどを取り込むように第1の酸化膜を形成することができる。第2の形成部において第1の酸化膜を除去することにより、SiC半導体の第1の表面に付着していた不純物、パーティクルなどを除去することで清浄化された第2の表面を形成することができる。同じ第2の形成部においてSi

50

C 半導体装置を構成する第 2 の酸化膜を形成することができるので、第 1 の酸化膜を除去してから第 2 の酸化膜を形成するまでの間に、不純物、パーティクルなどが除去された第 2 の表面を有する SiC 半導体を大気が遮断された雰囲気内に配置することができる。これにより、大気中の不純物、パーティクルなどが SiC 半導体の第 2 の表面に再付着することを抑制でき、SiC 半導体の第 2 の表面を清浄に維持した状態で SiC 半導体装置を構成する第 2 の酸化膜を形成することができる。このため、SiC 半導体の第 2 の表面と第 2 の酸化膜との界面に存在する不純物、パーティクルなどを低減できる。したがって、特性を向上できる SiC 半導体装置を製造することができる。

#### 【0029】

上記他の局面における SiC 半導体装置の製造装置において好ましくは、第 1 の形成部と第 2 の形成部とは、同一である。 10

#### 【0030】

これにより、第 1 の酸化膜を形成した後、および、第 1 の酸化膜を除去した後、不純物、パーティクルなどが再付着することを抑制できる。このため、SiC 半導体と第 2 の酸化膜との界面に存在する不純物、パーティクルなどをより低減できる。したがって、より特性を向上できる SiC 半導体装置を製造することができる。

#### 【発明の効果】

#### 【0031】

以上説明したように、本発明の SiC 半導体装置の製造方法および製造装置によれば、洗浄後の SiC 半導体は大気が遮断された雰囲気内に配置されるので、SiC 半導体と SiC 半導体装置を構成する酸化膜との界面に存在する不純物、パーティクルなどを低減できる。したがって、特性を向上した SiC 半導体を製造することができる。 20

#### 【図面の簡単な説明】

#### 【0032】

【図 1】本発明の実施の形態 1 における SiC 半導体装置の製造装置を示す模式図である。 。

【図 2】本発明の実施の形態 1 における SiC 半導体装置の製造方法を示すフローチャートである。

【図 3】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。 30

【図 4】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。

【図 5】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。

【図 6】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。

【図 7】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。

【図 8】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。 40

【図 9】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。

【図 10】本発明の実施の形態 1 における SiC 半導体装置の各製造工程を概略的に示す断面図である。

#### 【図 11】本発明の実施の形態 2 における SiC 半導体装置の製造装置の模式図である。

#### 【発明を実施するための形態】

#### 【0033】

以下、図面に基づいて本発明の実施の形態を説明する。なお、以下の図面において同一または相当する部分には、同一の参照符号を付し、その説明は繰り返さない。

#### 【0034】

10

20

30

40

50

(実施の形態 1)

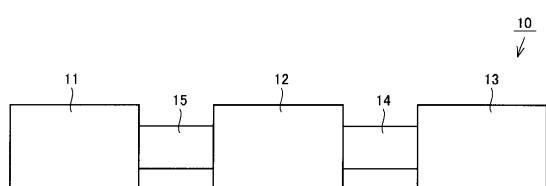

図1は、本発明の実施の形態1におけるSiC半導体装置の製造装置を示す模式図である。図1を参照して、本発明の一実施の形態におけるSiC半導体装置の製造装置10を説明する。

【0035】

図1に示すように、SiC半導体装置の製造装置10は、第1の形成部11と、除去部12と、第2の形成部13と、第1の接続部14と、第2の接続部15とを備えている。除去部12と、第2の形成部13とは、第1の接続部14により接続されている。第1の形成部11と除去部12とは、第2の接続部15により接続されている。除去部12、第2の形成部13および第1の接続部14の内部は大気から遮断されており、内部は互いに連通可能である。第1の形成部11、除去部12および第2の接続部15の内部は大気から遮断されており、内部は互いに連通可能である。

10

【0036】

第1の形成部11は、SiC半導体の第1の表面に第1の酸化膜を形成する。第1の形成部11は、たとえば熱酸化装置、プラズマ発生装置、オゾン水などのOを含む溶液を用いて第1の酸化膜を形成する装置などが用いられる。

【0037】

除去部12は、第1の形成部11で形成した第1の酸化膜を除去する。除去部12は、たとえば熱分解装置、ガスを用いたエッティング装置、プラズマ発生装置、フッ化水素(HF)などの溶液を用いて第1の酸化膜を除去する装置などが用いられる。

20

【0038】

第1の形成部11および除去部12で用いるプラズマ発生装置は、特に限定されず、たとえば平行平板型RIE(Reactive Ion Etching:反応性イオンエッティング)装置、ICP(Inductive Coupled Plasma:誘導結合プラズマ)型RIE装置、ECR(Electron Cyclotron Resonance:電子サイクロトロン共鳴)型RIE装置、SWP(Surface Wave Plasma:表面波プラズマ)型RIE装置などが用いられる。

【0039】

第2の形成部13は、除去部12で、SiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置(図9参照)を構成する第2の酸化膜を形成する。第2の形成部13は、たとえば熱酸化装置、CVD(Chemical Vapor Deposition:化学蒸着)装置などが用いられる。

30

【0040】

第1の接続部14は、SiC半導体を搬送可能に除去部12と第2の形成部13とを接続する。第2の接続部15は、SiC半導体を搬送可能に第1の形成部11と除去部12とを接続する。第1および第2の接続部14、15においてSiC半導体を搬送させる領域(内部空間)は、大気の遮断が可能である。

【0041】

ここで、大気の遮断(大気を遮断した雰囲気)とは、大気が混入しない雰囲気を意味し、たとえば、不活性ガスや窒素ガスよりなる雰囲気、真空である。具体的には、大気を遮断した雰囲気は、たとえば窒素(N)、ヘリウム(He)、ネオン(Ne)、アルゴン(Argon)、クリプトン(Kr)、キセノン(Xe)、ラドン(Rn)、またはこれらの組み合わせからなるガスが充填された雰囲気である。また、大気を遮断した雰囲気は、たとえば1Pa以下、好ましくは0.1Pa以下である。

40

【0042】

本実施の形態では、第1の接続部14は、除去部12の内部と第2の形成部13との内部とを連結している。第1の接続部14は、除去部12から搬出されるSiC半導体を第2の形成部13へ搬送するための空間を内部に有する。つまり、第1の接続部14は、SiC半導体を大気に開放しないように、除去部12から第2の形成部13へ搬送するため設置されている。

【0043】

50

同様に、第2の接続部15は、第1の形成部11の内部と除去部12の内部とを連結している。第2の接続部15は、第1の形成部11から搬出されるSiC半導体を除去部12へ搬送するための空間を内部に有する。つまり、第2の接続部15は、SiC半導体を大気に開放しないように、第1の形成部11から除去部12へ搬送するために設置されている。なお、第2の接続部15は省略されてもよい。

【0044】

第1および第2の接続部14、15は、内部でSiC半導体が搬送可能であるような大きさを有する。また第1および第2の接続部14、15は、SiC半導体をサセプタに載置した状態で搬送可能である大きさを有していてもよい。第1の接続部14は、たとえば除去部12の出口と第2の形成部13の入口とを接続するロードロック室である。第2の接続部15は、たとえば第1の形成部11の出口と、除去部12の入口とを連結するロードロック室である。10

【0045】

また、製造装置10は、第1の接続部14の内部に配置されるとともに、除去部12から第2の形成部13へSiC半導体を搬送するための第1の搬送部をさらに備えていてもよい。同様に、製造装置10は、第2の接続部15の内部に配置されるとともに、第1の形成部11から除去部12へSiC半導体を搬送するための第2の搬送部をさらに備えていてもよい。第1の搬送部と第2の搬送部とは、同一であっても異なっていてもよい。

【0046】

また、製造装置10は、第1および第2の接続部14、15を覆う断熱部材をさらに備えていてもよい。また、製造装置10は、第1および第2の接続部14、15の外周に配置され、第1および第2の接続部14、15を加熱する加熱部をさらに備えていてもよい。この場合、第1の形成部11、除去部12および第2の形成部13との間での温度差を低減できるので、搬送によるSiC半導体の温度低下を抑制できる。20

【0047】

また、製造装置10は、第1の接続部14内に配置され、かつ除去部12の内部と第2の形成部13との内部とを遮断するための第1の遮断部をさらに備えていてもよい。また製造装置10は、第2の接続部15内に配置され、かつ第1の形成部11の内部と除去部12の内部とを遮断するための第2の遮断部をさらに備えていてもよい。第1および第2の遮断部は、たとえばそれぞれの連通部を塞ぐことが可能な弁や扉などを用いることができ、複数あってもよい。30

【0048】

また、製造装置10は、内部の雰囲気ガスを排出するための真空ポンプや、内部の雰囲気ガスを置換するための置換ガスポンベをさらに備えていてもよい。真空ポンプや置換ガスポンベは、第1の形成部11、除去部12、第2の形成部13、第1の接続部14および第2の接続部15のそれぞれに接続されていてもよく、少なくともいずれか1つに接続されていてもよい。

【0049】

なお、製造装置10は、上記以外の様々な要素を含んでいてもよいが、説明の便宜上、これらの要素の図示および説明は省略する。40

【0050】

また、図1では、第1の接続部14は除去部12と第2の形成部13との間のみを連結し、第2の接続部15は第1の形成部11と除去部12との間のみを連結する形状を示したが、特にこれに限定されない。たとえば第1および第2の接続部14、15として、たとえば大気を遮断したチャンバを用い、このチャンバ内に第1の形成部11、除去部12および第2の形成部13が配置されていてもよい。

【0051】

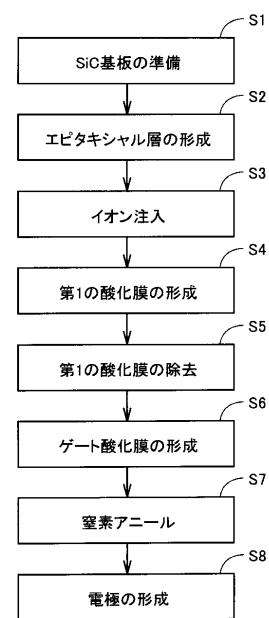

図2は、本発明の実施の形態1におけるSiC半導体装置の製造方法を示すフローチャートである。図3～図10は、本発明の実施の形態1におけるSiC半導体装置の各製造工程を概略的に示す断面図である。続いて、図1～図10を参照して、本発明の一実施の50

形態におけるSiC半導体装置の製造方法を説明する。本実施の形態では、図1に示すSiC半導体の製造装置10を用いて、SiC半導体装置の一例としてMOSFET (Metal Oxide Semiconductor Field Effect Transistor: 電界効果トランジスタ) を製造する。

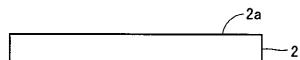

#### 【0052】

図2および図3に示すように、まず、表面2aを有するSiC基板2を準備する(ステップS1)。SiC基板2は、特に限定されないが、たとえば以下のように準備することができる。

#### 【0053】

具体的には、たとえば、昇華法、CVD法、HVP (Hydride Vapor Phase Epitaxy: ハイドライド気相成長) 法、MBE (Molecular Beam Epitaxy: 分子線エピタキシ) 法、OMVPE (Organometallic Vapor Phase Epitaxy: 有機金属気相成長) 法などの気相成長法、ラックス法、高圧素圧溶液法などの液相成長法などにより成長されたSiCインゴットを準備する。その後、SiCインゴットから表面を有するSiC基板を切り出す。切り出す方法は特に限定されず、SiCインゴットからスライスなどによりSiC基板を切り出す。

#### 【0054】

次いで、切り出したSiC基板の表面を研磨する。研磨する面は、表面のみでもよく、表面と反対側の裏面をさらに研磨してもよい。研磨する方法は特に限定されないが、表面を平坦にするとともに、傷などのダメージを低減するために、たとえばCMP (Chemical Mechanical Polishing: 化学機械研磨) を採用することができる。CMPでは、研磨剤としてコロイダルシリカ、砥粒としてダイヤモンド、酸化クロム、固定剤として接着剤、ワックスなどを用いる。なお、CMPと併せて、あるいは代わりに、電界研磨法、化学研磨法、機械研磨法などの他の研磨をさらに行なってもよい。また研磨を省略してもよい。

#### 【0055】

その後、SiC基板の表面を洗浄する。洗浄する方法は特に限定されないが、たとえば、熱酸化などにより酸化膜を形成した後に、その酸化膜を熱分解、熱エッ칭などにより除去することによる洗浄を採用することができる。なお洗浄を省略してもよい。

#### 【0056】

これにより、図3に示す表面2aを有するSiC基板2を準備することができる。このようなSiC基板2として、たとえば導電型がn型であり、抵抗が0.02cmの基板を用いる。

#### 【0057】

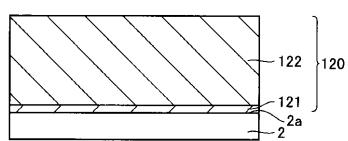

次に、図2および図4に示すように、SiC基板2の表面2a上に、気相成長法、液相成長法などにより、エピタキシャル層120を形成する(ステップS2)。本実施の形態では、たとえば以下のようにエピタキシャル層120を形成する。

#### 【0058】

具体的には、図4に示すように、SiC基板2の表面2a上に、バッファ層121を形成する。バッファ層121は、たとえば導電型がn型のSiCからなり、たとえば厚さが0.5μmのエピタキシャル層である。またバッファ層121における導電性不純物の濃度は、たとえば $5 \times 10^{17} \text{ cm}^{-3}$ である。

#### 【0059】

その後、図4に示すように、バッファ層121上に耐圧保持層122を形成する。耐圧保持層122として、気相成長法、液相成長法などにより、導電型がn型のSiCからなる層を形成する。耐圧保持層122の厚さは、たとえば15μmである。また耐圧保持層122におけるn型の導電性不純物の濃度は、たとえば $5 \times 10^{15} \text{ cm}^{-3}$ である。

#### 【0060】

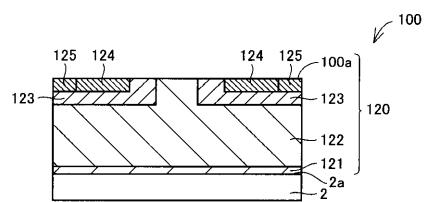

次に、図2および図5に示すように、エピタキシャル層120にイオン注入する(ステップS3)。本実施の形態では、図5に示すように、p型ウェル領域123と、n<sup>+</sup>ソース領域124と、p<sup>+</sup>コンタクト領域125とを、以下のように形成する。まず導電型が

10

20

30

40

50

p型の不純物を耐圧保持層122の一部に選択的に注入することで、ウエル領域123を形成する。その後、n型の導電性不純物を所定の領域に選択的に注入することによってソース領域124を形成し、また導電型がp型の導電性不純物を所定の領域に選択的に注入することによってコンタクト領域125を形成する。なお不純物の選択的な注入は、たとえば酸化膜からなるマスクを用いて行われる。このマスクは、不純物の注入後にそれぞれ除去される。

#### 【0061】

このようなイオン注入するステップS3の後、活性化アニール処理が行われてもよい。たとえば、アルゴン雰囲気中、加熱温度1700で30分間のアニールが行われる。

#### 【0062】

またイオン注入するステップS3の後、さらに、有機洗浄、酸洗浄、RCA洗浄などの表面洗浄を行ってもよい。

#### 【0063】

これらの工程により、図5に示すように、SiC基板2と、SiC基板2上に形成されたエピタキシャル層120とを備えたエピタキシャルウェハ100を準備することができる。

#### 【0064】

次に、エピタキシャルウェハ100(SiC半導体)の表面100a(第1の表面)を洗浄する。具体的には、図2および図6に示すように、エピタキシャルウェハ100の表面100aに、第1の酸化膜3を形成する(ステップS4)。第1の酸化膜3は、たとえば酸化シリコンである。本実施の形態のステップS4では、図1に示す製造装置10の第1の形成部11で第1の酸化膜3を形成する。

#### 【0065】

第1の酸化膜3の形成方法は、特に限定されず、たとえばOを含む溶液、Oプラズマ、Oガスを含む雰囲気での熱酸化などを用いて、エピタキシャルウェハ100の表面100aを酸化する方法が用いられる。

#### 【0066】

Oを含む溶液は、たとえばオゾン水が挙げられる。SiCが安定した化合物であることを考慮すると、たとえば30ppm以上の濃度を有するオゾン水を用いることが好ましい。この場合、オゾンの分解を抑制できるとともに、エピタキシャルウェハ100の表面100aとオゾンとの反応速度を高めることができるので、表面100aに第1の酸化膜3を容易に形成することができる。

#### 【0067】

また、Oガスを含む熱酸化は、SiCが安定した化合物であることを考慮すると、たとえば700以上の温度のドライ雰囲気で行なうことが好ましい。なお、ドライ雰囲気とは、気相中で第1の酸化膜3を形成することを意味し、意図しない液相成分を含んでいてもよい。

#### 【0068】

また、Oプラズマとは、O元素を含むガスから生成されるプラズマを意味し、たとえばOガスをプラズマ発生装置に供給することにより発生させることができる。「Oプラズマにより第1の酸化膜3を形成する」とは、O元素を含むガスを用いたプラズマにより第1の酸化膜3を形成することを意味する。言い換えると、O元素を含むガスから生成されるプラズマによって処理されることにより、第1の酸化膜3を形成することを意味する。

#### 【0069】

このステップS4において、表面100aに付着した不純物、パーティクルを除去することを目的とする場合には、たとえば1分子層以上10nm以下の厚み(表面100aからSiC基板2に向けた方向の厚み)の第1の酸化膜3を形成する。1分子層以上の厚みを有する第1の酸化膜3を形成することで、表面100aに付着している不純物、パーティクルなどを第1の酸化膜3の表面や内部に取り込むことができる。10nm以下の厚みの酸化膜を形成することで、後述するステップS5で第1の酸化膜3は除去されやすくな

10

20

30

40

50

る。表面 100a の不純物、パーティクルを取り込んで酸化する場合には、液相による洗浄（ウェット洗浄）および気相による洗浄（ドライ洗浄）を用いることができる。

【0070】

エピタキシャルウエハ 100 にイオン注入や活性化アニール処理などにより表面 100a がダメージを受け、エピタキシャルウエハ 100 の表面 100a に形成されたダメージ層を除去することを目的とする場合には、このステップ S4 においてダメージ層を酸化する。この場合、たとえば 10 nm を超えて 100 nm 以下の厚みを有する第 1 の酸化膜 3 を形成する。ダメージ層を酸化することで、表面 100a に付着した不純物、パーティクルなどを第 1 の酸化膜 3 に取り込むことができる。ダメージ層を酸化する場合には、気相による洗浄（ドライ洗浄）を採用する。ここで、ダメージ層は、他の領域に比べて表面荒れなどが生じているので、たとえば SIMS 分析を行なうことで、非注入領域に比べて過剰に Si もしくは C が存在していることにより特定される。

【0071】

次に、図 1 を参照して、第 1 の形成部 11 で第 1 の酸化膜 3 を形成したエピタキシャルウエハ 100 を、除去部 12 へ搬送する。このとき、エピタキシャルウエハ 100 は大気が遮断された雰囲気である第 2 の接続部 15 内で搬送される。言い換えると、第 1 の酸化膜 3 を形成するステップ S4 と第 1 の酸化膜 3 を除去するステップ S5 との間では、エピタキシャルウエハ 100 は大気が遮断された雰囲気内に配置される。これにより、第 1 の酸化膜 3 が形成された後に、エピタキシャルウエハ 100 の表面 101a に大気中に含まれる不純物が付着することを抑制できる。

【0072】

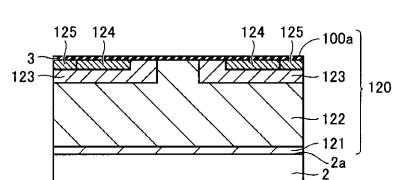

次に、図 2 および図 7 に示すように、第 1 の酸化膜 3 を除去する（ステップ S5）。本実施の形態のステップ S5 では、図 1 に示す製造装置 10 の除去部 12 で第 1 の酸化膜 3 を除去する。

【0073】

第 1 の酸化膜 3 の除去方法は、特に限定されず、たとえばウェットエッティング、ドライエッティング、熱分解、F プラズマなどを用いることができる。

【0074】

ウェットエッティングは、たとえば HF、NH<sub>4</sub>F（フッ化アンモニウム）などの溶液を用いて第 1 の酸化膜 3 を除去する。

【0075】

ドライエッティングは、800 以上 SiC の昇華温度以下、好ましくは 1000 以上 SiC の昇華温度以下で、水素ガス、塩化水素ガス、フッ化硫黄ガスおよびフッ化炭素ガスからなる群から選択される少なくとも 1 つを含むガスを用いて、第 1 の酸化膜 3 を除去することが好ましい。800 以上の水素ガス、塩化水素ガス、フッ化硫黄ガスおよびフッ化炭素ガスは、第 1 の酸化膜 3 を還元する効果が高い。この観点から 1000 以上がより好ましい。第 1 の酸化膜が SiO<sub>x</sub> の場合、水素ガスは SiO<sub>x</sub> を H<sub>2</sub>O と SiH<sub>y</sub> とに分解し、塩化水素ガスは SiO<sub>x</sub> を H<sub>2</sub>O と SiCl<sub>2</sub> とに分解する。SiC の昇華温度以下にすることで、エピタキシャルウエハ 100 の劣化を抑制できる。また、ドライエッティングは、反応を促進できる観点から、減圧下で行なうことが好ましい。

【0076】

熱分解は、O を含まない雰囲気で 1200 以上 SiC の昇華温度以下で、第 1 の酸化膜 3 を熱分解することが好ましい。1200 以上の O を含まない雰囲気でエピタキシャルウエハ 100 の表面 100a に形成された第 1 の酸化膜 3 を加熱すると、第 1 の酸化膜 3 を容易に熱分解することができる。SiC の昇華温度以下にすることで、エピタキシャルウエハ 100 の劣化を抑制できる。また、熱分解は、反応を促進できる観点から、減圧下で行なうことが好ましい。

【0077】

F プラズマとは、F 元素を含むガスから生成されるプラズマを意味し、たとえば四フッ化炭素 (CF<sub>4</sub>)、三フッ化メタン (CHF<sub>3</sub>)、フロン (C<sub>2</sub>F<sub>6</sub>)、六フッ化硫黄 (SF<sub>6</sub>)

10

20

30

40

50

)、三フッ化窒素( $NF_3$ )、二フッ化キセノン( $XeF_2$ )、フッ素( $F_2$ )、および三フッ化塩素( $ClF_3$ )の単独ガスあるいは混合ガスをプラズマ発生装置に供給することにより発生させることができる。「Fプラズマにより第1の酸化膜3を除去する」とは、F元素を含むガスを用いたプラズマにより第1の酸化膜3を除去することを意味する。言い換えると、F元素を含むガスから生成されるプラズマによって処理されることにより、第1の酸化膜3を除去することを意味する。

#### 【0078】

このステップS5を実施することにより、ステップS4で不純物、パーティクルなどを取り込んだ第1の酸化膜3を除去するので、エピタキシャルウェハ100の表面100aの不純物、パーティクルなどを除去できる。これにより、図7に示すように、不純物、パーティクルなどが低減された表面101a(第2の表面)を有するエピタキシャルウェハ101を形成することができる。

#### 【0079】

また、ステップS4でダメージ層を酸化させた第1の酸化膜3を形成した場合には、ステップS5を実施することにより、ダメージ層もさらに除去できる。これにより、図7に示すように、不純物、パーティクルなどが低減された表面101aを有するエピタキシャルウェハ101を形成することができる。これにより、図7に示すように、不純物、パーティクルなどが低減され、かつダメージ層が除去された表面101aを有するエピタキシャルウェハ101を形成することができる。

#### 【0080】

なお、上記ステップS4およびS5を繰り返してもよい。また必要に応じて、他の薬液での洗浄工程、純水リーン工程、乾燥工程などを追加して実施してもよい。他の薬液は、たとえば硫酸と過酸化水素水とを含むSPMが挙げられる。ステップS2前にSPMで洗浄する場合には有機物を除去することもできる。ただし、第1の酸化膜3を除去するステップS5と、後述するゲート酸化膜126を形成するステップS6との間に他の工程が追加される場合には、他の工程への移行時においてもエピタキシャルウェハは大気が遮断された雰囲気内に配置される。

#### 【0081】

次に、図1を参照して、除去部12で第1の酸化膜3を除去したエピタキシャルウェハ101を、第2の形成部13へ搬送する。このとき、エピタキシャルウェハ100は大気が遮断された雰囲気である第2の接続部15内で搬送される。言い換えると、第1の酸化膜3を除去するステップS5と第2の酸化膜としてのゲート酸化膜を形成するステップS6との間では、エピタキシャルウェハ101は大気が遮断された雰囲気内に配置される。これにより、第1の酸化膜3が除去された後に、エピタキシャルウェハ101の表面101aに大気中に含まれる不純物が付着することを抑制できる。

#### 【0082】

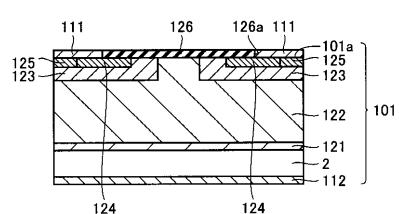

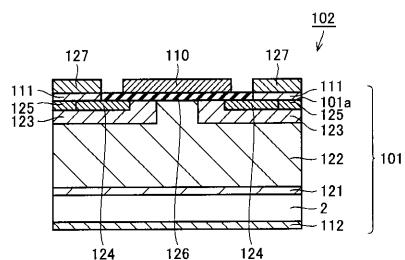

次に、図2および図8に示すように、エピタキシャルウェハ101において第1の酸化膜3が除去されることにより露出した表面101a(第2の表面)に、SiC半導体装置を構成する第2の酸化膜としてのゲート酸化膜126を形成する(ステップS6)。具体的には、図8に示すように、耐圧保持層122と、ウエル領域123と、ソース領域124と、コンタクト領域125との上を覆うように、ゲート酸化膜126を形成する。この形成はたとえば熱酸化(ドライ酸化)により行なうことができる。熱酸化は、たとえば $O_2$ 、 $O_3$ 、 $N_2O$ などの酸素元素を含む雰囲気中で高温に加熱する。熱酸化の条件は、たとえば、加熱温度が1200であり、また加熱時間が30分である。なお、ゲート酸化膜126の形成は、熱酸化に限定されず、たとえばCVD法、スパッタリング法などにより形成してもよい。ゲート酸化膜126は、たとえば50nmの厚みを有するシリコン酸化膜からなる。

#### 【0083】

第1の酸化膜3を除去するステップS5と、ゲート酸化膜126を形成するステップS6との間ににおいて、洗浄された表面101aを有するエピタキシャルウェハ101の温度

10

20

30

40

50

差を 500 以下に保持することが好ましい。この場合、ステップ S 5 とステップ S 6 との間でのエピタキシャルウェハの温度差が小さいため、スループットを向上できる。第 1 の酸化膜 3 を形成するステップ S 4 と、第 1 の酸化膜 3 を除去するステップ S 5 と、ゲート酸化膜 126 を形成するステップ S 6 とのそれぞれの間において、エピタキシャルウェハ 101 の温度差を 500 以下に保持することがより好ましい。この場合、ステップ S 4 開始からステップ S 6 終了までの間において、エピタキシャルウェハの温度差が小さいため、スループットを向上できる。

#### 【0084】

また、第 1 の酸化膜 3 を除去するステップ S 5 と、ゲート酸化膜 126 を形成するステップ S 6 との間において、洗浄された表面 101a を有するエピタキシャルウェハ 101 を 800 以上に保持することが好ましく、1000 以上に保持することがより好ましい。この場合、ステップ S 5 とステップ S 6 との間でのエピタキシャルウェハの温度の低下を抑制できるため、スループットを向上できる。また、第 1 の酸化膜 3 を形成するステップ S 4 と、第 1 の酸化膜 3 を除去するステップ S 5 と、ゲート酸化膜 126 を形成するステップ S 6 とのそれぞれの間において、エピタキシャルウェハ 100、101 を 800

10

以上に保持することが好ましく、1000 以上に保持することがより好ましい。この場合、ステップ S 4 開始からステップ S 6 終了までの間において、エピタキシャルウェハの温度の低下を抑制できるため、スループットを向上できる。

#### 【0085】

その後、窒素アニールを行なう（ステップ S 7）。具体的には、一酸化窒素（NO）雰囲気中のアニール処理が行われる。この処理の条件は、たとえば加熱温度が 1100 であり、加熱時間が 120 分である。この結果、耐圧保持層 122、ウエル領域 123、ソース領域 124、およびコンタクト領域 125 の各々と、ゲート酸化膜 126 との界面近傍に、窒素原子を導入することができる。

20

#### 【0086】

なお、この一酸化窒素を用いたアニール工程の後、さらに不活性ガスであるアルゴンガスを用いたアニール処理を行ってもよい。この処理の条件は、たとえば、加熱温度が 1100 であり、加熱時間が 60 分である。

#### 【0087】

この窒素アニール工程（ステップ S 7）の後、さらに、有機洗浄、酸洗浄、RCA 洗浄などの表面洗浄を行ってもよい。

30

#### 【0088】

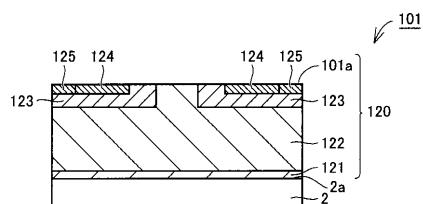

次に、図 2、図 9 および図 10 に示すように、電極を形成する（ステップ S 8）。まず、図 9 に示すソース電極 111 を、以下のように形成する。具体的には、ゲート酸化膜 126 上に、フォトリソグラフィ法を用いて、パターンを有するレジスト膜を形成する。このレジスト膜をマスクとして用いて、ゲート酸化膜 126 のうちソース領域 124 およびコンタクト領域 125 上に位置する部分をエッチングにより除去する。これによりゲート酸化膜 126 に開口部 126a を形成する。たとえば蒸着法により、この開口部 126a においてソース領域 124 およびコンタクト領域 125 の各々と接触するように導電体膜を形成する。次にレジスト膜を除去することにより、上記導電体膜のうちレジスト膜上に位置していた部分の除去（リフトオフ）が行われる。この導電体膜は、金属膜であってもよく、たとえばニッケル（Ni）からなる。このリフトオフの結果、ソース電極 111 が形成される。

40

#### 【0089】

なお、ここでアロイ化のための熱処理が行なわれることが好ましい。たとえば、不活性ガスであるアルゴン（Ar）ガスの雰囲気中、加熱温度 950 で 2 分の熱処理が行なわれる。

#### 【0090】

その後、図 10 に示すように、たとえば蒸着法により、ソース電極 111 上に上部ソース電極 127 を形成する。また、たとえば蒸着法により、SiC 基板 2 の裏面上にドレイ

50

ン電極 112 を形成する。

【0091】

またゲート電極 110 をたとえば以下のように形成する。予めゲート酸化膜 126 上の領域に位置する開口パターンを有するレジスト膜を形成し、当該レジスト膜の全面を覆うようにゲート電極を構成する導電体膜を形成する。そして、レジスト膜を除去することによって、ゲート電極となるべき導電体膜の部分以外の導電体膜を除去（リフトオフ）する。この結果、図 10 に示すように、ゲート酸化膜 126 上にゲート電極 110 を形成することができる。

【0092】

以上の工程（ステップ S1 ~ S8）を実施することにより、図 10 に示す SiC 半導体装置としての MOSFET 102 を製造することができる。

10

【0093】

なお、本実施の形態における導電型が入れ替えられた構成、すなわち p 型と n 型とが入れ替えられた構成を用いることもできる。

【0094】

また、MOSFET 102 を作製するために SiC 基板 2 を用いているが、基板の材料は SiC に限定されず、他の材料の結晶を用いて作製されてもよい。また、SiC 基板 2 が省略されてもよい。

【0095】

以上説明したように、本実施の形態における SiC 半導体装置の一例としての MOSFET 102 の製造方法は、第 1 の酸化膜 3 を除去するステップ S5 と、第 2 の酸化膜としての MOSFET 102 を構成するゲート酸化膜 126 を形成するステップ S6 との間ににおいて、SiC 半導体としてのエピタキシャルウェハ 100 は大気が遮断された雰囲気内に配置される。

20

【0096】

本実施の形態における SiC 半導体装置の一例としての MOSFET 102 の製造装置 10 は、エピタキシャルウェハ 101 を搬送可能に除去部 12 と第 2 の形成部 13 とを接続する第 1 の接続部 14 を備え、第 1 の接続部 14 におけるエピタキシャルウェハ 101 を搬送させる領域は、大気の遮断が可能である。

【0097】

30

本発明の MOSFET 102 の製造方法および製造装置によれば、第 1 の酸化膜を形成するステップ S4 において、エピタキシャルウェハ 100 の表面 100a に付着していたチタン（Ti）などの不純物、パーティクルなどを第 1 の酸化膜 3 に取り込むことができる。第 1 の酸化膜 3 を除去するステップ S5 により、エピタキシャルウェハ 100 の表面 100a に付着していた不純物、パーティクルなどを除去することができる。不純物、パーティクルなどが除去された表面 101a を有するエピタキシャルウェハ 101 を大気が遮断された雰囲気内（第 1 の接続部 14）に配置することで、大気中の不純物、パーティクルなどが洗浄後のエピタキシャルウェハ 101 の表面 101a に再付着することを抑制するので、ゲート酸化膜 126 形成前のエピタキシャルウェハ 101 の表面 101a を清浄に維持することができる。ゲート酸化膜 126 を形成するステップ S6 において、この状態のエピタキシャルウェハ 101 の表面 101a に、SiC 半導体装置を構成するゲート酸化膜 126 を形成することができるので、エピタキシャルウェハ 101 とゲート酸化膜 126 との界面に存在する不純物、パーティクルなどを低減できる。また、エピタキシャルウェハ 101 の表面 101a を清浄に維持できるので、表面 101a 上に形成するゲート酸化膜 126 中に存在する不純物、パーティクルなども低減することができる。さらに、ゲート酸化膜 126 の膜質も向上できる。したがって、MOSFET 102 の逆方向電圧印加時の耐圧を向上できるとともに、順方向電圧印加時の動作の安定性および長期信頼性を向上することができる。よって、特性を向上できる MOSFET 102 を製造することができる。

40

【0098】

50

本実施の形態では、エピタキシャルウェハの表面に第1の酸化膜3を形成し、第1の酸化膜3を除去することで表面を洗浄した後に、エピタキシャルウェハが大気暴露されることに起因した再汚染の可能性を低減している。SiCは安定な化合物であるので、エピタキシャルウェハ100の表面100aに第1の酸化膜3を形成することはSiCと比べて容易ではない。このため、SiC半導体であるエピタキシャルウェハ100の表面100aを洗浄した後に、エピタキシャルウェハ101を大気に暴露せずに次のステップ(ゲート酸化膜を形成するステップS6)に搬送することは、洗浄を簡略化でき、製造するSiC半導体装置の特性の向上に大きく寄与する。

#### 【0099】

また、大気が遮断された雰囲気の第1の接続部14内にエピタキシャルウェハ101を配置することで、第1の酸化膜3を除去する除去部12と第2の形成部13との間で互いにパーティクル、不純物などの汚染物質を持ち込みにくくなる。同様に、第1の酸化膜3を除去するステップS5およびゲート酸化膜126を形成するステップS6の各ステップ間からの汚染の持ち込みの可能性を低減できる。このため、除去部12および第2の形成部13の清浄化を維持できるので、製造するSiC半導体装置の特性の向上に大きく寄与する。

#### 【0100】

本実施の形態におけるSiC半導体装置の一例であるMOSFET102の製造方法において好ましくは、第1の酸化膜3を形成するステップS4と、第1の酸化膜3を除去するステップS5と、ゲート酸化膜126を形成するステップS6との間において、エピタキシャルウェハ100、101は大気が遮断された雰囲気内に配置される。

#### 【0101】

本実施の形態におけるSiC半導体装置の一例であるMOSFET102の製造装置10において好ましくは、エピタキシャルウェハ100を搬送可能に第1の形成部11と除去部12とを接続する第2の接続部15をさらに備え、第2の接続部15におけるエピタキシャルウェハ101を搬送させる領域は、大気の遮断が可能である。

#### 【0102】

これにより、エピタキシャルウェハの洗浄工程開始から終了まで大気に暴露されることを抑制でき、かつ洗浄工程終了からゲート酸化膜形成までエピタキシャルウェハ101を大気に暴露されることを抑制できる。このため、洗浄中および洗浄後のエピタキシャルウェハ100、101の表面100a、101aが再汚染されることを抑制できるので、特性をより向上できるSiC半導体装置を製造することができる。

#### 【0103】

なお、本実施の形態では、SiC半導体装置としてMOSFETの製造方法を例に挙げて説明したが、本発明は、表面を有するSiCエピタキシャルウェハと、この表面に形成されるSiC半導体装置を構成する酸化膜(SiC半導体装置として残る酸化膜)とを備えた半導体装置に適用できる。SiCエピタキシャルウェハは、表面からイオン注入されたものと、イオン注入されていないものとを含む。つまり、本発明は、たとえばMOSFETやIGBT(Insulated Gate Bipolar Transistor:絶縁ゲートバイポーラトランジスタ)などの絶縁ゲート型電界効果部を有する半導体装置や、JFET(Junction Field-Effect Transistor:接合電界効果トランジスタ)などの酸化膜を備えたSiC半導体装置全般に適用できる。

#### 【0104】

(実施の形態2)

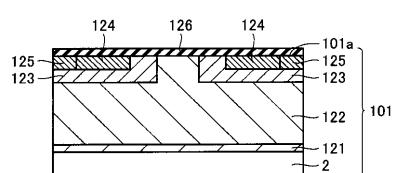

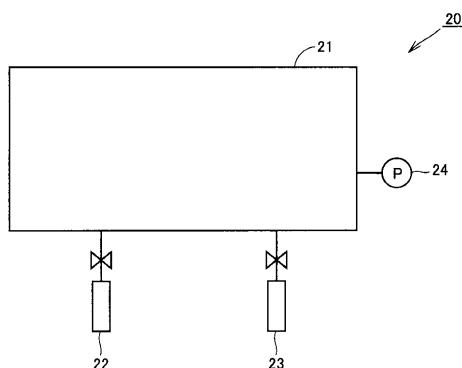

図11は、本発明の実施の形態2におけるSiC半導体装置の製造装置の模式図である。図11などを参照して、本実施の形態2におけるSiC半導体装置の製造装置を説明する。

#### 【0105】

図11に示すように、本実施の形態の製造装置20は、チャンバ21と、第1のガス供給部22と、第2のガス供給部23と、真空ポンプ24とを備えている。第1のガス供給

10

20

30

40

50

部 2 2、第 2 のガス供給部 2 3 および真空ポンプ 2 4 は、チャンバ 2 1 と接続されている。

【 0 1 0 6 】

チャンバ 2 1 は、内部にエピタキシャルウェハ 1 0 0、1 0 1 ( 図 5 ~ 図 7 参照 ) を収容する。チャンバ 2 1 は、たとえばプラズマ発生装置を用いることができる。

【 0 1 0 7 】

第 1 のガス供給部 2 2 は、エピタキシャルウェハ 1 0 0 に第 1 の酸化膜 3 ( 図 6 参照 ) を形成するため、および SiC 半導体装置 ( 本実施の形態では MOSFET 1 0 2 ) を構成する酸化膜 ( 本実施の形態ではゲート酸化膜 1 2 6 ) を形成する ( 図 8 参照 ) ために用いられるガスをチャンバ 2 1 に供給する。第 1 のガス供給部 2 2 は、たとえば O<sub>2</sub> を含むガスを供給する。

【 0 1 0 8 】

第 2 のガス供給部 2 3 は、エピタキシャルウェハ 1 0 0 に形成した第 1 の酸化膜 3 を除去するために用いられるガスをチャンバ 2 1 に供給する。第 2 のガス供給部 2 3 は、たとえば H<sub>2</sub> ガス、HCl ガスなどの Si と O<sub>2</sub> を還元するガスをチャンバ 2 1 に供給する。

【 0 1 0 9 】

真空ポンプ 2 4 は、チャンバ 2 1 の内部を真空にする。このため、第 1 のガス供給部 2 2 によりエピタキシャルウェハ 1 0 0 に第 1 の酸化膜 3 を形成した後に、チャンバ 2 1 の内部を真空にして、第 2 のガス供給部 2 3 により第 1 の酸化膜 3 を除去できる。また、第 1 の酸化膜 3 を除去した後に、チャンバ 2 1 の内部を真空にして、第 1 のガス供給部 2 2 により SiC 半導体装置を構成する第 2 の酸化膜 ( ゲート酸化膜 1 2 6 ) をエピタキシャルウェハ 1 0 1 に形成することができる。なお、真空ポンプ 2 4 は省略されてもよい。

【 0 1 1 0 】

なお、図 1 1 に示す製造装置 2 0 は、上記以外の様々な要素を含んでいてもよいが、説明の便宜上、これらの要素の図示および説明は省略する。

【 0 1 1 1 】

本実施の形態における SiC 半導体装置の製造方法は、図 9 に示す MOSFET 1 0 2 を製造し、基本的には実施の形態 1 と同様であるが、図 1 1 に示す製造装置 2 0 を用いる点において異なる。このため、第 1 の酸化膜を形成するステップ S 4 と第 1 の酸化膜を除去するステップ S 5 との間、および、第 1 の酸化膜を除去するステップ S 5 とゲート酸化膜 1 2 6 を形成するステップ S 6 との間ににおいて、エピタキシャルウェハはチャンバ 2 1 内に配置されるので、大気が遮断された雰囲気内に配置される。

【 0 1 1 2 】

また、第 1 の酸化膜 3 を除去するステップ S 5 で用いる装置を用いて第 2 の酸化膜としてのゲート酸化膜 1 2 6 を形成することができる。言い換えると、第 1 の酸化膜 3 を除去するステップ S 5 とゲート酸化膜 1 2 6 を形成するステップ S 6 とは同じ装置で実施される。このため、第 1 の酸化膜を除去するステップ S 5 とゲート酸化膜を形成するステップ S 6 との間ににおいて、エピタキシャルウェハの温度をできるだけ下げないように ( たとえば 500 以下に ) 維持することもできる。また、第 1 の酸化膜を除去するステップ S 5 とゲート酸化膜を形成するステップ S 6 との間ににおいて、エピタキシャルウェハの温度を 800 以上に、好ましくは 1000 以上に保持することもできる。

【 0 1 1 3 】

さらに、本実施の形態では、第 1 の酸化膜 3 を形成するステップ S 4 と、第 1 の酸化膜 3 を除去するステップ S 5 と、ゲート酸化膜 1 2 6 を形成するステップ S 6 とは、同じ装置で実施される。このため、第 1 の酸化膜 3 を形成するステップ S 4 と第 1 の酸化膜 3 を除去するステップ S 5 との間、および、第 1 の酸化膜 3 を除去するステップ S 5 とゲート酸化膜 1 2 6 を形成するステップ S 6 との間ににおいて、エピタキシャルウェハの温度をできるだけ下げないように ( たとえば 500 以下に ) 維持することもできる。また、第 1 の酸化膜を形成するステップ S 4 と第 1 の酸化膜を除去するステップ S 5 との間、および、第 1 の酸化膜を除去するステップ S 5 とゲート酸化膜を形成するステップ S 6 との間に

10

20

30

40

50

おいて、エピタキシャルウェハの温度を 800 以上、好ましくは 1000 以上に保持することもできる。

【 0 1 1 4 】

また、第1の酸化膜3を形成するステップS4終了後、および、第1の酸化膜3を除去するステップS5終了後、チャンバ21の内部を真空ポンプ24で真空引き（たとえば0.1Pa以下まで真空引き）をすることが好ましい。言い換えると、第1の酸化膜3を形成するステップS4と第1の酸化膜3を除去するステップS5との間のガス切替時、および、第1の酸化膜3を除去するステップS5とゲート酸化膜126を形成するステップS6との間のガス切替時に、雰囲気の圧力を減圧（たとえば0.1Pa以下まで減圧）することが好ましい。これにより、チャンバ21内の残留ガスを低減することができるので、第2または第1のガス供給部23、22を用いた置換ガス導入時の気相反応によるパーティクルの発生を低減できる。たとえば第1の酸化膜3がSiO<sub>x</sub>の場合、第1の酸化膜3を除去するステップS5とゲート酸化膜126を形成するステップS6との切替時、第1の酸化膜3を除去するステップS5で分解されたSiを低減することで、この残留するSiと、ゲート酸化膜126を形成するために導入するO<sub>2</sub>ガスとが反応してなるSiO<sub>2</sub>パーティクルの発生を低減できる。このため、エピタキシャルウエハの表面をより清浄にすることができる。つまり、ガス切替に伴うパーティクル発生を抑制できる。

10

[ 0 1 1 5 ]

以上より、本実施の形態におけるSiC半導体の製造装置20によれば、第1の酸化膜3を除去し、かつエピタキシャルウエハ100において第1の酸化膜3が除去されることにより露出した表面に、SiC半導体装置としてのMOSFET102を構成する第2の酸化膜としてのゲート酸化膜126)を形成するためのチャンバ21を備えている。このため、不純物、パーティクルなどが除去されたエピタキシャルウエハ101を大気が遮断された雰囲気内(チャンバ21内)に配置することで、大気中の不純物、パーティクルなどがエピタキシャルウエハ101の表面101aに再付着することを抑制できるので、ゲート酸化膜126形成前のエピタキシャルウエハ101の表面101aを清浄に維持することができる。ゲート酸化膜126を形成するステップS6において、この状態のエピタキシャルウエハ101の表面101aに、SiC半導体装置としてのMOSFET102を構成するゲート酸化膜126を形成することができるので、エピタキシャルウエハ101とゲート酸化膜126との界面に存在する不純物、パーティクルなどを低減できる。また、エピタキシャルウエハ101の表面101aを清浄に維持できるので、ゲート酸化膜126中に存在する不純物、パーティクルなども低減することができる。さらに、表面101a上に形成するゲート酸化膜126の膜質も向上できる。したがって、MOSFET102の逆方向電圧印加時の耐圧を向上できるとともに、順方向電圧印加時の動作の安定性および長期信頼性を向上することができる。よって、特性を向上できるMOSFET102を製造することができる。

20

〔 0 1 1 6 〕

なお、本実施の形態では、エピタキシャルウエハ100の表面100aに第1の酸化膜3を形成するための第1の形成部と、第1の酸化膜3を除去し、かつエピタキシャルウエハ100において第1の酸化膜3が除去されることにより露出した表面101aに、MOSFET102を構成するゲート酸化膜126を形成するための第2の形成部とは同じである製造装置20を例に挙げて説明した。しかし、本発明は、第1の形成部と第2の形成部とは、異なる装置であってもよい。つまり、本発明の製造装置は、第2の形成部が図11に示す構成であり、第2の形成部と別に第1の形成部が配置されていてもよい。この場合、製造装置は、SiC半導体を搬送可能に第1の形成部と第2の形成部とを接続する接続部をさらに備え、この接続部におけるSiC半導体を搬送させる領域は、大気の遮断が可能であることが好ましい。

30

[ 0 1 1 7 ]

以上のように本発明の実施の形態について説明を行なったが、各実施の形態の特徴を適宜組み合わせることも当初から予定している。また、今回開示された実施の形態はすべて

50

の点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した実施の形態ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0118】

2 SiC 基板、2a, 100a, 101a 表面、3 第1の酸化膜、10, 20

製造装置、11 第1の形成部、12 除去部、13 第2の形成部、14 第1の接続部、15 第2の接続部、21 チャンバ、22 第1のガス供給部、23 第2のガス供給部、24 真空ポンプ、100, 101 エピタキシャルウエハ、102 MOSFET、110 ゲート電極、111, 127 ソース電極、112 ドレイン電極、120 エピタキシャル層、121 バッファ層、122 耐圧保持層、123 ウエル領域、124 ソース領域、125 コンタクト領域、126 ゲート酸化膜、126a 開口部、129 ドレイン領域、131 p型SiC層。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

## フロントページの続き

(51)Int.Cl.

F I

|         |        |         |

|---------|--------|---------|

| H 0 1 L | 21/316 | S       |

| H 0 1 L | 21/316 | U       |

| H 0 1 L | 21/316 | P       |

| H 0 1 L | 21/304 | 6 4 5 C |

| H 0 1 L | 21/304 | 6 4 5 Z |

| H 0 1 L | 21/304 | 6 4 7 Z |

| H 0 1 L | 29/78  | 6 5 8 E |

| H 0 1 L | 29/78  | 3 0 1 B |

| H 0 1 L | 29/78  | 3 0 1 G |

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 増田 健良

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社 大阪製作所内

(72)発明者 和田 圭司

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社 大阪製作所内

(72)発明者 伊藤 里美

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社 大阪製作所内

(72)発明者 日吉 透

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社 大阪製作所内

審査官 宮本 靖史

(56)参考文献 特開2009-064955 (JP, A)

特開2002-093800 (JP, A)

特開2007-053227 (JP, A)

特開2002-075984 (JP, A)

特開2006-251744 (JP, A)

特開2000-349081 (JP, A)

特開平11-186256 (JP, A)

特開2008-098200 (JP, A)

特開昭60-066866 (JP, A)

特開2008-321707 (JP, A)

特開平09-052796 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 3 1 6 - 2 1 / 3 1 8

H 0 1 L 2 1 / 2 0 5

H 0 1 L 2 1 / 3 1

H 0 1 L 2 1 / 3 0 4

H 0 1 L 2 1 / 3 0 2

H 0 1 L 2 1 / 3 0 6 5

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 9 / 1 2

H 0 1 L 2 9 / 7 8

C 2 3 C 1 6 / 4 2

C 3 0 B 2 9 / 3 6