(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-104248

(P2014-104248A)

(43) 公開日 平成26年6月9日(2014.6.9)

(51) Int.Cl.

**A61F 2/14 (2006.01)**

**H01L 21/8234 (2006.01)**

**H01L 27/088 (2006.01)**

**H01L 27/06 (2006.01)**

**A61N 1/36 (2006.01)**

F 1

A 6 1 F 2/14

H 0 1 L 27/08 1 0 2 J

H 0 1 L 27/06 1 0 2 A

A 6 1 N 1/36

テーマコード(参考)

4 C 0 5 3

4 C 0 9 7

5 F 0 4 8

審査請求 未請求 請求項の数 13 O L (全 17 頁)

(21) 出願番号

特願2012-260786 (P2012-260786)

(22) 出願日

平成24年11月29日 (2012.11.29)

(71) 出願人 000135184

株式会社ニデック

愛知県蒲郡市拾石町前浜34番地14

(72) 発明者 鐘堂 健三

愛知県蒲郡市拾石町前浜34番地14 株式会社ニデック拾石工場内

F ターム (参考) 4C053 JJ01 JJ11 JJ13 JJ21

4C097 AA24 BB01 BB02 CC01 CC08

SA10

5F048 AA01 AB04 AB10 AC01 AC03

BA01 BE09 BF15 BF16 BF18

(54) 【発明の名称】半導体回路及び該半導体回路を備える生体組織刺激装置

## (57) 【要約】

【課題】 回路を小型に出来る半導体回路及び該半導体回路を備える生体組織刺激装置を提供する。

【解決手段】 半導体回路は、第1電源ラインと第1接地ラインを持つ第1回路の第1レベルの信号を、第2電源ラインと第2接地ラインを持つ第2回路の第2レベルの信号に変換するレベルシフト回路は、第1電源ラインに接続されて電流を出力する第1電流源と、第1レベルの信号に基づく導通と非導通の切り換えによって、第1電流源からの電流の出力の有無を切り換える高耐圧トランジスタと、電流を電圧に変換して前記第2レベルの信号を得る電流電圧変換手段と、電流電圧変換手段で変換される電圧が第2電源ラインの電圧以下となるように、高耐圧トランジスタを介して供給された電流を調整する第1低耐圧トランジスタからなるクランプ回路とを持つ。

【選択図】

図 1

**【特許請求の範囲】****【請求項 1】**

第1電源ラインと第1接地ラインを持つ第1回路の第1レベルの信号を、第2電源ラインと第2接地ラインを持つ第2回路の第2レベルの信号に変換するレベルシフト回路を備える半導体回路であって、

前記レベルシフト回路は、

前記第1電源ラインに接続されて電流を出力する第1電流源と、

前記第1レベルの信号に基づく導通と非導通の切り換えによって、前記第1電流源からの電流の出力の有無を切り換える高耐圧トランジスタと、

前記電流を電圧に変換して前記第2レベルの信号を得る電流電圧変換手段と、

前記電流電圧変換手段で変換される電圧が前記第2電源ラインの電圧以下となるよう、前記高耐圧トランジスタを介して供給された電流を調整する第1低耐圧トランジスタとを備えるクランプ回路と、

を備えることを特徴とする半導体回路。

**【請求項 2】**

前記クランプ回路において、

前記第1低耐圧トランジスタは、前記高耐圧のトランジスタと同極性であって、

前記第1低耐圧トランジスタの第1ソースは前記高耐圧トランジスタのドレインに接続され、前記第1低耐圧トランジスタの第1ドレインは前記電流電圧変換手段に接続され、前記第1低耐圧トランジスタの前記第1ドレインから出力された電流が前記電流電圧変換手段で電圧に変換される請求項1に記載の半導体回路。

**【請求項 3】**

前記クランプ回路は、

前記第1低耐圧トランジスタと同極性の第2低耐圧トランジスタであって、

前記第1ソースと前記第2低耐圧トランジスタの第2ソースを接続し、前記第2低耐圧トランジスタの第2ドレインを前記第2接地ラインに接続することで、

前記第1電流源から供給される電流のうち前記第1低耐圧トランジスタへの流入量を超えた電流を流入させる前記第2低耐圧トランジスタと、を備える請求項2に記載の半導体回路。

**【請求項 4】**

前記クランプ回路は、

前記第2接地ラインに接続される第2電流源と、

前記第1低耐圧トランジスタと同極性であって、第3ソースが前記第2電源ラインに接続され、第3ゲートならびに第3ドレインが共通に接続された第3低耐圧トランジスタと、

前記第2電源ラインより前記クランプ回路の電位を低くする電位下降手段であって、一端が前記第3低耐圧トランジスタの前記第3ゲートと第3ドレインの共通接続点に接続され、他端が前記第2電流源に接続される電位下降手段と、を備える請求項3に記載の半導体回路。

**【請求項 5】**

前記第1回路と前記第2回路の接続と非接続を切り換えるスイッチ手段を備え、

前記レベルシフト回路は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに、前記第1レベルの信号を前記第2レベルの信号に変換する請求項1～4のいずれかに記載の半導体回路。

**【請求項 6】**

前記第1接地ラインと前記第2接地ラインの電位は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに等しくなる請求項1～5のいずれかに記載の半導体回路。

**【請求項 7】**

前記半導体回路は、

10

20

30

40

50

前記第1レベルの信号がオンの時に前記高耐圧トランジスタを導通させて前記電流を前記クランプ回路に流入させ、前記第1レベルの信号がオフの時に前記高耐圧トランジスタを非導通として、前記電流を前記クランプ回路に流入させない請求項1～6のいずれかに記載の半導体回路。

【請求項8】

前記第1低耐圧トランジスタは、前記高耐圧トランジスタよりも小型である請求項1～7に記載のいずれかの半導体回路。

【請求項9】

前記第2低耐圧トランジスタは前記高耐圧トランジスタよりも小型である請求項3～7に記載のいずれかの半導体回路。

10

【請求項10】

前記電流電圧変換手段は抵抗である請求項1～9のいずれかに記載の半導体回路。

【請求項11】

前記電位下降手段は抵抗である請求項4～9のいずれかに記載の半導体回路。

【請求項12】

前記第1電源ラインに交流電力を供給する交流電源と、

前記交流電力を直流電力に整流する整流回路を備え、前記第2電源ラインに直流電力を供給する直流電源と、

を備える請求項1～11のいずれかに記載の半導体回路を備える生体組織刺激装置。

20

【請求項13】

生体組織を電気刺激する複数の刺激電極と、

前記刺激電極から出力される刺激電流を制御するデマルチプレクサと、

前記信号に基づき前記デマルチプレクサの動作制御をする制御手段と、

を備える請求項12に記載の生体組織刺激装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路間で異なる電圧レベルの論理信号を伝達する半導体回路、及び該半導体回路を備える生体組織刺激装置に関する。

【背景技術】

30

【0002】

半導体回路が持つ複数の回路が、異なる電圧レベルの論理信号で動作する場合、各回路間で論理信号を正しく伝達する為に、論理信号のレベルの違いを補償するレベルシフト回路が用いられる（特許文献1参照）。例えば、電極から出力された刺激電流で網膜を構成する細胞を電気刺激し視覚の再生を試みる視覚再生補助装置では、装置に電力を供給するための交流電源を持つ回路（第1回路）や、電極に刺激電流を供給するための回路（第2回路）など、異なる電圧レベルで信号が伝達される複数の回路が用意されている（特許文献2参照）。またこの種の生体組織刺激装置では、刺激電流を出力するときに、他の回路（第1回路等）で発生した不正電流が電極から出力されてしまうと生体内の電荷バランスを崩す原因となることから、刺激電流の出力時、第2回路に対して第1回路等の他の回路を電気的に切り離している。つまり、刺激電流の出力と、電力と制御信号の供給等の他の動作が、時分割で分離して行われることが好ましいとされている（特許文献3参照）。

40

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特表2007 531417号公報

【特許文献2】特表2005 516705号公報

【特許文献2】特開2012 120590号公報

【発明の概要】

【発明が解決しようとする課題】

50

## 【0004】

しかし回路が電気的に切り離されると、切り離された回路の電位がフローティングとなり変動しうる。切り離された回路の電位が上昇すると回路の破損につながる。一方、生体組織刺激装置のように、フローティングによる電位変動の程度を予測することが困難な装置では、図7の従来技術に示されるように、回路の電位変動に十分に耐え得る耐圧を確保するため、複数の大型の高耐圧トランジスタを用いてレベルシフト回路が構成されている。しかし生体組織刺激装置のように、装置(回路)が置かれるスペースが限られている場合、大型の高耐圧トランジスタの組み合わせで構成されたレベルシフト回路を用いることは、装置の小型化に不利になる課題がある。

10

## 【0005】

本発明は上記従来技術の問題点に鑑み、回路を小型に出来る半導体回路及び該半導体回路を備える生体組織刺激装置を提供することを技術課題とする。

## 【課題を解決するための手段】

## 【0006】

上記課題を解決するために、本発明は以下のような構成を備えることを特徴とする。

## 【0007】

(1) 第1電源ラインと第1接地ラインを持つ第1回路の第1レベルの信号を、第2電源ラインと第2接地ラインを持つ第2回路の第2レベルの信号に変換するレベルシフト回路を備える半導体回路であって、前記レベルシフト回路は、前記第1電源ラインに接続されて電流を出力する第1電流源と、前記第1レベルの信号に基づく導通と非導通の切り換えによって、前記第1電流源からの電流の出力の有無を切り換える高耐圧トランジスタと、前記電流を電圧に変換して前記第2レベルの信号を得る電流電圧変換手段と、前記電流電圧変換手段で変換される電圧が前記第2電源ラインの電圧以下となるように、前記高耐圧トランジスタを介して供給された電流を調整する第1低耐圧トランジスタとを備えるクランプ回路と、を備えることを特徴とする半導体回路。

20

(2) 前記クランプ回路において、前記第1低耐圧トランジスタは、前記高耐圧のトランジスタと同極性であって、前記第1低耐圧トランジスタの第1ソースは前記高耐圧トランジスタのドレインに接続され、前記第1低耐圧トランジスタの第1ドレインは前記電流電圧変換手段に接続され、前記第1低耐圧トランジスタの前記第1ドレインから出力された電流が前記電流電圧変換手段で電圧に変換される(1)に記載の半導体回路。

30

(3) 前記クランプ回路は、前記第1低耐圧トランジスタと同極性の第2低耐圧トランジスタであって、前記第1ソースと前記第2低耐圧トランジスタの第2ソースを接続し、前記第2低耐圧トランジスタの第2ドレインを前記第2接地ラインに接続することで、前記第1電流源から供給される電流のうち前記第1低耐圧トランジスタへの流入量を超えた電流を流入させる前記第2低耐圧トランジスタと、を備える(2)に記載の半導体回路。

(4) 前記クランプ回路は、前記第2接地ラインに接続される第2電流源と、前記第1低耐圧トランジスタと同極性であって、第3ソースが前記第2電源ラインに接続され、第3ゲートならびに第3ドレインが共通に接続された第3低耐圧トランジスタと、前記第2電源ラインより前記クランプ回路の電位を低くする電位下降手段であって、一端が前記第3低耐圧トランジスタの前記第3ゲートと第3ドレインの共通接続点に接続され、他端が前記第2電流源に接続される電位下降手段と、を備える(3)に記載の半導体回路。

40

(5) 前記第1回路と前記第2回路の接続と非接続を切り換えるスイッチ手段を備え、前記レベルシフト回路は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに、前記第1レベルの信号を前記第2レベルの信号に変換する(1)～(4)のいずれかに記載の半導体回路。

(6) 前記第1接地ラインと前記第2接地ラインの電位は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに等しくなる(1)～(5)のいずれかに記載の半導体回路。

(7) 前記半導体回路は、前記第1レベルの信号がオンの時に前記高耐圧トランジスタ

50

を導通させて前記電流を前記クランプ回路に流入させ、前記第1レベルの信号がオフの時に前記高耐圧トランジスタを非導通として、前記電流を前記クランプ回路に流入させない(1)～(6)のいずれかに記載の半導体回路。

(8) 前記第1低耐圧トランジスタは、前記高耐圧トランジスタよりも小型である(1)～(7)に記載のいずれかの半導体回路。

(9) 前記第2低耐圧トランジスタは前記高耐圧トランジスタよりも小型である(3)～(7)に記載のいずれかの半導体回路。

(10) 前記電流電圧変換手段は抵抗である(1)～(9)のいずれかに記載の半導体回路。

(11) 前記電位下降手段は抵抗である(4)～(9)のいずれかに記載の半導体回路。

10

(12) 前記第1電源ラインに交流電力を供給する交流電源と、前記交流電力を直流電力に整流する整流回路を備え、前記第2電源ラインに直流電力を供給する直流電源と、を備える(1)～(11)のいずれかに記載の半導体回路を備える生体組織刺激装置。

(13) 生体組織を電気刺激する複数の刺激電極と、前記刺激電極から出力される刺激電流を制御するデマルチプレクサと、前記信号に基づき前記デマルチプレクサの動作制御をする制御手段と、を備える(12)に記載の生体組織刺激装置。

#### 【発明の効果】

#### 【0008】

回路を小型に出来る半導体回路及び該半導体回路を備える生体組織刺激装置を提供できる。

20

#### 【発明を実施するための形態】

#### 【0009】

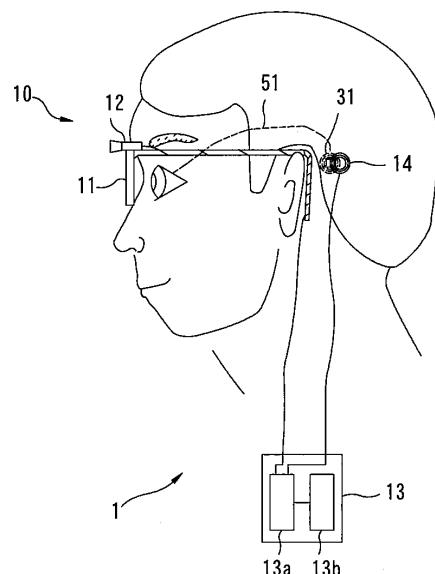

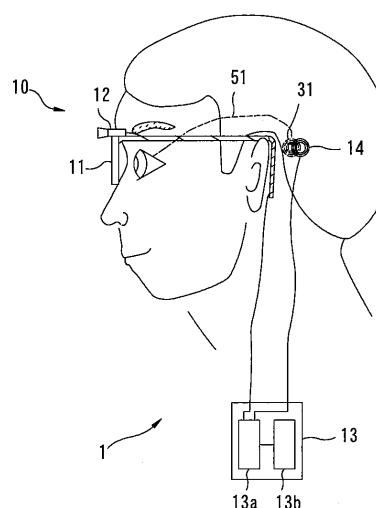

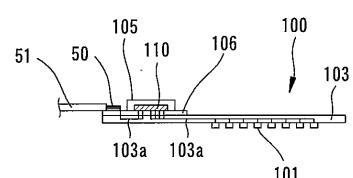

本開示の半導体回路及び該半導体回路を備える生体組織刺激装置を図面に基づき説明する。なお以下では生体組織刺激装置として視覚再生補助装置を例に挙げて説明する。図1は視覚再生補助装置の外観図である。図2は視覚再生補助装置の体内装置の説明図であり、図2(a)は体内装置20の外観図、図2(b)は刺激ユニット100の断面図である。

#### 【0010】

視覚再生補助装置1は、外界を撮影する体外装置10と、網膜を構成する細胞に電気刺激を与え視覚の再生を促す体内装置20からなる。体外装置10は、患者が掛ける眼鏡11と、眼鏡11に取り付けられるCCDカメラ等からなる撮影装置12と、外部デバイス13、送信手段14等で構成される。外部デバイス13は、CPU等の演算処理回路を持つデータ変調手段13a、視覚再生補助装置1(体外装置10及び体内装置20)に電力供給をするバッテリー13bを備える。データ変調手段13aは、撮影装置12で撮影した被写体像を画像処理して、視覚再生のための制御信号を生成する。またデータ変調手段13aは、振幅変調等によって、制御信号を電力に重畠して電磁波を生成する。電磁波は送信手段14の1次コイルで体内装置20側に伝送(無線送信)される。送信手段14の中心には体内装置20の受信部31との位置を固定するための磁石(図示を略す)がある。

30

#### 【0011】

体内装置20は、体外装置10から送信された電磁波を受信する受信ユニット30と、網膜を構成する細胞を電気刺激する刺激ユニット100を持つ。受信ユニット30は、受信部31、制御部32、対向電極34を持つ。受信部31と制御部32は基板33に組み込まれる。受信部31は体外装置10からの電磁波を受信する2次コイルを持つ。制御部32は、受信部31で受信された電磁波から、制御信号と電力を抽出する。抽出された電力は刺激ユニット100を駆動する電源Vacと、電極101に電流を供給する電流源Iacに用いられる。つまり受信ユニット30は、刺激ユニット100及び体内装置20全體に電力供給をする電力供給ユニットになる。対向電極34は網膜を介して各電極101に対向する位置に置かれる。なお受信ユニット30にも送信手段14との位置固定用の磁

40

50

石が設けられる。

【0012】

刺激ユニット100は、複数の電極101、眼球に沿って配置される基板103、刺激電流を出力する電極101を指定する刺激制御部110を持つ。電極101と刺激制御部110は基板103に組み込まれる。

【0013】

電極101は生体適合性が高い導体で形成される。例えば金や白金等の貴金属で形成される。基板103は、眼球(層状の眼組織内)に設置されるため、眼球の形状に沿って、層間(層内)に長期埋植されても患者の負担が少ないことが好ましい。例えば基板103は、生体適合性が高く、所要厚で湾曲可能な材料で長板状に加工される。基板内部に配線される複数のリード線103aは、各電極101と刺激制御部110を電気的に接続する。

10

【0014】

刺激制御部110は、制御部32から送信された電極指定信号等に基づき、双極性パルスを各電極101に振り分けるデマルチプレクサ120を持つ(図3参照)。デマルチプレクサ120は複数の回路が実装された周知のモノリシックIC(集積回路)である。モノリシックICは所要の許容電圧範囲内で駆動されることが安定動作の為に必要となる。デマルチプレクサ120の構成及び動作制御の詳細な説明は後述する。

【0015】

刺激制御部110は、蓋部材105と設置台106でハーメチックシール(密封)され、設置台106を介して基板103上に実装される。刺激制御部110は、半導体基板上に集積回路を機能させるパターン配線が形成された面が設置台106に接合される。設置台106は、絶縁性、気密性及び生体適合性を持つ素材で形成される。例えば設置台106は、セラミックスで平板状に形作られる。また設置台106には、刺激制御部110が持つパターン配線の端子部分と電気的に接続するための配線が、設置台106を貫通するように形成されている。蓋部材105は、生体適合性と、高気密性を持つ金属等の素材で形成され、刺激制御部110が収まる空間を持つ。なお蓋部材105と設置台106は、刺激制御部110を密封するために、設置台106の接合箇所にメタライズ処理で金属層を形成して、蓋部材105と設置台106の金属同士を接合する。

20

【0016】

受信ユニット30と刺激ユニット100はリード51で電気的に接続される。リード51は絶縁性と生体適合性を持つ樹脂の内側に複数の導線50を内包する。樹脂にはシリコーン、ポリイミド、パリレン等が用いられる。またリード51内の導線50も生体適合性が高いものが使用されることが好ましく、白金、金等が材料に用いられる。

30

【0017】

リード51に内包された複数の導線50は、刺激ユニット100に電力を供給するために電源V<sub>ac</sub>に接続される導線(電力線)50aと、電極101に双極性パルス(電流)を供給するために電流源I<sub>ac</sub>に接続される導線50bを持つ。

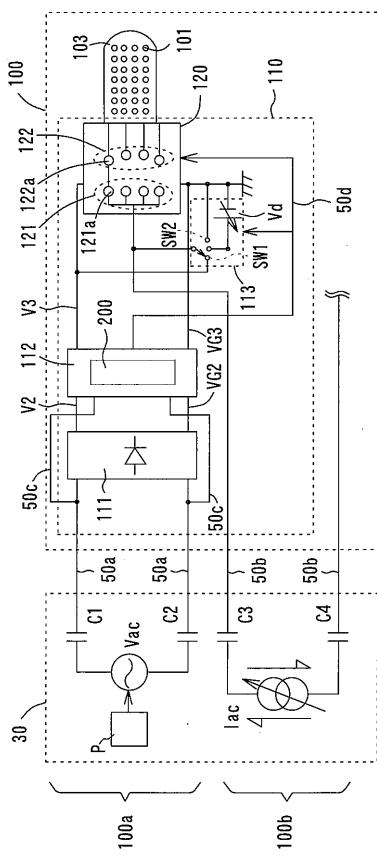

【0018】

次に体内装置20の回路構成について説明する。図3は体内装置20の制御回路の説明図である。体内装置20は刺激ユニット100に電力と制御信号を供給する電力供給回路100aと、刺激ユニット100の電極101から出力させる刺激電流を供給する刺激電流供給回路100bを持つ。電力供給回路100aは、電源V<sub>ac</sub>と、体内装置20に制御信号を供給する信号源Pと、コンデンサC1,C2と、整流回路111と、復調回路(デコーダ)112と、電位調整回路113を持つ。なお電源V<sub>ac</sub>、信号源P、コンデンサC1,C2は受信ユニット30側に設けられており、整流回路111、デコーダ112、電位調整回路113は刺激ユニット100側に設けられている。電源V<sub>ac</sub>の出力端にはコンデンサC1,C2が接続され、各コンデンサC1,C2は導線50aを介して整流回路111に接続される。また整流回路111から出力される直流電力は、電源ラインV2及び接地ラインVG2を介してデコーダ112に供給される。デコーダ112からの出

40

50

力は電源ラインV3及び接地ラインVG3を介してデマルチブレクサ120側に供給される。なお電源ラインV2とV3は後述するスイッチSW4(図5参照)によって接続の有無が切り換えられる。接地ラインVG2とVG3は後述するスイッチSW5(図5参照)によって接続の有無が切り換えられる。なおスイッチSW4, SW5が共に接続されているとき、電源ラインV2とV3の電位、接地ラインVG2とVG3の電位は同電位となる。一方、スイッチSW4, SW5が非接続のとき、電源ラインV2とV3、接地ラインVG2とVG3は異なる電位になり得る。なお以降の説明では、スイッチSW4, SW5を介して入力側の回路を第1回路112a、出力側の回路を第2回路112bとして説明する(図5参照)。なお図示は省略するが、電源ラインV3の電位を増幅するための増幅器が、デコーダ112とデマルチブレクサ120との間に設けられていても良い。

10

#### 【0019】

導線(信号線)50cは、導線50aに重畠されている制御信号(二進数)をデコーダ112へ導く。デコーダ112は、信号線50cから制御信号を抽出する。またデコーダ112は内部にレベルシフト回路200を持ち、抽出された制御信号のレベルを、第1回路112a側の第1レベルから、第2回路112b側の第2レベルにシフトさせる。本実施形態のレベルシフト回路200の詳細な説明は後述する。なおレベルシフト回路200で第2レベルにシフトされ、デコーダ112から出力された制御信号は、導線(信号線)50dを介してデマルチブレクサ120、電位調整回路113等に供給される。

#### 【0020】

電源Vacは、電力に制御信号が重畠された変調波を出力する。コンデンサC1, C2は変調波に含まれる直流成分をカットする。整流回路111は交流電力を直流電力に整流する。整流回路111にはダイオード等の周知の非線形素子が使用される。

20

#### 【0021】

刺激電流供給回路100bは、刺激電流を供給する電流源Iacと、電流源Iacの各出力端に接続されるコンデンサC3, C4と、各コンデンサC3, C4に接続される導線50bと、デマルチブレクサ120を介して導線50bと接続される電極101を備える。なお電流源IacとコンデンサC3, C4は受信ユニット30側に設けられ、電極101は刺激ユニット100側に設けられる。

#### 【0022】

電流源Iacからは正負に極性を持つ刺激電流が出力される。コンデンサC3, C4は刺激電流に含まれる直流成分をカットする。刺激制御部110側に入力された刺激電流は、デマルチブレクサ120に入力される。デマルチブレクサ120は、複数の入力端子121と出力端子122を持つ。一対の入力端子121と出力端子122の導通状態と非導通状態の切り換えによって、刺激電流が出力される電極101が指定される。なお刺激電流は正負の両方に極性を持つ双極性パルスとする。なお図3では入力端子121aと出力端子122aが電気的に接続された例が示されている。

30

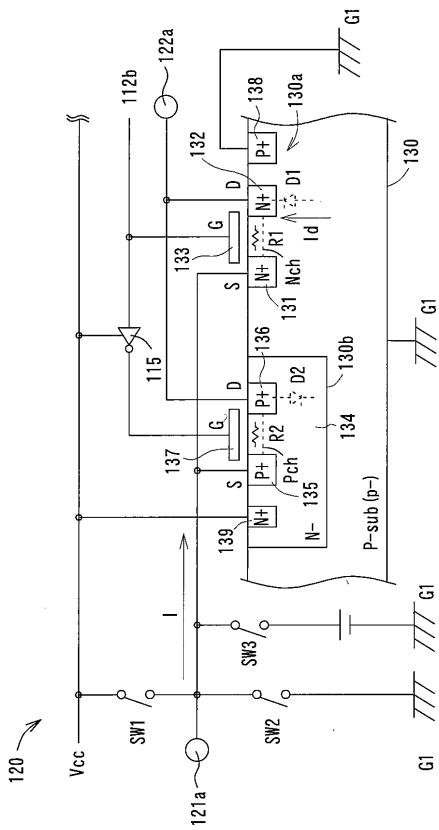

#### 【0023】

図4において、デマルチブレクサ120は、P型半導体基板130の所要領域に形成されるNチャネルトランジスタ領域(NMOS領域)130aと、Pチャネルトランジスタ領域(PMOS領域)130bの組み合わせを複数個持つ。一対のNMOS領域130aとPMOS領域130bのONとOFFの切り換えによって、対応する電極101からの刺激電流の出力の有無が切り換えられる。

40

#### 【0024】

NMOS領域130aは、半導体基板130の表面の所要領域に形成されるN型不純物拡散領域(ソースS)131と、N型不純物拡散領域(ドレインD)132と、N型不純物拡散領域131、132の間のP型半導体基板130表面上に絶縁膜(図示を略す)を介在させて形成されるゲート電極133を備える。またNMOS領域130aには、P型半導体基板130に電気的接続を与える為のP型不純物拡散領域138が設けられる。

#### 【0025】

PMOS領域130bは、P型半導体基板130の表面に形成されたN型ウェル134

50

内に形成される。PMOS領域130bは、N型ウェル134表面に形成されたP型不純物拡散領域(ソースS)135と、P型不純物拡散領域(ドレインD)136と、P型不純物拡散領域135、136の間のN型ウェル134表面上に絶縁膜(図示を略す)を介在させて形成されるゲート電極137から形成される。またPMOS領域130bのN型ウェル134内には電気的接続を与えるN型不純物拡散領域139が設けられる。

#### 【0026】

N型不純物拡散領域139は電源ラインVccに接続され、P型不純物拡散領域138は基準電位VGNPに接続される。これにより基板130と、N型ウェル134間に逆バイアスが与えられる。P型不純物拡散領域(ソースS)135とN型不純物拡散領域(ソースS)131は入力端子121aに接続される。N型不純物拡散領域(ドレインD)132とP型不純物拡散領域136は出力端子122aに接続される。ゲート電極133、137は、図示を略す制御回路を介してデコーダ112の出力端に接続される。なおゲート電極133とゲート電極137の間には、電位を反転させる周知の反転素子115が設けられる。

10

#### 【0027】

以上の構成により、基板130とN型ウェル134が逆バイアスされた状態で、デコーダ112からHighレベルの信号が入力されると、NMOS領域130aのゲート(G)133にスレッシュホールドよりも高い電位が加えられる。これによりNMOS領域130aのソース(S)131とドレイン(D)132間にNチャネルNchが形成され、電流が導通可能になる。一方、PMOS領域130bのゲート(G)137には、反転素子115を介してスレッシュホールドよりも低い電位が加えられる。これによりソース(S)135とドレイン(D)136間にPチャネルPchが形成され、電流が導通可能になる。

20

#### 【0028】

一方、デコーダ112からLowレベルの信号が入力されると、NMOS領域130aのゲート(G)133にスレッシュホールドよりも低い電位が加えられ、NMOS領域130aのソース(S)131とドレイン(D)132間が開放される。また反転素子115を介して、PMOS領域130bのゲート(G)137にスレッシュホールドよりも高い電位が加えられ、PMOS領域130bのソース(S)135とドレイン(D)136間が開放される。以上のようにして、一対のPMOS領域130bとNMOS領域130aが導通もしくは開放の状態になると、デマルチプレクサ120の選択された出力端子122を介して、対応する電極101から刺激電流(双極性パルス)が出力される。

30

#### 【0029】

ところでPMOS領域130bのソース(S)135とドレイン(D)136との間、NMOS領域130aのソース(S)131とドレイン(D)132との間には、電流の極性にかかわらず内部抵抗が存在し、デマルチプレクサ120内では内部抵抗による電圧降下が生じる。一方、同一の基板130にNMOS領域130aとPMOS領域130bの両方が形成されていると、各P領域と各N領域の間に寄生ダイオードが形成される。例えば、P型の基板130とN型のソース131又はドレイン132間に寄生ダイオードD1が形成される。N型ウェル134とP型のソース135又はドレイン136の間に寄生ダイオードD2が形成される。これらの寄生ダイオードD1、D2は、デマルチプレクサ120が、基準電位VGNPと電源ラインVccの間の許容電圧範囲内で駆動されている状態では、逆バイアス状態が保たれる。

40

#### 【0030】

しかし交流電流が供給されるリード51を介して、受信ユニット30と刺激ユニット100の電位(直流電位)が独立している場合には、生体内の受信ユニット30の電位変動の影響で、デマルチプレクサ120(入力端子121と出力端子122)の電位が変動する場合がある。電位が高くなる(低くなる)と、内部抵抗で生じる電圧降下で、デマルチプレクサ120の電位が基準電位(接地ライン)以下、又は電源ラインVccの電位以上となり、通常は逆バイアスされるべき寄生ダイオード等が、順バイアスされてしまうおそ

50

れがある。寄生ダイオード等が順バイアスされると、意図しない不正電流  $I_d$  が発生し、電極 101 から出力された不正電流  $I_d$  が双極性パルスの電荷バランスを崩す原因となる。

#### 【0031】

そこで電位調節回路 113 によって、デマルチプレクサ 120 の電位が電源電位  $V_{cc}$  と基準電位  $V_{GND}$ との間に収められるようにする。電位調節回路 113 は、入力端子 121 と電源ライン  $V_{cc}$  を接続するスイッチ SW1 と、入力端子 121 と基準電位  $V_{GND}$  を接続するスイッチ SW2 を持つ。

#### 【0032】

電位調節回路 113 に、デコーダ 112 からの電位信号が入力されると、刺激ユニット 100 側で、電流源  $I_{ac}$  から出力される双極性パルスの電流の向きが認識される。刺激制御部 110 は、電位調節回路 113 のスイッチ SW1 と SW2 を、双極性パルスの電流の向きに応じて切り換える。

10

#### 【0033】

例えば、図 3 の電流源  $I_{ac}$  から、アノーディックの電流  $I$  が出力されると、デマルチプレクサ 120 の内部抵抗による電圧降下の影響で、NMOS 領域 130a のドレイン (D) 132 の電位が基準電位  $V_{GND}$  よりも下がり、寄生ダイオード D1 が順バイアスされるおそれがある。この場合、電位調節回路 113 の電源ライン  $V_{cc}$  に接続されるスイッチ SW1 が ON にされ、基準電位  $V_{GND}$  に接続されるスイッチ SW2 が OFF にされる。これによりデマルチプレクサ 120 の電位が上昇する（持ち上げられる）。これにより内部抵抗 R による電圧降下の影響で、出力端子 122a の電位が下がっても、基準電位  $V_{GND}$  以下に下がる可能性はほとんどないので、ダイオード D1 の逆バイアス状態が保たれる。

20

#### 【0034】

一方、電流源  $I_{ac}$  から出力される電流  $I$  の極性が反転され、カソーディックとなると、PMOS 領域 130b のドレイン 136 の電位が、電源ライン  $V_{cc}$  の電位よりも上昇して、寄生ダイオード D2 が順バイアスされるおそれがある。このとき、電位調節回路 113 のスイッチ SW1 が OFF され、スイッチ SW2 が ON にされる。これにより出力端子 122a の電位が上昇しても、デマルチプレクサ 120 の電位が電源ライン  $V_{cc}$  の電圧を超える可能性は低くなるので、ダイオード D2 の逆バイアス状態が保たれる。

30

#### 【0035】

以上のように、双極性パルスの刺激電流の向きに応じて、電位調節回路 113 のスイッチ SW1 とスイッチ SW2 の ON と OFF を交互に切り換えることで、デマルチプレクサ 120 の電位を許容電圧範囲内に抑えられる。そして寄生ダイオードが順バイアスされないことで、不正電流  $I_d$  の発生が抑えられ、電極 101 から出力される双極性パルスの電荷バランスが保たれる。

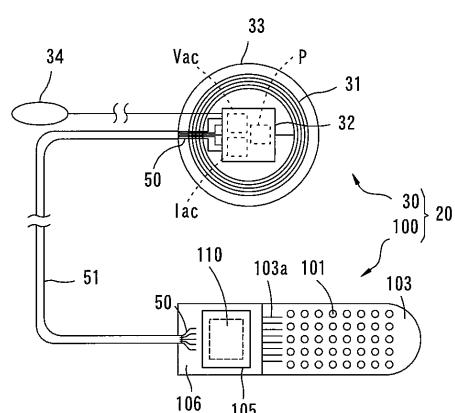

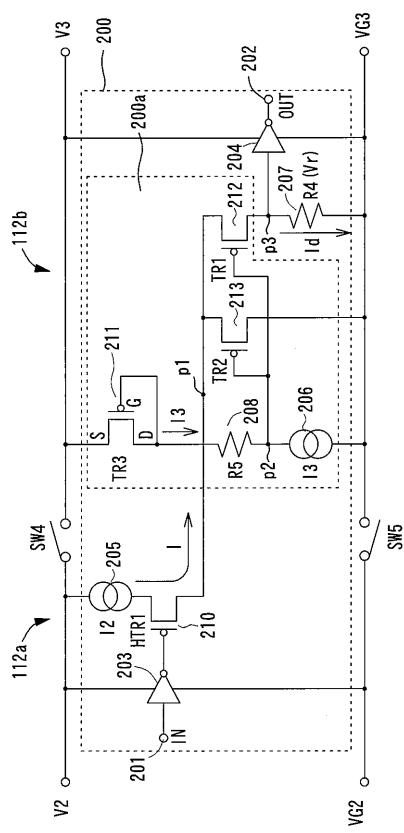

#### 【0036】

次にレベルシフト回路について説明する。図 5 はレベルシフト回路 200 の説明図である。レベルシフト回路 200 は、スイッチ SW4, SW5 を介して接続される第 1 回路 112a と、第 2 回路 112b との間で、制御信号（論理信号）を正しく伝達させるため、第 1 回路 112a の制御信号の第 1 レベルを、第 2 回路 112b の制御信号の第 2 レベルにシフト（変換）する回路である。

40

#### 【0037】

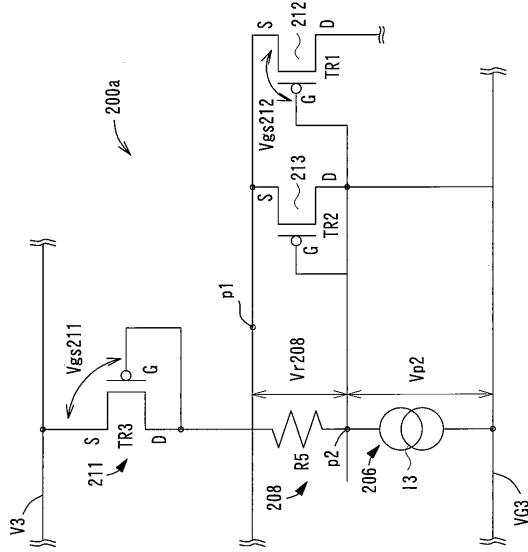

レベルシフト回路 200 は、入力端子 201、出力端子 202、インバータ 203、204、定電流源 205、高耐圧トランジスタ 210、抵抗 207、クランプ回路 200a を持つ。クランプ回路 200a は、定電流源 206、抵抗 208、低耐圧トランジスタ 211、212、213 を持つ。

#### 【0038】

入力端子 201 には、信号線 50c から抽出された制御信号が入力される。入力端子 201 の信号はインバータ 203 に入力される。インバータ 203 の出力は高耐圧トランジ

50

スタ 2 1 0 のゲート ( G ) に入力される。高耐圧トランジスタ 2 1 0 のソース ( S ) は定電流源 2 0 5 に接続される。定電流源 2 0 5 の他端 ( 入力 ) は電源ライン V 2 に接続される。高耐圧トランジスタ 2 1 0 のドレイン ( D ) はクランプ回路 2 0 0 a の低耐圧トランジスタ 2 1 2 ( 第 1 低耐圧トランジスタ ) のソース ( S ) に接続される ( 接点 p 1 )。

#### 【 0 0 3 9 】

以上の構成により高耐圧トランジスタ 2 1 0 は、ゲート ( G ) に入力された制御信号によって ON ( 導通 ) と OFF ( 非導通 ) が切り換えられる。つまり入力端子 2 0 1 に High レベルの信号が入力されると高耐圧トランジスタ 2 1 0 が導通され、定電流源 2 0 5 からの電流 I がクランプ回路 2 0 0 a 側に供給される。一方、入力端子 2 0 1 に Low レベルの信号が入力されると高耐圧トランジスタ 2 1 0 が非導通となり、定電流源 2 0 5 からの電流 I はクランプ回路 2 0 0 a に供給されない。10

#### 【 0 0 4 0 】

図 6 にクランプ回路の 2 0 0 a の説明図 ( 拡大図 ) を示す。クランプ回路 2 0 0 a 側は、第 3 低耐圧トランジスタ 2 1 1 の第 3 ゲート ( G ) と第 3 ドレイン ( D ) は抵抗 2 0 8 に接続される。第 3 低耐圧トランジスタ 2 1 1 のソース ( S ) は、電源ライン V 3 に接続される。抵抗 2 0 8 の他端は定電流源 2 0 6 ( 出力 ) に接続される ( 接点 p 2 )。なお定電流源 2 0 6 の他端 ( 入力 ) は、接地ライン V G 3 に接続される。以上の構成により、第 3 低耐圧トランジスタ 2 1 1 は、定電流源 2 0 6 からの電流で所定の電圧降下 ( V g s 2 1 1 ) を生じる。抵抗 2 0 8 は、定電流源 2 0 6 からの電流で所定の電圧降下 ( V r 2 0 8 ) を生じる。これらにより、接点 p 2 の電位は、 $V_{p2} = V_3 - V_{gs211} - V_{r208}$  にバイアスされる。20

#### 【 0 0 4 1 】

第 1 低耐圧トランジスタ 2 1 2 のゲート ( G ) は、定電流源 2 0 6 と抵抗 2 0 8 ( R 5 ) の間の接点 p 2 に接続され、第 1 低耐圧トランジスタ 2 1 2 のソース ( S ) は接点 p 1 を介して高耐圧トランジスタ 2 1 0 のドレイン ( D ) に接続される。第 1 低耐圧トランジスタ 2 1 2 のドレイン ( D ) は、電圧変換手段である抵抗 2 0 7 ( R 4 ) に接続され、抵抗 R 4 の他端は接地ライン V G 3 に接続される ( 図 5 参照 )。図 5 において、第 1 低耐圧トランジスタ 2 1 2 のドレイン ( D ) と抵抗 2 0 7 ( R 4 ) の間の接点 p 3 には、インバータ 2 0 4 が接続される。インバータ 2 0 4 の出力は出力端子 2 0 2 が接続される。30

#### 【 0 0 4 2 】

第 1 低耐圧トランジスタ 2 1 2 は、接点 p 2 にゲートがバイアスされているので、ゲート接地回路として働き、高耐圧トランジスタ 2 1 0 から電流 I が供給されると、第 1 低耐圧トランジスタ 2 1 2 を介して電流は抵抗 2 0 7 へと流れる。なお第 1 低耐圧トランジスタ 2 1 2 に流れる電流 I d は、ゲートバイアス電位と抵抗 2 0 7 によって制限される。第 2 回路 1 1 2 b の電位 V 3 , 第 1 低耐圧トランジスタ 2 1 2 のゲート ( G ) - ソース ( S ) 間電圧 V g s 2 1 2 、抵抗 2 0 7 で生じる電圧降下 V r としたときに、式 ( 1 ) で決定される電流 I d が第 1 低耐圧スイッチング素子 2 1 2 に流れる電流の最大値となる。40

#### 【 0 0 4 3 】

#### 【 数 1 】

$$\begin{aligned} Id &= \frac{1}{R} (V_{p2} + V_{gs211}) \\ &= \frac{1}{R} (V_3 - V_{gs211} - V_{r208} + V_{gs212}) \end{aligned}$$

... ( 1 )

ここで、第 1 低耐圧トランジスタ 2 1 2 を流れる電流 I d 、第 3 低耐圧トランジスタ 2 1 1 に流れる電流 ( I 3 ) による各トランジスタの電流密度を同程度とすると、式 ( 1 )

の電圧降下  $V_{gss211}$  と電圧降下  $V_{gss212}$  は同程度になり、第1低耐圧トランジスタ212に電流  $I_d$  が流れた時の接点 p1 の最大電圧（クランプ電圧）は、 $V_3 - V_{r208}$  となる。これによって、第1回路112aの電源電位  $V_2$  よりも第2回路112bの電源電位  $V_3$  の方が低い時でも、 $V_2 > V_3 - V_{r208}$  の範囲で、高耐圧トランジスタ210からの電流  $I$  を第1低耐圧トランジスタ211に流すことができ、信号を伝送することができるようになる。

#### 【0044】

第2低耐圧トランジスタ213は、第2ゲート（G）が定電流源206（接点 p2）に接続され、第2ソース（S）が高耐圧トランジスタ210のドレイン（D）（接点 p1）に接続される。第2低耐圧トランジスタ213の第2ドレイン（D）は、接地ライン  $V_{G3}$  に接続される。なお第2低耐圧トランジスタ213は、第1低耐圧トランジスタ212と同極性で、低耐圧トランジスタ212、213のソース共通でゲート（G）接地回路を構成している。第2低耐圧トランジスタ213は、高耐圧トランジスタ210から供給される電流  $I$  のうち、第1低耐圧トランジスタ212に流れる電流を差し引いた電流が流れ（分流される）。

10

#### 【0045】

以上のような回路構成によって、高耐圧トランジスタ210は、インバータ203を介してゲート（G）に Low レベルの信号が入力されたときに導通状態（ON）となり、ゲート（G）に High レベルの信号が入力されたときに非導通状態（OFF）となる。なお入力信号は、スイッチ SW4、SW5 が閉じて第1回路112aと第2回路112bが電気的に接続され、電源ライン  $V_2$  と  $V_3$ 、接地ライン  $V_{G2}$  と  $V_{G3}$  が同電位のときに入力される。スイッチ SW4 と SW5 が接続されているとき、入力端子 201 に High レベルの信号が入力されると、インバータ203で信号が反転され、高耐圧トランジスタ210のゲート（G）に Low レベルの信号が入力される。これにより高耐圧トランジスタ210は導通状態となり、定電流源205では所要の電流がソース（S）からドレイン（D）へと流れ出る。また、スイッチ SW4、SW5 が閉じているとき、定電流源205から供給される電流で第1低耐圧トランジスタ212は導通状態となり、電流  $I_d$  がソース（S）からドレイン（D）に流れ出る。そして抵抗 207 によって電流  $I_d$  が電圧  $V_r$  に変換されることで、第1回路112aの制御信号の第1レベルが、第2回路112bの制御信号の第2レベルにレベルシフトされる。第2レベルにレベルシフトされた信号は、信号線 50d を介して各回路（デマルチブレクサ120等）に供給される。

20

#### 【0046】

一方、入力端子 201 に Low レベルの信号が入力されると、インバータ203で信号が反転されて、高耐圧トランジスタ210のゲート（G）に High レベルの信号が入力される。これにより高耐圧トランジスタ210は非導通となり定電流源205からの電流は出力されない。以上のように制御信号の ON と OFF によって、高耐圧トランジスタ210の導通と非導通が切り換えられて、電流の出力の有無が切り換えられる。そして抵抗 207 に生じる電圧降下で、レベルシフトされた制御信号が、信号線 50d を介して、第2回路112b側へと伝達される。

30

#### 【0047】

ここで、第1回路112aと第2回路112bの間を、スイッチ SW4 と SW5 で切り離す理由について説明する。刺激ユニット100からは、デマルチブレクサ120の状態を変化させるときに電力（電源）が供給されればよく、デマルチブレクサ120の状態が変化しない刺激電流の出力時には、電源供給を止めることができる。一方、図2に示すように、受信ユニット30と刺激ユニット100はフレキシブルなリード51で電気的に接続される場合、フレキシブルなリード51は、柔軟性を保つために樹脂で包埋されることが好ましく、長期間防水性能を保つことが難しい場合がある。その為、電力を供給する給電用の導線（電力線）50aは、生体へのリーク経路がある事を考慮する必要がある。生体への刺激電流は、生体の安全性を担保するために、バイフェージックな電流（双極性パルス）の電荷バランスを保つ必要があるが、本来の刺激電流を流す経路以外で生体へのリ

40

50

ークが存在すると、電荷バランスを保てなくなる。そこで、導線 50a に生体へのリーク経路があつても、刺激電流を流す系と電気的に分離するために、スイッチ SW4 と SW5 を用いている。

#### 【0048】

ここでは第1回路 112a は、刺激ユニット 100 への電源供給を受電する回路であり、給電に重畠されている信号を復調するデコーダ 112 等を含む。電源（電力）の受電時には、スイッチ SW4 と SW5 を閉じ、デコーダ 112 出力を入力端子 201 から入力し、出力端子 202 へ伝送し、デマルチプレクサ 120 の状態をセットする。デマルチプレクサ 120 の状態のセットが完了すると、デマルチプレクサ 200 によって、スイッチ SW4 と SW5 が開かれる。これによって、導線 50a を介する電源（電力）の供給が断たれても、第2回路 112b 側に設置したコンデンサ（図示を略す）の充電電圧によって、デマルチプレクサ 120 の状態が保持されるようになる。そして導線 50a に生体とのリークがあつても、刺激電流を出力する前に、スイッチ SW4 と SW5 を開くことによって、本来の刺激電流を流す経路以外への電流の漏れを抑えることができ、電荷バランスを保つことが可能になる。10

#### 【0049】

なおスイッチ SW4, SW5 が開き、第1回路 112a と第2回路 112b が電気的に切り離されると、切り離された回路（ここでは第1回路 112a とする）の電源ライン V2 と接地ライン VG2 の電位は、第2回路 112b の電源ライン V3 と接地ライン VG3 の電位と同電位ではなくなり、フローティングで変動が生じうる。20

#### 【0050】

第1回路 112a と第2回路 112b が電気的に接続されているとき、各回路は共通の接地電位を持ち、電位変動は生じない。一方、回路（第1回路 112a、第2回路 112b）が電気的に切り離されると、切り離された回路の接地電位がフローティング（変動）する。フローティングで回路の電位が上昇して、耐圧を越えると破損の原因となる。一方、生体組織の影響で、フローティングによる電位変動の程度を予測することは容易ではない。

#### 【0051】

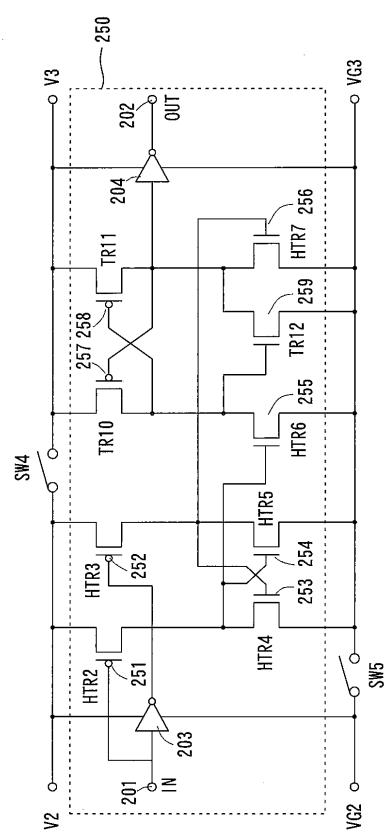

そこで電圧変換（電圧基準）で信号伝送を行う従来技術では、フローティングによる電位変動に十分に耐え得る大型の高耐圧トランジスタを複数個用いて、第1回路 112a と第2回路 112b 間に十分な耐圧を持たせる必要があった。図 7 に従来技術のレベルシフト回路 250 の例を示す。なお図 7において、図 5 のレベルシフト回路 200 と同じ構成には同じ図番号を付して詳細な説明は省略する。図 7 のような従来技術のレベルシフト回路 250 では、電圧基準で信号伝送を行うためにトランジスタ 251 ~ 259 が使用され、電位変動の影響を受ける複数箇所のトランジスタ 251 ~ 256 を、高耐圧トランジスタ HTR1 ~ HTR7 とする必要があった。しかし高耐圧トランジスタのサイズは大きく、装置の小型化に不利である。一方、本実施形態では、電流伝送にて情報（信号線 50c で抽出される制御信号）を伝達する。その為、スイッチ SW4, SW5 が OFF とされたときにフローティングによる電位変動の影響を受けるのは、入力端子 201 側にある高耐圧トランジスタ 210 のみとなる。その為、本実施形態では、高耐圧トランジスタ 210 以外のトランジスタを小型の低耐圧トランジスタで構成できる。例えば、高耐圧トランジスタのサイズは  $15 \times 20 \mu m$  程度であるのに対し、低耐圧トランジスタのサイズは  $3 \times 10 \mu m$  程度である。このように小型のトランジスタを用いてレベルシフト回路を構成することで、従来技術に比べて回路全体を小型にできる。30

#### 【0052】

また、刺激電流を出力している間は、デマルチプレクサ 120 の状態は変化させないので、電源受電が不要となり、消費電力を下げるために電源供給を停止する。次にデマルチプレクサ 120 の状態を変化させる時に電源供給を再開するが、スイッチ SW4 と SW5 を再び接続した際、電源ライン V2 と電源ライン V3 の電位が同じになるのに無視できない時間を要する場合がある。その時間内であっても、 $V2 > V3 - V_{r208}$  の範囲であ40

10

20

30

40

50

れば、信号伝達が可能であり、デマルチブレクサ120の誤設定を防ぐことができる。

#### 【0053】

なお図3では、説明の簡略化の為に信号線50dを一本のみ示しているが、実際には、制御する対象の数（例えば電極数101等）に応じて、複数本の信号線50dが用意される。つまり各信号線50dに対して、本実施形態のレベルシフト回路200が用いられることで、制御する対象の数が増えるほど、本発明による改善の効果は大きくなることが期待される。

#### 【0054】

次に以上の構成を備える生体組織刺激装置（生体組織刺激装置）の動作を説明する。撮影装置12で撮影された画像データは、データ変調手段13aで制御信号に変換されると共に、データ変調手段13aの変調で、バッテリー13aから供給される電力に重畠されて、送信手段14を介して体内装置20側に送信される。体内装置20では、制御部32が、受信された電磁波から電力と制御信号を復調する。電力は刺激ユニット100を駆動させる交流電力を供給する電源V1と、電極101から双極性パルス（電流）を出力させる電流源I1に用いられる。制御部32は制御信号から電極指定信号、電位調節信号等を抽出し、信号源Pから出力させる。信号源Pから出力された制御信号は、電源V1から供給された電力に重畠される。

10

#### 【0055】

刺激ユニット100の整流回路111は、受信ユニット30から送信された交流電圧を直流電圧に整流する。電位調整回路112は、交流電力に重畠された制御信号（電位調節信号）から双極性パルスの電流の極性を検出し、双極性パルスの電流の極性に応じて、スイッチ部113が持つスイッチSW1とSW2のONとOFFとを制御する。例えば、電流が電極101から流れ出るアノーディックの場合、電位調整回路112は、スイッチSW1をONとし、スイッチSW2をOFFとする。アノーディックの場合に、デマルチブレクサ120の電位を予め引き上げておくことで、内部抵抗Rによる電圧降下が生じたとしても、出力端子122の電位が接地電位VG1以下にならないようにできる。一方、電流が電極101から流入されるカソーディックの場合、電位調整回路112は、スイッチSW1をOFFとし、スイッチSW2をONとする。電流が電極101から流入される方向に流れるとときに、デマルチブレクサ120の電位を予め引き下げておくことで、内部抵抗Rによる電圧降下が生じたとしても、入力端子121の電位が電源電位Vccを越えないようになる。以上のようにして、デマルチブレクサ120が許容電圧範囲で駆動されることで、寄生ダイオード等が順バイアスされ、流れ出た不正電流Idで双極性パルスの電荷バランスが崩れることが防止される。

20

#### 【0056】

なお上記の構成において、信号源Pから複数の制御信号が同時に送信される場合には、制御手段112は、電位調節信号の処理を優先して行うようになる。このようにすると、スイッチSW1、SW2のONとOFFとが切り換えによって、電位が調節された状態で、双極性パルスの出力が安定して行なわれる。

30

#### 【0057】

また上記では、スイッチ部113を用いて、デマルチブレクサ120（入力端子121）の電位が、電源側と接地側とに切り換え接続することで、デマルチブレクサ120の電位を調節している。これ以外にも、刺激電流の電流の設定値に応じて、スイッチ部113が切り換えられることで、デマルチブレクサ120（入力端子121）の電位が調節されても良い。この場合、電流値に応じて、デマルチブレクサ120（入力端子121）の電位が可変抵抗等によってリニアに調節されても良い。

40

#### 【0058】

またデマルチブレクサ120に流れる電流の測定値に基づいて、入力端子121の電位が調節されても良い。この場合には、検出部112aは、デマルチブレクサ120に流れる電流値を検出する。なおこの場合の検出部112aは抵抗等が利用され、抵抗で生じた電圧降下で電流値が検出されるようになる。そして検出部112aによる電流値の検出結

50

果に基づき、電位調節部 112b がスイッチ SW1、SW2 の ON と OFF を制御する。この時、上述と同様に、スイッチ SW1、SW2 と入力端子 121との間に可変抵抗等を設けて、デマルチプレクサ 120 の電位がリニアに調節されるようにしてもよい。

#### 【0059】

なお上記では正負に極性を持つ双極性パルスを電極から出力させる例を示した。これ以外にも、1度の電気刺激で電極から正(負)方向の電流を出力させた後、2回目の電気刺激で電極から反対極性の負(正)方向の電流を出力させても良い。更には、電極から正負一方向のみの電流が出力される場合にも、上記の構成によってスイッチ部の ON と OFF とが切り換えられることで、デマルチプレクサ 120 の電位を許容電圧範囲に收めることができ、安定動作を維持できるようになる。

10

#### 【0060】

次に、レベルシフト回路 200 の動作を説明する。例えばデマルチプレクサ 120 の状態が切り換えられるとき、スイッチ SW4、SW5 が ON となり、デコーダ 112 を介して第1回路 112a 側と、第2回路 112b 側が接続される。なお第1回路 112a と第2回路 112b が接続されると各回路は同電位となる。この時、入力端子 201 に入力された Low レベルの信号は、インバータ 203 で反転されて High レベルの信号となる。High レベルの信号が高耐圧トランジスタ 210 に加わると、高耐圧トランジスタ 210 が OFF となり、電流 I が流れ出ない。一方、入力端子 201 に入力された High レベルの信号は、インバータ 203 により反転されて Low レベルの信号となる。Low レベルの信号が高耐圧トランジスタ 210 に加わると、高耐圧トランジスタ 210 が ON となり、定電流源 205 の電流が高耐圧トランジスタ 210 のソース(S) - ドレイン(D) 間を介して、クランプ回路 200a 側に流れ出る。なお低耐圧トランジスタ 211 ~ 213 はベース接地によるクランプ回路を構成し、高耐圧トランジスタ 210 から流れ出た電流 I は、低耐圧トランジスタ 212 のドレイン(D) - ソース(S) 間を経由して抵抗 207 に入力される。一方、抵抗 207 (R4) で所定の電圧降下(Vr) が生じることで、インバータ 204 へ信号を伝達する。インバータ 204 に供給された信号は、出力端子 202、信号線 50d を介してデマルチプレクサ 120、スイッチ部 113 に伝達され、制御信号に基づき状態が変化される。そして指定された電極 101 から刺激電流が出力される。

20

#### 【0061】

一方、スイッチ SW4、SW5 が OFF となり、第1回路 112a と第2回路 112b が電気的に切り離されると、第1回路 112a と第2回路 112b の電位が変わる場合があり、電位が上昇することで回路の破損の原因となる。しかし以上のような構成のレベルシフト回路 200 で耐圧が確保されることで、各回路は安定して動作される。またレベルシフト回路 200 を小型の素子で構成することで、半導体回路全体がより小型になる。

30

#### 【0062】

なお上記ではデコーダ 112 を介して接続される第1回路 112a と第2回路 112b に設けられたレベルシフト回路を例に挙げて説明した。これ以外にも回路間で異なる電圧レベルの論理信号を伝達する際に、本実施形態のレベルシフト回路が用いられることで、必要な耐圧を確保しつつ回路構成をより小型にすることができる。

40

#### 【図面の簡単な説明】

#### 【0063】

【図1】視覚再生補助装置の外観図である。

【図2】視覚再生補助装置の体内装置の説明図である。

【図3】体内装置の制御回路の説明図である。

【図4】デマルチプレクサの説明図である。

【図5】レベルシフト回路の説明図である。

【図6】クランプ回路の拡大図である。

【図7】従来技術のレベルシフト回路の構成の説明図である。

#### 【符号の説明】

50

## 【0064】

V2, V3 電源ライン

1 視覚再生補助装置

10 体外装置

20 体内装置

50a、50b、50c、50d 導線

100 刺激ユニット

100a 電力供給回路

100b 刺激電流供給回路

101 電極

10

112 デコーダ

112a 第1回路

112b 第2回路

120 デマルチプレクサ

200 レベルシフト回路

200a クランプ回路

201 入力端子

202 出力端子

205、206 定電流源

207、208 抵抗

20

210 高耐圧トランジスタ

211、212、213 低耐圧トランジスタ

【図1】

【図2】

(a)

(b)

【 図 3 】

【 义 5 】

【 図 4 】

【 四 6 】

【図 7】