(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2022-79407

(P2022-79407A)

(43)公開日 令和4年5月26日(2022.5.26)

| (51)国際特許分類 |                 | F I     | テーマコード(参考) |         |           |

|------------|-----------------|---------|------------|---------|-----------|

| G 0 6 F    | 11/10 (2006.01) | G 0 6 F | 11/10      | 6 4 8   | 5 B 0 4 8 |

| G 0 6 F    | 11/22 (2006.01) | G 0 6 F | 11/22      | 6 7 5 Z | 5 B 1 6 0 |

| G 0 6 F    | 12/00 (2006.01) | G 0 6 F | 12/00      | 5 9 7 U | 5 L 2 0 6 |

| G 1 1 C    | 29/42 (2006.01) | G 1 1 C | 29/42      |         |           |

| G 1 1 C    | 29/48 (2006.01) | G 1 1 C | 29/48      |         |           |

審査請求 有 請求項の数 20 O L (全44頁)

|                   |                             |         |                                                                                                                 |

|-------------------|-----------------------------|---------|-----------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2021-103681(P2021-103681) | (71)出願人 | 504056130<br>ウェスタン デジタル テクノロジーズ<br>インコーポレーテッド<br>アメリカ合衆国 95119 カリフォルニア州 サンノゼ, グレート オークス<br>パークウェイ 5601          |

| (22)出願日           | 令和3年6月22日(2021.6.22)        | (74)代理人 | 110000110<br>特許業務法人快友国際特許事務所                                                                                    |

| (31)優先権主張番号       | 63/114,103                  | (72)発明者 | ラン・ザミール<br>アメリカ合衆国 カリフォルニア州 95119 サンノゼ, グレート オークス<br>パークウェイ 5601, ウェスタン デジタル テクノロジーズ インコーポレーテッド宛<br>デヴィット・アブラハム |

| (32)優先日           | 令和2年11月16日(2020.11.16)      |         |                                                                                                                 |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |         |                                                                                                                 |

| (31)優先権主張番号       | 17/171,657                  |         |                                                                                                                 |

| (32)優先日           | 令和3年2月9日(2021.2.9)          |         |                                                                                                                 |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |         |                                                                                                                 |

最終頁に続く

## (54)【発明の名称】 不揮発性データ完全性の高速検証

## (57)【要約】 (修正有)

【課題】不揮発性メモリセルのデータ完全性を高速検証する装置及び方法を提供する。

【解決手段】方法は、データを完全にデコードすることなく、検証されるデータに関連するビットエラー率(BER)の推定を行う。記憶システム100は、推定されたBERが閾値を下回る場合、データがデータ完全性基準を満たすことを報告する。記憶システムは、推定されたBERが閾値を上回る場合、データをデコードして、BERを決定し、決定したBERに基づいて、データがデータ完全性基準を満たすかどうかを報告する。BERの推定値は、データのシンドローム重み、データの複数のコードワードから形成されるXORコードワードのBER又はデータのサンプルのBERに基づく。したがって、少なくともデータが完全にデコードされていないときに、データ完全性を検証する相当な時間及び電力が節約される。

【選択図】図1A

**【特許請求の範囲】****【請求項 1】**

装置であつて、

通信インターフェースと、

前記通信インターフェースに結合された制御回路であつて、前記制御回路が、不揮発性メモリセルに接続するように構成されており、前記制御回路が、

前記不揮発性メモリセルに記憶されたエンコードされたデータの完全性を検証するための要求を、前記通信インターフェースを介して受信することと、

前記要求に応答して、前記エンコードされたデータを完全にデコードすることなく、前記エンコードされたデータに関連するビットエラー率を推定することと、

前記ビットエラー率の前記推定値が、第1の閾値を下回ることに応答して、前記エンコードされたデータの前記完全性がデータ完全性基準を満たすことを、前記通信インターフェースを介して報告することと、を行うように構成されている、制御回路と、を備える、装置。

**【請求項 2】**

前記制御回路が、

前記推定されたビットエラー率が前記第1の閾値を上回ることに応答して、前記エンコードされたデータのビットエラー率を決定し、前記決定されたビットエラー率に基づいて、前記エンコードされたデータの前記データ完全性が前記データ完全性基準を満たすかどうかを報告するために、前記エンコードされたデータを完全にデコードするように更に構成されている、請求項1に記載の装置。

**【請求項 3】**

前記制御回路が、

前記推定されたビットエラー率が前記第1の閾値よりも大きい第2の閾値を上回ることに応答して、前記エンコードされたデータを完全にデコードすることなく、前記エンコードされたデータの前記完全性が前記データ完全性基準を満たさないことを報告するように更に構成されている、請求項1に記載の装置。

**【請求項 4】**

前記制御回路が、

前記エンコードされたデータを完全にデコードすることなく、前記エンコードされたデータのシンドローム重みを決定することと、

前記シンドローム重みに基づいて、前記エンコードされたデータに関連する前記ビットエラー率を推定することと、を行うように更に構成されている、請求項1に記載の装置。

**【請求項 5】**

前記制御回路が、

前記エンコードされたデータを完全にデコードすることなく、前記エンコードされたデータのシンドローム重みを決定することと、

前記シンドローム重みに基づいて、前記エンコードされたデータに関連する前記ビットエラー率を推定することと、

前記推定されたビットエラー率が前記第1の閾値よりも高い第2の閾値を上回ることに応答して、前記エンコードされたデータの前記完全性が、前記データ完全性基準を満たさないことを報告することと、を行うように更に構成されている、請求項1に記載の装置。

**【請求項 6】**

前記制御回路が、

XORコードワードを作成するために、前記エンコードされたデータの複数のコードワードのビット単位のXORを実行することと、

前記エンコードされたデータを完全にデコードすることなく、前記エンコードされたデータに関連する前記ビットエラー率を推定するために、前記XORコードワードのビットエラー率を決定することであつて、前記制御回路が、前記XORコードワードの前記ビットエラー率が前記第1の閾値を下回ることに応答して、前記エンコードされたデータの前記

10

20

30

40

50

完全性が前記データ完全性基準を満たすことを報告する、決定することと、を行うように更に構成されている、請求項1に記載の装置。

**【請求項7】**

前記制御回路が、

前記XORコードワードの前記ビットエラー率が前記第1の閾値を上回ることに応答して、前記エンコードされたデータの前記複数のコードワードの各々をデコードし、前記複数のコードワードの各々の決定されたビットエラー率に基づいて、前記エンコードされたデータの前記完全性が前記データ完全性基準を満たすかどうかを報告するように更に構成されている、請求項6に記載の装置。

**【請求項8】**

前記装置が、半導体ダイ及びメモリコントローラを備え、前記半導体ダイが、前記制御回路を備え、前記制御回路が、前記XORコードワードを作成するために前記エンコードされたデータの前記複数のコードワードの前記ビット単位のXORを実行するように更に構成されている、請求項6に記載の装置。

10

**【請求項9】**

前記制御回路が、

前記エンコードされたデータを完全にデコードすることなく、前記エンコードされたデータに関連する前記ビットエラー率を推定するために、前記エンコードされたデータのサンプルのビットエラー率を決定することであって、前記制御回路が、前記エンコードされたデータの前記サンプルの前記ビットエラー率が前記第1の閾値を下回ることに応答して、前記エンコードされたデータの前記完全性が前記データ完全性基準を満たすことを報告する、決定することを行うように更に構成されている、請求項1に記載の装置。

20

**【請求項10】**

前記制御回路が、

前記エンコードされたデータの前記サンプルの前記ビットエラー率が前記第1の閾値を上回ることに応答して、前記エンコードされたデータ内の各コードワードのビットエラー率を決定し、各コードワードの前記決定されたビットエラー率に基づいて、前記エンコードされたデータの前記完全性が前記データ完全性基準を満たすかどうかを報告するように更に構成されている、請求項9に記載の装置。

30

**【請求項11】**

不揮発性記憶システムを動作させる方法であって、

前記記憶システム内の不揮発性メモリセルに記憶されたデータの完全性を検証するための要求を、ホストシステムから前記不揮発性記憶システムで受信することと、前記要求に応答して、前記不揮発性メモリセルに記憶された1つ以上のECCコードワードのシンドローム重みを決定することと、

前記1つ以上のECCコードワードの各々の前記シンドローム重みが第1の閾値を下回ることに応答して、検証される前記データが、データ完全性基準を満たすことを前記ホストシステムに報告することと、を含む、方法。

**【請求項12】**

前記第1の閾値と、前記第1の閾値よりも大きい第2の閾値との間のシンドローム重みを有する、検証される前記データの各それぞれのECCコードワードに対して、

各それぞれのECCコードワードをデコードすることと、

各それぞれのECCコードワードをデコードするビットエラー率が、前記第1の閾値と前記第2の閾値との間の第3の閾値を下回ることに基づいて、検証される前記データが前記データ完全性基準を満たすことを前記ホストシステムに報告することと、を実行することを更に含む、請求項11に記載の方法。

40

**【請求項13】**

前記1つ以上のECCコードワードのうちのいずれかの前記シンドローム重みが前記第2の閾値を上回ることに応答して、前記記憶システムが、前記データを取得するために制限されたリトライ努力を適用すべきであると前記ホストシステムが指定した場合に、検証さ

50

れる前記データの前記完全性が前記データ完全性基準を満たさないことを前記ホストシステムに報告することを更に含む、請求項 1 2 に記載の方法。

**【請求項 1 4】**

前記 1 つ以上の E C C コードワードのうちのいずれかの前記シンドローム重みが前記第 2 の閾値を上回ることに応答して、前記データの完全性を検証するための前記要求を完了する前に、前記記憶システムが全ての利用可能なエラー回復を適用すべきであると前記ホストシステムが指定した場合に、検証される前記データを回復するためのエラー回復プロセスを実行することを更に含む、請求項 1 2 に記載の方法。

**【請求項 1 5】**

不揮発性記憶システムであって、

10

不揮発性メモリセルと、

前記メモリセルに記憶されたデータの完全性を検証するための要求に応答して、複数の E C C コードワードを前記メモリセルから感知するための感知手段と、

前記複数の E C C コードワードの X O R コードワードを形成するための X O R 手段と、

前記 X O R コードワードのビットエラー率が第 1 の閾値を下回るかどうかを推定するか、又は判定するためのビットエラー率手段と、

前記 X O R コードワードの前記推定されたビットエラー率又は前記決定されたビットエラー率のいずれかが前記第 1 の閾値を下回ることに応答して、検証される前記データが、デコード可能である可能性が高いことを報告するための通信手段と、を備える、不揮発性記憶システム。

20

**【請求項 1 6】**

前記 X O R 手段が、半導体ダイ上に存在し、

前記ビットエラー率手段が、メモリバスによって前記半導体ダイと通信するメモリコントローラ内に存在し、前記 X O R 手段が、前記メモリバスを介して、前記 X O R コードワードを前記メモリコントローラに転送するように構成されている、請求項 1 5 に記載の不揮発性記憶システム。

**【請求項 1 7】**

前記ビットエラー率手段が、前記 X O R コードワードの前記推定されたビットエラー率又は前記決定されたビットエラー率が前記第 1 の閾値を上回ることに応答して、

前記半導体ダイに、前記複数の E C C コードワードを転送することを要求することと、

30

前記複数の E C C コードワードをデコードすることと、

前記 E C C コードワードの各々のデコード結果に基づいて、検証される前記データが、デコード可能である可能性が高いかどうかをホストシステムに報告することと、を実行するように更に構成されている、請求項 1 6 に記載の不揮発性記憶システム。

**【請求項 1 8】**

前記ビットエラー率手段が、前記 X O R コードワードの前記推定されたビットエラー率又は前記決定されたエラー率が前記第 1 の閾値を上回ることに応答して、

前記半導体ダイに、前記複数の E C C コードワードを転送することを要求することと、

各それぞれのコードワードのシンドローム重みに基づいて、前記複数の E C C コードワードの各それぞれのコードワードのビットエラー率を推定することと、

40

検証される前記データが、各それぞれのコードワードの前記推定されたビットエラー率に基づいて、デコード可能である可能性が高いかどうかをホストシステムに報告することと、を実行するように更に構成されている、請求項 1 5 に記載の不揮発性記憶システム。

**【請求項 1 9】**

前記ビットエラー率手段が、前記 X O R コードワードの前記ビットエラー率を決定するために、前記 X O R コードワードをデコードするように構成されており、

前記通信手段が、前記 X O R コードワードの前記決定されたビットエラー率が前記第 1 の閾値を下回ることに応答して、検証される前記データがデコード可能である可能性が高いことを報告するように構成されている、請求項 1 5 に記載の不揮発性記憶システム。

**【請求項 2 0】**

50

前記ビットエラー率手段が、前記XORコードワードの前記ビットエラー率を推定するために、前記XORコードワードのシンドローム重みを決定するように構成されており、前記通信手段が、前記XORコードワードの前記推定されたビットエラー率が前記第1の閾値を下回ることに応答して、検証される前記データがデコード可能である可能性が高いことを報告するように構成されている、請求項15に記載の不揮発性記憶システム。

【発明の詳細な説明】

【技術分野】

【0001】

(優先権の主張)

本出願は、Zamirらによって2020年11月16日に出願され、「FAST VEFIFICATION OF NON-VOLATILE DATA INTEGRITY」と題された米国仮特許出願第63/114,103号の優先権を主張するものであり、参照によりその全体が本明細書に組み込まれる。 10

【背景技術】

【0002】

ポータブル消費者向け電子デバイスに対する需要の大きな高まりは、高容量記憶デバイスの必要性を推進している。フラッシュメモリなどの不揮発性半導体メモリデバイス(本明細書では、「不揮発性記憶システム」又は「不揮発性メモリシステム」とも呼ばれる)は、デジタル情報の記憶及び交換に対する、ますます高まる要求に応じるために広く使用されている。これらの携帯性、汎用性、及び頑丈な設計は、これらの高い信頼性及び大きな容量と共に、このようなメモリデバイスを、例えば、デジタルカメラ、デジタル音楽プレーヤ、ビデオゲームコンソール、PDA、携帯電話、及びデスクトップ、ラップトップ、並びにノートパッドコンピュータを含む、多種多様なホスト電子デバイスにおける使用に理想的なものにしてきた。典型的には、ホスト電子デバイスは、不揮発性記憶システムに電力を提供する。 20

【0003】

不揮発性半導体メモリデバイスは、データを記憶するようにプログラムされ得る不揮発性メモリセルを含む。典型的には、メモリセルは、いくつかのデータ状態にプログラムされる。より多くのデータ状態を使用することにより、メモリセル当たりより多くのビットが記憶されることが可能になる。例えば、メモリセル当たり2ビットを記憶するために4つのデータ状態が使用されてもよく、メモリセル当たり3ビットを記憶するために8つのデータ状態が使用されてもよく、メモリセル当たり4ビットを記憶するために16のデータ状態が使用されてもよいなどである。メモリセルからデータを読み戻すためには、メモリセルが現時点でどのデータ状態にあるかを判定するために、読み出し基準電圧を使用することが典型的である。 30

【0004】

いくつかのメモリセルは、メモリセルのプログラムされた状態を反映する電荷量を保持するようにプログラムされた電荷蓄積領域を有する。例えば、電荷は、メモリセルトランジスタの閾値電圧を目標閾値電圧にプログラムするために、NANDメモリセルの電荷蓄積領域に電荷を追加してもよい。いくつかのメモリセルは、抵抗などの他の物理パラメータに基づいてプログラムされる。 40

【0005】

メモリセルがプログラムされると、その状態を高信頼度で読み戻すことができる事が重要である。しかしながら、感知された状態は、プログラムディスターブ、読み出しディスターブ、及びデータ保持の問題を含む要因に起因して、意図されたプログラム状態から変化する場合があり得る。プログラムディスターブとは、隣接するメモリセルのプログラミングが目標メモリセルの状態を妨害するという結果である。例えば、隣接NANDメモリセルをプログラミングすることにより、目標NANDメモリセルに電荷を追加することができ、それにより、目標NANDメモリセルの閾値電圧を増加させる。読み出しディスターブとは、標的メモリセルの読み出しが標的メモリセルの状態を妨害するという結果であ

る。データ保持の問題とは、長期間にわたってデータを保持することができないことを指す。データ保持の問題は、電荷損失などの要因により、経時的に発生する状態の変化をもたらす可能性がある。例えば、経時的に、NANDメモリセルは電荷を損失することがあり、それにより、NANDメモリセルの閾値電圧を減少させる。

#### 【0006】

データ状態の意図しない変化は、データ完全性の失敗である。データ完全性を維持するために、エラー訂正コード(error correction code、ECC)を、複数の回復階層に加えて使用してもよい。ECCエンコーダは、ユーザデータに基づいてパリティビットを生成してもよい。パリティビットは、メモリセルに記憶されてもよい。例えば、ユーザデータ及びパリティビットを含むECCコードワード(又はより簡単に「コードワード」)は、メモリセルに記憶されてもよい。ECCデコーダを使用して、ECCアルゴリズムを実施して、データ内のエラーを検出及び訂正してもよい。しかしながら、場合によっては、ECCデコーダにはエラーが多くなりすぎて、ECCコードワード内のユーザデータを訂正することができないことがある。いくつかの技術では、これらのエラー訂正能力が異なるいくつかのECCデコーダを使用する。より低電力の、より低い訂正能力のECCデコーダが失敗した場合、より高い電力の、より高い訂正能力のECCデコーダが使用されてもよい。ECCデコーダが失敗した場合、別の選択肢としては、読み出し基準電圧を較正し、別のデコードを試みることである。

#### 【0007】

読み出し基準電圧を較正した後にデータが依然としてデコードできない場合、データをデコードするためにソフトビットを使用してもよい。ソフトビットは、「ソフトビット基準レベル」のセットでメモリセルを感知することに由来する。ソフトビットは、各メモリセルに対するハードビットの信頼性を示すことができる。例示するために、ソフトビットをECCデコードと共に使用してエラー訂正能力を向上させてもよい。例えば、エラー訂正能力の向上は、低密度パリティチェック(low-density parity-check、LDPC)コードを使用し、ハードビットのみを使用することに基づくデコード方式と比較して、デコーダへの入力としてソフトビット値を含めることによって達成され得る。

#### 【0008】

ソフトビットを使用した後に依然としてデータがデコードできない場合、RAID(独立ディスクの冗長アレイ)技術などの冗長情報を使用して、デコード不可能データを復元してもよい。

#### 【0009】

しかしながら、前述の保護は、かなりの時間及び電力を使用する可能性がある。

#### 【0010】

不揮発性メモリに記憶されたデータの完全性を検証するための技術が提案されている。例えば、NVMe検証コマンドは、2019年6月10日のNVMeクスプレス(商標)Base Specification, Revision 1.4のsection 6.14に記載されている。別の例として、NVMe Get LBA状態コマンドは、2019年6月10日のNVMeクスプレス(商標)Base Specification, Revision 1.4のsection 5.27に記載されている。しかしながら、このようなコマンドの実行は、潜在的にかなりの時間及び電力を消費する可能性がある。

#### 【図面の簡単な説明】

#### 【0011】

同様に番号付けされた要素は、異なる図で共通の構成要素を指す。

#### 【0012】

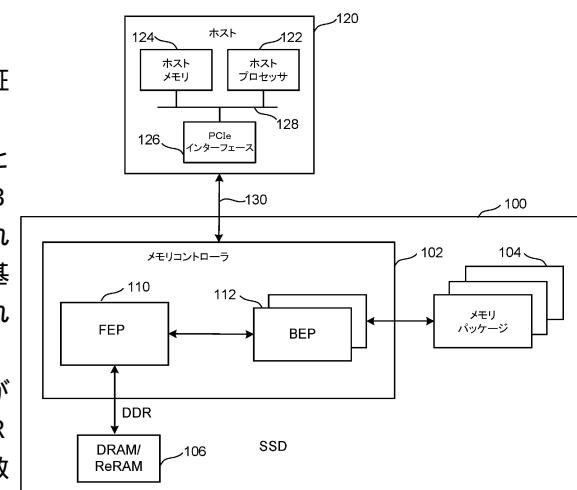

【図1A】ホストに接続された記憶システムの一実施形態のブロック図である。

#### 【0013】

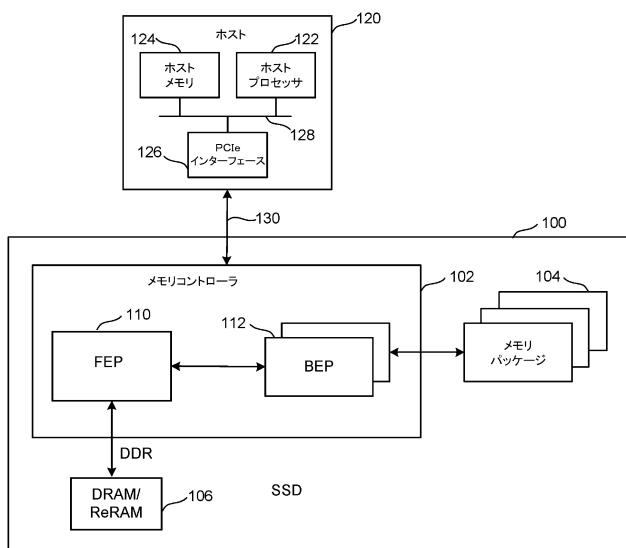

【図1B】フロントエンドプロセッサ回路の一実施形態のブロック図である。

#### 【0014】

10

20

30

40

50

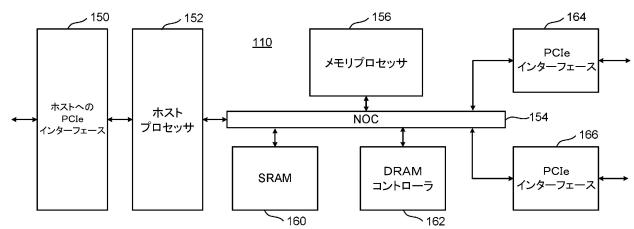

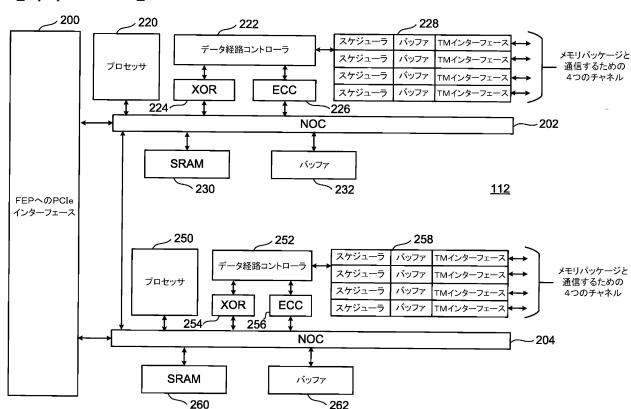

【図 2 A】バックエンドプロセッサ回路の一実施形態のブロック図である。

【0015】

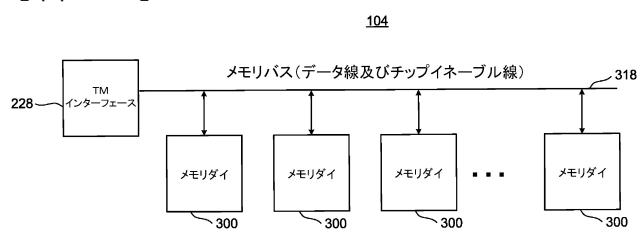

【図 2 B】メモリパッケージの一実施形態のブロック図である。

【0016】

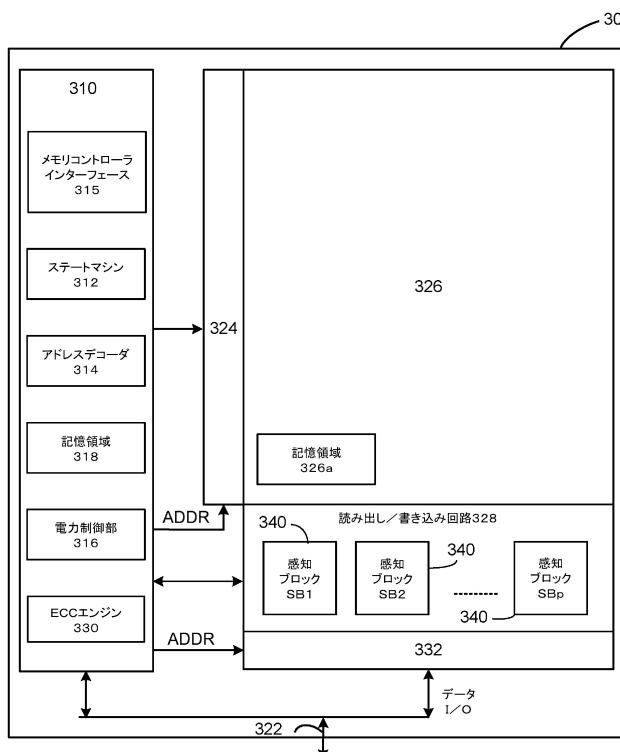

【図 3 A】メモリダイの一実施形態の機能ブロック図である。

【0017】

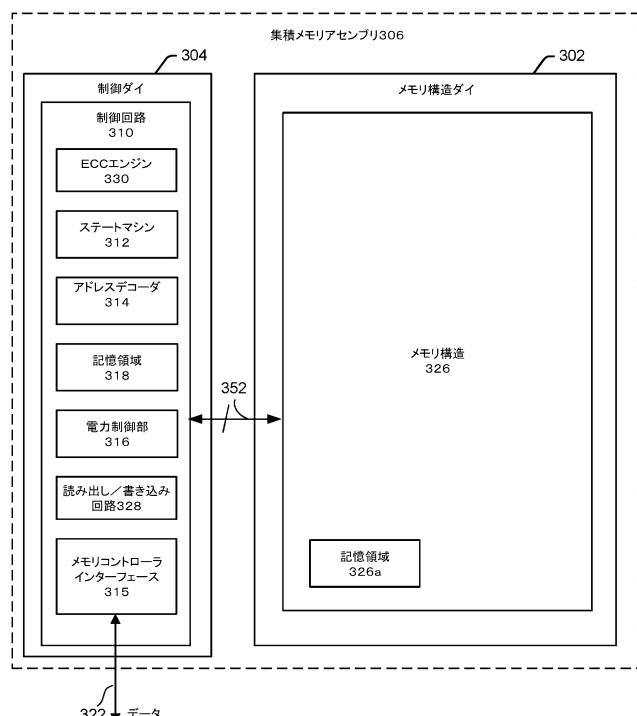

【図 3 B】集積メモリアセンブリの一実施形態の機能ブロック図である。

【0018】

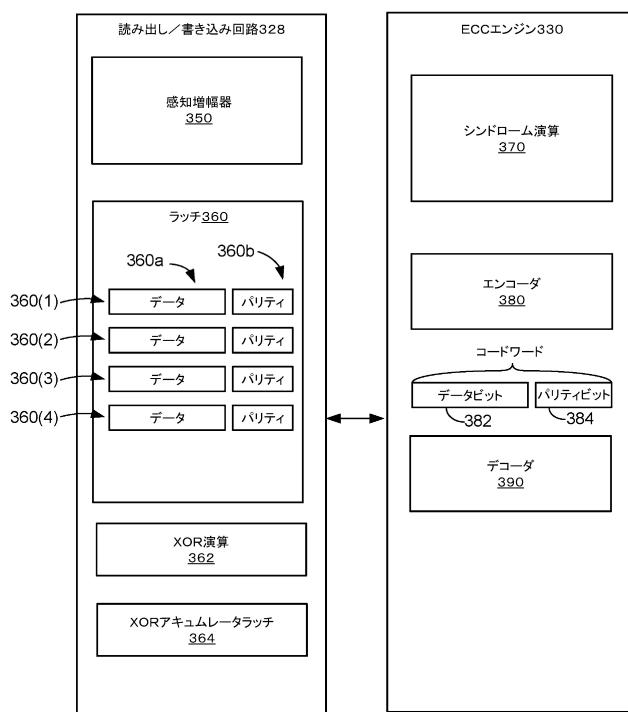

【図 3 C】集積メモリアセンブリの読み出し / 書き込み回路及び E C C の一実施形態のブロック図である。 10

【0019】

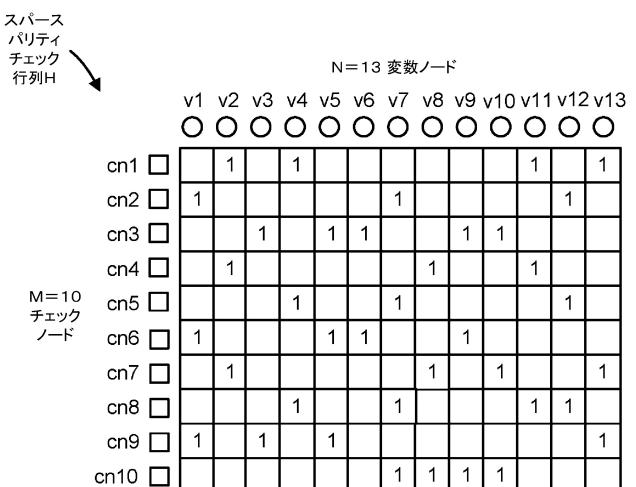

【図 3 D】スパースパリティチェック行列 H の一例を示す。

【0020】

【図 3 E】図 3 D のスパースパリティチェック行列に対応するスパース 2 部グラフを示す。

。

【0021】

【図 4】感知ブロックの一実施形態を示すブロック図である。

【0022】

【図 5 A】基板上に積層された集積メモリアセンブリの一実施形態の側面図を示す。 20

【0023】

【図 5 B】基板上に積層された集積メモリアセンブリの一実施形態の側面図を示す。

【0024】

【図 6】各メモリセルが 4 ビットのデータを記憶するときのメモリアレイの例示的な閾値電圧分布を示す。 20

【0025】

【図 7】不揮発性メモリセルに記憶されたデータの完全性を検証するプロセスの一実施形態を示すフローチャートである。

【0026】

【図 8】検証コマンドに応答する SW を決定するプロセスの一実施形態を示す。

【0027】

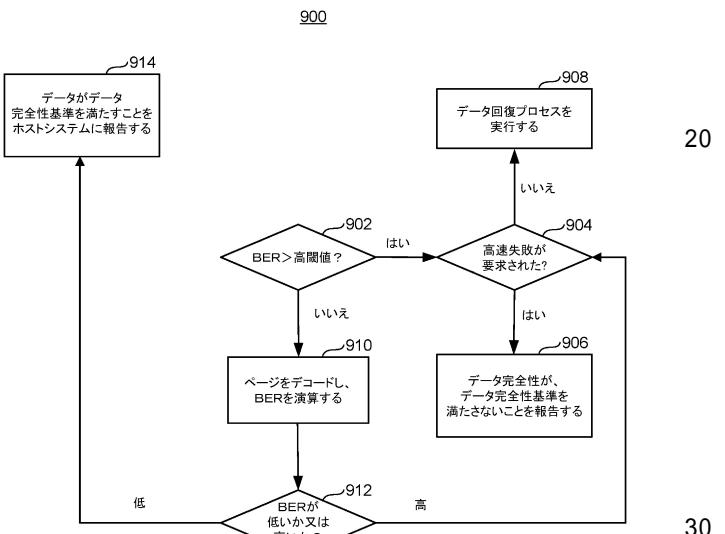

【図 9】SW が B E R を推定するために使用されるときに、検証コマンドに応答するプロセスの一実施形態のフローチャートである。 30

【0028】

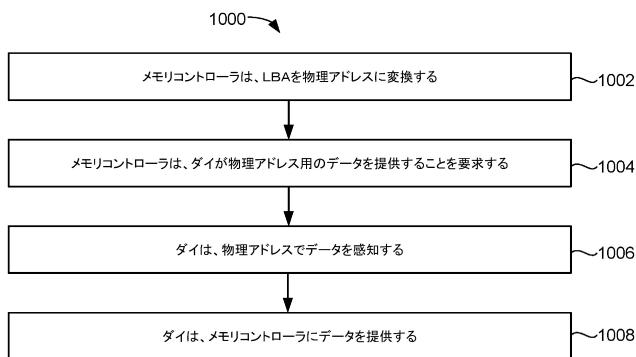

【図 10】検証されるデータのページを取得するメモリコントローラのプロセスの一実施形態のフローチャートである。

【0029】

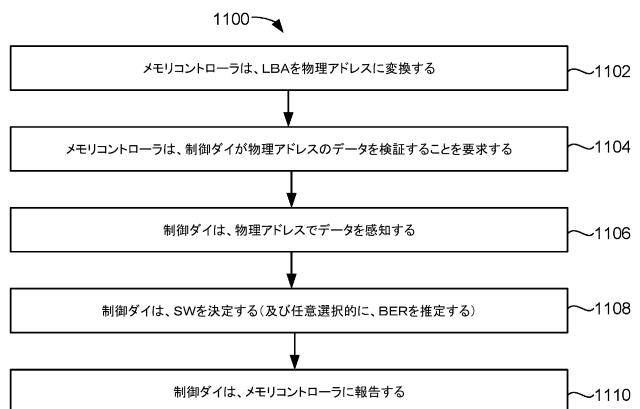

【図 11】検証コマンドに応答して、使用する SW を演算するプロセスの一実施形態のフローチャートである。

【0030】

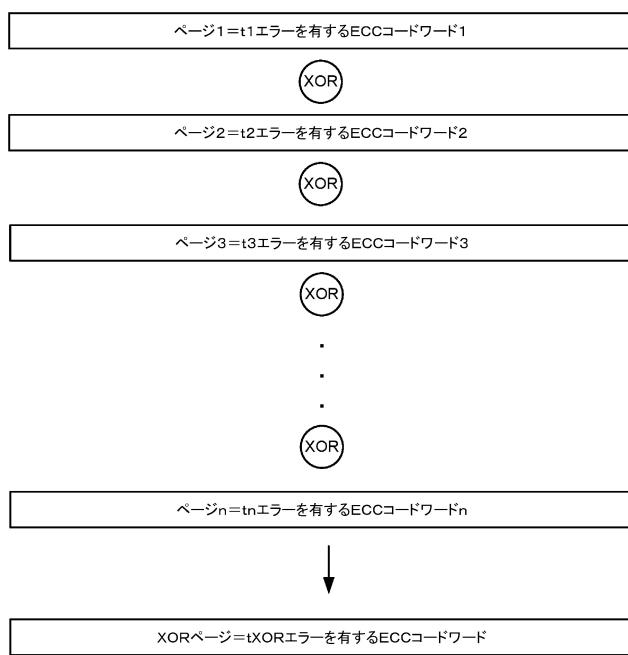

【図 12】X O R ページがどのように形成され得るかを示す図である。 40

【0031】

【図 13】X O R コードワードに基づいて、データの完全性を検証するプロセスの一実施形態のフローチャートである。

【0032】

【図 14】ダイが、メモリコントローラの X O R コードワードを形成して処理するプロセスの一実施形態のフローチャートである。

【0033】

【図 15】データのサンプルのチェックに基づいてデータの完全性を検証するプロセスの一実施形態のフローチャートである。

【0034】

10

20

30

40

50

【図16】図15のプロセスにおけるサンプルがワード線のサブセットであるプロセスの一実施形態のフローチャートである。

【0035】

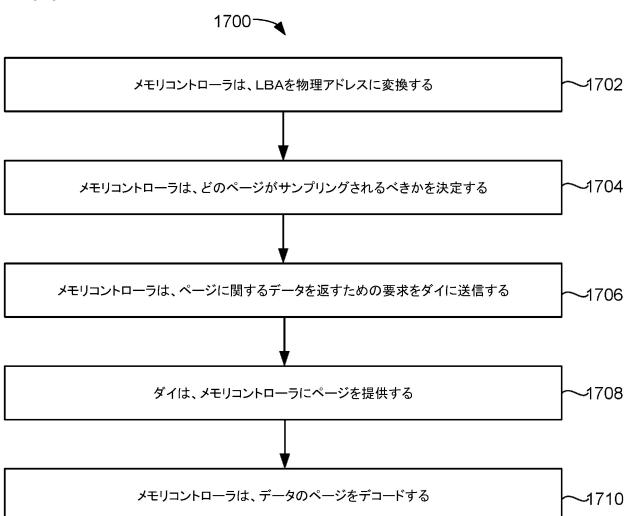

【図17】図15のプロセスにおけるサンプルがページのサブセットであるプロセスの一実施形態のフローチャートである。

【0036】

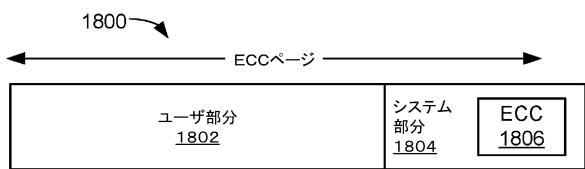

【図18A】ECCフィールドを含むECCページを概略的に示す。

【0037】

【図18B】4つのECCページを有するデータページを示す。

【0038】

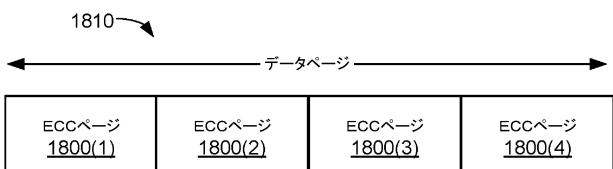

【図19】図15のプロセスにおけるサンプルが1ページ当たり1つのコードワードであるプロセスの一実施形態のフローチャートである。

10

【発明を実施するための形態】

【0039】

ここで、本技術が、図面を参照して説明され、それは実施形態において、不揮発性メモリセルのデータ完全性の高速検証に関する。一実施形態では、記憶システムは、ホストシステムからの検証コマンドに応答して、メモリセルに記憶されたデータの完全性を検証する。検証コマンドは、論理ブロックアドレス(logical block address、LBA)などによって、何らかの方法でデータを特定する。検証コマンドは、検証されるデータがリクエスタに返されないことを除いて、読み出しコマンドと同様であってもよい。したがって、記憶システムは、データをリクエスタに送信することなく、データ完全性を決定するためにメモリセルを感知してもよい。一実施形態では、記憶システムは、データの完全性がデータ完全性基準を満たすかどうかを報告する。例えば、記憶システムは、データにエラーがないかどうか、CECC(訂正可能なECCエラー)、訂正不可能なECC(uncorrectable ECC、UECC)を報告することができる。CECCとは、記憶されたデータにおいてエラー(例えば、ビットフリップ)が検出される場合を指すが、エラーは、データに関連するECCを使用することによって訂正可能である。UECCは、データに関連するECCを使用することによって、データ内のエラーが訂正されないときに発生する。検証コマンドのための1つの可能な使用事例としては、ホストインターフェースがデータを転送することによってボトルネックされることなく、記憶されたデータの低レベルのスクラップを実行することである。記憶システムは、劣化したデータを移動するか、又は再び書き込むことによって、CECCに反応し得る。したがって、検証コマンドは、同じ挙動をトリガすることができます。全体として、これにより、ファイルシステムレベルでのチェック合計スクラビング/検証の必要性が減少する。検証コマンドの例は、NVMe(不揮発性メモリエクスプレス)の検証コマンドである。しかしながら、検証コマンドは、他のメモリ仕様でも可能である。

20

【0040】

いくつかの実施形態では、データ完全性の高速検証は、通常読み出し動作に対して実行されるデータの正常な感知及びデコードの一部分のみを実行することによって行われる。一実施形態では、データを完全にデコードすることなく、検証されるデータに関連するビットエラー率(bit error rate、BER)の推定が行われる。推定されたBERが閾値を下回る場合、記憶システムは、データがデータ完全性基準を満たすことをホストシステムに報告する。データ完全性基準は、読み出しコマンドが、結果として報告されている特定の種類のエラーをもたらした可能性が高いかどうかに基づいてもよい。可能なエラーの例としては、CECC及び訂正不可能なECC(UECC)が挙げられるが、これらに限定されない。例えば、推定されたBERが、読み出しコマンドがエラーなし又はCECCのいずれかを返す可能性が高いことを示す場合、データ完全性基準は、データ基準が、データがECCによって訂正可能である場合に満たされる。いくつかの実施形態では、推定されたBERが閾値を上回る場合、記憶システムは、データを完全にデコードしてBERを決定し、データが、決定されたBERに基づいてデータ完全性基準を満たすかどうかを報

30

40

50

告する。したがって、少なくともデータが完全にデコードされていない場合は、データ完全性を検証する相当な時間及び電力が節約される。

#### 【0041】

一実施形態では、BERの推定は、データを完全にデコードすることなく、データのシンドローム重み(syndrome weight、SW)を最初に決定することによって行われる。次いで、BERは、SWに基づいて推定することができる。一実施形態では、BERの推定は、XORコードワードを作成するために、データの複数のコードワードのビット単位のXORを実行することによって行われる。次いで、XORコードワードのBERは、検証されるデータに関連するBERを推定するために決定される。一実施形態では、XORコードワードのSWは、XORコードワードのBERを推定するために決定される。検証されるデータに関連するBERは、XORコードワードの推定されたBERに基づいて推定され得る。一実施形態では、検証されるデータのサンプルのBERが作られる。例えば、サンプルは、1ページ当たり1つのコードワード、ワード線当たり1ページ、又はブロック内のワード線のサブセットなどであってもよい。

10

#### 【0042】

本発明は、多くの異なる形態で具現化されてもよく、本明細書に記載される実施形態に限定されるものとして解釈されるべきではないことが理解される。むしろ、これらの実施形態は、本開示が完璧かつ完全であり、本発明を当業者に十分に伝えるように提供される。実際、本発明は、添付の「特許請求の範囲」によって定義される本発明の範囲及び趣旨内に含まれる、これらの実施形態の代替物、修正、及び均等物を網羅することが意図される。更に、本発明の以下の詳細な説明において、本発明の完璧な理解を提供するために、数多くの具体的な詳細が記載される。しかしながら、本発明が、そのような具体的な詳細を伴わずに実施され得ることは、当業者には明らかであろう。

20

#### 【0043】

図1A～図3C及び図4～図5Bは、本明細書に開示される技術を実装するために使用することができる記憶システムの一例を説明する。図1Aは、ホストシステム120に接続された記憶システム100の一実施形態のブロック図である。記憶システム100は、本明細書に開示される技術を実装することができる。多くの異なる種類の記憶システムは、本明細書に開示される技術と共に使用することができる。一例では、記憶システムは、ソリッドステートドライブ(「solid state drive、SSD」)であり、しかしながら、他の種類の記憶システムも使用することができる。記憶システム100は、メモリコントローラ102、データを記憶するためのメモリパッケージ104、及びローカルメモリ(例えば、DRAM/ReRAM)106を含む。メモリコントローラ102は、フロントエンドプロセッサ回路(Front End Processor Circuit、FEP)110、及び1つ以上のバックエンドプロセッサ回路(Back End Processor Circuit、BEP)112を含む。一実施形態では、FEP回路110は、ASIC上に実装される。一実施形態では、各BEP回路112は、別個のASIC上に実装される。BEP回路112及びFEP回路110の各々のASICは、メモリコントローラ102がシステムオンチップ(「System on a Chip、SoC」)として製造されるように、同じ半導体上に実装される。FEP110及びBEP112は両方とも、それら自体のプロセッサを含む。一実施形態では、FEP110及びBEP112は、FEP110がマスターであり、各BEP112がスレーブであるマスタースレーブ構成として機能する。例えば、FEP回路110は、メモリ管理(例えば、ガベージコレクション、ウェアアレベリングなど)、論理アドレスから物理アドレスへの変換、ホストとの通信、DRAM(ローカル揮発性メモリ)の管理、及びSSD(又は他の不揮発性記憶システム)の全体動作の管理を実行するフラッシュ変換層を実装する。BEP回路112は、FEP回路110の要求でメモリパッケージ/ダイ内のメモリ動作を管理する。例えば、BEP回路112は、読み出し、消去、及びプログラミングプロセスを実行することができる。加えて、BEP回路112は、バッファ管理を実行し、FEP回路110によって要求された特定の電圧レベルを設定し、エラー訂正(ECC)を実行し、トグルモードインターフェースをメモリパッケージに制御す

30

40

50

ことなどができる。一実施形態では、各BEP回路112は、それ自体のメモリパッケージのセットに関与する。メモリコントローラ102は、制御回路の一例である。

#### 【0044】

一実施形態では、複数のメモリパッケージ104が存在する。各メモリパッケージ104は、1つ以上のメモリダイを含んでもよい。一実施形態では、メモリパッケージ104内の各メモリダイは、NANDフラッシュメモリ（2次元NANDフラッシュメモリ及び／又は3次元NANDフラッシュメモリを含む）を利用する。他の実施形態では、メモリパッケージ104は、他の種類のメモリを含むことができ、例えば、メモリパッケージは、位相変化メモリ（Phase Change Memory、PCM）メモリを含むことができる。

#### 【0045】

一実施形態では、メモリコントローラ102は、PCIエクスプレス（PCI Express、PCIe）を介してNVMエクスプレス（NVM Express、NVMe）を実装するインターフェース130を使用してホストシステム120と通信する。インターフェース130は、PCIeを介してNVMeを実装する必要はない。記憶システム100と共に動作するために、ホスト120は、ホストプロセッサ122、ホストメモリ124、及びバス128を介して通信するPCIeインターフェース126を含む。ホストメモリ124は、ホストの物理メモリであり、DRAM、SRAM、不揮発性メモリ、又は別の種類の記憶装置であってもよい。ホスト120は、記憶システム100の外部にあり、記憶システム100とは別個である。他の実施形態では、記憶システム100は、ホスト120内に埋め込まれる。

#### 【0046】

図1Bは、FEP回路110の一実施形態のブロック図である。図1Bでは、ホスト120と通信するためのPCIeインターフェース150、及びそのPCIeインターフェースと通信するホストプロセッサ152を示す。ホストプロセッサ152は、実装に好適な、当該技術分野において既知の任意の種類のプロセッサとすることができます。ホストプロセッサ152は、ネットワークオンチップ（network-on-chip、NOC）154と通信している。NOCは、典型的には、SoC内のコア間の集積回路上の通信サブシステムである。NOCは、同期及び非同期クロックドメインにまたがるか、又はクロックされていない非同期論理を使用することができます。NOC技術は、ネットワーキング理論及び方法をオンチップ通信に適用し、従来のバス及びクロスバー相互接続に顕著な改善をもたらす。NOCは、他の設計と比較して、SoCの拡張性、及び複雑なSoCの電力効率を向上させる。NOCのワイヤ及びリンクは、多くの信号によって共有される。NOC内の全てのリンクが異なるデータパケット上で同時に動作するため、高レベルの並列性が達成される。したがって、統合サブシステムの複雑性が増大し続けると、NOCは、以前の通信アーキテクチャ（例えば、専用のポイントツーポイント信号ワイヤ、共有バス、又はブリッジを有するセグメント化バス）と比較して、向上した性能（スループットなど）及び拡張性をもたらす。NOC154に接続され、NOC154と通信しているのは、メモリプロセッサ156、SRAM160、及びDRAMコントローラ162である。DRAMコントローラ162は、DRAM（例えば、DRAM106）を動作させ、かつ、これと通信するために使用される。SRAM160は、メモリプロセッサ156が使用するローカルRAMメモリである。メモリプロセッサ156は、FEP回路を実施し、様々なメモリ動作を実行するために使用される。また、NOCと通信しているのは、2つのPCIeインターフェース164及び166である。図1Bの実施形態では、メモリコントローラ102は、2つのBEP回路112を含み、したがって、2つのPCIeインターフェース164／166が存在する。各PCIeインターフェースは、BEP回路112のうちの1つと通信する。他の実施形態では、3つ以上、又は2つ未満のBEP回路112が存在することができ、したがって、3つ以上のPCIeインターフェースが存在することができる。

#### 【0047】

図2Aは、BEP回路112の一実施形態のブロック図である。図2Aでは、FEP回路

10

20

30

40

50

110と通信する（例えば、図1BのPCIeインターフェース164及び166のうちの1つと通信する）ためのPCIeインターフェース200を示す。PCIeインターフェース200は、2つのNOC202及び204と通信している。一実施形態では、2つのNOCを、1つの大きなNOCと組み合わせることができる。各NOC（202/204）は、SRAM（230/260）、バッファ（232/262）、プロセッサ（220/250）、及びXORエンジン（224/254）、ECCエンジン（226/256）を介してデータ経路コントローラ（222/252）に接続されている。

#### 【0048】

ECCエンジン226/256は、当該技術分野において既知のように、エラー訂正を実行するために使用される。本明細書では、ECCエンジン226/256は、コントローラのECCエンジンと呼ばれることがある。XORエンジン224/254は、データが、プログラミングエラーがある場合に回復することができる様式で組み合わされ、記憶することができるよう、データをXOR演算するために使用される。一実施形態では、XORエンジン224/254は、ECCエンジン226/256を使用してデコードできないデータを回復することができる。いくつかの実施形態では、ECCエンジン226/256は、コードワードのSWを決定するように構成されている。いくつかの実施形態では、プロセッサ（220/250）は、本明細書に記載されるように、検証されるデータのBERを推定するように構成されている。プロセッサ（220/250）は、データの完全性が、推定されたBERに基づいてデータ完全性基準を満たすかどうかを報告してもよい。

10

20

30

40

#### 【0049】

データ経路コントローラ222は、集積メモリアセンブリを有する4つのチャネルを介して通信するためのメモリインターフェース228に接続されている。したがって、上部NOC202は、メモリパッケージと通信するための4つのチャネル用のメモリインターフェース228に関連付けられ、下部NOC204は、メモリパッケージと通信するための4つの追加のチャネル用のメモリインターフェース258に関連付けられている。一実施形態では、各メモリインターフェース228/258は、4つのトグルモードインターフェース（Toggle Mode interface、TMインターフェース）、4つのバッファ、及び4つのスケジューラを含む。チャネルの各々について、1つのスケジューラ、バッファ、及びTMインターフェースが存在する。プロセッサは、当該技術分野において既知の任意の標準プロセッサとすることができます。データ経路コントローラ222/252は、プロセッサ、FPGA、マイクロプロセッサ、又は他の種類のコントローラとすることができます。XORエンジン224/254及びECCエンジン226/256は、ハードウェアアクセラレータとして知られている専用ハードウェア回路である。他の実施形態では、XORエンジン224/254、ECCエンジン226/256は、ソフトウェアで実装することができる。スケジューラ、バッファ、及びTMインターフェースは、ハードウェア回路である。他の実施形態では、メモリインターフェース（メモリダイと通信するための電気回路）は、図2Aに示すものとは異なる構造とすることができます。加えて、図1B及び図2Aとは異なる構造を有するコントローラはまた、本明細書に記載される技術と共に使用することができる。

#### 【0050】

図2Bは、メモリバス（データ線及びチップインテーブル線）322に接続された複数のメモリダイ300を含むメモリパッケージ104の一実施形態のブロック図である。メモリバス322は、BEP回路112のTMインターフェースと通信するためのトグルモードインターフェース228に接続している（例えば、図2Aを参照）。いくつかの実施形態では、メモリパッケージは、メモリバス及びTMインターフェースに接続された小型コントローラを含むことができる。合計で、メモリパッケージ104は、8つ又は16個のメモリダイを有してもよく、しかしながら、他の数のメモリダイもまた実装することができる。本明細書に記載される技術は、任意の特定の数のメモリダイに限定されない。

#### 【0051】

50

図3Aは、メモリダイ300の一実施形態の機能ブロック図である。図2Bの1つ以上のメモリダイ300の各々は、図3Aのメモリダイ300として実装することができる。図3Aに示す構成要素は、電気回路である。一実施形態では、各メモリダイ300は、メモリ構造326、制御回路310、読み出し/書き込み回路328、及びデコーダ324/332を含み、これらは全て電気回路である。メモリ構造326は、行デコーダ324を介してワード線によりアドレス指定可能であり、列デコーダ332を介してビット線によりアドレス指定可能である。読み出し/書き込み回路328は、SB1、SB2、...、SBp(感知回路)など複数の感知ブロック340を含み、複数のメモリセル内のデータのページ(又は複数のページ)が並列に読み出し又はプログラムされることを可能にする。一実施形態では、各感知ブロックは、感知増幅器と、ビット線に接続された1セットのラッチと、を含む。ラッチは、書き込みされたデータ及び/又は読み出しされたデータを記憶する。感知ブロックは、ビット線ドライバを含む。

10

#### 【0052】

コマンド及びデータは、メモリコントローラインターフェース315(「通信インターフェース」とも呼ばれる)を介してコントローラ102とメモリダイ300との間で転送される。メモリコントローラインターフェース315は、メモリコントローラ102と通信するための電気的インターフェースである。メモリコントローラインターフェース315の例としては、トグルモードインターフェース及びオープンNANDフラッシュインターフェース(Open NAND Flash Interface、ONFI)が挙げられる。他のI/Oインターフェースも使用することができる。例えば、メモリコントローラインターフェース315は、メモリコントローラ102用のメモリインターフェース228/258のトグルモードインターフェースに接続しているトグルモードインターフェースを実装してもよい。一実施形態では、メモリコントローラインターフェース315は、メモリバス322に接続する1セットの入力及び/又は出力(input and/or output、I/O)ピンを含む。一実施形態では、メモリバス322は、トグルモードインターフェースの一部としてメモリコントローラ102に接続している。

20

#### 【0053】

制御回路310は、読み出し/書き込み回路328と協働して、メモリ構造326上でメモリ動作(例えば、書き込み、読み出し、消去、及びその他)を実行する。一実施形態では、制御回路310は、ステートマシン312、オンチップアドレスデコーダ314、電力制御部316、メモリコントローラインターフェース315、及び記憶領域318を含む。ステートマシン312は、メモリ動作のダイレベル制御を提供する。一実施形態では、ステートマシン312は、ソフトウェアによってプログラム可能である。他の実施形態では、ステートマシン312は、ソフトウェアを使用せず、ハードウェア(例えば、電気回路)内に完全に実装される。いくつかの実施形態では、ステートマシン312をマイクロコントローラ又はマイクロプロセッサに置き換えることができる。一実施形態では、制御回路310は、レジスタ、ROMヒューズ、並びにベース電圧及び他のパラメータなどのデフォルト値を記憶するための他の記憶デバイスなどのバッファを含む。デフォルト値及び他のパラメータは、メモリ構造326の領域(例えば、構造パラメータ記憶部326a)に記憶することができる。これらのデフォルト値は、隨時更新されてもよい。

30

#### 【0054】

オンチップアドレスデコーダ314は、コントローラ102によって使用されるアドレスと、デコーダ324及び332によって使用されるハードウェアアドレスとの間にアドレスインターフェースを提供する。電力制御部316は、メモリ動作中にワード線及びビット線に供給される電力及び電圧を制御する。電力制御部316は、電圧を生成するための電荷ポンプを含み得る。

40

#### 【0055】

記憶領域318は、メモリ構造326を動作させるためのパラメータを記憶するために使用されてもよい。記憶領域318は、揮発性メモリ又は不揮発性メモリを含んでもよい。いくつかの実施形態では、パラメータは、読み出し基準電圧を含む。一実施形態では、記

50

憶領域 318 は、SW を B E R に相關させるルックアップテーブルを含む。メモリ構造 326 は、記憶領域 326a を有し、記憶領域 326a はまた、メモリ構造 326 を動作させるためのパラメータのコピーを含んでもよい。いくつかの実施形態では、パラメータは、メモリダイ300 が電源オンされたときに、記憶領域 326a から記憶領域 318 にコピーされる。

#### 【 0056 】

本明細書の目的のために、制御回路 310 は、単独で、又は読み出し / 書き込み回路 328 及びデコーダ 324 / 332 と組み合わせて、メモリ構造 326 に接続された制御回路を含む。制御回路は、フローチャートで以下に説明する機能を実行する電気回路である。他の実施形態では、制御回路は、ソフトウェア（例えば、ファームウェア）と組み合わせた電気回路であるコントローラ 102（又は他のコントローラ）のみから構成することができ、フローチャートで以下に説明される機能を実行する。一実施形態では、制御回路は、コントローラであり、このコントローラは、ハードウェアを使用しない電気回路である。別の代替例では、制御回路は、コントローラ 102、及びフローチャートで以下に説明される機能を実行する制御回路 310 を含む。別の実施形態では、制御回路は、ステートマシン 312（及び / 又はマイクロコントローラ及び / 又はマイクロプロセッサ）を単独で、又はコントローラ 102 と組み合わせて含む。別の代替例では、制御回路は、コントローラ 102、制御回路 310、読み出し / 書き込み回路 328、及びフローチャートで以下に説明される機能を実行するデコーダ 324 / 332 を含む。他の実施形態では、制御回路は、不揮発性メモリを動作させる 1 つ以上の電気回路を含む。

10

20

30

40

50

#### 【 0057 】

一実施形態では、メモリ構造 326 は、ウェハなど单一基板上に複数のメモリレベルが形成される不揮発性メモリセルのモノリシック 3 次元メモリアレイを備える。メモリ構造は、シリコン（又は他の種類の）基板上に配置された活性領域を有する、1 つ以上の物理レベルのメモリセルアレイにモノリシックに形成される、任意の種類の不揮発性メモリを備え得る。一例では、メモリ構造 326 の不揮発性メモリセルは、例えば米国特許第 9,721,662 号に記載されているような電荷トラップ材料を有する垂直 N A N D ストリングを備え、その全体は参照により本明細書に組み込まれる。別の実施形態では、メモリ構造 326 は、不揮発性メモリセルの 2 次元メモリアレイを備える。一例では、不揮発性メモリセルは、例えば米国特許第 9,082,502 号に記載されているような浮動ゲートを利用する N A N D フラッシュメモリセルであり、その全体は参照により本明細書に組み込まれる。他の種類のメモリセル（例えば、N O R 型フラッシュメモリ）も使用することができる。

#### 【 0058 】

メモリ構造 326 に含まれるメモリアレイアーキテクチャ又はメモリセルの正確な種類は、上記の例に限定されない。多くの異なる種類のメモリアレイアーキテクチャ又はメモリセル技術を使用して、メモリ構造 326 を形成することができる。本明細書で提案された新たに特許請求される実施形態の目的には、特定の不揮発性メモリ技術は必要とされない。メモリ構造 326 のメモリセルに好適な技術の他の例として、R e R A M メモリ、磁気抵抗メモリ（例えば、M R A M、スピントランスマートルクM R A M、スピントルクM R A M）、位相変化メモリ（例えば P C M）などが挙げられる。メモリ構造 326 のアーキテクチャに好適な技術の例として、2 次元アレイ、3 次元アレイ、クロスポイントアレイ、積層型 2 次元アレイ、垂直ビット線アレイなどが挙げられる。

#### 【 0059 】

R e R A M 又は P C M R A M、クロスポイントメモリの一例として、X 線及び Y 線（例えば、ワード線及びビット線）によってアクセスされるクロスポイントアレイに配置された可逆抵抗スイッチング素子が挙げられる。別の実施形態では、メモリセルは、導電性ブリッジメモリ素子を含み得る。導電性ブリッジメモリ素子はまた、プログラム可能なメタライゼーションセルと呼ばれ得る。導電性ブリッジメモリ素子は、固体電解質内のイオンの物理的再配置に基づく状態変化素子として使用され得る。場合によっては、導電性ブリッ

ジメモリ素子は、2つの電極間に固体電解質薄膜を有する、2つの固体金属電極を含んでもよく、一方は、比較的不活性であり（例えば、タンゲステン）、他方は、電気化学的に活性である（例えば、銀又は銅）。温度が上昇すると、イオンの移動度も増加し、導電性ブリッジメモリセルのプログラミング閾値が低下する。したがって、導電性ブリッジメモリ素子は、温度に対して広範囲のプログラミング閾値を有し得る。

#### 【0060】

磁気抵抗メモリ（Magnetoresistive memory、MRAM）は、磁気記憶素子によってデータを記憶する。素子は、各々が薄い絶縁層によって分離された磁化を保持することができる、2つの強磁性プレートから形成される。2つのプレートのうちの1つは、特定の極性に設定された永久磁石である。他方のプレートの磁化は、メモリを記憶するために外場の磁化と一致するように変更することができる。記憶デバイスは、このようなメモリセルのグリッドから構築される。プログラミングのための一実施形態では、各メモリセルは、互いに直角に、セルに平行に、セルの1つ上及び1つ下に配置された一対の書き込み線の間にある。電流がそれらを通過すると、誘導磁場が生成される。

10

#### 【0061】

位相変化メモリは、カルコゲナイトガラス特有の挙動を利用する。一実施形態は、Ge<sub>2</sub>Si<sub>2</sub>T<sub>e</sub>5合金を使用して、位相変化材料を電気加熱することによって位相変化を達成する。複数回のプログラミングは、異なる振幅及び／又は長さの電気パルスであって、異なる抵抗値の位相変化材料をもたらす。

20

#### 【0062】

当業者であれば、本明細書に記載されるこの技術は単一の特定のメモリ構造に限定されず、本明細書に記載され、当業者によって理解されるように、技術の趣旨及び範囲内で、多くの関連するメモリ構造をカバーすることを理解するであろう。

#### 【0063】

図3Bは、集積メモリアセンブリ306の一実施形態の機能ブロック図を示す。集積メモリアセンブリ306は、記憶システム100内のメモリパッケージ104に使用されてもよい。一実施形態では、集積メモリアセンブリ306は、2種類の半導体ダイ（又はより簡潔に「ダイ」）を含む。メモリ構造ダイ302は、メモリ構造326を含む。メモリ構造326は、不揮発性メモリセルを含んでもよい。制御ダイ304は、制御回路310を含む。いくつかの実施形態では、制御ダイ304は、メモリ構造ダイ302内のメモリ構造326に接続するように構成されている。例えば、制御回路310は、メモリ構造ダイ302内のメモリ構造326内の不揮発性メモリセルに接続されるように構成されている。いくつかの実施形態では、メモリ構造ダイ302及び制御ダイ304は、一緒に接合されている。制御回路310は、ステートマシン312、アドレスデコーダ314、電力制御部316、メモリコントローラインインターフェース315、記憶領域318、及びECCエンジン330を含む。記憶領域は、読み出し基準電圧などのパラメータを記憶してもよい。制御回路310はまた、読み出し／書き込み回路328を含む。別の実施形態では、読み出し／書き込み回路328の一部分は、制御ダイ304上に位置付けされ、読み出し／書き込み回路328の一部分は、メモリ構造ダイ302上に位置付けされる。本明細書で使用される装置という用語は、メモリダイ300、制御ダイ304、メモリパッケージ104、記憶システム100、メモリコントローラ102、又は記憶システム100を含むホストシステム120を含み得るが、これらに限定されない。

30

#### 【0064】

ECCエンジン330は、コードワードをデコード及びエラー訂正するように構成されている。本明細書では、ECCエンジン330は、オンダイECCエンジンと呼ばれることがある。一実施形態では、オンダイECCエンジン330は、メモリコントローラ102からのデータビットを、データビット及びパリティビットを含むコードワードにエンコードするように構成されている。制御回路は、メモリ構造326内にコードワードを記憶する。一実施形態では、オンダイECCエンジン330は、メモリ構造326から読み返されるコードワードをデコードするように構成されている。

40

50

**【 0 0 6 5 】**

制御ダイ 3 0 4 の制御回路 3 1 0 内の構成要素の任意のサブセットは、制御回路と見なすことができる。別の代替例では、制御回路は、コントローラ 1 0 2 、及びフロー・チャートで以下に説明される機能を実行する制御ダイ 3 0 4 の制御回路 3 1 0 を含む。制御回路は、ハードウェアのみ、又はハードウェアとソフトウェア（ファームウェアを含む）との組み合わせを含むことができる。例えば、ファームウェアによってプログラマされたコントローラは、制御回路の一例である。制御回路は、プロセッサ、プログラマブルゲートアレイ（programmable gate array、P G A）、フィールドプログラマブルゲートアレイ（field programmable gate array、F P G A）、特定用途向け集積回路（application specific integrated circuit、A S I C）、集積回路、又は他の種類の回路を含むことができる。

10

**【 0 0 6 6 】**

経路 3 5 2 は、制御回路 3 1 0 内の 1 つ以上の構成要素とメモリ構造ダイ 3 0 2 上のメモリ構造との間の経路である。経路は、信号（例えば、電圧、電流）を提供又は受信するために使用され得る。経路は、導電性経路を含む。経路は、ボンドパッド、金属相互接続、ビア、トランジスタ、導電性材料、及び電気信号を転送又は搬送し得る他の材料のうちの 1 つ以上を含み得るが、これらに限定されない。経路を使用して、メモリ構造 3 2 6 内で読み出されたメモリセルに接続された選択されたワード線に、電力制御部 3 1 6 からの読み出し基準電圧を提供してもよい。

20

**【 0 0 6 7 】**

一実施形態では、集積メモリアセンブリ 3 0 6 は、メモリバス 3 2 2 に接続する 1 セットの入力及び／又は出力（I / O）ピンを含む。メモリバス 3 2 2 は、メモリコントローラインターフェース 3 1 5 に接続されているように図示されている。

**【 0 0 6 8 】**

図 3 C は、制御ダイ 3 0 4 の読み出し／書き込み回路 3 2 8 及び E C C エンジン 3 3 0 の一実施形態のブロック図である。いくつかの実施形態では、メモリダイ 3 0 0 は、図 3 C に示す読み出し／書き込み回路 3 2 8 を有するが、E C C エンジン 3 3 0 を有さない。読み出し／書き込み回路 3 2 8 は、感知增幅器 3 5 0 及びラッチ 3 6 0 を有する。ラッチ 3 6 0 は、データラッチ 3 6 0 a 及びパリティラッチ 3 6 0 b を含んでもよい。一実施形態では、データラッチ 3 6 0 a は、コードワードのデータビットを記憶し、パリティラッチは、コードワードのパリティビットを記憶する。パリティビットは、エラー訂正コード（E C C）を含んでもよい。データビット及びパリティビットに対して特定のラッチが存在することは必須ではない。図 3 C は、4 セットのデータラッチ 3 6 0 ( 1 )、3 6 0 ( 2 )、3 6 0 ( 3 )、3 6 0 ( 4 ) を示す。各セットを使用して、異なるページのコードワードを記憶してもよい。メモリセル当たり 4 ビットが記憶される実施形態では、メモリセルのセットに 4 ページが記憶される。これらの 4 ページは、下部ページ（lower page、L P）、下部中央ページ（lower-middle page、L M P）、上部中央ページ（upper-middle page、U M P）、及び上部ページ（upper page、U P）と呼ばれることがある。別の実施形態では、感知增幅器 3 5 0 は、メモリ構造ダイ 3 0 2 上にあるが、ラッチ 3 6 0 は、制御ダイ 3 0 4 上にある。

30

**【 0 0 6 9 】**

X O R 演算器 3 6 2 は、2 つのコードワードのビット単位の X O R を形成することができる。ビット単位の X O R はまた、和モジュロ 2 と呼ばれることもある。ビット単位の X O R の結果は、X O R アキュムレータラッチ 3 6 4 に記憶される。一実施形態では、コードワードのうちの 1 つは、ラッチのセット 3 6 0 のうちの 1 つから取得され、他のコードワードは、X O R アキュムレータラッチ 3 6 4 から取得される。

40

**【 0 0 7 0 】**

オンダイ E C C エンジン 3 3 0 は、メモリコントローラ 1 0 2 から受信したデータビットをエンコードすることができる。一実施形態では、オンダイ E C C エンジン 3 3 0 は、データビット及びパリティビットを各々含むコードワードを形成する。一実施形態では、メ

50

モリコントローラ 102 は、コードワードを制御ダイ 304 に提供する。制御回路 310 は、メモリ構造 326 内の不揮発性メモリセルにコードワードを記憶する。メモリコントローラ 102 からデータを読み出す要求時に、制御回路 310 は、メモリ構造 326 からコードワードを読み出す。オンダイ ECC エンジン 330 はまた、メモリ構造 326 から読み出されたコードワードをデコード及びエラー訂正することもできる。いくつかの実施形態では、オンダイ ECC エンジン 330 は、記憶されているデータの各ユニット（例えば、ページ）についてパリティビットを演算する。パリティビット（エラー訂正コードとも呼ばれる）は、データのユニット（例えば、ページ）と共に記憶され得る。データのユニットとその関連するパリティビットとの組み合わせは、コードワードと呼ばれる。一実施形態において、パリティビットは、データのユニット（例えば、ページ）から離れて記憶される。

10

#### 【0071】

オンダイ ECC エンジン 330 は、シンドローム演算論理 370、エンコーダ 380、及びデコーダ 390 を含む。エンコーダ 380 は、リードソロモンエンコーダ、Boisse-Chaudhuri-Hocquenghem (BCH) エンコーダ、低密度パリティチェック (low-density parity check, LDPC) エンコーダ、ターボコードエンコーダ、1つ以上の他の ECC エンコードスキームをエンコードするように構成されたエンコーダ、又はこれらの任意の組み合わせなどの ECC スキームを使用してデータをエンコードするように構成されている。エンコーダ 380 は、データビット 382 及びパリティビット 384 を含むコードワードを形成してもよい。データビットは、メモリコントローラ 102 によって提供されてもよい。

20

#### 【0072】

一実施形態では、データビット 382 は、データラッチ 360a 内に記憶され、パリティビット 384 は、パリティラッチ 360b 内に記憶される。ラッチ 360 内のビットに基づいて、感知增幅器 350 は、メモリセルがプログラムされているときに、メモリ構造 326 内のビット線電圧を制御してもよい。このようにして、コードワードは、メモリ構造 326 内のメモリセルにプログラムされてもよい。また、他の電圧は、プログラミング用に選択されたメモリセルにプログラム電圧を印加するなど、メモリ構造 326 に印加されてもよいことが理解されるであろう。

30

#### 【0073】

デコーダ 390 は、メモリ構造ダイ 302 に記憶されたコードワードをデコードするように構成されている。一実施形態では、感知增幅器 350 は、コードワードを読み出すために、メモリ構造 326 内のビット線を感知する。感知增幅器 350 は、読み出したコードワードをラッチ 360 に記憶してもよい。デコーダ 390 は、コードワード内のエラーを検出し、訂正することができる。一実施形態では、デコーダ 390 は、メモリコントローラ 102 上のデコーダと比較して、比較的低電力のデコーダである。一実施形態では、メモリコントローラ 102 上のデコーダは、デコーダ 390 によって典型的に訂正され得るよりも、コードワード内により多くのビットエラーを訂正することができる。したがって、デコーダ 390 は、電力とエラー訂正能力との妥協点を提供することができる。例えば、デコーダ 390 は、消費電力に対しては非常に効率的であり得るが、コードワード内の多数のエラーを訂正することができない場合がある。

40

#### 【0074】

いくつかの実施形態は、デコーダ 390 は、ビット（又は可変）ノード及びチェックノードを有するスペース 2 部グラフに基づく。デコーダ 390 は、ビットノードとチェックノードとの間でメッセージを渡し得る。いくつかの実施形態では、ビットノードとチェックノードとの間でメッセージを渡すことは、メッセージパッシング計算を実行することによって達成される。メッセージパッシング計算は、確率伝搬法に基づき得る。

#### 【0075】

シンドローム演算論理 370 は、コードワードの SW を決定することができる。SW は、パリティチェック方程式が満たされていない数を指す。パリティチェック方程式は、図 3

50

D 及び図 3 E に関連してより詳細に論じられる。コードワードの SW は、そのコードワードの BER と相関し得る。したがって、制御ダイ 304 は、SW に基づいてコードワードの BER を推定することができる。一実施形態では、シンドローム演算論理 370 は、ハードウェアで実装される。SW は、コードワードを完全にデコードすることなく決定することができる。したがって、SW は、コードワードをデコードするよりも少ない時間及びより少ない電力で演算することができる。

#### 【0076】

上述したように、いくつかの実施形態では、オンダイ ECC エンジン 330 は、スパースパリティチェック行列を使用する。コントローラ 102 上の ECC 226 / 256 はまた、スパースパリティチェック行列を実装することができることにも留意されたい。図 3 D 10 は、スパースパリティチェック行列 H (スパースの 2 部グラフとしても表すことができる) の一例を示す。行列は、M 行 K + M 列を含み、これは、長さ N = K + M の各コードワードにおける K 個の情報ビット及び M 個のパリティビットに対応している。更に、パリティビットは、M 個のパリティチェック方程式が満たされるように定義され、行列の各行は、パリティチェック方程式を表す。

#### 【0077】

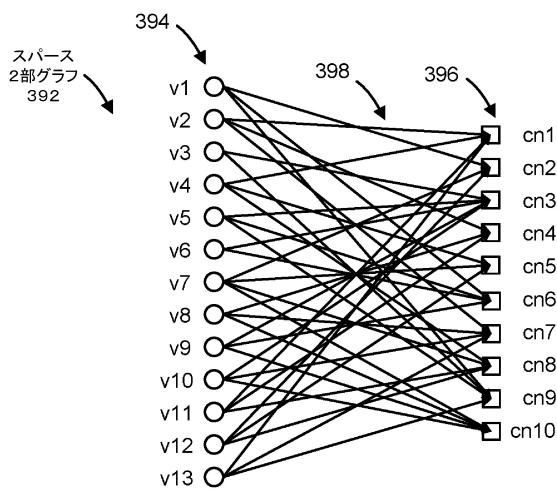

図 3 E は、図 3 D のスパースパリティチェック行列に対応するスパース 2 部グラフ 392 を示す。具体的には、コードは、N ビットノード 394 のセット V (この例では N = 13 )、M 個のチェックノード 396 のセット C (この例では M = 10 )、及びビットノード 394 をチェックノード 396 に接続するエッジ 398 のセット E (この例では E = 38 ) を備えたスパース 2 部グラフ G = (V、C、E) によって定義することができる。ビットノードはコードワードビットに対応し、チェックノードはビットに対するパリティチェック制約に対応する。ビットノード 394 は、エッジ 398 によって、参加するチェックノード 396 に接続される。 20

#### 【0078】

デコード中、デコーダ 390 の一実施形態は、パリティチェックを満たすことを試みる。この例では、チェックノード cn1 ~ cn10 によって示されるように、10 個のパリティチェックが存在する。cn1 での第 1 のパリティチェックは、

#### 【数 1】

$$v2 \oplus v4 \oplus v11 \oplus v13 = 0$$

30

であるかどうかを決定し、

#### 【数 2】

「⊕」

は、排他的 OR (XOR) 論理演算を示す。このチェックは、可変ノード v2、v4、v11 及び v13 に対応するビット内に偶数個の「1」が存在する場合に満たされる。このチェックは、可変ノード v2、v4、v11 及び v13 からの矢印が、2 部グラフ内のチェックノード cn1 に接続されているという事実によって示される。cn2 での第 2 のパリティチェックは、 40

#### 【数 3】

$$v1 \oplus v7 \oplus v12 = 0$$

であるかどうかを決定し、cn3 での第 3 のパリティチェックは、

#### 【数 4】

$$v3 \oplus v5 \oplus v6 \oplus v9 \oplus v10 = 0$$

40

であるかどうかを決定し、cn4 での第 4 のパリティチェックは、

#### 【数 5】

$$v2 \oplus v8 \oplus v11 = 0$$

50

であるかどうかを決定し、c n 5 での第 5 のパリティチェックは、

【数 6】

$$v4 \oplus v7 \oplus v12 = 0$$

であるかどうかを決定し、c n 6 での第 6 のパリティチェックは、

【数 7】

$$v1 \oplus v5 \oplus v6 \oplus v9 = 0$$

であるかどうかを決定し、c n 7 での第 7 のパリティチェックは、

【数 8】

$$v2 \oplus v8 \oplus v10 \oplus v13 = 0$$

10

であるかどうかを決定し、c n 8 での第 8 のパリティチェックは、

【数 9】

$$v4 \oplus v7 \oplus v11 \oplus v12 = 0$$

であるかどうかを決定し、c n 9 での第 9 のパリティチェックは、

【数 10】

$$v1 \oplus v3 \oplus v5 \oplus v13 = 0$$

20

であるかどうかを決定し、c n 10 での第 10 のパリティチェックは、

【数 11】

$$v7 \oplus v8 \oplus v9 \oplus v10 = 0$$

であるかどうかを決定する。

【0079】

一実施形態では、デコーダ 390 は、反復メッセージパッシングデコードアルゴリズムを伴う反復確率デコードプロセスを使用する。これらのアルゴリズムは、コードを表す下にある 2 部グラフのエッジを介してビットノードとチェックノードとの間でメッセージを交換することによって動作する。

30

【0080】

デコーダ 390 は、(メモリ構造 326 から読み出された内容に基づいて) コードワードビットの初期推定値を提供することができる。これらの初期推定値は、有効なコードワードとしてビットが満たされるべきであるパリティックチェック制約を課すことによって改良及び改善され得る。これは、グラフエッジに沿って渡されるメッセージを使用して、コードワードビットを表すビットノードと、コードワードビットに対するパリティック制約を表すチェックノードとの間で情報を交換することによって行われ得る。

30

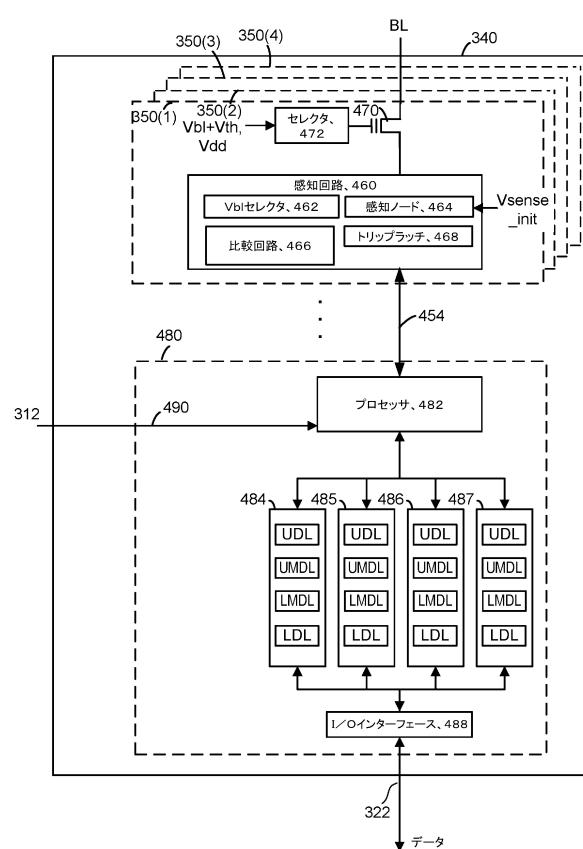

【0081】

図 4 は、感知ブロック 340 の一実施形態を示すブロック図である。感知ブロックは、読み出し / 書き込み回路 328 の一部である。個々の感知ブロック 340 は、感知回路又は感知増幅器 350 (1) ~ 350 (4) として参照される 1 つ以上のコア部分と、管理回路 480 として参照される共通部分とに区画化されている。一実施形態では、各ビット線 / NAND ストリングのための別個の感知回路と、1 セットの複数、例えば、4 個又は 8 個の感知回路のための 1 つの共通の管理回路 480 とが存在する。グループ内の各感知回路は、データバス 454 を介して関連する管理回路と通信する。したがって、1 セットの記憶素子 (メモリセル) の感知回路と通信する 1 つ以上の管理回路が存在する。

40

【0082】

一例として、感知増幅器 350 (1) は、接続されたビット線における伝導電流が所定の閾値レベルを上回るか下回るかを判定することによって感知を実行する感知回路 460 を備える。感知は、読み出し又は検証動作において発生し得る。感知回路はまた、プログラ

50

ム動作におけるプログラム電圧の印加中にビット線電圧を供給する。他の回路（例えば、ステートマシン 312 の制御下の電力制御部 316）は、読み出し又はプログラム中にワード線への電圧の印加を制御し得ることに留意されたい。したがって、ステートマシン 312 は、読み出し基準電圧（並びに他の電圧）のワード線へのタイミングを制御するために、電力制御部 316 を制御してもよい。

#### 【0083】

感知回路 460 は、Vb1 セレクタ 462、感知ノード 464、比較回路 466、及びトリップラッチ 468 を含み得る。プログラム電圧の印加中、Vb1 セレクタ 462 は、プログラムイネーブル電圧（例えば、V\_pgm\_enable）又はプログラム禁止電圧（例えば、Vb1\_inh）を、メモリセルに接続されたビット線に渡すことができる。10

#### 【0084】

トランジスタ 470（例えば、nMOS）は、トランジスタの制御ゲート電圧を十分に高く、例えば、Vb1 セレクタから渡された Vb1 よりも高く設定することによって、Vb1 セレクタ 462 から Vb1 を渡すためのバスゲートとして構成することができる。例えば、セレクタ 472 は、電源電圧 Vdd、例えば、3~4V をトランジスタ 470 の制御ゲートに渡すことができる。

#### 【0085】

感知回路 350(1) は、ビット線に電圧が印加されるタイミングを制御するように構成されている。読み出し及び検証動作などの感知動作中、ビット線電圧は、セレクタ 472 が渡した電圧に基づいてトランジスタ 470 によって設定される。ビット線電圧は、トランジスタの制御ゲート電圧からその Vt（例えば、3V）を引いたものとほぼ等しい。例えば、Vb1 + Vt がセレクタ 472 によって渡される場合、ビット線電圧は Vb1 となる。これは、ソース線が 0V にあると仮定する。トランジスタ 470 は、制御ゲート電圧に従ってビット線電圧をクランプし、バスゲートではなくソースフォロワとして作用する。Vb1 セレクタ 462 は、トランジスタ 470 上の制御ゲート電圧よりも高い Vdd などの比較的高い電圧を渡して、ソースフォロワモードを提供することができる。したがって、感知中、トランジスタ 470 は、ビット線を充電する。20

#### 【0086】

1つのアプローチでは、各感知增幅器のセレクタ 472 は、Vb1 又は Vdd を渡すために、他の感知增幅器のセレクタとは別個に制御することができる。各感知增幅器の Vb1 セレクタ 462 はまた、他の感知增幅器の Vb1 セレクタとは別個に制御することができる。30

#### 【0087】

感知中、感知ノード 464 は、V\_sense\_int = 3V などの初期電圧まで充電される。次に、感知ノードは、トランジスタ 470 を介してビット線に接続され、感知ノードの減衰量は、メモリセルが導電性又は非導電性状態にあるかどうかを判定するために使用される。一実施形態では、ビット線内を流れる電流は、感知ノード（例えば、感知コンデンサ）を放電する。感知ノードが減衰する時間の長さは、本明細書では「積分時間」と呼ばれることがある。比較回路 466 は、感知ノード電圧を感知時間でトリップ電圧と比較するために使用される。感知ノード電圧がトリップ電圧 Vtrip を下回って減衰する場合、メモリセルは導電性状態となり、その Vt は検証信号の電圧以下である。感知ノード電圧が Vtrip を下回って減衰しない場合、メモリセルは非導電性状態となり、その Vt は検証信号の電圧を上回る。感知増幅器 350(1) は、メモリセルが導電性又は非導電性状態にあるかどうかに基づいて、比較回路 466 によって設定されるトリップラッチ 468 を含む。トリップラッチ内のデータは、プロセッサ 482 によって読み出されるビットとすることができる。40

#### 【0088】

管理回路 480 は、プロセッサ 482、例示的な 4 つのデータラッチ 484、485、486、487 のセット、及びデータラッチのセットとメモリバス 322 との間に結合された I/O インターフェース 488 を備える（メモリバスは、メモリコントローラ 102 に

10

20

30

40

50

接続されてもよい）。例えば、個々のラッチ L D L、L M D L、U M D L、及び U D L を含む 1 セットのデータラッチを、各感知増幅器のために提供することができる。場合によっては、より少ないデータラッチ、又は追加のデータラッチが使用されてもよい。L D L は、データの下位ページのビットを記憶し、L M D L は、データの下位中央ページのビットを記憶し、U M D L は、データの上位中央ページのビットを記憶し、U D L は、データの上位ページのビットを記憶する。これは、メモリセルメモリデバイス当たり、16 ビット又は 4 ビットである。一実施形態では、メモリセル当たり 8 ビット又は 3 ビットが存在する。

#### 【 0 0 8 9 】

プロセッサ 482 は、感知されたメモリセルに記憶されたデータを判定し、データラッチのセット内に判定されたデータを記憶するように、計算を実行する。例えば、プロセッサ 482 は、生コードワード内のビットを判定し、ラッチ 484 ~ 487 内に生コードワードのビットを記憶してもよい。データラッチ 484 ~ 487 の各セットは、読み出し動作中にプロセッサ 482 によって判定されたデータビットを記憶し、メモリにプログラムされることを意味する書き込みデータを表すプログラム動作中に、メモリバス 322 からインポートされたデータビットを記憶するために使用される。I/O インターフェース 488 は、データラッチ 484 ~ 487 とメモリバス 322 との間にインターフェースを提供する。

#### 【 0 0 9 0 】

プロセッサ 482 はまた、ラッチ 484 ~ 487 内の情報に基づいて、それぞれのメモリセルに関するデータ状態情報を決定してもよい。読み出し中、システムの動作は、アドレス指定されたメモリセルへの異なる制御ゲート電圧の供給を制御するステートマシン 312 の制御下にある。メモリによってサポートされる様々なメモリ状態に対応する様々な所定の制御ゲート電圧をステップ実行すると、感知回路は、これらの電圧のうちの 1 つでトリップすることができ、対応する出力は、データバス 454 を介してプロセッサ 482 に感知回路から提供されることになる。その時点で、プロセッサ 482 は、感知回路のトリップイベント（複数可）及び入力線 490 を介したステートマシンからの印加された制御ゲート電圧に関する情報を考慮することによって、結果として得られるメモリ状態を判定する。次いで、メモリ状態のバイナリエンコードを計算し、結果として得られるデータビットをデータラッチ 484 ~ 487 に記憶する。

#### 【 0 0 9 1 】

プロセッサ 482 はまた、ラッチの内容に基づいて、XOR コードワード、又は少なくともその一部分を形成してもよい。例えば、ビット単位の XOR は、UDL ラッチ及び XOR アキュムレータラッチ（図 4 には図示せず）の内容間で実行されてもよい。したがって、プロセッサ 482 は、XOR 演算の少なくとも一部分として機能してもよい（図 3C の 362 を参照）。

#### 【 0 0 9 2 】

いくつかの実装形態には、複数のプロセッサ 482 を含めることができる。一実施形態では、各プロセッサ 482 は、出力線の各々が有線 OR であるように、出力線（図示せず）を含む。いくつかの実施形態では、出力線は、有線 OR 線に接続される前に反転される。この構成により、有線 OR を受信するステートマシンは、プログラムされている全てのビットが所望のレベルに到達したことを判定することができるため、プログラミングプロセスが完了したときのプログラム検証テスト中に迅速に判定できる。例えば、各ビットがその所望のレベルに到達したとき、そのビットの論理ゼロは、有線 OR 線（又は、データ 1 が反転）に送信される。全てのビットがデータ 0（又は、データ 1 が反転）を出力すると、ステートマシンはプログラミングプロセスを終了することを知る。各プロセッサは、4 つの感知増幅器と通信するため、ステートマシンは、有線 OR 線を 4 回読み出す必要があり、又は、論理は、関連するビット線の結果を蓄積するためにプロセッサ 482 に追加されて、その結果、ステートマシンが有線 OR 線を一度に読み出す必要がある。同様に、論理レベルを正しく選択することによって、グローバルステートマシンは、第 1 のビットが

10

20

30

40

50

その状態を変更し、それに応答してアルゴリズムを変更するときを検出することができる。

#### 【0093】

プログラム又はメモリセルの動作を検証する間、プログラムされるデータ（書き込みデータ）は、メモリセル実装当たり4ビットで、LDL、LMDL、UMDL、及びUDLラッチ内のメモリバス322からデータラッチ484～487のセット内に記憶される。

#### 【0094】

データラッチ484～487の各セットは、各感知増幅器のデータラッチのスタックとして実装されてもよい。いくつかの実装形態では、データラッチは、シフトレジスタとして実装されており、その結果、そこに記憶されたパラレルデータは、メモリバス322のシリアルデータに変換され、逆もまた同様である。メモリセルの読み出し／書き込みブロックに対応する全てのデータラッチをリンクして、データのブロックがシリアル転送によって入力又は出力され得るように、ブロックシフトレジスタを形成することができる。具体的には、読み出し／書き込み回路のバンクは、データラッチのセットの各々が、読み出し／書き込みブロック全体のシフトレジスタの一部であるかのように、データバスの中又は外のデータをシーケンス内でシフトさせるように適合される。10

#### 【0095】

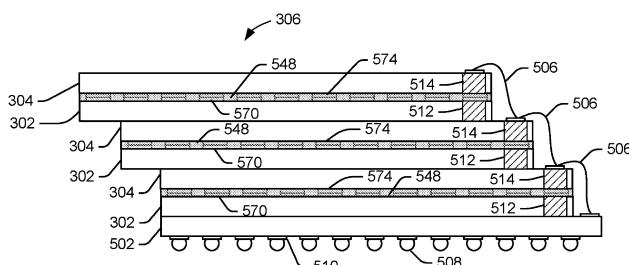

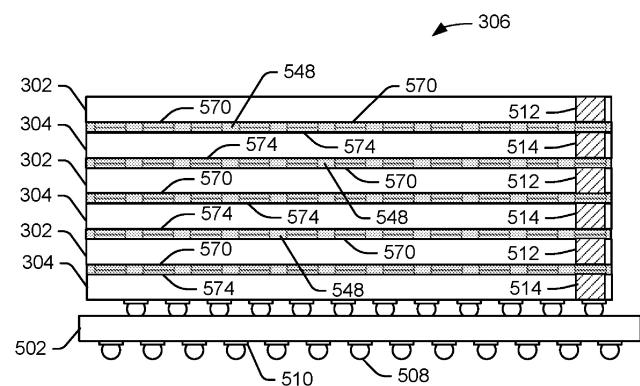

いくつかの実施形態では、集積メモリアセンブリ306内に、2つ以上の制御ダイ304及び2つ以上のメモリ構造ダイ302が存在する。いくつかの実施形態では、集積メモリアセンブリ306は、複数の制御ダイ304及び複数のメモリ構造ダイ302のスタックを含む。図5Aは、基板502上に積層された集積メモリアセンブリ306（例えば、制御ダイ304及びメモリ構造ダイ302を含むスタック）の一実施形態の側面図を示す。集積メモリアセンブリ306は、3つの制御ダイ304及び3つのメモリ構造ダイ302を有する。いくつかの実施形態では、4つ以上のメモリ構造ダイ302及び4つ以上の制御ダイ304が存在する。20

#### 【0096】

各制御ダイ304は、メモリ構造ダイ302のうちの少なくとも1つに固着（例えば、接合）される。ボンドパッド570、574のいくつかが示されている。更に多くのボンドパッドが存在し得る。2つのダイ302、304の間の空間は、エポキシ又は他の樹脂若しくはポリマーから形成され得る固体層548で充填される。この固体層548は、ダイ302、304間の電気的接続を保護し、ダイを一緒に更に固定する。様々な材料を固体層548として使用し得るが、実施形態では、米国カリフォルニア州にオフィスを構える、Henkel社のHysolエポキシ樹脂であってもよい。30

#### 【0097】

集積メモリアセンブリ306は、例えば、ステップオフセットで積層されてもよく、各レベルのボンドパッドは、被覆されておらず、上方からアクセス可能である。ボンドパッドに接続されたワイヤボンド506は、制御ダイ304を基板502に接続する。いくつかのこののようなワイヤボンドは、各制御ダイ304の幅全体に（すなわち、図5Aのページ内に）形成されてもよい。

#### 【0098】

メモリダイのスルーシリコンビア（through silicon via、TSV）512を使用して、メモリ構造ダイ302を介して信号をルーティングすることができる。制御ダイのスルーシリコンビア（TSV）514を使用して、制御ダイ304を介して信号をルーティングすることができる。TSV512、514は、半導体ダイ302、304内の集積回路の形成前、形成中、又は形成後に形成されてもよい。TSVは、ウェハを貫通する孔をエッチングすることによって形成されてもよい。次いで、孔は、金属拡散に対するバリアで裏打ちされてもよい。バリア層は、次にシード層で裏打ちされてもよく、シード層は、銅などの導電体でめっきされてもよいが、アルミニウム、スズ、ニッケル、金、ドープシリコン、及びこれらの合金又は組み合わせなどの他の好適な材料を使用することができる。40

## 【 0 0 9 9 】

はんだボール 508 は、任意選択的に、基板 502 の下面上の接触パッド 510 に固着されてもよい。はんだボール 508 は、集積メモリアセンブリ 306 を、プリント回路基板などのホストデバイスに電気的及び機械的に結合するために使用されてもよい。はんだボール 508 は、集積メモリアセンブリ 306 が LGA パッケージとして使用される場合、省略されてもよい。はんだボール 508 は、集積メモリアセンブリ 306 とメモリコントローラ 102との間のインターフェースの一部を形成してもよい。

## 【 0 1 0 0 】

図 5B は、基板 502 上に積層された集積メモリアセンブリ 306 の一実施形態の側面図を示す。集積メモリアセンブリ 306 は、3 つの制御ダイ 304 及び 3 つのメモリ構造ダイ 302 を有する。いくつかの実施形態では、4 つ以上の多くのメモリ構造ダイ 302 及び 4 つ以上の多くの制御ダイ 304 が存在する。この例では、各制御ダイ 304 は、少なくとも 1 つのメモリ構造ダイ 302 に接合されている。任意選択的に、制御ダイ 304 は、2 つのメモリ構造ダイ 302 に接合されてもよい。

10

## 【 0 1 0 1 】

ボンドパッド 570、574 のいくつかが示されている。更に多くのボンドパッドが存在し得る。2 つのダイ 302、304 の間の空間は、エポキシ又は他の樹脂若しくはポリマーから形成され得る固体層 548 で充填される。図 5A の例とは対照的に、図 5B の集積メモリアセンブリ 306 は、ステップオフセットを有さない。メモリダイのスルーシリコンビア (TSV) 512 を使用して、メモリ構造ダイ 302 を介して信号をルーティングすることができる。制御ダイのスルーシリコンビア (TSV) 514 を使用して、制御ダイ 304 を介して信号をルーティングすることができる。

20

## 【 0 1 0 2 】

はんだボール 508 は、任意選択的に、基板 502 の下面上の接触パッド 510 に固着されてもよい。はんだボール 508 は、集積メモリアセンブリ 306 を、プリント回路基板などのホストデバイスに電気的及び機械的に結合するために使用されてもよい。はんだボール 508 は、集積メモリアセンブリ 306 が LGA パッケージとして使用される場合、省略されてもよい。

## 【 0 1 0 3 】

簡単に上述したように、制御ダイ 304 及びメモリ構造ダイ 302 は、一緒に接合されてもよい。各ダイ 302、304 上のボンドパッドを使用して、2 つのダイを一緒に接合してもよい。いくつかの実施形態では、ボンドパッドは、はんだ又は他の追加材料なしで、いわゆる Cu ~ Cu 接合プロセスにおいて互いに直接接合される。Cu ~ Cu 接合プロセスでは、ボンドパッドは、高度に平坦であるように制御され、周囲の微粒子がほとんどない高度に制御された環境で形成され、微粒子は、そうしないと、ボンドパッド上に沈降し、密接な接合を妨げる可能性がある。このような適切に制御された条件下で、ボンドパッドは、互いに位置合わせされ、互いに押し付けられて、表面張力に基づいて相互接合を形成する。このような接合は室温で形成されてもよいが、熱が適用されてもよい。Cu ~ Cu 接合を使用する実施形態では、ボンドパッドは、約 5 μm 平方であり得、5 μm ~ 5 μm のピッチで互いに離間され得る。このプロセスは、本明細書では Cu ~ Cu 接合と称されるが、この用語はまた、ボンドパッドが Cu 以外の材料で形成される場合にも適用され得る。

30

## 【 0 1 0 4 】

ボンドパッドの面積が小さいとき、半導体ダイと一緒に接合することは困難であり得る。ボンドパッドのサイズ及びボンドパッド間ピッチは、ボンドパッドを含む半導体ダイの表面上にフィルム層を提供することによって、更に低減され得る。フィルム層は、ボンドパッドの周囲に設けられる。ダイが一緒にになると、ボンドパッドは互いに接合し得、それぞれのダイ上のフィルム層が互いに接合し得る。このような接合技法は、ハイブリッド接合と呼ばれることがある。ハイブリッド接合を使用する実施形態では、ボンドパッドは、約 5 μm 平方であり得、1 μm ~ 5 μm のピッチで互いに離間され得る。いっそより小さ

40

50

いサイズ及びピッチを有するボンドパッドを提供する接合技法が使用されてもよい。

#### 【 0 1 0 5 】

いくつかの実施形態には、ダイ 302、304 の表面上にフィルムを含み得る。このようなフィルムが最初に提供されない場合、ダイ間の空間は、エポキシ又は他の樹脂若しくはポリマーでアンダーフィルされてもよい。アンダーフィル材料は液体として塗布されてもよく、それはその後固体層に固化する。このアンダーフィルステップは、ダイ 302、304 間の電気的接続を保護し、ダイと一緒に更に固定する。様々な材料をアンダーフィル材料として使用し得るが、実施形態では、米国カリフォルニア州にオフィスを構える、H enke1 社の H y s o l エポキシ樹脂であってもよい。

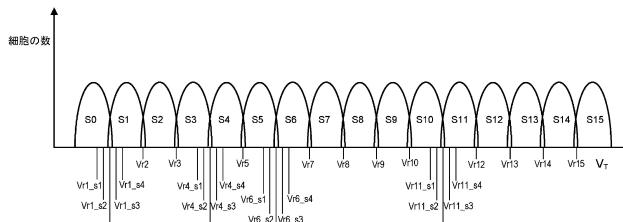

#### 【 0 1 0 6 】

良好なプログラミングプロセスの最後に、必要に応じて、メモリセルの閾値電圧は、プログラムされたメモリセルの閾値電圧の 1 つ以上の分布内、又は消去されたメモリセルの閾値電圧の分布内にあるべきである。図 6 は、各メモリセルが 4 ビットのデータを記憶するときのメモリアレイの例示的な閾値電圧分布を示す。しかしながら、他の実施形態は、メモリセル当たり他のデータ容量（例えば、メモリセル当たり 1、2、3、又は 5 ビットのデータなど）を使用し得る。図 6 は、メモリセルからデータを読み出すための 15 個のハードビット (hard bit、HB) 読み出し基準電圧 V r 1 ~ V r 15 を示す。メモリセルのセットは、同じワード線に接続されてもよい。各 HB 読み出し基準レベルは、2 つの隣接する閾値電圧分布間を区別するために使用される。別の言い方をすれば、各 HB 読み出し基準レベルは、2 つの隣接するデータ状態間を区別するために使用される。例えば、HB 読み出し基準レベル V r 4 は、データ状態 S 3 と S 4 とを区別するために使用される。所与のメモリセルの閾値電圧がこの 15 個の読み出し基準電圧よりも高いか低いかを試験する（例えば、感知動作を実行する）ことによって、システムは、メモリセルがどのデータ状態（即ち、S 0、S 1、S 2、S 3、...）にあるのかを判定することができる。

#### 【 0 1 0 7 】

図 6 は、データ状態 S 0 ~ S 15 間にいくらかの重なりが存在し得ることを示す。この重なりは、電荷を失う（したがって、閾値電圧で低下する）メモリセルなどの要因に起因して発生し得る。図 6 は、メモリセル当たり 4 ビットが記憶されている一例を示す。したがって、1 セットのメモリセルに 4 ページが記憶されてもよい。メモリセルのセットは、同じワード線に接続されてもよい。これらのページは、下部ページ、下部中央ページ、上部中央ページ、及び上部ページと呼ばれることがある。一実施形態では、下部ページを読み出すために、メモリセルは、4 つの異なる HB 読み出し基準電圧を使用して感知される。例えば、メモリセルは、V r 1、V r 4、V r 6、及び V r 11 で感知され得る。

#### 【 0 1 0 8 】

読み出し又は検証動作中にメモリセルの伝導電流を測定する多くの方法がある。一例では、メモリセルの伝導電流は、感知增幅器内の専用コンデンサを放電又は充電する速度によって測定される。別の例では、選択されたメモリセルの伝導電流は、メモリセルを含む N AND ストリングが対応するビット線を放電することを可能にする（又は可能にしない）。ビット線の電圧は、それが放電されていたかどうかを調べるために一定時間後に測定される。本明細書に記載される技術は、検証 / 読み出しのための当該技術分野で既知の様々な方法と共に使用され得ることに留意されたい。当該技術分野で既知の他の読み出し及び検証技術も使用することができる。

#### 【 0 1 0 9 】

図 6 はまた、4 つの HB 基準電圧に関連する、ソフトビット (SB) 基準電圧を示す。V r 1、V r 4、V r 6、及び V r 11 の各々の周囲にグループ化された 1 セットの SB 基準電圧が存在する。例えば、SB 基準電圧 V r 1\_s 1、V r 1\_s 2、V r 1\_s 3、及び V r 1\_s 4 のセットを HB 基準電圧 V r 1 の周囲にグループ化し、SB 基準レベル V r 4\_s 1、V r 4\_s 2、V r 4\_s 3、及び V r 4\_s 4 のセットを HB 基準電圧 V r 4 の周囲にグループ化し、SB 基準レベル V r 6\_s 1、V r 6\_s 2、V r 6\_s 3、及び V r 6\_s 4 のセットを HB 基準電圧 V r 6 の周囲にグループ化し、SB 基準レ

10

20

30

40

50

ベル  $V_{r11\_s1}$ 、 $V_{r11\_s2}$ 、 $V_{r11\_s3}$ 、及び  $V_{r11\_s4}$  のセットを HB 基準電圧  $V_{r11}$  の周囲にグループ化する。他の HB 基準電圧に関連する SB 基準電圧が存在し得るが、これらは、図 6 には示されていない。図 6 では、各対応する HB 基準電圧に関連する 4 つの SB 基準電圧が存在するが、HB 基準電圧に関連するより多くの SB 基準レベル又はより少ない SB 基準レベルが存在し得る。

#### 【0110】

本明細書に開示されるいくつかの実施形態は、状態がメモリセルの閾値電圧 ( $V_t$ ) によって表されるメモリセルを対象とするが、メモリセルの状態は、抵抗又はコンダクタンスを含むがこれらに限定されない別の物理パラメータによって表され得ることに留意されたい。例えば、図 6 では、データ状態は、 $V_t$  分布によって表される。しかしながら、他の種類のメモリセルでは、データ状態は、抵抗分布又はコンダクタンス分布によって表されてもよい。

10

#### 【0111】

いくつかの実施形態では、ソフトビット基準電圧は、ECC エンジンが、ハードビット基準電圧を使用して感知されたデータを使用してメモリセルに記憶されたコードワードをデコードできないときに、メモリセル内のデータを読み出すために使用される。典型的には、各ハードビット基準電圧に対するソフトビット基準電圧のセットが存在する。ソフトビット基準電圧は、対応するハードビット基準電圧がわずかに高い電圧及びわずかに低い電圧での基準電圧である。ソフトビット基準電圧のセットは、デコーダの訂正能力を増大させる「ソフト」信頼性情報を生成するために使用される。ソフトビット基準電圧での感知は、ハードビット基準レベルに近いメモリセルの物理パラメータ（例えば、 $V_t$ 、抵抗）が、そのメモリセルのハードビットの信頼性を低くするか、又はハードビット基準レベルから遠いメモリセルの物理パラメータ（例えば、 $V_t$ 、抵抗）が、ハードビットの信頼性を高くするかを示す「ソフトビット」を生成する。換言すれば、ソフト信頼性情報が、ハードビット基準レベルに近い物理パラメータ（例えば、 $V_t$ 、抵抗）の値を有することを示す場合、これは、ソフト信頼性情報が、メモリセルがハードビット基準レベルから遠い物理パラメータ（例えば、 $V_t$ 、抵抗）の値を有することを示す場合よりも信頼性が低いと考えられる。

20

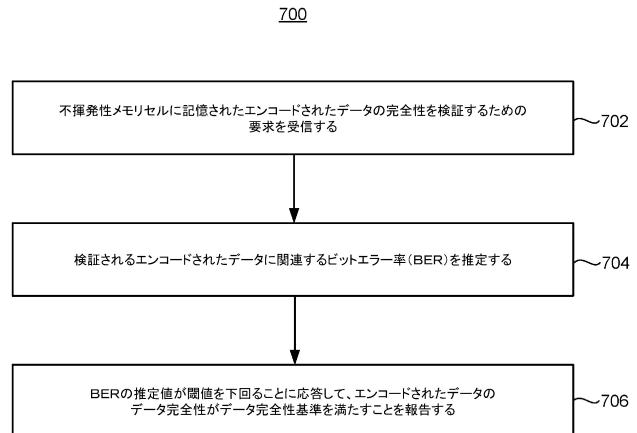

#### 【0112】

図 7 は、不揮発性メモリセルに記憶されたデータの完全性を検証するプロセス 700 の一実施形態を示すフローチャートである。プロセス 700 は、例えば、記憶システム 100、メモリコントローラ 102、メモリダイ 300、制御ダイ 304、又は集積メモリアセンブリ 306 によって実行されてもよい。

30

#### 【0113】

ステップ 702 は、不揮発性メモリセルに記憶されたエンコードされたデータの完全性を検証するための要求を受信することを含む。エンコードされたデータとは、データが 1 つ以上の ECC コードワードとしてエンコードされたことを意味する。一実施形態では、ホストシステム 120 は、記憶システム 100 に要求を提供する。記憶システム 100 は、ホスト 120 への PCIe インターフェースを介して要求を受信してもよい。一実施形態では、ホストシステム 120 は、NVMe 検証コマンドを提供する。一実施形態では、ホストシステム 120 は、NVM Get LBA 状態コマンドを提供する。しかしながら、データ完全性を検証するための要求は、NVM エクスプレス（商標）仕様からのコマンドに限定されない。

40

#### 【0114】

一実施形態では、要求は、検証される LBA 又は LBA のセット（LBA の範囲など）のいずれかを特定する。メモリコントローラ 102 は、LBA（複数可）をメモリ構造 326 内の 1 つ以上の物理アドレスに変換してもよい。次いで、メモリコントローラ 102 は、メモリダイ 300 又は制御ダイ 304 に 1 つ以上の要求を送信する。ダイ 300 は、メモリコントローラ インターフェース 315 を介して要求を受信してもよい。ダイ 300、304 に対する要求は、実装に依存し得る。更なる詳細が以下に論じられる。

50

**【 0 1 1 5 】**

ステップ 704 は、検証されるエンコードされたデータに関連する B E R を推定することを含む。エンコードされたデータは、1つ以上のECC コードワードを有する。一実施形態では、B E R は、エンコードされたデータを完全にデコードすることなく、推定される。エンコードされたデータを完全にデコードすることは、コードワードの全てについて有効なコードワードを決定することを意味する。データが完全にデコードされない方法の1つは、有効なコードワードに収束する前にECC デコーダを停止することである。データが完全にデコードされない別の方法は、コードワードのサブセット（ただし全てではない）のみに有効なコードワードを決定することである。

**【 0 1 1 6 】**

一実施形態では、B E R は、エンコードされたデータ内のコードワードの S W を決定することによって推定される。一実施形態では、B E R は、エンコードされたデータの複数のページから単一のXOR ページを形成し、単一のXOR ページをデコードすることによって推定され、XOR ページの B E R を決定する。一実施形態では、B E R は、エンコードされたデータのサンプルをデコードすることによって推定される。したがって、これらの例の各々において、B E R は、データを完全にデコードすることなく、推定することができる。したがって、時間及び電力の両方が節約される。また、いくつかの実施形態では、制御ダイ（又はメモリダイ）とメモリコントローラとの間のデータ転送が低減される。ステップ 704 は、メモリコントローラ 102 又は制御ダイ 304 によって実行することができる。

**【 0 1 1 7 】**

ステップ 706 は、B E R の推定値が閾値を下回ることに応答して、エンコードされたデータのデータ完全性がデータ完全性基準を満たすことを報告することを含む。したがって、データの完全性は、データを完全にデコードすることなく検証され、それにより、時間及び電力の両方が節約される。一実施形態では、メモリコントローラ 102 は、ホストシステム 120 にコマンド応答を提供する。検証要求がN V M e 検証コマンドである実施形態では、メモリコントローラ 102 は、N V M e コマンド応答待ち行列にコマンド応答を配置することができる。

**【 0 1 1 8 】**

いくつかの実施形態では、データ完全性基準は、読み出しコマンドが、結果としてホストシステム 120 に報告されている特定の種類のエラーをもたらしたかどうかに基づく。可能なエラーの例としては、訂正可能なECC（C E C C）及び訂正不可能なECC（U E C C）が挙げられるが、これらに限定されない。一実施形態では、データ完全性基準は、ECC デコード器によってデータが訂正可能であることであり、この場合、データ完全性基準は、C E C C が存在する場合であってもデータ完全性基準が満たされる（ただし U E C C が存在する場合は満たされない）。一実施形態では、データ完全性基準は、データがビットエラーを有さないことであり、この場合、データ完全性基準は、C E C C が存在する場合は満たされない。いくつかの実施形態では、ステップ 706 では、エラーがないことを報告することによって、データ完全性基準が満たされたことを報告する。いくつかの実施形態では、ステップ 706 では、訂正可能なエラー（例えば、C E C C）を報告することによって、データ完全性基準が満たされたことを報告する。データ完全性が満たされたことを報告することは、エラーがないか、又は C E C C のどちらかを報告することに限定されない。

**【 0 1 1 9 】**

場合によっては、記憶システム 100 は、エンコードされたデータを完全にデコードして、データ完全性基準が満たされたかどうかを判定する。例えば、ステップ 704 の B E R が閾値よりも大きい場合、記憶システムは、データを完全にデコードして、データ完全性基準が満たされたかどうかを判定してもよい。更なる詳細が以下に論じられる。

**【 0 1 2 0 】**

場合によっては、記憶システム 100 は、検証されたデータのデータスクラブを実行して

10

20

30

40

50

もよい。例えば、C E C C が存在した場合、記憶システムは、任意のエラーを訂正した後にデータを再書き込みしてもよい。N A N Dなどのいくつかの技術では、データは、新しい場所に書き込まれてもよい。

#### 【0 1 2 1】

プロセス700は、データ完全性基準が満たされているシナリオを説明することに留意されたい。場合によっては、データ完全性基準は満たされず、その場合、ステップ706は、データ完全性基準が満たされないことをホストシステム120に報告するステップと置き換える。この場合、エラー（例えば、データ基準に応じてU E C C、又は場合によってはC E C C）をリクエスタ（例えば、ホストシステム120）に報告してもよい。したがって、エラーは、読み出しコマンドに応答し、その結果エラーがリクエスタに返された場合、検証コマンドに応答して報告されてもよい。検証コマンドについて報告されたエラーは、読み出しコマンドに応答して報告されたエラーとは異なる場合がある。

10

#### 【0 1 2 2】

一実施形態では、記憶システム100は、検証コマンドに応答するために、検証されるデータのS Wを決定する。S Wは、B E Rを推定するために使用され得る。S Wは、満たされていないパリティチェックの数である。S Wの選択肢は、低密度パリティックチェック行列を有するE C Cに適用可能である。E C CコードワードのB E Rは、式1のように推定することができる。

#### 【数12】

$$\widehat{BER} = \frac{1 - (1 - 2 * W/M)^{1/d}}{2} \quad \text{式1}$$

20

#### 【0 1 2 3】

式1では、Wは、満たされていないパリティチェックの数であり、Mは、パリティチェックの総数であり、dは、各パリティチェックに関与するビット数（固定されていると仮定）である。実際には、このような計算は、オフラインで行うことができ、ルックアップテーブル（Look-Up-Table、L U T）は、満たされていないパリティチェックWの数を推定されたB E Rに変換するために使用されてもよい。完全なデコードに対するこの利点は、高速であり、確定的な時間で完了することである。また、低消費電力でもある。

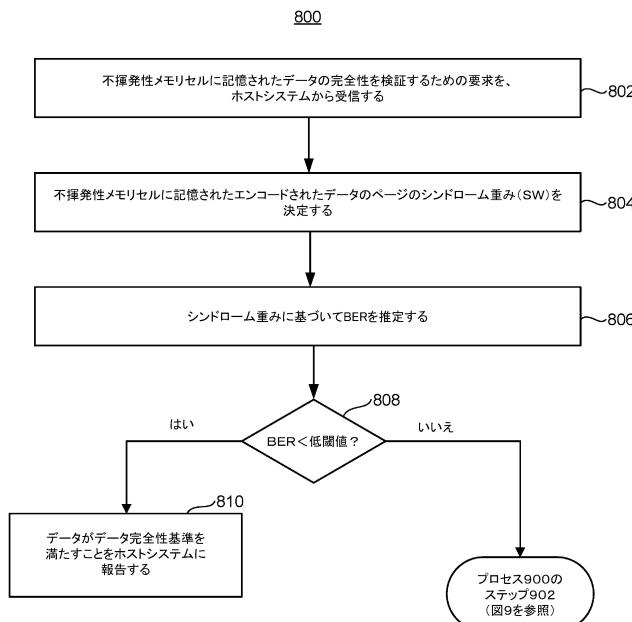

#### 【0 1 2 4】

図8は、検証コマンドに応答するS Wを決定するプロセス800の一実施形態を示す。プロセス800は、プロセス700の一実施形態についての更なる詳細を提供する。ステップ802は、不揮発性メモリセルに記憶されたデータの完全性を検証するための要求を、ホストシステム120から受信することを含む。

30

#### 【0 1 2 5】

ステップ804は、メモリセルに記憶されたエンコードされたデータのページのS Wを決定することを含む。一実施形態では、ページは、1つ以上のE C Cコードワードを含む。上述したように、S Wは、満たされていないパリティチェック方程式の数である。ステップ806は、S Wに基づいて、B E Rを推定することを含む。上述したように、B E Rは、式1に示すようにS Wから推定されてもよい。一実施形態では、S WをB E Rに相關させるL U Tがステップ806で使用される。

40

#### 【0 1 2 6】

プロセス800では、ステップ808において、推定されたB E Rに基づいて2つの分岐のうちの1つを取る。推定されたB E Rが閾値を下回る場合、ステップ810において、記憶システム100は、データがデータ完全性基準を満たすことをホストシステム120に報告する。一実施形態では、記憶システム100は、ホストがデータを要求した場合に、エラーなしに、データがホストシステム120に返されたことをホストシステム120に報告する。したがって、この実施形態では、ステップ808の低閾値は、ビットエラーがないことと相關している。一実施形態では、記憶システム100は、ホストがデータを要求した場合に、エラーなし又はC E C Cのいずれかでデータがホストシステム120に

50

返されたことをホストシステム 120 に報告する。したがって、この実施形態では、ステップ 808 の低閾値は、CECC が存在し得る場合でもデータがデコード可能である可能性が高いことと相関している。換言すれば、ステップ 808 の低閾値は、UECC が存在する可能性が非常に低いことと相関し得る。

#### 【0127】

推定された BER が閾値を上回る場合、プロセスは、プロセス 900 のステップ 902 で継続する（図 9 を参照）。図 9 は、SW が BER を推定するために使用されるときに、検証コマンドに応答するプロセス 900 の一実施形態のフローチャートである。プロセス 900 は、推定された BER が、プロセス 800 のステップ 808 で低閾値を下回っていないときに実行され得る。ステップ 902 は、推定された BER が高閾値を上回るかどうかの判定を含む。一実施形態では、高閾値は、データがデコードされた場合に UECC が存在する可能性に基づいて設定される。ステップ 910 でのデコード（以下で説明する）が UECC エラーを捕捉するという点で、高閾値を設定する際にいくらかの柔軟性があることに留意されたい。

#### 【0128】

推定された BER が高閾値を上回る場合、ステップ 904 は、ホストシステム 120 が高速失敗を要求したかどうかのチェックを含む。一実施形態では、高速失敗とは、データの完全性をチェックする要求を完了する前に、全ての利用可能なエラー回復を適用する記憶システム 100 とは対照的に、記憶システム 100 がデータを取得するために制限されたリトライ努力を適用すべきであるとホストシステム 120 が指定したことを意味する。高速失敗が要求された場合、記憶システムは、ステップ 906 で、データ完全性が基準を満たさないことを報告する。したがって、記憶システム 100 は、データをデコードすることなく、又はデコードが失敗する可能性があると決定されるまでデコードを何度も繰り返すことなく、検証コマンドに応答する。したがって、時間及び電力の両方が節約される。

#### 【0129】

高速失敗が要求されない場合、記憶システム 100 は、ステップ 908 で、様々なレベルの利用可能なエラー回復を実行する。全ての利用可能なエラー回復の例は、最初に、訂正することができるコードワード当たりのビット数に対して、異なる強度を有する 1 つ以上の ECC デコーダを用いてデータのデコードを試みることである。次に、記憶システムは、読み出し基準レベルを再較正し、続いて、より多くのデコードを試みる。次に、記憶システムは、ソフトビットを読み出し、ソフトビット（ハードビットと共に）を使用してデータのデコードを試みる。最後に、記憶システムは、XOR ストライプ内のデータなど、冗長データを使用してもよい。ステップ 908 での検証コマンドに対する応答は、CEC、UECC などが存在するかどうかに依存し得る。

#### 【0130】

ステップ 902 の説明に再び戻ると、推定された BER が高閾値を超えていない場合、ステップ 910 が実行される。プロセス 800 のステップ 806 と組み合わせたとき、推定された BER が低閾値と高閾値との間にあることを意味することに留意されたい。ステップ 910 は、ページをデコードし、BER を決定する記憶システムを含む。ステップ 912 では、記憶システム 100 は、決定された BER が低いか又は高いかを判定する。例えば、記憶システム 100 は、BER が閾値を上回るか又は下回るかを判定する。一実施形態では、ステップ 912 の閾値は、ステップ 808 の低閾値である。一実施形態では、ステップ 912 の閾値は、CECC がステップ 914 に進み、UECC がステップ 904 に進むように設定されている。決定された BER が低い場合、記憶システム 100 は、低 BER に基づいて、ステップ 914 でホストシステム 120 に報告する。一実施形態では、ステップ 914 の報告は、プロセス 800 のステップ 808 と同じである。例えば、メモリコントローラ 102 は、データの完全性が基準を満たすことをホストシステム 120 に報告する。決定された BER が高い場合、プロセス 900 は、先に説明したステップ 904 に進む。

#### 【0131】

10

20

30

40

50

一実施形態では、メモリコントローラ 102 は、(プロセス 800 のステップ 804 で) SW を決定し、(プロセス 900 のステップ 910 で必要とされる場合) ページをデコードする。図 10 は、検証されるデータのページを取得するメモリコントローラ 102 のプロセス 1000 の一実施形態のフローチャートである。プロセス 1000 は、メモリコントローラ 102 が SW を決定し、必要に応じてデータをデコードするプロセス 800 の一実施形態の更なる詳細を提供する。ステップ 1002 は、メモリコントローラ 102 が、検証コマンドで、LBA をメモリ構造 326 内の物理アドレスに変換することを含む。ステップ 1004 は、メモリコントローラ 102 が、ダイ(例えば、メモリダイ 300 又は制御ダイ 304) が、物理アドレス用のデータを提供することを要求することを含む。ステップ 1006 は、ダイが物理アドレスでデータを感知することを含む。ステップ 1008 は、ダイがメモリコントローラ 102 にデータを提供することを含む。ステップ 1008 の後、メモリコントローラ 102 は、プロセス 800 のステップ 804 ~ 808 を実行してもよい。次いで、メモリコントローラ 102 は、ステップ 810 又はプロセス 900 のいずれかを実行してもよい。

10

#### 【0132】

いくつかの実施形態では、制御ダイ 304 は、ECC エンジン 330 を有する。ECC エンジン 330 は、メモリ構造 326 に記憶されたデータをデコードするために使用され得るデコーダ 390 を有する。ECC エンジン 330 はまた、データの SW を演算することができる。一実施形態では、制御ダイ 304 は、(プロセス 800 のステップ 804 で SW を演算する)。図 11 は、検証コマンドに応答して、使用する SW を演算するプロセス 1100 の一実施形態のフローチャートである。プロセス 1100 は、SW が制御ダイ 304 によって演算されるプロセス 800 の一実施形態の更なる詳細を提供する。ステップ 1102 は、メモリコントローラ 102 が、検証コマンドで、LBA をメモリ構造 326 内の物理アドレスに変換することを含む。ステップ 1104 は、メモリコントローラ 102、制御ダイ 304 が物理アドレスでデータを検証することを要求することを含む。ステップ 1106 は、制御ダイ 304 が、物理アドレスでデータを感知することを含む。ステップ 1108 は、制御ダイ 304 が、データの SW を決定することを含む。制御ダイ 304 はまた、SW に基づいて BER を推定することができる。ステップ 1110 は、制御ダイ 304 がメモリコントローラ 102 に報告することを含む。制御ダイ 304 は、BER が低閾値を下回るかどうか(ステップ 808 を参照)、BER が高閾値を上回るかどうか(ステップ 902 を参照)を報告することができる。制御ダイ 304 は、SW を単に報告することができる。他の選択肢もあり得る。

20

30

40

#### 【0133】

ステップ 1110 の後、メモリコントローラ 102 は、推定された BER が低閾値を下回る場合、ステップ 808 及びステップ 810 を実行してもよい。推定された BER が低閾値と高閾値との間にある場合、1つの選択肢としては、制御ダイ 304 が、メモリコントローラ 102 にデータを転送して、メモリコントローラ がデコードすることである(例えば、ステップ 910)。別の選択肢としては、制御ダイ 304 が、ECC エンジン 330 を使用してデータをデコードすることである。いくつかの実施形態では、制御部 304 は、コードワード当たり少数のエラーを訂正することができる低出力のデコーダを有するのに対し、メモリコントローラ 102 は、コードワード当たり多数のエラーを訂正することができる高出力のデコーダを有する。したがって、1つの選択肢としては、制御ダイ 304 は、低出力のデコーダを使用してページのデコードを試み、メモリコントローラ 102 は、制御ダイ 304 が失敗した場合に高出力のデコーダのみを使用してページのデコードを試みることである。

#### 【0134】

一実施形態では、記憶システム 100 は、検証されるデータの BER を推定するために、検証されるデータの複数の ECC コードワードから XOR コードワードを形成する。図 12 は、XOR ページがページ 1 の XOR からページ n までどのように形成され得るかを示す図である。図 12 の XOR 演算はまた、和モジュロ 2 と呼ばれることがある。各ページ

50

は、いくつかのエラーを伴うECCコードワードを有する。XORページは、t XORエラーを有するXORコードワードを有し、線形ECCコードを仮定する場合、t XORは、Pages 1 ~ nのエラーの合計とほぼ等しい(式2を参照)。

$$t \text{ XOR } t_1 + t_2 + t_3 \dots t_n \quad \text{式2}$$

### 【0135】

線形ECCの場合(LDPC、BCH、及び他のECC技術の場合のように)、複数のECCコードワードのXORはまた、有効なECCコードワードである。したがって、ECCページのXORページもECCコードワードである。XORコードワードのBERは、式3で表され得る。

### 【数13】

$$BER_{\oplus} = \frac{1 - \prod_{i=1}^n (1 - 2 \cdot BER_i)}{2} \approx \sum_{i=1}^n BER_i \quad \text{式3}$$

### 【0136】

式3では、

### 【数14】

$BER_{\oplus}$

10

20

は、XORコードワードのBERであり、 $BER_i$ は、 $i$ 番目のコードワードのBERである。したがって、一実施形態では、XORコードワードのBERは、その構成コードワード上のBERの合計を評価するために評価される。したがって、XORコードワードのBERは、検証されるデータ内のコードワードのBERの合計の推定値として機能する。したがって、検証されるコードワードのうちの1つ以上の問題が特定され得る。

### 【0137】

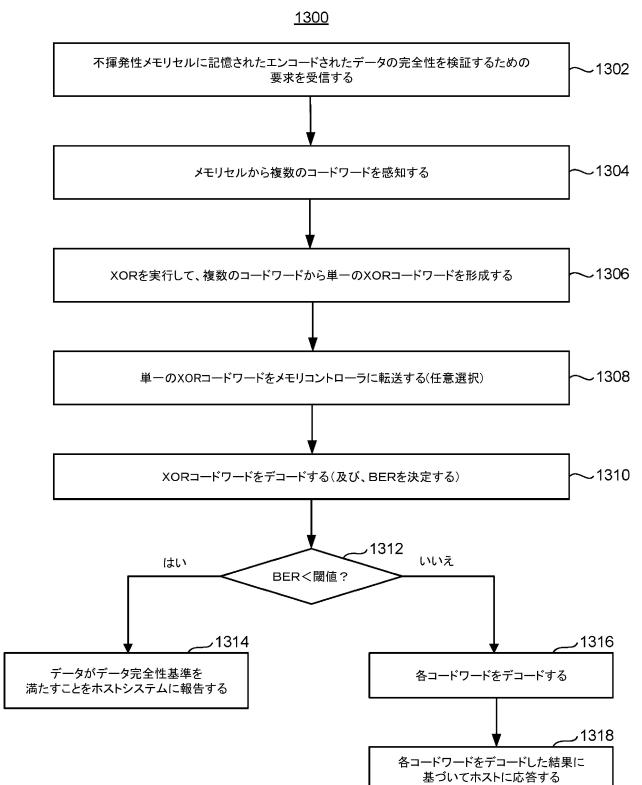

図13は、XORコードワードに基づいて、データの完全性を検証するプロセス1300の一実施形態のフローチャートである。プロセス1300は、プロセス700の一実施形態についての更なる詳細を提供する。プロセス1300のステップは、説明の便宜上、特定の順序で図示されることに留意されたい。ステップは、異なる順序で行うことができる。

30

### 【0138】

ステップ1302は、不揮発性メモリセルに記憶されたエンコードされたデータの完全性を検証するための要求を受信することを含む。ステップ1304は、エンコードされたデータの複数のコードワードをメモリセルから感知することを含む。図12を参照すると、 $n$ 個のコードワードの合計が感知され、 $n$ は、4、8、16、又はいくつかの他の数とすることができる。 $n$ の値は、期待されるBERに依存し得る。期待されるBERの要因の1つは、メモリセルがセル当たり1ビット(SLC)又はセル当たり複数ビット(MLC)を記憶するかどうかである。SLCデータの場合、BERは、通常は非常に低い。したがって、 $n$ は、SLCデータの方がMLCデータよりも高くなり得る。

40

### 【0139】

ステップ1306は、複数のECCコードワードから単一のECCコードワードを形成するためにXORを実行することを含む。一実施形態では、ステップ1306は、メモリダイ300によって実行される。一実施形態では、ステップ1306は、制御ダイ304によって実行される。ステップ1308は、単一のXORコードワードをダイ300、304からメモリコントローラ102に転送することを含む。

### 【0140】

ステップ1310は、XORコードワードをデコードすることを含む。ステップ1310はまた、XORコードワードのBERを決定することを含む。XORコードワードのBE

50

Rは、検証されるデータ内のコードワードの合計BERの推定値として使用されてもよい。更に、XORコードワードのBERは、コードワードのうちの1つを有する潜在的に高いBERを特定するために使用されてもよく、これを更に調査することができる。

#### 【0141】

ステップ1312では、BERが閾値未満であるかどうかの判定が行われる。閾値は、コードワードのうちの1つを有する潜在的に高いBERが特定されるように確立されてもよい。以下では、ステップ1312で使用する閾値を確立するための1つの技術について記載する。n = 16のコードワードをXOR演算することを考える。更に、期待されるBERは0.1%、標準偏差 = 0.01%であると仮定する。すると、

#### 【数15】

$$\text{BER}_{\oplus}$$

の期待値は、 $n * 0.1\% = 1.6\%$ で、標準偏差

#### 【数16】

$$\sigma_{\oplus} = \sqrt{\{\text{平方根}(n \cdot \sigma^2)\}} = 0.04\%$$

10

となる。したがって、

#### 【数17】

$$\text{BER}_{\oplus} \text{ が } 1.6\% + 3 \cdot \sigma_{\oplus} = 1.72\%$$

20

よりも高い場合、これは、コードワードのうちの1つに問題が存在し得るという指標として機能する。この例では、正常な挙動で閾値を超える確率が約1/1000であることを確実にするために、

#### 【数18】

$$3 \cdot \sigma_{\oplus}$$

の余地を取っている。

#### 【0142】

BERが閾値未満である場合、ステップ1314では、記憶システム100は、データの完全性がデータ完全性基準を満たすことをホストシステム120に報告する。一実施形態では、レポートは、ホストがデータを要求した場合に、エラーなしに、データがホストに返されたことを示す。一実施形態では、レポートは、ホストがデータを要求した場合に、エラーなし又はCECCのいずれかでデータがホストに返されたことを示す。BERが閾値を下回っていない場合、ステップ1316及び1318が実行される。ステップ1316では、各コードワードがデコードされる。一実施形態では、各コードワードは、メモリダイ300又は制御ダイ304のいずれかによってメモリコントローラ102に転送される。ステップ1318は、メモリコントローラ102が、各コードワードのBERに基づいてホストシステム120に報告することを含む。一実施形態では、コードワードのいずれかをデコードした結果、エラー（例えば、CECC、UECC）が生じた場合、データがデータ完全性基準を満たさないことを報告する。一実施形態では、UECCが発生していない限り、データがデータ完全性基準を満たすことを報告する。一実施形態では、報告は、ステップ1316で発生したCECC及び/又はUECCの数を含む。このような報告により、データがデータ完全性基準を満たすかどうかを本質的に示すことができる。

30

40

#### 【0143】

NANDを含むが、これらに限定されないメモリ技術は、正規対数型のエラー分布によって特徴付けられることがあり、これは、記憶システムの大部分のBERが低いことを意味する。したがって、少数のページ/WLのみでは、高いBERが観察される。したがって、プロセス1300を使用して、転送及びデコードの試みる回数を大幅に低減することができる。多くの記憶システム（例えば、大企業のドライブ）は、典型的には、（多くのダ

50

イが存在するため)、転送量が制限されており、したがって、プロセス 1300 はまた、大幅な時間短縮にも繋がり得る。

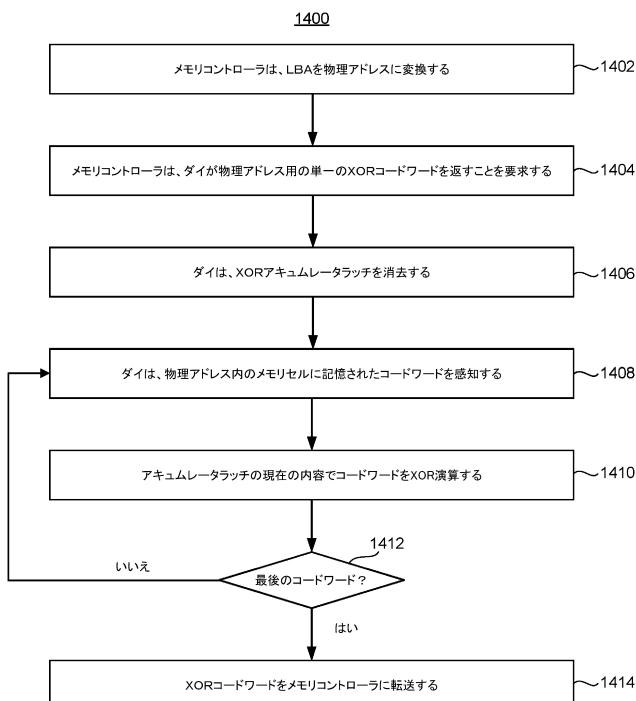

#### 【0144】

一実施形態では、ダイ(例えば、メモリダイ300、制御ダイ304)は、XORコードワードを形成し、XORコードワードをメモリコントローラ102に転送して処理する。検証される各コードワードとは対照的に、XORコードワードのみを転送することで、ダイとメモリコントローラ102との間のデータ転送が実質的に低減される。図14は、ダイが、メモリコントローラ102のXORコードワードを形成して処理するプロセス1400の一実施形態のフローチャートである。ステップ1402は、メモリコントローラ102が、検証コマンドで、LBAを不揮発性メモリセルの物理アドレスに変換することを含む。ステップ1404は、メモリコントローラ102が、ダイが物理アドレスの単一のXORコードワードを返すことを要求することを含む。ステップ1406は、ダイが、XORアキュムレータラッ奇364を消去することを含む。ステップ1408は、ダイが、物理アドレスのうちの1つを有するメモリセルに記憶されたコードワードを感知することを含む。コードワードは、ラッ奇360の1セットに記憶されてもよい。例えば、図3Cを簡単に参照すると、コードワードがメモリ構造326から感知されると、ラッ奇360(1)にラッ奇され得る。ステップ1410は、感知されたコードワードをXORアキュムレータラッ奇364の内容でXOR演算することを含む。例えば、XOR演算器362は、XORアキュムレータラッ奇364の内容のビット単位のXORをラッ奇360(1)の内容で実行し、その結果をXORアキュムレータラッ奇364に記憶する。ステップ1412は、より多くの感知するコードワードが存在するかどうかの判定である。そうである場合、ステップ1408～1410は、次のコードワードに対して実行される。全てのコードワードが処理されたとき、XORアキュムレータラッ奇364は、XORコードワードを含む。ステップ1414では、XORコードワードがメモリコントローラ102に転送される。次いで、メモリコントローラ102は、プロセス1300のステップ1310及び後続のステップを実行してもよい。

#### 【0145】

プロセス1300の変形例の1つは、コードワードをデコードしてBERを決定する代わりに、SWに基づいてコードワードのBERを推定することである。BERに基づいてコードワードのBERを推定することは、プロセス800に関連して説明してきた。一実施形態では、ステップ1310は、XORコードワードのSWに基づいてXORコードワードのBERを推定することによって修正される。したがって、XORコードワードは、完全にデコードされる必要はない。一実施形態では、ステップ1316は、それぞれのコードワードのSWに基づいて、検証される各コードワードのBERを推定することによって修正される。したがって、個々のコードワードは、ステップ1316で完全にデコードされる必要はない。SWの推定は、メモリコントローラ102又は制御ダイ304によって実行されてもよいことに留意されたい。

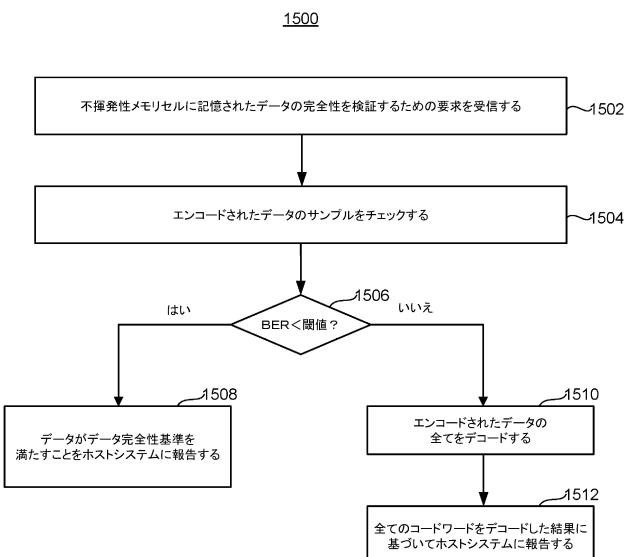

#### 【0146】

一実施形態では、記憶システム100は、データに関連するBERを推定するために、検証されるデータのサンプルのみをチェックする。図15は、データのサンプルのチェックに基づいてデータの完全性を検証するプロセス1500の一実施形態のフローチャートである。プロセス1500は、プロセス700の一実施形態についての更なる詳細を提供する。

#### 【0147】

ステップ1502は、記憶システム100が、不揮発性メモリセルに記憶されたデータの完全性を検証するための要求を受信することを含む。ステップ1504は、記憶システム100が、データのサンプルをチェックすることを含む。一実施形態では、サンプルは、サンプルのBERを決定するためにデコードされる。サンプルのBERは、検証される他のデータのBERの推定値として使用されてもよい。場合によっては、サンプルは、最悪の事例のBERを有すると予想されるメモリセルから取られ、その場合、他のメモリセル

10

20

30

40

50

は、サンプルほど悪くない B E R を有することが予想される。場合によっては、サンプルは、他のセルを表すと予想されるメモリセルから取られ、その場合、他のメモリセルは、ほぼ同じ B E R を有することが予想される。

#### 【 0 1 4 8 】

一実施形態では、サンプルは、ワード線のサブセットである。サンプルがワード線のサブセットである一実施形態の更なる詳細は、図 1 6 に關して説明される。一実施形態では、サンプルは、データのページのサブセットである。サンプルがページのサブセットである一実施形態の更なる詳細は、図 1 7 に關して説明される。一実施形態では、サンプルは、1 ページのデータ当たり 1 つのコードワードである。サンプルが 1 ページのデータ当たり 1 つのコードワードである一実施形態の更なる詳細は、図 1 8 に關して説明される。ステップ 1 5 0 2 のサンプルは、前述の例に限定されない。10

#### 【 0 1 4 9 】

ステップ 1 5 0 6 は、B E R が閾値未満であるかどうかの判定を含む。そうである場合、記憶システム 1 0 0 は、ステップ 1 5 0 8 で、データがデータ完全性基準を満たすことをホスト 1 2 0 に報告する。一実施形態では、B E R が閾値未満である場合、ステップ 1 5 0 6 の閾値は、データ内にエラーが存在しないか、又は、デコード可能な任意のエラーが C E C C であるかのいずれかの可能性が高いかどうかに相関する。換言すれば、閾値は、デコードされるデータである U E C C が存在する可能性が低いように確立されてもよい。

#### 【 0 1 5 0 】

B E R が閾値以上である場合、ステップ 1 5 1 0 ~ 1 5 1 2 が実行される。ステップ 1 5 1 0 は、エンコードされたデータの全てをデコードすることを含む。ステップ 1 5 1 2 は、データの全てをデコードした結果に基づいてホスト 1 2 0 に報告することを含む。ステップ 1 5 1 2 は、検証されるデータがデータ完全性基準を満たすかどうかを報告することを含む。一実施形態では、報告は、ステップ 1 5 1 0 で発生した C E C C 及び / 又は U E C C の数を含む。このような報告により、データがデータ完全性基準を満たすかどうかを本質的に示すことができる。20

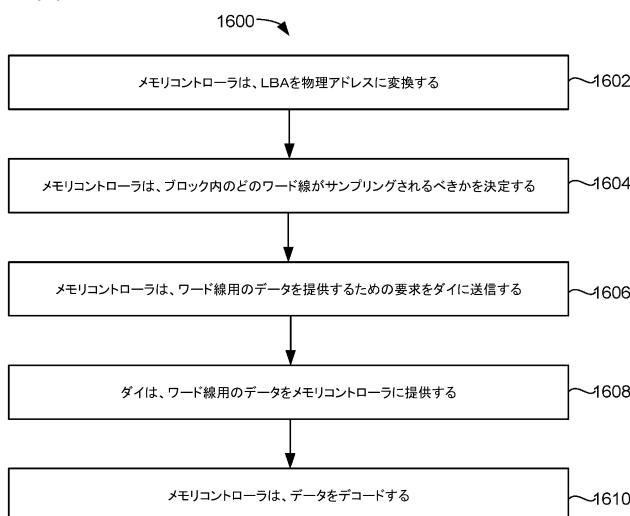

#### 【 0 1 5 1 】

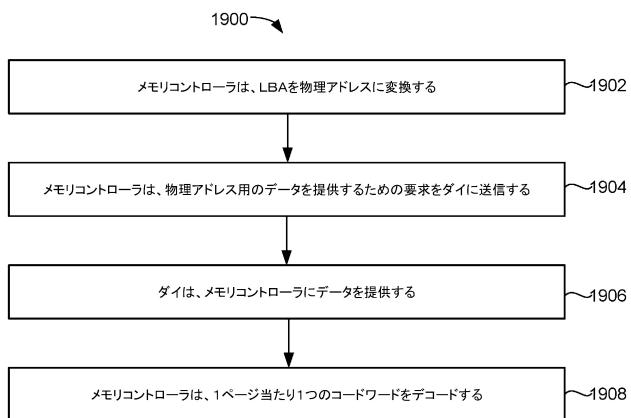

一実施形態では、ステップ 1 5 0 4 のサンプルは、ワード線のサブセットである。図 1 6 は、サンプルがワード線のサブセットであるプロセス 1 6 0 0 の一実施形態のフローチャートである。プロセス 1 6 0 0 は、ステップ 1 5 0 4 の一実施形態の更なる詳細を提供する。ステップ 1 6 0 2 は、メモリコントローラ 1 0 2 が、L B A を記憶システム 1 0 0 内の物理アドレスに変換することを含む。物理アドレスは、記憶システム内の複数のワード線のアドレスを含む。ステップ 1 6 0 4 は、メモリコントローラ 1 0 2 が、ワード線のうちのどのワード線をサンプリングすべきかを決定することを含む。一例として、ロックの特定の領域内のワード線は、これらのワード線が B E R に関して最悪の場合であることが予想されるため、サンプリングがある。ステップ 1 6 0 6 は、メモリコントローラ 1 0 2 が、ワード線用のデータを提供するための要求を、ダイ（例えば、メモリダイ 3 0 0 、制御ダイ 3 0 4 ）に送信することを含む。ステップ 1 6 0 8 は、ダイが、ワード線用のデータをメモリコントローラ 1 0 2 に提供することを含む。ステップ 1 6 1 0 は、メモリコントローラ 1 0 2 が、データをデコードし、データ用の 1 つ以上の B E R を決定することを含む。次いで、メモリコントローラは、ステップ 1 5 0 6 において、プロセス 1 5 0 0 を進めてよい。各ワード線に 1 つ以上の B E R が存在し得るため、ステップ 1 5 0 6 の選択肢の 1 つは、最も高い（最悪の事例の） B E R を使用して閾値と比較することである。30

#### 【 0 1 5 2 】

一実施形態では、検証されるデータは、データのいくつかのページを含み、ステップ 1 5 0 4 のサンプルは、ページのサブセットである。図 1 7 は、サンプルがページのサブセットであるプロセス 1 7 0 0 の一実施形態のフローチャートである。プロセス 1 7 0 0 は、ステップ 1 5 0 4 の一実施形態の更なる詳細を提供する。ステップ 1 7 0 2 は、メモリコントローラ 1 0 2 が、L B A を記憶システム 1 0 0 内の物理アドレスに変換することを含む40

10

20

30

40

50

む。物理アドレスは、記憶システム内のメモリセルに記憶された複数のページのアドレスを含む。

#### 【 0 1 5 3 】

ステップ 1704 は、メモリコントローラ 102 が、ページのうちのどのページをサンプリングすべきかを決定することを含む。一例として、メモリセルのページと呼ばれる一群のメモリセルは、データの複数ページを集合的に記憶することができる。例えば、メモリセルのページは、下部ページ、中央ページ、及び上部ページを記憶することができる。より具体的には、各メモリセルは、これら 3 つのページの各々の 1 ビットを記憶してもよい。したがって、各メモリセルは、この例では 3 ビットを記憶する。

#### 【 0 1 5 4 】

ステップ 1706 は、メモリコントローラ 102 が、サンプリングされるページ用のデータを提供するための要求を、ダイ（例えば、メモリダイ 300、制御ダイ 304）に送信することを含む。ステップ 1708 は、ダイが、ページ用のデータをメモリコントローラ 102 に提供することを含む。ステップ 1704 で説明した例では、メモリセル当たり 3 ビットを感知して時間及び電力を節約するのとは対照的に、1 ビットのみが各メモリセルから感知されることに留意されたい。また、ページのサブセットのみをメモリコントローラに転送することで、データ転送を低減する。

#### 【 0 1 5 5 】

ステップ 1710 は、メモリコントローラ 102 が、データをデコードし、データ用の 1 つ以上の B E R を決定することを含む。次いで、メモリコントローラは、ステップ 1506 において、プロセス 1500 を進めてよい。各ページに 1 つの B E R が存在し得るため、ステップ 1506 の選択肢の 1 つは、最も高い（最悪の事例の）B E R を使用して閾値と比較することである。

#### 【 0 1 5 6 】

一実施形態では、検証されるデータは、データのいくつかのページを含み、ステップ 1504 のサンプルは、1 ページ当たり 1 つのコードワードである。図 18A 及び図 18B は、データページ当たり複数のコードワードを有する概念を説明するために論じられる。図 18A は、E C C フィールドを含む E C C ページ 1800 を概略的に示す。E C C ページ 1800 は、ユーザ部分 1802 及びシステム部分 1804 を含む。ユーザ部分 1802 は、ユーザデータを記憶するためのものである。システム部分 1804 は、一般にシステムデータを記憶するための記憶システムによって使用される。システム部分には E C C 1806 が含まれる。E C C は、例えば、メモリコントローラ 102 によって、E C C ページに対して計算される。

#### 【 0 1 5 7 】

図 18B は、4 つの E C C ページ 1800 (1) ~ 1800 (4) を有するデータページ 1810 を示す。データページ 1810 は、W L 上のメモリセルのページの各メモリセルからの論理ビットから構成されたデータのセットである。一般に、データページを作成する N 個の E C C ページが存在する。図 18B では、N = 4 で、1 つのデータページを作成する 4 つの E C C ページが存在する。したがって、図 18B は、データページ 1810 がどのように（E C C ページ 1800 で）複数のコードワードを含むことができるかを示す。典型的には、同じデータページ 1810 内の E C C ページ 1800 の B E R は、非常に類似している。したがって、データページ 1810 当たりの E C C ページのうちの 1 つのみをチェックし、いくらかの余地を計算に入れることにより、他の E C C ページの B E R が低いと確実に決定することができる。いくつかの実施形態では、ステップ 1504 のサンプルは、データページ 1810 内の E C C ページ 1800 のうちの 1 つである。したがって、データページ 1810 内の E C C ページ 1800 の全てをデコードしないことによって、時間及び電力が節約される。

#### 【 0 1 5 8 】

図 19 は、サンプルが 1 ページ当たり 1 つのコードワードであるプロセス 1900 の一実施形態のフローチャートである。プロセス 1900 は、ステップ 1504 の一実施形態の

10

20

30

40

50

更なる詳細を提供する。ステップ1902は、メモリコントローラ102が、LBAを記憶システム100内の物理アドレスに変換することを含む。

#### 【0159】

ステップ1904は、メモリコントローラ102が、物理アドレス用のデータを提供するための要求を、ダイ（例えば、メモリダイ300、制御ダイ304）に送信することを含む。ステップ1906は、ダイが、物理アドレス用のデータをメモリコントローラ102に提供することを含む。

#### 【0160】

ステップ1908は、メモリコントローラ102が、データの1ページ当たり1つのコードワードをデコードすることを含む。例えば、図18Bを参照すると、ECCページ1800(1)は、各データページ1810についてデコードされる。したがって、データページ1810のいずれかにおいて、ECCページ1800(2)、1800(3)、又は1800(4)をデコードしないことによって、時間及び電力が節約される。次いで、メモリコントローラは、各データページについてデコードされたECCページのBERを決定することができる。次いで、メモリコントローラは、ステップ1506において、プロセス1500を進めてよい。各ECCページに1つのBERが存在し得るため、ステップ1506の選択肢の1つは、最も高い（最悪の事例の）BERを使用して閾値と比較することである。

10

#### 【0161】

上記を考慮すると、第1の実施形態は、通信インターフェース、及び通信インターフェースに結合された制御回路を含む装置を備えることが分かる。制御回路は、不揮発性メモリセルに接続するように構成されている。制御回路は、不揮発性メモリセルに記憶されたエンコードされたデータの完全性を検証するための要求を、通信インターフェースを介して受信するように構成されている。制御回路は、要求に応答して、エンコードされたデータを完全にデコードすることなく、エンコードされたデータに関連するBERを推定するように構成されている。制御回路は、ビットエラー率の推定値が、第1の閾値を下回ることに応答して、エンコードされたデータの完全性がデータ完全性基準を満たすことを、通信インターフェースを介して報告するように構成されている。

20

#### 【0162】

第2の実施形態では、第1の実施形態を更に進めて、制御回路は、ビットエラー率の推定値が第1の閾値を上回ることに応答して、エンコードされたデータのビットエラー率を決定し、決定されたビットエラー率に基づいて、エンコードされたデータのデータ完全性がデータ完全性基準を満たすかどうかを報告するために、エンコードされたデータを完全にデコードするように更に構成されている。

30

#### 【0163】

第3の実施形態では、第1又は第2の実施形態を更に進めて、制御回路は、推定されたビットエラー率が第1の閾値よりも大きい第2の閾値を上回ることに応答して、エンコードされたデータを完全にデコードすることなく、エンコードされたデータの完全性がデータ完全性基準を満たさないことを報告するように更に構成されている。

40

#### 【0164】

第4の実施形態では、第1～第3の実施形態のいずれかを更に進めて、制御回路は、エンコードされたデータを完全にデコードすることなく、エンコードされたデータのシンドローム重みを決定するように更に構成されている。制御回路は、シンドローム重みに基づいて、エンコードされたデータに関連するビットエラー率を推定するように更に構成されている。

#### 【0165】

第5の実施形態では、第1～第4の実施形態のいずれかを更に進めて、制御回路は、エンコードされたデータを完全にデコードすることなく、エンコードされたデータのシンドローム重みを決定するように更に構成されている。制御回路は、シンドローム重みに基づいて、エンコードされたデータに関連するビットエラー率を推定するように更に構成されて

50

いる。制御回路は、推定されたビットエラー率が第1の閾値よりも高い第2の閾値を上回ることに応答して、エンコードされたデータの完全性が、データ完全性基準を満たさないことを報告するように更に構成されている。

#### 【0166】

第6の実施形態では、第1～第5の実施形態のいずれかを更に進めて、制御回路は、XORコードワードを作成するために、エンコードされたデータの複数のコードワードのビット単位のXORを実行するように更に構成されている。制御回路は、エンコードされたデータを完全にデコードすることなく、エンコードされたデータに関連するビットエラー率を推定するために、XORコードワードのビットエラー率を決定するように更に構成されており、制御回路は、XORコードワードのビットエラー率が第1の閾値を下回ることに応答して、エンコードされたデータの完全性がデータ完全性基準を満たすことを報告する。

10

#### 【0167】

第7の実施形態では、第1～第6の実施形態のいずれかを更に進めて、制御回路は、XORコードワードのビットエラー率が第1の閾値を上回ることに応答して、エンコードされたデータの複数のコードワードの各々をデコードし、複数のコードワードの各々の決定されたビットエラー率に基づいて、エンコードされたデータの完全性がデータ完全性基準を満たすかどうかを報告するように更に構成されている。

#### 【0168】

第8の実施形態では、第1～第7の実施形態のいずれかを更に進めて、装置は、半導体ダイ及びメモリコントローラを備える。半導体ダイは、制御回路を備える。制御回路は、XORコードワードを作成するために、エンコードされたデータの複数のコードワードのビット単位のXORを実行するように更に構成されている。

20

#### 【0169】

第9の実施形態では、第1～第8の実施形態のいずれかを更に進めて、制御回路は、エンコードされたデータを完全にデコードすることなく、エンコードされたデータに関連するビットエラー率を推定するために、エンコードされたデータのサンプルのビットエラー率を決定するように更に構成されており、制御回路は、エンコードされたデータのサンプルのビットエラー率が第1の閾値を下回ることに応答して、エンコードされたデータの完全性がデータ完全性基準を満たすことを報告する。

30

#### 【0170】

第10の実施形態では、第1～第9の実施形態のいずれかを更に進めて、制御回路は、エンコードされたデータのサンプルのビットエラー率が第1の閾値を上回ることに応答して、エンコードされたデータ内の各コードワードのビットエラー率を決定し、各コードワードの決定されたビットエラー率に基づいて、エンコードされたデータの完全性がデータ完全性基準を満たすかどうかを報告するように更に構成されている。

#### 【0171】

一実施形態は、不揮発性記憶システムを動作させる方法を含む。本方法は、記憶システム内の不揮発性メモリセルに記憶されたデータの完全性を検証するための要求を、ホストシステムから不揮発性記憶システムで受信することを含む。本方法は、要求に応答して、不揮発性メモリセルに記憶された1つ以上のECCコードワードのシンドローム重みを決定することを含む。本方法は、1つ以上のECCコードワードの各々のシンドローム重みが第1の閾値を下回ることに応答して、検証されるデータが、データ完全性基準を満たすことをホストシステムに報告することを含む。

40

#### 【0172】

一実施形態は、不揮発性メモリセルを含む不揮発性記憶システム、及びメモリセルに記憶されたデータの完全性を検証するための要求に応答して、複数のECCコードワードをメモリセルから感知するための感知手段を備える。記憶システムは、複数のECCコードワードのXORコードワードを形成するためのXOR手段を含む。記憶システムは、XORコードワードのビットエラー率が第1の閾値を下回るかどうかを推定するか、又は決定す

50

るためのビットエラー率手段を含む。記憶システムは、XORコードワードの推定されたビットエラー率又は決定されたビットエラー率のいずれかが第1の閾値を下回ることに応答して、検証されるデータが、デコード可能である可能性が高いことを報告するための通信手段を含む。

【0173】

実施形態では、感知手段は、ステートマシン312、アドレスデコーダ314、電力制御部316、読み出し／書き込み回路328、感知ブロック340、及び／又はラッチ360のうちの1つ以上を含む。

【0174】

実施形態では、XOR手段は、XOR演算362、データラッ奇360、XORアキュムレータラッ奇364、及び／又はメモリコントローラインインターフェース315のうちの1つ以上を含む。実施形態では、XOR手段は、図12に示すプロセスを実行する。実施形態では、XOR手段は、プロセス1400のステップ1406～1412を実行する。

【0175】

実施形態では、ビットエラー率手段は、ECC226/256、プロセッサ220/250、ステートマシン312、シンドローム演算370、デコーダ390、PGA（プログラマブルゲートアレイ、FPGA（フィールドプログラマブルゲートアレイ）、ASIC（特定用途向け集積回路）、集積回路、又は他の種類の回路のうちの1つ以上を含む。一実施形態では、ビットエラー率は、式1の演算を実行する。一実施形態では、ビットエラー率は、ルックアップテーブルを参照して、いくつかの満たされていないパリティチェックWを推定されたBERに変換する。

【0176】

実施形態では、通信手段は、ホスト150へのPCIeインターフェース、メモリコントローラインターフェース315、PGA（プログラマブルゲートアレイ、FPGA（フィールドプログラマブルゲートアレイ）、ASIC（特定用途向け集積回路）、集積回路、又は他の種類の回路のうちの1つ以上を含む。

【0177】

本発明の前述の詳細な説明は、例示及び説明の目的のために提示したものである。前述の詳細な説明は、網羅的であること、又は開示した正確な形態に本発明を限定することを意図したものではない。上記の教示に鑑みて多くの修正及び変形が可能である。説明した実施形態は、本発明の原理及びその実際の用途を最良に説明するために選択されたものであり、それによって、当業者が様々な実施形態で、企図される特定の使用法に適するよう様々な修正を伴って、本発明を最良に利用することを可能にする。本発明の範囲は、本明細書に添付の請求項によって定義されることが意図されている。

10

20

30

40

50

## 【図面】

【図 1 A】

【図 1 B】

10

20

30

40

【図 2 A】

【図 2 B】

50

【図3A】

【図3B】

10

20

30

40

50

【図3C】

【図3D】

【図3E】

【図4】

【図5A】

【図5B】

10

20

30

40

50

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

10

20

30

40

50

【図12】

【図13】

10

20

30

40

50

【図14】

【図15】

10

20

【図16】

【図17】

30

40

50

【図 18 A】

【図 18 B】

【図 19】

10

20

30

40

50

---

フロントページの続き

アメリカ合衆国 カリフォルニア州 95119 サンノゼ , グレート オークス パークウェイ 5

601 , ウエスタン デジタル テクノロジーズ インコーポレーテッド宛

(72)発明者 エラン・シャロン

アメリカ合衆国 カリフォルニア州 95119 サンノゼ , グレート オークス パークウェイ 5

601 , ウエスタン デジタル テクノロジーズ インコーポレーテッド宛

F ターム(参考) 5B048 AA19

5B160 NA02

5L206 AA10 BB01 DD25 EE02 HH05