(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 600 05 259 T2 2004.07.01

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 067 660 B1

(21) Deutsches Aktenzeichen: 600 05 259.1

(96) Europäisches Aktenzeichen: 00 305 690.0

(96) Europäischer Anmeldetag: 06.07.2000

(97) Erstveröffentlichung durch das EPA: 10.01.2001

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 17.09.2003

(47) Veröffentlichungstag im Patentblatt: 01.07.2004

(51) Int Cl.<sup>7</sup>: H02M 3/02

H02H 3/20

(30) Unionspriorität:

**350625** 09.07.1999 US

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**ATI International Srl, Christ Church, BB**

(72) Erfinder:

**Drapkin, Oleg, 905 North York, Ontario MR2 1Z8,

CA; Temkine, Grigori, 404 Toronto, Ontario M6A

1X3, CA**

(74) Vertreter:

**P.E. Meissner und Kollegen, 14199 Berlin**

(54) Bezeichnung: **Einzelgatteroxid Tiefsetzstellerschaltkreis mit Überspannungsschutz**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

[0001] Die Erfindung betrifft allgemein Überspannungsschutzschaltkreise zum Schutz anderer Schaltkreise gegen unerwünscht hohe Spannungspegel und insbesondere Spannungsuntersetzerschaltkreise zum Schutz eines Eingangs in einen geschützten Schaltkreis.

[0002] Angesichts der anhaltenden Forderung nach integrierten Schaltkreisen mit immer höherer Geschwindigkeit und geringerem Stromverbrauch besteht ein Bedarf an einfachen, kostengünstigen und zuverlässigen Überspannungsschutzschaltkreisen. Beispielsweise besteht die Anforderung, dass Videografik-Chips auf CMOS-Basis mit 128 oder mehr Eingangs-/ Ausgangsanschlüssen (E/A-Anschlüssen) bei Taktfrequenzen von 125 MHz bis 250 MHz oder darüber funktionieren sollen. Bei solchen Geräten kann zur Senkung des Stromverbrauchs die Versorgung eines Großteils ihrer Logik durch eine Spannungsquelle von 2,5 V erfolgen. Eine Möglichkeit zur Erhöhung der Betriebsgeschwindigkeit solcher Geräte besteht dann, die Gatelänge der Transistoren der Kernschaltung zu verringern. Eine Verringerung der Gatelänge von MOS-Geräten kann jedoch dazu führen, dass die Gatedurchschlagspannung niedriger wird. Wenn zum Beispiel ein integrierter Schaltkreis digitale Schaltungselemente enthält, die von einer Spannungsquelle von 2,5 V versorgt werden und mit einer Siliziumdioxid-Gatedicke von 50 Angström hergestellt sind, kann sich eine Gatedurchschlagspannung von etwa 3,5 Volt ergeben. Häufig müssen solche integrierten Schaltkreise Verbindungen mit konventionelleren digitalen Geräten herstellen, die mit 5 V oder 3,3 V betrieben werden. Dabei entsteht ein Problem, wenn die (mit 2,5 V betriebene) Kernlogikschaltung an den Eingangsstiften digitale Eingangssignale von 5 V von Peripheriegeräten empfängt. Wenn kein geeigneter Überspannungsschutz eingebaut ist, können solche Standardeingangssignale von 5 V oder Eingangssignale von 3,3 V zu Durchschlagschäden führen.

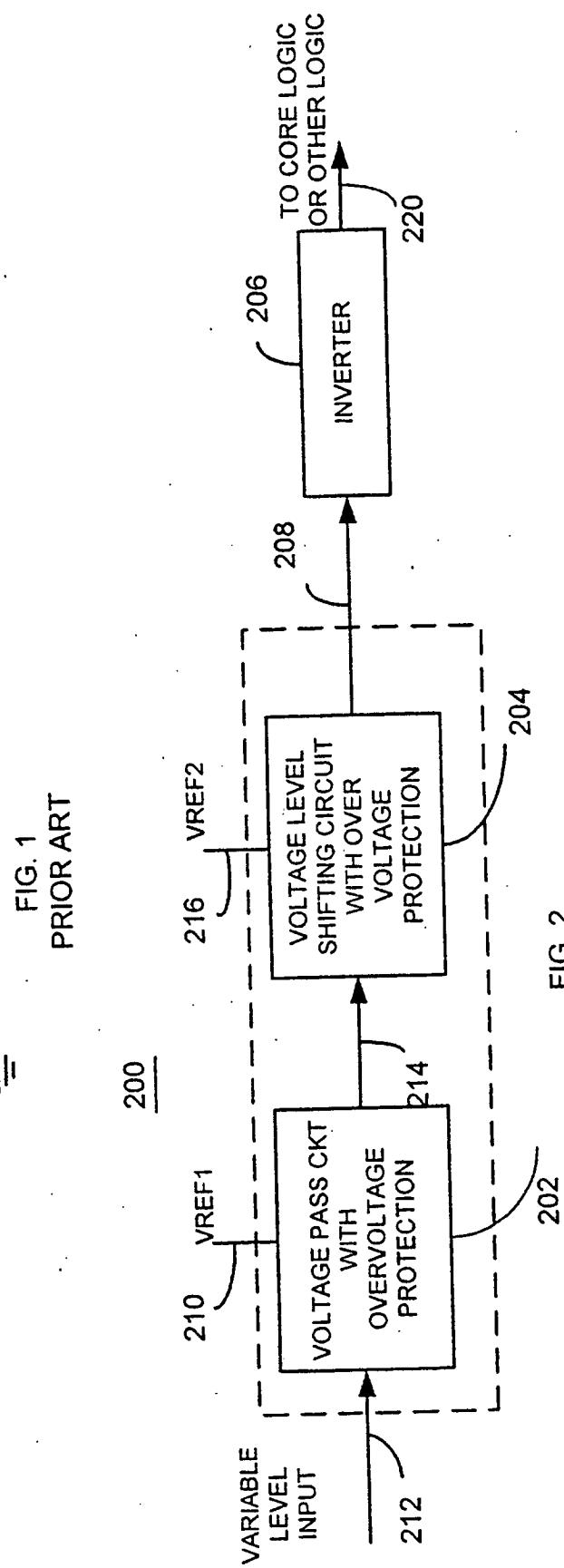

[0003] **Fig. 1** zeigt eine bekannte Überspannungsschutzanordnung, die dieses Problem überwinden soll. Wie man sieht, ist im Eingangspfad von einem Eingangsstift P zum Eingang einer Kernlogikstufe auf MOS-Basis, wie z. B. ein Eingangs-/Ausgangsanschluss an einer Zentraleinheit oder sonstigen Prozessorbaugruppe, ein Widerstand R angeordnet. Quer zum Eingang 1 der Kernlogikstufe ist eine Abfangdiode D angeordnet und an eine Spannungsquelle von 2,5 V angeschlossen, die zum Auffangen der vom Stift P kommenden Überspannungen dient. Unter Betriebsbedingungen begrenzt der Widerstand R den Stromfluss zur Kernlogikschaltung, und es tritt ein Spannungsabfall durch den Widerstand auf. Wenn eine Eingangsspannung hoch genug ist, um die Diode D leitend zu machen, hält die Diode die Eingangsspannung auf einem festen Pegel (2,5V + Spannungsabfall am Diodenanschluss). Bei einer

solchen Konfiguration treten diverse Probleme auf. Wenn die Kernlogik mit einer Gateoxiddicke von 50 Angström hergestellt ist, genügt schon eine Durchschlagspannung von 3,5 V, um die Kernlogikstufe zu beschädigen ( $0,7 \text{ V}/\text{A} \cdot 50 \text{ a} = 3,5 \text{ V}$ ). Bei einem Diodenspannungsabfall von 0,7 Volt ist 3,2 V die maximale Eingangsspannung in die Kernlogikstufe, die jedoch sehr nah bei der Durchschlagspannung von 3,5 V liegt, so dass über die Temperatur und die Zeit die Zuverlässigkeit des Schaltkreises gefährdet sein kann. Außerdem lässt die Abfangdiode D einen zusätzlichen Stromfluss durch das Substrat zu, was zum dauerhaften Leiten (Latch-up) der Kernlogikschaltung führen kann.

[0004] Ein weiteres Problem ist der Einsatz des Widerstands R. Solche ohmschen Elemente beanspruchen in integrierten Schaltkreisen viel Platz und bewirken beim Anlegen einer Eingangsspannung von beispielsweise 5 Volt an den Stift P eine Abstrahlung von viel Energie und somit Wärme. Außerdem kann durch den Widerstand R und den kapazitiven Störwiderstand des Gateanschlusses der Kernlogikschaltung eine große Zeitverzögerung auftreten. Diese Zeitverzögerung verringert die Betriebsgeschwindigkeit des Systems.

[0005] Es sind noch andere Überspannungsschutzschaltungen bekannt, wie z. B. aus dem US-Patent Nr. 5.905.621 mit dem Titel "Spannungsuntersetzerschaltkreis zum Schutz eines Eingangsknotens in einen geschützten Schaltkreis", der Einzelgatteroxid-Überspannungsschutzschaltkreise beinhaltet kann. Solche Schaltkreise können in vielen Anwendungsfällen recht nützlich sein. Bei der Ausführungsform, bei der ein NMOS-Spannungs durchlassgerät mit einer Eingangsspannung beaufschlagt wird, kann jedoch der Ausgang der Überspannungsschutzschaltung auf eine Gateversorgungsspannung abzüglich einer Schwellenspannung des Spannungs durchlassgerätes begrenzt sein. Bei geschützten Schaltkreisen mit niedrigeren Quellenspannungen kann es aber zum Beispiel wünschenswert sein, den Ausgang der Schutzschaltung ohne einen zusätzlichen Schwellenspannungsabfall zu haben.

[0006] Eine weitere Überspannungsschutzschaltung ist zum Beispiel aus dem US-Patent Nr. 5.319.259 vom 7. Juni 1994 mit dem Titel "Niederspannungseingangs- und -ausgangsschaltkreise mit Überspannungsschutz" bekannt. Bei einem solchen Stromkreis kommt u. a. ein Rückkopplungspfad zur Anwendung, mit dem ein Ausgang einer Schutzschaltung hochgesetzt werden soll, der als Eingang für eine andere Stufe dient. Eine solche Schaltung kann jedoch anfangen, Strom zu verbrauchen, wenn der Spannungseingang von einem Hochpegel zu einem Niederpegel wechselt. Die Schutzschaltung selbst kann zum Beispiel unnötigerweise Strom verbrauchen, wenn die das Eingangssignal bereitstellende Eingangsstufe nicht genug Treibstrom hat, um einen Eingangsdurchlasstransistor ordnungsgemäß zu schalten.

[0007] Infolgedessen besteht Bedarf an einer Einzelgatteroxid-Schutzschaltung, die den Stromverbrauch senkt und die Betriebsgeschwindigkeit eines Systems auf einfache und zuverlässige Weise steigert. Es wäre wünschenswert, wenn die Schutzschaltung ohne Eingangsstromverbrauch sowie ohne GS-Stromverbrauch bei Bedarf eine Ausgangsspannung bereitstellen würde, die im Wesentlichen gleich der Bezugsspannung der Schutzschaltung ist.

[0008] Nach einem ersten Aspekt der vorliegenden Erfindung beinhaltet ein Eingangsstufenschaltkreis zur Spannungsumsetzung einen Überspannungsschutz, bestehend aus einem Spannungsdurchlassschaltkreis mit einem ersten Anschluss, der wirksam zur Aufnahme einer ersten Bezugsspannung gekoppelt ist, einem zweiten Anschluss, der wirksam zur Aufnahme eines Eingangssignals gekoppelt ist, dessen Spannungspegel höher und niedriger als die Bezugsspannung sein kann, und einem dritten Anschluss, wobei der Spannungsdurchlassschaltkreis aus einer Einzelgatteroxidicke besteht; und

einem Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis mit einem wirksam zwischen dem dritten Anschluss des Spannungsdurchlassschaltkreises und einem Ausgangssignalanschluss des Spannungstiefsetzstellerschaltkreises gekoppelten Einzelgatteroxid-Überspannungsschaltkreis, wobei der Spannungstiefsetzstellerschaltkreis die Erzeugung eines skalierten Ausgangssignals bewirkt, dessen maximaler Spannungspegel im Wesentlichen gleich einer zweiten Bezugsspannung ist, wenn die Eingangsspannung die zweite Bezugsspannung übersteigt.

[0009] Nach einem zweiten Aspekt der vorliegenden Erfindung besteht ein Verfahren zur Schaffung einer Spannungsumsetzung und eines Überspannungsschutzes für einen Eingangsstufenschaltkreis aus folgenden Schritten:

Aufnahme eines Eingangssignals durch einen Einzelgatteroxid-Spannungsdurchlassschaltkreis, wobei der Spannungspegel des Eingangssignals höher und niedriger als eine erste Bezugsspannung für den Spannungsdurchlassschaltkreis sein kann; und Umsetzung eines Spannungspegels des Eingangssignals von einem ersten logischen Hochpegel auf einen zweiten niedrigeren logischen Hochpegel durch einen Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis, der wirksam an eine zweite Bezugsspannung gekoppelt ist und auch einen Einzelgatteroxid-Überspannungsschaltkreis aufweist, um ein skaliertes Ausgangssignal zu erzeugen, dessen maximaler Spannungspegel im Wesentlichen gleich der zweiten Bezugsspannung ist, wenn das Eingangssignal die zweite Bezugsspannung übersteigt.

[0010] Unter Bezugnahme auf die Zeichnungen wird die Erfindung anhand von Beispielen leichter verständlich sein. In den Zeichnungen zeigen:

[0011] **Fig. 1** eine Überspannungsschutzschaltung nach dem bekannten Stand der Technik;

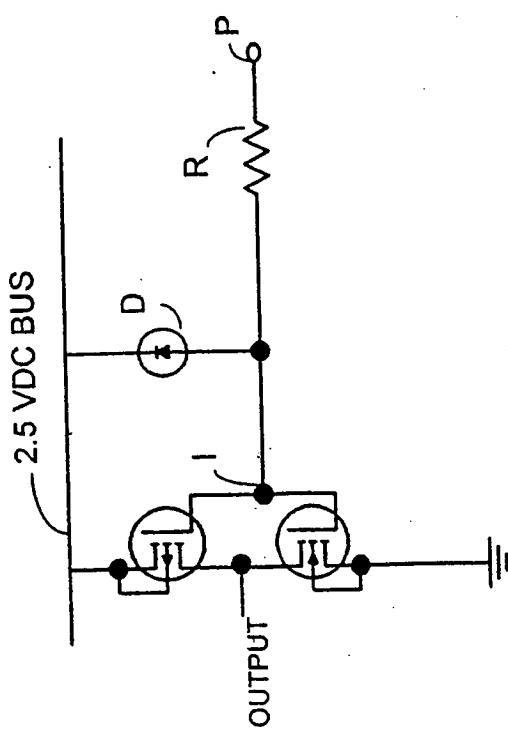

[0012] **Fig. 2** ein Blockdiagramm zur Veranschaulichung eines Beispiels der Erfindung nach einer Ausführungsform der Erfindung;

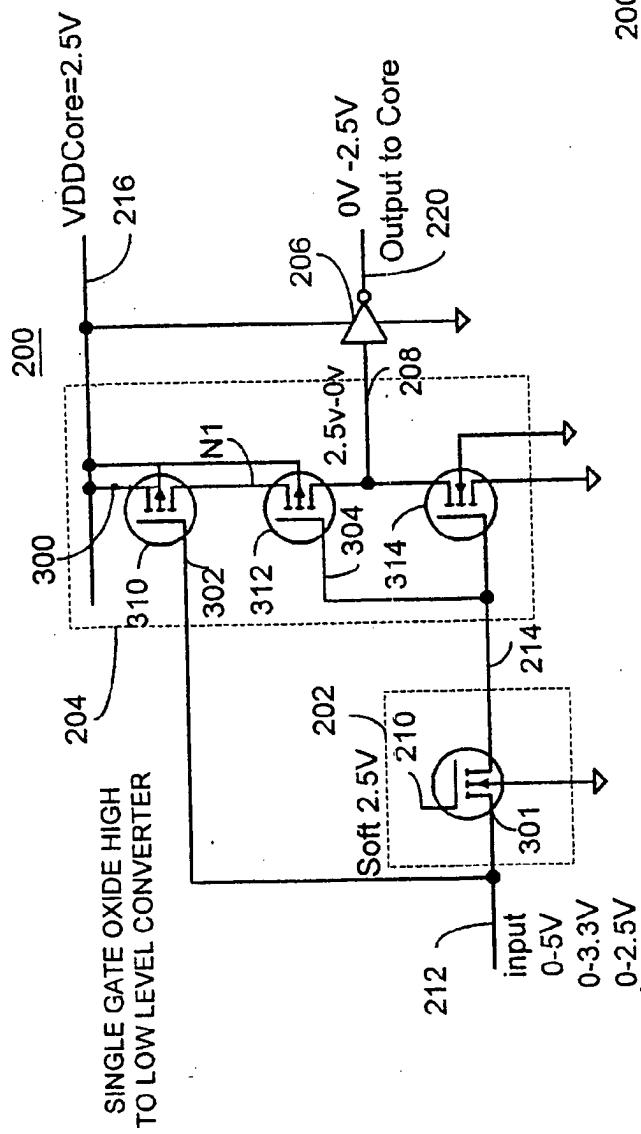

[0013] **Fig. 3** ein Beispiel des Spannungsuntersetzerschaltkreises nach einer Ausführungsform der Erfindung; und

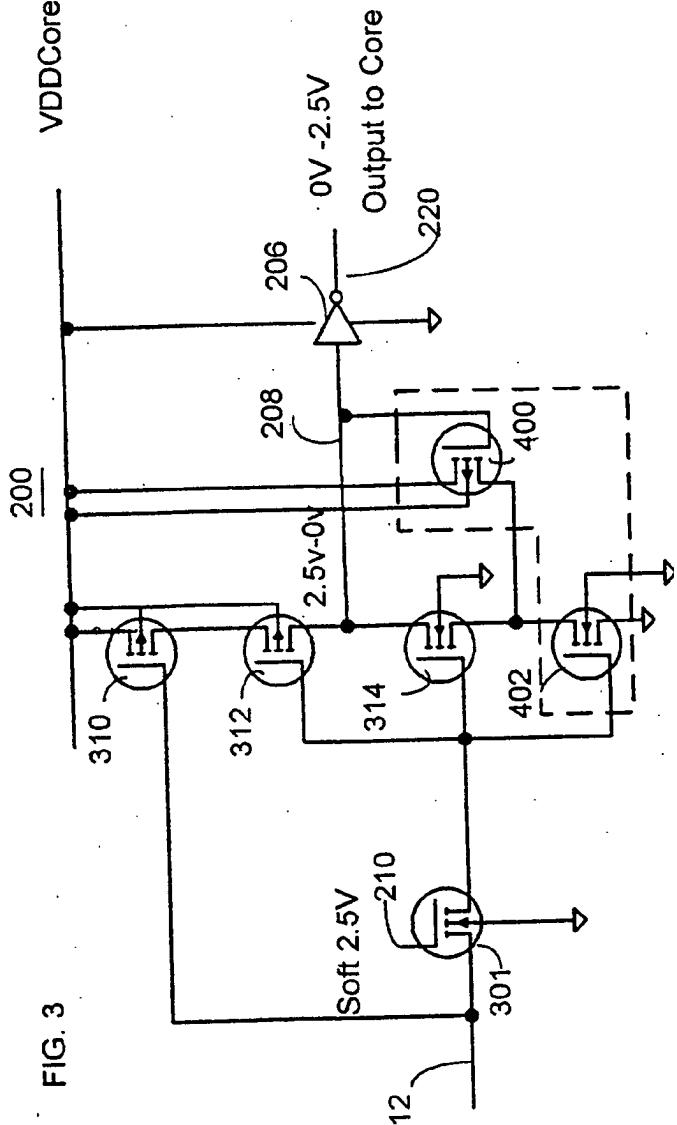

[0014] **Fig. 4** ein Schaltbild zur Veranschaulichung des Schaltkreises aus **Fig. 3**, bei dem auch eine Schmitt-Triggerschaltung zur Rauschverminderung verwendet wird.

[0015] Kurz gesagt, wird durch einen Eingangsstufenschaltkreis und ein Verfahren eine Spannungsumsetzung und ein Überspannungsschutz für einen Eingangsstufenschaltkreis unter Verwendung eines Einzelgatteroxid-Spannungsdurchlassschaltkreises und eines Einzelgatteroxid-Spannungstiefsetzstellerschaltkreises geschaffen. Bei einer Ausführungsform beinhaltet der Schaltkreis und das Verfahren die Aufnahme eines Eingangssignals durch den Einzelgatteroxid-Spannungsdurchlassschaltkreis, wobei der Spannungspegel des Eingangssignals höher und niedriger als eine erste Bezugsspannung für den Spannungsdurchlassschaltkreis sein kann. Ein Ausgangssignal vom Spannungsdurchlassschaltkreis wird einem Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis bereitgestellt, der mittels Inverter den Spannungspegel des Eingangssignals von einem ersten logischen Hochpegel auf einen zweiten niedrigeren logischen Hochpegel umsetzt, wenn das Eingangssignal eine Bezugsspannung übersteigt. Der Schaltkreis und das Verfahren erzeugt ein skaliertes Ausgangssignal, dessen maximaler Spannungspegel im Wesentlichen gleich einer mit dem Tiefsetzstellerschaltkreis zusammenhängenden Bezugsspannung ist, wenn das Eingangssignal die Bezugsspannung übersteigt, so dass ein Ausgangssignal für einen geschützten Schaltkreis, wie z. B. eine Kernlogikschaltung, höher ist als ein Eingangssignal minus ein Schwellenspannungsabfall, der durch den Spannungsdurchlassschaltkreis auftritt. Bei einer anderen Ausführungsform wird für ein Ausgangssignal vom Spannungstiefsetzstellerschaltkreis Hysterese einzogen, um für eine angemessene Rauschverminderung zu sorgen, bevor das umgesetzte Signal nachfolgenden Stufen zugeleitet wird.

[0016] **Fig. 2** veranschaulicht ein Beispiel eines Eingangsstufenschaltkreises **200**, der in einem beliebigen geeigneten Schaltkreis verwendet werden kann. Beispielsweise kann der Eingangsstufenschaltkreis **200** als Schnittstelle zu Kernschaltungselementen mit einer Stromversorgung von 2,5 V oder mit einem anderen geeigneten Spannungspegel in einem integrierten Schaltkreis verwendet werden, wie z. B. in einem Video- und/oder Grafikverarbeitungsschaltkreis, einem Mikroprozessor oder einem anderen geeigneten integrierten Schaltkreis. Der Eingangsstufenschaltkreis **200** ist für die Aufnahme mehrerer verschiedener Spannungsbereiche ausgelegt, wie z. B. 0 bis 5 V, 0 bis 3,3 V, 0 bis 2,5 V oder sonstige geeignete Spannungsbereiche. Dadurch lässt sich der Ein-

gangsstufenschaltkreis **200** an unterschiedliche Schaltkreise koppeln, die derartige Spannungspegel liefern können. Auf diese Weise ist es möglich, den Eingangsstufenschaltkreis **200** an neuere und ältere Schaltkreise sowie an Schaltkreise mit verschiedenen Stromversorgungspegeln und Ausgangssignalpegeln zu koppeln.

[0017] Der Eingangsstufenschaltkreis **200** weist einen Spannungsdurchlassschaltkreis **202** mit Überspannungsschutz und einen Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis **204** mit Überspannungsschutz auf. Ein Inverter **206** oder irgendein anderes geeignetes logisches Element am Ausgang des Tiefsetzstellerschaltkreises **204** stellt nicht invertierten Ausgang **220** zur Kernlogik oder zu anderen logischen Schaltkreisen bereit. Der Spannungsdurchlassschaltkreis **202** besteht aus einem oder mehreren Einzelgatteroxidgeräten mit der gleichen Gateoxiddicke wie die Geräte, aus denen der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis **204** besteht. Dadurch bietet der Eingangsstufenschaltkreis **200** u. a. den Vorteil, dass für alle enthaltenen Bauelemente ein einheitliches Herstellungsverfahren beibehalten werden kann. Die Einzelgattergeräte weisen vorzugsweise die gleiche Gateoxiddicke auf wie der Schaltkreis, für den sie eine skalierte Ausgangsspannung **220** bereitstellen. Die externen Schaltungselemente, die die skalierte Ausgangsspannung **220** aufnehmen, können zum Beispiel eine Kernlogikschaltung oder andere geeignete logische Elemente sein. Der Spannungsdurchlassschaltkreis **202** ist mit einheitlicher Gateoxiddicke hergestellt und weist einen ersten Anschluss auf, der wirksam zur Aufnahme einer ersten Bezugsspannung **210** gekoppelt ist. Der hier gebrauchte Ausdruck "Anschluss" kann jeder Draht, Kontaktfleck, Knotenpunkt, jede Spur oder jeder andere geeignete Mechanismus sein, der eine direkte oder indirekte Kopplung zur Aufnahme elektrischer oder optischer Energie ermöglicht. Der Spannungsdurchlassschaltkreis **202** weist ferner einen zweiten Anschluss auf, der wirksam zur Aufnahme eines Eingangssignals (**212**) gekoppelt ist, dessen Spannungspegel höher und niedriger als die Bezugsspannung (**210**) sein kann. Über einen dritten Anschluss gibt der Spannungsdurchlassschaltkreis **202** eine durchgelassene Spannung **214** aus.

[0018] Die Bezugsspannung **210** ist auf einen Pegel eingestellt, der eine Gate-Source-Spannung oder Gate-Drain-Spannung in akzeptablen normalen Betriebsbereichen gewährleistet.

[0019] Dadurch ist Überspannungsschutz für den Spannungsdurchlassschaltkreis **202** gewährleistet.

[0020] Der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis **204** bewirkt die Erzeugung eines skalierten Ausgangssignals **208**, dessen maximaler Spannungspegel im Wesentlichen gleich einer Bezugsspannung **216** ist. Der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis **204** weist einen Anschluss zur Aufnahme einer durchgelassenen Span-

nung **214** und einen Ausgangssignalanschluss zur Ausgabe der skalierten Ausgangsspannung **208** auf. [0021] Fig. 3 veranschaulicht ein Beispiel einer Ausführungsform des Eingangsstufenschaltkreises **200**. Bei dieser Ausführungsform weist der Spannungsdurchlassschaltkreis **202** ein NMOS-Transistorgerät **301** mit einem Gate als erstem Anschluss, einer Source als zweitem Anschluss zur Bereitstellung der durchgelassenen Spannung **214** und einem Drain als drittem Anschluss zur Aufnahme des variablen Eingangssignals **212** auf.

[0022] Der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis **204** weist einen wirksam an die Bezugsspannung **216** gekoppelten Anschluss **300**, einen wirksam zur Aufnahme des Eingangssignals **212** gekoppelten Anschluss **302** und einen wirksam an den dritten Anschluss des Spannungsdurchlassschaltkreises gekoppelten Anschluss **304** zur Aufnahme der durchgelassenen Spannung **214** auf. Bei dieser Ausführungsform weist der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis **204** einen PMOS-Transistor **310**, einen Spannungsschutz-PMOS-Transistor **312** und einem NMOS-Transistor **314** auf. Der PMOS-Transistor **310** hat ein Gate, das wirksam zur Aufnahme des Eingangssignals **212** gekoppelt ist, eine Source, die wirksam an die Bezugsspannung **216** gekoppelt ist, und einen Drain, der wirksam an eine Source des PMOS-Transistors **312** gekoppelt ist. Der PMOS-Transistor **312** hat ein Gate, das wirksam an die Source des NMOS-Durchlasstransistors gekoppelt ist, und einen Drain, der die Erzeugung eines skalierten Ausgangssignals **208** bewirkt. Der Drain ist auch an die Source des NMOS-Transistors **314** gekoppelt. Der NMOS-Transistor **314** hat eine Source, die auch das skalierte Ausgangssignal **208** bereitstellt, ein Gate, das wirksam zur Aufnahme der durchgelassenen Eingangsspannung gekoppelt ist und wirksam an die Source des NMOS-Transistor-durchlassschaltkreises gekoppelt ist, und einen Drain, der wirksam an Erde gekoppelt ist. Die Transistoren **310**, **312**, **314** und der Durchlasstransistor **301** sind in Form von Einzelgatteroxidgeräten hergestellt, vorzugsweise mit einer Gateoxiddicke von weniger als 50 Å. Man wird erkennen, dass bei Bedarf auch eine andere geeignete Transistorkonfiguration verwendet werden kann. Die Kopplung kann im Übrigen je nach der gewünschten Implementierung des Schaltkreises entweder direkt oder indirekt erfolgen.

[0023] Die Bezugsspannung **216** kann beispielsweise eine Kernlogikversorgungsspannung von 2,5 V oder eine andere geeignete Bezugsspannung sein. Die Bezugsspannung **210** kann beispielsweise bei Bedarf die gleiche Spannung wie die Bezugsspannung **216** sein, jedoch von der Bezugsspannung **216** getrennt.

[0024] Unter Betriebsbedingungen ist der Spannungsbereich der vom Eingangsstufenschaltkreis **200** und Inverter **206** ausgegebenen skalierten Ausgangsspannung **220** im Wesentlichen gleich dem

Eingangsspannungsbereich **212**, wenn beispielsweise die Eingangsspannung im L-Bereich liegt. Wenn zum Beispiel eine variable Eingangsspannung **212** im Bereich von 0 bis 2,5 V liegt, wird das Ausgangsspannungssignal **208** im Bereich von 2,5 V bis 0 V liegen. Bei der Weiterleitung zum Inverter **206** wird die Ausgangsspannung **220** für Kernschaltungselemente oder andere Schaltungselemente beispielsweise 0 V bis 2,5 V betragen. Der Spannungstiefsetzstellerschaltkreis **204** erzeugt zusammen mit dem Inverter **206** eine Ausgangsspannung **220**, deren Bereich im Wesentlichen gleich dem der Eingangsspannung im L-Bereich ist. Auch die maximale Ausgangsspannung **208** sowie die maximale Ausgangsspannung **220** ist im Wesentlichen gleich der Bezugsspannung **216**, wodurch ein durch den Spannungsduchlasstransistor **301** eingebauter Spannungsschwellenabfall vermieden wird. Wenn unter Überspannungsbedingungen z. B. die Eingangsspannung **212** von 0 bis 5 V geht, ermöglichen die Transistoren **310**, **312** und **314** den vollen Bereich von 0 V bis 2,5 V ohne Stromentnahme. Außerdem sind die Transistoren **310**, **312** und **314** gegen Überspannungszustände dadurch geschützt, dass ein Gate-Drain-Potenzial und Gate-Source-Potenzial bereitgestellt wird, das in den normalen Betriebsbereichen für die Geräte liegt.

[0025] Während das Eingangssignal **212** vom logischen Element 0 zum logischen Element 1 geht, begrenzt der Durchlasstransistor **301** die Durchgangsspannung **14** auf etwa die Bezugsspannung **210** minus Schwellenspannung für alle logischen Hochpegel, so dass die Transistoren **301** und **314** nicht durch Überspannungszustände beschädigt werden. Der Transistor **314** schaltet sich ein, der Transistor **310** schaltet sich aus, und die Ausgangsspannung **208** wird zwangsgeerdet. Wenn zum Beispiel die Eingangsspannung 5 V beträgt, wird die Spannung am Knoten N1 niedrig genug gehalten, um die Transistoren **310** und **312** während solcher Überspannungszustände (d. h. wenn die Bezugsspannung zum Beispiel 2,5 V und der logische Hochpegel der Eingangsspannung 5 V beträgt) vor Schäden zu bewahren. Die Spannung bei N1 muss jedoch hoch genug sein, um den Transistor **312** ausgeschaltet zu lassen, darf aber nicht so niedrig sein, dass der Drain-Gate-Pfad beschädigt wird. Wenn der Transistor **310** ausgeschaltet ist, findet kein Stromdurchgang durch den Transistor **312** statt. In diesem Fall ist die Gate-Source-Spannung des Transistors **312** niedriger als beispielsweise die durchgelassene Spannung **214** plus Schwellenspannung des Transistors **312** (in diesem Beispiel ergibt die Summe 2,5 V). Der Transistor **312** trennt die Drains von Transistor **314** und Transistor **310**. Wenn der Transistor **314** im "Ein"-Zustand und der Transistor **310** im "Aus"-Zustand ist, würde die Gate-Drain-Spannung des Transistors **310** ohne die durch den Transistor **312** bewirkte Trennung 5 V betragen. In diesem Fall würde der Einzelgatteroxid-Transistor **310** beschädigt werden.

[0026] Der Schaltkreis als solcher funktioniert so,

dass bei einer Eingangsspannung von 0 V die durchgelassene Spannung **214** etwa 0 V, die Ausgangsspannung **208** etwa 2,5 V und die Spannung bei N1 etwa 2,5 V beträgt. Der Ausgang zum Kern beträgt nach erfolgter Inversion 0 V. Außerdem ist Transistor **310** "Ein", Transistor **314** ist "Aus", Transistor **310** ist "Ein", und Transistor **312** ist "Ein". Bei einer Eingangsspannung von 5 V beträgt die durchgelassene Spannung etwa 1,8 V, und die Ausgangsspannung **208** beträgt etwa 0 V, weil der Transistor **314** eingeschaltet ist. Die Spannung bei N1 beträgt 2,5 V, was hoch genug ist, um eine Beschädigung zwischen dem Gate-Drain-Transistor **310** und dem Source-Gate-Transistor **312** zu vermeiden. Sie ist auch niedrig genug, um den Transistor **312** ausgeschaltet zu lassen. Die Ausgangsspannung zum Kern beträgt nach erfolgter Inversion 2,5 V.

[0027] Fig. 4 zeigt eine andere Ausführungsform des Schaltkreises **200** unter Einbeziehung einer Hystereseschaltung, die wirksam zur Aufnahme des Ausgangssignals **208** gekoppelt ist, um die Rauschverminderung für ein skaliertes Ausgangssignal zu fördern. Bei dieser Ausführungsform ist die Hystereseschaltung in Form einer Schmitt-Triggerschaltung mit mehreren Transistoren **400** und **402** ausgeführt. Das Ausgangssignal **208** als solches kann in angemessener Weise gefiltert werden, um den Durchgang von Störimpulsen durch die an den Ausgang des Eingangsstufenschaltkreises **200** angeschlossene Kernlogikschaltung oder sonstige Schaltung zu vermeiden. Es kann aber auch jede andere geeignete Rauschverminderungsschaltung verwendet werden.

#### Bezugszeichenliste

FIG. 1

#### Bekannter Stand der Technik

|                    |                        |

|--------------------|------------------------|

| <b>2.5 VDC bus</b> | Sammelschiene 2,5 V GS |

| <b>Output</b>      | Ausgang                |

FIG. 2

|                                     |                                                       |

|-------------------------------------|-------------------------------------------------------|

| <b>Variable level input</b>         | Eingang mit variablem Pegel                           |

| <b>VREF1 (2)</b>                    | Bezugsspannung 1 (2)                                  |

| <b>Voltage pass ckt with ...</b>    | Spannungsdurchlassschaltkreis mit Überspannungsschutz |

| <b>Inverter</b>                     | Inverter                                              |

| <b>To core logic or other logic</b> | Zur Kernlogik oder sonstigen Logik                    |

FIG. 3

|                                          |                                           |

|------------------------------------------|-------------------------------------------|

| <b>Single gate oxide high to low ...</b> | Einzelgatteroxid-Spannungstiefsetzsteller |

| <b>Input</b>                             | Eingang                                   |

| <b>Soft</b>                              | Weich                                     |

| <b>VDD core = 2.5V</b>                   | VDD-Kern = 2,5 V                          |

| <b>Output to core</b>                    | Ausgang zum Kern                          |

FIG. 4

(Beschriftung wie FIG. 3)

### Patentansprüche

1. Eingangsstufenschaltkreis (200) zur Spannungsumsetzung mit Überspannungsschutz, bestehend aus einem Spannungs durchlassschaltkreis (202) mit einem ersten Anschluss, der wirksam zur Aufnahme einer ersten Bezugsspannung (210) gekoppelt ist, einem zweiten Anschluss, der wirksam zur Aufnahme eines Eingangssignals (212) gekoppelt ist, dessen Spannungspegel höher und niedriger als die erste Bezugsspannung (210) sein kann, und einem dritten Anschluss, wobei der Spannungs durchlassschaltkreis aus einer Einzelgatteroxiddicke besteht; und einem Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis (204) mit einem wirksam zwischen dem dritten Anschluss des Spannungs durchlassschaltkreises (202) und einem Ausgangssignalanschluss des Spannungstiefsetzstellerschaltkreises (204) gekoppelten Einzelgatteroxid-Überspannungsschaltkreis, wobei der Spannungstiefsetzstellerschaltkreis (204) die Erzeugung eines skalierten Ausgangssignals (208) bewirkt, dessen maximaler Spannungspegel im Wesentlichen gleich einer zweiten Bezugsspannung (216) ist, wenn die Eingangsspannung (212) die zweite Bezugsspannung (216) übersteigt.

2. Schaltkreis nach Anspruch 1, bei dem der Spannungs durchlassschaltkreis (202) ein Transistor (301) ist.

3. Schaltkreis nach Anspruch 1 oder 2, bei dem der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis (204) einen vierten Anschluss, der wirksam an die zweite Bezugsspannung (216) gekoppelt ist, einen fünften Anschluss, der wirksam zur Aufnahme des Eingangssignals (212) gekoppelt ist, und einen sechsten Anschluss, der wirksam an den dritten Anschluss des Spannungs durchlassschaltkreises (202) gekoppelt ist, aufweist.

4. Schaltkreis nach einem der vorhergehenden Ansprüche, bei dem der Einzelgatteroxid-Spannungs durchlassschaltkreis (202) eine NMOS-Transistorvorrichtung (301) mit einem Gate als erstem An-

schluss, einer Source als zweitem Anschluss und einem Drain als drittem Anschluss aufweist.

5. Schaltkreis nach einem der vorhergehenden Ansprüche, bei dem der Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis (204) mindestens einen ersten Transistor (310), der wirksam an die zweite Bezugsspannung (216) und an das Eingangssignal (212) gekoppelt ist, einen zweiten Transistor (312), der wirksam an den ersten Transistor (310) und an den dritten Anschluss gekoppelt ist, und einen dritten Transistor (314), der wirksam an den zweiten Transistor (312) und an den dritten Anschluss des Spannungs durchlassschaltkreises (202) gekoppelt ist, aufweist.

6. Eingangsstufenschaltkreis (200) zur Spannungsumsetzung mit Überspannungsschutz, bestehend aus mindestens einem NMOS-Spannungsdurchlasstransistor (301) mit einem Gate, das wirksam zur Aufnahme einer ersten Bezugsspannung (210) gekoppelt ist, einem Drain, der wirksam zur Aufnahme eines Eingangssignals (212) gekoppelt ist, dessen Spannungspegel höher und niedriger als die erste Bezugsspannung (210) sein kann, und einer Source zur Ausgabe eines durchgelassenen Eingangssignals (214); und einem Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis (204) mit einem ersten PMOS-Transistor (310), einem zweiten PMOS-Transistor (312) und einem NMOS-Transistor (314), wobei der erste PMOS-Transistor (310) ein Gate, das wirksam zur Aufnahme des Eingangssignals (212) gekoppelt ist, eine Source, die wirksam an eine zweite Bezugsspannung (216) gekoppelt ist, und einen Drain, der wirksam an eine Source des zweiten PMOS-Transistors (312) gekoppelt ist, aufweist und wobei der zweite PMOS-Transistor (312) ein Gate, das wirksam an die Source des NMOS-Durchlasstransistors (301) gekoppelt ist, und einen Drain, der die Erzeugung eines skalierten Ausgangssignals (208) bewirkt, aufweist und wobei der NMOS-Transistor (314) eine Source, die wirksam an den Drain des zweiten PMOS-Transistors (312) gekoppelt ist, und ein Gate, das wirksam zur Aufnahme des durchgelassenen Eingangssignals (214) gekoppelt ist, aufweist; und wobei der NMOS-Spannungsdurchlasstransistor (301), der erste PMOS-Transistor (310), der zweite PMOS-Transistor (312) und der NMOS-Transistor (314) in Form von Einzelgatteroxidvorrichtungen hergestellt sind.

7. Schaltkreis nach Anspruch 5 oder 6 unter Einbeziehung einer Hystereseschaltung, die wirksam an den dritten Anschluss des Spannungs durchlassschaltkreises (202) bzw. an die Source des NMOS-Spannungsdurchlasstransistors und wirksam an das skalierte Ausgangssignal gekoppelt ist, um die Rauschverminderung für das skalierte Ausgangs-

signal zu fördern.

8. Schaltkreis nach Anspruch 7, bei dem die Hystereseschaltung eine Schmitt-Triggerorschaltung ist.

9. Schaltkreis nach einem der Ansprüche 4 bis 6 oder einem davon abhängigen Anspruch, wenn dieser entweder von Anspruch 2 oder Anspruch 3 abhängt, sofern von Anspruch 2 abhängig, bei dem die Transistoren (**301, 310, 312, 314**) des Einzelgatteroxid-Spannungstiefsetzstellerschaltkreises (**204**) und des Einzelgatteroxid-Spannungs durchlassschaltkreises (**202**) eine Gatteroxiddicke von 50 Å oder weniger haben und bei dem das Eingangssignal (**212**) einer von mehreren, und zwar von mindestens drei verschiedenen Spannungsbereichen ist.

10. Schaltkreis nach einem der vorhergehenden Ansprüche, bei dem die erste und zweite Bezugsspannung (**210, 216**) 2,5 V beträgt und bei dem das Eingangssignal (**212**) zwischen mindestens 0 und 5 V variieren kann.

11. Verfahren zur Schaffung einer Spannungs umsetzung und eines Überspannungsschutzes für einen Eingangsstufenschaltkreis, bestehend aus folgenden Schritten:

Aufnahme eines Eingangssignals (**212**) durch einen Einzelgatteroxid-Spannungs durchlassschaltkreis (**202**), wobei der Spannungspegel des Eingangssignals (**212**) höher und niedriger als eine erste Bezugsspannung (**210**) für den Spannungs durchlassschaltkreis (**202**) sein kann; und

Umsetzung eines Spannungspegels des Eingangssignals (**212**) von einem ersten logischen Hochpegel auf einen zweiten niedrigeren logischen Hochpegel durch einen Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis (**204**), der wirksam an eine zweite Bezugsspannung (**216**) gekoppelt ist und auch einen Einzelgatteroxid-Überspannungsschutzschaltkreis aufweist, um ein skaliertes Ausgangssignal (**208**) zu erzeugen, dessen maximaler Spannungspegel im Wesentlichen gleich der zweiten Bezugsspannung (**216**) ist, wenn das Eingangssignal (**212**) die zweite Bezugsspannung (**216**) übersteigt.

12. Verfahren nach Anspruch 11 unter Einbeziehung der Schaffung einer Hystere für einen Ausgangssignalanschluss, um die Rauschverminderung für ein skaliertes Ausgangssignal (**208**) aus dem Einzelgatteroxid-Spannungstiefsetzstellerschaltkreis (**204**) zu fördern.

Es folgen 2 Blatt Zeichnungen

VDDCore=2.5V

३

५