(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4053232号

(P4053232)

(45) 発行日 平成20年2月27日(2008.2.27)

(24) 登録日 平成19年12月14日(2007.12.14)

(51) Int.Cl.

F 1

**H01L 21/8247 (2006.01)**

**H01L 27/115 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

**H01L 27/10 434**

**H01L 29/78 371**

請求項の数 11 (全 27 頁)

(21) 出願番号

特願2000-353423 (P2000-353423)

(22) 出願日

平成12年11月20日 (2000.11.20)

(65) 公開番号

特開2002-158300 (P2002-158300A)

(43) 公開日

平成14年5月31日 (2002.5.31)

審査請求日

平成16年3月1日 (2004.3.1)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 池田 良広

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内

(72) 発明者 岡崎 勉

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内

(72) 発明者 塚本 恵介

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性半導体記憶装置を含む半導体集積回路装置であって、

主面を有する半導体基板と、

前記半導体基板の主面上に互いに隣接して形成され、それぞれが第1ゲート絶縁膜と、

フローティングゲート電極と、第2ゲート絶縁膜と、コントロールゲート電極と、両側壁部にエッティング防止膜を有する第1保護絶縁膜とからなり、それらの順で積層された少なくとも一対の積層構造体と、

前記一対の積層構造体の互いに対向する側壁部間に位置する前記半導体基板の主面に形成され、ソース領域またはドレイン領域として作用する第1不純物導入領域と、

前記一対の積層構造体のそれぞれの側壁部を覆って形成され、その底部が前記第1不純物導入領域の一表面部に延在する第2保護絶縁膜と、

前記一対の積層構造体の互いに対向する前記側壁部を覆う前記第2保護絶縁膜によって規定された接続孔を埋めるように形成され、前記第1不純物導入領域に電気的に接続された第1導体層と、

を有し、

前記第1ゲート絶縁膜は、酸化シリコン膜からなり、

前記第1保護絶縁膜は、少なくともその一部に酸化シリコン膜を含み、

前記エッティング防止膜および前記第2保護絶縁膜は、窒化シリコン膜からなることを特徴とする半導体集積回路装置。

10

20

**【請求項 2】**

請求項 1 記載の半導体集積回路装置において、前記第 1 保護絶縁膜は、酸化シリコン膜とその上部に積層された窒化シリコン膜とからなることを特徴とする半導体集積回路装置。

**【請求項 3】**

請求項 1 記載の半導体集積回路装置において、前記第 1 不純物導入領域は、ドレイン領域として作用し、前記第 1 導体層は、データ線の一部として作用することを特徴とする半導体集積回路装置。

**【請求項 4】**

請求項 3 記載の半導体集積回路装置において、前記少なくとも一対の積層構造体の上部には、少なくとも一層以上の酸化シリコン膜からなる層間絶縁膜が形成され、前記データ線は、前記層間絶縁膜上に形成されていることを特徴とする半導体集積回路装置。 10

**【請求項 5】**

請求項 3 記載の半導体集積回路装置において、前記一対の積層構造体の前記第 1 不純物導入領域が形成された側壁部とは反対側の側壁部に位置する前記半導体基板の主面には、ソース領域として作用する第 2 不純物領域が形成され、前記第 2 不純物領域には、ソース線の一部として作用する第 2 導体層が電気的に接続されていることを特徴とする半導体集積回路装置。

**【請求項 6】**

請求項 5 記載の半導体集積回路装置において、前記ソース線の一部として作用する第 2 導体層は、前記第 2 不純物領域を挟む前記一対の積層構造体の互いに対向する前記側壁部を覆う前記第 2 保護絶縁膜によって規定された接続孔を埋めるように形成されていることを特徴とする半導体集積回路装置。 20

**【請求項 7】**

請求項 1 記載の半導体集積回路装置において、前記第 2 ゲート絶縁膜は、酸化シリコン膜と窒化シリコン膜とを交互に 3 層以上積層した絶縁膜からなることを特徴とする半導体集積回路装置。

**【請求項 8】**

請求項 1 記載の半導体集積回路装置において、前記少なくとも一対の積層構造体のそれぞれは、フラッシュメモリのメモリセルを構成し、前記メモリセルの書き込みは、前記フローティングゲート電極に電荷を注入して行うことを特徴とする半導体集積回路装置。 30

**【請求項 9】**

請求項 8 記載の半導体集積回路装置において、前記フラッシュメモリは、NOR 型フラッシュメモリであることを特徴とする半導体集積回路装置。

**【請求項 10】**

以下の工程を有する半導体集積回路装置の製造方法：

( a ) 半導体基板の主面に酸化シリコン膜からなる第 1 ゲート絶縁膜を形成し、前記第 1 ゲート絶縁膜上に第 1 導電膜、第 2 ゲート絶縁膜および第 2 導電膜をこの順に形成する工程、

( b ) 前記第 2 導電膜上に酸化シリコン膜の単層膜、または酸化シリコン膜上に窒化シリコン膜を形成した積層膜からなる第 1 保護絶縁膜を形成する工程、 40

( c ) 前記第 1 保護絶縁膜をパターニングすることにより、前記第 1 保護絶縁膜からなるエッチングマスクを形成する工程、

( d ) 前記エッチングマスクをマスクに用いたドライエッチングで前記第 2 導電膜、前記第 2 ゲート絶縁膜および前記第 1 導電膜をこの順にパターニングすることにより、前記第 1 導電膜からなるフローティングゲート電極と前記第 2 導電膜からなるコントロールゲート電極とを有し、前記コントロールゲート電極の上部が前記第 1 保護絶縁膜で覆われた積層構造のゲート電極を複数形成する工程、

( e ) 前記( c ) 工程の後、前記( d ) 工程に先立って、または前記( d ) 工程の後、パターニングされた前記第 1 保護絶縁膜の両側壁部に窒化シリコン膜からなるエッチング防 50

止膜を形成する工程、

(f) 前記(e)工程の後、フッ酸を含んだエッティング液を用いて前記半導体基板の表面を処理することにより、前記複数のゲート電極の互いに対向する側壁部間に位置する前記第1ゲート絶縁膜を洗浄する工程、

(g) 前記(f)工程の後、前記複数のゲート電極のそれぞれの上部および両側壁部を覆い、前記複数のゲート電極の互いに対向する側壁部間を埋め込まない程度の膜厚を有する窒化シリコン膜からなる第2保護絶縁膜を形成する工程、

(h) 前記第2保護絶縁膜の上部に酸化シリコン膜からなる層間絶縁膜を形成し、前記複数のゲート電極の互いに対向する側壁部間を前記層間絶縁膜で埋め込む工程、

(i) 前記複数のゲート電極の互いに対向する側壁部間に位置する前記層間絶縁膜および前記第2保護絶縁膜をエッティングすることにより、接続孔を形成する工程。 10

#### 【請求項11】

請求項10記載の半導体集積回路装置の製造方法において、前記複数のゲート電極のそれぞれは、フラッシュメモリのメモリセルを構成し、前記メモリセルの書き込みは、前記フローティングゲート電極に電荷を注入して行い、前記メモリセルの消去は、前記フローティングゲート電極に注入された前記電荷を前記半導体基板に放出して行うことを特徴とする半導体集積回路装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

20

本発明は、半導体集積回路装置およびその製造技術に関し、特に、電気的に一括消去・再書き込み可能な不揮発性半導体記憶装置(フラッシュメモリ)を含んだ半導体集積回路装置に適用して有効な技術に関する。

##### 【0002】

##### 【従来の技術】

半導体集積回路装置の製造プロセスでは、半導体基板上に堆積した酸化シリコン膜をエッティングしてコンタクトホールを形成する際、コンタクトホールの底部に露出した下層の酸化シリコン膜が過剰にエッティングされるのを防止する対策として、コンタクトホールを形成する上層の酸化シリコン膜と下層の酸化シリコン膜との間に窒化シリコン膜を設け、これをエッティングのストップとして利用することにより、上層の酸化シリコン膜のみをエッティングする技術が使用されている(例えば特開平11-26574号公報など)。 30

##### 【0003】

また、近年の大容量DRAM(Dynamic Random Access Memory)の製造プロセスでは、微細化されたゲート電極のスペースにピット線や容量素子と半導体基板とを接続するコンタクトホールを形成する際、ゲート電極の上部を覆う絶縁膜(キャップ絶縁膜または保護絶縁膜などと呼ばれる)と側壁を覆う絶縁膜(側壁絶縁膜)とを窒化シリコン膜で構成し、酸化シリコン膜と窒化シリコン膜とのエッティングレート差を利用して、上記コンタクトホールをゲート電極のスペースに対して自己整合的に形成するセルファーライン・コンタクト(Self Align Contact; SAC)技術が採用されている(例えば特開平9-252098号公報など)。 40

##### 【0004】

また近年は、DRAM以外の半導体記憶装置の製造プロセスにも上記SAC技術が採用されつつある。例えば特開平10-289951号公報には、EEPROM(Electrically Erasable Programmable Read Only Memory)の製造プロセスにSAC技術を適用した発明が開示されている。

##### 【0005】

##### 【発明が解決しようとする課題】

フラッシュメモリの一種にNOR型フラッシュメモリがある。NOR型フラッシュメモリのメモリセルは、ゲート酸化膜とその上部のコントロールゲート電極(ワード線)との間に設けられ、周囲と電気的に絶縁されたフローティング(浮遊)ゲート電極を電荷の蓄積

50

領域とする、いわゆるフローティングゲート型M I S F E T (Metal Insulator Semiconductor Field Effect Transistor) で構成される。フローティングゲート型M I S F E T は、半導体基板主表面に形成された薄いゲート絶縁膜を介して形成されたフローティングゲート電極の上部にコントロールゲート電極(ワード線)を積層することから、メモリセルサイズを比較的小さくすることができ、大容量化に適したメモリセル構造といえる。

#### 【 0 0 0 6 】

上記N O R型フラッシュメモリの場合、メモリセルへの書き込み動作の代表的な方法として、フローティングゲート電極中に電子を注入し、コントロールゲート電極から見たトランジスタのしきい値電圧( $V_{th}$ )を電子の蓄積のない状態に比較して上昇させることができ 10 われている。フローティングゲート電極への電子の注入は、代表的な例として、ソース・ドレイン通路に流れるチャネル電流をドレイン近傍でホットエレクトロンとすることによつて、正電圧にバイアスされたコントロールゲート電極の電界によりフローティングゲート電極へ引き込む方式があり、その他の例として、アバランシェ・ブレークダウンによって発生するドレイン近傍のホットエレクトロンをコントロールゲート電極に印加した正電圧によってフローティングゲート電極へ引き込む方式がある。一方、消去動作の代表的な例としては、フローティングゲート電極に蓄積された電子をフローティングゲート電極下のゲート絶縁膜にF Nトンネルリング(Fowler-Nordheim Tunneling)させることにより、半導体基板のソース或いはドレイン領域に放出させる方式が行われている。

#### 【 0 0 0 7 】

また、N O R型フラッシュメモリは、一方向に並行して延在する所定数のワード線と、これら 20 のワード線と直交する方向に並行して延在する所定数のデータ線との各交点に格子状にメモリセルを配置し、これらのメモリセルを構成するM I S F E Tのドレイン領域にデータ線を接続し、ソース領域にソース線を接続する。従って、N O R型フラッシュメモリを大容量化するためにメモリセルサイズを微細化した場合は、ドレイン領域にデータ線を接続するためのコンタクトホールや、ソース領域にソース線を接続するためのコンタクトホールを形成する際に前述したS A C技術が不可欠となる。

#### 【 0 0 0 8 】

しかし、S A C技術は、コントロールゲート電極の上部を保護する絶縁膜を窒化シリコン膜で形成するため、この技術をフラッシュメモリの製造プロセスに導入した場合は、コントロールゲート電極上の窒化シリコン膜がゲート酸化膜やその下部の基板に大きなストレスを及ぼし、ゲート酸化膜中に結晶欠陥を引き起こす結果、フローティングゲート電極に蓄積された電荷が基板にリークし易くなる、というフローティングゲート型M I S F E Tに特有の問題が生じることが本発明者らの検討によって明らかとなつた。 30

#### 【 0 0 0 9 】

そこで、本発明者らは、コントロールゲート電極上の保護絶縁膜を窒化シリコン膜に替えて酸化シリコン膜、または酸化シリコン膜と窒化シリコン膜との積層膜で形成し、側壁絶縁膜を窒化シリコン膜で形成することによって、ゲート酸化膜やその下部の基板へのストレスを抑制しつつ、S A C技術を利用してメモリセルの微細加工を実現することを検討した。

#### 【 0 0 1 0 】

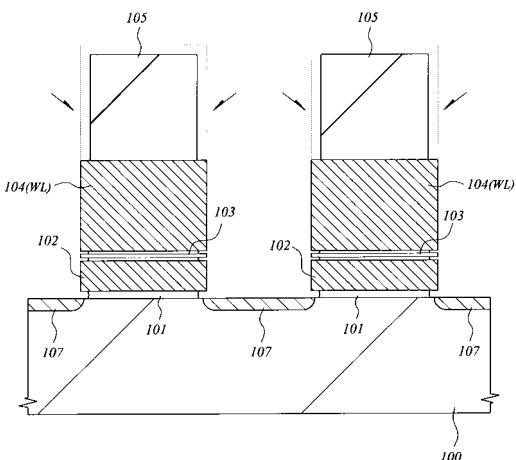

ところが、コントロールゲート電極上の保護絶縁膜を酸化シリコン膜で形成した場合は、M I S F E Tの製造工程で次のような問題が生じることが明らかとなつた。これを図45～図50を用いて説明する。

#### 【 0 0 1 1 】

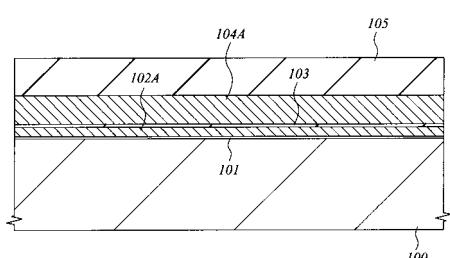

フローティングゲート電極とコントロールゲート電極とを有する2層ゲート構造のM I S F E Tを形成するには、まず図45に示すように、半導体基板100の主面に形成したゲート酸化膜101上にフローティングゲート用の多結晶シリコン膜102A、酸化シリコン膜、窒化シリコン膜および酸化シリコン膜からなるO N O膜103、コントロールゲート用の多結晶シリコン膜104A、保護絶縁膜である酸化シリコン膜105をこの順に堆積する。

10

20

30

40

50

**【0012】**

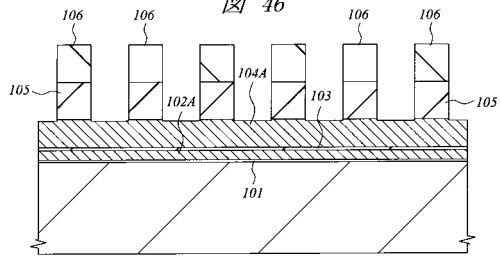

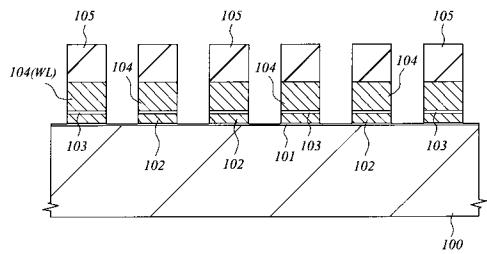

次に、図46に示すように、フォトレジスト膜106をマスクにして酸化シリコン膜105をドライエッチングする。続いてフォトレジスト膜106を除去した後、図47に示すように、酸化シリコン膜105をマスクにして下層の多結晶シリコン膜104A、ONO膜103および多結晶シリコン膜102Aを順次ドライエッチングすることにより、多結晶シリコン102Aからなるフローティングゲート電極102および多結晶シリコン膜104Aからなるコントロールゲート電極104(ワード線WL)を形成する。

**【0013】**

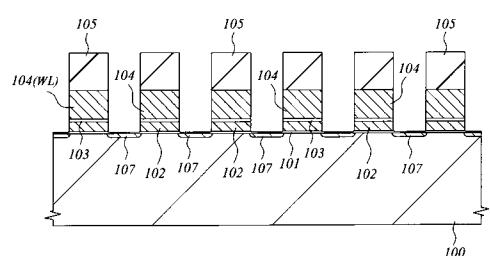

次に、図48に示すように、ゲート電極(フローティングゲート電極102およびコントロールゲート電極104)のスペース領域の半導体基板100に不純物をイオン注入し、

10 続いて半導体基板100を熱処理して上記不純物を拡散させることにより、MISFETのソース領域およびドレイン領域を構成する不純物導入領域107を形成する。

**【0014】**

次に、図49に示すように、上記ゲート電極の加工工程や不純物のイオン注入工程でゲート酸化膜101に生じたダメージを除去するために、フッ酸水溶液を使ってゲート酸化膜101をエッチング(ウェット洗浄)する。ゲート酸化膜101に生じたダメージは、フローティングゲート電極102に注入された電子がフローティングゲート電極102の端部から半導体基板100にリークするパスとなるなど、ゲート酸化膜101の膜質を劣化させる原因となるので、このエッチング(ウェット洗浄)で十分に除去しておく必要がある。

20

**【0015】**

ところが、フッ酸水溶液を使ってゲート酸化膜101を洗浄すると、コントロールゲート電極104の上部を覆う保護絶縁膜である酸化シリコン膜105の表面も同時にエッティングされ、図示したように、酸化シリコン膜105の側壁がゲート電極の中心方向に後退する。

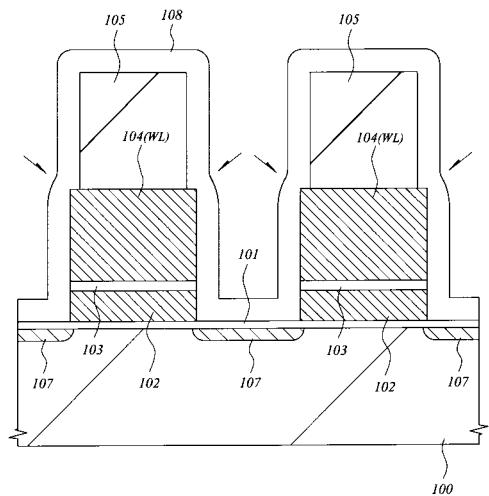

**【0016】**

そのため、図50に示すように、次の工程で半導体基板100上に側壁絶縁膜である窒化シリコン膜108を堆積した際に、コントロールゲート電極104と酸化シリコン膜105との境界部近傍の窒化シリコン膜108に段差が発生する。その結果、SAC技術を使ってゲート電極(フローティングゲート電極102およびコントロールゲート電極104)

30 のスペース領域にコンタクトホールを形成する際、上記段差部の窒化シリコン膜108が削れてその膜厚が薄くなるために、その後、コンタクトホールに埋め込まれるメタル膜とコントロールゲート電極104とが上記段差部近傍で極めて接近し、場合によっては両者が短絡する不良が発生する。なお、このような問題は、コントロールゲート電極104の上部を覆う保護絶縁膜を酸化シリコン膜と窒化シリコン膜との積層膜で形成した場合にも生じる。

**【0017】**

このように、窒化シリコン膜に起因するゲート酸化膜やその下部の基板へのストレスを抑制するために、コントロールゲート電極の上部を覆う保護絶縁膜の一部または全部を酸化シリコン膜で形成した場合は、SAC技術を利用したMISFETの微細加工を実現することが極めて困難になることが本発明者らの検討によって明らかとなった。

40

**【0018】**

本発明の目的は、窒化シリコン膜によるゲート酸化膜やその下部の基板へのストレスを抑制しつつ、SAC技術を利用したMISFETの微細加工を実現することのできる技術を提供することにある。

**【0019】**

本発明の他の目的は、フラッシュメモリの大容量化、微細化を推進することのできる技術を提供することにある。

**【0020】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から

50

明らかになるであろう。

【0021】

【課題を解決するための手段】

本願において開示される発明のうち、代表的な実施態様について説明すれば、次のとおりである。

【0022】

本発明の一つの態様によれば、半導体基板の主面上に互いに隣接して形成され、それぞれが第1ゲート絶縁膜と、フローティングゲート電極と、第2ゲート絶縁膜と、コントロールゲート電極と、第1保護絶縁膜とからなり、それらの順で積層された少なくとも一対の積層構造体によって少なくとも二辺が区画される接続孔（コンタクトホール）を含む半導体集積回路装置を対象とし、上記第1保護絶縁膜の両側壁部にはエッティング防止膜を有している。このエッティング防止膜は、上記第1保護絶縁膜とともに前記第1ゲート絶縁膜のエッティング工程に曝されたとき、第1保護絶縁膜に比べ、エッティングしにくいもの、すなわち、エッティング選択比が異なるものであり、或いは実質的にエッティングされないものである。好ましい態様において、上記第1保護絶縁膜は酸化シリコン膜を含み、その側壁部に形成される上記エッティング防止膜は窒化シリコン膜である。10

【0023】

SAC技術により、一対の上記積層構造体間に存在する酸化シリコン膜のような層間絶縁膜に接続孔を形成する場合、まず、サイドスペーサ用の薄い窒化シリコン膜を積層構造体表面全体に沿って形成し、その上面に積層構造体間の溝を埋めるように層間絶縁膜を形成する。そして、この酸化シリコン膜のような層間絶縁膜に対し、エッティングされにくい下地のサイドスペーサ用絶縁膜である窒化シリコン膜をエッティングの停止層（ストッパー）として使用して、上記層間絶縁膜をエッティング除去する。この場合、上記第1保護絶縁膜を覆うサイドスペーサ用窒化シリコン膜にエッティング停止層として充分な厚さを確保できないとき、上記層間絶縁膜の接続孔形成のために必要なエッティング量に耐え得るように、第1保護絶縁膜は酸化シリコン膜の上層に窒化シリコン膜を積層した多層膜としても良い。これによって、上記第1保護絶縁膜の窒化シリコン膜をエッティング停止層の一部として使用できる。上記態様によれば、コントロールゲート電極に積層される半導体基板にストレスを与える窒化シリコン材料のような保護絶縁膜材料の使用を省略または低減できる。20

【0024】

本発明の他の態様によれば、半導体基板主面にMISトランジスタ構造を含む半導体集積回路装置の製造方法を対象とし、半導体基板の主面の活性領域を覆って形成された第1ゲート絶縁膜を形成する工程と、フローティングゲート電極と、第2ゲート絶縁膜と、コントロールゲート電極と、第1保護絶縁膜とからなり、それらの順で積層された少なくとも一対の積層構造体に形成する工程と、前記一対の積層構造体間に露出する前記第1ゲート絶縁膜を通してソースまたはドレインを形成するための不純物を導入する工程と、上記不純物導入工程によってダメージを受けた前記第1ゲート絶縁膜の露出部分を除去或いは洗浄する工程とを含み、前記除去または洗浄工程において上記第1保護絶縁膜の側壁部が後退しないように、上記積層構造体の形成工程において、上記第1保護絶縁膜の側壁部にエッティング防止膜を形成することを特徴とする。好ましい態様において、上記第1保護絶縁膜は酸化シリコン膜を含み、上記と同様な理由により、酸化シリコン膜と窒化シリコン膜の多層膜にても良い。一方、第1保護絶縁膜の側壁部を覆う上記エッティング保護膜は窒化シリコン膜である。これによって、コントロールゲート電極に積層される半導体基板にストレスを与える窒化シリコン材料のような保護絶縁膜材料の使用を省略または低減できる。また、上記第1ゲート絶縁膜の露出部分を除去或いは洗浄する工程において、フローティングゲート電極下から露出する第1ゲート絶縁膜の除去或いは洗浄を、通常のMISトランジスタの製造工程において行われる洗浄に比べ、十分な除去或いは洗浄とすることができます。従って、特に、第1ゲート絶縁膜のダメージ部分を除去することができるので、フラッシュメモリの書き込み情報の保持特性を良好なものとすることができます。40

【0025】

50

本発明のさらに他の態様によれば、フラッシュメモリのMISトランジスタ構造を含む次の工程を含む半導体集積回路装置の製造方法に向けられている。すなわち、

(a) 半導体基板の正面に酸化シリコン膜からなる第1ゲート絶縁膜を形成し、前記第1ゲート絶縁膜上に第1導電膜、第2ゲート絶縁膜および第2導電膜をこの順に形成する工程、

(b) 前記第2導電膜上に酸化シリコン膜の単層膜、または酸化シリコン膜上に窒化シリコン膜を形成した積層膜からなる第1保護絶縁膜を形成する工程、

(c) 前記第1保護絶縁膜をパターニングすることにより、前記第1保護絶縁膜からなるエッチングマスクを形成する工程、

(d) 前記エッチングマスクをマスクに用いたドライエッチングで前記第2導電膜、前記第2ゲート絶縁膜および前記第1導電膜をこの順にパターニングすることにより、前記第1導電膜からなるフローティングゲート電極と前記第2導電膜からなるコントロールゲート電極とを有し、前記コントロールゲート電極の上部が前記第1保護絶縁膜で覆われた積層構造のゲート電極を複数形成する工程、

(e) 前記(c)工程の後、前記(d)工程に先立って、または前記(d)工程の後、パターニングされた前記第1保護絶縁膜の両側壁部に窒化シリコン膜からなるエッチング防止膜を形成する工程、

(f) 前記複数のゲート電極の互いに対向する側壁部間に位置する前記半導体基板の正面に不純物を導入することによって、ソース領域およびドレイン領域を形成する工程、

(g) 前記(f)工程の後、フッ酸を含んだエッチング液を用いて前記半導体基板の表面を処理することにより、前記複数のゲート電極の互いに対向する側壁部間に位置する前記第1ゲート絶縁膜を洗浄する工程、

(h) 前記(g)工程の後、前記複数のゲート電極のそれぞれの上部および両側壁部を覆い、前記複数のゲート電極の互いに対向する側壁部間を埋め込まない程度の膜厚を有する窒化シリコン膜からなる第2保護絶縁膜を形成する工程、

(i) 前記第2保護絶縁膜の上部に酸化シリコン膜からなる層間絶縁膜を形成し、前記複数のゲート電極の互いに対向する側壁部間を前記層間絶縁膜で埋め込む工程、

(j) 前記複数のゲート電極の互いに対向する側壁部間に位置する前記層間絶縁膜および前記第2保護絶縁膜をエッチングすることにより、前記ソース領域の表面を露出する第1接続孔および前記ドレイン領域の表面を露出する第2接続孔を形成する工程、および

(k) 前記第1接続孔の内部に、前記ソース領域と電気的に接続される第3導電膜を形成し、前記第2接続孔の内部に、前記ドレイン領域と電気的に接続される第4導電膜を形成する工程

を含む。このような形態によれば、コントロールゲート電極の上部を覆う第1保護絶縁膜を酸化シリコン膜で構成することにより、第1ゲート酸化膜やその下部の半導体基板に及ぼすストレスが低減され、第1ゲート酸化膜中に結晶欠陥が発生するのを抑制することができる。

#### 【0026】

また、上記酸化シリコン膜からなる第1保護絶縁膜の両側壁部に窒化シリコン膜からなるエッチング防止膜を形成することにより、フッ酸を含んだエッチング液で第1ゲート絶縁膜を洗浄する際に第1保護絶縁膜がエッチングされて後退する不具合を防止することができる。

#### 【0027】

さらに、第1保護絶縁膜の後退が防止され、従って、上記第2保護絶縁膜である窒化シリコン膜の異方性エッチング処理時における該第2保護絶縁膜の側壁部の不要なエッチング除去も防止される。これによって、図50を参照した上述のような、ドレイン領域或いはソース領域にコンタクトする導電膜とコントロールゲート電極との間の耐圧低下の問題、或いはそれら導体間短絡の問題を防止することができる。

#### 【0028】

#### 【発明の実施の形態】

10

20

30

40

50

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

#### 【0029】

##### (実施の形態1)

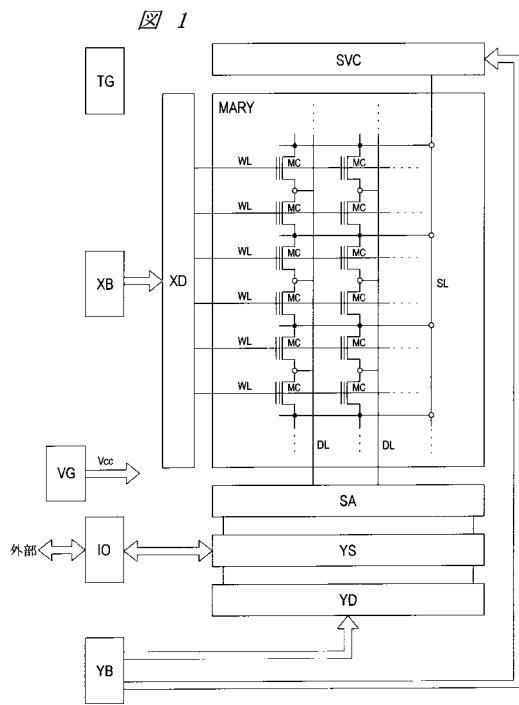

図1は、本発明の一実施の形態であるフラッシュメモリ(電気的に一括消去・再書き込み可能な不揮発性半導体記憶装置)の主要部を示すブロック図である。

#### 【0030】

フラッシュメモリは、単結晶シリコンからなる1個の半導体チップの正面に形成されており、記憶部を構成するメモリアレイ(MARY)とその周囲に配置された周辺回路部とを有している。10

#### 【0031】

メモリアレイ(MARY)は、図の左右方向に並行して延在する所定数のワード線WLと、図の上下方向に並行して延在する所定数のデータ線DLと、これらのワード線WLおよびデータ線DLの各交点に格子状に配置された多数のメモリセルMCを含んでいる。メモリセルMCは、フローティングゲート電極とコントロールゲート電極とを有する2層ゲート構造のMISFETで構成されている。このMISFETの構造および製造方法については、後に詳述する。

#### 【0032】

本実施形態のフラッシュメモリは、例えばNOR型のメモリアレイ構造を採用している。20

NOR型のフラッシュメモリは、同一行に配置される所定数(例えば16個)のメモリセルMCを単位としてセルユニットを構成する。セルユニットを構成する各メモリセルMCのコントロールゲート電極は、対応するワード線WLに接続される。また、各メモリセルMCのドレイン領域は、対応するデータ線DLに接続され、ソース領域は、図の上下方向に延在するソース線SLに接続される。

#### 【0033】

上記ワード線WLは、XアドレスデコーダXDに接続され、ソース線SLは、ソース電圧制御回路SVCに接続される。また、データ線DLは、センスアンプSAおよびYスイッチ回路YSを介して入出力回路IOに接続される。

#### 【0034】

XアドレスデコーダXDには、XアドレスバッファXBから内部Xアドレス信号が供給されると共に、タイミング発生回路TGから各種内部制御信号が供給され、内部電圧発生回路VGから各種内部電圧が供給される。また、ソース電圧制御回路SVCには、YアドレスバッファYBから内部Yアドレス信号が供給されると共に、タイミング発生回路TGから各種内部制御信号が供給され、内部電圧発生回路VGから各種内部電圧が供給される。さらに、Yスイッチ回路YSには、YアドレスデコーダYDからデータ線選択信号が供給され、YアドレスデコーダYDには、YアドレスバッファYBから内部Yアドレス信号が供給される。XアドレスバッファXBには、外部装置からXアドレス信号が供給され、YアドレスバッファYBには、Yアドレス信号が供給される。30

#### 【0035】

XアドレスバッファXBは、供給されたXアドレス信号をもとに内部Xアドレス信号を形成し、これをXアドレスデコーダXDに供給する。また、XアドレスデコーダXDは、XアドレスバッファXBから供給される内部Xアドレス信号をデコードし、メモリアレイ(MARY)のワード線WLを選択または非選択レベルとする。40

#### 【0036】

一方、YアドレスバッファYBは、供給されたYアドレス信号をもとに内部Yアドレス信号を形成し、これをソース電圧制御回路SVCおよびYアドレスデコーダYDに供給する。また、ソース電圧制御回路SVCは、YアドレスバッファYBから供給される内部Yアドレス信号をデコードし、メモリアレイ(MARY)のソース線SLを選択または非選択レベルとする。YアドレスデコーダYDは、YアドレスバッファYBから供給される内部50

Yアドレス信号をデコードし、Yスイッチ回路YSに対するデータ線選択信号を選択レベルとする。さらに、Yスイッチ回路YSは、YアドレスデコーダYDから供給されるデータ線選択信号のハイレベルを受けてセンスアンプSAの対応する回路と入出力回路IOとの間を選択的に接続する。

#### 【0037】

タイミング発生回路TGは、外部装置から起動制御信号として供給されるチップイネーブル信号(CEB)、ライトイネーブル信号(WEB)および出力イネーブル信号(OEB)をもとに各種内部制御信号を選択的に形成し、フラッシュメモリの各部に供給する。また、内部電圧発生回路VGは、外部装置から供給される電源電圧(VccおよびVss)をもとに各種内部電圧を生成し、フラッシュメモリの各部に供給する。電源電圧Vccは、例えば3.3Vのような正電位である。また、内部電圧発生回路VGにより生成される内部電圧には、書き込み、消去あるいは読み出し動作に必要な、例えば10V、3Vあるいは1Vといった各種電位が含まれる。10

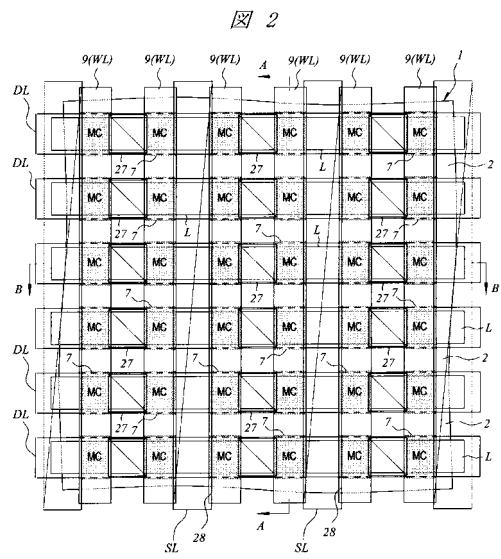

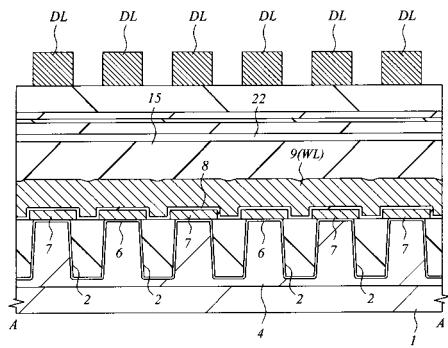

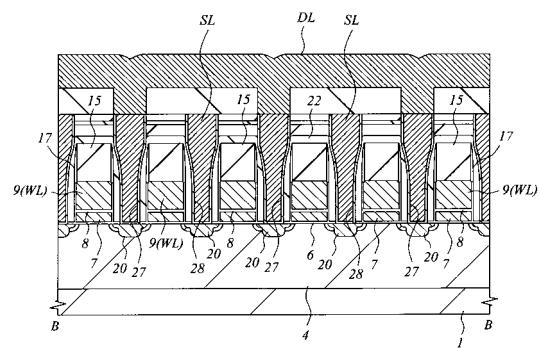

#### 【0038】

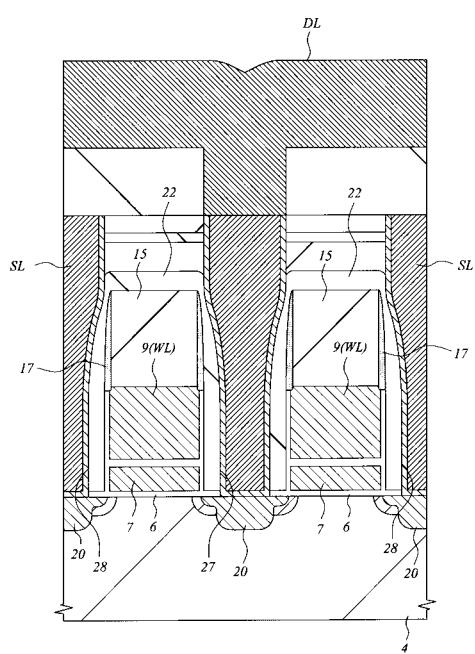

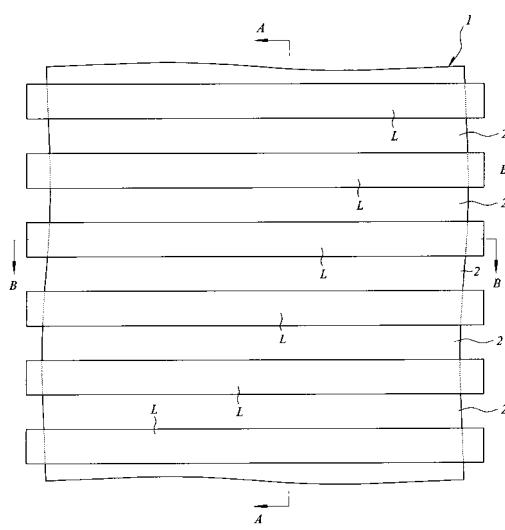

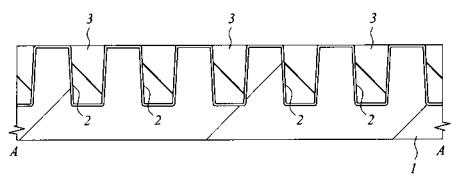

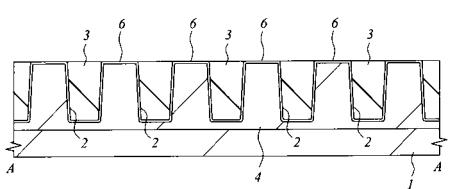

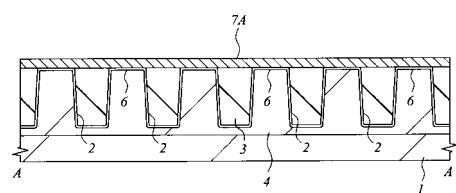

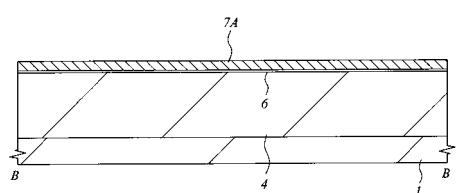

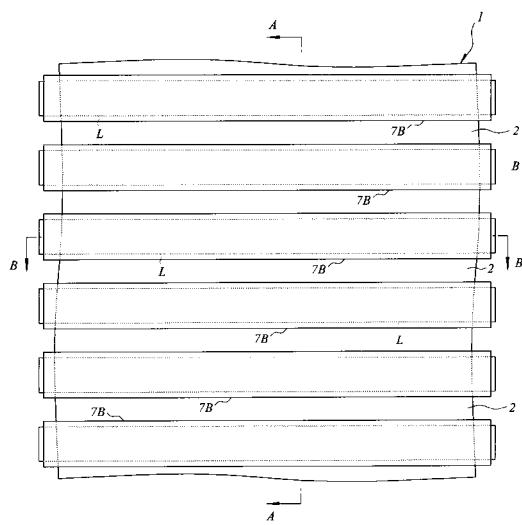

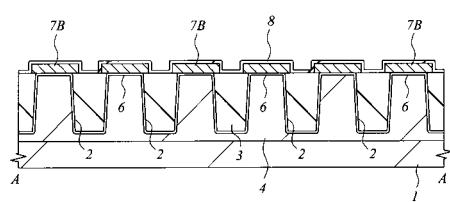

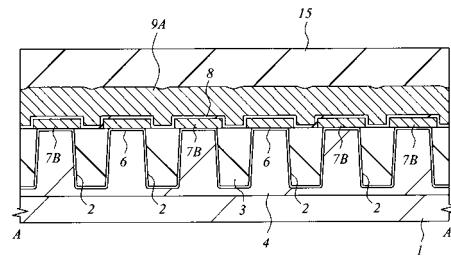

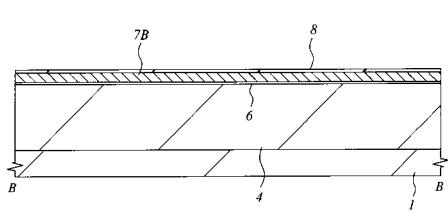

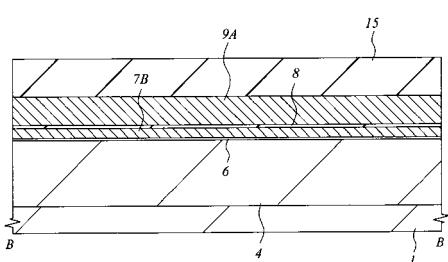

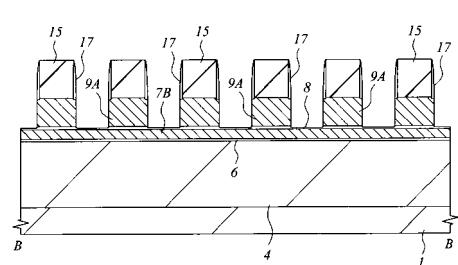

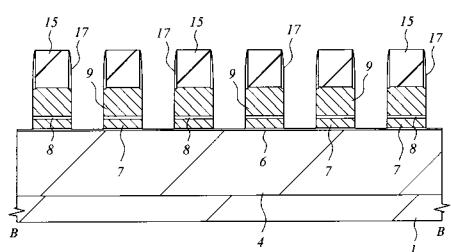

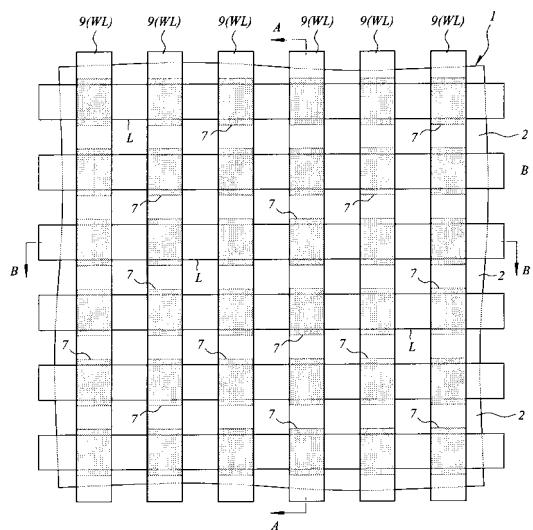

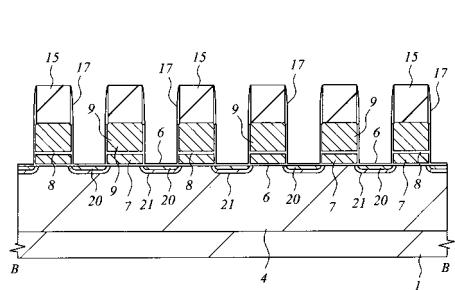

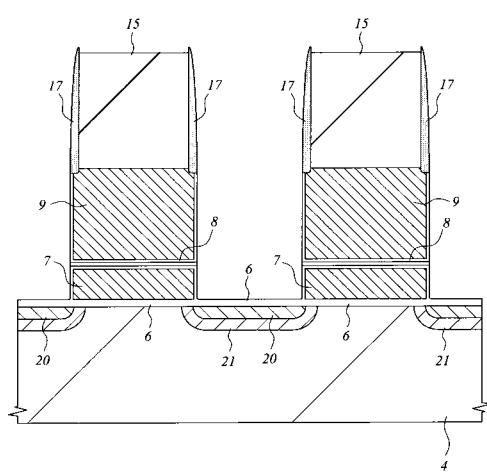

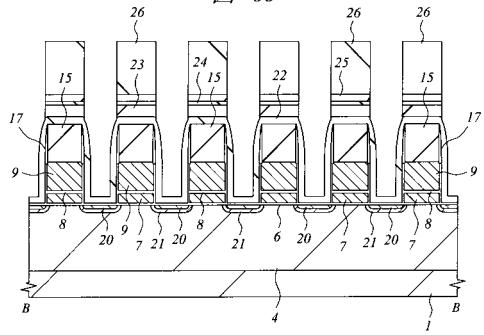

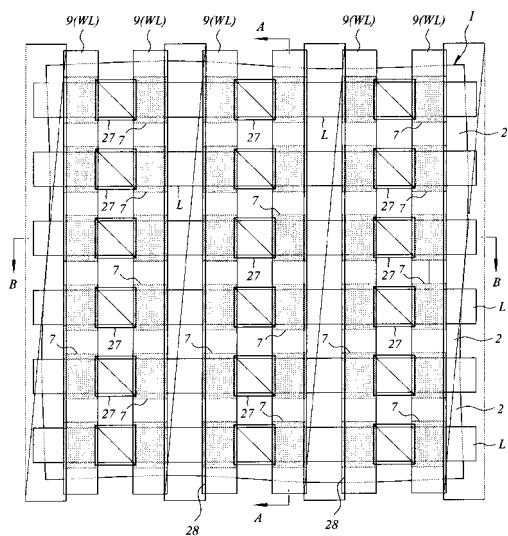

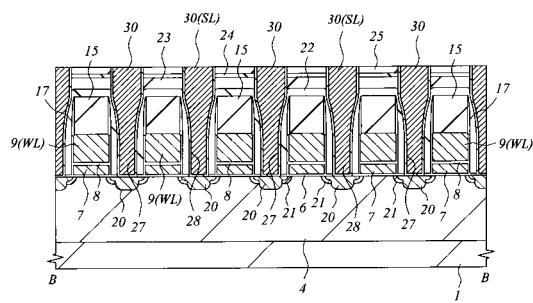

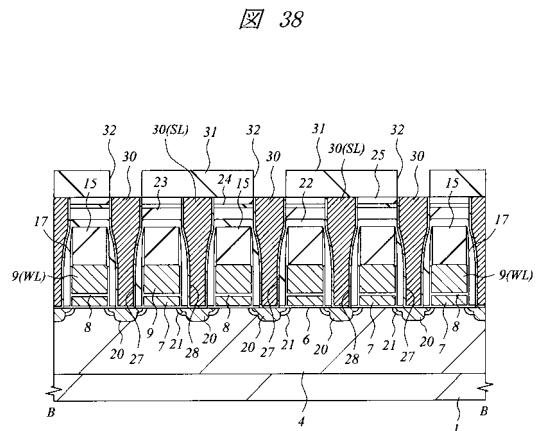

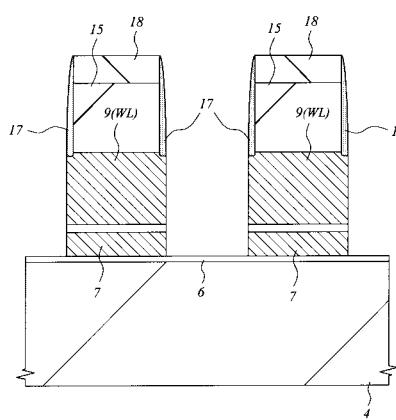

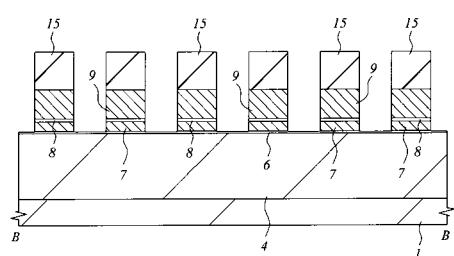

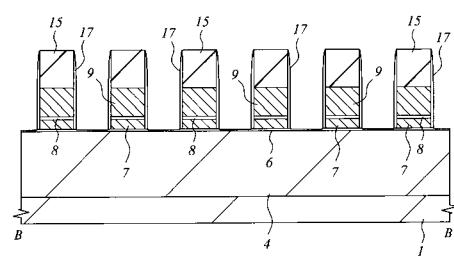

図2は、上記メモリアレイ(MARY)の要部平面図、図3は、図2のA-A線に沿った断面図、図4は、図2のB-B線に沿った断面図、図5は、図4の拡大断面図である。

#### 【0039】

p型の単結晶シリコンからなる半導体基板(以下、基板という)1にはp型ウエル4が形成されている。このp型ウエル4には、周囲が素子分離溝2で囲まれた多数の活性領域Lが形成されている。これらの活性領域Lは、図2の左右方向に並行して延在する長い帯状の平面パターンを有している。20

#### 【0040】

メモリアレイ(MARY)の基板1上には、図2の左右方向に並行して延在する多数のワード線WLと、図2の上下方向、すなわちワード線WLと直交する方向に並行して延在する多数のデータ線DLとが形成され、これらのワード線WLとデータ線DLとの交点に多数のメモリセルMCが格子状に配置されている。

#### 【0041】

上記メモリセルMCを構成するMISFETは、p型ウエル4の表面に形成されたゲート酸化膜(第1ゲート絶縁膜)6と、ゲート酸化膜6上に形成されたフローティングゲート電極7と、フローティングゲート電極7上に形成されたONO膜(第2ゲート絶縁膜)8と、ONO膜8上に形成されたコントロールゲート電極9と、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)の両側のp型ウエル4に形成されたn型不純物導入領域(ソース領域、ドレイン領域)20とを含んでいる。30

#### 【0042】

上記MISFETのコントロールゲート電極9は、活性領域L以外の領域ではワード線WLを構成している。また、MISFETのn型不純物導入領域20の一方(ドレイン領域)には、その上部に形成されたコンタクトホール(接続孔)27を通じてデータ線DLが接続され、他方(ソース領域)には、その上部に形成されたコンタクトホール(接続孔)28を通じてソース線SLが接続されている。

#### 【0043】

図5に示すように、メモリセルMCを構成するMISFETのコントロールゲート電極9(ワード線WL)上には、酸化シリコン膜(第1保護絶縁膜)15が形成されており、この酸化シリコン膜15の側壁には窒化シリコン膜からなるエッティング防止膜17が形成されている。このエッティング防止膜17の機能については後述する。また、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)の側壁および酸化シリコン膜15の上面には、窒化シリコン膜(第2保護絶縁膜)22が形成されている。この窒化シリコン膜22は、後述するように、前記コンタクトホール27、28をゲート電極(フローティングゲート電極7およびコントロールゲート電極9)に対して自己整合(セルフアライン)で形成するために使用される。

#### 【0044】

50

メモリセルMCへの書き込み動作は、選択したメモリセルMCのドレイン領域に6Vの電圧、コントロールゲート電極9に9Vの電圧をそれぞれ印加し、一方、ソース領域およびウエル4を基準電位（ゼロ電位）とする。これにより、ドレイン領域の端部に電界強度のピークが生じ、チャネル電流がこの領域でホットエレクトロン（e-）となって、ゲート酸化膜6を通じてフローティングゲート電極7に注入されることにより、書き込みが行われる。

#### 【0045】

また、読み出し動作は、選択したメモリセルMCのドレイン領域に1Vの電圧を、コントロールゲート電極9に5Vの電圧をそれぞれ印加し、ソース領域およびウエル4を基準電位（ゼロ電位）にする。これにより、選択トランジスタのドレイン電流の有無を検出することにより、蓄積情報を検知する。一方、消去動作は、メモリセルMCのドレイン領域およびウエル領域をフローティング状態とし、コントロールゲート電極9に0Vの電圧、ソース領域に14Vの電圧を印加し、フローティングゲート電極7中に蓄積された電子を、ゲート酸化膜6のFNトンネリングによって、ソース領域側へ放出することにより行う。

10

#### 【0046】

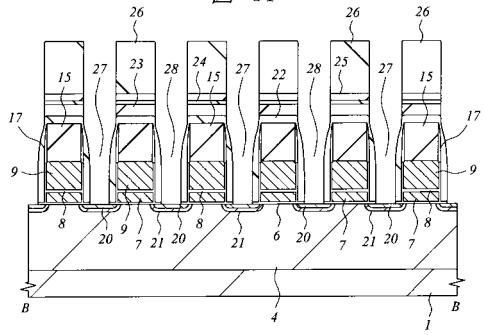

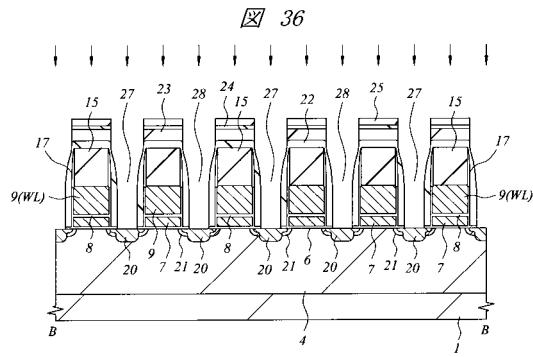

次に、本実施形態のフラッシュメモリの製造方法を図6～図38を用いて工程順に説明する。これらの図のうち、符号A-Aを付した断面図は、前記図2のA-A線に沿った断面図、符号B-Bを付した断面図は、前記図2のB-B線に沿った断面図である。

#### 【0047】

まず、図6（メモリアレイ領域の要部平面図）および図7に示すように、基板1の主面の素子分離領域に複数の素子分離溝2を形成する。素子分離溝2は、基板1の主面をエッチングして深さ250nm程度の溝を形成し、続いてこの溝の内部を含む基板1上にCVD法で膜厚600nm程度酸化シリコン膜3を堆積した後、溝の外部の不要な酸化シリコン膜3を化学機械研磨(Chemical Mechanical Polishing; CMP)法で研磨、除去することによって形成する。図6に示すように、これらの素子分離溝2を形成することにより、メモリアレイ領域の基板1には、図の左右方向に並行して延在する長い帯状の平面パターンを有する多数の活性領域Lが形成される。

20

#### 【0048】

次に、図8に示すように、基板1の表面にp型不純物、例えばB（ホウ素）をイオン注入した後、基板1を1000°C程度で熱処理してp型不純物を基板1内に拡散することにより、p型ウエル4を形成する。続いて、基板1を800°C～900°Cで湿式酸化することにより、p型ウエル4の表面に膜厚10nm程度のゲート酸化膜6を形成する。

30

#### 【0049】

次に、図9および図10に示すように、基板1上にCVD法で膜厚70nm～100nm程度の多結晶シリコン膜7Aを堆積する。多結晶シリコン膜7Aには、その堆積工程中にn型不純物、例えばリン（P）をドープする。あるいは、ノンドープの多結晶シリコン膜7Aを堆積した後にイオン注入法でn型不純物をドープしてもよい。多結晶シリコン膜7Aは、メモリセルを構成するMISFETのフローティングゲート電極7として使用される。

#### 【0050】

40

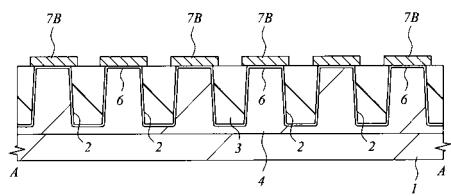

次に、図11、図12および図13に示すように、フォトレジスト膜をマスクにして多結晶シリコン膜7Aをドライエッティングすることにより、活性領域Lの上部に、その延在方向に沿って延在する長い帯状の平面パターンを有する多結晶シリコン膜7Bを形成する。

#### 【0051】

次に、図14および図15に示すように、多結晶シリコン膜7Bが形成された基板1上に酸化シリコン膜、窒化シリコン膜および酸化シリコン膜からなるONO膜8を形成する。ONO膜8は、メモリセルを構成するMISFETの第2ゲート絶縁膜として使用され、例えば基板1上にCVD法で膜厚5nmの酸化シリコン膜、膜厚7nmの窒化シリコン膜および膜厚4nmの酸化シリコン膜を順次堆積することによって形成する。

#### 【0052】

50

次に、図16および図17に示すように、ONO膜8の上部に膜厚200nm程度の多結晶シリコン膜9Aを形成し、続いて多結晶シリコン膜9Aの上部に膜厚300nm程度の酸化シリコン膜15を形成する。多結晶シリコン膜9Aは、CVD法で堆積し、その後、イオン注入法で膜中にn型不純物をドープする。酸化シリコン膜15は、例えばテトラエトキシシランガスを700°C程度で熱分解する熱CVD法で堆積する。多結晶シリコン膜9Aは、メモリセルを構成するMISFETのコントロールゲート電極9およびワード線WLとして使用される。また、酸化シリコン膜15は、コントロールゲート電極9の上部を保護する絶縁膜として使用される。

#### 【0053】

このように、本実施形態では、コントロールゲート電極9の上部を保護する絶縁膜を酸化シリコン膜15で構成するので、この絶縁膜を窒化シリコン膜で構成した場合のように、ゲート酸化膜6やその下部の基板1に大きなストレスが生じることはない。これにより、ゲート酸化膜6中に結晶欠陥が発生するのを抑制することができるので、リーク電流が極めて少ない高品質のゲート酸化膜6を実現することができる。

#### 【0054】

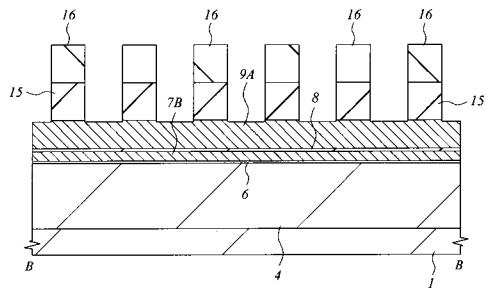

次に、図18に示すように、フォトレジスト膜16をマスクにして酸化シリコン膜15をドライエッチングすることにより、多結晶シリコン膜9Aの一部を露出させる。ドライエッチング後の酸化シリコン膜15は、活性領域Lの延在方向と直交する方向に延在する長い帯状の平面パターンを有している。

#### 【0055】

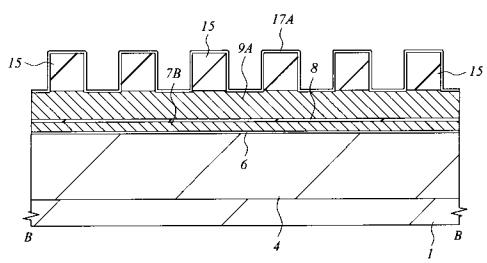

次に、フォトレジスト膜16を除去した後、図19に示すように、基板1上にCVD法で膜厚15nm~30nm程度の薄い窒化シリコン膜17Aを堆積し、続いて図20に示すように、上記窒化シリコン膜17Aを異方的にドライエッチングして酸化シリコン膜15の側壁のみに残すことにより、この側壁に窒化シリコン膜17Aからなるエッチング防止膜17を形成する。

#### 【0056】

次に、図21に示すように、側壁にエッチング防止膜17が形成された酸化シリコン膜15をマスクにして多結晶シリコン膜9Aをドライエッチングし、さらに図22に示すように、多結晶シリコン膜9Aの下層のONO膜8および多結晶シリコン膜7Bを順次ドライエッチングすることにより、多結晶シリコン7Bからなるフローティングゲート電極7および多結晶シリコン膜9Aからなるコントロールゲート電極9(ワード線WL)を形成する。図23に示すように、コントロールゲート電極9(ワード線WL)は、活性領域Lの延在方向と直交する方向(図の上下方向)に並行して延在する長い帯状の平面パターンを有している。

#### 【0057】

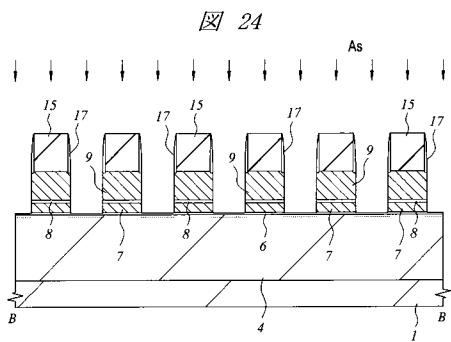

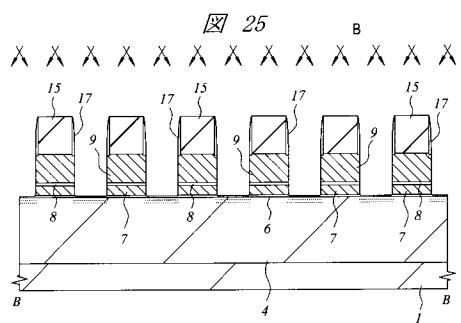

次に、図24に示すように、メモリセルを構成するMISFETのソース領域およびドレイン領域を形成するために、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)のスペース領域のp型ウエル4にn型不純物(例えばヒ素(Ass))をイオン注入する。続いて、図25に示すように、メモリセルを構成するMISFETの短チャネル効果を抑制するために、上記スペース領域のp型ウエル4にp型不純物(ホウ素(B))をイオン注入する。p型不純物のイオン注入は、斜めイオン注入法を用い、n型不純物よりも広い領域に導入する。

#### 【0058】

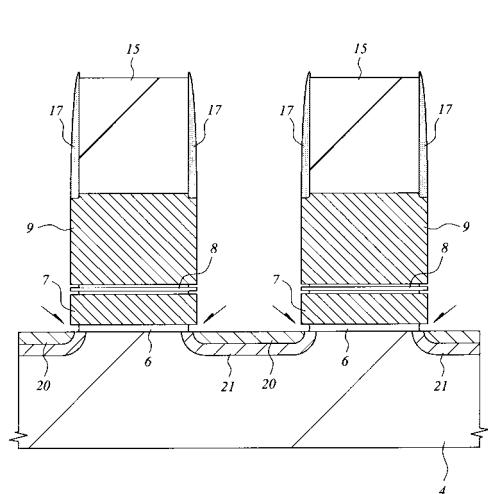

次に、図26に示すように、基板1を約900°Cで熱処理し、上記n型不純物およびp型不純物をp型ウエル4内に拡散させることにより、MISFETのソース領域およびドレイン領域を構成するn型不純物導入領域20と、n型不純物導入領域20を取り囲むパンチスルーストップ用のp型不純物導入領域21とを形成する。

#### 【0059】

ここまで工程で、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)のスペース領域のゲート酸化膜6には、ゲート電極の加工工程や不純物のイオン

10

20

30

40

50

注入工程で生じたダメージが残っている。このダメージは、フローティングゲート電極7に注入された電子がフローティングゲート電極7の端部から基板1にリークするパスとなるなど、ゲート酸化膜6の品質を劣化させるため、十分に除去しておく必要がある。

#### 【0060】

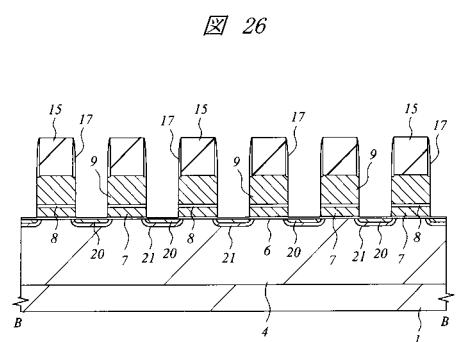

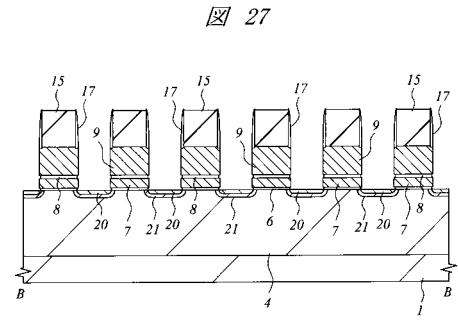

そこで、図27に示すように、フッ酸水溶液(HF:H<sub>2</sub>O=1:99)を使ってゲート酸化膜6をエッチングする。ゲート酸化膜6中のダメージを十分に除去するためには、図28に拡大して示すように、フローティングゲート電極7の側壁端部下のゲート酸化膜6(矢印で示す箇所)が、少なくともその膜厚分程度、後退するまでエッチングすることが望ましい。

#### 【0061】

前述したように、本実施形態では、コントロールゲート電極9の上部を保護する酸化シリコン膜15の側壁に窒化シリコン膜からなるエッチング防止膜17を形成する。そのため、上記したゲート酸化膜6中のダメージを除去するためのエッチング工程で酸化シリコン膜15の側壁がエッチングされ、ゲート電極の中心方向に後退することはない。

#### 【0062】

次に、図29および図30(図29の拡大図)に示すように、基板1を約850で湿式酸化することによって、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)のスペース領域すなわちn型不純物導入領域(ソース領域、ドレイン領域)20の表面と、フローティングゲート電極7の側壁端部下とに膜厚10nm程度の清浄で、ダメージのない高品質のゲート酸化膜6を再形成する。

#### 【0063】

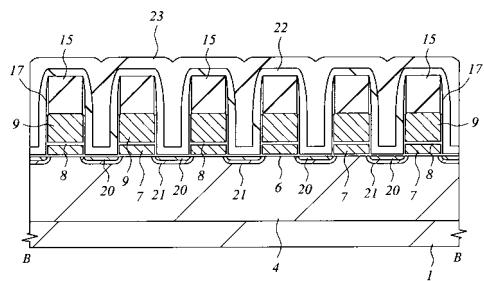

次に、図31に示すように、基板1上にCVD法で膜厚130nm程度の窒化シリコン膜22を堆積し、続いてその上部にCVD法で膜厚200nm程度の酸化シリコン膜23を堆積する。窒化シリコン膜22の膜厚は、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)のスペースの半分以下とし、このスペース領域が窒化シリコン膜22で完全に埋まらないようとする。一方、酸化シリコン膜23は、このスペース領域を完全に埋め込むように堆積する。

#### 【0064】

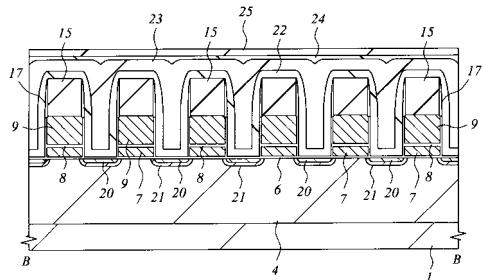

次に、図32に示すように、酸化シリコン膜23の上部にCVD法で膜厚800nm程度の酸化シリコン膜24を堆積し、続いて酸化シリコン膜24を化学機械研磨法で研磨してその表面を平坦化した後、酸化シリコン膜24の上部にCVD法で膜厚90nm程度の酸化シリコン膜25を堆積する。酸化シリコン膜24の研磨、平坦化は、メモリアレイと他の領域(周辺回路部)の段差を低減するために行う。また、酸化シリコン膜25は、上記研磨工程で酸化シリコン膜24の表面に生じたスクラッチを埋めるために堆積する。

#### 【0065】

次に、図33に示すように、酸化シリコン膜25の上部に形成したフォトマスクとして、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)のスペース領域の酸化シリコン膜25、24、23をドライエッチングする。このエッチングは、窒化シリコンに対する酸化シリコンのエッチング選択比が大きくなるような条件で行い、窒化シリコン膜22の表面が露出した段階でエッチングを停止する。

#### 【0066】

次に、図34に示すように、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)のスペース領域の窒化シリコン膜22およびその下層の薄いゲート酸化膜6をドライエッチングすることにより、n型不純物導入領域(ソース領域、ドレイン領域)20の表面を露出するコンタクトホール27、28を形成する。窒化シリコン膜22のエッチングは、異方性エッチング法を用い、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)の側壁に窒化シリコン膜22を残すようにする。これにより、ゲート電極(フローティングゲート電極7およびコントロールゲート電極9)に対して自己整合(セルフアライン)でコンタクトホール27、28を形成することができる。

10

20

30

40

50

**【 0 0 6 7 】**

図35は、コンタクトホール27、28の平面パターンを示している。図示のように、n型不純物導入領域（ソース領域、ドレイン領域）20の一方（ドレイン領域）の上部に形成されるコンタクトホール27は、活性領域L毎に分離された穴状のパターンを有している。すなわち、コンタクトホール27は、活性領域Lの延在方向に隣接する2個のMISFET（メモリセルMC）に1個の割合で形成される。

**【 0 0 6 8 】**

これに対し、n型不純物導入領域（ソース領域、ドレイン領域）20の他方（ソース領域）の上部に形成されるコンタクトホール28は、コントロールゲート電極9（ワード線WL）の延在方向に沿って延在する長い帯状の平面パターンを有している。すなわち、コンタクトホール28は、コントロールゲート電極9（ワード線WL）の延在方向に沿った多数のMISFET（メモリセルMC）に共通のコンタクトホールとなる。

**【 0 0 6 9 】**

次に、図36に示すように、コンタクトホール27、28を通じてn型不純物導入領域（ソース領域、ドレイン領域）20にn型不純物（PまたはAs）をイオン注入することによって、n型不純物導入領域（ソース領域、ドレイン領域）20を低抵抗化する。このイオン注入は、後の工程でコンタクトホール27、28の内部に形成されるプラグ30とn型不純物導入領域（ソース領域、ドレイン領域）20とのコンタクト抵抗を低減するために行う。

**【 0 0 7 0 】**

次に、図37に示すように、コンタクトホール27、28の内部にプラグ30を形成する。プラグ30を形成するには、例えばコンタクトホール27、28の内部を含む酸化シリコン膜25上にスパッタリング法で膜厚10nm程度のTi膜および膜厚80nm程度のTiN膜を堆積し、続いてTiN膜の上部にCVD法で膜厚350nm程度のW膜を堆積した後、コンタクトホール27、28の外部のTi膜、TiN膜およびW膜を化学的機械研磨法で除去する。ソース領域の上部のコンタクトホール28内に形成されたプラグ30は、コントロールゲート電極9（ワード線WL）の延在方向に沿った多数のMISFET（メモリセルMC）に共通のソース線SLを構成する。

**【 0 0 7 1 】**

次に、図38に示すように、酸化シリコン膜25の上部にCVD法で膜厚300nm程度の酸化シリコン膜を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでコンタクトホール27の上部の酸化シリコン膜25を除去し、プラグ30の表面を露出するスルーホール32を形成する。

**【 0 0 7 2 】**

その後、スルーホール32の内部を含む酸化シリコン膜25上にスパッタリング法とCVD法とで膜厚350nm程度のW膜を堆積し、続いてフォトレジスト膜をマスクにしたドライエッチングでW膜をパターニングしてデータ線DLを形成することにより、前記図2～図4に示すメモリセルMCが略完成する。その後、データ線DLの上部には層間絶縁膜を介して2層程度のA1配線が形成されるが、その図示は省略する。

**【 0 0 7 3 】**

本実施形態によれば、メモリセルMCを構成するMISFETの特性を劣化させることなく、SAC技術を利用した微細加工を実現できるので、NOR型フラッシュメモリの大容量化、微細化を推進することができる。

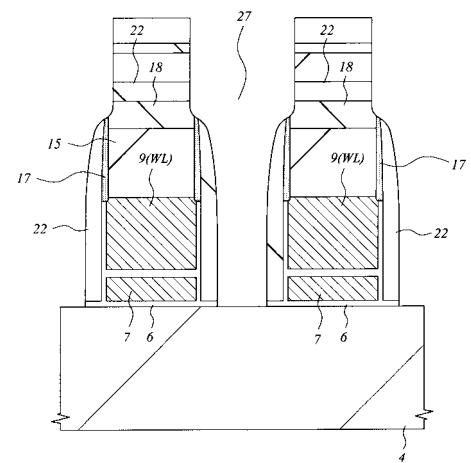

**【 0 0 7 4 】****（実施の形態2）**

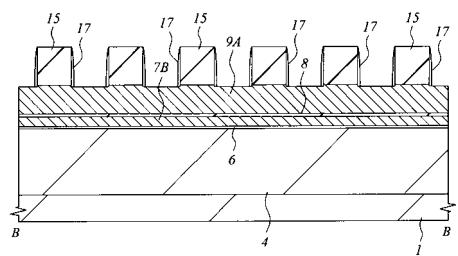

前記実施の形態1では、メモリセルMCを構成するMISFETのゲート酸化膜6中に結晶欠陥が発生するのを抑制するために、コントロールゲート電極9の上部を保護する絶縁膜を酸化シリコン膜15のみで構成したが、本実施形態では、図39に示すように、コントロールゲート電極9上の保護絶縁膜を酸化シリコン膜15とその上部に堆積した窒化シリコン膜18とで構成する。

10

20

30

40

50

**【 0 0 7 5 】**

これにより、メモリセルMCのサイズの微細化と共に、隣接するメモリセルMCとのスペースが縮小し、このスペースよりもコンタクトホール27(28)の径が相対的に大きくなつた場合でも、図40に示すように、コンタクトホール27(28)を形成する際のエッティングでコントロールゲート電極9上の酸化シリコン膜15が深く削れる不具合を防止することができる。この場合でも、ゲート酸化膜6中に結晶欠陥が発生するのを抑制するため、窒化シリコン膜18の膜厚は最小限に止めることが望ましい。

**【 0 0 7 6 】**

また、この場合でも、保護絶縁膜(酸化シリコン膜15および窒化シリコン膜18)の側壁に窒化シリコン膜からなるエッティング防止膜17を形成することにより、前述したフッ酸洗浄工程で酸化シリコン膜15の側壁がエッティングされて後退する不具合を防止することができる。

10

**【 0 0 7 7 】**

また、前記実施の形態1では、前記図18～図22に示したように、酸化シリコン膜15をドライエッティングして多結晶シリコン膜9Aの一部を露出させた後、酸化シリコン膜15の側壁にエッティング防止膜17を形成し、次いで側壁にエッティング防止膜17が形成された酸化シリコン膜15をマスクにして多結晶シリコン膜9A、ONO膜8および多結晶シリコン膜7Bを順次ドライエッティングしたが、図41および図42に示すように、酸化シリコン膜15をマスクにして多結晶シリコン膜9A、ONO膜8および多結晶シリコン膜7Bをドライエッティングした後、それらの側壁にエッティング防止膜17を形成してもよい。この場合も、前述したフッ酸洗浄工程で酸化シリコン膜15の側壁がエッティングされて後退する不具合を防止することができる。

20

**【 0 0 7 8 】**

以上、本発明者によってなされた発明を前記実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

**【 0 0 7 9 】**

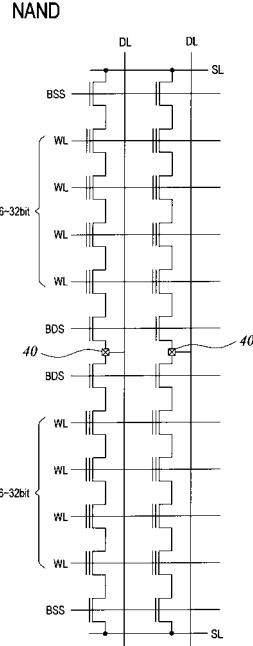

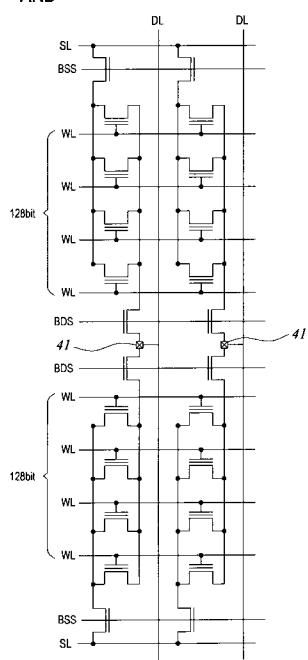

前記実施の形態では、NOR型フラッシュメモリに適用した場合について説明したが、これに限定されるものではなく、例えばNAND型フラッシュメモリやAND型フラッシュメモリのように、フローティングゲート電極とコントロールゲート電極とを有する2層ゲート構造のMISFETでメモリセルを構成する他のフラッシュメモリに適用することもできる。すなわち、図43に示すようなNAND型フラッシュメモリの選択MISFET(BDS)のドレイン領域とデータ線DLとを接続するコンタクトホール40を自己整合で形成する場合や、図44に示すような、AND型フラッシュメモリの選択MISFET(BDS)のドレイン領域とデータ線DLとを接続するコンタクトホール41を自己整合で形成する場合などに適用することで、NAND型フラッシュメモリやAND型フラッシュメモリの微細化、大容量化を推進することができる。

30

**【 0 0 8 0 】****【発明の効果】**

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

40

**【 0 0 8 1 】**

本発明によれば、メモリセルを構成するMISFETの特性を劣化させることなく、SAC技術を利用した微細加工を実現することができる。

**【 0 0 8 2 】**

本発明によれば、フラッシュメモリの大容量化、微細化を推進することができる。

**【図面の簡単な説明】**

【図1】本発明の一実施の形態であるNOR型フラッシュメモリの主要部を示すプロク図である。

【図2】本発明の一実施の形態であるフラッシュメモリのメモリアレイを示す要部平面図

50

である。

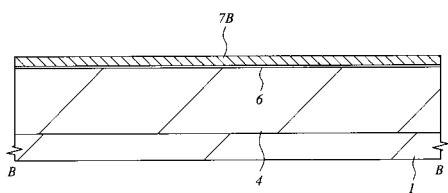

【図 3】図 2 の A - A 線に沿った半導体基板の要部断面図である。

【図 4】図 2 の B - B 線に沿った半導体基板の要部断面図である。

【図 5】図 4 の拡大断面図である。

【図 6】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部平面図である。

【図 7】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 8】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

10

【図 9】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 10】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 11】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部平面図である。

【図 12】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 13】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

20

【図 14】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 15】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 16】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 17】本発明の実施の形態 1 であるフラッシュメモリの製造方法を示す要部断面図である。

【図 18】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

30

【図 19】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 20】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 21】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 22】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 23】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部平面図である。

40

【図 24】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 25】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 26】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 27】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図 28】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部拡大断面図である。

50

【図29】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図30】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部拡大断面図である。

【図31】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図32】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図33】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。 10

【図34】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図35】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部平面図である。

【図36】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。 20

【図37】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図38】本発明の一実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。 20

【図39】本発明の他の実施の形態であるフラッシュメモリを示す要部拡大断面図である。

【図40】本発明の他の実施の形態であるフラッシュメモリの製造方法を示す要部拡大断面図である。

【図41】本発明の他の実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図42】本発明の他の実施の形態であるフラッシュメモリの製造方法を示す要部断面図である。

【図43】本発明の他の実施の形態であるNAND型フラッシュメモリの概略回路図である。 30

【図44】本発明の他の実施の形態であるAND型フラッシュメモリの概略回路図である。

【図45】本発明者らが検討した課題を説明する断面図である。

【図46】本発明者らが検討した課題を説明する断面図である。

【図47】本発明者らが検討した課題を説明する断面図である。

【図48】本発明者らが検討した課題を説明する断面図である。

【図49】本発明者らが検討した課題を説明する拡大断面図である。

【図50】本発明者らが検討した課題を説明する拡大断面図である。

#### 【符号の説明】

- 1 半導体基板

- 2 素子分離溝

- 3 酸化シリコン膜

- 4 p型ウエル

- 6 ゲート酸化膜（第1ゲート絶縁膜）

- 7 フローティングゲート電極

- 7A 多結晶シリコン膜

- 8 ONO膜（第2ゲート絶縁膜）

- 9A 多結晶シリコン膜

- 9 コントロールゲート電極

- 15 酸化シリコン膜（第1保護絶縁膜）

10

20

30

40

50

|             |                         |    |

|-------------|-------------------------|----|

| 1 6         | フォトレジスト膜                |    |

| 1 7         | エッチング防止膜                |    |

| 1 7 A       | 窒化シリコン膜                 |    |

| 1 8         | 窒化シリコン膜                 |    |

| 2 0         | n型不純物導入領域(ソース領域、ドレイン領域) |    |

| 2 1         | p型不純物導入領域               |    |

| 2 2         | 窒化シリコン膜(第2保護絶縁膜)        |    |

| 2 3、2 4、2 5 | 酸化シリコン膜                 |    |

| 2 6         | フォトレジスト膜                |    |

| 2 7、2 8     | コントラクトホール               | 10 |

| 3 0         | プラグ                     |    |

| 3 1         | 酸化シリコン膜                 |    |

| 3 2         | スルーホール                  |    |

| 4 0、4 1     | コントラクトホール               |    |

| 1 0 0       | 半導体基板                   |    |

| 1 0 1       | ゲート酸化膜                  |    |

| 1 0 2       | フローティングゲート電極            |    |

| 1 0 2 A     | 多結晶シリコン膜                |    |

| 1 0 3       | ONO膜                    |    |

| 1 0 4       | コントロールゲート電極             | 20 |

| 1 0 4 A     | 多結晶シリコン膜                |    |

| 1 0 5       | 酸化シリコン膜                 |    |

| 1 0 6       | フォトレジスト膜                |    |

| 1 0 7       | 不純物導入領域(ソース領域、ドレイン領域)   |    |

| 1 0 8       | 窒化シリコン膜                 |    |

| D L         | データ線                    |    |

| I O         | 入出力回路                   |    |

| M A R Y     | メモリアレイ                  |    |

| M C         | メモリセル                   |    |

| S A         | センスアンプ                  | 30 |

| S L         | ソース線                    |    |

| S V C       | ソース電圧制御回路               |    |

| T G         | タイミング発生回路               |    |

| V G         | 内部電圧発生回路                |    |

| W L         | ワード線                    |    |

| X B         | Xアドレスバッファ               |    |

| X D         | Xアドレスデコーダ               |    |

| Y B         | Yアドレスバッファ               |    |

| Y D         | Yアドレスデコーダ               |    |

| Y S         | Yスイッチ回路                 | 40 |

【 図 1 】

【 図 2 】

【図3】

【 四 4 】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図16】

図16

【図15】

図15

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

【図25】

【図28】

【図26】

【図27】

【図29】

【図30】

图 30

【図31】

31

【図32】

☒ 32

【図33】

☒ 33

【図35】

☒ 35

【図34】

图 34

【図36】

【図37】

図37

【図38】

【図39】

図39

【図40】

図40

【図41】

図41

【図42】

図42

【図43】

図43

【図44】

図44

AND

【図45】

図45

【図46】

図46

【図47】

図47

【図48】

図48

【図49】

図49

【図50】

図50

---

フロントページの続き

(72)発明者 柳田 博史

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内

(72)発明者 岡田 大介

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内

審査官 瀧内 健夫

(56)参考文献 特開平10-032243(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792