(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 198 11 568 B4 2005.10.06

(12)

## Patentschrift

(21) Aktenzeichen: **198 11 568.7**

(22) Anmeldetag: **17.03.1998**

(43) Offenlegungstag: **24.09.1998**

(45) Veröffentlichungstag

der Patenterteilung: **06.10.2005**

(51) Int Cl.<sup>7</sup>: **H01L 29/06**

**H01L 29/739**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zur erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(30) Unionspriorität:

9-065151 18.03.1997 JP

10-050745 03.03.1998 JP

(72) Erfinder:

Tsukuda, Masanori, Yokohama, JP; Shinohe, Takashi, Yokosuka, Kanagawa, JP; Yamaguchi, Masakazu, Kawasaki, JP

(73) Patentinhaber:

Kabushiki Kaisha Toshiba, Kawasaki, Kanagawa, JP

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US 51 73 435

US 43 74 389

EP 7 26 603 A2

EP 5 26 084 A1

(74) Vertreter:

HOFFMANN & EITLE, 81925 München

### (54) Bezeichnung: Halbleitervorrichtung mit einem Leistungshalbleiterelement

(57) Hauptanspruch: Halbleitervorrichtung, umfassend ein einen hohen Widerstand aufweisendes Halbleitersubstrat (1; 21; 41; 61) von einem ersten Leitfähigkeitstyp mit einer ersten und zweiten Hauptoberfläche und einer Ausnehmung in der ersten oder zweiten Hauptoberfläche; ein Leistungs-Halbleiterelement (1-4; 21-27; 41b, 48; 61b, 64-67) mit einer Feldrelaxationsanordnung (4; 12; 27), die zumindest teilweise in einem Bereich des Halbleitersubstrats (1; 21; 41; 61) ausgebildet sind, in welchem die Ausnehmung vorgesehen ist;

wobei

das Leistungs-Halbleiterelement ein Hauptelement (1-3; 21-26; 61b, 64-67) mit einer aktiven Region aufweist;

die Feldrelaxationsanordnung (4; 12; 27) von einem zweiten Leitfähigkeitstyp ist; und

die Dicke eines einen hohen Widerstand aufweisenden ersten Bereiches des Halbleitersubstrat (1; 21; 41; 61), in welchem das Hauptelement (1-3; 21-26; 61b, 64-67) vorgesehen ist, geringer ist als die Dicke eines einen hohen Widerstand aufweisenden zweiten Bereiches des Halbleitersubstrats unter der Feldrelaxationsanordnung (4; 12; 27).

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft eine Halbleitervorrichtung mit einem Leistungshalbleiterelement.

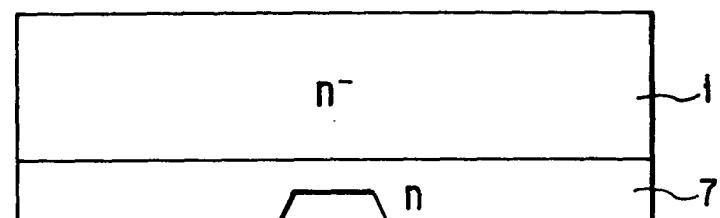

**[0002]** Eines der Hochspannungs-Halbleiterelemente, die in Hochspannungs-Halbleitervorrichtungen für die Leistungssteuerung oder Leistungsregelung eingesetzt werden, ist eine Hochspannungsdiode. [Fig. 1](#) der beigefügten Zeichnungen zeigt als Schnittansicht eine herkömmliche Hochspannungsdiode.

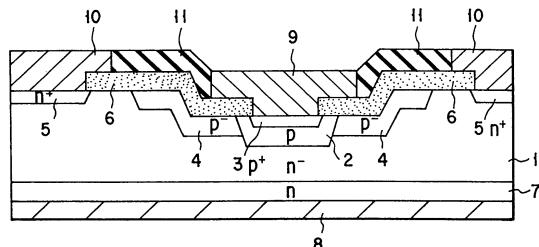

**[0003]** In [Fig. 1](#) ist mit dem Bezugszeichen **81** eine erste Kathodenschicht des n-Typs (Halbleitersubstrat) bezeichnet, welche einen hohen Widerstand aufweist. Eine erste Anodenschicht **82** des p-Typs ist selektiv in der Vorderoberfläche der Kathodenschicht **81** des n-Typs ausgebildet. Eine zweite, stark dotierte Anodenschicht **83** des p-Typs ist selektiv in der Oberfläche der ersten Anodenschicht **82** des p-Typs vorgesehen.

**[0004]** Eine leicht dotierte Auftragsschicht **84** des p-Typs mit einem Feldrelaxationsaufbau (Übergangsbeendigungsaufbau) ist um die Anodenschicht des p-Typs herum in der Vorderoberfläche der Kathodenschicht **81** des n-Typs in Kontakt mit der Anodenschicht des p-Typs angeordnet. Eine stark dotierte Kanalstoppschicht **85** des n-Typs ist außerhalb der Auftragsschicht **84** des p-Typs in der Vorderoberfläche der Kathodenschicht **81** des n-Typs angeordnet, und ist von der Auftragsschicht **84** des p-Typs in einem vorbestimmten Abstand angeordnet.

**[0005]** Ein Film **86** mit hohem Widerstand ist in dem Bereich vorgesehen, der von einem Rand der zweiten Anodenschicht **83** des p-Typs zur ersten Anodenschicht **82** des p-Typs, zur Auftragsschicht **84** des p-Typs, zur Kathodenschicht **81** des n-Typs und zur Kanalstoppschicht **85** des n-Typs geht. Statt des Films **86** mit hohem Widerstand kann auch ein Isolierfilm vorgesehen werden.

**[0006]** Eine zweite Kathodenschicht **87** des n-Typs, die stärker dotiert ist als die Kathodenschicht **81** des n-Typs, ist auf der rückwärtigen Oberfläche der ersten Kathodenschicht **81** des n-Typs vorgesehen, die einen hohen Widerstand aufweist. Eine Kathodenelektrode **88** ist auf der Kathodenschicht **87** des n-Typs vorgesehen. Eine Anodenelektrode **89** ist auf der zweiten Anodenschicht **83** des p-Typs angeordnet, wogegen eine Elektrode **90** auf der Kanalstoppschicht **85** des n-Typs vorgesehen ist. Mit dem Bezugszeichen **91** ist ein Isolierfilm bezeichnet.

**[0007]** Bei einer herkömmlichen Hochspannungsdiode des voranstehend geschilderten Typs treten allerdings folgende Schwierigkeiten auf. Um die Span-

nungsfestigkeit zu erhöhen muss die Kathodenschicht **81** des n-Typs dick ausgebildet werden. Mit wachsender Dicke der Kathodenschicht **81** des n-Typs nehmen der Spannungsabfall in Vorwärtsrichtung und der Rückwärtserholungsverlust zu, was sich ungünstig auswirken kann. Schlimmstenfalls kann die Halbleitervorrichtung zerstört werden.

**[0008]** Seit einigen Jahren nimmt das Bedürfnis zu, kleinere Halbleitervorrichtungen mit höherer Leistung zur Verfügung zu stellen, beispielsweise Inverterschaltungen (Wechselrichterschaltungen) und Zerhackerschaltungen.

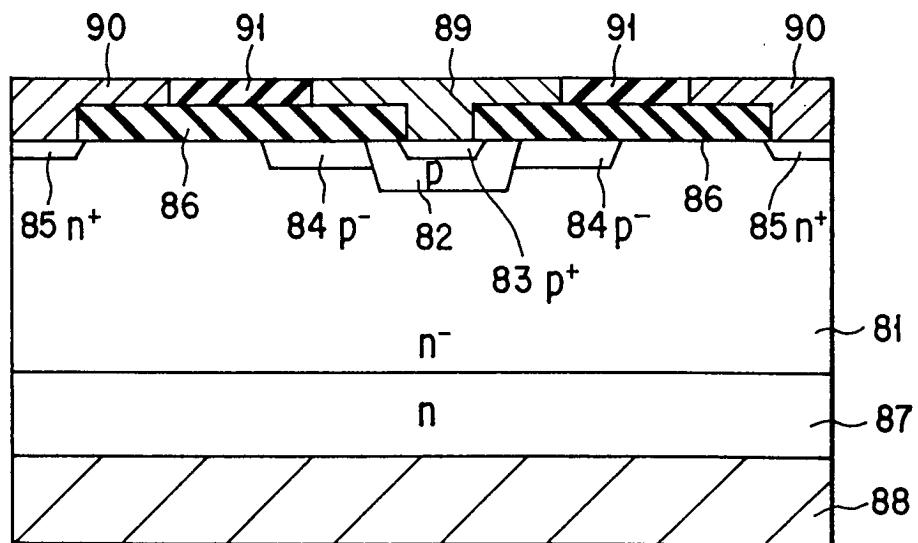

**[0009]** [Fig. 2](#) zeigt den grundlegenden Aufbau der Schaltung eines Inverters, der einen herkömmlichen IGBT (Bipolartransistor mit isoliertem Gate) verwendet. Da die Inverterschaltung als Verbraucher eine Induktivität aufweist, etwa bei der Motorsteuerung, muss in der Induktivität des Verbrauchers gespeicherte Energie nach dem selektiven Abschalten von Schaltelementen Tr1 bis Tr4 abgegeben werden. Für die Rückführung der elektrischen Energie sind Freilaufdioden (Umpolungsdioden) D1 bis D4 antiparallel zu den IGBTs geschaltet.

**[0010]** Bei diesem herkömmlichen Halbleitergerät muss ein Übergangsbeendigungsbereich größer oder gleich einer vorbestimmten Fläche innerhalb eines Halbleiterchips vorgesehen werden, um eine Spannungsfestigkeit zu erzielen, die größer oder gleich der Versorgungsspannung in jedem Paar aus IGBT und Freilaufdiode ist. Daher lässt sich die Chipfläche nur schwer verkleinern, so dass die Stromdichten nicht erhöht werden kann. Zur Herstellung eines Bauteils, welches das Halbleitergerät enthält (beispielsweise IGBT), ist ein getrenntes Element wie etwa eine Freilaufdiode extern an den IGBT angeschlossen. Daher werden ein IGBT-Chip und ein Freilaufdiodenchip auf einer einzelnen Platine angebracht, und werden Elektroden auf den betreffenden Chips sowie externe Elektroden über Leitungen verbunden. Bei einer derartigen Anordnung lässt sich infolge der Induktivität der Anschlussleitungen kein Hochgeschwindigkeitsbetrieb erzielen.

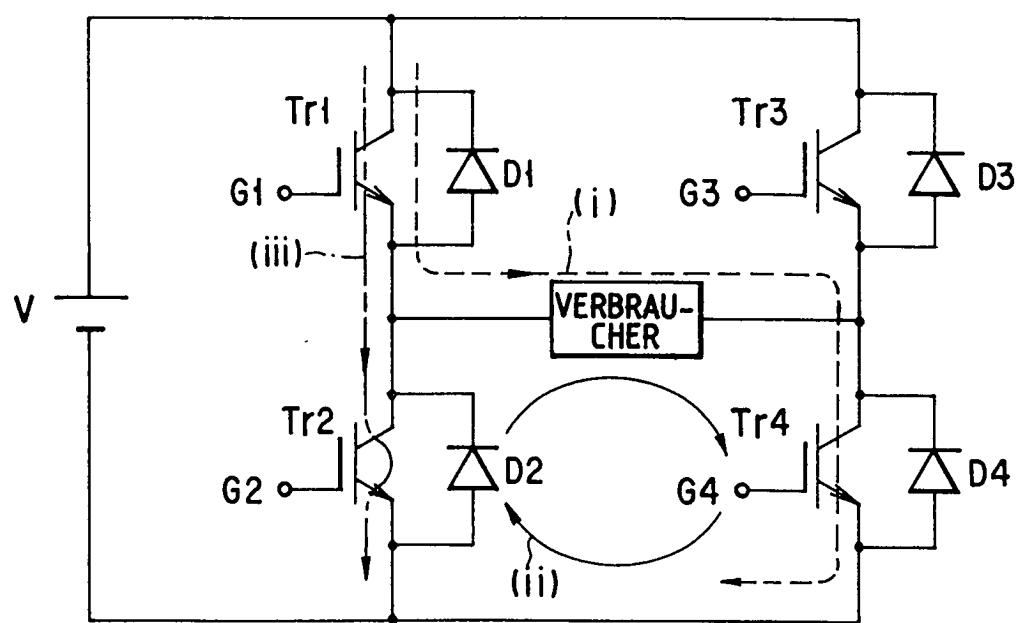

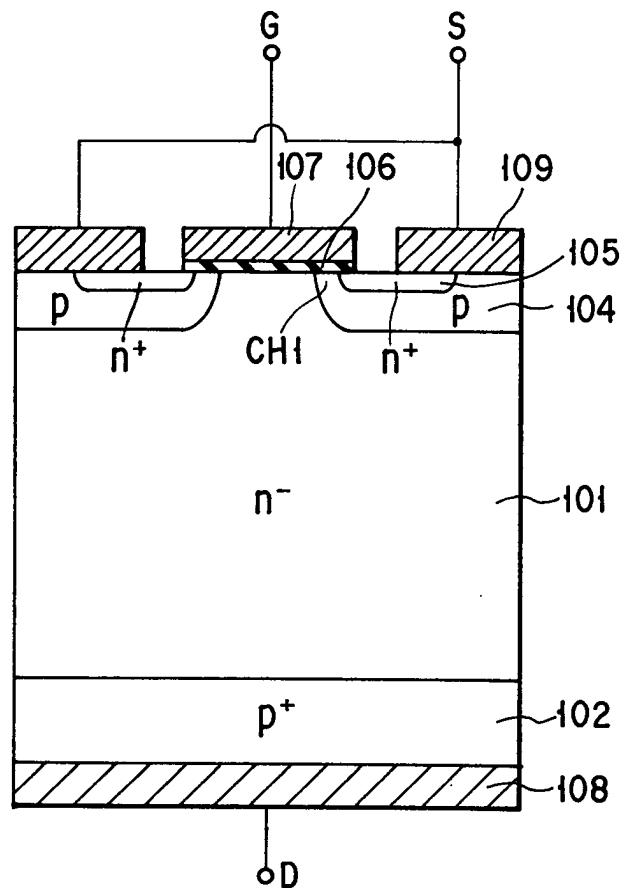

**[0011]** Auch bei dem IGBT besteht das Bedürfnis, dass dort Verluste gering gehalten werden. [Fig. 3](#) zeigt als Schnittansicht die Ausbildung eines IGBT der genannten Art. Bei dem IGBT ist eine Drainsschicht **102** des p-Typs auf einer Oberfläche einer Basisschicht des n-Typs mit hohem Widerstand (Halbleitersubstrat) **101** vorgesehen. Eine Basissschicht **104** des p-Typs ist selektiv in der anderen Oberfläche der Basisschicht **101** des n-Typs angeordnet, und eine Sourceschicht **105** des n-Typs ist in der Basisschicht **104** des p-Typs angeordnet. Eine Gateelektrode **107** ist auf der Basisschicht **104** des p-Typs zwischen der Basisschicht **101** des n-Typs und der Sourceschicht **105** des n-Typs vorgesehen,

wobei sich dazwischen ein Gateisolierfilm **106** befindet. Die Gateelektrode **107**, der Gateisolierfilm **106**, die Basisschicht **104** des p-Typs, die Basisschicht **101** des n-Typs, und die Sourceschicht **105** des n-Typs bilden einen Elektroneninjektions-MOSFET, der einen Kanalbereich CH1 aufweist. Eine Drainelektrode **108** ist auf der Drainschicht **102** des p-Typs vorgesehen, und eine Sourceelektrode **109** ist auf der Sourceschicht **105** des n-Typs und der Basisschicht **104** des p-Typs angeordnet.

**[0012]** Als nächstes wird der Betrieb des Halbleitergerätes geschildert. Wenn eine positive bzw. negative Spannung an die Drain- bzw. Sourceelektrode **108** bzw. **109** angelegt wird, kehrt sich dann, wenn eine positive Spannung in Bezug auf die Source an die Gateelektrode **107** angelegt wird, der Leitungstyp der Basisschicht **104** des p-Typs gegenüber der Gateelektrode **107** um, und wird zum n-Typ. Elektronen e werden von der Sourceschicht **105** des n-Typs in die Basisschicht **101** des n-Typs über die Schicht mit dem geänderten Leitungstyp injiziert, so dass die Drainschicht **102** des p-Typs erreichen.

**[0013]** Gleichzeitig werden Löcher h von der Drainschicht **102** des p-Typs in die Basisschicht **101** des n-Typs injiziert. Auf diese Art und Weise werden sowohl die Elektronen e als auch die Löcher h in die Basisschicht **101** des n-Typs injiziert, so daß eine Leitfähigkeitsmodulation hervorgerufen wird, was eine Verringerung der Einschaltspannung gestattet.

**[0014]** Bei einem Abschaltvorgang wird eine negative Spannung in Bezug auf die Source-Region an die Gateelektrode **107** angelegt. Die im Leitungstyp umgekehrte Schicht, die unmittelbar unterhalb der Gateelektrode **107** ausgebildet wurde, verschwindet dann, so dass keine weitere Injektion von Elektronen erfolgt. Einige der Löcher h in der Basisschicht **101** des n-Typs werden über die Basisschicht **104** des p-Typs an die Sourceelektrode **109** abgegeben, und die übrigen Löcher h re kombinieren mit Elektronen e und verschwinden. Dies führt dazu, dass das Halbleitergerät abgeschaltet wird.

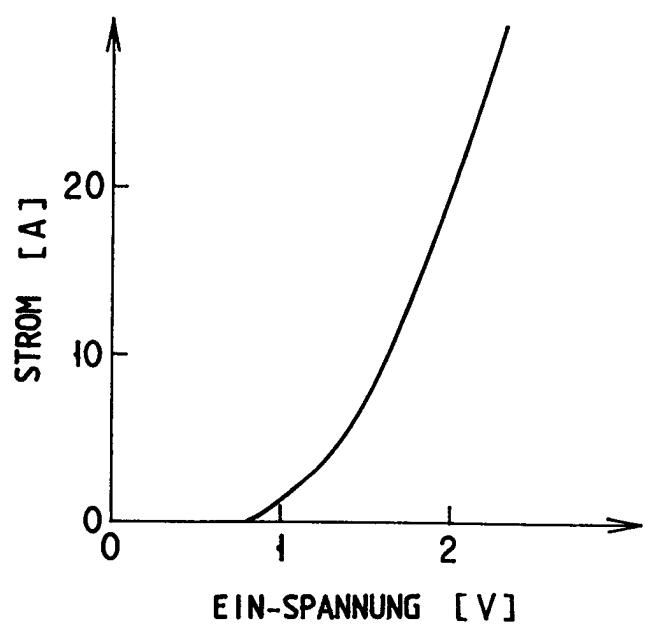

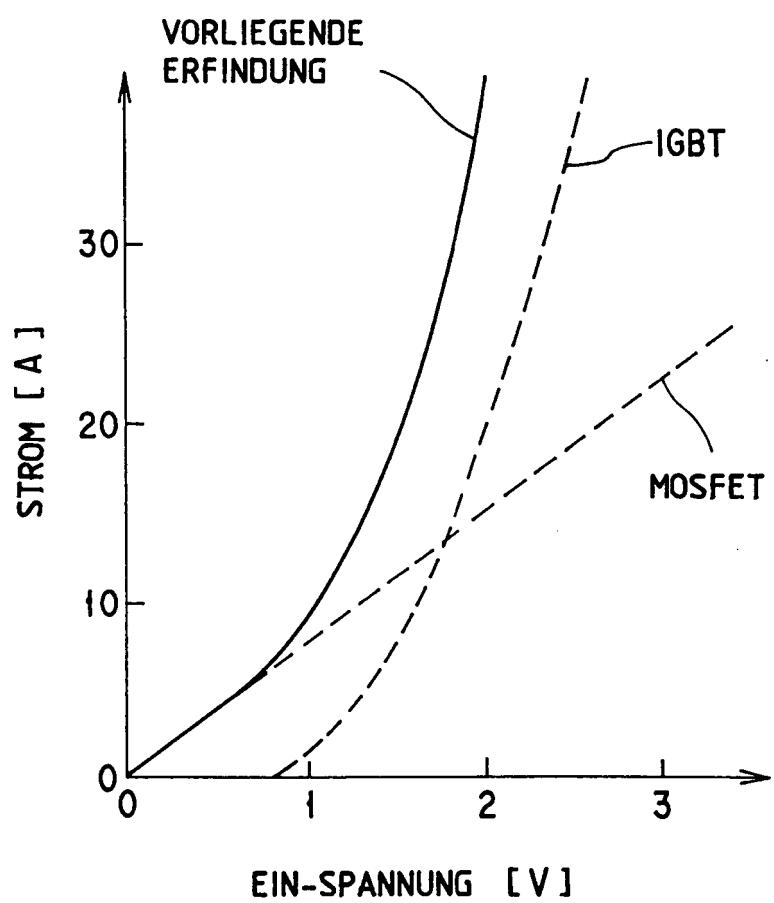

**[0015]** Allerdings müssen bei dem herkömmlichen IGBT die Elektronen e und die Löcher h eine Potenialbarriere überwinden, die durch den p-n-Übergang zwischen der Basisschicht **101** des n-Typs und die Drainschicht **102** des p-Typs im leitenden Zustand hervorgerufen wird. Wie aus dem Strom-Spannungsdiagramm von [Fig. 4](#) hervorgeht, nimmt daher der Einschaltwiderstand durch eine eingebaute Spannung von etwa 0,7 V proportional zum Spannungsabfall zu, der durch den p-n-Übergang hervorgerufen wird. Bei dem herkömmlichen IGBT kann daher der Einschaltwiderstand im leitenden Zustand nicht ausreichend verringert werden.

**[0016]** Aus der US 4 374 389 ist eine Halbleitervorrichtung bekannt mit einem Halbleitersubstrat eines ersten Leitungstyps mit hohem Widerstand, das eine erste und zweite Hauptoberfläche aufweist sowie eine Ausnehmung in der ersten oder zweiten Hauptoberfläche, und mit einem Leistungs-Halbleiterbauelement mit einer Feldrelaxationsanordnung, von welcher zumindest ein Teil in einem Bereich des Halbleitersubstrats vorgesehen ist, in welchem die Ausnehmung angeordnet wird.

#### Aufgabenstellung

**[0017]** Der Erfindung liegt die Aufgabe zugrunde, eine Halbleitervorrichtung dieser Art derart weiterzubilden, bei welcher auch bei Ausbildung in vergleichsweise kleinen Abmessungen eine eichende Spannungsfestigkeit sichergestellt werden kann.

**[0018]** Gemäß der vorliegenden Erfindung wird diese Aufgabe mit einer Halbleitervorrichtung nach dem Patentanspruch 1 gelöst.

**[0019]** Weiterbildungen der Erfindung ergeben sich aus den Unteransprüchen.

**[0020]** Eine erfindungsgemäße Halbleitervorrichtung umfasst:

Ein Halbleitersubstrat mit hohem Widerstand eines ersten Leitfähigkeitsstyps, welches eine erste und eine zweite Hauptoberfläche aufweist, sowie eine Ausnehmung entweder in der ersten oder der zweiten Hauptoberfläche, und ein Leistungshalbleiterelement mit einem Feldrelaxationsaufbau, welches zumindest teilweise in dem Bereich des Halbleitersubstrats vorgesehen ist, in welchem die Ausnehmung vorhanden ist. Dabei weist das Leistungshalbleiterelement ein Hauptelement mit einem aktiven Bereich und dem Feldrelaxationsaufbau eines zweiten Leitfähigkeitsstyps auf. Dabei ist die Dicke eines Abschnitts mit hohem Widerstand des Halbleitersubstrats, an welchem das Hauptelement des Halbleiterelements vorgesehen ist, geringer als die Dicke eines Abschnitts mit hohem Widerstand des Halbleitersubstrats unterhalb des Feldrelaxationsaufbaus.

**[0021]** Der Feldrelaxationsaufbau wird vorzugsweise in einem Bereich vorgesehen, der von einer Bodenoberfläche und einer Seitenwandoberfläche der in der ersten Hauptoberfläche vorgesehenen Ausnehmung zur ersten Hauptoberfläche reicht, welche die Ausnehmung umgibt, und ist vorzugsweise mit mehreren Stufen an einer Grenzfläche zwischen dem Feldrelaxationsaufbau und dem Halbleitersubstrat des ersten Leitfähigkeitsstyps versehen.

**[0022]** Der Feldrelaxationsaufbau kann entweder

eine Resurf-Schicht oder einen Schutzring enthalten.

**[0023]** Das Halbleiterelement kann als Diode ausgebildet sein, und eine Anodenschicht des zweiten Leitfähigkeitstyps der Diode kann mehrere Stufen an einer Grenzfläche zwischen der Anodenschicht und dem Halbleitersubstrat des ersten Leitfähigkeitstyps aufweisen.

**[0024]** Das Halbleiterelement kann ein IGBT sein, und die Dicke eines Abschnitts mit hohem Widerstand des Halbleitersubstrats unterhalb einer Basischicht des zweiten Leitfähigkeitstyps des IGBT kann geringer sein als die Dicke des Abschnitts mit hohem Widerstand der Halbleitersubstrats unterhalb des Feldrelaxationsaufbaus, der an einem Abschlusselement des IGBT vorgesehen ist.

**[0025]** Bei der vorliegenden Erfindung wird als Halbleitersubstrat mit hohem Widerstand des ersten Leitfähigkeitstyps ein derartiges Substrat vorgesehen, in dessen Oberfläche eine Ausnehmung ausgebildet ist. Ein Hochspannungshalbleiterelement ist in einem dünnen Bereich der Ausnehmung vorgesehen. Aus diesem Grund kann, selbst wenn das Halbleitersubstrat dick ist, das Hochspannungshalbleiterelement entsprechend der Tiefe der Ausnehmung dünn ausgebildet werden.

**[0026]** Selbst wenn die Halbleitervorrichtung dick ausgebildet wird, um den Wirkungsgrad der Feldrelaxationsanordnung zu erhöhen, treten keine Beeinträchtigungen der Eigenschaften des Bauteils auf, etwa ein Abfall der Vorwärtsspannung, ein Rückwärtserholungsverlust, und dergleichen.

**[0027]** Selbst wenn aus Festigkeitsgründen das Halbleitersubstrat dick ausgebildet wird bei zunehmendem Durchmesser des Halbleiterwafer, kann das Hochspannungshalbleiterelement entsprechend der Tiefe der Ausnehmung dünn ausgebildet werden. Daher kann ein Hochspannungshalbleitergerät, bei welchem die Dicke des Halbleitersubstrats frei gewählt werden kann, und die erforderliche Spannungsfestigkeit sichergestellt werden kann, ohne daß sich die Eigenschaften des Elements verschlechtern, realisiert werden.

**[0028]** Infolge der Verwendung der Feldrelaxationsanordnung, die mehrere Stufen an der Grenzfläche zwischen der Anordnung und dem Halbleitersubstrat aufweist, nimmt die Anzahl an Feldkonzentrationsabschnitten zu und es steigt die Spannungsfestigkeit an, die durch Integration des elektrischen Feldes erhalten wird, verglichen mit einer herkömmlichen Feldrelaxationsanordnung ohne irgendeine Stufe. Daher lässt sich ein Hochspannungshalbleitergerät erzielen, welches eine höhere Spannungsfestigkeit aufweist als die herkömmliche Feldrelaxationsanordnung.

**[0029]** Bei der vorliegenden Erfindung kann als das Halbleitersubstrat mit hohem Widerstand des ersten Leitfähigkeitstyps ein Substrat verwendet werden, welches Ausnehmungen in der ersten Hauptoberfläche (der vorderen Oberfläche) und der zweiten Hauptoberfläche (der rückseitigen Oberfläche) aufweist. In diesem Fall wird das Hochspannungshalbleiterelement an einem Abschnitt zwischen den Ausnehmungen in der vorderen und hinteren Oberfläche vorgesehen. Selbst wenn das Halbleitersubstrat dick ist, kann das Hochspannungshalbleiterelement dünn ausgebildet werden, entsprechend der Tiefe der Ausnehmung.

**[0030]** Bei der Herstellung einer Stufe auf der vorderen Oberfläche kann keine große Stufe ausgebildet werden, infolge der Einschränkungen bezüglich der Herstellung eines feinen Musters. Im Gegensatz hierzu gibt es bei der Ausbildung einer Stufe auf der rückwärtigen Oberfläche keine Einschränkungen bezüglich der Stufe, und kann die Dicke des Halbleitersubstrats innerhalb eines weiten Bereiches frei gewählt werden. Daher kann ein Hochspannungshalbleitergerät realisiert werden, bei welchem die Dicke des Halbleitersubstrats innerhalb eines weiten Bereiches frei gewählt werden kann, und die erforderliche Spannungsfestigkeit sichergestellt werden kann, ohne Beeinträchtigung der Eigenschaften des Elements.

**[0031]** Vorzugsweise wird bei einer erfindungsgemäßen Halbleitervorrichtung eine Freilaufdiode in einem Bereich vorgesehen, in welchem die Ausnehmung vorhanden ist, und wird ein IGBT in einem anderen Bereich als jenem vorgesehen, in welchem die Ausnehmung vorhanden ist.

**[0032]** Die Dicke des Halbleitersubstrats in dem Bereich, in welchem die Freilaufdiode vorgesehen ist, ist geringer als die Dicke des Halbleitersubstrats in jenem Bereich, in welchem der IGBT vorhanden ist.

**[0033]** Die Dicke eines Abschnitts mit hohem Widerstand des Halbleitersubstrats, welcher einen Teil der Diode bildet, kann geringer sein als die Dicke eines Abschnitts mit hohem Widerstand des Halbleitersubstrats, der einen Teil des IGBT bildet.

**[0034]** Das Leistungshalbleiterelement kann weiterhin eine erste Hauptelektrode und eine Unterelektrode aufweisen, die auf der ersten Hauptoberfläche vorgesehen sind, sowie eine zweite Hauptelektrode, die auf der zweiten Hauptoberfläche vorgesehen ist, wobei der IGBT, der in einem Bereich vorgesehen ist, in welchem die Ausnehmung nicht vorhanden ist, aufweist:

eine Basisschicht mit hohem Widerstand des ersten Leitfähigkeitstyps, die auf dem Halbleitersubstrat vorgesehen ist,

eine Drainschicht mit einem zweiten Leitfähigkeitstyp, die in der zweiten Hauptoberfläche des Halblei-

tersubstrats vorgesehen ist,

eine Basisschicht des zweiten Leitfähigkeitstyps, die selektiv in der ersten Hauptoberfläche des Halbleitersubstrats vorgesehen ist,

eine Sourceschicht des ersten Leitfähigkeitstyps, die selektiv in der Basisschicht des zweiten Leitfähigkeitstyps vorgesehen ist, und

eine Gateelektrode, die über einen Gateisolierfilm auf der Basisschicht des zweiten Leitfähigkeitstyps zwischen der Basisschicht des ersten Leitfähigkeitstyps und der Sourceschicht des ersten Leitfähigkeitstyps vorgesehen ist, wobei die Freilaufdiode, die in dem Bereich vorhanden ist, in welchem die Ausnehmung vorgesehen ist, aufweist:

eine Basisschicht mit hohem Widerstand des ersten Leitfähigkeitstyps, die in dem Halbleitersubstrat vorgesehen ist,

eine Kathodenschicht des ersten Leitfähigkeitstyps, die in der zweiten Hauptoberfläche der Basisschicht des ersten Leitfähigkeitstyps vorgesehen ist, und

eine Anodenschicht des zweiten Leitfähigkeitstyps, die in der ersten Hauptoberfläche der Basisschicht des ersten Leitfähigkeitstyps vorgesehen ist, wobei die erste Hauptelektrode so ausgebildet ist, daß sie in Kontakt mit der Basisschicht des zweiten Leitfähigkeitstyps und der Sourceschicht des ersten Leitfähigkeitstyps des IGBT steht, sowie mit der Anodenschicht des zweiten Leitfähigkeitstyps der Diode, die zweite Hauptelektrode so ausgebildet ist, daß sie sowohl in Kontakt mit der Drainschicht des zweiten Leitfähigkeitstyps als auch mit der Kathode des ersten Leitfähigkeitstyps steht, und die Unterelektrode an die Gateelektrode angeschlossen ist.

**[0035]** Die Gateelektrode kann über den Gateisolierfilm in einem Graben vergraben sein, der so ausgebildet ist, daß er in der ersten Hauptoberfläche des Halbleitersubstrat von einer Oberfläche der Sourceschicht des ersten Leitfähigkeitstyps bis zu einer mittleren Tiefe der Basisschicht des ersten Leitfähigkeitstyps geht, durch die Basisschicht des zweiten Leitfähigkeitstyps hindurch.

**[0036]** Das Leistungshalbleitergerät weist weiterhin vorteilhafterweise einen Isolierbereich auf, der zwischen der Freilaufdiode und dem IGBT vorgesehen ist.

**[0037]** Eine Seitenwandoberfläche der Ausnehmung kann verjüngt ausgebildet sein.

**[0038]** Die Anodenschicht des zweiten Leitfähigkeitstyps der Freilaufdiode kann, abgesehen von ihrer oberen Oberfläche, von einer Schicht des zweiten Leitfähigkeitstyps umgeben sein, deren Widerstand höher ist als jener der Anodenschicht.

**[0039]** Bei der voranstehend geschilderten Ausbil-

dung weist die Halleitervorrichtung gemäß der vorliegenden Erfindung die Funktion einer antiparallelen Freilaufdiode auf, hat eine Schaltfunktion in Vorförwärtsrichtung, und Leitungseigenschaften in Rückwärtsrichtung. Nach Erzeugung einer elektromotorischen Gegenkraft durch einen induktiven Verbraucher wird daher das Halbleitergerät in Rückwärtsrichtung eingeschaltet. Dann wird die Diode bei einer niedrigen Einschaltspannung leitend, da die Diode die Basisschicht mit hohem Widerstand aufweist, die dünner ist als der IGBT. Es ist keine externe antiparallele Freilaufdiode erforderlich, so dass die Stromdichte und die Geschwindigkeit zunehmen, so dass sich ein Halbleitergerät mit kleinen Abmessungen und hoher Leistung ergibt.

**[0040]** Vorzugsweise kann ein vertikaler MOSFET in einem Bereich vorgesehen sein, in welchem die Ausnehmung vorhanden ist, und ein IGBT in einem Bereich mit Ausnahme des Bereiches vorgesehen, in welchem die Ausnehmung vorhanden ist.

**[0041]** Die Dicke des Halbleitersubstrats in dem Bereich, in welchem der vertikale MOSFET vorgesehen ist, ist geringer als die Dicke des Halbleitersubstrats in dem Bereich, in welchem der IGBT vorgesehen ist.

**[0042]** Das Leistungshalbleiterelement weist weiterhin eine erste Hauptelektrode und eine Unterelektrode auf, die auf der ersten Hauptoberfläche vorgesehen sind, sowie eine zweite, auf der zweiten Hauptoberfläche vorgesehene Hauptelektrode, wobei der IGBT, der in dem Bereich mit Ausnahme der Ausnehmung vorgesehen ist, aufweist:

eine Basisschicht mit hohem Widerstand des ersten Leitfähigkeitstyps, die auf dem Halbleitersubstrat vorgesehen ist,

eine Drainschicht mit einem zweiten Leitfähigkeitstyp, die in der zweiten Hauptoberfläche des Halbleitersubstrats vorgesehen ist,

eine erste Basisschicht des zweiten Leitfähigkeitstyps, die selektiv in der ersten Hauptoberfläche des Halbleitersubstrats vorgesehen ist,

eine erste Sourceschicht des ersten Leitfähigkeitstyps, die selektiv in der ersten Basisschicht ausgebildet ist, und

eine erste Gateelektrode, die über einen Gateisolierfilm auf der ersten Basisschicht des zweiten Leitfähigkeitstyps zwischen der Basisschicht mit hohem Widerstand des ersten Leitfähigkeitstyps und der ersten Sourceschicht vorgesehen ist, wobei der vertikale MOSFET, der in dem Bereich vorgesehen ist, in welchem die Ausnehmung vorhanden ist, aufweist:

eine Basisschicht mit hohem Widerstand des ersten Leitfähigkeitstyps, die in dem Halbleitersubstrat vorhanden ist,

eine Drainschicht des ersten Leitfähigkeitstyps, die in der zweiten Hauptoberfläche des Halbleitersubstrats vorgesehen ist,

eine zweite Basisschicht des zweiten Leitfähigkeitsstyps, die selektiv in der ersten Hauptoberfläche des Halbleitersubstrat vorgesehen ist, eine zweite Sourceschicht des ersten Leitfähigkeitsstyps, die selektiv in der zweiten Basisschicht vorgesehen ist, und eine zweite Gateelektrode, die über einen Gateisolierfilm auf der zweiten Basisschicht des zweiten Leitfähigkeitsstyps zwischen der Basisschicht mit hohem Widerstand und der zweiten Sourceschicht vorgesehen ist, wobei die erste Hauptelektrode so ausgebildet ist, daß sie in Kontakt sowohl mit der ersten als auch der zweiten Basisschicht des Leitfähigkeitsstyps als auch der ersten und zweiten Sourceschicht des ersten Leitfähigkeitsstyps steht, die zweite Hauptelektrode so ausgebildet ist, daß sie in Kontakt sowohl mit der Drainschicht des zweiten Leitfähigkeitsstyps als auch der Drainschicht des ersten Leitfähigkeitsstyps steht, und die Unterelektrode an die erste und zweite Gateelektrode angeschlossen ist.

**[0043]** Die erste und die zweite Gateelektrode können über den Gateisolierfilm in Gräben vergraben sein, die so ausgebildet sind, dass sie in der ersten Hauptoberfläche des Halbleitersubstrats von einer Oberfläche der ersten und der zweiten Sourceschicht des ersten Leitfähigkeitsstyps zu einer mittleren Tiefe der ersten und der zweiten Basisschicht des ersten Leitfähigkeitsstyps gehen, durch die erste bzw. zweite Basisschicht des zweiten Leitfähigkeitsstyps hindurch.

**[0044]** Weiterhin weist die erfindungsgemäße Halbleitervorrichtung vorzugsweise einen Isolierungsbereich auf, der zwischen dem MOSFET und dem IGBT vorgesehen ist.

**[0045]** Eine Seitenwand der Ausnehmung ist verjüngt ausgebildet.

**[0046]** Infolge der voranstehend geschilderten Ausbildung wird bei der Halbleitervorrichtung gemäß der vorliegenden Erfindung in dem Bereich mit kleinem Strom, infolge der Tatsache, dass der Pfad, welcher die zweite Hauptelektrode, die Sourceschicht des ersten Leitfähigkeitsstyps, die invertierte Schicht (Kanal) unterhalb der Gateelektrode, die Basisschicht des ersten Leitfähigkeitsstyps, die Drainschicht des ersten Leitfähigkeitsstyps, und die erste Elektrode verbindet, hauptsächlich den Flußpfad von Majoritätsladungsträgern bildet, kein Spannungsabfall durch den p-n-Übergang hervorgerufen, und beginnt der Strom von 0 V an. In dem Bereich mit hohem Strom tritt eine Leitfähigkeitsmodulation auf, da Minoritätsladungsträger von der Drainschicht des zweiten Leitfähigkeitsstyps in die Basisschicht des ersten Leitfähigkeitsstyps injiziert werden. Daher kann der Einschaltwiderstand über dem Bereich mit kleinem Strom bis zum Bereich mit hohem Strom verringert werden.

**[0047]** Bevorzugte Ausführungsformen der Erfindung werden nachstehend anhand der Zeichnungen näher erläutert, woraus sich weitere Vorteile und Merkmale ergeben.

**[0048]** In den Zeichnungen zeigen:

**[0049]** [Fig. 1](#) eine Teilschnittansicht des Aufbaus des Hauptteils einer herkömmlichen Hochspannungsdiode;

**[0050]** [Fig. 2](#) ein Schaltbild des Hauptteils eines Inverters (Wechselrichters), der einen herkömmlichen IGBT verwendet;

**[0051]** [Fig. 3](#) eine Schnittansicht des Hauptteils eines herkömmlichen IGBT;

**[0052]** [Fig. 4](#) eine Darstellung der Strom-Spannungseigenschaften des IGBT;

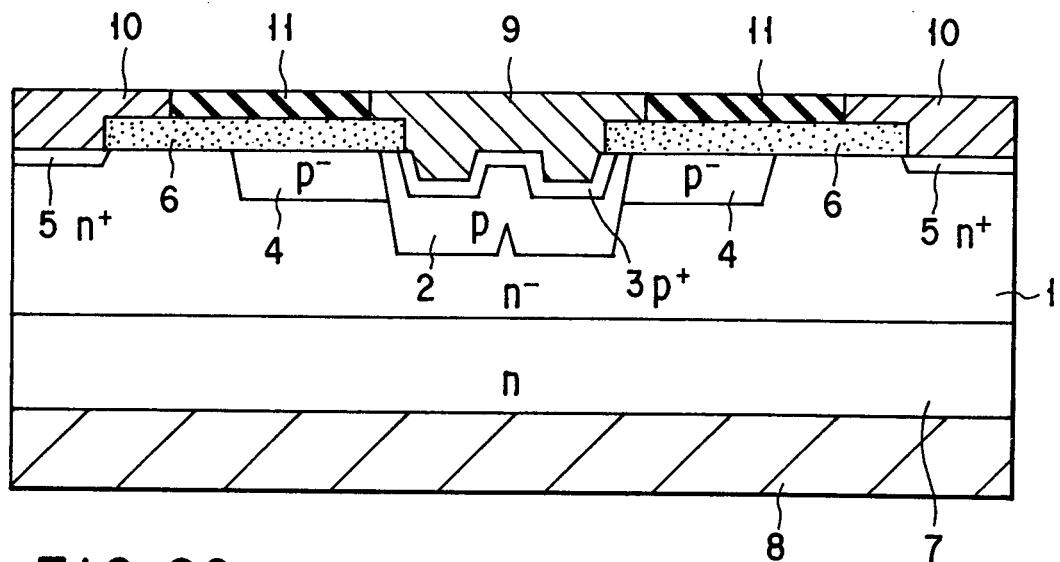

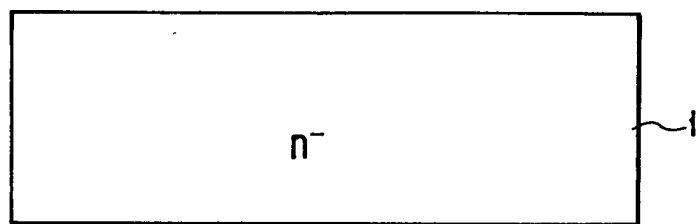

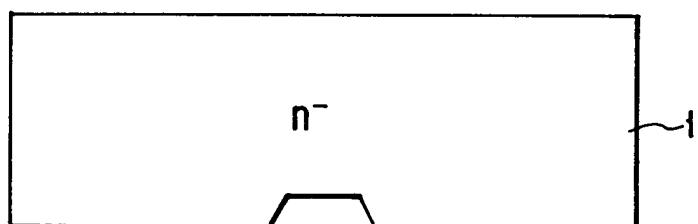

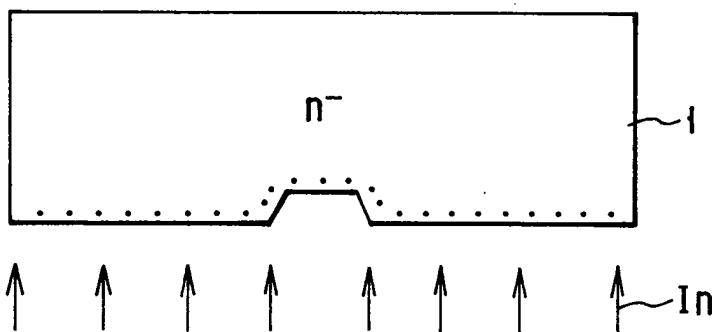

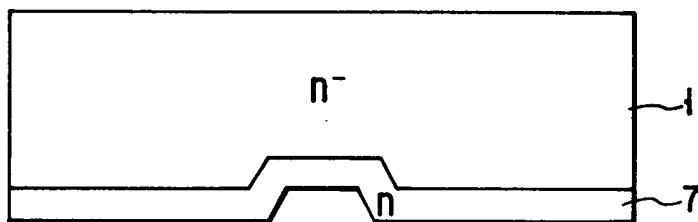

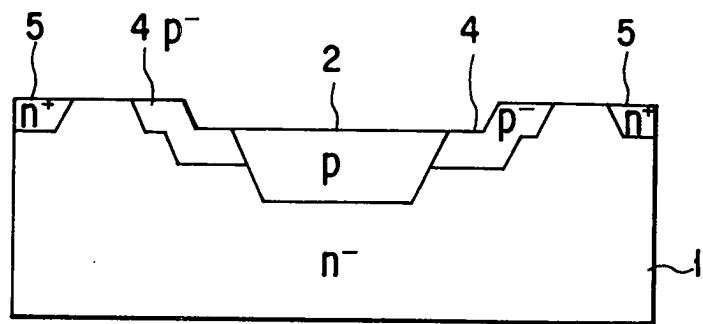

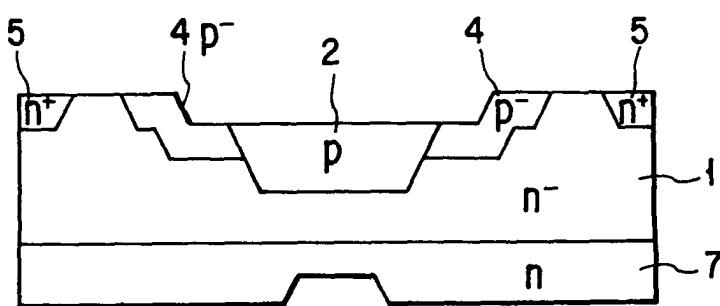

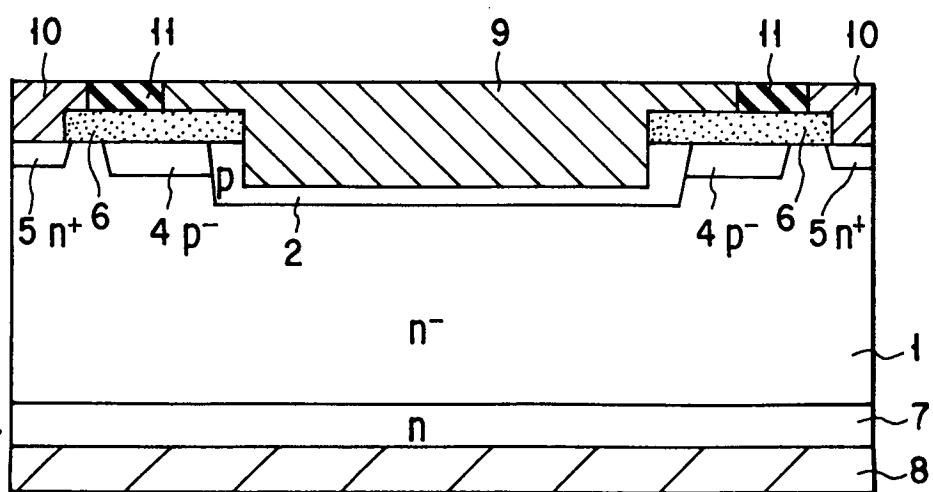

**[0053]** [Fig. 5](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer ersten Ausführungsform der vorliegenden Erfindung;

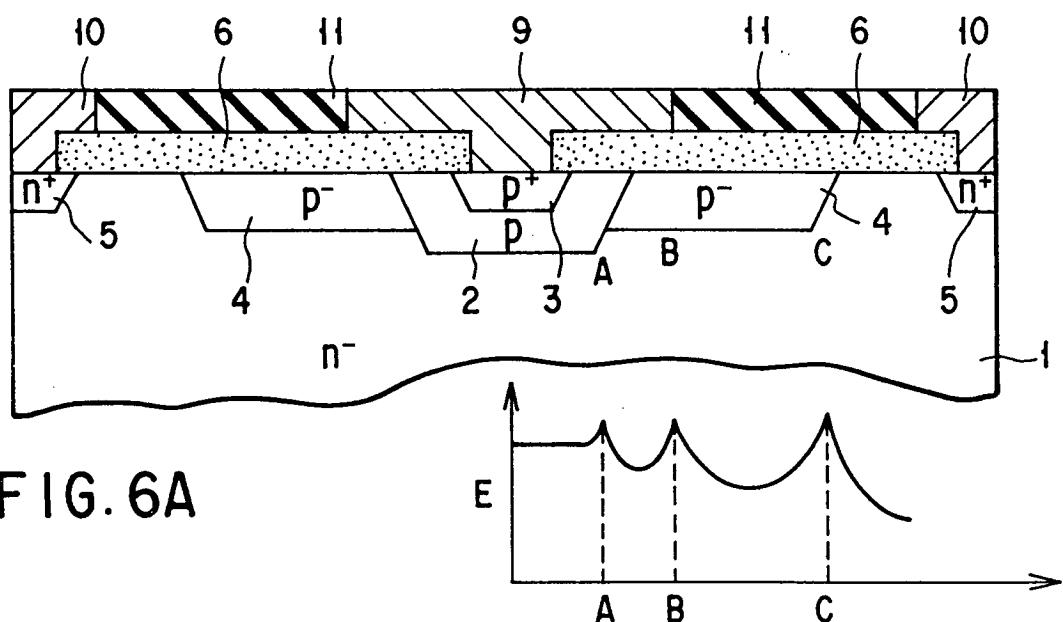

**[0054]** [Fig. 6A](#) eine Schnittansicht einer Hochspannungshalbleitervorrichtung, welche eine herkömmliche Auftragsschicht des p-Typs verwendet;

**[0055]** [Fig. 6B](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke in [Fig. 6A](#);

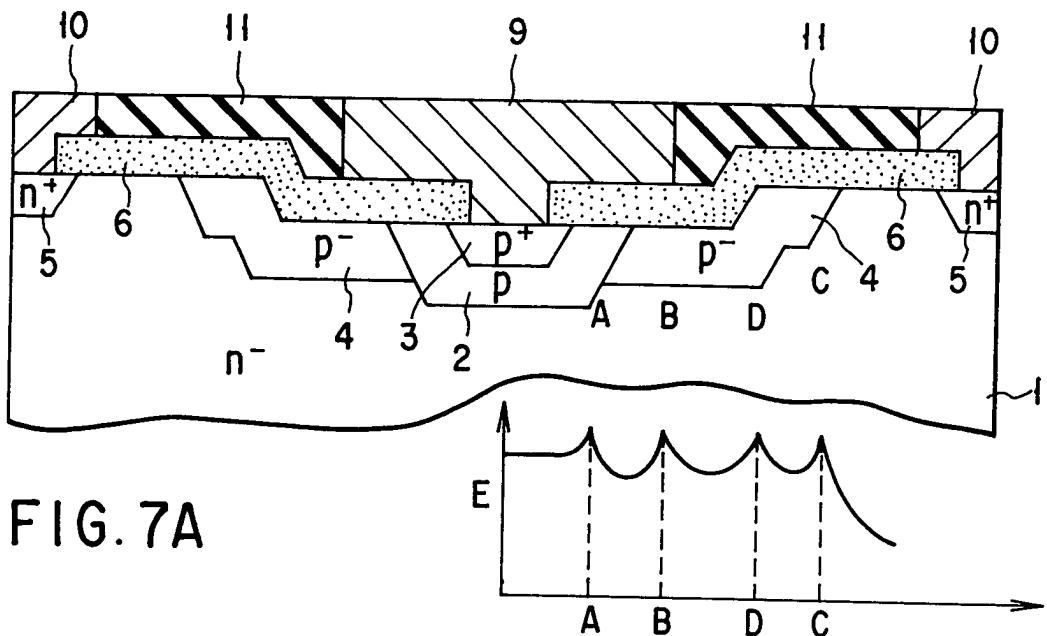

**[0056]** [Fig. 7A](#) eine Schnittansicht zur Erläuterung der Feldverteilung bei der ersten Ausführungsform;

**[0057]** [Fig. 7B](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke in [Fig. 7A](#);

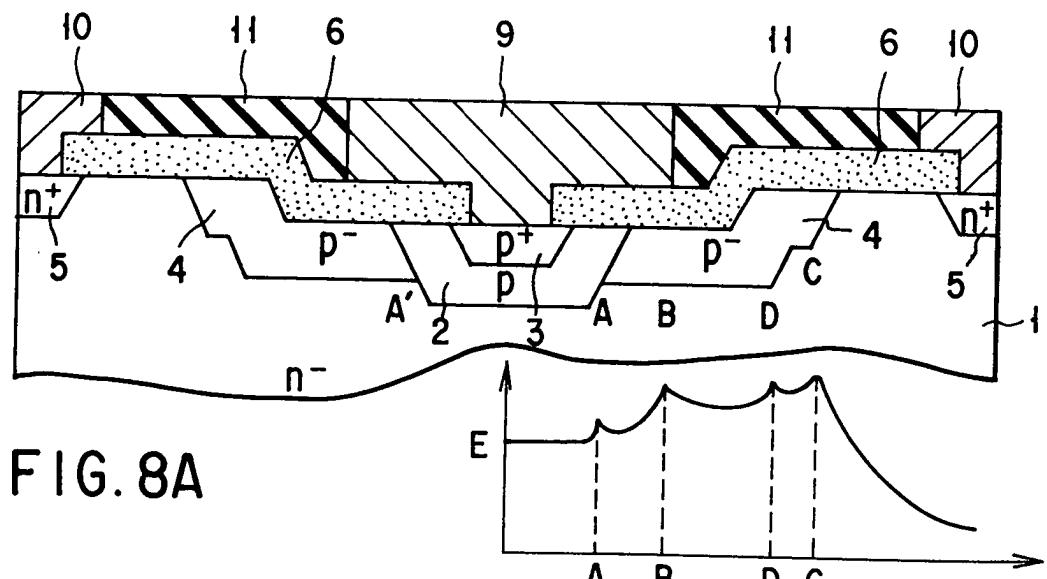

**[0058]** [Fig. 8A](#) eine Schnittansicht der Hochspannungshalbleitervorrichtung, wenn die Tiefe einer Ausnehmung bei der ersten Ausführungsform gering ist;

**[0059]** [Fig. 8B](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke in [Fig. 8A](#);

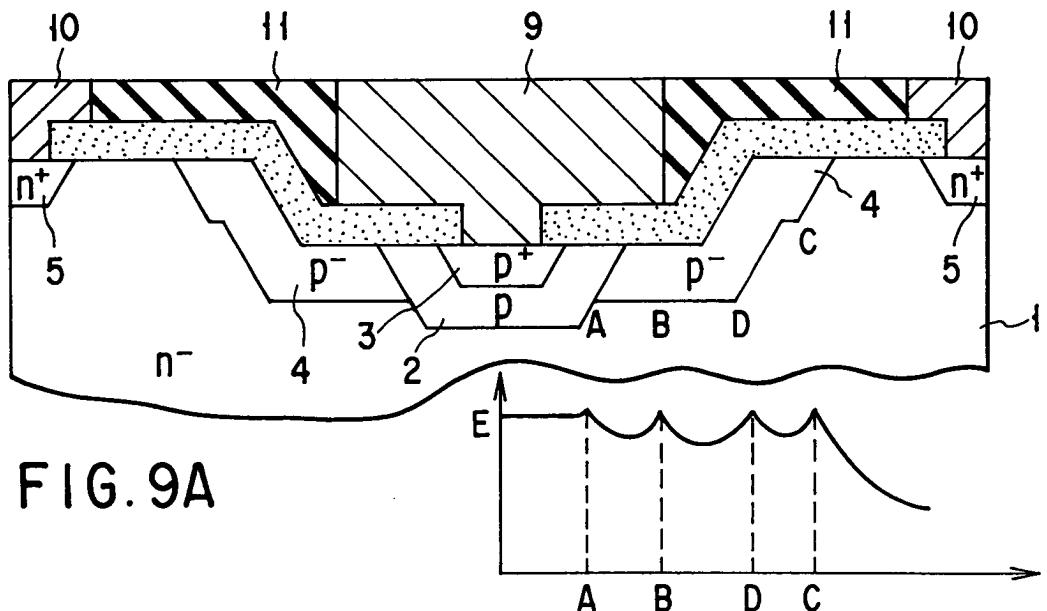

**[0060]** [Fig. 9A](#) eine Schnittansicht der Hochspannungshalbleitervorrichtung, wenn die Tiefe der Ausnehmung bei der ersten Ausführungsform mittelgroß ist;

**[0061]** [Fig. 9B](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke in [Fig. 9A](#);

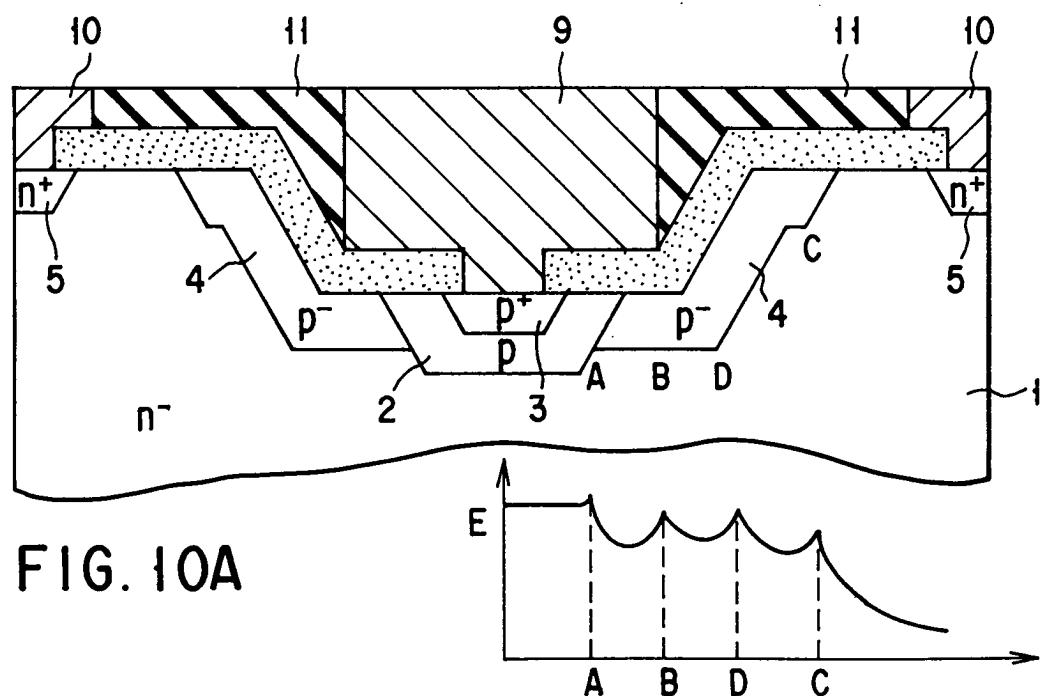

**[0062]** [Fig. 10A](#) eine Schnittansicht der Hochspannungshalbleitervorrichtung, wenn die Tiefe der Ausnehmung bei der ersten Ausführungsform groß ist;

**[0063]** [Fig. 10B](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke in [Fig. 10A](#);

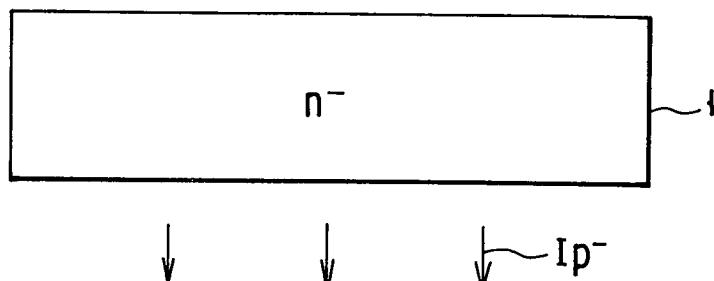

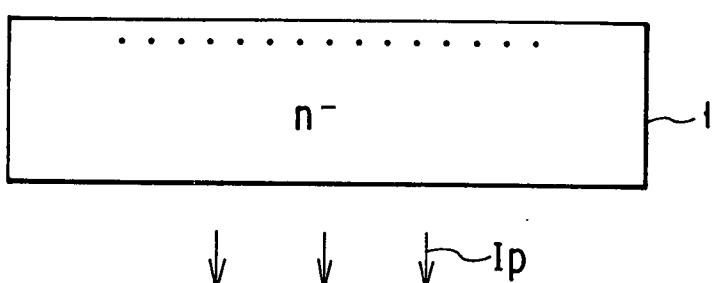

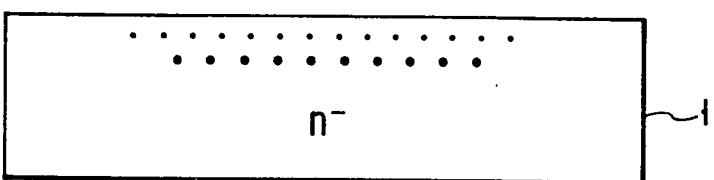

[0064] [Fig. 11A](#) bis [Fig. 11E](#) Schnittansichten, die nacheinander die Schritte eines Verfahrens zur Herstellung des Elementenaufbaus der Ausnehmung bei der ersten Ausführungsform zeigen;

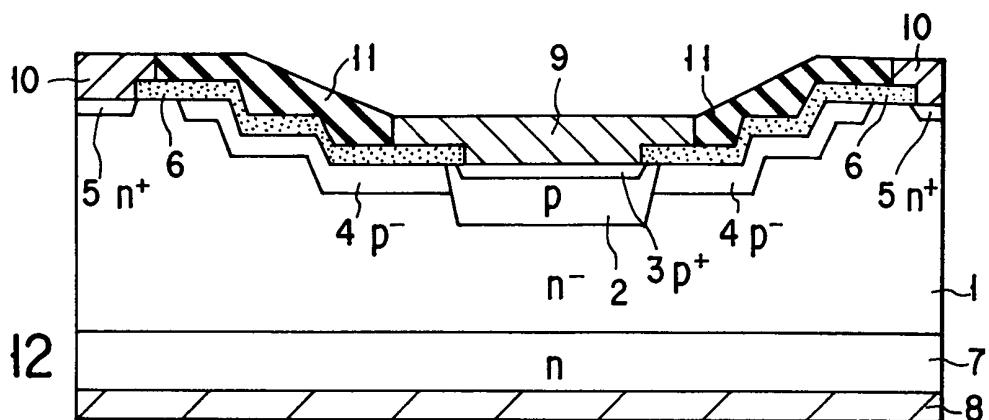

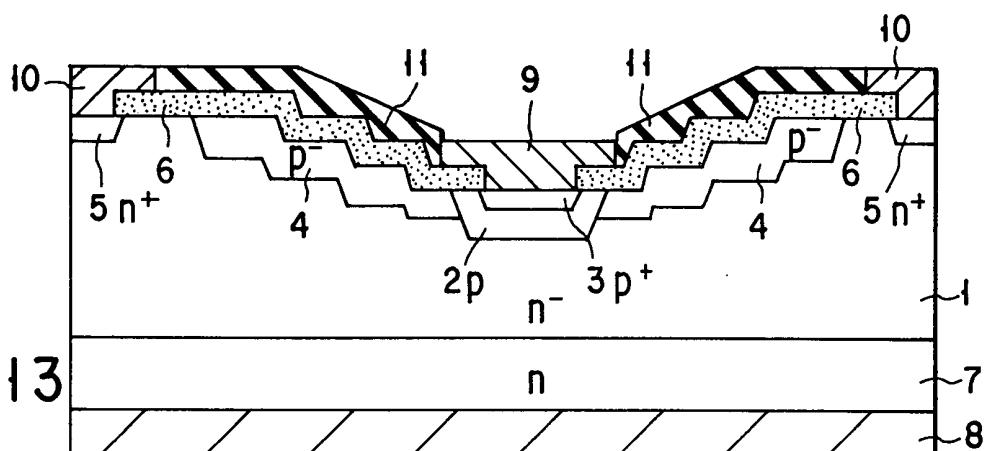

[0065] [Fig. 12](#) eine Schnittansicht mit einer Darstellung einer modifizierten Hochspannungshalbleitervorrichtung gemäß der ersten Ausführungsform;

[0066] [Fig. 13](#) eine Schnittansicht mit einer Darstellung einer Modifikation der Hochspannungshalbleitervorrichtung gemäß der ersten Ausführungsform;

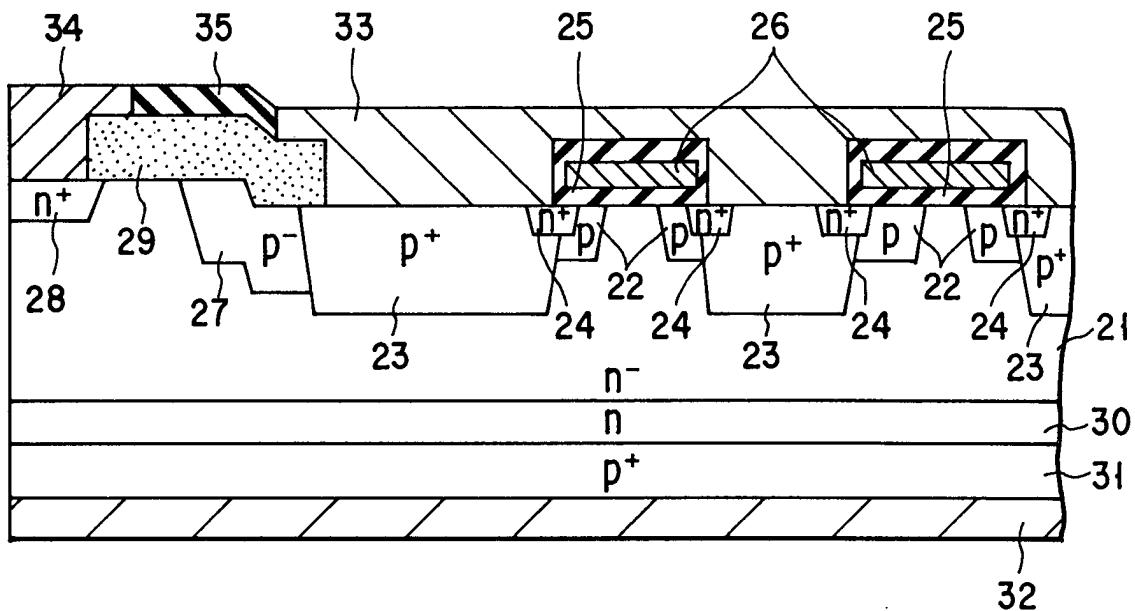

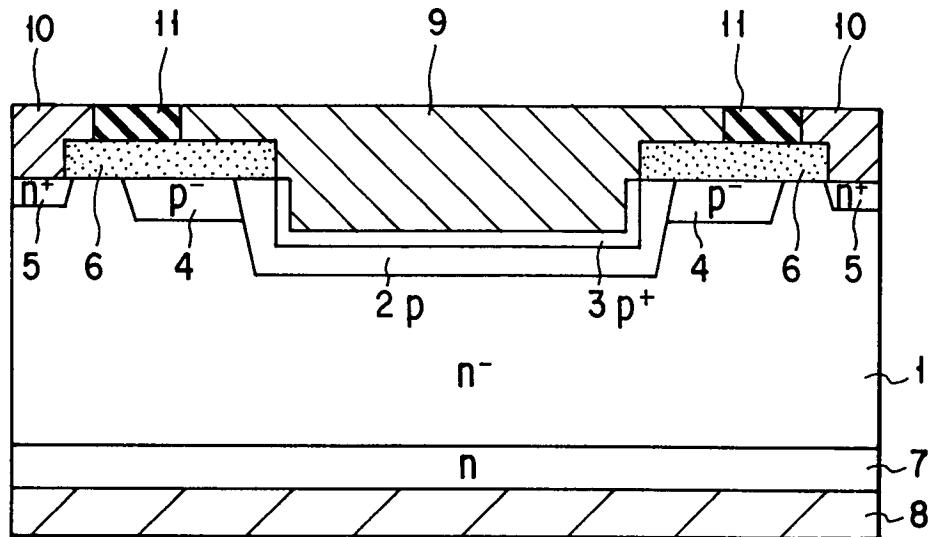

[0067] [Fig. 14](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer zweiten Ausführungsform der vorliegenden Erfindung;

[0068] [Fig. 15](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer dritten Ausführungsform der vorliegenden Erfindung;

[0069] [Fig. 16](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer vierten Ausführungsform der vorliegenden Erfindung;

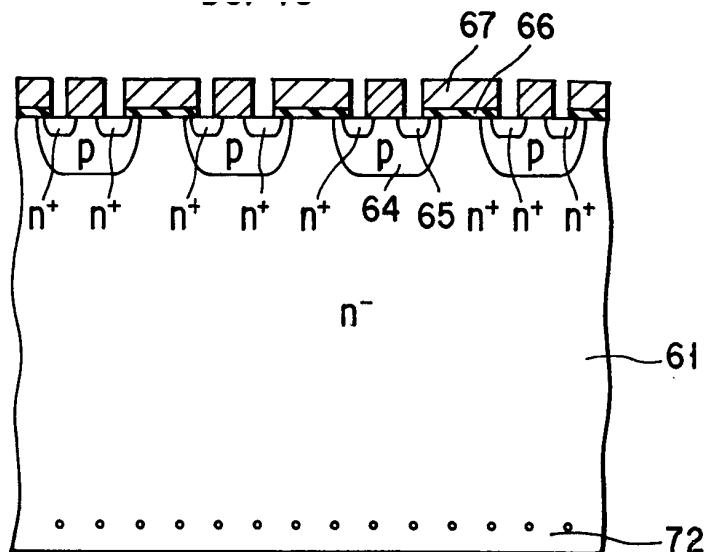

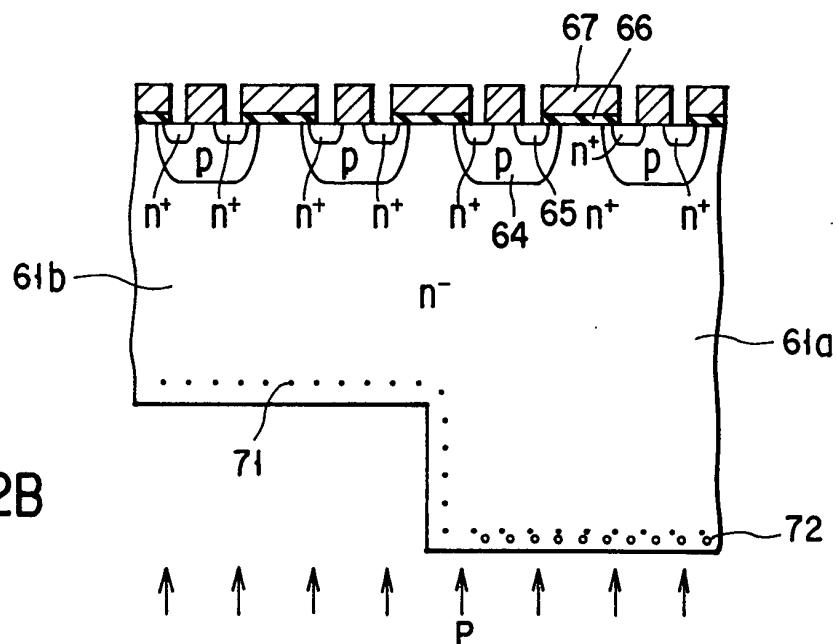

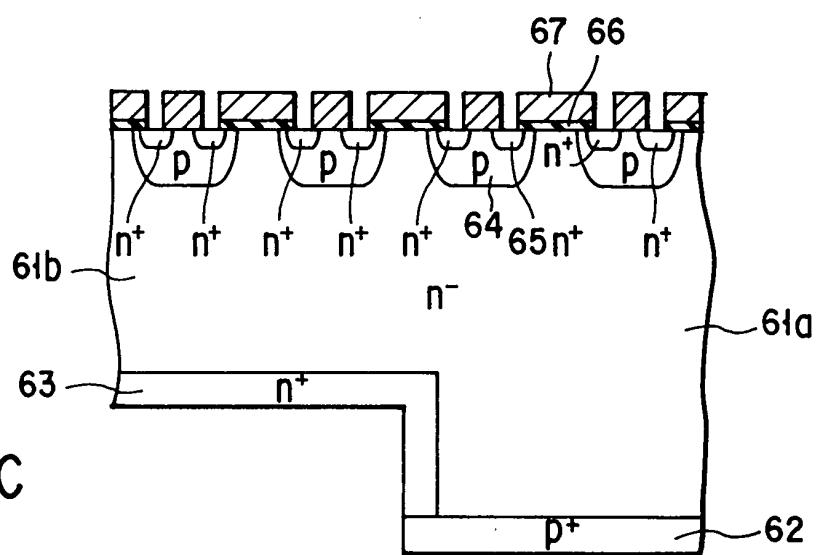

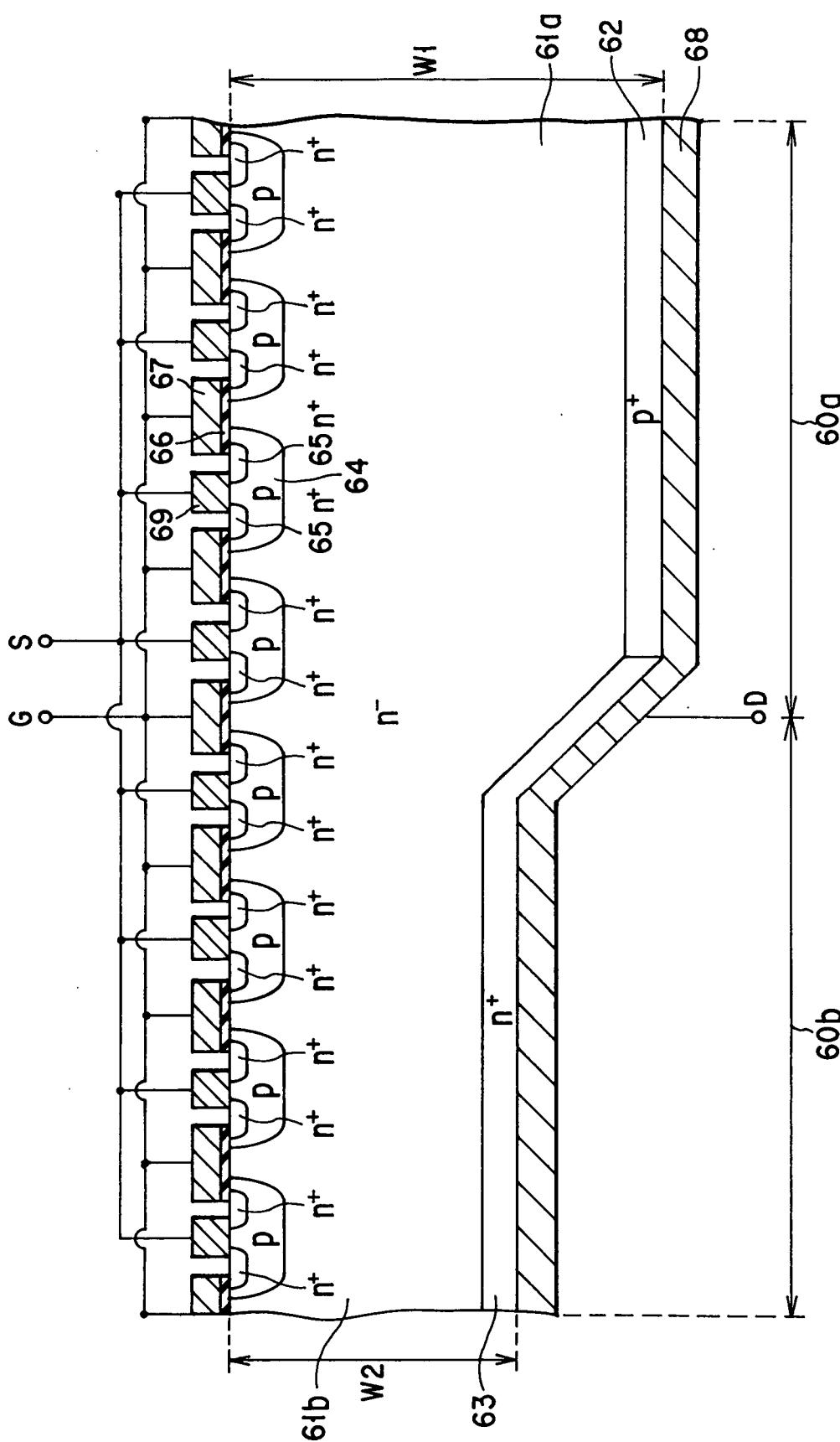

[0070] [Fig. 17](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer fünften Ausführungsform der vorliegenden Erfindung;

[0071] [Fig. 18](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer sechsten Ausführungsform der vorliegenden Erfindung;

[0072] [Fig. 19A](#) bis [Fig. 19E](#) Schnittansichten einer zu Vergleichszwecken herangezogenen Halbleitervorrichtung, in welcher aufeinanderfolgende Schritte bei der Herstellung des Elementenaufbaus der Ausnehmung dargestellt sind;

[0073] [Fig. 20](#) eine Schnittansicht mit einer Darstellung einer Modifizierung der Hochspannungshalbleitervorrichtung gemäß [Fig. 18](#);

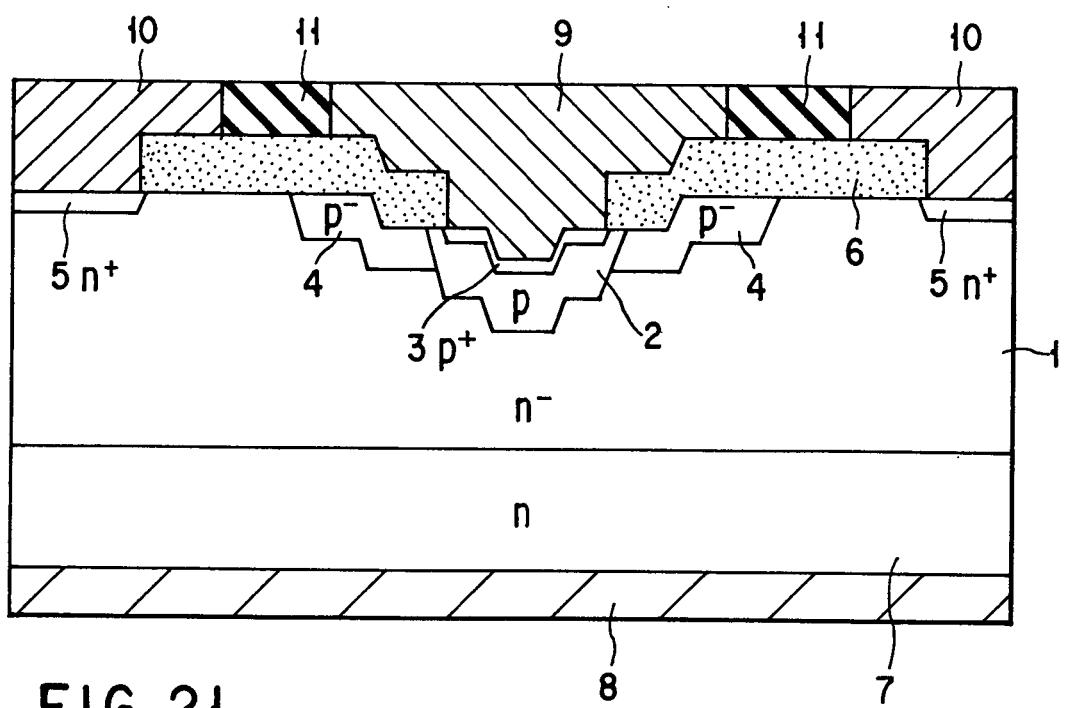

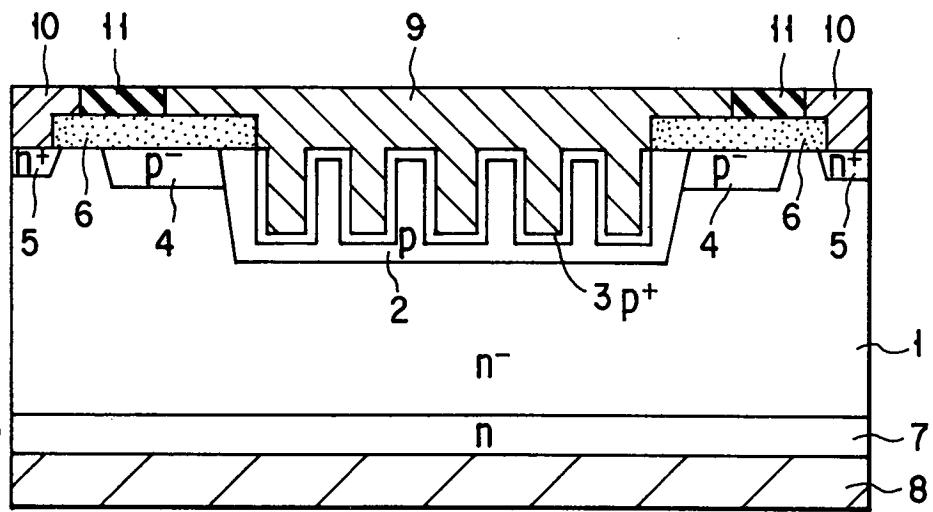

[0074] [Fig. 21](#) eine Schnittansicht einer Hochspannungshalbleitervorrichtung gemäß einer siebten Ausführungsform der vorliegenden Erfindung;

[0075] [Fig. 22](#) eine Schnittansicht des Hauptteils eines Hochspannungshalbleitervorrichtung gemäß einer achtten Ausführungsform der vorliegenden Erfindung;

[0076] [Fig. 23](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer neunten Ausführungsform der vorliegenden Er-

findung;

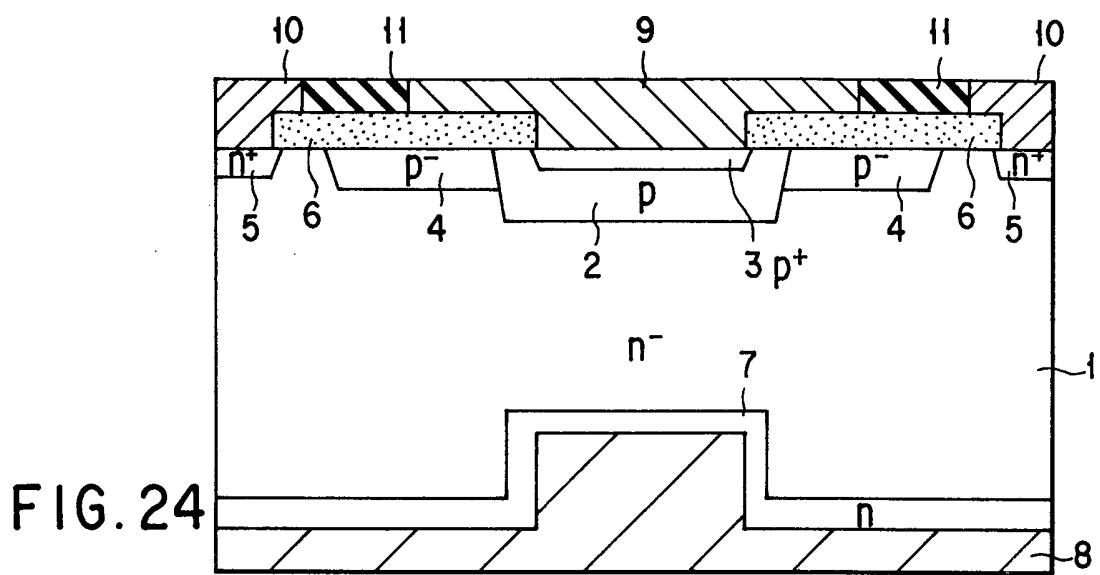

[0077] [Fig. 24](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer zehnten Ausführungsform der vorliegenden Erfindung;

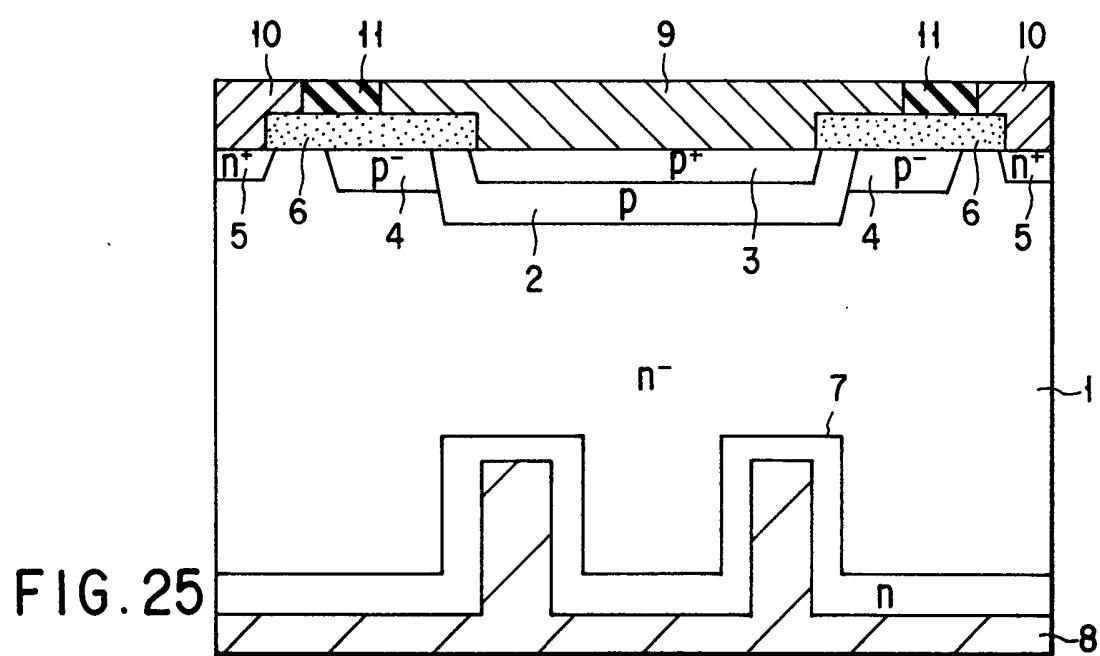

[0078] [Fig. 25](#) eine Schnittansicht einer Modifizierung der Hochspannungshalbleitervorrichtung gemäß [Fig. 24](#);

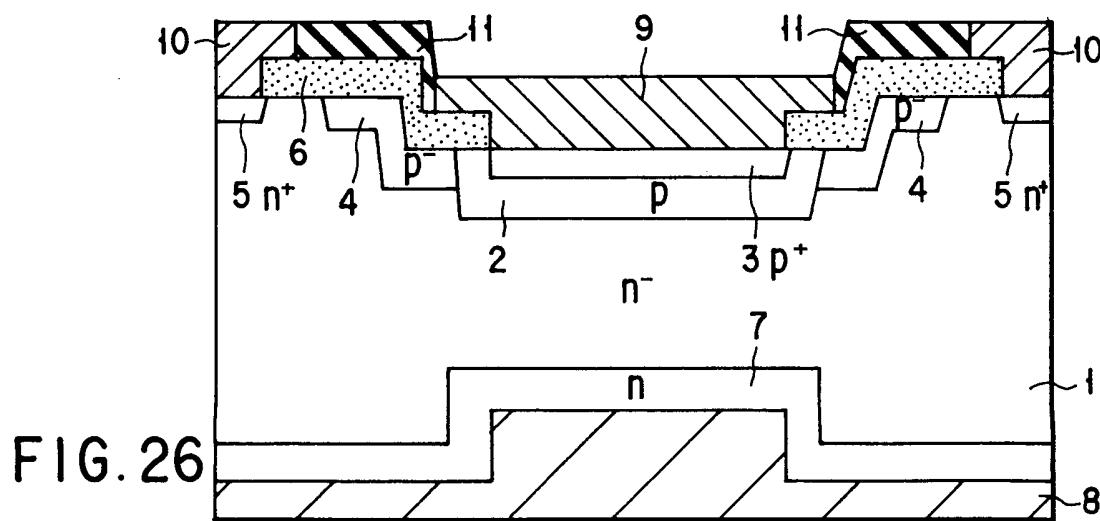

[0079] [Fig. 26](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer elften Ausführungsform der vorliegenden Erfindung;

[0080] [Fig. 27A](#) bis [Fig. 27D](#) Schnittansichten, in denen hintereinander die Schritte eines Verfahrens zur Herstellung des grundlegenden Aufbaus der Hochspannungshalbleitervorrichtung von [Fig. 26](#) gezeigt sind;

[0081] [Fig. 28A](#) bis [Fig. 28E](#) Schnittansichten, in denen nacheinander die Schritte eines anderen Verfahrens zur Herstellung des grundlegenden Aufbaus der Hochspannungshalbleitervorrichtung von [Fig. 26](#) dargestellt sind;

[0082] [Fig. 29A](#) bis [Fig. 29D](#) Schnittansichten, in denen hintereinander die Schritte eines weiteren Verfahrens zur Herstellung des grundlegenden Aufbaus der Hochspannungshalbleitervorrichtung von [Fig. 26](#) dargestellt sind;

[0083] [Fig. 30A](#) bis [Fig. 30E](#) Schnittansichten, in denen hintereinander die Schritte eines weiteren Verfahrens zur Herstellung des grundlegenden Aufbaus der Hochspannungshalbleitervorrichtung von [Fig. 26](#) dargestellt sind;

[0084] [Fig. 31](#) eine Schnittansicht, in welcher der Hauptteil einer Hochspannungshalbleitervorrichtung gemäß einer zwölften Ausführungsform der vorliegenden Erfindung dargestellt ist;

[0085] [Fig. 32A](#) bis [Fig. 32E](#) Schnittansichten, in denen hintereinander die Schritte eines Verfahrens zur Herstellung des Elementenaufbaus einer Ausnehmung in [Fig. 31](#) dargestellt sind;

[0086] [Fig. 33](#) eine Schnittansicht mit einer Darstellung einer Modifikation der Hochspannungshalbleitervorrichtung von [Fig. 31](#);

[0087] [Fig. 34](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer dreizehnten Ausführungsform der vorliegenden Erfindung;

[0088] [Fig. 35](#) eine Schnittansicht des Hauptteils ei-

ner Hochspannungshalbleitervorrichtung gemäß einer vierzehnten Ausführungsform der vorliegenden Erfindung;

[0089] [Fig. 36](#) eine Schnittansicht einer Modifikation der Hochspannungshalbleitervorrichtung von [Fig. 33](#);

[0090] [Fig. 37](#) eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß einer fünfzehnten Ausführungsform der vorliegenden Erfindung;

[0091] [Fig. 38](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer sechzehnten Ausführungsform der vorliegenden Erfindung;

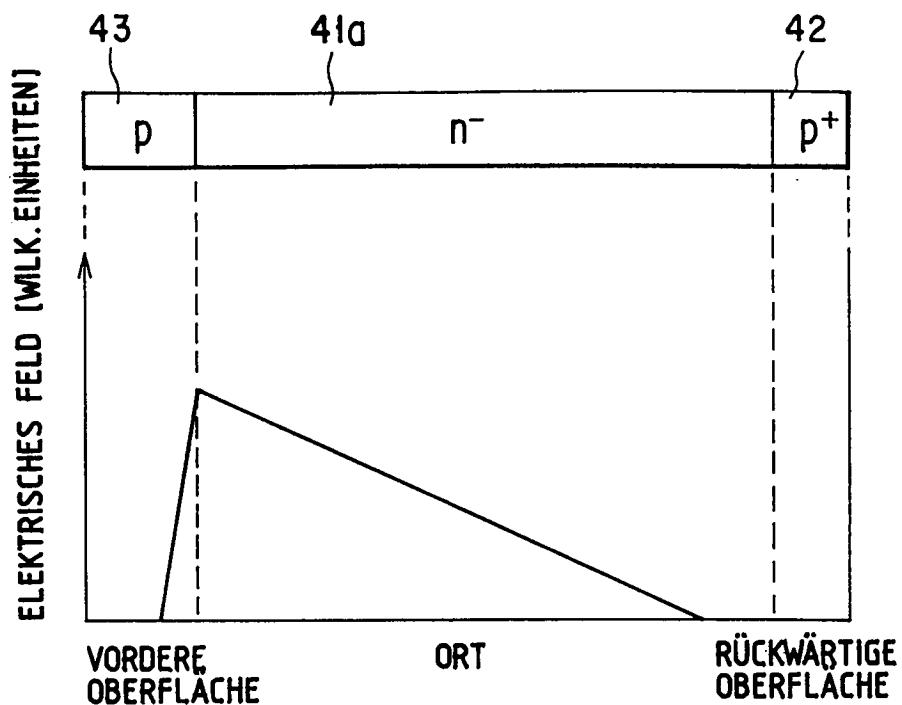

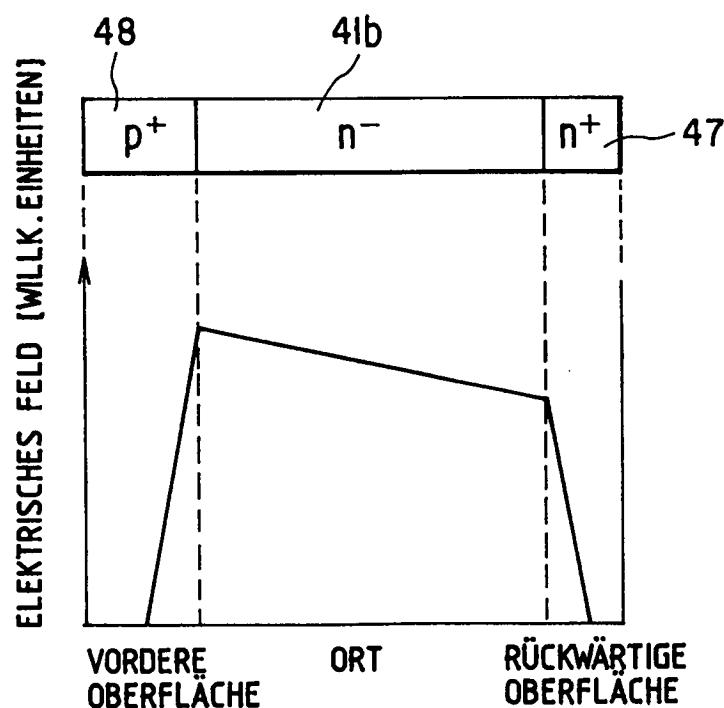

[0092] [Fig. 39A](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke an einem IGBT-Abschnitt in [Fig. 38](#);

[0093] [Fig. 39B](#) ein Diagramm mit einer Darstellung des Profils der Feldstärke an einem Diodenabschnitt in [Fig. 38](#);

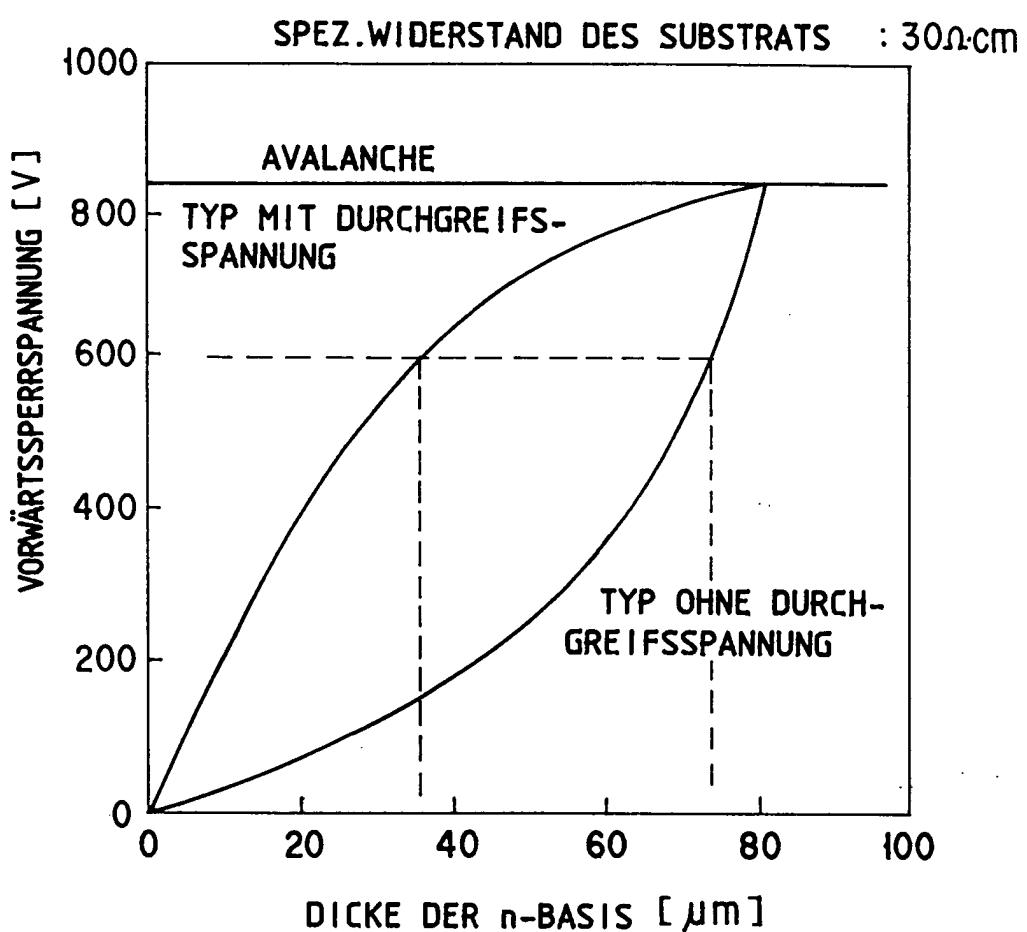

[0094] [Fig. 40](#) ein Diagramm mit einer Darstellung der Vergleichsergebnisse für die Beziehung zwischen der Dicke einer Basisschicht des n-Typs und der Vorwärtssperrspannung bei einem Element mit Durchgreifspannung (z. B. Diode) und einem Element ohne Durchgreifspannung (z. B. IGBT);

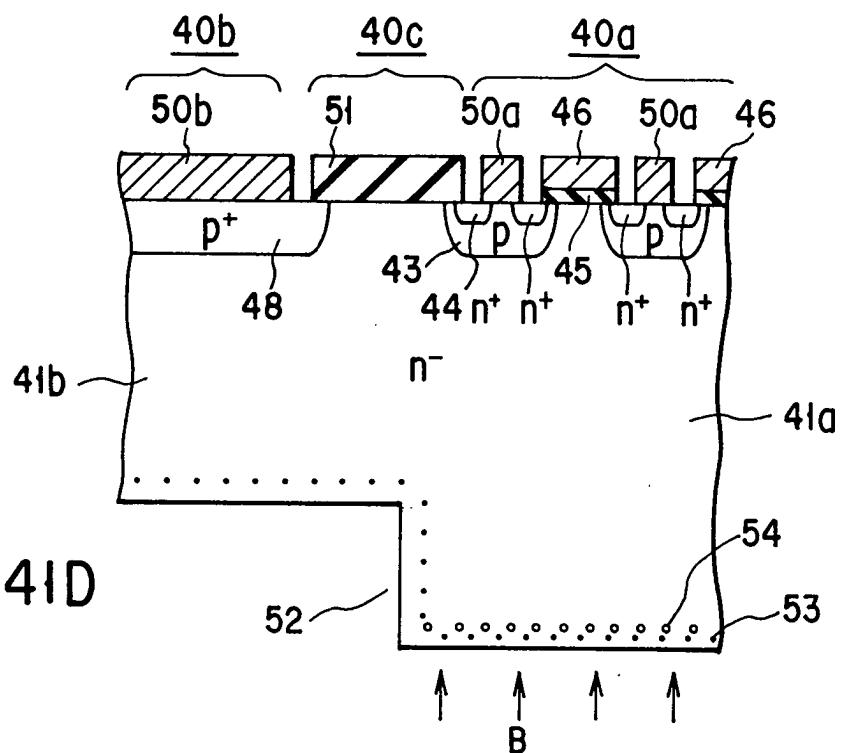

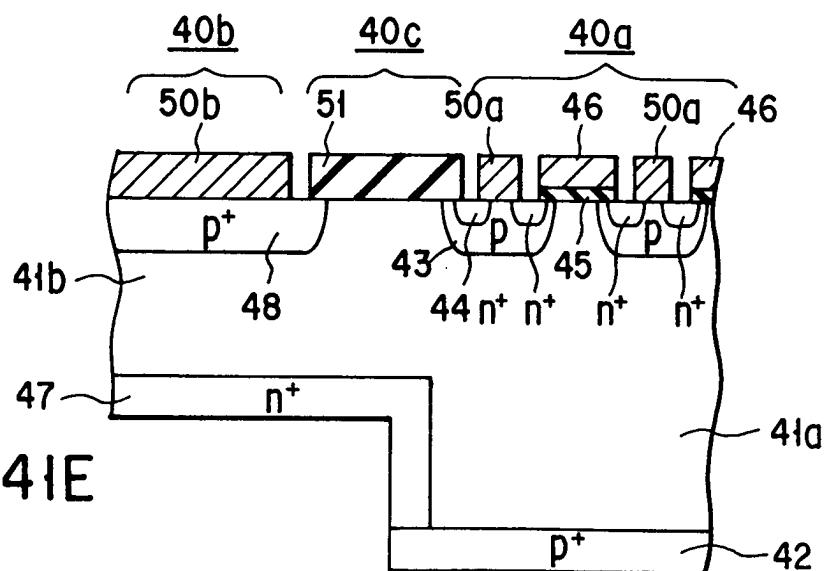

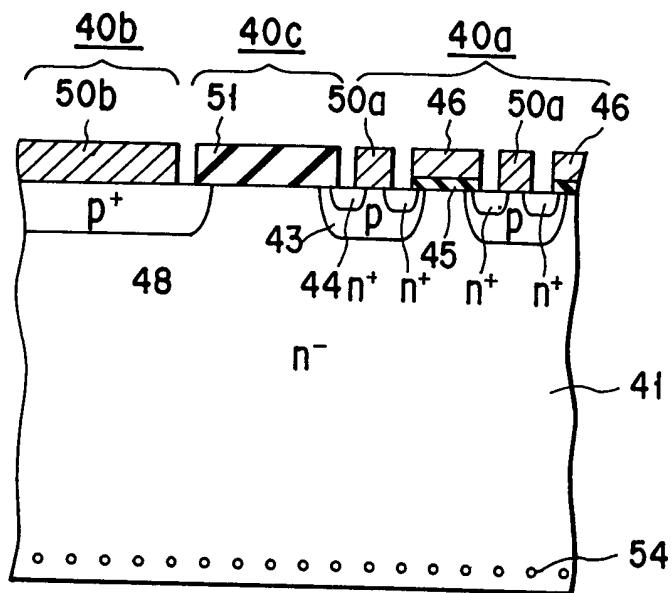

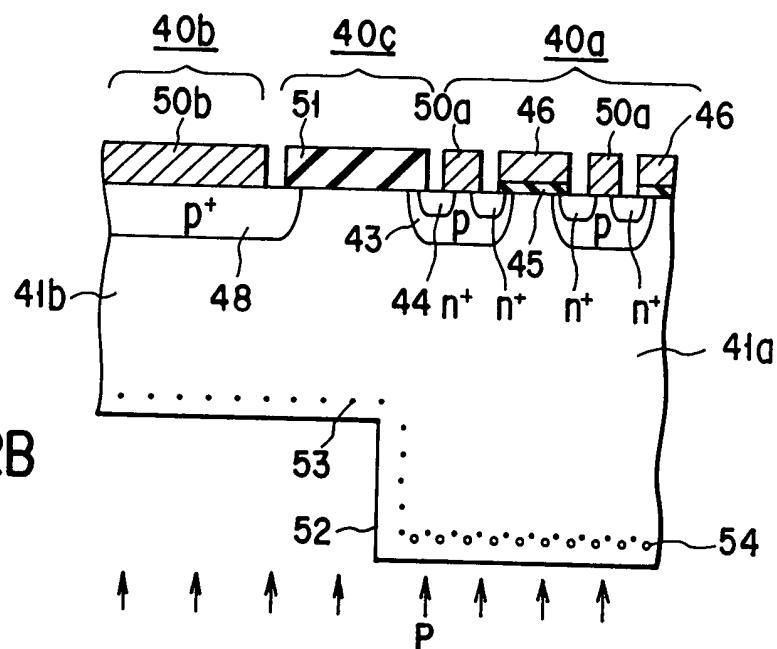

[0095] [Fig. 41A](#) bis [Fig. 41E](#) Schnittansichten, in denen hintereinander die Schritte eines Verfahrens zur Herstellung des grundlegenden Aufbaus der Leistungshalbleitervorrichtung von [Fig. 38](#) dargestellt sind;

[0096] [Fig. 42A](#) bis [Fig. 42C](#) Schnittansichten, in denen hintereinander die Schritte eines anderen Herstellungsverfahrens dargestellt sind, entsprechend [Fig. 41C](#) bis [Fig. 41E](#);

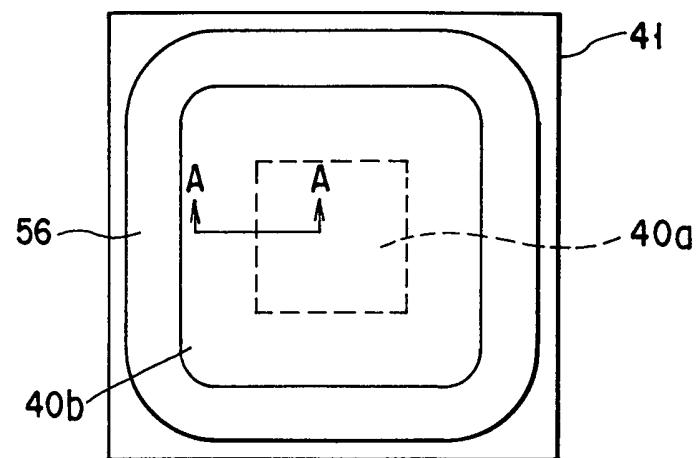

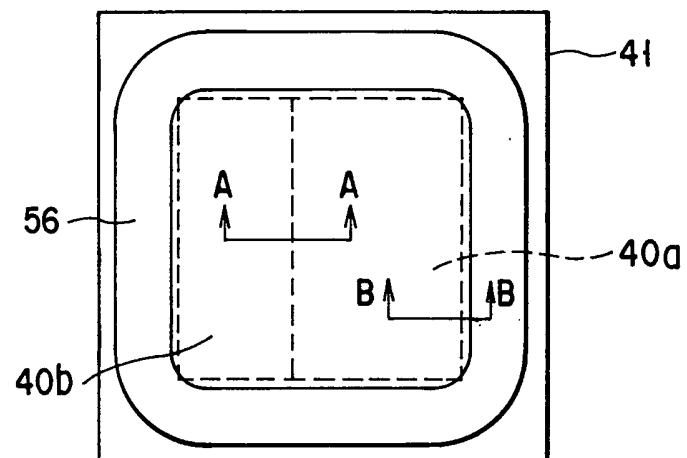

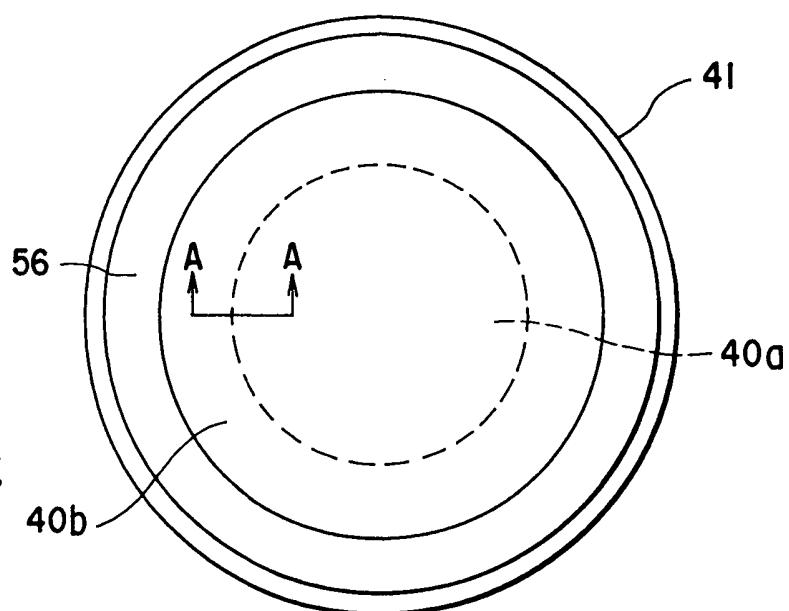

[0097] [Fig. 43A](#) bis [Fig. 43C](#) Ansichten von Beispielen für eine ebene Form der Leistungshalbleitervorrichtung von [Fig. 38](#), wobei [Fig. 38](#) einem Schnitt entlang der Linie A-A in jeder der [Fig. 43A](#) bis [Fig. 43C](#) entspricht;

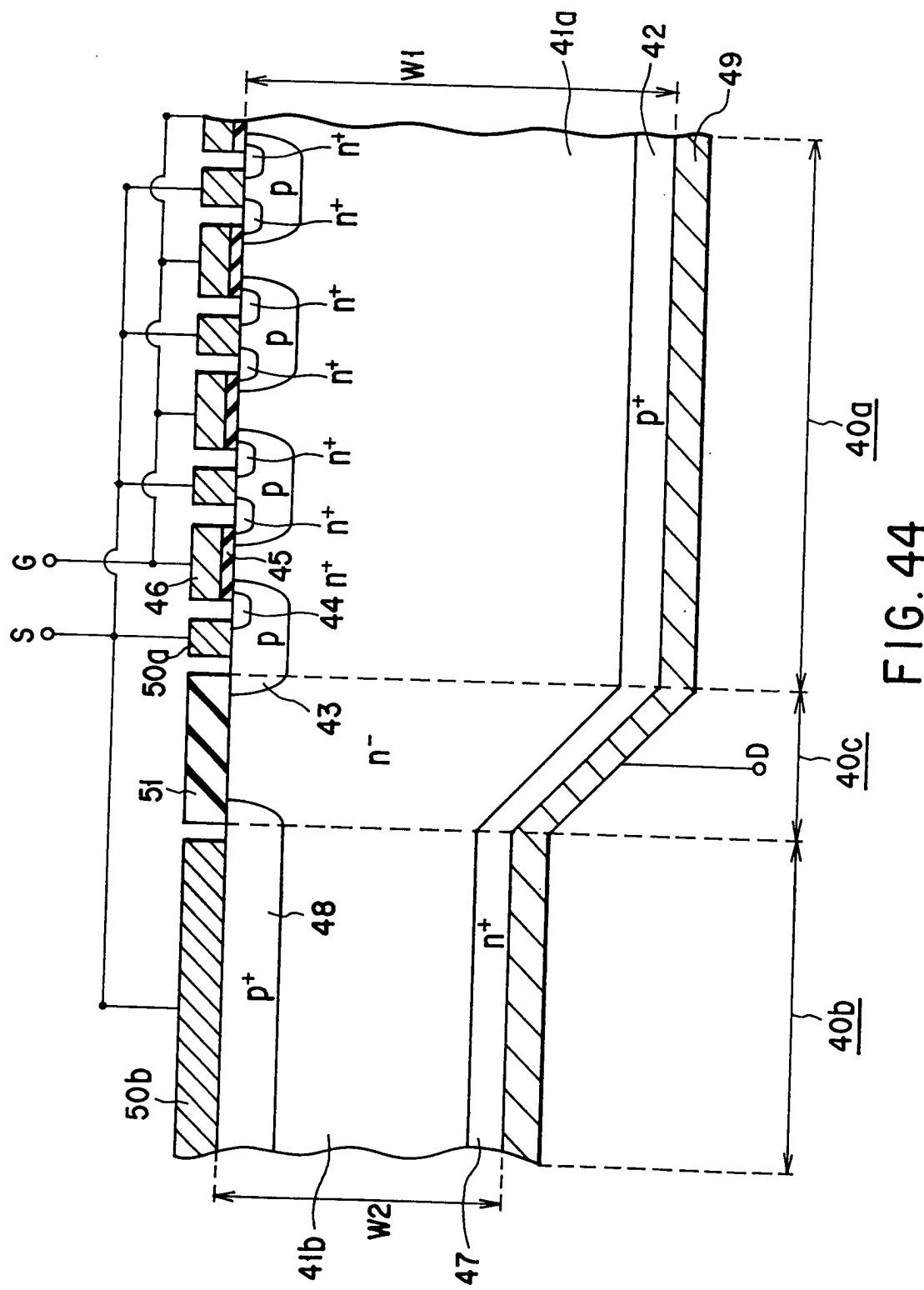

[0098] [Fig. 44](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer siebzehnten Ausführungsform der vorliegenden Erfindung;

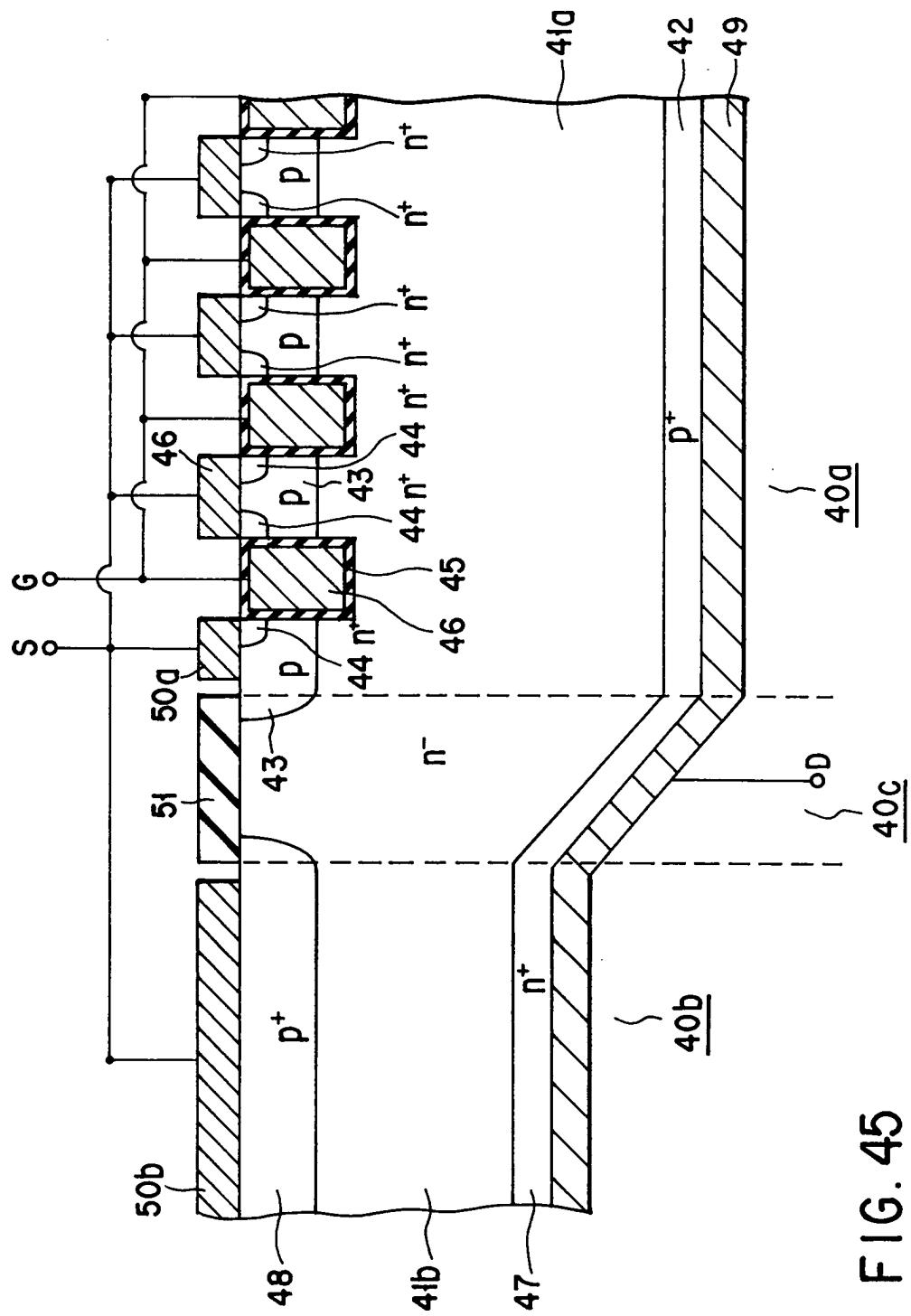

[0099] [Fig. 45](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer achtzehnten Ausführungsform der vorliegenden Erfindung;

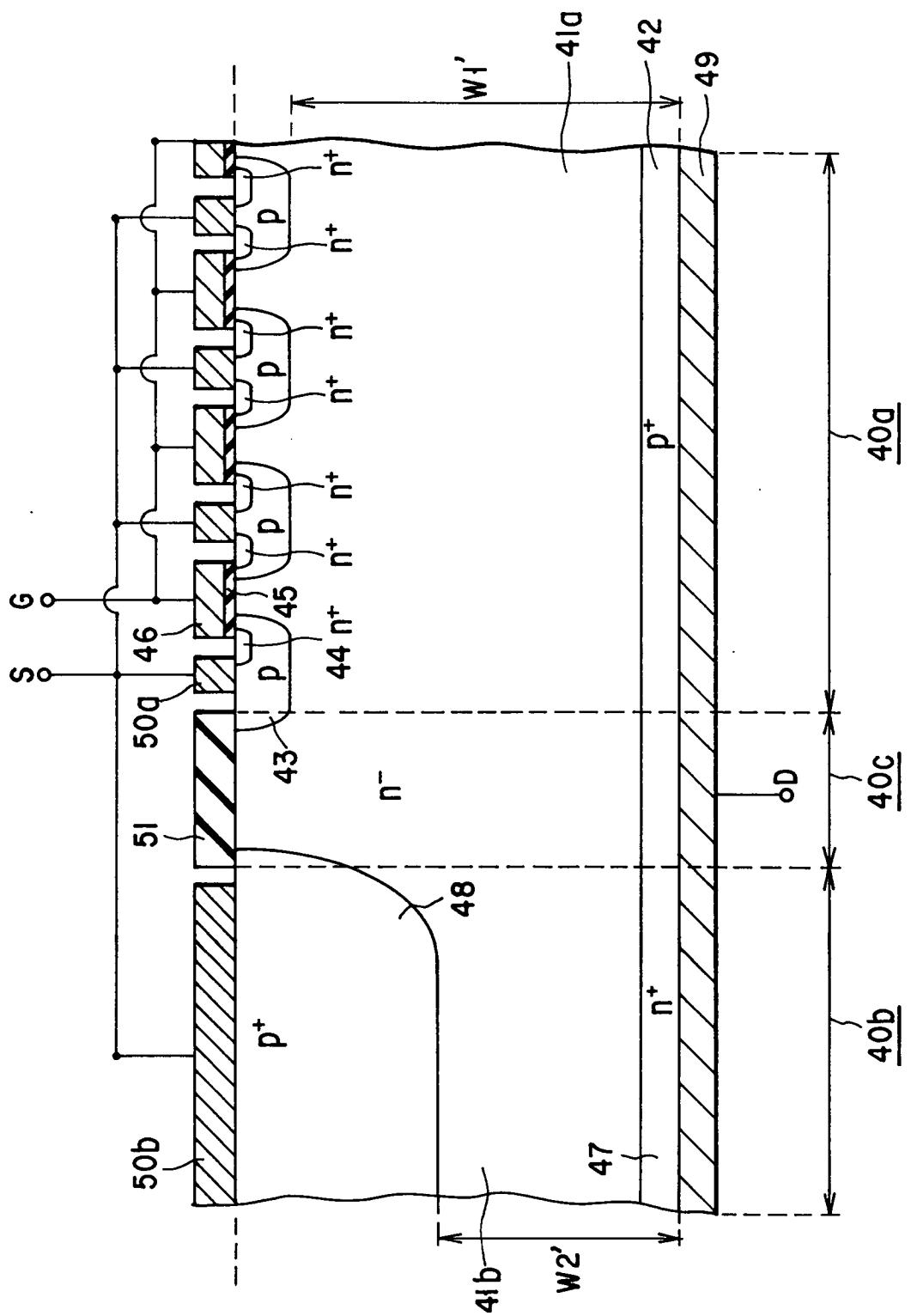

[0100] [Fig. 46](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer neunzehnten Ausführungsform der vorliegenden Erfindung;

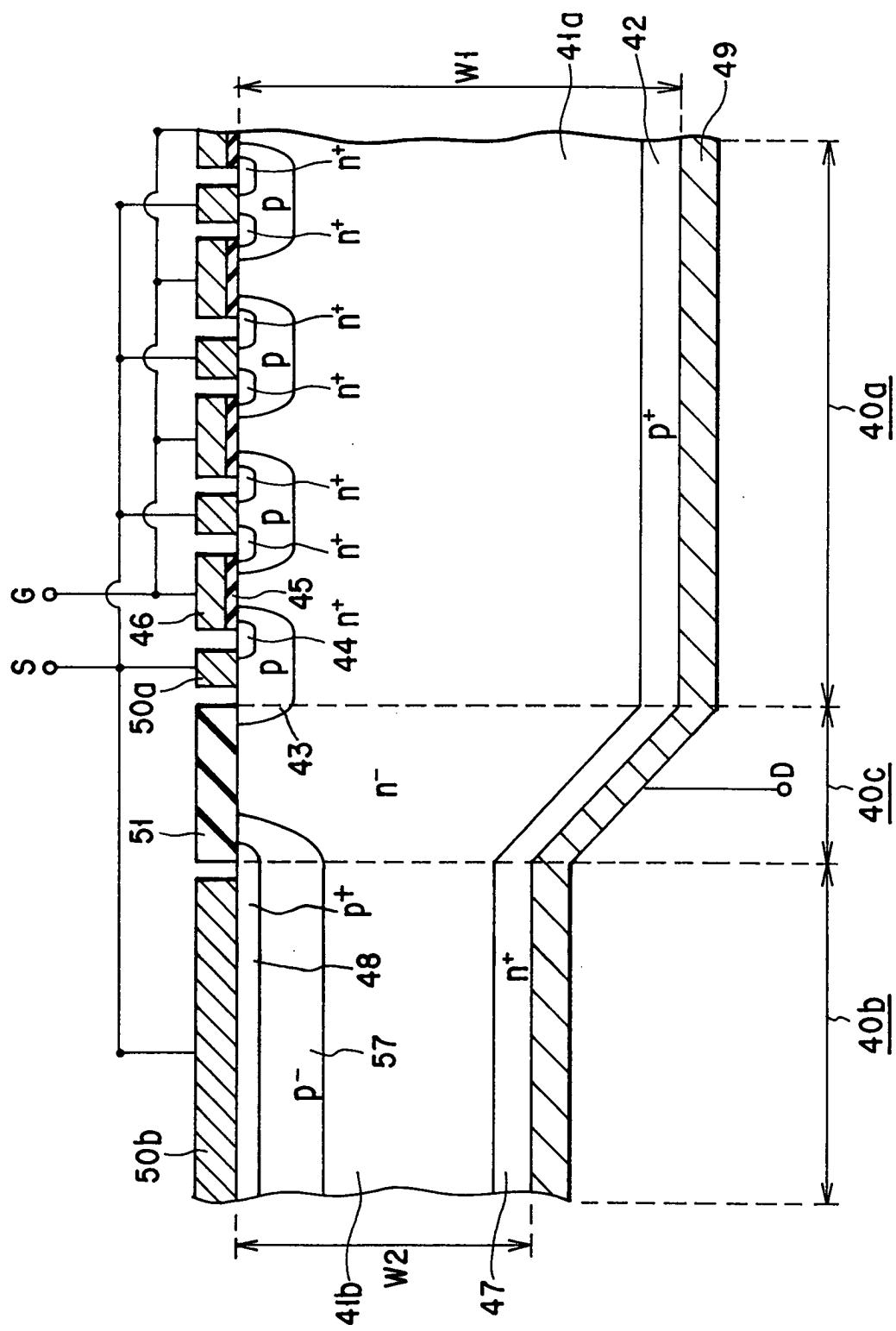

[0101] [Fig. 47](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer zwanzigsten Ausführungsform der vorliegenden Erfindung;

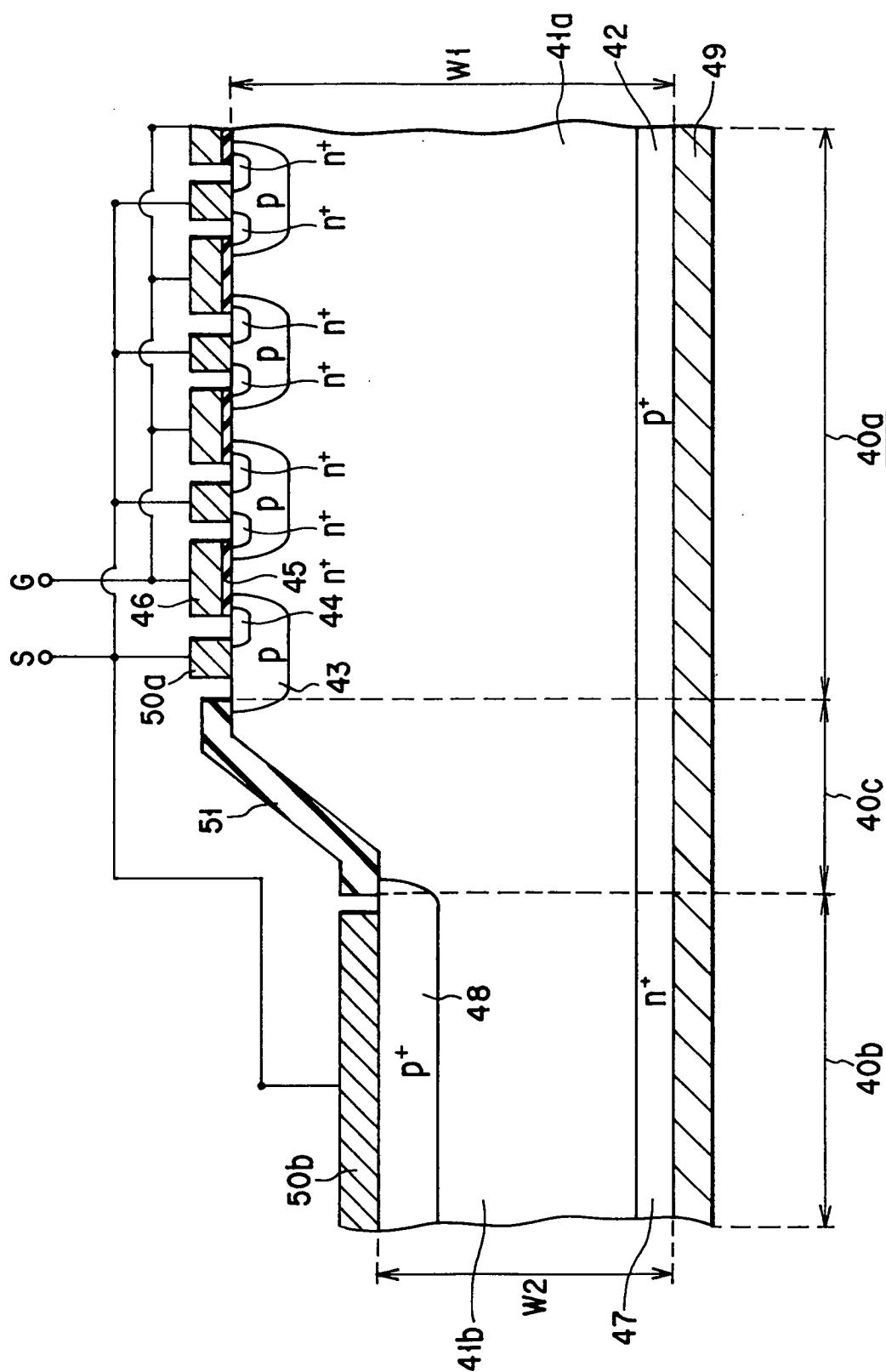

[0102] [Fig. 48](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer ein- und zwanzigsten Ausführungsform der vorliegenden Erfindung;

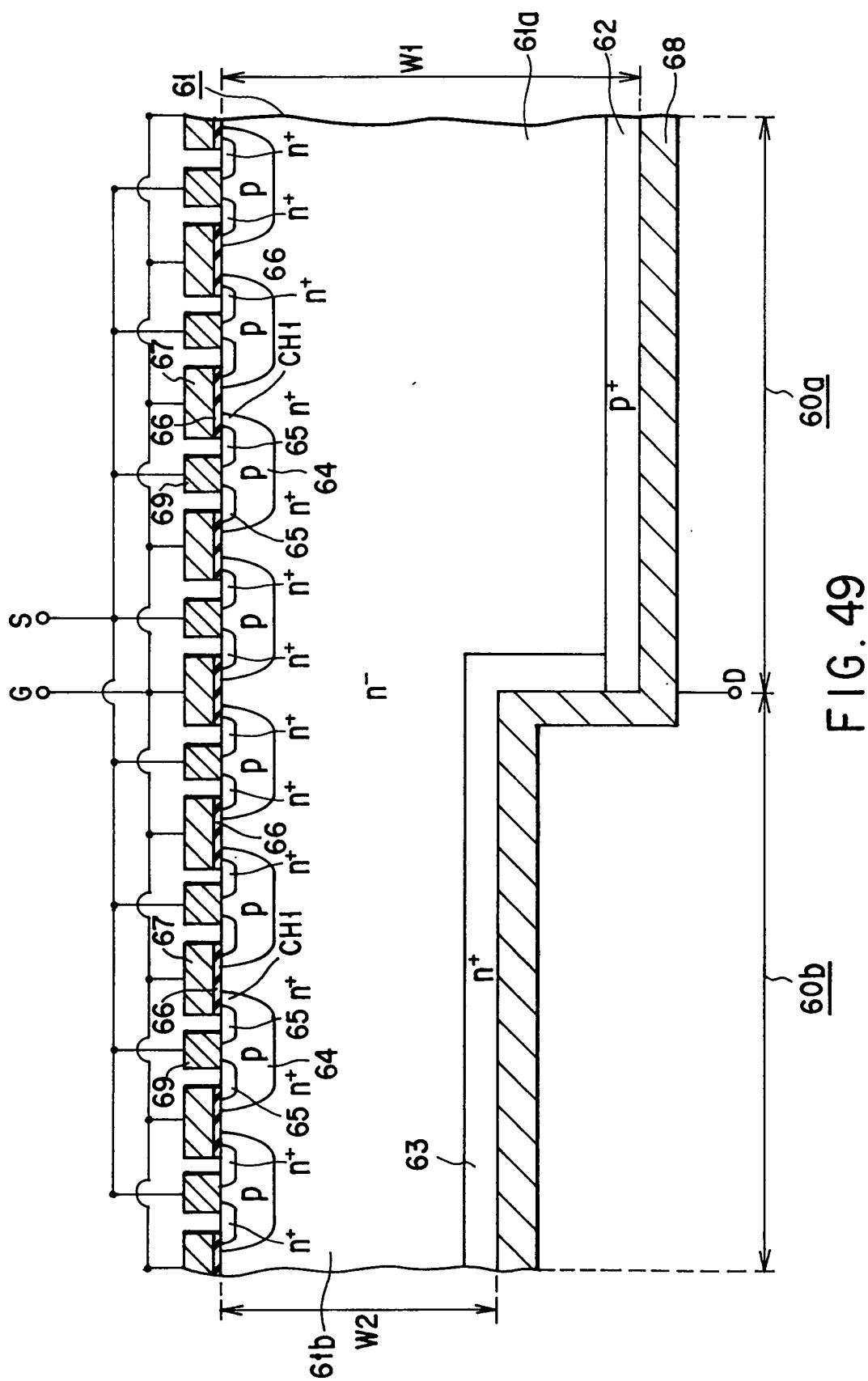

[0103] [Fig. 49](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer zwei- und zwanzigsten Ausführungsform der vorliegenden Erfindung;

[0104] [Fig. 50](#) eine Diagramm zur Erläuterung der Strom/Spannungs-Eigenschaften der Leistungshalbleitervorrichtung von [Fig. 49](#);

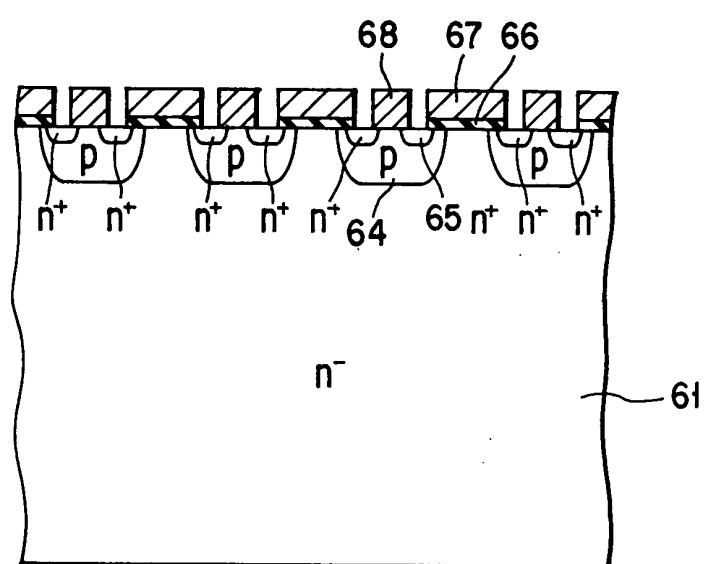

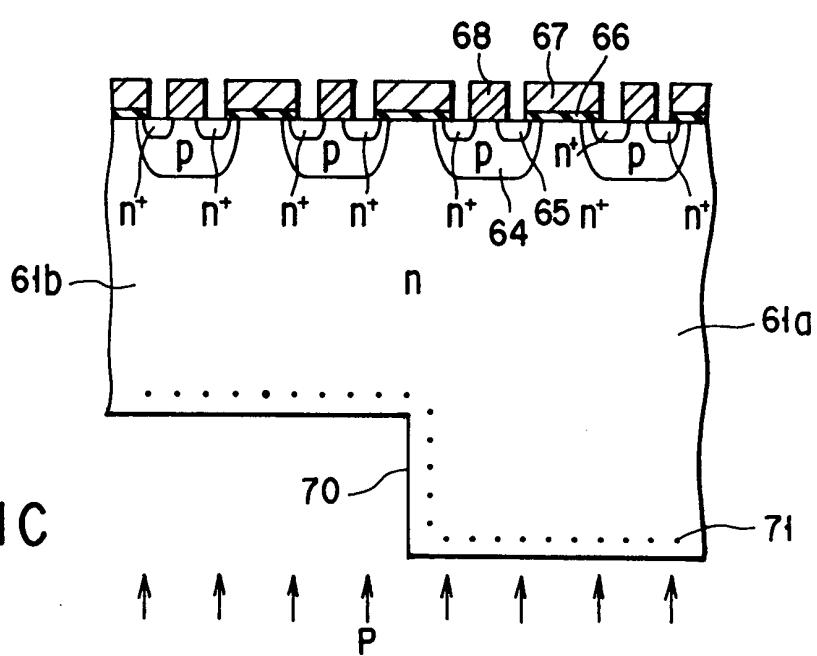

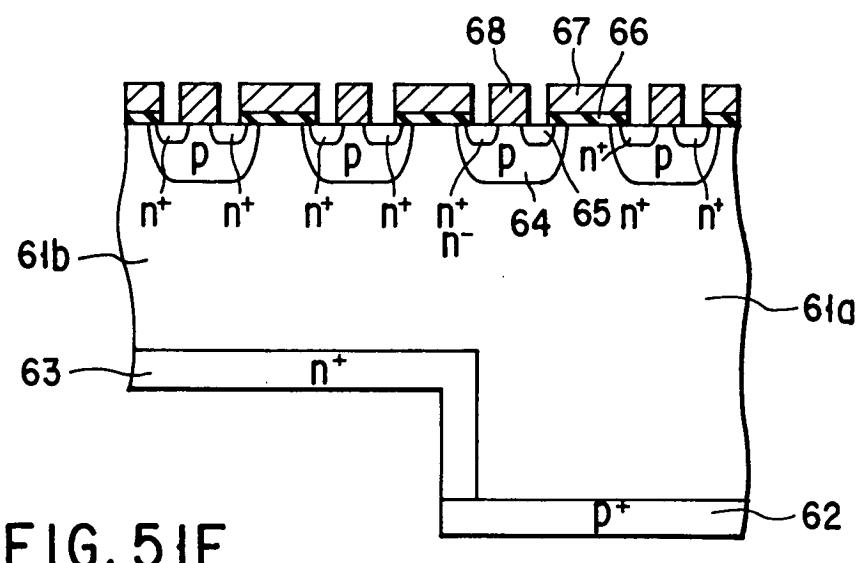

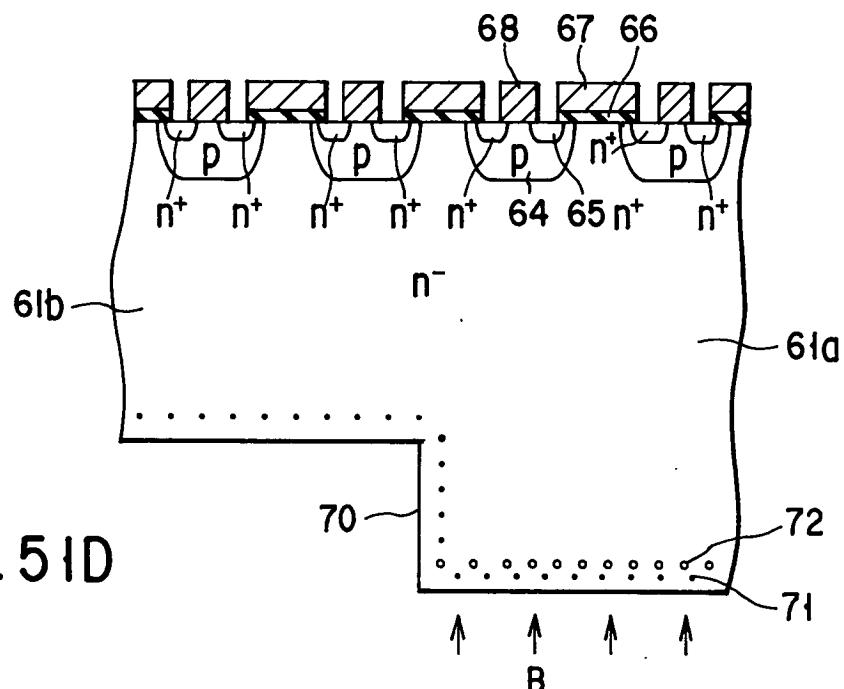

[0105] [Fig. 51A](#) bis [Fig. 51E](#) Schnittansichten, in denen hintereinander die Schritte eines Verfahrens zur Herstellung des grundlegenden Aufbaus der Leistungshalbleitervorrichtung gemäß [Fig. 49](#) dargestellt sind;

[0106] [Fig. 52A](#) bis [Fig. 52C](#) Schnittansichten, in denen hintereinander die Schritte eines weiteren Herstellungsverfahrens entsprechend den [Fig. 51C](#) bis [Fig. 51E](#) dargestellt sind;

[0107] [Fig. 53](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer drei- und zwanzigsten Ausführungsform der vorliegenden Erfindung;

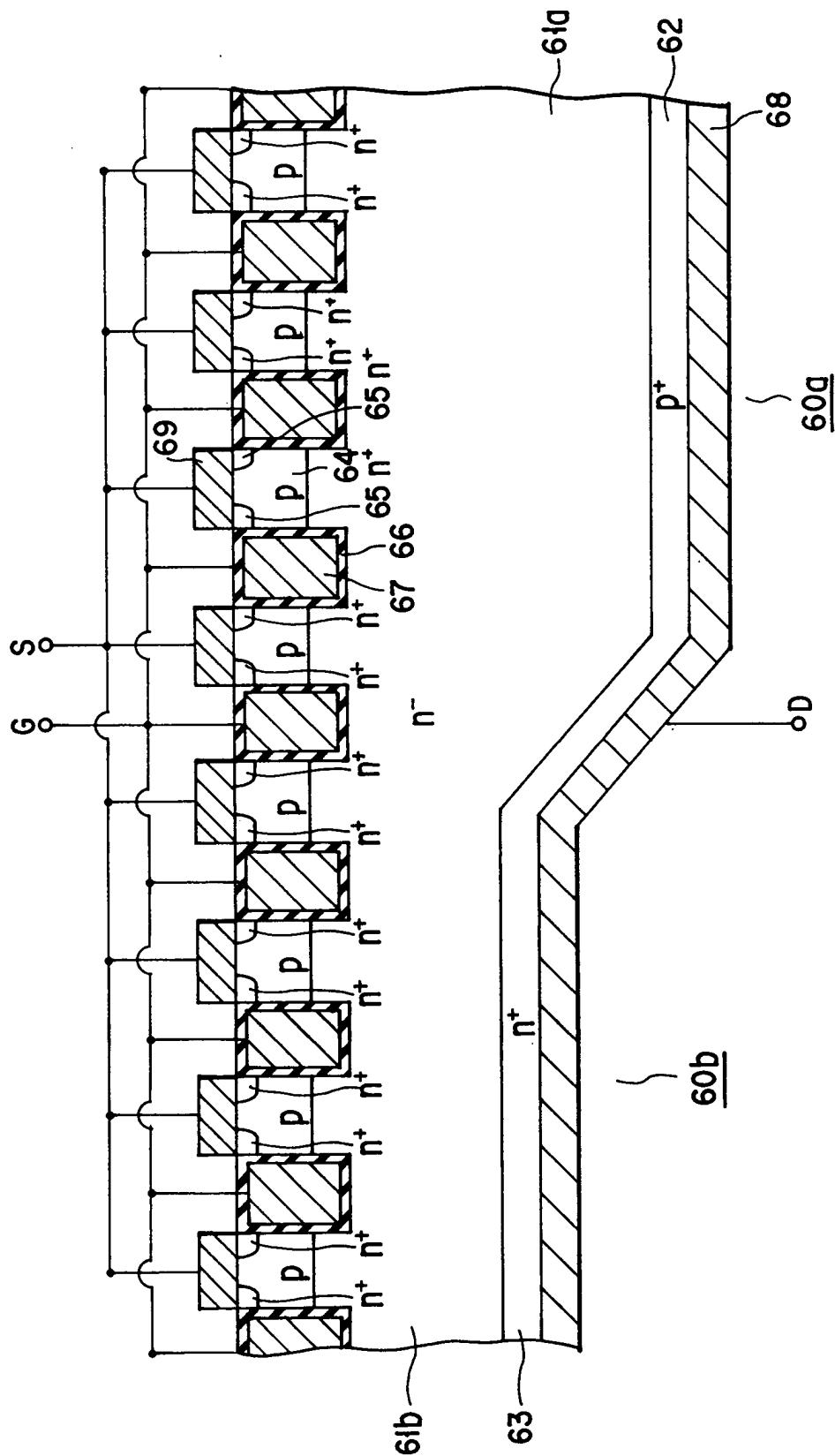

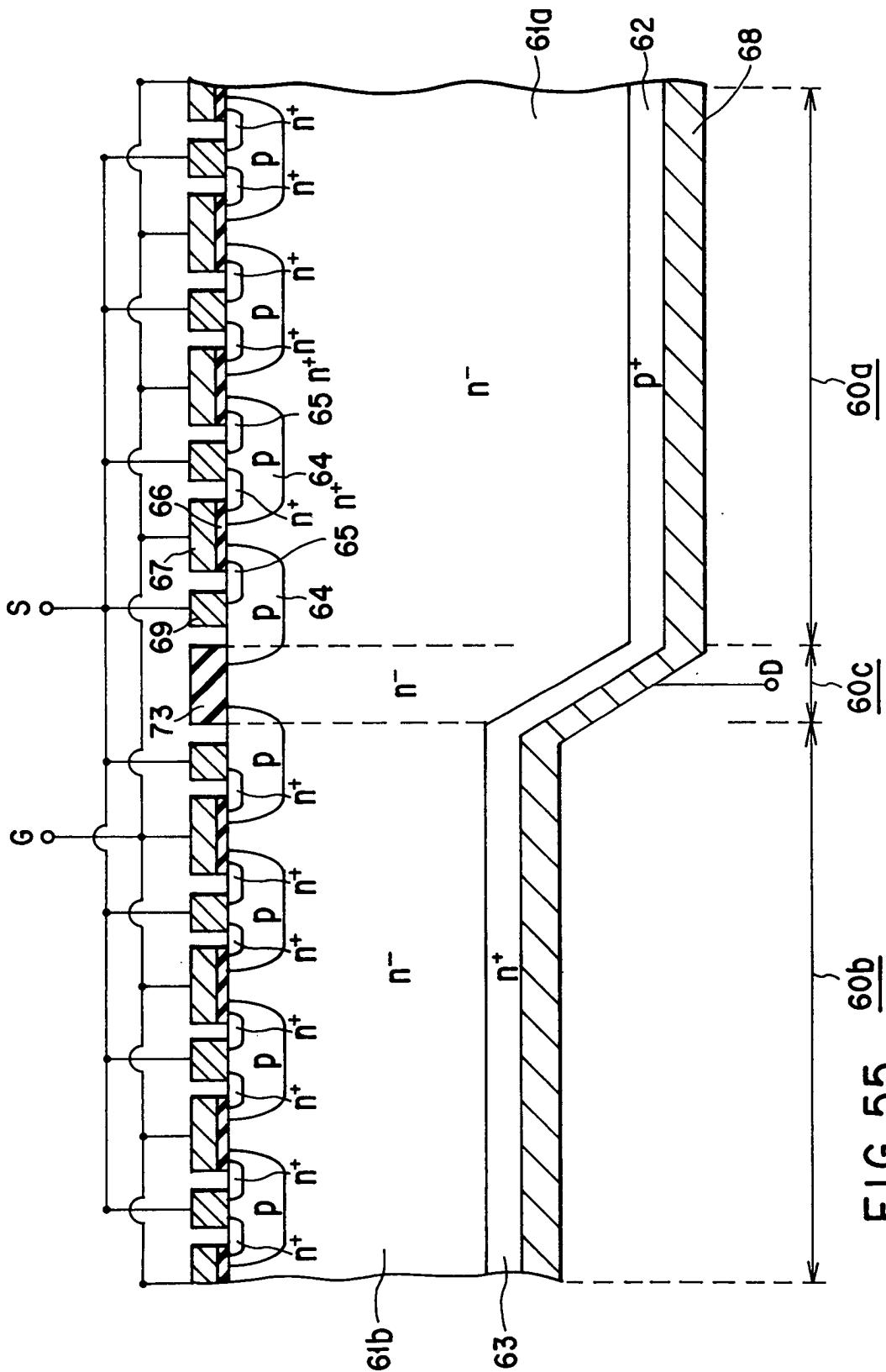

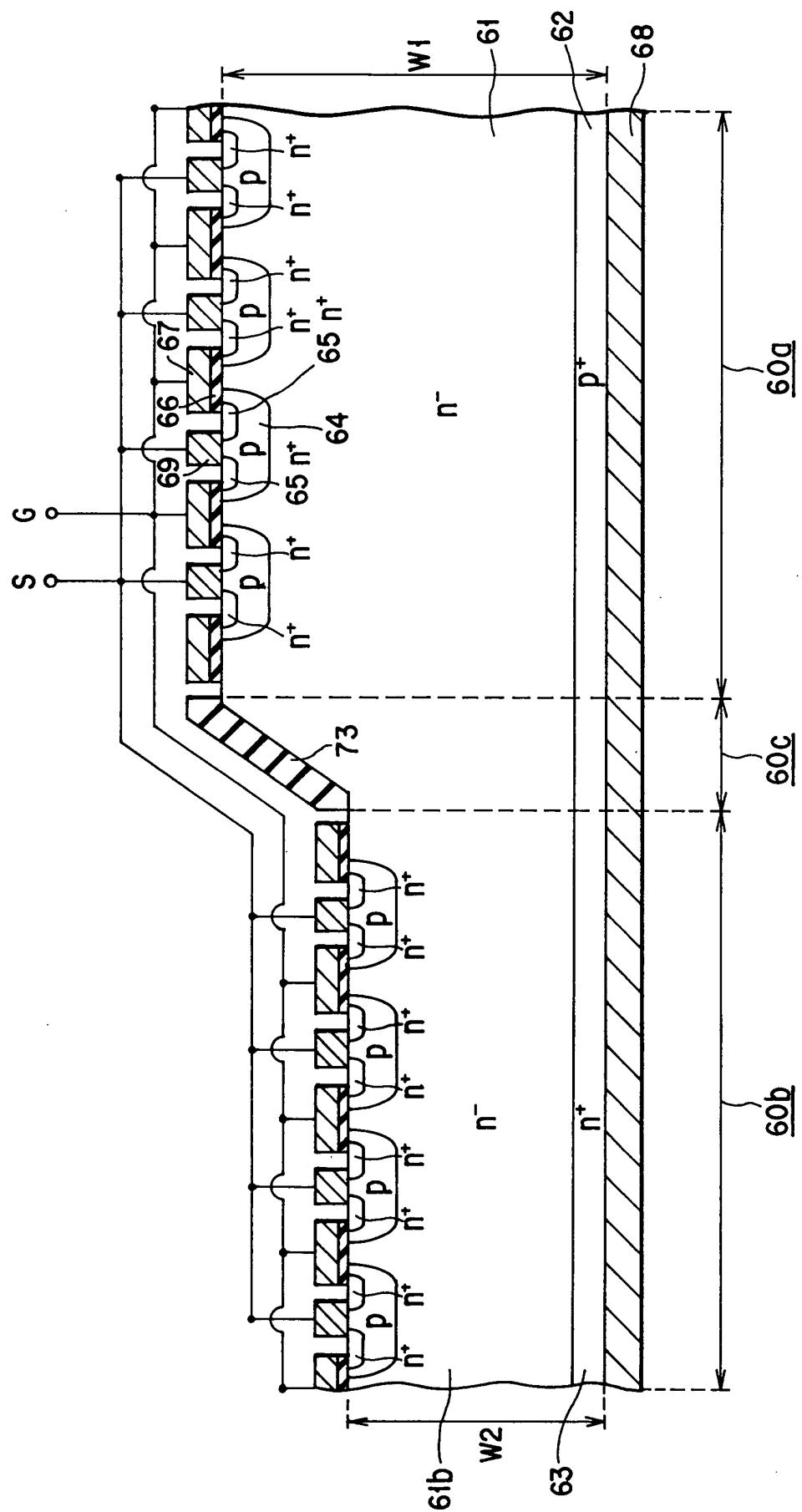

[0108] [Fig. 54](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer vier- und zwanzigsten Ausführungsform der vorliegenden Erfindung;

[0109] [Fig. 55](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer fünf- und zwanzigsten Ausführungsform der vorliegenden Erfindung; und

[0110] [Fig. 56](#) eine Schnittansicht des Hauptteils einer Leistungshalbleitervorrichtung gemäß einer sechsund zwanzigsten Ausführungsform der vorliegenden Erfindung.

[0111] Nachstehend werden Ausführungsformen der vorliegenden Erfindung unter Bezugnahme auf die verschiedenen Darstellungen in den beigefügten Zeichnungen beschrieben.

[0112] Zuerst werden Ausführungsformen (erste bis fünfzehnte Ausführungsform) gemäß einer ersten Zielrichtung der Erfindung erläutert. Bei diesen Ausführungsformen ist der erste Leitfähigkeitstyp ein n-Typ, kann jedoch statt dessen auch ein p-Typ sein. Gleiche Bezugszeichen bezeichnen gleiche oder entsprechende Teile bei den jeweiligen Ausführungsformen, und insoweit erfolgt nicht immer eine Wiederholung entsprechender Beschreibungsteile.

[0113] In der nachfolgenden Beschreibung ist die jeweilige Halbleitervorrichtung auch als Halbleitergerät bezeichnet.

#### Ausführungsbeispiel

##### (ERSTE AUSFÜHRUNGSFORM)

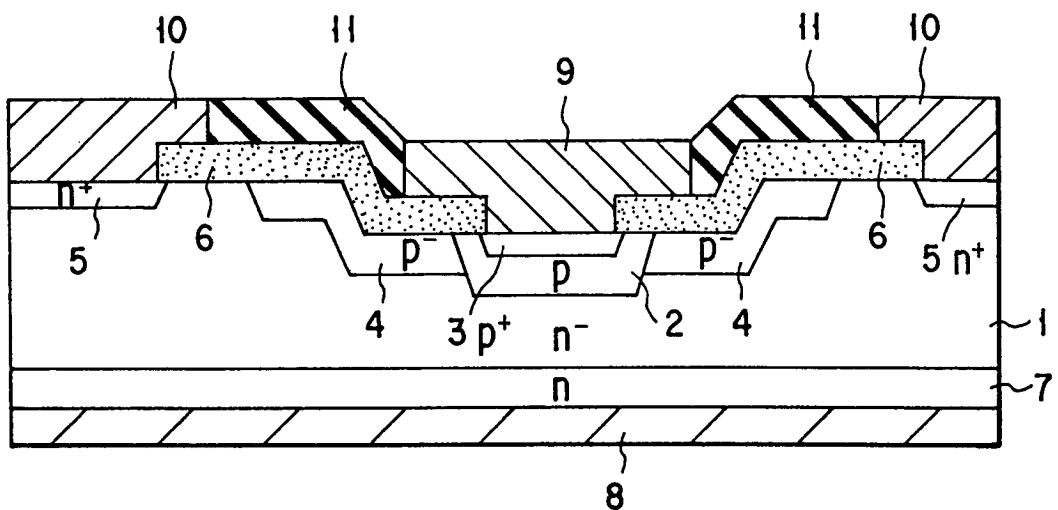

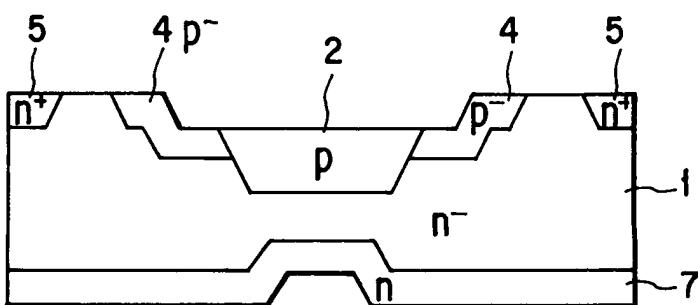

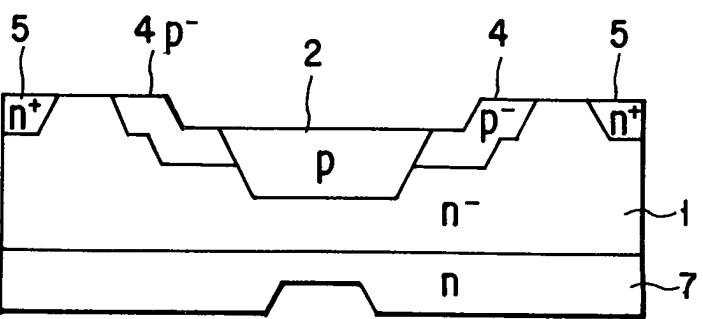

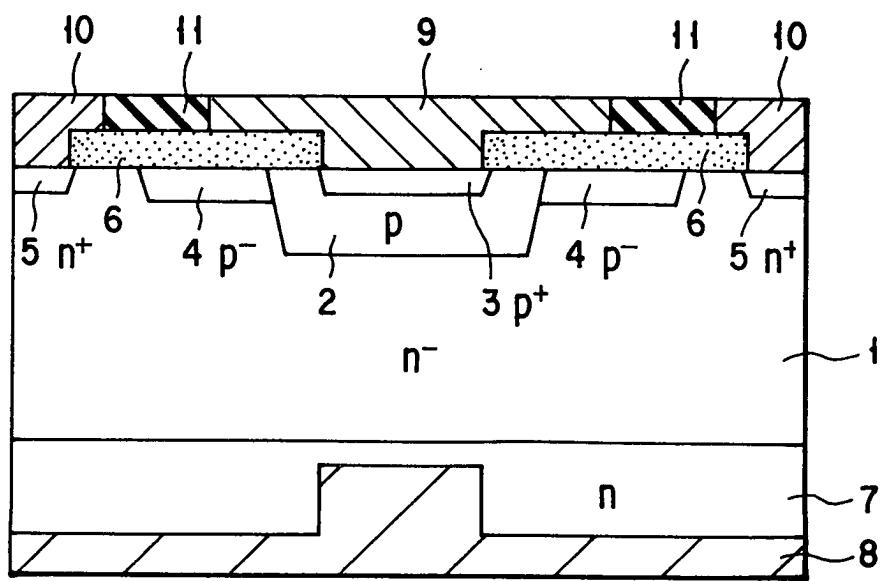

[0114] [Fig. 5](#) ist eine Schnittansicht des Hauptteils einer Hochspannungshalbleitervorrichtung gemäß der ersten Ausführungsform der vorliegenden Erfindung. Bei der ersten Ausführungsform wird eine Hochspannungsdiode als Hochspannungshalbleiter-element verwendet.

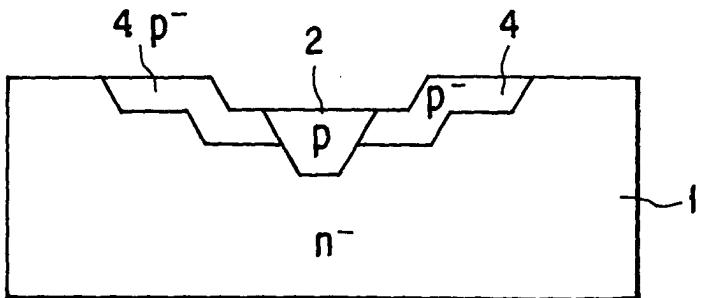

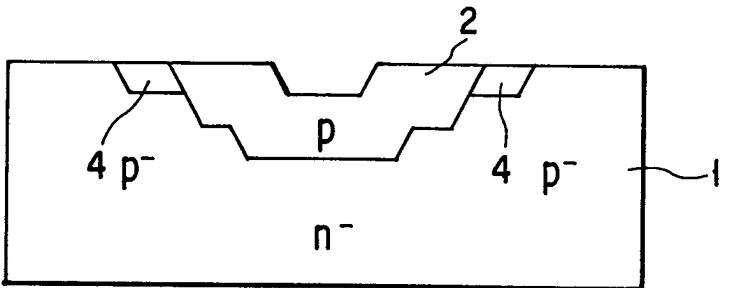

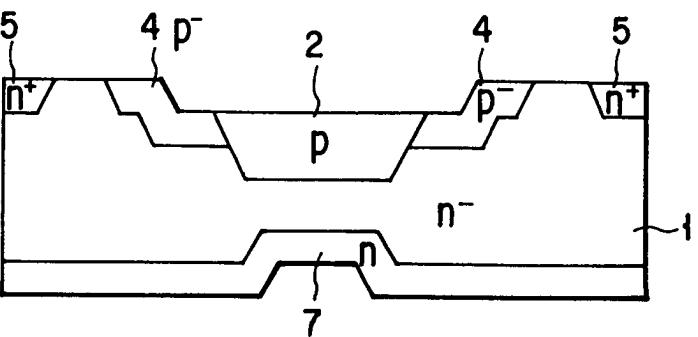

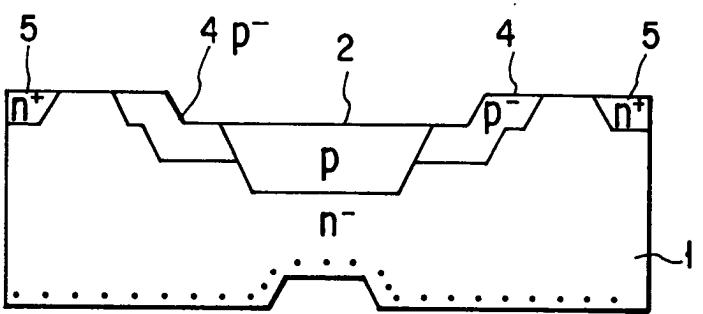

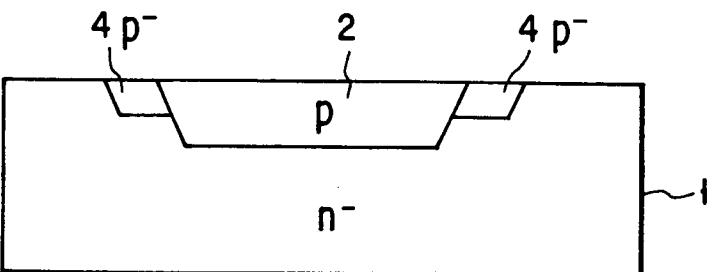

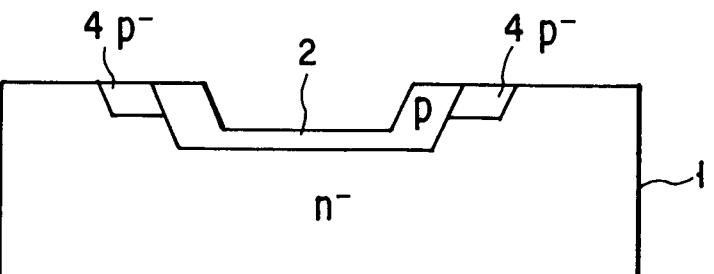

[0115] In [Fig. 5](#) bezeichnet das Bezugszeichen 1 eine erste Kathodenschicht des n-Typs (Halbleiter-substrat), die einen hohen Widerstand aufweist. Eine Ausnehmung ist in der vorderen Oberfläche der Kathodenschicht 1 des n-Typs vorgesehen. Eine erste Anodenschicht 2 des p-Typs ist selektiv in der Boden-oberfläche der Ausnehmung vorgesehen. Eine zweite, stark dotierte Anodenschicht 3 des p-Typs ist selektiv in der Oberfläche der ersten Anodenschicht des p-Typs vorgesehen.

[0116] Eine leicht dotierte Auftragsschicht 4 des p-Typs mit einem Feldrelaxationsaufbau ist um die erste Anodenschicht 2 des p-Typs herum in der vorderen Oberfläche der Kathodenschicht des n-Typs in Kontakt mit der ersten Anodenschicht 2 des p-Typs angeordnet. In diesem Fall wird die Auftragsschicht 4 des p-Typs so ausgebildet, daß sie von der Boden- und Seitenoberfläche der Ausnehmung in der Kathodenschicht 1 des n-Typs bis zur Substratoberfläche außerhalb der Ausnehmung geht.

[0117] Eine stark dotierte Kanalstoppschicht 5 des n-Typs mit einem Übergangsbeendigungsaufbau ist außerhalb der Auftragsschicht 4 des p-Typs in der vorderen Oberfläche der Kathodenschicht 1 des n-Typs so vorgesehen, daß sie um eine vorbestimmte Entfernung von der Auftragsschicht 4 des p-Typs beabstandet angeordnet ist.

[0118] Ein Film 6 mit hohem Widerstand, zum Beispiel ein SIPOS-Film (ein Film aus halbisolierendem, polykristallinem Silizium) ist in dem Bereich vorgesehen, der von einem Rand der zweiten Anodenschicht 3 des p-Typs zur ersten Anodenschicht 2 des p-Typs,

zur Auftragsschicht 4 des p-Typs, zur Kathodenschicht 1 des n-Typs und zur Kanalstoppschicht 5 des n-Typs hingehört. Statt des Films 6 mit hohem Widerstand kann auch ein Isolierfilm vorgesehen werden.

[0119] Eine zweite Kathodenschicht 7 des n-Typs, die stärker dotiert ist als die Kathodenschicht 1 des n-Typs, ist auf der rückwärtigen Oberfläche der ersten Kathodenschicht 1 des n-Typs vorgesehen. Eine Kathodenelektrode 8 ist auf der Kathodenschicht 7 des n-Typs angeordnet. Eine Anodenelektrode 9 ist auf der zweiten Anodenschicht 3 des p-Typs vorgesehen, wogegen eine Elektrode 10 auf der Kanalstoppschicht 5 des n-Typs angeordnet ist. Die Elektrode 10 ist eine Hilfselektrode, die zum Stabilisieren der Spannungsfestigkeit erforderlich ist, und kann als Kathodenelektrode dienen, so daß eine laterale Diodenanordnung zwischen der Elektrode 10 und der Anodenelektrode 9 ausgebildet wird. Mit dem Bezugszeichen 11 ist ein Isolierfilm bezeichnet.

[0120] Bei der ersten Ausführungsform ist die Ausnehmung in der vorderen Oberfläche der Kathodenschicht 1 des n-Typs vorgesehen, und ist eine Diode in einem dünnen Bereich der Ausnehmung vorgesehen. Bei der ersten Ausführungsform ist selbst dann, wenn die Kathodenschicht 1 des n-Typs (Halbleiter-substrat) dick ist, der als Diode arbeitende Abschnitt dünn ausgebildet, entsprechend der Tiefe der Ausnehmung. Daher führt eine Erhöhung der Dicke der Kathodenschicht 1 des n-Typs nicht zu einer Beeinträchtigung der Bauteileigenschaften, beispielsweise zu einem Spannungsabfall in Vorwärtsrichtung und Rückwärtserholungsverlusten.

[0121] Bei der ersten Ausführungsform können die voranstehenden Eigenschaften aus den nachstehend geschilderten Gründen erhalten werden.

[0122] Das Bauteil gemäß der ersten Ausführungsform wird mit einem Bauteil mit herkömmlichen Aufbau verglichen. Bei dem herkömmlichen Bauteil ist keine Stufe in dem Bereich vorgesehen, in welchem die Auftragsschicht 4 des p-Typs vorgesehen ist, wie aus [Fig. 6A](#) hervorgeht, und konzentriert sich das elektrische Feld an drei Abschnitten A, B und C in [Fig. 6A](#). [Fig. 6B](#) zeigt die Feldstärke an diesen Abschnitten. Bei dem herkömmlichen Bauteil muß das Substrat dick ausgebildet werden, um die Spannungsfestigkeit zu erhöhen, was zu hohen Bereitschaftszustands-Einschaltverlusten und großen Ausschaltverlusten führt.

[0123] Im Gegensatz hierzu ist bei der ersten Ausführungsform die Stufe in dem Bereich vorgesehen, in welchem die Auftragsschicht 4 des p-Typs angeordnet ist, und konzentriert sich das elektrische Feld an vier Abschnitten A, B, C und D, wie in den [Fig. 7A](#) und [Fig. 7B](#) gezeigt ist. Bei der ersten Ausführungs-

form ist daher die Anzahl an Abschnitten, in denen sich das Feld konzentriert, infolge der Stufe um Eins erhöht.

**[0124]** Die Spannungsfestigkeit, die durch Integration des elektrischen Feldes erhalten wird, wird daher bei der ersten Ausführungsform größer als im herkömmlichen Fall, so daß ein Halbleiterelement mit höherer Spannungsfestigkeit selbst dann realisiert werden kann, wenn sein Halbleitersubstrat dieselbe Dicke aufweist wie das herkömmliche Substrat.

**[0125]** Eine Verschlechterung der Eigenschaften des Bauteils, beispielsweise der Spannungsabfall in Vorwärtsrichtung und die Rückwärtserholungsverluste, kann allein dadurch verhindert werden, daß das Bauteil in dem dünnen Bereich der Ausnehmung ohne irgendeine Auftragsschicht 4 des p-Typs ausgebildet wird. Wenn zwei oder drei Stufen in dem Bereich vorgesehen werden, in welchem die Auftragsschicht 4 des p-Typs vorgesehen ist, läßt sich ein Halbleiterelement realisieren, welches erheblich höhere Spannungen verträgt.

**[0126]** Als nächstes wird die Beziehung zwischen der Tiefe der Ausnehmung und der Feldverteilung erläutert.

**[0127]** Die [Fig. 8A](#) und [Fig. 8B](#) zeigen die Feldverteilung für eine geringe Tiefe der Ausnehmung. Bei dieser Tiefe tritt ein Durchbruch oder ein Zusammenbruch in der Auftragsschicht 4 des p-Typs auf, da das elektrische Feld im Hauptbauteilbereich (dem Bereich zwischen A und A') des Halbleiterelements kleiner ist als jenes in der Auftragsschicht 4 des p-Typs, und der Hauptbauteilbereich eine gewisse Toleranz aufweist. Daher nimmt die Spannungsfestigkeit nicht ab, selbst wenn die Ausnehmung bis zu einem tieferen Bereich hin ausgebildet wird, um die Einschaltverluste und die Ausschaltverluste zu verringern.

**[0128]** Die [Fig. 9A](#) und [Fig. 9B](#) zeigen die Feldverteilung für eine mittlere Tiefe der Ausnehmung. In dieser Tiefe tritt ein Durchbruch gleichzeitig in dem Bauteil und der Auftragsschicht 4 des p-Typs auf, da das elektrische Feld in dem Hauptbauteil gleich groß ist wie jenes in der Auftragsschicht 4 des p-Typs.

**[0129]** Die [Fig. 10A](#) und [Fig. 10B](#) zeigen die Feldverteilung für eine große Tiefe der Ausnehmung. In dieser Tiefe tritt der Durchbruch in dem Hauptbauteil auf, da das elektrische Feld in dem Hauptbauteil größer ist als jenes in der Auftragsschicht 4 des p-Typs. Die gesamte Spannungsfestigkeit wird daher nur durch die Spannungsfestigkeit des Hauptbauteils bestimmt (sogenannte Hauptbauteilauslegung), unabhängig von der Feldrelaxationsanordnung der Auftragsschicht 4 des p-Typs und dergleichen. In diesem Fall ist der Absolutwert für die Spannungsfestigkeit niedriger als jener in [Fig. 9A](#). Gleichzeitig werden je-

doch der Spannungsabfall in Vorwärtsrichtung und die Rückwärtserholungsverluste verringert, so daß man ein hervorragendes Halbleitergerät mit niedrigen Leistungsverlusten erhält. Da der Durchbruch am Punkt A entfernt von der Halbleiteroberfläche auftritt, läßt sich ein Halbleiterbauteil erzielen, welches widerstandsfähig in Bezug auf Einflüsse der Oberfläche ist, und eine stabile Spannungsfestigkeit aufweist.

**[0130]** Das Hochspannungsbauteil ist vorzugsweise so aufgebaut, wie dies in den [Fig. 9A](#) und [Fig. 10A](#) dargestellt ist. Gemäß der vorliegenden Erfindung können, wenn das Substrat am Stromdurchgangsabschnitt dünn ausgebildet wird, und das Substrat in dem Feldrelaxationsaufbau (Auftragsschicht und dergleichen) dick ausgebildet wird, die Bereitschaftszustandseinschaltverluste und die Einschaltverluste verringert werden, und läßt sich eine Spannungsfestigkeit erzielen, die gleich jener eines ebenen Übergangs ist.

**[0131]** Die [Fig. 11A](#) bis [Fig. 11E](#) zeigen ein Verfahren zur Herstellung eines Bauteilaufbaus an der Ausnehmung.

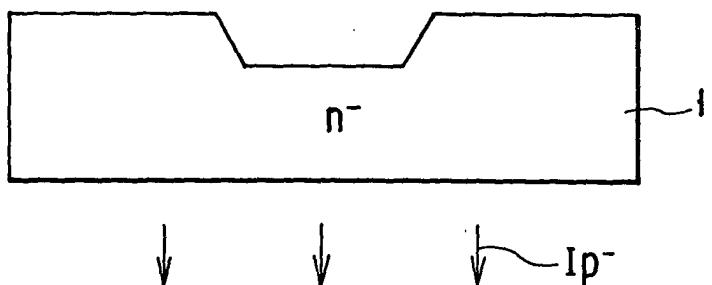

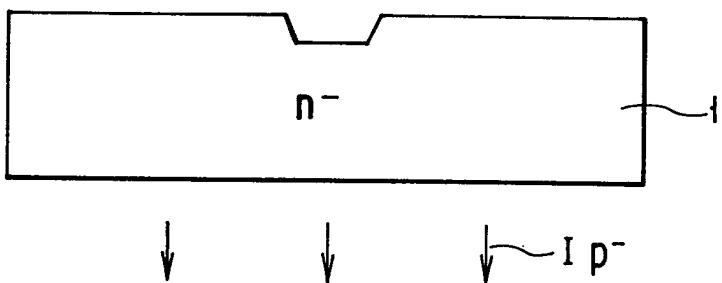

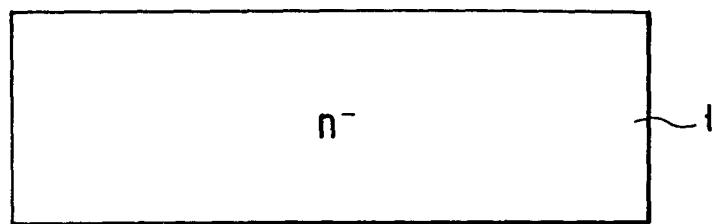

**[0132]** Zuerst wird die Basisschicht 1 des n-Typs (Halbleitersubstrat) hergestellt, wie in [Fig. 11A](#) gezeigt ist, und wird eine Ausnehmung in der vorderen Oberfläche der Basisschicht 1 des n-Typs ausgebildet, gemäß [Fig. 11b](#).

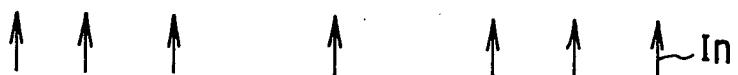

**[0133]** Wie aus [Fig. 11C](#) hervorgeht, werden Verunreinigungen  $Ip^-$  des p-Typs selektiv in die Ausnehmung und die Vorderoberfläche der Basisschicht 1 des n-Typs um die Ausnehmung herum unter Verwendung einer Maske (nicht gezeigt) implantiert.

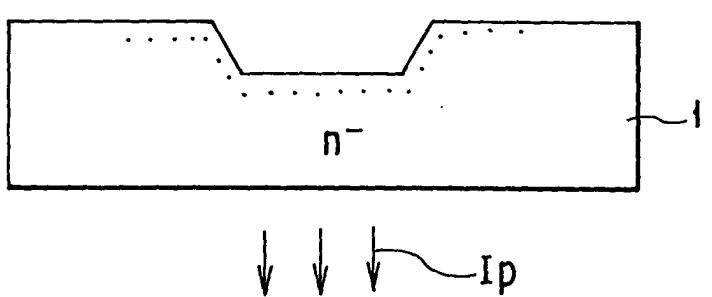

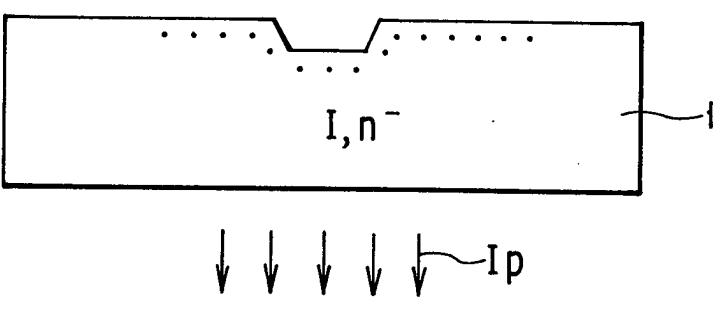

**[0134]** Wie in [Fig. 11D](#) dargestellt werden Verunreinigungen  $Ip$  des p-Typs selektiv in die Vorderoberfläche der Basisschicht 1 des n-Typs am Boden der Ausnehmung unter Verwendung einer (nicht dargestellten) Maske implantiert. Hierbei ist die Dosis der Verunreinigungen  $Ip$  des p-Typs höher als jene der Verunreinigungen  $Ip^-$  des p-Typs.

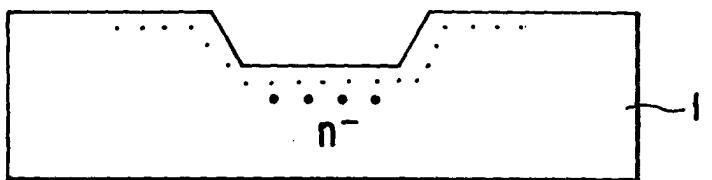

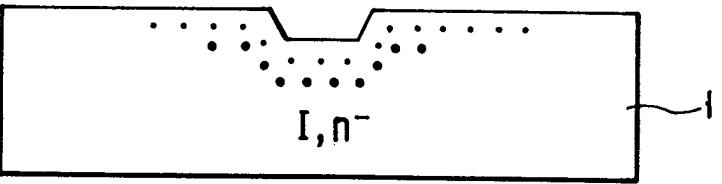

**[0135]** Schließlich erfolgt, wie in [Fig. 11E](#) gezeigt, eine Wärmebehandlung, um die Anodenschicht 2 des p-Typs und die Auftragsschicht 4 des p-Typs fertigzustellen.

**[0136]** Die [Fig. 11A](#) bis [Fig. 11E](#) zeigen die Anodenschicht 3 des p-Typs nicht. Bei der Herstellung der Anodenschicht 3 des p-Typs werden Verunreinigungen des p-Typs mit höherer Verunreinigungskonzentration selektiv in die Vorderoberfläche des Implantierungsbereiches der Verunreinigungen  $Ip$  des p-Typs implantiert, beispielsweise nach dem Schritt in [Fig. 11D](#).

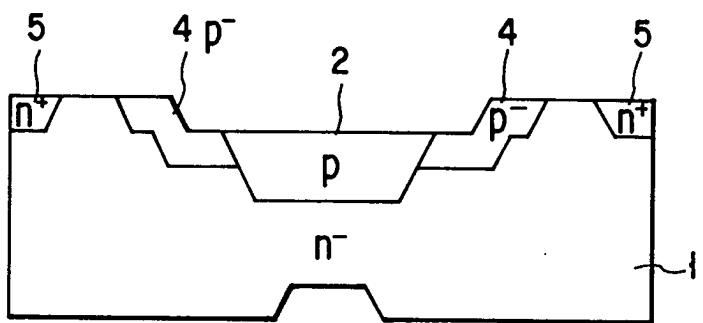

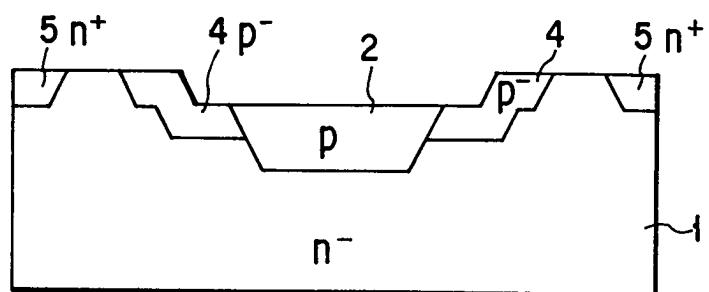

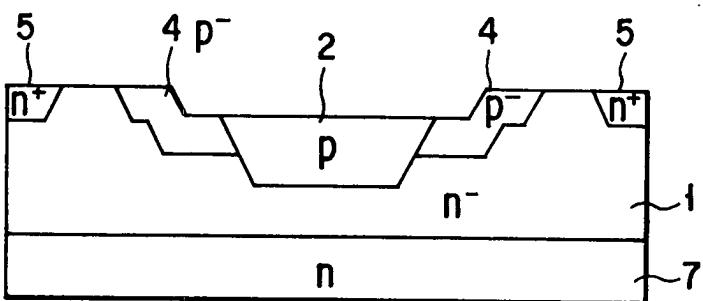

[0137] Die [Fig. 12](#) und [Fig. 13](#) zeigen Änderungen der ersten Ausführungsform. Bei dem Bauteil von [Fig. 12](#) ist die Ausnehmung mit zwei Stufen versehen. Bei dem Bauteil gemäß [Fig. 13](#) weist die Ausnehmung drei Stufen auf. Die Erhöhung der Anzahl an Stufen kann den Krümmungsradius des gebogenen Abschnitts in der Feldrelaxationsanordnung vergrößern, um so die Spannungsfestigkeit zu erhöhen. Mit einem derartigen Aufbau kann ein Bauteil mit geringer Substratdicke einfach hergestellt werden. Die Anzahl der Stufen der Ausnehmung kann auch vier oder mehr betragen.

(ZWEITE AUSFÜHRUNGSFORM)

[0138] [Fig. 14](#) ist eine Schnittansicht des Hauptteils eines Hochspannungshalbleitergerätes gemäß der zweiten Ausführungsform der vorliegenden Erfindung.

[0139] Die zweite Ausführungsform unterscheidet sich von der ersten Ausführungsform in der Hinsicht, daß eine Ausnehmung nur in einem Bereich innerhalb eines Halbleiterbauteils ausgebildet wird, in welchem eine Auftragsschicht 4 des p-Typs hergestellt werden soll. Die Auftragsschicht 4 des p-Typs wird von der Boden- und Seitenoberfläche der Ausnehmung in einer Kathodenschicht 1 des n-Typs aus bis zur vorderen Oberfläche der Kathodenschicht 1 des n-Typs außerhalb der Ausnehmung ausgebildet. Dies führt dazu, daß zwei Stufen an der Grenzfläche zwischen der Auftragsschicht 4 des p-Typs und der Kathodenschicht 1 des n-Typs hergestellt werden. Bei der zweiten Ausführungsform nimmt daher der Krümmungsradius des gebogenen Abschnitts in der Feldrelaxationsanordnung zu, um so die Spannungsfestigkeit zu erhöhen, die durch Integration des elektrischen Feldes erhalten wird.

(DRITTE AUSFÜHRUNGSFORM)

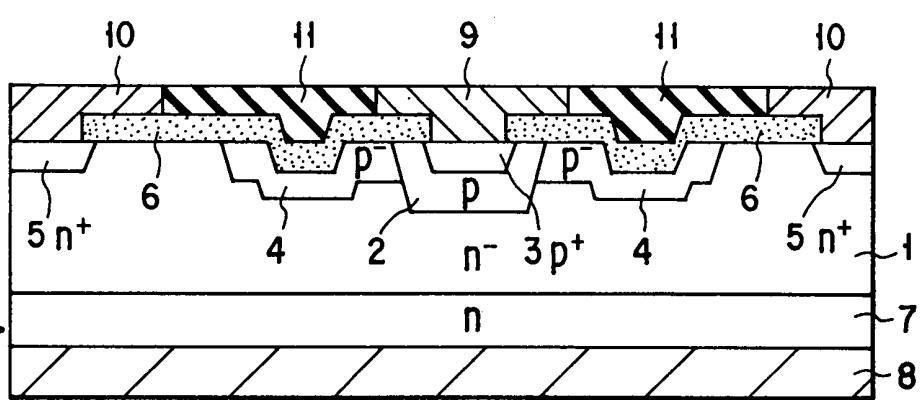

[0140] [Fig. 15](#) zeigt in einer Schnittansicht das Hauptteil eines Hochspannungshalbleitergerätes gemäß der dritten Ausführungsform der vorliegenden Erfindung.

[0141] Die dritte Ausführungsform unterscheidet sich von der zweiten Ausführungsform in der Hinsicht, daß der äußere Abschnitt einer Auftragsschicht 4 des p-Typs so ausgebildet wird, daß er nicht in Querrichtung (lateral) vom Boden einer Ausnehmung aus vorspringt. Auch in diesem Fall nimmt die Spannungsfestigkeit zu, die durch Integration des elektrischen Feldes erhalten wird, so daß die gleichen Auswirkungen wie bei der zweiten Ausführungsform erzielt werden.

(VIERTE AUSFÜHRUNGSFORM)

[0142] [Fig. 16](#) zeigt als Schnittansicht das Hauptteil

eines Hochspannungshalbleitergeräts gemäß der vierten Ausführungsform der vorliegenden Erfindung.

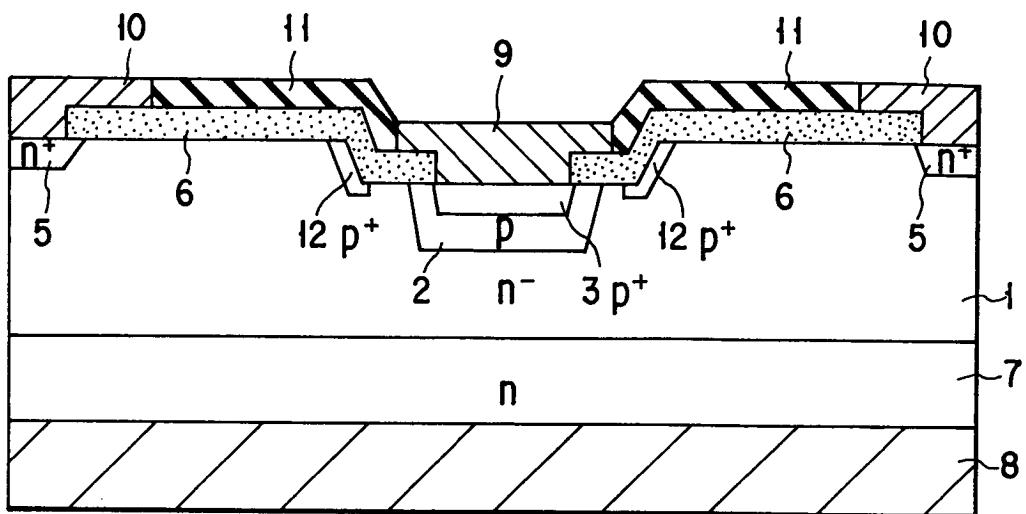

[0143] Die vierte Ausführungsform unterscheidet sich von der ersten Ausführungsform in der Hinsicht, daß eine stark dotierte Schutzzschicht 12 des p-Typs die Auftragsschicht 4 des p-Typs als Feldrelaxationsanordnung ersetzt (Übergangsbeendigungsanordnung). Die Schutzzschicht 12 des p-Typs kann in dem Bereich mit Ausnahme der Ausnehmung vorgesehen sein.

[0144] Auch bei der vierten Ausführungsform kann ein Bauteil entsprechend der Tiefe der Ausnehmung dünn ausgebildet werden, selbst bei einer dicken Kathodenschicht 1 des n-Typs (Halbleitersubstrat). Selbst wenn die Schutzzschicht 12 des p-Typs ausgebildet wird, und die Kathodenschicht 1 des n-Typs dick ausgebildet wird, um die erforderliche Spannungsfestigkeit sicherzustellen, tritt keine Beeinträchtigung der Bauteileigenschaften auf, beispielsweise ein Spannungsabfall in Vorwärtsrichtung und die Rückwärtserholungsverluste.

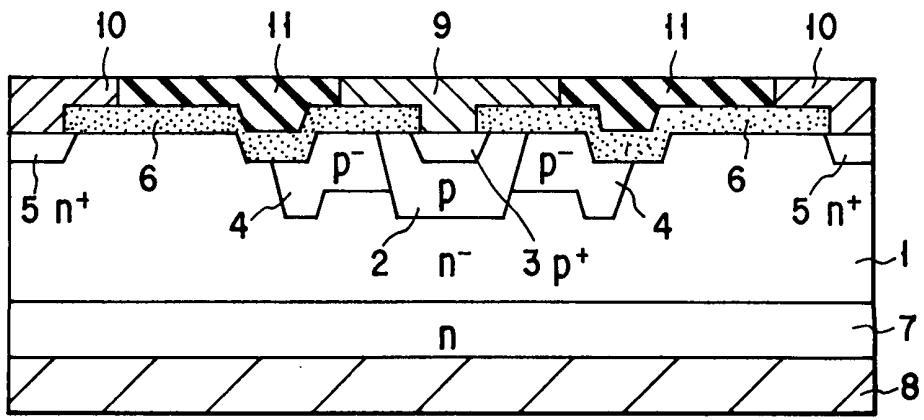

(FÜNFTE AUSFÜHRUNGSFORM)

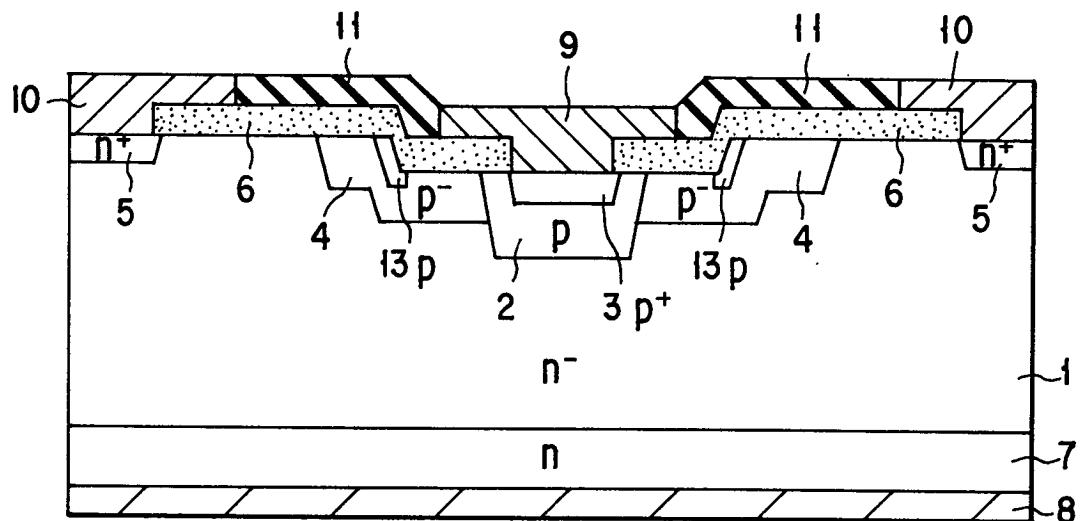

[0145] [Fig. 17](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergerätes gemäß der fünften Ausführungsform der vorliegenden Erfindung.

[0146] Die fünfte Ausführungsform unterscheidet sich von der ersten Ausführungsform in der Hinsicht, daß eine zweite, stark dotierte Auftragsschicht 13 des p-Typs selektiv in der Oberfläche einer Auftragsschicht 4 des p-Typs so ausgebildet wird, daß sie in Kontakt mit der Stufe einer Ausnehmung steht. Die Auftragsschicht 13 des p-Typs deckt einen instabilen Abschnitt der Oberfläche der Substratstufe ab, um ihn zu stabilisieren.

[0147] Bei der fünften Ausführungsform können dieselben Auswirkungen wie bei der ersten Ausführungsform erzielt werden, und darüber hinaus sind die Auswirkungen bei der fünften Ausführungsform stabiler, infolge des Vorhandenseins der Auftragsschicht 13 des p-Typs.

(SECHSTE AUSFÜHRUNGSFORM)

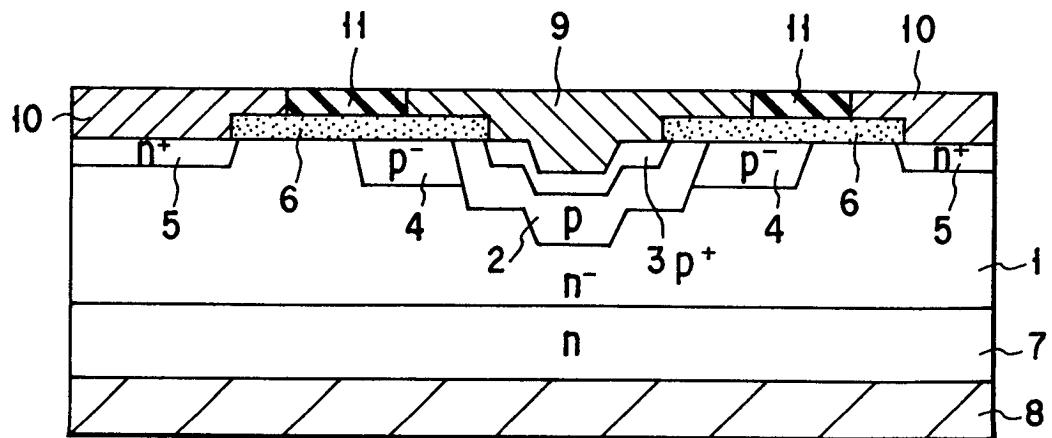

[0148] [Fig. 18](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergerätes gemäß der sechsten Ausführungsform der vorliegenden Erfindung.

[0149] Die sechste Ausführungsform unterscheidet sich von der ersten Ausführungsform in der Hinsicht, daß die Stufe einer Ausnehmung nicht im Ausbildungsbereich einer Auftragsschicht 4 des p-Typs vorhanden ist, sondern nur in einem Hauptbauteilbereich. Daher werden Stufen in den Anodenschichten

2 und 3 des p-Typs ausgebildet.

[0150] Auch bei der sechsten Ausführungsform kann das Hauptbauteil entsprechend der Tiefe der Ausnehmung dünn ausgebildet werden, selbst bei einer dicken Kathodenschicht 1 des n-Typs (Halbleitersubstrat). Selbst wenn die Auftragsschicht 4 des p-Typs ausgebildet wird, und die Kathodenschicht 1 des n-Typs dick ausgebildet wird, um die erforderliche Spannungsfestigkeit sicherzustellen, treten keine Beeinträchtigungen der Eigenschaften des Bauteils auf, etwa ein Spannungsabfall in Vorwärtsrichtung und Rückwärtserholungsverluste.

[0151] Die [Fig. 19A](#) bis [Fig. 19E](#) zeigen ein Verfahren zur Herstellung einer Bauteilanordnung an der Ausnehmung.

[0152] Zunächst wird die Basisschicht 1 des n-Typs (Halbleitersubstrat) hergestellt, wie in [Fig. 19A](#) gezeigt ist, und wird eine Ausnehmung in der Vorderoberfläche der Basisschicht 1 des n-Typs hergestellt, wie in [Fig. 19B](#) gezeigt ist.

[0153] Wie aus [Fig. 19C](#) hervorgeht, werden Verunreinigungen  $Ip^-$  des p-Typs selektiv in der Ausnehmung und der Vorderoberfläche der Basisschicht 1 des n-Typs um die Ausnehmung herum unter Verwendung einer (nicht dargestellten) Maske implantiert.

[0154] Wie in [Fig. 19D](#) gezeigt ist, werden Verunreinigungen  $Ip$  des p-Typs selektiv in der Ausnehmung und der Vorderoberfläche der Basisschicht 1 des n-Typs um die Ausnehmung (also innerhalb des Implantierungsbereiches für die Verunreinigungen  $Ip^-$ ) herum unter Verwendung (nicht dargestellten) Maske implantiert. Hierbei ist die Dosis für die Verunreinigungen  $Ip$  des p-Typs höher als jene für die Verunreinigungen  $Ip^-$  des p-Typs.

[0155] Schließlich wird, wie in [Fig. 19E](#) gezeigt, eine Wärmebehandlung durchgeführt, um die Anodenschicht 2 des p-Typs und die Auftragsschicht 4 des p-Typs fertigzustellen.

[0156] Bei der sechsten Ausführungsform wurde keine Anodenschicht 3 des p-Typs beschrieben. Bei der Herstellung der Anodenschicht 3 des p-Typs werden Verunreinigungen des p-Typs mit höherer Verunreinigungskonzentration selektiv in der Ausnehmung und der Vorderoberfläche des Abschnitts um die Ausnehmung herum implantiert (also innerhalb des Implantierungsbereiches für die Verunreinigungen  $Ip$  des p-Typs), beispielsweise nach dem Schritt in [Fig. 19D](#).

[0157] [Fig. 20](#) zeigt eine Abänderung der sechsten Ausführungsform. Bei dem Bauteil von [Fig. 20](#) sind zwei Ausnehmungen, die jeweils eine Stufe aufwei-

sen, in einem Bauteilbereich vorgesehen. Diese Anordnung ist dann wirksam, wenn die Abmessungen für den Ausnehmungsherstellungsbereich begrenzt sind, infolge verfahrensbedingter Einschränkungen, beispielsweise der Waferfestigkeit und der Steuerung der Herstellung in einem Ätzvorgang. Die Anzahl der Ausnehmungen kann auch drei oder mehr betragen.

(SIEBTE AUSFÜHRUNGSFORM)

[0158] [Fig. 21](#) ist eine Schnittansicht eines Hochspannungshalbleitergeräts gemäß der siebten Ausführungsform der vorliegenden Erfindung. Die siebte Ausführungsform unterscheidet sich von der ersten Ausführungsform in der Hinsicht, daß eine zweite Ausnehmung am Boden einer (ersten) Ausnehmung vorgesehen ist, und daß Anodenschichten 2 und 3 des p-Typs am Boden der ersten Ausnehmung einschließlich der zweiten Ausnehmung vorgesehen sind. Mit der siebten Ausführungsform können dieselben Auswirkungen wie bei der ersten Ausführungsform erzielt werden.

(ACHTE AUSFÜHRUNGSFORM)

[0159] [Fig. 22](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergeräts gemäß der achten Ausführungsform der vorliegenden Erfindung. Bei der achten Ausführungsform wird ein IGBT als Hochspannungs-Halbleiterelement eingesetzt.

[0160] In [Fig. 22](#) bezeichnet das Bezugssymbol 21 eine Basisschicht des n-Typs mit hohem Widerstand. Ausnehmungen sind in der Vorderoberfläche der Basisschicht 21 des n-Typs vorgesehen, und eine erste Basisschicht 22 des p-Typs wird selektiv auf der Bodenoberfläche jeder Ausnehmung ausgebildet. Eine zweite, stark dotierte Basisschicht 23 des p-Typs wird selektiv in dem Herstellungsbereich für die erste Basisschicht 22 des p-Typs bis zu einer Tiefe ausgebildet, die ausreichend groß ist, um durch die erste Basisschicht 22 des p-Typs hindurchzugehen.

[0161] Eine stark dotierte Sourceschicht 24 des n-Typs wird in den Oberflächen der Basisschichten 22 und 23 des p-Typs hergestellt. Eine Gateelektrode 26 wird über einen Gateisolierfilm 25 auf der Basisschicht 22 des p-Typs in dem Bereich angeordnet, der sandwichartig zwischen den Sourceschichten 24 des n-Typs und den Basisschichten 21 des n-Typs eingeschlossen ist.

[0162] Eine leicht dotierte Auftragsschicht 27 des p-Typs mit einer Feldrelaxationsanordnung (Übergangsbeendigungsanordnung) wird um die Basisschicht 23 des p-Typs herum in der Vorderoberfläche der Basisschicht 21 des n-Typs in Kontakt mit der Basisschicht 23 des p-Typs hergestellt. Hierbei wird die Auftragsschicht 27 des p-Typs so ausgebildet, daß sie sich von der Boden- und Seitenoberfläche der

Ausnehmung in der Basisschicht **21** des n-Typs zur vorderen Oberfläche der Basisschicht **21** des n-Typs außerhalb der Ausnehmung erstreckt. Unter den Halbleitergeräten, die in den Ausnehmungen ausgebildet werden, liegt die Basisschicht **23** des p-Typs, die in Kontakt mit der Auftragsschicht **27** des p-Typs steht, im äußersten Abschnitt.

**[0163]** Eine stark dotierte Kanalstoppschicht **28** des n-Typs mit einem Übergangsbeendigungsaufbau wird in der Vorderoberfläche der Basisschicht **21** des n-Typs so ausgebildet, daß sie um eine vorbestimmte Entfernung von der Auftragsschicht **27** des p-Typs beabstandet angeordnet ist. Ein Film **29** mit hohem Widerstand, beispielsweise ein SIPOS-Film, wird in dem Bereich ausgebildet, der von einem Rand der zweiten Basisschicht **23** des p-Typs bis zur Auftragsschicht **27** des p-Typs, zur Basisschicht **21** des n-Typs, und zur Kanalstoppschicht **28** des n-Typs geht. Statt des Films **29** mit hohem Widerstand kann auch ein Isolierfilm hergestellt werden.

**[0164]** Ein zweiter Basisfilm **30** des n-Typs, der stärker dotiert ist als die erste Basisschicht **21** des n-Typs, wird auf der rückwärtigen Oberfläche der ersten Basisschicht **21** des n-Typs ausgebildet, die einen hohen Widerstand aufweist. Eine stark dotierte Drainschicht **31** des p-Typs wird auf der Oberfläche des Basisfilms **30** des n-Typs ausgebildet. Eine Drainelektrode **32** wird auf der Drainschicht **31** des p-Typs hergestellt, wogegen eine Sourceelektrode **33** auf der Sourceschicht **24** des n-Typs ausgebildet wird. Darüber hinaus steht die Sourceelektrode **33** in Kontakt mit der Basisschicht **23** des p-Typs. Eine Elektrode **34** ist auf der Kanalstoppschicht **28** des n-Typs vorgesehen. Das Bezugszeichen **35** bezeichnet einen Isolierfilm.

**[0165]** Bei der achten Ausführungsform ist die Ausnehmung in der Vorderoberfläche der Basisschicht **21** des n-Typs angeordnet, und ist ein IGBT in einem dünnen Bereich der Ausnehmung vorgesehen. Da-her ist der IGBT entsprechend der Tiefe der Ausnehmung dünn, selbst bei einer dicken Basisschicht **21** des n-Typs (Halbleitersubstrat).

**[0166]** Selbst wenn die Auftragsschicht **27** des p-Typs ausgebildet wird, und die Basisschicht **21** des n-Typs dick ausgebildet wird, um eine ausreichende Spannungsfestigkeit sicherzustellen, tritt keine Beeinträchtigung der Eigenschaften der Bauteile auf, beispielsweise ein Spannungsabfall in Vorwärtsrichtung, oder der Abschalteigenschaften.

**[0167]** Ein weiterer Grund dafür, daß die voranstehenden Eigenschaften bei der achten Ausführungsform erhalten werden können, ist folgender. Da bei der achten Ausführungsform die Stufe in dem Bereich ausgebildet wird, in welchem die Auftragsschicht **27** des p-Typs ausgebildet wird, ist die Anzahl

an Feldkonzentrationsabschnitten größer als bei dem herkömmlichen Bauteil. Daher nimmt die Spannungsfestigkeit zu, die durch Integration des elektrischen Feldes erhalten wird.

**[0168]** Die voranstehenden Auswirkungen lassen sich auch dann erzielen, wenn nur ein Bauteil in dem dünnen Bereich der Ausnehmung ausgebildet wird, oder wenn nur die Auftragsschicht **27** des p-Typs mit mehreren Stufen an der Grenzfläche zwischen der Auftragsschicht **27** des p-Typs und der Basisschicht **21** des n-Typs vorgesehen wird.

(NEUNTE AUSFÜHRUNGSFORM)

**[0169]** [Fig. 23](#) ist eine Schnittansicht des Hauptteils eines Hochspannungshalbleitergeräts gemäß der neunten Ausführungsform der vorliegenden Erfindung. Die neunte Ausführungsform unterscheidet sich von der achten Ausführungsform in der Hinsicht, daß die Stufe einer Ausnehmung nicht in dem Herstellungsbereich einer Auftragsschicht **27** des p-Typs vorhanden ist, sondern nur in einem Hauptbauteilbereich.

**[0170]** Auch bei der neunten Ausführungsform kann ein Hauptbauteil dünn ausgebildet werden, entsprechend der Tiefe der Ausnehmung, selbst bei einer dicken Basisschicht **21** des n-Typs (Halbleitersubstrat). Selbst wenn die Auftragsschicht **24** des p-Typs vorgesehen wird, und die Basisschicht **21** des n-Typs dick ausgebildet wird, um eine erforderliche Spannungsfestigkeit sicherzustellen, tritt keine Beeinträchtigung der Bauteileigenschaften auf, beispielsweise ein Spannungsabfall in Vorwärtsrichtung, und keine Beeinträchtigung der Abschalteigenschaften.

(ZEHNTE AUSFÜHRUNGSFORM)

**[0171]** [Fig. 24](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergeräts gemäß der zehnten Ausführungsform der vorliegenden Erfindung. Die zehnte Ausführungsform unterscheidet sich von der ersten Ausführungsform in der Hinsicht, daß eine Ausnehmung in der rückwärtigen Oberfläche einer Kathodenschicht **1** des n-Typs (der Oberfläche entgegengesetzt zur Hauptoberfläche auf der Anodenseite) vorgesehen ist, und daß die Ausnehmung Anodenschichten **2** und **3** des p-Typs gegenüberliegt.

**[0172]** Bei der zehnten Ausführungsform kann ein Hauptbauteil entsprechend der Tiefe der Ausnehmung in der rückwärtigen Oberfläche dünn ausgebildet werden, selbst bei einer dicken Kathodenschicht **1** des n-Typs (Halbleitersubstrat). Selbst wenn eine Auftragsschicht **4** des p-Typs vorgesehen ist, und die Kathodenschicht **1** des n-Typs dick ausgebildet ist, um eine erforderliche Spannungsfestigkeit sicherzustellen, tritt keine Beeinträchtigung der Bauteileigen-

schaften auf, etwa ein Spannungsabfall in Vorwärtsrichtung und Rückwärtswiederherstellungsverluste.

[0173] [Fig. 25](#) zeigt eine Abänderung der zehnten Ausführungsform. Bei diesem Bauteil sind zwei Ausnehmungen, die jeweils eine Stufe aufweisen, in der rückwärtigen Oberfläche der Kathodenschicht 1 des n-Typs in dem Bereich vorgesehen, welcher den Anodenschichten 2 und 3 des p-Typs gegenüberliegt. Diese Anordnung ist dann wirksam, wenn die Abmessungen für eine herzustellende Ausnehmung begrenzt sind, infolge herstellungsbedingter Einschränkungen, beispielsweise der Waferfestigkeit und der Herstellungsgenauigkeit bei einem Ätzvorgang.

(ELFTE AUSFÜHRUNGSFORM)

[0174] [Fig. 26](#) ist eine Schnittansicht des Hauptteils eines Hochspannungshalbleitergeräts gemäß der elften Ausführungsform der vorliegenden Erfindung. Die elfte Ausführungsform stellt eine Kombination der zehnten und ersten Ausführungsform dar. Im einzelnen ist bei dem Bauteil von [Fig. 5](#) eine Ausnehmung in der rückwärtigen Oberfläche einer Basisschicht 1 des n-Typs so vorgesehen, daß sie Anodenschichten 2 und 3 des p-Typs gegenüberliegt. Die elfte Ausführungsform kann dieselben Auswirkungen zur Verfügung stellen wie die erste und die zehnte Ausführungsform.

[0175] Die [Fig. 27A](#) bis [Fig. 27D](#) zeigen ein Verfahren zur Herstellung des grundlegenden Aufbaus eines Bauteils.

[0176] Wie aus [Fig. 27A](#) hervorgeht, wird ein Bauteilaufbau auf der vorderen Oberfläche (auf der Seite des Hauptübergangs) der Basisschicht 1 des n-Typs entsprechend dem bezüglich der ersten Ausführungsform geschilderten Verfahren ausgebildet.

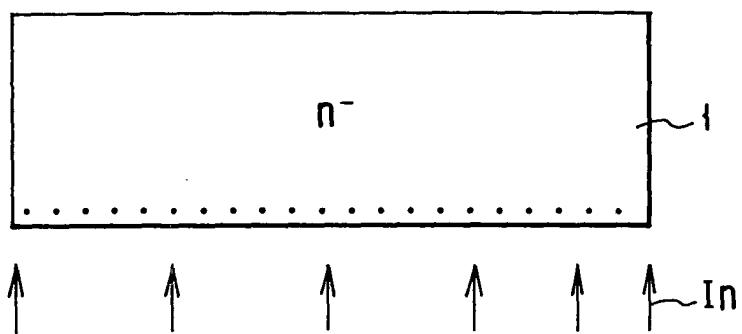

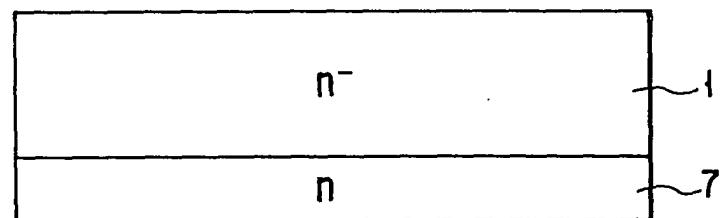

[0177] Nachdem eine Ausnehmung in der rückwärtigen Oberfläche der Basisschicht 1 des n-Typs hergestellt wurde, wie dies in [Fig. 27B](#) gezeigt ist, werden Verunreinigungen in des n-Typs in die gesamte rückwärtige Oberfläche der Basisschicht 1 des n-Typs implantiert, wie in [Fig. 27C](#) gezeigt ist.

[0178] Schließlich wird, wie in [Fig. 27D](#) gezeigt, eine Wärmebehandlung durchgeführt, um eine Kathodenschicht 7 des n-Typs herzustellen, wodurch der grundlegende Aufbau des Bauteils fertig ist.

[0179] Die [Fig. 28A](#) bis [Fig. 28E](#) zeigen ein anderes Herstellungsverfahren. Bei dem in den [Fig. 27A](#) bis [Fig. 27D](#) gezeigten Verfahren wird, nachdem der Bauteilaufbau auf der vorderen Oberfläche der Basisschicht des n-Typs hergestellt wurde, der Bauteilaufbau (Kathodenschicht 7 des n-Typs) auf der rückwärtigen Oberfläche hergestellt. Bei dem in den

[0180] [Fig. 28A](#) bis [Fig. 28E](#) dargestellten Verfahren ist die Reihenfolge der Herstellung umgekehrt.

[0181] Im einzelnen wird die Basisschicht 1 des n-Typs (Halbleitersubstrat) vorbereitet, und wird eine Ausnehmung in der rückwärtigen Oberfläche der Basisschicht 1 des n-Typs hergestellt, wie in den [Fig. 28A](#) und [Fig. 28B](#) gezeigt ist.

[0182] Wie in den [Fig. 28C](#) und [Fig. 28D](#) gezeigt ist, wird eine Wärmebehandlung zur Herstellung der Kathodenschicht 7 des n-Typs durchgeführt, nachdem die Verunreinigungen des n-Typs in die gesamte rückwärtige Oberfläche der Basisschicht 1 des n-Typs implantiert wurden.

[0183] Schließlich wird, wie in [Fig. 28E](#) gezeigt, eine Bauteilanordnung auf der vorderen Oberfläche (auf der Seite des Hauptübergangs) der Basisschicht 1 des n-Typs entsprechend dem Verfahren ausgebildet, welches bei der ersten Ausführungsform beschrieben wurde.

[0184] Die [Fig. 29A](#) bis [Fig. 29D](#) sowie [Fig. 30A](#) bis [Fig. 30E](#) zeigen jeweils andere Herstellungsverfahren. Bei dem Herstellungsverfahren gemäß den [Fig. 29A](#) bis [Fig. 29D](#), welches in entgegengesetzter Reihenfolge abläuft wie das Herstellungsverfahren gemäß den [Fig. 27A](#) bis [Fig. 27D](#), wird eine Ausnehmung ausgebildet, nachdem die Verunreinigungen in des n-Typs in die gesamte rückwärtige Oberfläche der Basisschicht 1 des n-Typs implantiert wurden, um die Kathodenschicht 7 des n-Typs auszubilden. Entsprechend wird bei dem in den [Fig. 30A](#) bis [Fig. 30E](#) gezeigten Herstellungsverfahren, das in entgegengesetzter Reihenfolge abläuft wie das Herstellungsverfahren gemäß den [Fig. 28A](#) bis [Fig. 28E](#), eine Ausnehmung ausgebildet, nachdem die Verunreinigungen in des n-Typs in die gesamte rückwärtige Oberfläche der Basisschicht 1 des n-Typs implantiert wurden, um die Kathodenschicht 7 des n-Typs herzustellen.

[0185] Bei den Herstellungsverfahren gemäß [Fig. 29A](#) bis [Fig. 29D](#) sowie [Fig. 30A](#) bis [Fig. 30E](#) kann, da die Oberflächenkonzentration der Kathodenschicht 7 des n-Typs in dem Bauteilbereich verringert werden kann, der Schwanzstrom verringert werden, damit man eine Diode mit kleinen Rückwärtserholungsverlusten erhält.

(ZWÖLFTE AUSFÜHRUNGSFORM)

[0186] [Fig. 31](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergeräts gemäß der zwölften Ausführungsform der vorliegenden Erfindung. Die zwölfte Ausführungsform unterscheidet sich von der sechsten Ausführungsform bezüglich des Verfahrens zur Herstellung eines Bauteilaufbaus in einer Ausnehmung. Bei der zwölften Ausführungs-

form wird, nachdem eine Anodenschicht **2** des p-Typs hergestellt wurde, eine Ausnehmung durch das Verfahren zur Herstellung eines Bauteilaufbaus in einer Ausnehmung hergestellt.

**[0187]** Die [Fig. 32A](#) bis [Fig. 32E](#) zeigen das Verfahren zur Herstellung eines Bauteilaufbaus in einer Ausnehmung. Wie aus den [Fig. 32A](#) und [Fig. 32B](#) hervorgeht, wird eine Basisschicht **1** des n-Typs (Halbleitersubstrat) hergestellt, und werden Verunreinigungen I<sub>p</sub> des p-Typs in einen Teil ihrer vorderen Oberfläche implantiert.

**[0188]** Wie in [Fig. 32C](#) gezeigt werden Verunreinigungen I<sub>p</sub> des p-Typs in einen Teil des Bereichs implantiert, in welchen die Verunreinigungen I<sub>p</sub> des p-Typs implantiert wurden. Hierbei ist die Dosis für die Verunreinigungen I<sub>p</sub> des p-Typs höher als jene für die Verunreinigungen I<sub>p</sub> des p-Typs.

**[0189]** Wie in [Fig. 32D](#) gezeigt wird dann eine Wärmebehandlung durchgeführt, um die Anodenschicht **2** des p-Typs und eine Auftragsschicht **4** des p-Typs herzustellen.

**[0190]** Schließlich wird, wie in [Fig. 32E](#) gezeigt, die vordere Oberfläche der Anodenschicht **2** des p-Typs geätzt, um eine Ausnehmung auszubilden, wodurch der grundlegende Aufbau des Ausnehmungsbereiches beendet ist.

**[0191]** Bei der zwölften Ausführungsform wurde keine Anodenschicht **3** des p-Typs beschrieben. Zur Herstellung der Anodenschicht **3** des p-Typs werden Verunreinigungen des p-Typs mit höherer Verunreinigungskonzentration selektiv in die Oberfläche des Implantierungsbereiches der Verunreinigungen I<sub>p</sub> des p-Typs implantiert, beispielsweise nach dem in [Fig. 32E](#) dargestellten Schritt.

**[0192]** [Fig. 33](#) zeigt eine Abänderung der zwölften Ausführungsform. Bei diesem Bauteil sind fünf Ausnehmungen vorgesehen, die jeweils eine Stufe aufweisen, jedoch ist die Anzahl der Stufen nicht auf diesen Wert beschränkt. Da diese Anordnung die Basis des Hauptbauteilbereichs im wesentlichen dünn ausbilden kann, lassen sich dieselben Auswirkungen erzielen, wie sie voranstehend bereits beschrieben wurden.

#### (DREIZEHNTEN AUSFÜHRUNGSFORM)

**[0193]** [Fig. 34](#) ist eine Schnittansicht des Hauptteils eines Hochspannungshalbleitergeräts gemäß der dreizehnten Ausführungsform der vorliegenden Erfindung.

**[0194]** Die dreizehnte Ausführungsform unterscheidet sich von der zwölften Ausführungsform im Hinblick auf die Abwesenheit irgendeiner stark dotierten

Anodenschicht **3** des p-Typs. Da mit diesem Aufbau die Oberflächenkonzentration einer Anodenschicht **2** des p-Typs verringert werden kann, läßt sich eine Diode erhalten, bei welcher der maximale Rückwärtsstrom bei der Rückwärtserholung der Diode verringert ist, um so die Rückwärtswiederherstellungsverluste zu verringern. Bei der dreizehnten Ausführungsform ist die Fläche der Anodenschicht des p-Typs so gewählt, daß sie größer ist als bei der sechsten Ausführungsform, so daß die Vorwärtsspannung V<sub>F</sub> niedrig gehalten werden kann.

#### (VIERZEHNTE AUSFÜHRUNGSFORM)

**[0195]** [Fig. 35](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergeräts gemäß der vierzehnten Ausführungsform der vorliegenden Erfindung.

**[0196]** Die vierzehnte Ausführungsform zeichnet sich zusätzlich zu den Merkmalen des Bauteils in [Fig. 24](#) dadurch aus, daß eine stark dotierte Kathodenschicht **14** des n-Typs auf der Oberfläche einer Kathodenschicht **7** des n-Typs in Kontakt mit der Bodenwand und der Seitenwand einer Ausnehmung in einer rückwärtigen Oberfläche ausgebildet wird. Diese Anordnung erhöht den Injektionswirkungsgrad für Elektronen, und ist besonders wirksam zur Verringerung des Spannungsabfalls in Vorwärtsrichtung.

**[0197]** [Fig. 36](#) zeigt eine Abänderung der vierzehnten Ausführungsform. Bei diesem Bauteil sind drei Ausnehmungen, die jeweils eine Stufe aufweisen, in der rückwärtigen Oberfläche vorgesehen. Die Anzahl der Ausnehmungen kann auch zwei oder vier oder mehr als vier betragen.

#### (FÜNFZEHNTE AUSFÜHRUNGSFORM)

**[0198]** [Fig. 37](#) zeigt als Schnittansicht das Hauptteil eines Hochspannungshalbleitergeräts gemäß der fünfzehnten Ausführungsform der vorliegenden Erfindung. Die fünfzehnte Ausführungsform zeichnet sich dadurch aus, daß die stark dotierte Kathodenschicht **14** des n-Typs bei dem Hochspannungshalbleitergerät gemäß der vierzehnten Ausführungsform weggelassen ist, wodurch der Aufbau des Bauteils vereinfacht wird.

**[0199]** Wie voranstehend geschildert kann gemäß der ersten Zielrichtung der vorliegenden Erfindung durch Ausbildung einer Ausnehmung in einem Halbleitersubstrat der Bereich, in welchem ein Hochspannungshalbleiterbauteil ausgebildet werden soll, dünn ausgebildet werden, und wird eine Feldrelaxationsnordnung eingesetzt, die mehrere Stufen an der Grenzfläche zwischen der Ausnehmung und dem Halbleitersubstrat aufweist. Daher läßt sich ein Hochspannungshalbleitergerät erhalten, welches jegliche Beeinträchtigung der Bauteileigenschaften verhin-

dern kann, beispielsweise einen Spannungsabfall in Vorwärtsrichtung, Rückwärtswiederherstellungsverluste, und dergleichen des Hochspannungshalbleiterbauteils, selbst wenn die Feldrelaxationsanordnung verwendet wird, und ist das Halbleitersubstrat dick ausgebildet, um die nötige Spannungsfestigkeit sicherzustellen.

**[0200]** Nachstehend werden Ausführungsform (sechzehnte bis einundzwanzigste Ausführungsform) gemäß der zweiten Zielrichtung der vorliegenden Erfindung beschrieben. Obwohl der erste Leitfähigkeitsyp der n-Typ ist, und der zweite Leitfähigkeitsyp bei diesen Ausführungsformen der p-Typ ist, lassen sie sich umkehren. Gleiche Bezugszeichen bezeichnen gleiche oder entsprechende Teile, und insoweit erfolgt nachstehend nicht unbedingt eine erneute Beschreibung.

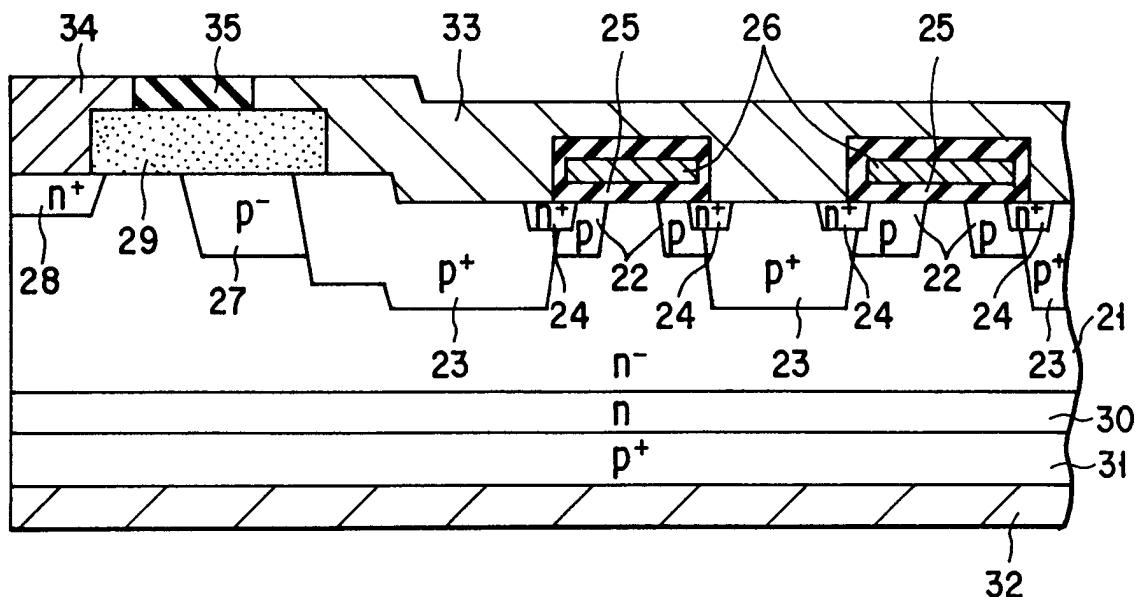

(SECHZEHNTE AUSFÜHRUNGSFORM)

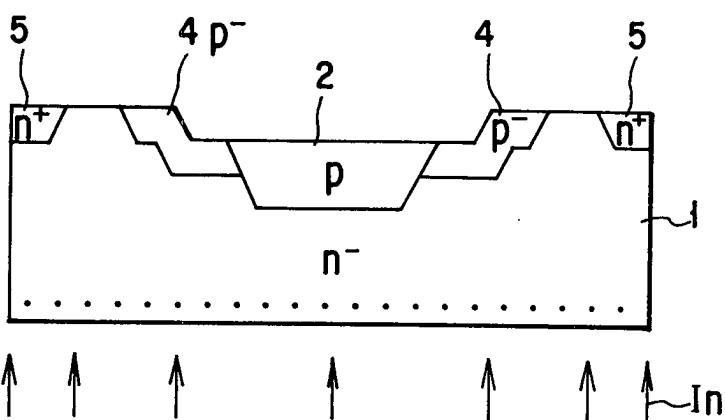

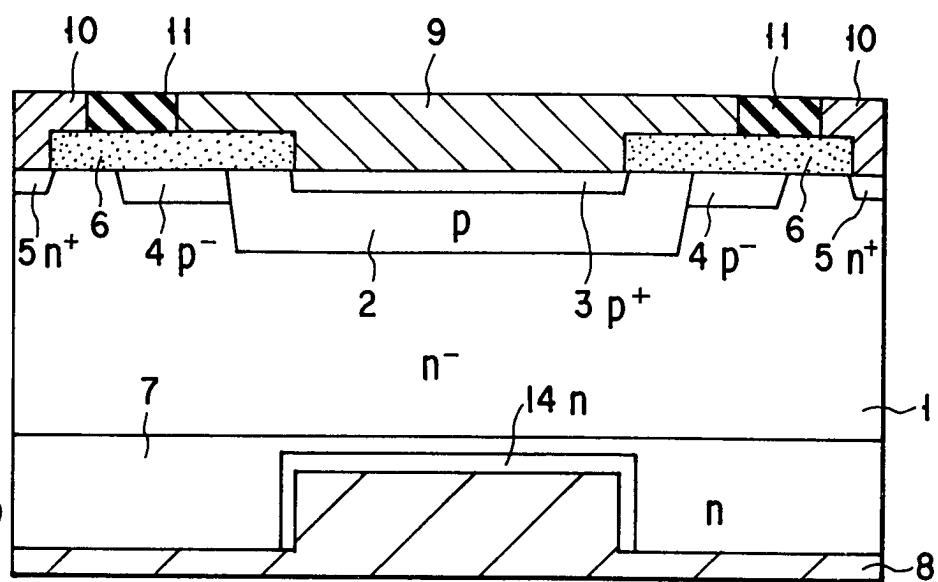

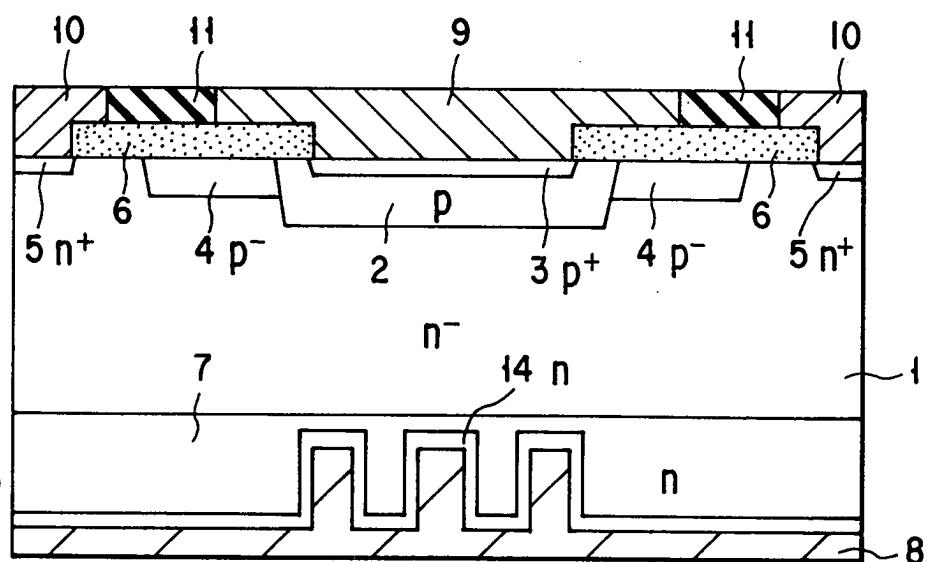

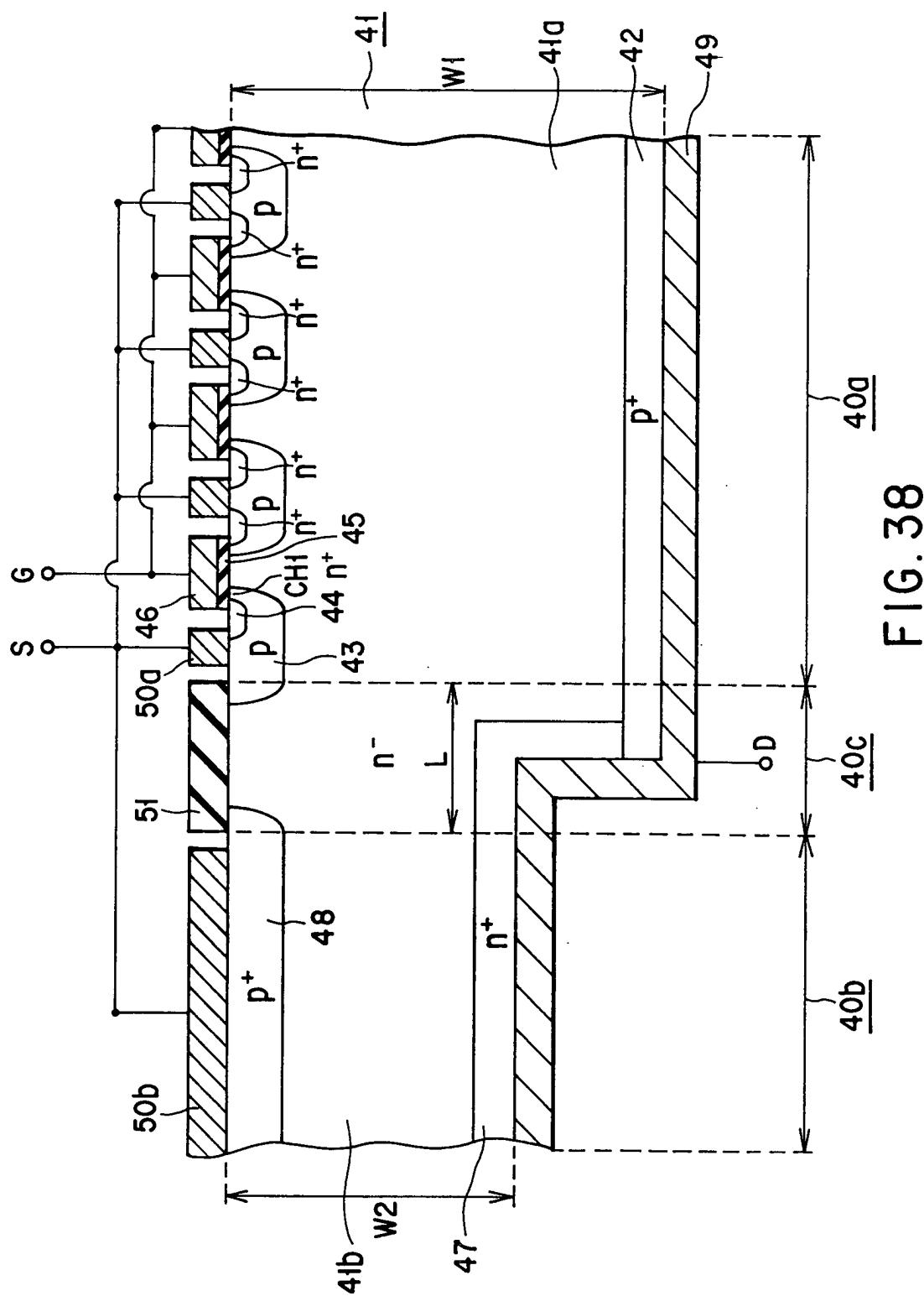

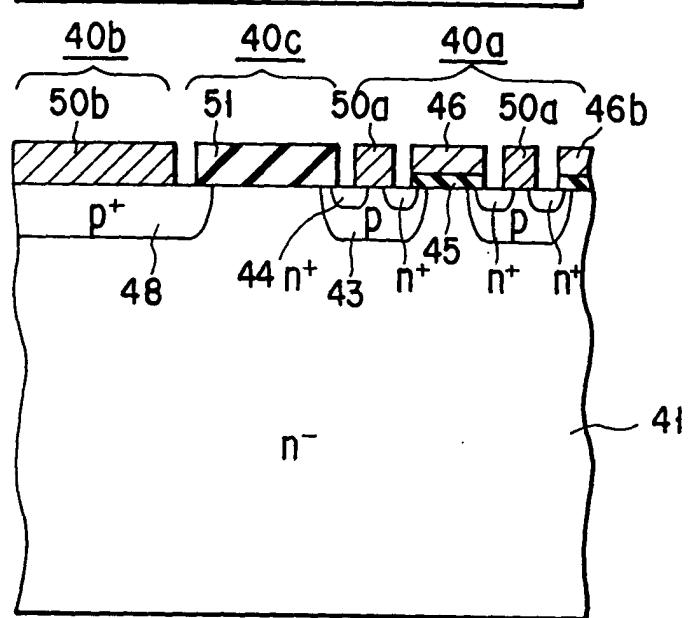

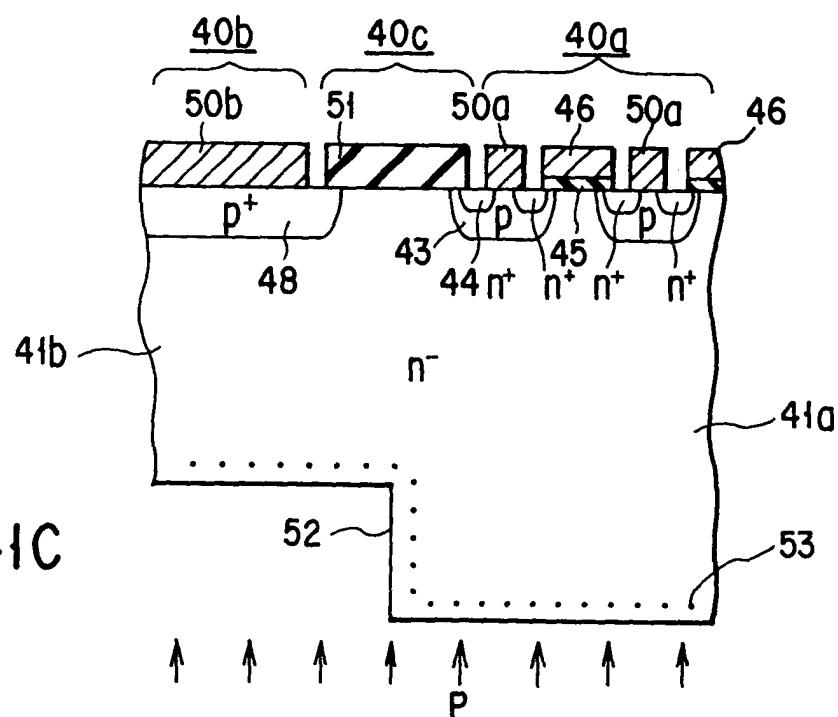

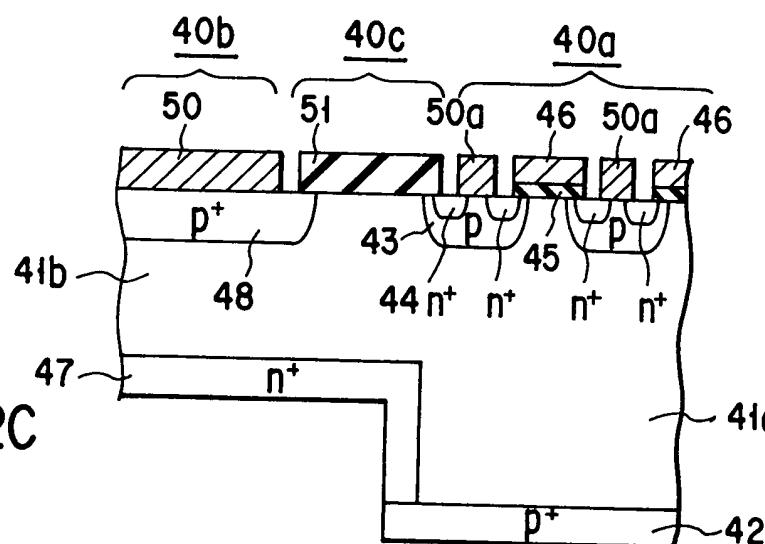

**[0201]** [Fig. 38](#) zeigt als Schnittansicht ein Leistungshalbleitergerät gemäß der sechzehnten Ausführungsform der vorliegenden Erfindung. In [Fig. 38](#) ist mit dem Bezugszeichen **41** eine Basisschicht des n-Typs mit hohem Widerstand (Halbleitersubstrat) bezeichnet. Eine Ausnehmung wird selektiv in einer Oberfläche (der rückwärtigen Oberfläche) der Basisschicht **41** des n-Typs hergestellt.

**[0202]** Eine Drainschicht **42** des p-Typs wird auf der rückwärtigen Oberfläche der Basisschicht **41** des n-Typs in dem Bereich hergestellt, in welchem keine Ausnehmung vorgesehen ist, wogegen Basisschichten **43** des p-Typs auf der anderen Oberfläche (der vorderen Oberfläche) der Basisschicht **41** des n-Typs hergestellt werden. Eine Sourceschicht **44** des n-Typs wird in jeder Basisschicht **43** des p-Typs ausgebildet. Eine Gateelektrode **46** wird über einen Gateisolierfilm **45** auf der Basisschicht **43** des p-Typs zwischen der Basisschicht **41** des n-Typs und der Sourceschicht **44** des n-Typs ausgebildet. Die Gateelektrode **46**, der Gateisolierfilm **45**, die Basisschicht **43** des p-Typs, die Basisschicht **41** des n-Typs, und die Sourceschicht **44** des n-Typs bilden einen Elektroneninjektions-MOSFET, der einen Kanalbereich CH1 aufweist.

**[0203]** Eine Kathodenschicht **47** des n-Typs wird auf der Bodenoberfläche (rückwärtigen Oberfläche) und der Seitenwand der Ausnehmung in der Basisschicht **41** des n-Typs hergestellt. Eine Anodenschicht **48** des p-Typs wird in dem Bereich der anderen Oberfläche (der vorderen Oberfläche) der Basisschicht **41** des n-Typs hergestellt, welcher der Ausnehmung gegenüberliegt.

**[0204]** Eine Drainelektrode (zweite Haupteletrode) **49** wird auf der Drainschicht **42** des p-Typs und der Kathodenschicht **47** des n-Typs so ausgebildet, daß

sie in Kontakt mit beiden Schichten **42** und **47** steht. Eine Sourceelektrode **50a** wird auf jeder Sourceschicht **44** des n-Typs und einer entsprechenden Basisschicht **43** des p-Typs so ausgebildet, daß sie in Kontakt mit diesen Schichten steht. Eine Sourceelektrode (Anodenelektrode) **50b** wird auf der Anodenschicht **48** des p-Typs hergestellt. Die Elektroden **50a** und **50b** bilden die erste Haupteletrode, und die Gateelektrode **46** dient als Unterelektrode. Mehrere Sourceelektroden und mehrere Gateelektroden sind miteinander verbunden, und diese Verbindung ist schematisch in [Fig. 38](#) dargestellt.

**[0205]** Bei der voranstehenden Anordnung wird eine Diode in einem Bereich **40b** hergestellt, in welchem die Ausnehmung vorgesehen ist, und wird ein IGBT in einem Bereich **40a** hergestellt, in welchem keine Ausnehmung vorgesehen ist.

**[0206]** Ein Isolationsbereich **40c** unterhalb eines Isolierfilms **51**, der sandwichartig zwischen dem IGBT-Bereich **40a** und dem Diodenbereich **40b** eingeschlossen ist, dient als Isolationsbereich für den IGBT und die Diode. Die Breite L des Bereichs **40c** ist vorzugsweise so gewählt, daß sie gleich einer Ladungsträgerdiffusionslänge  $L_d$  oder größer ist. Wenn  $\tau$  die Lebensdauer eines Ladungsträgers ist, und  $D$  der Diffusionskoeffizient, wird folgende Beziehung erfüllt:

$$L > K_d = (D \tau)^{1/2}$$

**[0207]** Alternativ hierzu kann der Isolationsbereich **40c** sogenannte "Lebensdauermörder" (die nachstehend noch genauer erläutert werden) enthalten.

**[0208]** Als nächstes wird der Betriebsablauf bei diesem Halbleitergerät geschildert. Wenn positive und negative Spannungen an die Drainelektrode **49** bzw. die Sourceelektrode **50a** angelegt werden, und wenn eine positive Spannung in Bezug auf die Source an die Gateelektrode **46** angelegt wird, kehrt sich der Leitungstyp der Basisschicht **43** des p-Typs um, welche in Kontakt mit der Gateelektrode **46** steht, und werden Elektronen  $d$  von der Sourceschicht **44** des n-Typs in eine Basisschicht **41a** des n-Typs über die Schicht mit den umgekehrten Eigenschaften injiziert, so daß sie die Drainschicht **42** des p-Typs erreichen. Gleichzeitig werden Löcher  $h$  von der Drainschicht **42** des p-Typs in die Basisschicht **41** des n-Typs injiziert. Auf diese Weise werden sowohl die Elektronen  $e$  als auch die Löcher  $h$  in die Basisschicht **41** des n-Typs injiziert, so daß sie eine Leitfähigkeitsmodulation hervorrufen, und die Einschaltspannung verringern.

**[0209]** In einem Abschaltvorgang wird eine negative Spannung in Bezug auf die Source an die Gateelektrode **46** angelegt. Dann verschwindet die Schicht mit den entgegengesetzten Eigenschaften, die sich unmittelbar unterhalb der Gateelektrode **46** ausgebildet

hatte, so daß die Injektion von Elektronen aufhört. Einige der Löcher  $h$  in der Basisschicht **41a** des n-Typs werden über die Basisschicht **43** des p-Typs an die Sourceelektrode **50a** abgegeben, und die übrigen Löcher  $h$  rekombinieren mit den Elektronen  $e$  und verschwinden. Daher wird das Halbleitergerät abgeschaltet.