(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6809489号

(P6809489)

(45) 発行日 令和3年1月6日(2021.1.6)

(24) 登録日 令和2年12月14日(2020.12.14)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

C

請求項の数 6 (全 20 頁)

(21) 出願番号 特願2018-10547 (P2018-10547)

(22) 出願日 平成30年1月25日 (2018.1.25)

(65) 公開番号 特開2019-129631 (P2019-129631A)

(43) 公開日 令和1年8月1日 (2019.8.1)

審査請求日 令和2年3月13日 (2020.3.13)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110000567

特許業務法人 サトー国際特許事務所

(72) 発明者 山中 豊

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

審査官 山崎 雄司

最終頁に続く

(54) 【発明の名称】昇圧型スイッチング電源回路

## (57) 【特許請求の範囲】

## 【請求項 1】

インダクタ(L1)と、オンすることにより前記インダクタに流れる電流を増加させるスイッチング素子(Q4)と、を備え、入力端子(5)を介して供給される入力電圧を昇圧する昇圧動作を行う昇圧型スイッチング電源回路(8、22、32、42、52、62、72、82)であって、

前記スイッチング素子の駆動を制御して前記昇圧動作を実行する昇圧制御回路(12)と、

前記スイッチング素子の駆動を制御して前記スイッチング素子の故障を検出する故障検出制御回路(15、64、83)と、

前記スイッチング素子に流れる電流を検出する電流検出部(19、33、43、63、73)と、

前記昇圧制御回路および前記故障検出制御回路のうちいずれか一方が前記スイッチング素子の駆動を制御可能となるように切り替えを行う切替部(16)と、

を備え、

前記昇圧動作の実行に先立って、

前記切替部は、前記故障検出制御回路により前記スイッチング素子の駆動が制御されるように切り替えを行い、

前記故障検出制御回路は、前記スイッチング素子をオン駆動し、前記電流検出部による電流の検出結果に基づいて前記スイッチング素子のオープン故障を検出し、

10

20

前記昇圧制御回路は、前記スイッチング素子の駆動を制御するための制御信号を出力し

前記故障検出制御回路は、前記スイッチング素子の駆動を制御するための制御信号を出力し、

前記切替部は、前記昇圧制御回路および前記故障検出制御回路から出力される各制御信号のうちいずれか一方を出力する切替動作を行うセレクタを備え、前記セレクタから出力される制御信号に基づいて前記スイッチング素子が駆動されることにより、前記昇圧制御回路および前記故障検出制御回路のうちいずれか一方が前記スイッチング素子の駆動を制御可能となるように切り替えを行う昇圧型スイッチング電源回路。

**【請求項 2】**

10

さらに、前記入力端子から前記インダクタへと至る電源供給経路に直列に介在する通断電用スイッチを備え、

前記通断電用スイッチ（Q1、Q2）のオンとオフは、前記故障検出制御回路により制御され、

前記昇圧動作の実行に先立って、

前記故障検出制御回路は、前記通断電用スイッチをオンし、前記電流検出部による電流の検出結果に基づいて前記スイッチング素子のショート故障を検出する請求項1に記載の昇圧型スイッチング電源回路。

**【請求項 3】**

20

前記故障検出制御回路は、前記スイッチング素子のオープン故障の検出に先立って、前記スイッチング素子のショート故障の検出を行う請求項2に記載の昇圧型スイッチング電源回路。

**【請求項 4】**

前記電流検出部（33、43、63）は、前記スイッチング素子とグランドとの間に直列に介在するように設けられたシャント抵抗（R1）と、前記シャント抵抗の端子電圧に基づいて前記スイッチング素子に流れる電流を検出する検出回路（13、65）と、を備え、

前記検出回路は、前記グランドを基準電位として動作するようになっている請求項1から3のいずれか一項に記載の昇圧型スイッチング電源回路。

**【請求項 5】**

30

前記電流検出部（43、63、73）は、

前記スイッチング素子に流れる電流が流れる経路に直列に介在するように設けられたシャント抵抗（R1、R71）と、

前記シャント抵抗の端子電圧を増幅する増幅回路（44）と、

前記増幅回路の出力電圧に基づいて前記スイッチング素子に流れる電流を検出する検出回路（13、65、74）と、

を備える請求項1から3のいずれか一項に記載の昇圧型スイッチング電源回路。

**【請求項 6】**

さらに、前記スイッチング素子に過電流判定閾値を超える過大な電流が流れたことを検出する過電流検出回路（64）を備え、

40

前記電流検出部（63）は、前記過電流検出回路の構成の少なくとも一部を共用化することにより構成されている請求項1から5のいずれか一項に記載の昇圧型スイッチング電源回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、昇圧動作を行う昇圧型スイッチング電源回路に関する。

**【背景技術】**

**【0002】**

例えば特許文献1に開示されているように、車両に搭載される電子制御装置には、昇圧

50

型スイッチング電源回路が設けられている。なお、以下、電子制御装置のことをＥＣＵとも称するとともに、昇圧型スイッチング電源回路のことを昇圧電源とも称する。近年、電子製品の機能安全への対応として、ＥＣＵに実装された昇圧電源を含む各ディスクリート部品を、製品として出荷された後の実動作時に部品外れや故障などが発生していないかどうかをセルフチェックする機能が求められている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010-229877号公報

【発明の概要】

10

【発明が解決しようとする課題】

【0004】

昇圧電源が備えるMOSトランジスタなどのスイッチング素子が故障しているか否かを確認する場合、昇圧電源を実際に動作させる必要がある。しかし、ＥＣＵに設けられる昇圧電源は、例えばクランキングなどによりバッテリ電圧が一時的に低下したときに補助的に動作するような使用方法が多い。そのため、他の主たる電源回路が動作している場合、昇圧電源が動作しなくなることから、上記故障を確認することが困難であった。

【0005】

そこで、昇圧電源の出力目標値を意図的に高めることにより、主たる電源回路の動作中においても昇圧電源を強制的に動作させるといった方法が考えられる。しかし、このような方法を採用するためには、フィードバック系の回路に大幅な変更および追加を加える必要があるため、回路規模の大幅な増加を招くという別の問題が生じる。

20

【0006】

本発明は上記事情に鑑みてなされたものであり、その目的は、回路規模の大幅な増加を招くことなく、スイッチング素子の故障を検出することができる昇圧型スイッチング電源回路を提供することにある。

【課題を解決するための手段】

【0007】

請求項1に記載の昇圧型スイッチング電源回路(8、22、32、42、52、62、72、82)は、インダクタ(L1)と、オンすることによりインダクタに流れる電流を増加させるスイッチング素子(Q4)と、を備え、入力端子(5)を介して供給される入力電圧を昇圧する昇圧動作を行う。このような昇圧型スイッチング電源回路は、昇圧制御回路(12)、故障検出制御回路(15、64、83)、電流検出部(19、33、43、63、73)および切替部(16)を備える。昇圧制御回路は、スイッチング素子の駆動を制御して昇圧動作を実行する。故障検出制御回路は、スイッチング素子の駆動を制御してスイッチング素子の故障を検出する。電流検出部は、スイッチング素子に流れる電流を検出する。切替部は、昇圧制御回路および故障検出制御回路のうちいずれか一方がスイッチング素子の駆動を制御可能となるように切り替えを行う。この場合、昇圧制御回路は、スイッチング素子の駆動を制御するための制御信号を出力する。また、この場合、故障検出制御回路は、スイッチング素子の駆動を制御するための制御信号を出力する。そして、切替部は、昇圧制御回路および故障検出制御回路から出力される各制御信号のうちいずれか一方を出力する切替動作を行うセレクタを備え、セレクタから出力される制御信号に基づいてスイッチング素子が駆動されることにより、昇圧制御回路および故障検出制御回路のうちいずれか一方がスイッチング素子の駆動を制御可能となるように切り替えを行う

30

【0008】

上記構成では、昇圧動作の実行に先立って、切替部は、故障検出制御回路によりスイッチング素子の駆動が制御されるように切り替えを行う。そして、故障検出制御回路は、スイッチング素子をオン駆動し、電流検出部による電流の検出結果に基づいてスイッチング素子のオープン故障を検出する。上記構成において、スイッチング素子がオープン故障し

40

50

ている場合、そのスイッチング素子がオン駆動されたとしても、そのスイッチング素子に流れる電流は増加する事がない。そのため、上記オープン故障の検出では、例えば電流検出部による電流の検出値が所定の閾値に達しない場合にスイッチング素子がオープン故障していると判断することができる。

#### 【0009】

このようにすれば、実際の昇圧動作を実行することなく、スイッチング素子のオープン故障を検出することが可能となる。そして、この場合、従来の昇圧型スイッチング電源回路の構成に対し、故障検出制御回路を追加することにより、上記オープン故障の検出が可能となっており、フィードバック系の回路に大幅な変更および追加を加える必要がない。したがって、上記構成によれば、回路規模の大幅な増加を招くことなく、スイッチング素子の故障を検出することができるという優れた効果が得られる。10

#### 【0010】

請求項2に記載の昇圧型スイッチング電源回路は、さらに、入力端子からインダクタへと至る電源供給経路に直列に介在する通断電用スイッチを備える。その通断電用スイッチのオンとオフは、故障検出制御回路により制御される。この場合、昇圧動作の実行に先立って、故障検出制御回路は、通断電用スイッチをオンし、電流検出部による電流の検出結果に基づいてスイッチング素子のショート故障を検出する。

#### 【0011】

上記構成において、スイッチング素子がショート故障している場合、通断電用スイッチがオンされると、上記スイッチング素子がオン駆動されていないにもかかわらず、そのスイッチング素子に流れる電流が増加する。そのため、上記ショート故障の検出では、例えば電流検出部による電流の検出値が所定の閾値に達した場合にスイッチング素子がショート故障していると判断することができる。このようにすれば、実際の昇圧動作を実行することなく、スイッチング素子のオープン故障に加えてショート故障についても検出することができる。20

#### 【図面の簡単な説明】

#### 【0012】

【図1】第1実施形態に係る電源システムの構成を模式的に示す図

【図2】第1実施形態に係る故障検出処理の内容を模式的に示す図

【図3】第1実施形態に係る正常時における電源回路の動作を説明するためのものであり、各部の信号の波形を模式的に示す図30

【図4】第1実施形態に係る検出閾値の具体的な設定例を説明するためのものであり、発生電流を模式的に示す図

【図5】第1実施形態に係るショート故障発生時における電源回路の動作を説明するためのものであり、各部の信号の波形を模式的に示す図

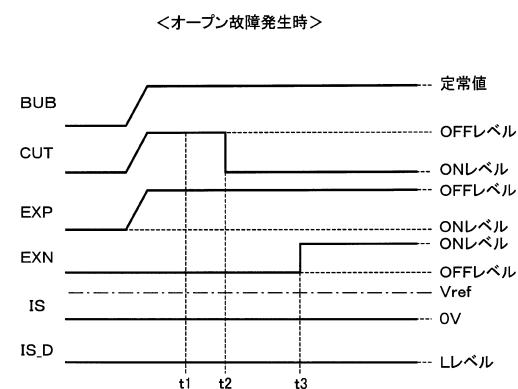

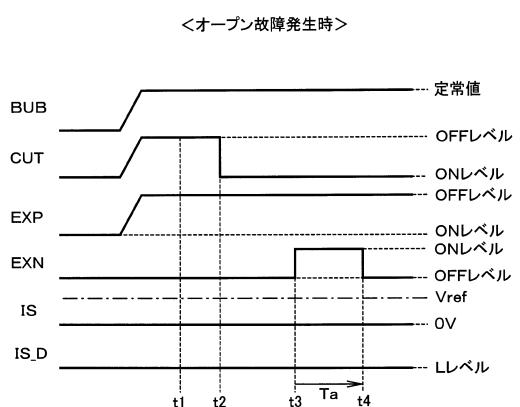

【図6】第1実施形態に係るオープン故障発生時における電源回路の動作を説明するためのものであり、各部の信号の波形を模式的に示す図

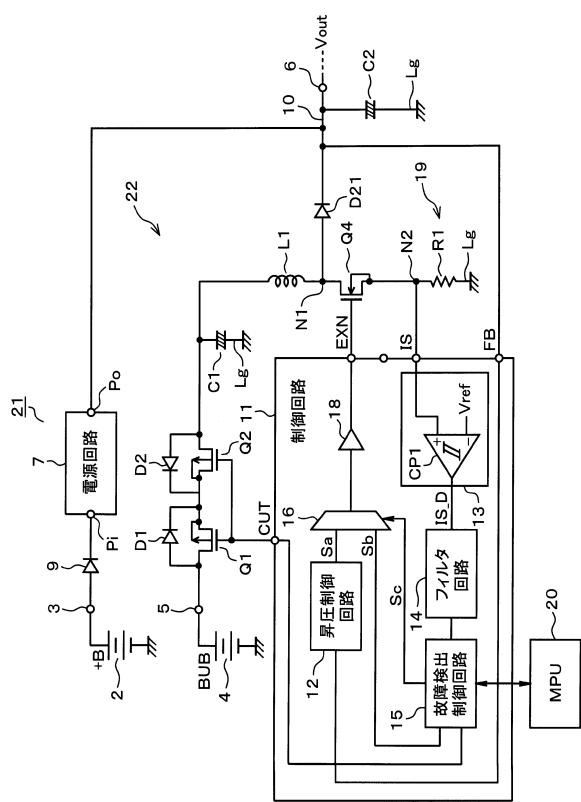

【図7】第2実施形態に係る電源システムの構成を模式的に示す図

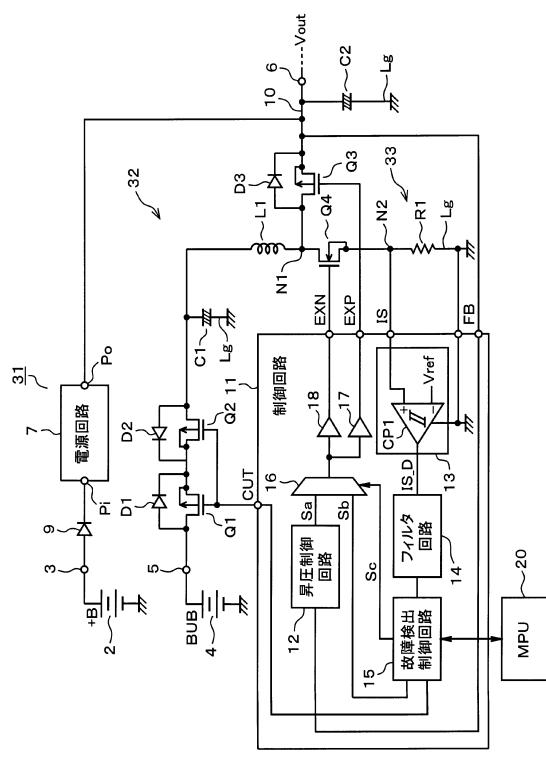

【図8】第3実施形態に係る電源システムの構成を模式的に示す図

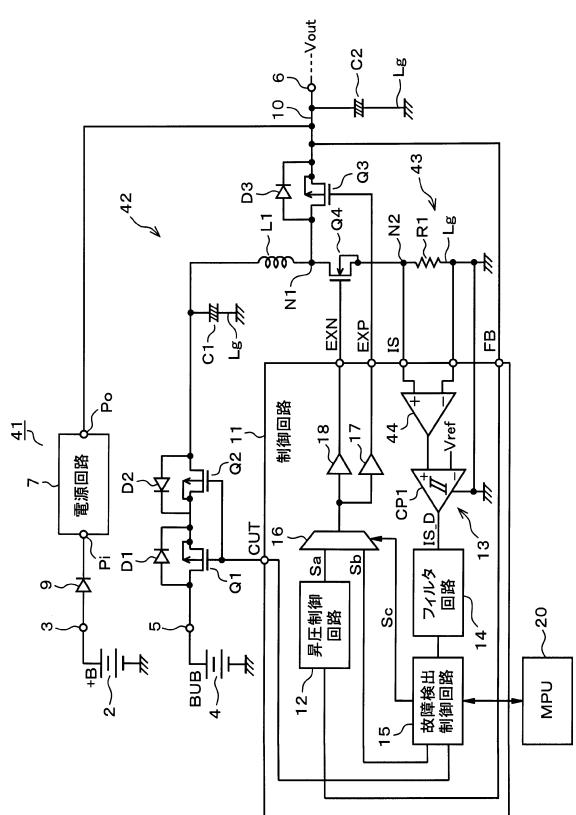

【図9】第4実施形態に係る電源システムの構成を模式的に示す図40

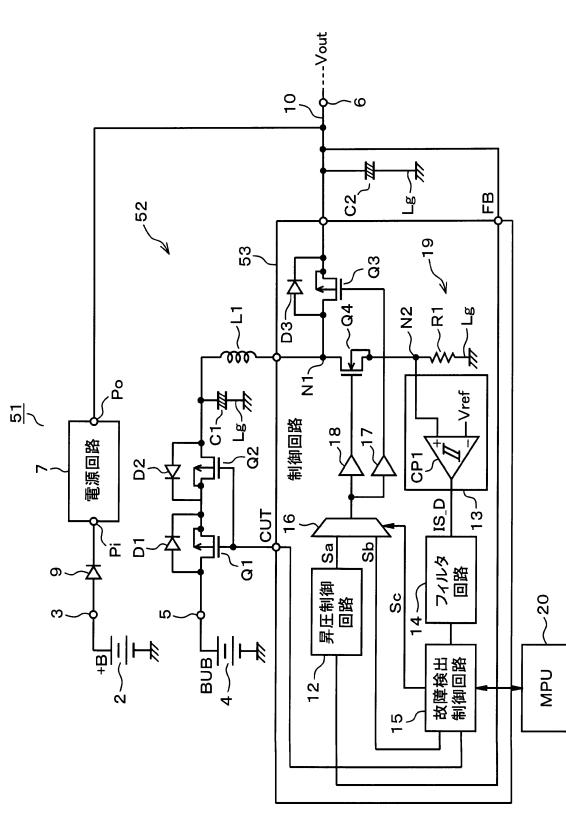

【図10】第5実施形態に係る電源システムの構成を模式的に示す図

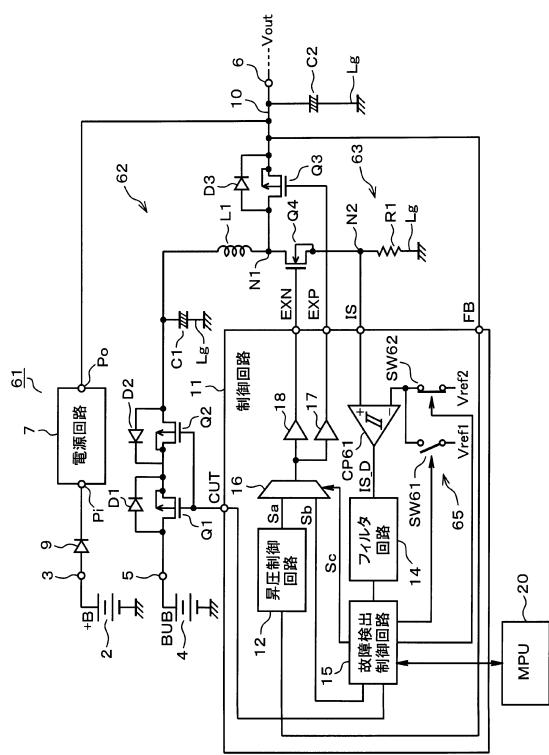

【図11】第6実施形態に係る電源システムの構成を模式的に示す図

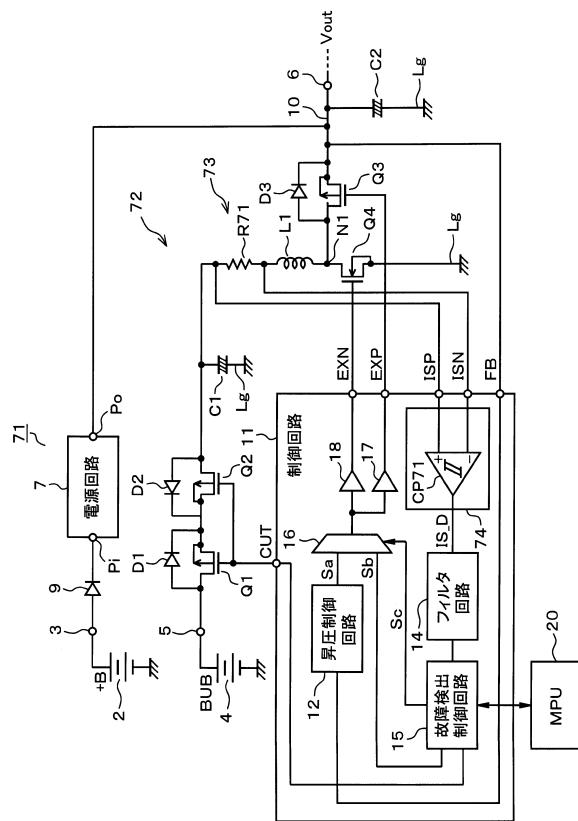

【図12】第7実施形態に係る電源システムの構成を模式的に示す図

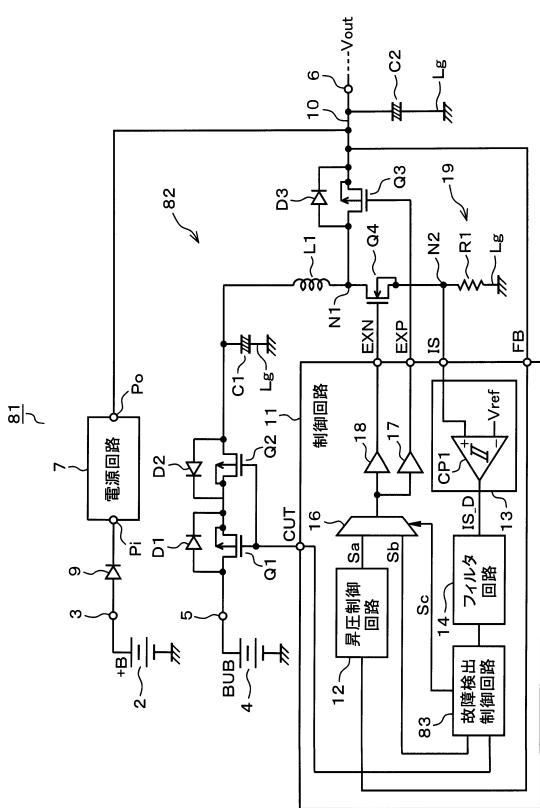

【図13】第8実施形態に係る電源システムの構成を模式的に示す図

【図14】第8実施形態に係るオープン故障発生時における電源回路の動作を説明するためのものであり、各部の信号の波形を模式的に示す図

#### 【発明を実施するための形態】

#### 【0013】

以下、複数の実施形態について図面を参照して説明する。なお、各実施形態において実質的に同一の構成には同一の符号を付して説明を省略する。50

(第1実施形態)

以下、第1実施形態について図1～図6を参照して説明する。

図1に示す電源システム1は、車両に搭載されるData Communication Module、つまりDCMと称される無線通信ECUに用いられる。

【0014】

電源システム1には、車両に搭載された車両バッテリ2から入力端子3を介して電圧+Bが供給されるとともに、車両に搭載されたバックアップバッテリ4から入力端子5を介して電圧BUBが供給される。なお、バックアップバッテリ4は、例えばリチウムイオン電池などから構成されている。電源システム1は、電圧+Bまたは電圧BUBから上記無線通信ECUの各構成の電源電圧となる出力電圧Voutを生成し、出力端子6を介して出力する。なお、出力電圧Voutの目標値は、例えば+5Vとなっている。10

【0015】

電源システム1は、2つの電源回路7、8を備えている。電源回路7は、車両バッテリ2から供給される電圧+Bを降圧して出力する降圧型のDC/DCコンバータである。この場合、電源回路7は、電圧+Bが正常と考えられる範囲の電圧値である期間、つまり定常時に動作するものであり、電源システム1における主たる電源回路である。

【0016】

一方、電源回路8は、バックアップバッテリ4から供給される電圧BUBを昇圧して出力する昇圧型スイッチング電源回路である。なお、詳細な構成は後述するが、本実施形態の電源回路8は、同期整流構成となっている。この場合、電源回路8は、例えばクランкиングなどにより電圧+Bの電圧値が出力電圧Voutの目標値未満にまで低下した場合、車両バッテリ2が車両から外された場合などの異常時に動作するものであり、電源システム1における補助的な電源回路である。20

【0017】

電源回路7の入力端子Piは、逆流阻止用のダイオード9を逆方向に介して電源システム1の入力端子3に接続されている。電源回路7の出力端子Poは、電源線10に接続されている。なお、電源線10は、電源システム1の出力端子6に接続されている。電源回路7の出力電圧の目標値は、電源システム1の出力電圧Voutの目標値と同様の値(例えば+5V)となっている。

【0018】

電源回路8は、入力端子5を介して供給される入力電圧である電圧BUBを昇圧する昇圧動作を行うものであり、トランジスタQ1～Q4、インダクタL1、コンデンサC1、C2、抵抗R1および制御回路11などを備えている。トランジスタQ1、Q2は、いずれもPチャネル型のMOSトランジスタである。トランジスタQ1、Q2の各ドレイン・ソース間には、ドレイン側をアノードとしたボディダイオードD1、D2が接続されている。30

【0019】

トランジスタQ1、Q2は、互いのソースが共通接続されている。トランジスタQ1のドレインは、入力端子5に接続されている。トランジスタQ2のドレインは、コンデンサC1を介して回路の基準電位となるグランド電位(0V)が与えられるグランド線Lgに接続されている。また、トランジスタQ2のドレインは、インダクタL1を介してノードN1に接続されている。トランジスタQ1、Q2の各ゲートには、制御回路11から出力される駆動信号CUTが与えられている。これにより、トランジスタQ1、Q2の駆動は、制御回路11により制御される。40

【0020】

トランジスタQ3は、Pチャネル型のMOSトランジスタであり、そのドレイン・ソース間には、ドレイン側をアノードとしたボディダイオードD3が接続されている。トランジスタQ3のドレインはノードN1に接続され、そのソースは電源線10に接続されている。トランジスタQ3のゲートには、制御回路11から出力される駆動信号EXPが与えられている。これにより、トランジスタQ3の駆動は、制御回路11により制御される。50

電源線 1 0 およびグランド線 L g の間には、出力電圧 V<sub>out</sub>を平滑するためのコンデンサ C 2 が接続されている。

#### 【 0 0 2 1 】

トランジスタ Q 4 は、N チャネル型の M O S トランジスタであり、そのドレインはノード N 1 に接続されている。トランジスタ Q 4 のソースは、電流検出用の抵抗 R 1 を介してグランド線 L g に接続されている。トランジスタ Q 4 のゲートには、制御回路 1 1 から出力される駆動信号 E X N が与えられている。これにより、トランジスタ Q 4 の駆動は、制御回路 1 1 により制御される。

#### 【 0 0 2 2 】

トランジスタ Q 4 および抵抗 R 1 の相互接続点であるノード N 2 の電圧は、トランジスタ Q 4 に流れる電流に対応した電圧信号である電流検出信号 I<sub>S</sub> として、制御回路 1 1 に入力されている。また、電源線 1 0 の電圧そのもの、または電源線 1 0 の電圧を分圧した電圧は、出力電圧 V<sub>out</sub> に対応した電圧信号である電圧検出信号 F<sub>B</sub> として、制御回路 1 1 に入力されている。制御回路 1 1 は、電圧検出信号 F<sub>B</sub> に基づいて、出力電圧 V<sub>out</sub> を目標値に一致させるようにフィードバック制御を行う。

10

#### 【 0 0 2 3 】

上記構成において、トランジスタ Q 1、Q 2 は、入力端子 5 からインダクタ L 1 へと至る電源供給経路に直列に介在する通断電用スイッチに相当する。また、上記構成において、トランジスタ Q 4 は、オンされることによりインダクタ L 1 に流れる電流を増加させるスイッチング素子に相当する。さらに、上記構成において、抵抗 R 1 は、スイッチング素子とグランドとの間に直列に介在するように設けられたシャント抵抗に相当する。

20

#### 【 0 0 2 4 】

なお、この場合、トランジスタ Q 1、Q 2 は、入力端子 5 およびインダクタ L 1 の間に、それぞれのボディダイオード D 1、D 2 が互いに逆向きとなるように直列接続されている。このような構成によれば、トランジスタ Q 1、Q 2 がオフされると、ボディダイオード D 1、D 2 を経由して電流が流れることも防止されるため、入力端子 5 からインダクタ L 1 へと至る電源供給経路を完全に遮断することができる。

#### 【 0 0 2 5 】

制御回路 1 1 は、例えば Application Specific Integrated Circuit、つまり A S I C により構成されている。制御回路 1 1 は、昇圧制御回路 1 2、検出回路 1 3、フィルタ回路 1 4、故障検出制御回路 1 5、セレクタ 1 6 およびプリドライバ 1 7、1 8 を備えている。図示は省略しているが、制御回路 1 1 には、電圧 B U B または電圧 B U B に基づいて生成される電圧が電源電圧として供給されている。制御回路 1 1 は、このような電源電圧の供給を受けて動作する構成となっている。

30

#### 【 0 0 2 6 】

昇圧制御回路 1 2 は、トランジスタ Q 3、Q 4 の駆動を制御して昇圧動作を実行するものであり、例えばロジック回路により構成されている。昇圧制御回路 1 2 は、電圧検出信号 F<sub>B</sub> に基づいてトランジスタ Q 3、Q 4 の駆動を制御するための制御信号 S<sub>a</sub> を生成して出力する。

#### 【 0 0 2 7 】

40

この場合、トランジスタ Q 3、Q 4 は、一方がオンされるときには他方がオフされる、つまり相補的にオンオフされる。なお、「相補的にオンオフされる」とは、双方のスイッチがオフする期間、いわゆるデッドタイムを設けるケースを除外するものではない。昇圧制御回路 1 2 から出力される制御信号 S<sub>a</sub> は、セレクタ 1 6 の一方の入力端子に入力される。

#### 【 0 0 2 8 】

検出回路 1 3 は、抵抗 R 1 の端子電圧に基づいてトランジスタ Q 4 に流れる電流を検出するもので、ヒステリシス付きのコンパレータ C P 1 を備えている。コンパレータ C P 1 の非反転入力端子には電流検出信号 I<sub>S</sub> が入力され、その反転入力端子には基準電圧 V<sub>ref</sub> が入力される。基準電圧 V<sub>ref</sub> は、図示しない基準電圧生成回路により生成されるもので

50

あり、トランジスタ Q 4 に流れる電流の検出閾値に対応した電圧である。なお、検出閾値は、後述するトランジスタ Q 4 の故障検出などに用いられる。

#### 【 0 0 2 9 】

上記構成によれば、コンパレータ C P 1 の出力信号 I S \_ D は、電流検出信号 I S が基準電圧 V ref を下回るとロウレベル（例えば 0 V）になり、電流検出信号 I S が基準電圧 V ref を上回るとハイレベル（例えば + 5 V）になる。以下、ロウレベルを L レベルと称するとともに、ハイレベルを H レベルと称する。この場合、抵抗 R 1 および検出回路 1 3 により、トランジスタ Q 4 に流れる電流を検出する電流検出部 1 9 が構成される。

#### 【 0 0 3 0 】

フィルタ回路 1 4 は、例えばローパスフィルタであり、コンパレータ C P 1 の出力信号 I S \_ D を入力し、その入力した信号からノイズを除去した信号を出力する。フィルタ回路 1 4 の出力信号は、故障検出制御回路 1 5 に入力されている。故障検出制御回路 1 5 は、トランジスタ Q 3 、 Q 4 の駆動を制御してトランジスタ Q 4 の故障を検出するものであり、例えばロジック回路により構成されている。詳細は後述するが、故障検出制御回路 1 5 は、電流検出部 1 9 による電流の検出結果を表すフィルタ回路 1 4 の出力信号に基づいてトランジスタ Q 4 の故障を検出する。

10

#### 【 0 0 3 1 】

故障検出制御回路 1 5 は、トランジスタ Q 1 、 Q 2 を駆動するための駆動信号 C U T を生成し、その駆動信号 C U T をトランジスタ Q 1 、 Q 2 のゲートへ出力する。つまり、この場合、トランジスタ Q 1 、 Q 2 のオンとオフは、故障検出制御回路 1 5 により制御される。故障検出制御回路 1 5 は、トランジスタ Q 3 、 Q 4 の駆動を制御するための制御信号 S b を生成して出力する。故障検出制御回路 1 5 から出力される制御信号 S b は、セレクタ 1 6 の他方の入力端子に入力される。

20

#### 【 0 0 3 2 】

また、故障検出制御回路 1 5 は、セレクタ 1 6 による切替動作を制御するための切替信号 S c を生成し、その切替信号 S c をセレクタ 1 6 へ出力する。この場合、故障検出制御回路 1 5 は、外部の制御装置 2 0 との間で通信を行うことができる。なお、制御装置 2 0 は、Micro Processor Unit、つまり M P U を主体として構成されている。詳細は後述するが、故障検出制御回路 1 5 は、トランジスタ Q 4 の故障を検出する際、制御装置 2 0 と通信を行うようになっている。

30

#### 【 0 0 3 3 】

セレクタ 1 6 は、切替信号 S c に基づいて、入力される制御信号 S a および S b のうちいずれか一方を出力する切替動作を行う。セレクタ 1 6 の出力信号は、プリドライバ 1 7 、 1 8 に与えられる。この場合、セレクタ 1 6 は、昇圧制御回路 1 2 および故障検出制御回路 1 5 のうちいずれか一方がトランジスタ Q 3 、 Q 4 の駆動を制御可能となるように切り替えを行う切替部に相当する。

#### 【 0 0 3 4 】

プリドライバ 1 7 は、セレクタ 1 6 の出力信号に基づいてトランジスタ Q 3 を駆動するための駆動信号 E X P を生成し、その駆動信号 E X P をトランジスタ Q 3 のゲートへ出力する。プリドライバ 1 8 は、セレクタ 1 6 の出力信号に基づいてトランジスタ Q 4 を駆動するための駆動信号 E X N を生成し、その駆動信号 E X N をトランジスタ Q 4 のゲートへ出力する。

40

#### 【 0 0 3 5 】

次に、上記構成の作用について参照して説明する。

##### [ 1 ] 故障検出処理について

電源回路 8 では、昇圧制御回路 1 2 による昇圧動作の実行に先立って、トランジスタ Q 4 の故障を検出するための処理である故障検出処理が行われる。具体的には、電源回路 8 では、例えば起動時に故障検出処理が実行される。なお、起動時とは、電源投入時、つまり電源回路 8 に対して電圧 B U B の供給が開始されたときのことである。

#### 【 0 0 3 6 】

50

故障検出処理は、故障検出制御回路15を主体として実行されるものであり、その具体的な内容は、例えば図2に示すような内容となっている。なお、この場合、故障検出処理が開始される時点よりも前の任意の時点において、セレクタ16から制御信号Sbが出力されるように、つまり故障検出制御回路15によりトランジスタQ3、Q4の駆動が制御されるように、セレクタ16の動作が制御されるようになっている。

#### 【0037】

図2に示すように、故障検出処理が開始されると、まずステップS101が実行される。ステップS101では、トランジスタQ1、Q2がオン駆動される。なお、この時点では、トランジスタQ3、Q4は、オフ駆動されている。続くステップS102では、フィルタ回路14の出力信号に基づいて、トランジスタQ4に流れる電流が検出閾値に達したか否かが判断される。10

#### 【0038】

ここで、トランジスタQ4に流れる電流が検出閾値に達した場合、ステップS102で「YES」となり、ステップS103に進む。この場合、トランジスタQ4がオフ駆動されているにもかかわらず、トランジスタQ4に電流が流れていると考えられる。したがって、ステップS103では、トランジスタQ4にショート故障が生じていることが検出され、今回の故障検出処理による検出結果として「ショート故障」が記憶される。ステップS103の実行後は、故障検出処理が終了となる。

#### 【0039】

この場合、故障検出処理においてトランジスタQ4がショート故障していることが検出されたため、故障検出処理の終了後、昇圧制御回路12による昇圧動作の実行が禁止されるとともに、故障検出時の処理が実行される。なお、故障検出時の処理としては、例えば制御装置20に対してトランジスタQ4が故障している旨を報知するといった処理などを挙げることができる。20

#### 【0040】

一方、トランジスタQ4に流れる電流が検出閾値に達しない場合、ステップS102で「NO」となり、ステップS104に進む。ステップS104では、トランジスタQ4がオン駆動される。続くステップS105では、フィルタ回路14の出力信号に基づいて、トランジスタQ4に流れる電流が検出閾値に達したか否かが判断される。

#### 【0041】

ここで、トランジスタQ4に流れる電流が検出閾値に達しない場合、ステップS105で「NO」となり、ステップS106に進む。この場合、トランジスタQ4がオン駆動されているにもかかわらず、トランジスタQ4に電流が流れていないと考えられる。したがって、ステップS106では、トランジスタQ4にオープン故障が生じていることが検出され、今回の故障検出処理による検出結果として「オープン故障」が記憶される。30

#### 【0042】

ステップS106の実行後は、故障検出処理が終了となる。この場合、故障検出処理においてトランジスタQ4がオープン故障していることが検出されたため、故障検出処理の終了後、昇圧制御回路12による昇圧動作の実行が禁止されるとともに、故障検出時の処理が実行される。40

#### 【0043】

一方、トランジスタQ4に流れる電流が検出閾値に達した場合、ステップS105で「YES」となり、ステップS107に進む。この場合、トランジスタQ4には、ショート故障およびオープン故障のいずれも生じていないと考えられる。したがって、ステップS107では、トランジスタQ4が正常であることが検出され、今回の故障検出処理による検出結果として「正常」が記憶される。

#### 【0044】

また、ステップS107では、トランジスタQ4がオフ駆動される。ステップS107の実行後は、故障検出処理が終了となる。この場合、故障検出処理においてトランジスタQ4が正常であることが検出されたため、故障検出処理の終了後、昇圧制御回路12によ50

る昇圧動作の実行が許可される。

#### 【0045】

このように、上記構成の電源回路8では、昇圧制御回路12による昇圧動作の実行に先立って、故障検出制御回路15は、故障検出制御回路15によりトランジスタQ3、Q4の駆動が制御されるようにセレクタ16の動作を制御する。そして、故障検出制御回路15は、トランジスタQ4をオン駆動し、電流検出部19による電流の検出結果に基づいてトランジスタQ4のオープン故障を検出する。

#### 【0046】

また、上記構成の電源回路8では、昇圧制御回路12による昇圧動作の実行に先立って、故障検出制御回路15は、トランジスタQ1、Q2をオンし、電流検出部19による電流の検出結果に基づいてトランジスタQ4のショート故障を検出する。ただし、この場合、故障検出制御回路15は、トランジスタQ4のオープン故障の検出に先立って、トランジスタQ4のショート故障の検出を行う。10

#### 【0047】

##### [2] 正常時の動作

トランジスタQ4に故障が生じていない正常時における電源回路8の動作について図3を参照して説明する。なお、図3などにおいて、電流検出信号ISは、紙面の都合上、比較的緩やかに上昇するような波形として示しているが、実際はさらに急峻に上昇するような信号波形となっている。

#### 【0048】

図3に示すように、電圧BUBが定常値まで上昇すると、制御回路11が正常に動作を開始する。このとき、駆動信号CUTおよびEXPは電圧BUBと同程度の電圧値であるOFFレベルとなっており、これにより、トランジスタQ1～Q3はオフ駆動されている。また、駆動信号EXNはグランド電位(0V)と同程度の電圧値であるOFFレベルとなっており、これにより、トランジスタQ4はオフ駆動されている。20

#### 【0049】

このような状態となっている期間中の任意の時刻t1において、故障検出制御回路15によりトランジスタQ3、Q4の駆動が制御されるようにセレクタ16の切替動作が行われる。その後、時刻t2において、故障検出制御回路15は、駆動信号CUTをグランド電位(0V)と同程度の電圧値であるONレベルに転じさせることにより、トランジスタQ1、Q2をオン駆動する。30

#### 【0050】

この場合、トランジスタQ4は正常であるとともにオフ駆動されているため、トランジスタQ4に電流は流れない。そのため、電流検出信号ISがグランド電位(0V)から上昇することなく、これにより出力信号IS\_DはLレベルのままとなる。したがって、この場合、トランジスタQ4にショート故障が生じていないと判断することができる。

#### 【0051】

その後、時刻t3において、故障検出制御回路15は、駆動信号EXNを電源電圧(例えば電圧BUB)と同程度の電圧値であるONレベルに転じさせることにより、トランジスタQ4をオン駆動する。この場合、トランジスタQ4は正常であるとともにオン駆動されているため、トランジスタQ4に電流が流れ、これに伴い、電流検出信号ISが上昇する。40

#### 【0052】

そして、電流検出信号ISが基準電圧Vrefに達した時点、つまりトランジスタQ4に流れる電流が検出閾値に達した時点である時刻t4において、出力信号IS\_DがHレベルに転じる。したがって、この場合、トランジスタQ4にオープン故障が生じていないと判断することができる。

#### 【0053】

故障検出制御回路15は、フィルタ回路14の出力信号に基づいて出力信号IS\_DがHレベルに転じたことを検出すると、駆動信号EXNをOFFレベルに転じさせることに50

より、トランジスタQ4をオフ駆動する。なお、ここで、トランジスタQ4を直ちにオフ駆動しないと、トランジスタQ4に過大な電流が流れるおそれがある。そのため、故障検出制御回路15は、上記検出の後、直ちにトランジスタQ4をオフ駆動するように制御を行うようになっている。

#### 【0054】

しかし、上記検出から実際にトランジスタQ4がオフされるまでには、回路動作などに起因する遅延時間が存在する。この場合、故障検出制御回路15は、ロジック回路として構成されており、クロック信号に同期した動作となる。したがって、上記遅延時間には、故障検出制御回路15におけるクロック同期に伴う遅延も含まれることになる。このような遅延時間を無視して検出閾値を設定すると、上記検出から実際にトランジスタQ4がオフされるまでの間に過大な電流が流れてしまい、トランジスタQ4が故障するおそれがある。10

#### 【0055】

そこで、本実施形態では、このような遅延時間を考慮し、トランジスタQ4に流れる電流がトランジスタQ4の定格電流未満に抑えられるように、検出閾値を設定している。以下、検出閾値の具体的な設定例に関して図4を参照して説明する。この場合、上記遅延時間は、 $1.5\mu s$ となっており、トランジスタQ4の定格電流は、6Aとなっている。

#### 【0056】

また、この場合、バックアップバッテリ4がリチウムイオン電池などの二次電池であり、電圧BUBの定常値は、+3.6Vとなっている。また、インダクタL1のインダクタンス値は、 $2.2\mu H$ となっている。さらに、電源回路8を構成する各素子の抵抗に関する仕様は、次のようになっている。20

#### 【0057】

トランジスタQ1のオン抵抗： $25m$

トランジスタQ2のオン抵抗： $25m$

インダクタL1の等価直列抵抗： $34m$

トランジスタQ4のオン抵抗： $19m$

抵抗R1の抵抗値： $33m$

回路基板などの寄生抵抗： $50m$

したがって、入力端子5からグランド線Lgへと至る経路の抵抗値は、 $186m$ となっている。30

#### 【0058】

上記構成の電源回路8では、トランジスタQ4がオンされた直後、電圧BUBの電圧値、入力端子5からグランド線Lgへと至る経路の抵抗値、インダクタL1のインダクタンス値などにより定まる電流がトランジスタQ4に流れる。なお、以下、トランジスタQ4に流れる電流のことを発生電流とも呼ぶ。図4に示すように、トランジスタQ4がオンされた時点からの経過時間に比例して発生電流は増加するようになっている。

#### 【0059】

本実施形態では、検出閾値は $1.26A$ に設定されている。なお、検出閾値を $1.26A$ に設定するためには、基準電圧Vrefを $42mV$ とすればよい。この場合、図4に示すように、トランジスタQ4がオンされた時点から約 $0.8\mu s$ 後に発生電流が $1.26A$ に達する。これにより、電流検出信号ISが基準電圧Vrefに達してコンパレータCP1の出力信号IS\_Dが反転する。40

#### 【0060】

その後、遅延時間( $1.5\mu s$ )が経過した後、つまりトランジスタQ4がオンされた時点から約 $2.3\mu s$ 後、トランジスタQ4がオフされる。このとき、発生電流は $3.49A$ となっており、トランジスタQ4の定格電流である $6A$ より十分低い電流に抑えられている。したがって、上記構成によれば、故障検出処理において、トランジスタQ4に、その定格電流を超える電流が流れることがない。

#### 【0061】

10

20

30

40

50

### [ 3 ] ショート故障発生時の動作

トランジスタ Q 4 にショート故障が生じているショート故障発生時における電源回路 8 の動作について図 5 を参照して説明する。なお、この場合、トランジスタ Q 1、Q 2 がオン駆動される時点、つまり時刻  $t_2$  までの動作は、正常時の動作と同様である。ただし、この場合、トランジスタ Q 4 はショート故障している。そのため、トランジスタ Q 1、Q 2 がオン駆動されると、直ちにトランジスタ Q 4 に電流が流れ、これに伴い、電流検出信号 I\_S が上昇する。

#### 【 0 0 6 2 】

そして、電流検出信号 I\_S が基準電圧  $V_{ref}$  に達した時点、つまりトランジスタ Q 4 に流れる電流が検出閾値に達した時点である時刻  $t_3$  において、出力信号 I\_S\_D が H レベルに転じる。したがって、この場合、トランジスタ Q 4 にショート故障が生じていると判断することができる。10

#### 【 0 0 6 3 】

故障検出制御回路 15 は、フィルタ回路 14 の出力信号に基づいて出力信号 I\_S\_D が H レベルに転じたことを検出すると、駆動信号 C\_U\_T を OFF レベルに転じさせることにより、トランジスタ Q 1、Q 2 をオフ駆動する。このようにすることで、ショート故障したトランジスタ Q 4 に過大な電流が流れることが防止される。

#### 【 0 0 6 4 】

### [ 4 ] オープン故障発生時の動作

トランジスタ Q 4 にオープン故障が生じているオープン故障発生時における電源回路 8 の動作について図 6 を参照して説明する。なお、この場合、トランジスタ Q 4 がオン駆動される時点、つまり時刻  $t_3$  までの動作は、正常時の動作と同様である。ただし、この場合、トランジスタ Q 4 はオープン故障しているため、トランジスタ Q 4 がオン駆動されても、トランジスタ Q 4 に電流は流れない。20

#### 【 0 0 6 5 】

そのため、電流検出信号 I\_S がグランド電位 (0 V) から上昇することがなく、これにより出力信号 I\_S\_D は L レベルのままとなる。したがって、この場合、トランジスタ Q 4 にオープン故障が生じていると判断することができる。このようにしてオープン故障の検出が終わった後は、トランジスタ Q 4 をオフ駆動する必要がある。なぜなら、トランジスタ Q 4 をオン駆動し続けていると、トランジスタ Q 4 が急に正常に復帰した場合などに、過大な電流が流れおそれがあるからである。30

#### 【 0 0 6 6 】

本実施形態では、故障検出制御回路 15 は、外部の制御装置 20 からトランジスタ Q 4 をオフ駆動する旨の指示が与えられるまでトランジスタ Q 4 のオン駆動を継続し、上記指示が与えられるとトランジスタ Q 4 をオフ駆動するようになっている。これにより、オープン故障の検出が終了してから一定時間が経過した後、トランジスタ Q 4 がオフ駆動される。

#### 【 0 0 6 7 】

以上説明した本実施形態によれば、次のような効果が得られる。

電源回路 8 では、昇圧制御回路 12 による昇圧動作の実行に先立って、故障検出制御回路 15 によりトランジスタ Q 3、Q 4 の駆動が制御されるようにセレクタ 16 の切替動作が行われる。そして、故障検出制御回路 15 は、トランジスタ Q 4 をオン駆動し、電流検出部 19 による電流の検出結果に基づいてトランジスタ Q 4 のオープン故障を検出する。電源回路 8 において、トランジスタ Q 4 がオープン故障している場合、トランジスタ Q 4 がオン駆動されたとしても、トランジスタ Q 4 に流れる電流は増加することがない。そのため、上記オープン故障の検出では、トランジスタ Q 4 に流れる電流が所定の検出閾値に達しない場合にトランジスタ Q 4 がオープン故障していると判断することができる。40

#### 【 0 0 6 8 】

このようにすれば、実際の昇圧動作を実行することなく、トランジスタ Q 4 のオープン故障を検出することが可能となる。そして、この場合、従来の昇圧型スイッチング電源回50

路の構成に対し、ロジック回路として構成される故障検出制御回路 15などを追加することにより、上記オープン故障の検出が可能となっており、フィードバック系の回路に大幅な変更および追加を加える必要がない。したがって、本実施形態によれば、回路規模の大 10 増を招くことなく、トランジスタ Q4 の故障を検出することができるという優れた効果が得られる。

#### 【0069】

電源回路 8 は、入力端子 5 からインダクタ L1 へと至る電源供給経路に直列に介在するトランジスタ Q1、Q2 を備え、それらトランジスタ Q1、Q2 のオンとオフは、故障検出制御回路 15 により制御される。この場合、昇圧動作の実行に先立って、故障検出制御回路 15 は、トランジスタ Q1、Q2 をオン駆動し、電流検出部 19 による電流の検出結果に基づいてトランジスタ Q4 のショート故障を検出する。

#### 【0070】

電源回路 8において、トランジスタ Q4 がショート故障している場合、トランジスタ Q1、Q2 がオン駆動されると、トランジスタ Q4 がオン駆動されていないにもかかわらず、トランジスタ Q4 に流れる電流が増加する。そのため、上記ショート故障の検出では、トランジスタ Q4 に流れる電流が所定の検出閾値に達した場合にトランジスタ Q4 がショート故障していると判断することができる。このようにすれば、実際の昇圧動作を実行することなく、トランジスタ Q4 のオープン故障に加えてショート故障についても検出することができる。

#### 【0071】

トランジスタ Q4 は、電圧 BUB が与えられる入力端子 5 とグランド線 LGとの間に直列に介在している。そのため、トランジスタ Q4 がショート故障した場合、過大な短絡電流が流れるおそれがある。一方、トランジスタ Q4 がオープン故障した場合、昇圧動作を実行することができなくなるものの、過大な短絡電流が流れるおそれはない。そこで、本実施形態では、故障検出制御回路 15 は、トランジスタ Q4 のオープン故障の検出に先立って、トランジスタ Q4 のショート故障の検出を行うようになっている。このようにすれば、故障が生じた場合において一層問題となる可能性があるショート故障の検出を優先的に実行することが可能となり、安全性を向上させることができる。

#### 【0072】

なお、本実施形態の構成によれば、次のように、トランジスタ Q3 のショート故障を検出することも可能である。すなわち、故障検出制御回路 15 は、昇圧制御回路 12 による昇圧動作の実行に先立って、トランジスタ Q1、Q2 をオン駆動するとともに、トランジスタ Q3、Q4 をオフ駆動する。このような状態において、制御装置 20 は、通信を介して電流検出信号 FB をモニタする。

#### 【0073】

この場合、トランジスタ Q3 が正常であれば、電流検出信号 FB はロウレベル(0V)に固定されている。しかし、トランジスタ Q3 がショート故障している場合、電流検出信号 FB は電圧 BUB の電圧値に近いレベルとなる。制御装置 20 は、このような点を考慮し、上述したようにモニタした電流検出信号 FB のレベルに基づいてトランジスタ Q3 のショート故障を検出することができる。なお、トランジスタ Q3 のショート故障の検出は、必ずしも制御装置 20 側で行わなくともよく、制御回路 11 側で行ってもよい。

#### 【0074】

##### (第2実施形態)

以下、第2実施形態について図7を参照して説明する。

図7に示すように、本実施形態の電源システム 21 が備える電源回路 22 は、第1実施形態の電源回路 8 と同様の昇圧型スイッチング電源回路である。ただし、電源回路 22 は、電源回路 8 に対し、トランジスタ Q3 に代えてダイオード D21 を備えたダイオード整流の構成となっている点が異なる。

#### 【0075】

この場合、ダイオード D21 のアノードはノード N1 に接続され、そのカソードは電源

10

20

30

40

50

線 10 に接続されている。このようなダイオード整流の構成である電源回路 22 であっても、第 1 実施形態と同様の故障検出を行うことが可能である。したがって、本実施形態によつても、第 1 実施形態と同様の効果が得られる。

#### 【0076】

##### (第 3 実施形態)

以下、第 3 実施形態について図 8 を参照して説明する。

図 8 に示すように、本実施形態の電源システム 31 が備える電源回路 32 は、第 1 実施形態の電源回路 8 と同様の昇圧型スイッチング電源回路である。ただし、電源回路 32 は、電源回路 8 に対し、電流検出部 19 に代えて電流検出部 33 を備えている点が異なる。電流検出部 33 は、電流検出部 19 と同様の構成、つまり抵抗 R1 および検出回路 13 を備えている。ただし、この場合、検出回路 13 のコンパレータ CP1 は、抵抗 R1 の低電位側の電位であるグランドを基準電位として動作するようになっている。10

#### 【0077】

以上説明した本実施形態によつても、第 1 実施形態と同様の故障検出を行うことが可能であるため、第 1 実施形態と同様の効果が得られる。さらに、本実施形態では、電流検出部 33 におけるグランドが共通化されている。つまり、抵抗 R1 側のグランドと検出回路 13 側のグランドとが共通化されているため、グランドの電位差による電流検出の誤差が生じることがない。したがって、本実施形態によれば、電流検出の精度を向上させることができるとなり、その結果、故障検出の精度を高めることができる。20

#### 【0078】

##### (第 4 実施形態)

以下、第 4 実施形態について図 9 を参照して説明する。

図 9 に示すように、本実施形態の電源システム 41 が備える電源回路 42 は、第 3 実施形態の電源回路 32 と同様の昇圧型スイッチング電源回路である。ただし、電源回路 42 は、電源回路 32 に対し、電流検出部 33 に代えて電流検出部 43 を備えている点が異なる。

#### 【0079】

電流検出部 43 は、電流検出部 33 と同様の構成に加え、増幅回路 44 を備えている。増幅回路 44 は、差動増幅器であり、その非反転入力端子には、電流検出信号 IS が入力されている。増幅回路 44 の反転入力端子には、グランド線 Lg の電位に対応した信号が入力されている。このような構成により、増幅回路 44 は、抵抗 R1 の端子電圧を増幅して出力する。この場合、コンパレータ CP1 の非反転入力端子には、増幅回路 44 の出力信号が入力されている。30

#### 【0080】

以上説明した本実施形態によつても、第 1 実施形態と同様の故障検出を行うことが可能であるため、第 1 実施形態と同様の効果が得られる。さらに、本実施形態では、抵抗 R1 の端子電圧を増幅する増幅回路 44 を設け、その増幅回路 44 の出力信号を用いてトランジスタ Q4 に流れる電流が検出閾値に達したか否かを判断する構成となっている。このようにすれば、抵抗 R1 の抵抗値を一層小さくすることが可能となり、電源回路 42 における損失低減、効率向上などの効果が得られる。40

#### 【0081】

##### (第 5 実施形態)

以下、第 5 実施形態について図 10 を参照して説明する。

図 8 に示すように、本実施形態の電源システム 51 が備える電源回路 52 は、第 1 実施形態の電源回路 8 に対し、制御回路 11 に代えて制御回路 53 を備えている点が異なる。制御回路 53 は、制御回路 11 と同様の構成に加え、トランジスタ Q3、Q4 および抵抗 R1 を備えている。

#### 【0082】

すなわち、電源回路 52 では、トランジスタ Q3、Q4 および抵抗 R1 は、ASIC として構成された制御回路 53 に内蔵されている。このようにトランジスタ Q3、Q4 など50

が制御回路 5 3 に内蔵された構成の電源回路 5 2 であっても、第 1 実施形態と同様の故障検出を行うことが可能である。したがって、本実施形態によつても、第 1 実施形態と同様の効果が得られる。

#### 【 0 0 8 3 】

##### ( 第 6 実施形態 )

以下、第 6 実施形態について図 1 1 を参照して説明する。

一般に、昇圧型スイッチング電源回路は、オンすることによりインダクタに流れる電流を増加させるスイッチング素子に過電流判定閾値を超える過大な電流が流れたことを検出するための過電流検出回路を備えている。このような過電流検出回路の構成の少なくとも一部を共用化することにより、トランジスタ Q 4 に流れる電流を検出する電流検出部を構成することが可能である。10

#### 【 0 0 8 4 】

本実施形態では、上述した過電流検出回路が備えるコンパレータを共用化することにより、トランジスタ Q 4 に流れる電流を検出する電流検出部を構成するようになっている。具体的には、図 1 1 に示すように、本実施形態の電源システム 6 1 が備える電源回路 6 2 は、第 1 実施形態の電源回路 8 に対し、電流検出部 1 9 に代えて電流検出部 6 3 を備えている点、故障検出制御回路 1 5 に代えて故障検出制御回路 6 4 を備えている点などが異なる。

#### 【 0 0 8 5 】

電流検出部 6 3 の検出回路 6 5 は、検出回路 1 3 が備えるコンパレータ C P 1 と同様のヒステリシス付きのコンパレータ C P 6 1 、スイッチ S W 6 1 、S W 6 2 などを備えている。コンパレータ C P 6 1 の非反転入力端子には、電流検出信号 I S が入力される。コンパレータ C P 6 1 の反転入力端子には、スイッチ S W 6 1 を介して基準電圧 V ref1 が入力されるとともに、スイッチ S W 6 2 を介して基準電圧 V ref2 が入力される。20

#### 【 0 0 8 6 】

基準電圧 V ref1 は、第 1 実施形態などにおける基準電圧 V ref と同様の検出閾値に対応した電圧である。一方、基準電圧 V ref2 は、過電流判定閾値に対応した電圧であり、基準電圧 V ref1 よりも高い電圧となっている。過電流判定閾値は、トランジスタ Q 4 に過大な電流が流れたことを検出する際、つまり過電流検出の際に用いられる。

#### 【 0 0 8 7 】

スイッチ S W 6 1 、S W 6 2 のオンとオフは、故障検出制御回路 6 4 により制御される。故障検出制御回路 6 4 は、故障検出制御回路 1 5 と同様、トランジスタ Q 4 の故障を検出する機能を有するとともに、トランジスタ Q 4 に過電流判定閾値を超える過大な電流が流れたことを検出する過電流検出回路としての機能も有する。なお、故障検出制御回路 6 4 は、単独で過電流検出回路としての機能を実現する構成および外部の制御装置 2 0 と協働して過電流検出回路としての機能を実現する構成のいずれでもよい。30

#### 【 0 0 8 8 】

故障検出制御回路 6 4 は、電源回路 6 2 の起動時などにはスイッチ S W 6 1 をオンするとともにスイッチ S W 6 2 をオフする。これにより、起動時などにおいて、第 1 実施形態などと同様の故障検出処理を実行することが可能となる。また、故障検出制御回路 6 4 は、通常時にはスイッチ S W 6 1 をオフするとともにスイッチ S W 6 2 をオンする。これにより、通常時において、上述した過電流検出を実現することが可能となる。40

#### 【 0 0 8 9 】

以上説明した本実施形態によつても、第 1 実施形態と同様の故障検出を行うことが可能であるため、第 1 実施形態と同様の効果が得られる。さらに、本実施形態では、トランジスタ Q 4 に過電流が流れたことを検出するための過電流検出回路の構成の一部、具体的にはコンパレータ C P 6 1 を共用化することにより、故障検出に用いるための電流検出部 6 3 を構成するようになっている。このようにすれば、共用化された構成の分だけ回路素子を削減することが可能となり、その結果、電源回路 6 2 の回路規模を小さく抑えることができるという効果が得られる。50

**【0090】****(第7実施形態)**

以下、第7実施形態について図12を参照して説明する。

図12に示すように、本実施形態の電源システム71が備える電源回路72は、第1実施形態の電源回路8に対し、電流検出部19に代えて電流検出部73を備えている点などが異なる。電流検出部73は、電流検出部19と同様、トランジスタQ4に流れる電流を検出するものであるが、次の点において電流検出部19とは異なる。

**【0091】**

すなわち、電流検出部19は、トランジスタQ4のロウサイド側にシャント抵抗である抵抗R1が設けられたロウサイド電流検出の構成であった。これに対し、電流検出部73は、トランジスタQ4のハイサイド側にシャント抵抗である抵抗R71が設けられたハイサイド電流検出の構成となっている。

**【0092】**

具体的には、抵抗R71の一方の端子はトランジスタQ2のドレインに接続され、その他方の端子はインダクタL1を介してノードN1に接続されている。抵抗R71の各端子電圧は、それぞれトランジスタQ4に流れる電流に対応した電圧信号である電流検出信号ISP、ISNとして、検出回路74に入力されている。

**【0093】**

検出回路74は、抵抗R71の端子電圧に基づいてトランジスタQ4に流れる電流を検出するもので、ヒステリシス付きのコンパレータCP71を備えている。コンパレータCP71の非反転入力端子には電流検出信号ISPが入力され、その反転入力端子には電流検出信号ISNが入力されている。

**【0094】**

上記したようなハイサイド電流検出の構成である電流検出部73を備えた電源回路72であっても、ロウサイド電流検出の構成である電流検出部19を備えた第1実施形態の電源回路8と同様の故障検出を行うことが可能である。したがって、本実施形態によっても、第1実施形態と同様の効果が得られる。

**【0095】****(第8実施形態)**

以下、第8実施形態について図13および図14を参照して説明する。

図13に示すように、本実施形態の電源システム81が備える電源回路82は、第1実施形態の電源回路8に対し、故障検出制御回路15に代えて故障検出制御回路83を備えている点などが異なる。故障検出制御回路83は、故障検出制御回路15と同様、トランジスタQ4の故障を検出する機能を有する。ただし、故障検出制御回路83は、タイムアウト機能を有しており、外部の制御装置20との間で通信を行うことなく、トランジスタQ4の故障検出を行う。本実施形態の構成では、オープン故障発生時の動作は、図14に示すようなものとなる。

**【0096】**

なお、この場合、トランジスタQ4がオン駆動される時点、つまり時刻t3までの動作は、図6に示した第1実施形態の構成による動作と同様である。ただし、この場合、故障検出制御回路83は、トランジスタQ4にオープン故障が生じていると判断した後、出力信号IS\_Dが反転することなく一定時間Taが経過した時刻t4にてトランジスタQ4をオフ駆動するようになっている。

**【0097】**

以上説明したように、外部の制御装置20との間で通信を行うことなくトランジスタQ4の故障検出を行う構成の電源回路82であっても、第1実施形態と同様のショート故障の検出およびオープン故障の検出を行うことが可能である。したがって、本実施形態によっても、第1実施形態と同様の効果が得られる。

**【0098】****(その他の実施形態)**

10

20

30

40

50

なお、本発明は上記し且つ図面に記載した各実施形態に限定されるものではなく、その要旨を逸脱しない範囲で任意に変形、組み合わせ、あるいは拡張することができる。

上記各実施形態で示した数値などは例示であり、それに限定されるものではない。

### 【0099】

本発明は、車両に搭載される無線通信ECUに適用される電源回路8、22、32、42、52、62、72、82に限らず、昇圧型スイッチング電源回路全般に適用することができる。

### 【0100】

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

10

### 【符号の説明】

#### 【0101】

5...入力端子、8、22、32、42、52、62、72、82...電源回路、12...昇圧制御回路、13、65、74...検出回路、15、64、83...故障検出制御回路、16...セレクタ、19、33、43、63、73...電流検出部、44...增幅回路、L1...インダクタ、R1、R71...抵抗、Q1、Q2、Q4...トランジスタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(56)参考文献 特開2014-128183(JP,A)

特開2015-171246(JP,A)

特開2017-38424(JP,A)

特開2004-357437(JP,A)

特開2011-182519(JP,A)

特開2010-226819(JP,A)

特開2005-51951(JP,A)

特開2017-93110(JP,A)

米国特許出願公開第2015/0200536(US,A1)

特開2011-250627(JP,A)

特開2015-47040(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/00 - 3/44