(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4471480号

(P4471480)

(45) 発行日 平成22年6月2日(2010.6.2)

(24) 登録日 平成22年3月12日(2010.3.12)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 621  |

| HO1L 21/76   | (2006.01) | HO1L 21/76 | L    |

| HO1L 21/8238 | (2006.01) | HO1L 21/76 | S    |

| HO1L 27/092  | (2006.01) | HO1L 27/08 | 321A |

| HO1L 27/08   | (2006.01) | HO1L 29/78 | 613Z |

請求項の数 7 (全 37 頁) 最終頁に続く

(21) 出願番号

特願2000-317991 (P2000-317991)

(22) 出願日

平成12年10月18日 (2000.10.18)

(65) 公開番号

特開2002-124681 (P2002-124681A)

(43) 公開日

平成14年4月26日 (2002.4.26)

審査請求日

平成18年2月1日 (2006.2.1)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 秋山 肇

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 棚田 一也

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するよう前に記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

前記第1のMOSトランジスタは、

平面視形状が直線状の第1の主電極と、

前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、

前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、

前記第2のMOSトランジスタは、

前記第2のMOSトランジスタの前記第1の主電極の平面視形状が、前記第1のMOS

10

20

トランジスタの前記第1の主電極を中心部として囲み、前記第1のMOSトランジスタを内包する長円環状であって、その内側に沿って配設され、その開口部に前記第1のMOSトランジスタを配置した平面視形状がC字形状の制御電極と、

第2の主電極とを備え、

前記第2の主電極は、前記第1のMOSトランジスタの前記第1の主電極と共に通の電極であり、

前記分離構造は、

前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の両端部にそれ配設され、前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る分離領域を備え、

10

前記分離領域は、

P N接合分離のための不純物領域によってその外形が規定され、

前記不純物領域内に配設され、前記SOI基板を構成する埋め込み酸化膜に達する複数のトレンチを備え、

前記複数のトレンチは、

前記第1のMOSトランジスタの前記第1の主電極側から前記第2の主電極側に向かって少なくとも一列に配列され、

それぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

20

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。

### 【請求項2】

前記第2のMOSトランジスタの前記第1の主電極よりも内側の前記SOI層の上部に、前記第1のMOSトランジスタの前記第1の主電極を中心として同心状に複数配設されたマルチフィールドプレートをさらに備え、

前記複数のトレンチの前記配列方向に沿ったトレンチ幅およびトレンチ間隔は、前記マルチフィールドプレートの配列方向に沿ったプレート幅およびプレート間隔にほぼ一致するように設定される、請求項1記載の半導体装置。

30

### 【請求項3】

支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

40

前記第1のMOSトランジスタは、

同心構造の中心をなす第1の主電極と、

前記第1の主電極を囲む制御電極と、

前記制御電極を囲む第2の主電極とを備え、

前記第2のMOSトランジスタは、

同心構造の最外周をなす前記第1の主電極と、

同心構造の中心をなす第2の主電極と、

前記第1の主電極の内側に沿って配設された制御電極とを備え、

50

前記分離構造は、

前記第1のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1のトレンチ分離壁と、

前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第2のトレンチ分離壁とを備え、

前記第1および第2のトレンチ分離壁のそれぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、 10

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。

**【請求項4】**

支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するよう前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、 20

前記第1のMOSトランジスタは、

同心構造の最外周をなす第1の主電極と、

前記第1の主電極の内側に沿って配設された制御電極と、

同心構造の中心をなす第2の主電極とを備え、

前記第2のMOSトランジスタは、

同心構造の最外周をなす前記第1の主電極と、

同心構造の中心をなす第2の主電極と、 30

前記第1の主電極の内側に沿って配設された制御電極とを備え、

前記分離構造は、

比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、

前記第1および第2のトレンチ分離壁のそれぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、 40

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。

**【請求項5】**

支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、 50

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するよう前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

前記第1のMOSトランジスタは、

平面視形状が直線状の第1の主電極と、

前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、

前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、

前記第2のMOSトランジスタは、

同心構造の最外周をなす前記第1の主電極と、

同心構造の中心をなす第2の主電極と、

前記第1の主電極の内側に沿って配設された制御電極とを備え、

前記分離構造は、

比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、

前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、

前記第1および第2のトレンチ分離壁のそれぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のトレンチ分離壁は、

前記第1のMOSトランジスタの前記第1の主電極、前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1の主電極、前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る側面分離壁と、

前記第1のMOSトランジスタの前記第1の主電極および前記第2の主電極の外側に配設された第1および第2の分離壁とを有し、

前記側面分離壁と前記第1および第2の分離壁とで前記第1のMOSトランジスタを囲み、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。

#### 【請求項6】

前記側面分離壁は、

前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数のトレンチを有し、

前記複数のトレンチのそれぞれは、

前記内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、

前記複数のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列される、請求項5記載の半導体装置。

#### 【請求項7】

前記側面分離壁は、

前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数の第1のトレンチと、

前記複数の第1のトレンチの配列の端縁部に配設された平面視形状が矩形の複数の第2のトレンチとを有し、

前記複数の第1および第2のトレンチのそれぞれは、

10

20

30

40

50

前記内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、

前記複数の第1のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列され、

前記複数の第2のトレンチは、

前記複数の第1のトレンチ間の前記SOI層の端部を塞ぐように配列され、

前記複数の第1のトレンチの前記内壁酸化膜と前記複数の第2のトレンチの前記内壁酸化膜とが互いに接合して一体化している、請求項5記載の半導体装置。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

本発明は半導体装置に関し、特に、電力用集積回路装置に内蔵される電力用半導体装置に関する。

【0002】

20

【従来の技術】

電力用半導体装置（パワーデバイス）と論理回路をワンチップ上に集積した電力用集積回路装置（パワーICあるいはHVIC: High Voltage IC）は、モーター制御をはじめとするメカトロニクス分野で高機能化と低コスト化を図るために欠かせない装置である。

【0003】

特に電力ラインのブリッジ整流を行う上で、ハイサイド（高電位）回路から発信される信号（ハイサイド信号）をローサイド（低電位）回路に伝えるハイサイドレベルシフトデバイスには、通常はPチャネルLHV MOS（Lateral High Voltage MOS）トランジスタや、PチャネルDAD（Dual Action Device）が使われている。

【0004】

PチャネルDADは、PチャネルLHV MOSトランジスタとNチャネルLHV MOSトランジスタを一体的に形成した構造を有し、PチャネルLHV MOSトランジスタと比較してオン電流密度を5倍以上に向上させることができる特徴がある（参考資料：K.Watabe et al., IEEE Journal of Solid-state circuits, vol.33, No.9, September 1998 "An 0.8  $\mu$ m High-Voltage IC Using a Newly Designed 600-V Lateral P-Channel Dual-Action Device on SOI）。

30

【0005】

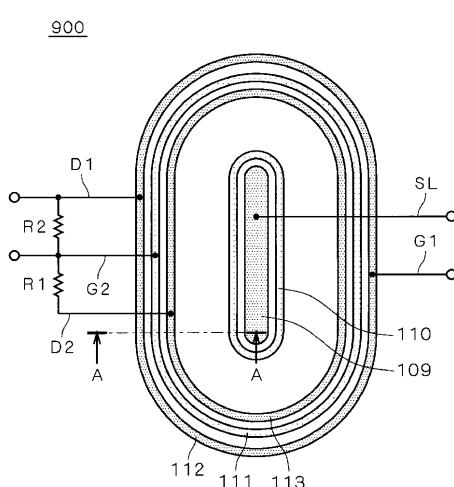

図30に従来のPチャネルDAD900の平面構成を示し、図31に、図30におけるA-A線での断面構成を示す。

【0006】

図30に示すように、PチャネルDAD900は直線状のソース電極109を中心部に有し、その外周を第1ゲート電極110が取り囲み、さらに外周を、第2ドレイン電極113、第2ゲート電極111、第1ドレイン電極112が順に取り囲む構造となっている。なお、何れの電極も長円環状をなしている。

【0007】

なお、ソース電極109、第1ゲート電極110、第2ドレイン電極112、第2ゲート電極111および第1ドレイン電極112にはそれぞれ、ソース配線SL、第1ゲート配線G1、第2ドレイン配線D2、第2ゲート配線G2および第1ドレイン配線D1が接続されている。

40

【0008】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2と第1ドレイン配線D1とは抵抗R2を介して電気的に接続されている。

【0009】

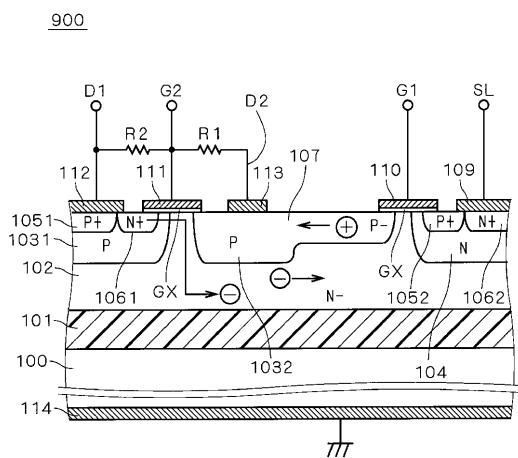

次に、図31を用いて断面構成について説明する。図31に示すようにPチャネルDAD900は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層

50

102 (N型不純を比較的低濃度に含む: N<sup>-</sup>) が配設された SOI 基板上に形成される。

【0010】

図31において、SOI層102の表面内に、図に向かって左側からP型ウエル領域1031、P型ウエル領域1032およびN型ウエル領域104がそれぞれ独立して配設されている。また、P型ウエル領域1032とN型ウエル領域104との間には、P型ウエル領域1032に連続するようにP型ドレイン領域107 (P型不純を比較的低濃度に含む: P<sup>-</sup>) が形成されている。なお、P型ドレイン領域107の形成深さは、P型ウエル領域1032よりも浅い。

【0011】

そして、P型ウエル領域1031の表面内には、図に向かって左側からP型拡散領域1051 (P型不純を比較的高濃度に含む: P<sup>+</sup>) およびN型拡散領域1061 (N型不純を比較的高濃度に含む: N<sup>+</sup>) が隣接して形成され、N型ウエル領域104の表面内には、図に向かって右側からN型拡散領域1062 (N<sup>+</sup>) およびP型拡散領域1052 (P<sup>+</sup>) が隣接して形成されている。

【0012】

また、SOI層102の第1の主面上には、P型拡散領域1051およびN型拡散領域1061を短絡するように接触して形成された第1ドレイン電極112、P型ウエル領域1032上に接触して形成された第2ドレイン電極113、P型拡散領域1052およびN型拡散領域1062を短絡するように接触して形成されたソース電極109が配設されている。

【0013】

さらに、絶縁ゲート電極として、P型ドレイン領域107の端縁部上から、(P型ドレイン領域107とN型ウエル領域104との間の) SOI層102上、N型ウエル領域104上およびP型拡散領域1052の端縁部上をカバーするように第1ゲート電極110が配設され、また、N型拡散領域1061の端縁部上から、P型ウエル領域1031上、(P型ウエル領域1031とP型ウエル領域1032との間の) SOI層102上、P型ウエル領域1032の端縁部上をカバーするように第2ゲート電極111が配設されている。なお、第1ゲート電極110および第2ゲート電極111はSOI層102との間にゲート絶縁膜GXを有している。

【0014】

また、支持基板100の第2の主面上には、全面に渡って裏面電極114が配設され、通常は接地電位に接続されている。

【0015】

次に動作について説明する。

まず、オフ状態(順方向阻止状態)は、第1ドレイン電極112と裏面電極114とを接地電位に接続して相互に短絡し、ソース電極109に電源電圧を与えて正電位とし、第1ゲート電極110をソース電極109に接続して短絡させることにより実現できる。なお、オフ状態下および以後説明するオン動作においても第2ゲート電極G2はフリー(外部から制御信号が与えられることはない)である。

【0016】

オン状態は、第1ゲート電極110の電位をソース電極109に対してマイナス側に制御することによって実現できる。すなわち、第1ゲート電極110の電位をソース電極109に対して低くすることで、第1ゲート電極110直下のN型ウエル領域104およびSOI層102の表面内でP型チャネルが形成され、P型拡散領域1052からP型ドレイン領域107に向かってホールが注入される。これは通常の横型PチャネルMOSトランジスタと同じ動作である。

【0017】

P型ドレイン領域107に注入されたホールは、第2ドレイン電極113を通り抵抗R1およびR2を経由して第1ドレイン電極112に到達するが、この際に、抵抗R1および

10

20

30

40

50

R 2 中にて発生した電位差が所定の値になった時点で第 2 ゲート電極 111 がゲートとして機能し、その直下の P 型ウエル領域 1031 の表面内に N 型チャネルが形成される。

【0018】

その結果、N 型拡散領域 1061 から S O I 層 102 に向かって電子が注入され、注入された電子は N 型ウエル領域 104、N 型拡散領域 1062 を経由してソース電極 109 に到達する。これは横型 N チャネル M O S トランジスタと同じ動作である。

【0019】

このように、P チャネル D A D とは横型 P チャネル M O S トランジスタと横型 N チャネル M O S トランジスタとが一体的に複合したデバイスであり、電源側信号（ハイサイド信号）で第 1 ゲート電極 110 が制御され、オン状態では N チャネル M O S F E T が動作する 10 ので、オン抵抗を低減できるという利点があった。

【0020】

【発明が解決しようとする課題】

しかし、従来の P チャネル D A D 900 は以上のように構成されているため、P 型拡散領域 1052、N 型ウエル領域 104、S O I 層 102、P 型ウエル領域 1031、N 型拡散領域 1061 で構成される、P / N / P / N 構造を必然的に内蔵してしまい、この構造によって形成される寄生サイリスタがオンしてしまうと、デバイスはラッチアップ状態となり制御不能に陥るという問題があった。

【0021】

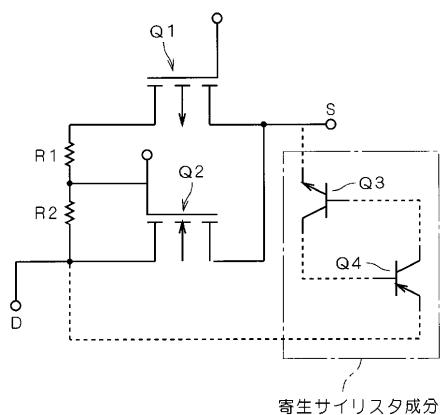

図 32 に P チャネル D A D 900 の等価回路図を示す。図 32 において、P チャネル M O S トランジスタ Q 1 のソースに N P N 型トランジスタ Q 3 のエミッタが接続され、N P N 型トランジスタ Q 3 のコレクタが P N P 型トランジスタ Q 4 のベースに接続され、P N P 型トランジスタ Q 4 のコレクタが N P N 型トランジスタ Q 3 のベースに接続され、P N P 型トランジスタ Q 4 のエミッタが、N チャネル M O S トランジスタ Q 2 のドレインに接続され、P チャネル D A D 900 のソース ( S ) - ドレイン ( D ) 間にサイリスタが寄生した構成となっている。

【0022】

このような構成において、電子およびホールが高密度に注入されると、モジュレーションを引き起こし、ラッチアップ状態になる可能性がある。

【0023】

本発明は上記のような問題点を解消するためになされたもので、ラッチアップ耐性を向上し、耐電圧特性を安定させた D A D を提供することを目的とする。

【0024】

【課題を解決するための手段】

本発明に係る請求項 1 記載の半導体装置は、支持基板上に、埋め込み酸化膜および S O I 層を有して構成される S O I 基板上に配設され、主電流が横方向に流れる導電型の異なる第 1 および第 2 の M O S トランジスタを備え、前記第 1 の M O S トランジスタの主電流に基づく電位により前記第 2 の M O S トランジスタの制御電極の電位を制御して前記第 2 の M O S トランジスタのオン・オフ動作を制御する半導体装置であって、前記第 1 の M O S トランジスタの主電流が、前記第 2 の M O S トランジスタの形成領域を通って前記第 2 の M O S トランジスタの第 1 の主電極に流入する経路を遮断するように、前記第 1 の M O S トランジスタと前記第 2 の M O S トランジスタとを電気的に分離する分離構造を前記 S O I 層内に備え、前記第 1 の M O S トランジスタが、平面視形状が直線状の第 1 の主電極と、前記第 1 の主電極に平行するように配設され、前記第 1 の主電極を超えない長さの直線状の制御電極と、前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第 2 の主電極とを備え、前記第 2 の M O S トランジスタは、前記第 2 の M O S トランジスタの前記第 1 の主電極の平面視形状が、前記第 1 の M O S トランジスタの前記第 1 の主電極を中心部として囲み、前記第 1 の M O S トランジスタを内包する長円環状であって、その内側に沿って配設され、その開口部に前記第 1 の M O S トランジスタを配置した平面視形状が C 字形状の制御電極と、第 2 の主電極とを備え、前記第 2 の主電極は

10

20

30

40

50

、前記第1のMOSトランジスタの前記第1の主電極と共に通の電極であり、前記分離構造は、前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る分離領域を備え、前記分離領域は、PN接合分離のための不純物領域によってその外形が規定され、前記不純物領域内に配設され、前記SOI基板を構成する埋め込み酸化膜に達する複数のトレンチを備え、前記複数のトレンチは、前記第1のMOSトランジスタの前記第1の主電極側から前記第2の主電極側に向けて少なくとも一列に配列され、それぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

## 【0026】

本発明に係る請求項2記載の半導体装置は、前記第2のMOSトランジスタの前記第1の主電極よりも内側の前記SOI層の上部に、前記第1のMOSトランジスタの前記第1の主電極を中心として同心状に複数配設されたマルチフィールドプレートをさらに備え、前記複数のトレンチの前記配列方向に沿ったトレンチ幅およびトレンチ間隔は、前記マルチフィールドプレートの配列方向に沿ったプレート幅およびプレート間隔にほぼ一致するように設定される。

## 【0027】

本発明に係る請求項3記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、同心構造の中心をなす第1の主電極と、前記第1の主電極を囲む制御電極と、前記制御電極を囲む第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、前記第1のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1のトレンチ分離壁と、前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第2のトレンチ分離壁とを備え、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

## 【0028】

本発明に係る請求項4記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、同心構造の中心をなす第1の主電極と、前記第1の主電極を囲む制御電極と、前記制御電極を囲む第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、前記第1のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1のトレンチ分離壁と、前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第2のトレンチ分離壁とを備え、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

10

20

30

40

50

O I層内に備え、前記第1のMOSトランジスタが、同心構造の最外周をなす第1の主電極と、前記第1の主電極の内側に沿って配設された制御電極と、同心構造の中心をなす第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続されている。

10

## 【0029】

本発明に係る請求項5記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、平面視形状が直線状の第1の主電極と、前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、第1のトレンチ分離壁は、前記第1のMOSトランジスタの前記第1の主電極、前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1の主電極、前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る側面分離壁と、前記第1のMOSトランジスタの前記第1の主電極および前記第2の主電極の外側に配設された第1および第2の分離壁とを有し、前記側面分離壁と前記第1および第2の分離壁とで前記第1のMOSトランジスタを囲み、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

20

## 【0030】

本発明に係る請求項6記載の半導体装置は、前記側面分離壁は、前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数のトレンチを有し、前記複数のトレンチのそれぞれは、前記内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、前記複数のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列される。

30

## 【0031】

本発明に係る請求項7記載の半導体装置は、前記側面分離壁が、前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数の第1のトレンチと、前記複数の第

40

50

1のトレンチの配列の端縁部に配設された平面視形状が矩形の複数の第2のトレンチとを有し、前記複数の第1および第2のトレンチのそれぞれは、前記内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、前記複数の第1のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列され、前記複数の第2のトレンチは、前記複数の第1のトレンチ間の前記SOI層の端部を塞ぐように配列され、前記複数の第1のトレンチの前記内壁酸化膜と前記複数の第2のトレンチの前記内壁酸化膜とが互いに接合して一体化している。

## 【0033】

## 【発明の実施の形態】

&lt; A . 実施の形態 1 &gt;

10

&lt; A - 1 . 装置構成 &gt;

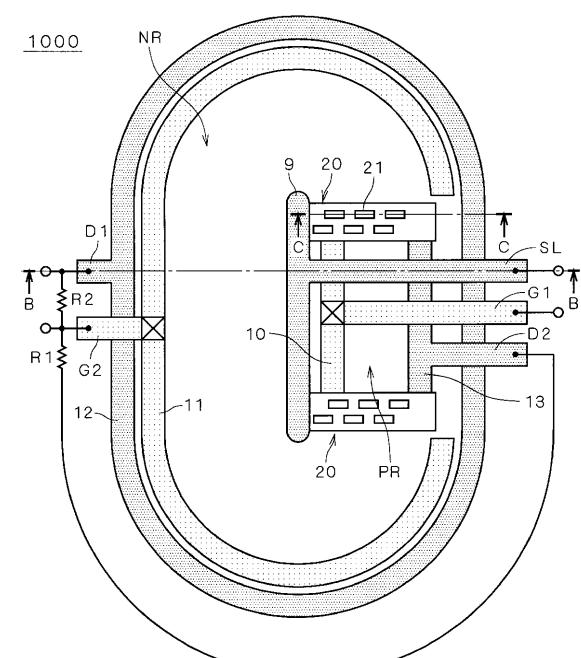

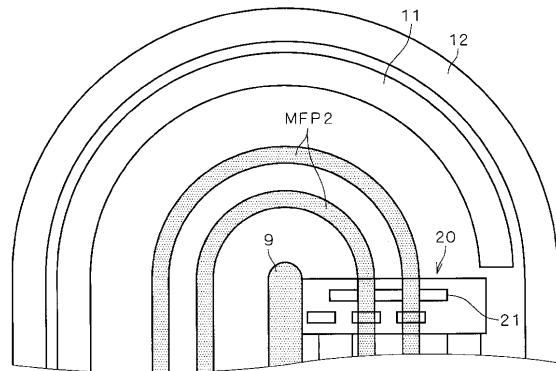

本発明に係る実施の形態1として、図1～図4を用いてPチャネルDAD (Dual Action Device) 1000の構成について説明する。

## 【0034】

&lt; A - 1 - 1 . 平面構成 &gt;

図1はPチャネルDAD 1000の平面構成を示す図である。図1に示すように、PチャネルDAD 1000は直線状のソース電極9を中央部に有し、ソース電極9を取り囲むように、長円環状の第1ドレイン電極12が配設されている。また、第1ドレイン電極12の内周に沿ってC字形状の第2ゲート電極11が配設されている。

## 【0035】

20

また、ソース電極9に平行するように第1ゲート電極10が配設され、第1ゲート電極10に平行するように第2ドレイン電極13が配設されている。第1ゲート電極10および第2ドレイン電極13はソース電極9の長さを超えない長さの直線状の電極であり、各々の両端部には分離領域20(分離構造)が配設され、2つの分離領域20とソース電極9とで囲まれる領域が、PチャネルMOSトランジスタが形成されるPチャネルMOS領域PRとなる。

## 【0036】

そして、第2ゲート電極11は2つの分離領域20の手前に端部を有し、PチャネルMOS領域はC字形状の開口部から内側にかけて配設されたレイアウトとなっている。

## 【0037】

30

また、ソース電極9と、それを囲む第2ゲート電極11および第1ドレイン電極12によってNチャネルMOSトランジスタが形成され、PチャネルMOS領域PRの3方を囲むようにNチャネルMOS領域NRが配設されたレイアウトとなっている。

## 【0038】

ソース電極9、第1ゲート電極10および第2ドレイン電極13にはそれぞれソース配線SL、第1ゲート配線G1、第2ドレイン配線D2が接続されている。

## 【0039】

ソース配線SLおよび第1ゲート配線G1は、例えば第2層アルミ配線で構成され、ソース配線SLは第1ゲート電極10および第2ドレイン電極13上をオーバーラップするように配設され、第1ゲート配線G1は第2ドレイン電極13上をオーバーラップするように配設されている。

40

## 【0040】

また、第2ゲート電極11および第1ドレイン電極12には、それぞれ第2ゲート配線G2および第1ドレイン配線D1が接続されている。なお第2ゲート配線G1は、例えば第2層アルミ配線で構成され、第2ドレイン配線D2は、例えば第1層アルミ配線で構成されている。

## 【0041】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2と第1ドレイン配線D1とは抵抗R2を介して電気的に接続されている。

50

## 【0042】

なお、第1ゲート電極10および第2ゲート電極11は不純物を含んだドープトポリシリコンで構成され、第1ゲート配線G1および第2ゲート配線G2とはコンタクトホールにより接続される構成となっている。

## 【0043】

分離領域20は、平面視形状がほぼ矩形になるように配設されたP型不純物領域内に、トレンチ21が複数配設されたマルチトレンチ構造となっている。各トレンチ21にはポリシリコン等の導電体が充填されており、充填された各導電体は他の特定の部位と電気的に接続されることなく形成されている。なお、分離領域20の構成については後にさらに説明する。

10

## 【0044】

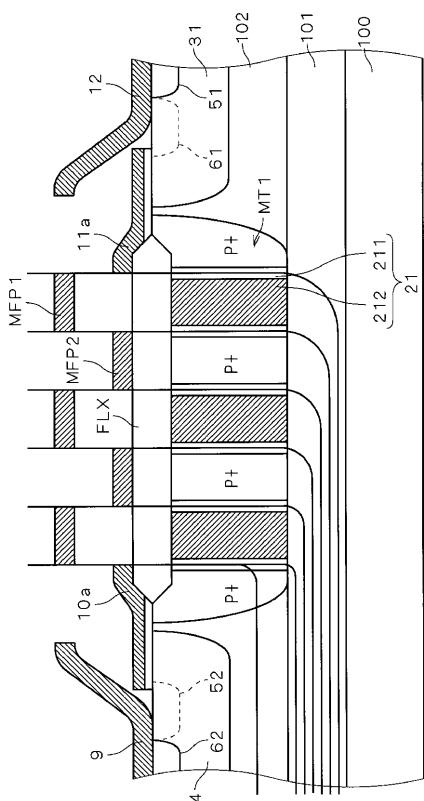

< A - 1 - 2 . 主要部断面構成 >

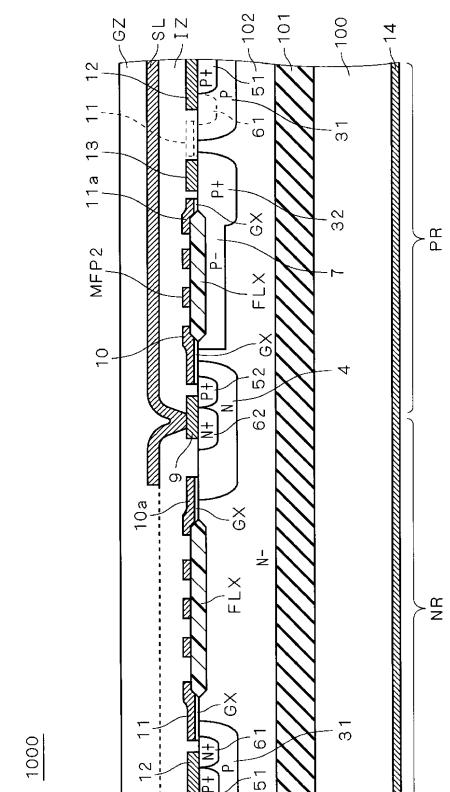

図1におけるB-B線での断面構成を図2に示す。図2に示すようにPチャネルDAD1000は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層102(N型不純を比較的低濃度に含む: N<sup>-</sup>)が配設されたSOI基板上に形成される。

20

## 【0045】

図2において、SOI層102の表面内に、図に向かって左側からP型ウエル領域31、N型ウエル領域4、P型ウエル領域32(P型不純を比較的高濃度に含む: P<sup>+</sup>)およびP型ウエル領域31が、それぞれ独立して配設されている。なお、左右端にあるP型ウエル領域31は平面視形状が長円環状の連続した不純物領域の断面である。

## 【0046】

また、P型ウエル領域32とN型ウエル領域4との間には、P型ウエル領域32に連続するようにP型ドレイン領域7(P型不純を比較的低濃度に含む: P<sup>-</sup>)が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域32よりも浅い。

## 【0047】

そして、図に向かって左側のP型ウエル領域31の表面内には、図に向かって左側からP型拡散領域51(P型不純を比較的高濃度に含む: P<sup>+</sup>)およびN型拡散領域61(N型不純を比較的高濃度に含む: N<sup>+</sup>)が隣接して配設され、N型ウエル領域4の表面内には、図に向かって左側からN型拡散領域62(N<sup>+</sup>)およびP型拡散領域52(P<sup>+</sup>)が隣接して配設され、図に向かって右側のP型ウエル領域31の表面内にはP型拡散領域51が配設されている。

30

## 【0048】

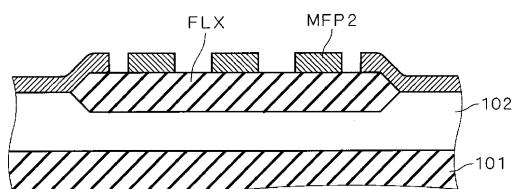

また、P型ウエル領域31とN型ウエル領域4との間のSOI層102の表面上にはフィールド酸化膜FLXが配設されている。なお、当該フィールド酸化膜FLXは、P型ドレイン領域7およびP型ウエル領域32の表面上にも配設されている。

## 【0049】

さらに、フィールド酸化膜FLXの上部には、マルチフィールドプレートMFP2が配設されている。なお、マルチフィールドプレートMFP2の構成については後にさらに説明する。

40

## 【0050】

そして、SOI層102の第1の主面上には、P型拡散領域51およびN型拡散領域61を短絡するように接触して形成された第1ドレイン電極12、P型ウエル領域32上に接触して形成された第2ドレイン電極13、P型拡散領域52およびN型拡散領域62を短絡するように接触して形成されたソース電極9が配設されている。

## 【0051】

さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)SOI層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10が配設され、また、N型拡散領域61の端縁部上から、P型ウエル領域31上およびSOI層102上をカバーする

50

ように第2ゲート電極11が配設されている。なお、第1ゲート電極10および第2ゲート電極11はポリシリコンで構成され、ゲート絶縁膜GXによって絶縁されている。そして、どちらもフィールド酸化膜FLXの端部に一部が係合している。

【0052】

また、第2ドレイン電極13とフィールド酸化膜FLXとの間のP型ウエル領域32上には、第2ゲート電極11と同じ工程で形成されたゲート電極11aが配設され、N型ウエル領域4の端縁部上部からSOI層102上をカバーするように第1ゲート電極10と同じ工程で形成されたゲート電極10aが配設されている。なお、ゲート電極10aおよび11aはゲート絶縁膜GXによって絶縁され、どちらもフィールド酸化膜FLXの端部に一部が係合している。

10

【0053】

そして、SOI層102の第1の主面上を覆うように、層間絶縁膜IZが配設されている。なお、層間絶縁膜IZはソース電極9の上部が開口部となっており、ソース配線SLは当該開口部においてソース電極9と接続し、さらに層間絶縁膜IZの上部に配設されている。

【0054】

また、層間絶縁膜IZおよびソース配線SLを覆うようにガラス等の保護膜GZが配設されている。

【0055】

また、支持基板100の第2の主面上には、全面に渡って裏面電極14が配設されている。

20

【0056】

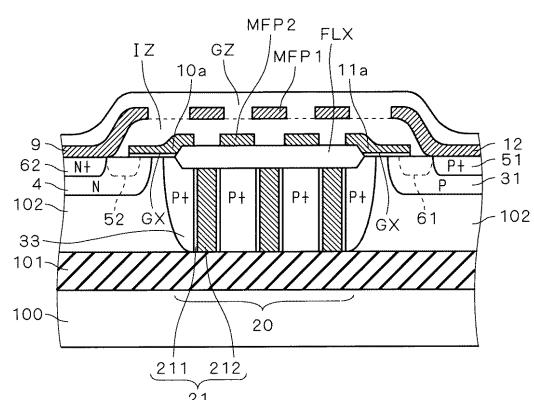

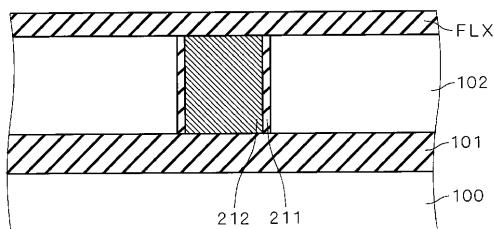

< A - 1 - 3 . 分離領域の断面構成 >

次に、図1におけるC-C線での断面構成、すなわち分離領域20の断面構成を図3に示す。図3に示すように分離領域20は、N型ウエル領域4とP型ウエル領域31とで挟まれるSOI層102の表面内に、埋め込み酸化膜101に達するように配設されたP型不純物領域33(P型不純を比較的高濃度に含む: P<sup>+</sup>)と、P型不純物領域33を貫通するように配設された複数のトレンチ21で構成されるマルチトレンチ構造とを有している。

【0057】

30

このP型不純物領域33は、PN接合分離のための不純物領域であり、PチャネルMOS領域PRとNチャネルMOS領域NRとの電気的な分離は、PN接合分離により達成される。この配設領域が分離領域20の外形を規定している。

【0058】

トレンチ21のそれぞれは、内壁酸化膜211によって壁面が覆われ、内壁酸化膜211で囲まれた領域にドープトポリシリコン等の導電体212が埋め込まれた構成となっている。

【0059】

そして、マルチトレンチ構造部分を覆うようにP型不純物領域33の表面にフィールド酸化膜FLXが配設され、フィールド酸化膜FLXの上部には、ポリシリコンで構成されるマルチフィールドプレートMFP2が配設されている。

40

【0060】

また、フィールド酸化膜FLXの端部に係合するようにゲート電極10aおよび11aが配設されているが、ゲート電極10aは第1ゲート電極10とは電気的には接続されず、ソース電極9に接続されるか、フローティング状態となり、ゲート電極11aは第2ゲート電極11とは電気的には接続されず、第1ドレイン電極12に接続されるか、フローティング状態となっている。

【0061】

これは、ゲート電極10aおよび11aを電界緩和のためのフィールドプレートとして使用するための構成である。また、分離領域20を挟むN型ウエル領域4およびP型ウエル

50

領域 3 1 においては、MOS デバイスとしての機能は不要であるので、P 型拡散領域 5 2 および N 型拡散領域 6 1 も不要となるが、図 3 中においては位置関係を明白にするため破線で示している。

【 0 0 6 2 】

また、分離領域 2 0 の上部を覆うように層間絶縁膜 IZ が配設され、層間絶縁膜 IZ 上にはマルチフィールドプレート MFP 1 が配設されている。マルチフィールドプレート MFP 1 は、ソース電極 9 および第 1 ドレイン電極 12 と同様にアルミニウム等の金属によって構成され、マルチフィールドプレート MFP 2 の間隙の上部を覆うように配設されている。

【 0 0 6 3 】

なお、その他、図 2 に示す断面構成と同一の構成については同一の符号を付し、重複する説明は省略する。

【 0 0 6 4 】

< A - 2 . 動作 >

次に図 1 ~ 図 3 を用いて P チャネル DAD1000 の動作について説明する。

【 0 0 6 5 】

P チャネル DAD1000 のオン、オフ動作は、従来の P チャネル DAD900 と基本的には同様であるが、オン動作時には、まず P チャネル MOS 領域 PR において、第 1 ゲート電極 10 直下の N 型ウエル領域 4 および SOI 層 102 の表面内で形成される P 型チャネルを通って、P 型拡散領域 5 2 から P 型ドレイン領域 7 に向かって注入されるホールは、第 2 ドレイン電極 13 に流れ込み、第 2 ドレイン電極 13 から第 2 ドレイン配線 D 2 を通って第 1 ドレイン電極 12 に流れる。

【 0 0 6 6 】

一方、ホール電流によって抵抗 R 1 および R 2 中にて発生した電位差が所定の値になると、第 2 ゲート電極 11 がゲートとして機能し、その直下の P 型ウエル領域 3 1 の表面内に形成された N 型チャネルを通って N 型拡散領域 6 1 から SOI 層 102 に向かって電子が注入され、注入された電子は N 型ウエル領域 4 、 N 型拡散領域 6 2 を経由してソース電極 109 に到達するが、P チャネル MOS 領域 PR は分離領域 2 0 によって N チャネル MOS 領域 NR と電気的に分離され、ホールは直接に N チャネル MOS 領域 NR を流れることなく、また電子も P チャネル MOS 領域 PR を直接に流れることがない。すなわちホールおよび電子は分離領域 2 0 によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

【 0 0 6 7 】

また、分離領域 2 0 においてはマルチトレンチ構造により、順方向阻止電圧印加時にソース・ドレイン間で発生する電界を各トレンチ 2 1 ごとに分担することができ、分離領域 2 0 における電界集中を緩和することができる。

【 0 0 6 8 】

さらに、マルチフィールドプレートと組み合わせて用いることで、分離領域 2 0 における電界集中をさらに緩和することができる。

【 0 0 6 9 】

< A - 3 . マルチトレンチ構造およびマルチフィールドプレート >

以下、図 4 ~ 図 15 を用いて、マルチトレンチ構造およびマルチフィールドプレートについて説明する。

【 0 0 7 0 】

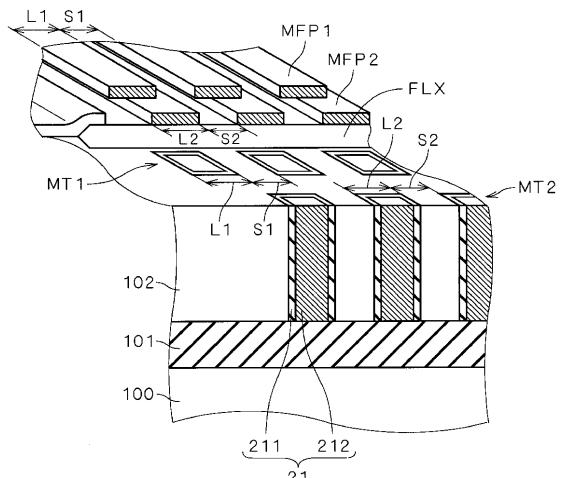

図 4 に、マルチトレンチ構造およびマルチフィールドプレートの構成を斜視図で示す。

【 0 0 7 1 】

図 4 に示すように、マルチトレンチ構造はトレンチ 2 1 の配列を複数有し、隣り合う配列ではトレンチが互い違いになるように配設されている。

【 0 0 7 2 】

また、マルチトレンチ構造の上部を覆うフィールド酸化膜 FLEX 上には、ドープトポリシ

10

20

30

40

50

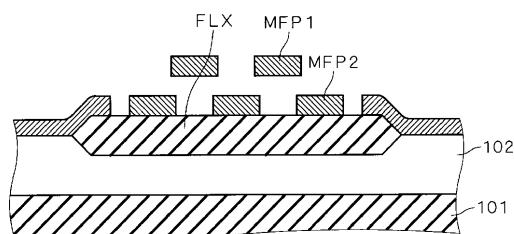

リコンで構成されるマルチフィールドプレートMFP2が配設され、さらに上部には、マルチフィールドプレートMFP2とは互い違いになるように配列されたアルミニウム等の金属で構成されるマルチフィールドプレートMFP1が配設されている。

【0073】

ここで、トレンチ配列のある一列をMT1とし、その配列方向に沿ったトレンチ幅（ライン）およびトレンチ間隔（スペース）を、各々L1およびS1とする。

【0074】

同様に別の一列をMT2とし、そのラインおよびスペースをL2およびS2とする。

【0075】

さらに、マルチフィールドプレートMFP1およびMFP2の、その配列方向に沿ったプレート幅（ライン）およびプレート間隔（スペース）を、それぞれL1およびS1、L2およびS2とすると、トレンチ配列MT2とマルチフィールドプレートMFP2とはラインおよびスペースが一致するので、マルチフィールドプレートMFP2の個々のフィールドプレートが、トレンチ配列MT2の個々のトレンチ21の上部に重なることになり、またトレンチ配列MT1とマルチフィールドプレートMFP1とはラインおよびスペースが一致するので、マルチフィールドプレートMFP1の個々のフィールドプレートが、トレンチ配列MT1の個々のトレンチ21の上部に重なることになる。

10

【0076】

なお、ラインL1およびL2とスペースS1およびS2は数値的には同じでも良く、例えばラインL1およびL2は何れも10~20μm、スペースS1およびS2も10~20μmとすれば良い。その場合、トレンチ配列MT1とMT2との間隔はトレンチ21の間隔で定義すれば2~3μm、トレンチ21のラインと直交する方向の長さは2~3μm程度とすれば良い。

20

【0077】

以上のように配設されたマルチトレンチ構造およびマルチフィールドプレートによる作用効果について図5を用いて説明する。

【0078】

図5は、トレンチ配列MT1とマルチフィールドプレートMFP1との組み合わせによる作用効果を説明する断面図である。なお、図5は図3に示す構成を拡大して示した図であるので、図3と同一の構成については同一の符号を付し、重複する説明は省略する。

30

【0079】

図5において、順方向阻止電圧印加時にソース・ドレイン間で発生する電界は、その大部分が埋め込み酸化膜101中を通り、さらにトレンチ21の内壁酸化膜211を通ってフィールド酸化膜FLXの上部に達する。このとき、トレンチ配列MT1の上部にはマルチフィールドプレートMFP1が位置するので、電界はマルチフィールドプレートMFP1の各プレートの端縁部に沿って延在し、局所的な電界集中が発生することが防止される。

【0080】

なお、埋め込み酸化膜101中では電界密度が高くなっているが、シリコン酸化膜の絶縁破壊強度は、シリコンの10倍以上あるので、電界集中による耐圧特性の低下を防止できる。

40

【0081】

このように、トレンチ21の内壁酸化膜211を電界の通過経路として、シリコン層中での局所的な電界の集中を効果的に防止して、耐圧特性の保持と安定化を図ることができる。従って、分離領域20を配設することで耐圧の低下を招く心配がなく、確実にラッチアップ特性の改善を図ることができる。

【0082】

また、マルチトレンチ構造によって分配された電界分布は、マルチフィールドプレートによっても維持され、マルチトレンチ構造との組み合わせにより、シリコン層中での局所的な電界の集中をより効果的に防止することができる。

【0083】

50

## &lt; A - 4 . マルチトレーニング構造の製造方法 &gt;

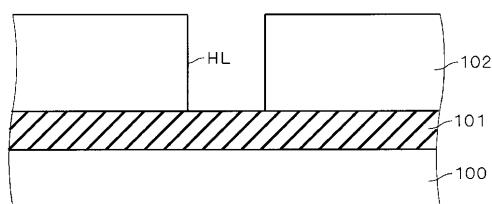

次に、図 6 ~ 図 9 を用いてマルチトレーニング構造の製造方法について説明する。

## 【 0 0 8 4 】

まず、図 6 に示す工程において SOI 層 102 を貫通する開口部 HL を複数形成する。この複数の開口部 HL はトレーニング 21 の外形形状と配列に合わせて形成すれば良い。

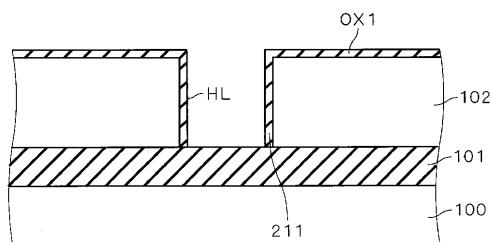

## 【 0 0 8 5 】

次に、図 7 に示す工程において、開口部 HL の壁面に内壁酸化膜 211 を形成するためには、SOI 層 102 の全面に厚さ 100 nm (1000 オングストローム) 程度のシリコン酸化膜 OX1 を形成する。

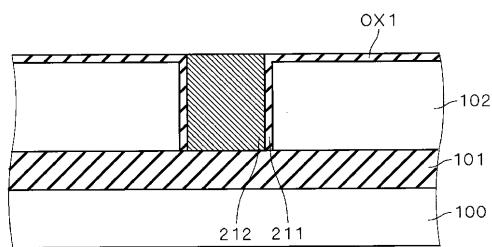

## 【 0 0 8 6 】

次に、図 8 に示す工程において、ドープトポリシリコン 212 を全面に形成した後、エッチャックにより除去して、開口部 HL 内にのみドープトポリシリコン 212 を残すようにする。

## 【 0 0 8 7 】

その後、SOI 層 102 上のシリコン酸化膜 OX1 を除去し、フィールド酸化を行って、フィールド酸化膜 FLX を形成することで、フィールド酸化膜 FLX の下部にマルチトレーニング構造を有した構成を得る。

## 【 0 0 8 8 】

## &lt; A - 5 . マルチフィールドプレートの変形例 1 &gt;

以上の説明においては、マルチフィールドプレート MFP1 および MFP2 の 2 層を有する構成について説明したが、マルチフィールドプレートは必ずしも 2 層である必要はなく、1 層または 3 層以上であっても良い。

## 【 0 0 8 9 】

図 10 には、フィールド酸化膜 FLX 上にマルチフィールドプレート MFP2 だけを有する構成を示す。

## 【 0 0 9 0 】

このような構成を採ることで、マルチフィールドプレートの形成工程を簡略化できるが、容量性結合力は低下する。

## 【 0 0 9 1 】

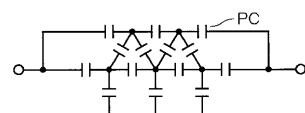

図 11 は、図 10 の構成における容量成分 PC を等価回路として示した図である。

## 【 0 0 9 2 】

また、図 12 は、フィールド酸化膜 FLX 上にマルチフィールドプレート MFP2 を有し、さらに上層にマルチフィールドプレート MFP1 を有する構成を示し、図 13 には、図 12 の構成における容量成分 PC を等価回路として示す。

## 【 0 0 9 3 】

図 11 と図 13 とを比較することで、マルチフィールドプレートを複数層有することで、容量性結合を飛躍的に強化できることが判る。

## 【 0 0 9 4 】

従って、マルチフィールドプレートを 3 層以上とすれば、さらに容量性結合を強化でき、耐圧特性を安定化できるという効果が得られる。

## 【 0 0 9 5 】

## &lt; A - 6 . マルチフィールドプレートの変形例 2 &gt;

また、図 3 ~ 図 5 においては、マルチフィールドプレート MFP1 および MFP2 が、分離領域 20 の上部にオーバーラップする構成を示したが、マルチフィールドプレート MFP1 および MFP2 が、分離領域 20 の上部においてオーバーラップしない構成であっても良い。

## 【 0 0 9 6 】

すなわち、マルチフィールドプレートは横型高耐圧デバイスにおいて、ソース・ドレイン間の電界緩和のために、ソース・ドレイン間のフィールド酸化膜の上部に配設されるものであり、分離領域 20 の上部だけに配設されるものではない。

10

20

30

40

50

## 【0097】

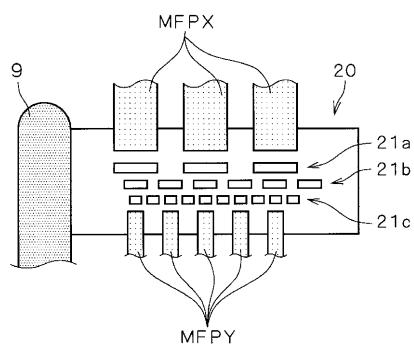

図14はマルチフィールドプレートの配設状態を示すためのPチャネルDAD1000の部分平面図である。図14においては、マルチフィールドプレートMFP2だけを示しており、マルチフィールドプレートMFP2がソース電極9と第1ドレイン電極12との間に配設されていることが判る。

## 【0098】

分離領域20においては、図5を用いて説明したように、マルチトレンチ構造によりソース・ドレイン間の電界を緩和できるので、マルチフィールドプレートを設けずとも、電界緩和が達成できる。

## 【0099】

逆に、分離領域20においてマルチフィールドプレートを省略することで、図15に示すような構成を探ることも可能となる。

## 【0100】

図15は、分離領域20上においてはマルチフィールドプレートを形成せず、NチャネルMOS領域NRにおいてはマルチフィールドプレートMFPXを形成し、PチャネルMOS領域PRにおいてはマルチフィールドプレートMFPYを形成する構成となっている。

## 【0101】

そして、分離領域20においては、外形寸法が異なるトレンチの配列を複数設け、各トレンチ配列ごとにラインおよびスペースを変えた構成としても良い。

## 【0102】

図15においては、トレンチ21aの配列、トレンチ21bの配列、トレンチ21cの配列の3種類の配列が示されている。なお、NチャネルMOS領域NRに最も近いトレンチ21aのライン（配列方向に沿ったトレンチ幅）が最も長く、PチャネルMOS領域PRに最も近いトレンチ21cのラインが最もラインが短くなるように配設されている。

## 【0103】

また、マルチフィールドプレートMFPXのプレート幅は、トレンチ21aのラインと同等に設定され、マルチフィールドプレートMFPYのプレート幅は、トレンチ21cのラインと同等に設定されている。

## 【0104】

このように構成することで、マルチフィールドプレートMFPXとトレンチ21aとの境界部における電界集中を緩和し、耐圧特性を安定化できるという効果が得られる。

## 【0105】

<B. 実施の形態2>

<B-1. 装置構成>

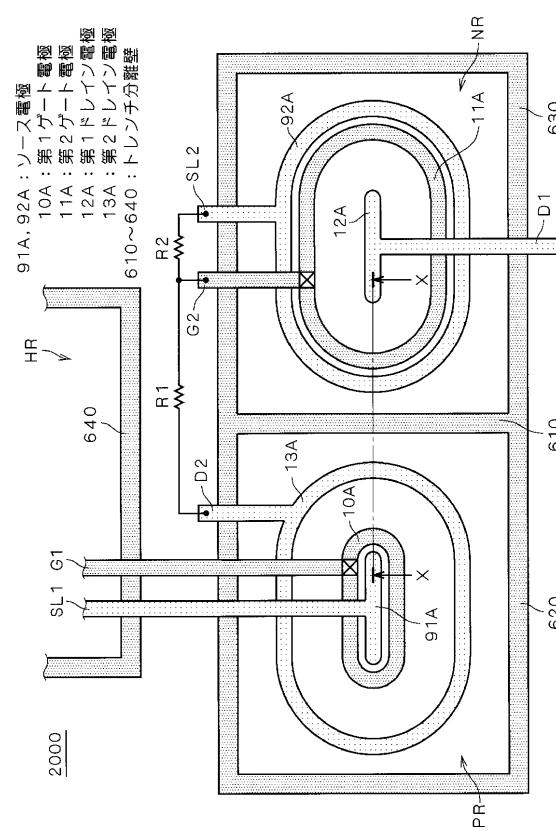

本発明に係る実施の形態2として、図16および図17を用いてPチャネルDAD2000の構成について説明する。

## 【0106】

<B-1-1. 平面構成>

図16はPチャネルDAD2000の平面構成を示す図である。図16に示すように、PチャネルDAD2000は、PチャネルMOS領域PRとNチャネルMOS領域NRとがトレンチ分離壁610によって電気的に分離され、さらにPチャネルMOS領域PRがトレンチ分離壁610および620（第1のトレンチ分離壁）によって囲まれて独立し、NチャネルMOS領域NRがトレンチ分離壁610および630（第2のトレンチ分離壁）によって囲まれて独立している。

## 【0107】

また、ハイサイド（高電位）領域HRもトレンチ分離壁640によって囲まれて独立している。なお、トレンチ分離壁610～640は、PチャネルMOS領域PRとNチャネルMOS領域NRとを電気的に分離するので、分離構造と呼称することができる。

## 【0108】

PチャネルMOS領域PRにおいては、直線状のソース電極91Aを中央部に有し、ソ-

10

20

30

40

50

ス電極 9 1 A を取り囲むように、長円環状の第 1 ゲート電極 1 0 A が配設され、第 1 ゲート電極 1 0 A を取り囲むように、長円環状の第 2 ドレイン電極 1 3 A が配設されて P チャネルMOSトランジスタを構成している。

【 0 1 0 9 】

そして、ソース電極 9 1 A 、第 1 ゲート電極 1 0 A および第 2 ドレイン電極 1 3 A にはそれぞれソース配線 S L 1 、第 1 ゲート配線 G 1 、第 2 ドレイン配線 D 2 が接続されている。

【 0 1 1 0 】

ソース配線 S L 1 および第 1 ゲート配線 G 1 は、例えば第 2 層アルミ配線で構成され、ソース配線 S L 1 は第 1 ゲート電極 1 0 A および第 2 ドレイン電極 1 3 A 上をオーバーラップし、第 1 ゲート配線 G 1 は第 2 ドレイン電極 1 3 A 上をオーバーラップし、さらにトレンチ分離壁 6 2 0 および 6 4 0 上をオーバーラップしてハイサイド領域 H R にまで延在している。

【 0 1 1 1 】

また、第 2 ドレイン配線 D 2 は、例えば第 1 層アルミ配線で構成され、トレンチ分離壁 6 2 0 上をオーバーラップし、ハイサイド領域 H R 側の P チャネルMOS領域 P R 外部に延在している。

【 0 1 1 2 】

N チャネルMOS領域 N R においては、直線状の第 1 ドレイン電極 1 2 A を中央部に有し、第 1 ドレイン電極 1 2 A を取り囲むように、長円環状の第 2 ゲート電極 1 1 A が配設され、第 2 ゲート電極 1 1 A を取り囲むように、長円環状のソース電極 9 2 A が配設されて N チャネルMOSトランジスタを構成している。

【 0 1 1 3 】

そして、第 1 ドレイン電極 1 2 A 、第 2 ゲート電極 1 1 A およびソース電極 9 2 A には、それぞれ第 1 ドレイン配線 D 1 、第 2 ゲート配線 G 2 およびソース配線 S L 2 が接続されている。

【 0 1 1 4 】

ソース配線 S L 2 および第 2 ゲート配線 G 2 は、例えば第 2 層アルミ配線で構成され、ソース配線 S L 2 はトレンチ分離壁 6 2 0 上をオーバーラップし、第 2 ゲート配線 G 2 はソース電極 9 2 A 上およびトレンチ分離壁 6 2 0 上をオーバーラップして、ハイサイド領域 H R 側の N チャネルMOS領域 N R 外部に延在している。

【 0 1 1 5 】

また、第 1 ドレイン配線 D 1 は、例えば第 1 層アルミ配線で構成され、第 2 ゲート電極 1 1 A およびソース電極 9 2 A 上をオーバーラップし、さらにトレンチ分離壁 6 2 0 上をオーバーラップして、ハイサイド領域 H R とは反対側の N チャネルMOS領域 N R 外部に延在している。

【 0 1 1 6 】

なお、第 1 ゲート電極 1 0 A および第 2 ゲート電極 1 1 A はドープトポリシリコンで構成され、第 1 ゲート配線 G 1 および第 2 ゲート配線 G 2 とはコンタクトホールにより接続される構成となっている。

【 0 1 1 7 】

そして、第 2 ドレイン配線 D 2 と第 2 ゲート配線 G 2 とは抵抗 R 1 を介して電気的に接続され、第 2 ゲート配線 G 2 とソース配線 S L 2 とは抵抗 R 2 を介して電気的に接続されている。

【 0 1 1 8 】

なお、以上の説明においては、P チャネルMOSトランジスタおよび N チャネルMOSトランジスタは、長円環状の同心形状を有するものとして説明したが、この形状に限定されるものではなく、円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

【 0 1 1 9 】

< B - 1 - 2 . 主要部断面構成 >

10

20

30

40

50

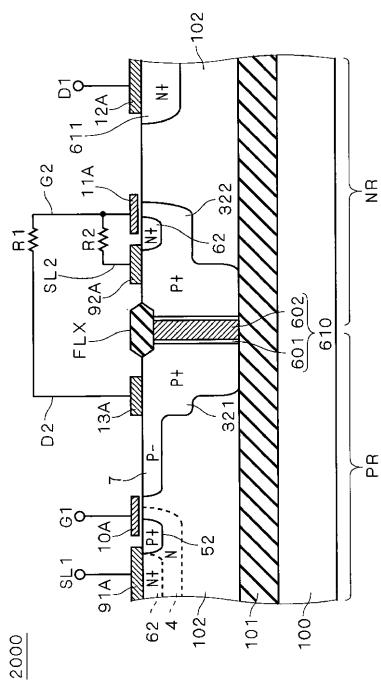

図16におけるX-X線での断面構成を図17に示す。図17に示すようにPチャネルD A D 2 0 0 0は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびS O I層102( $N^-$ )が配設されたS O I基板上に形成される。

【0120】

図17に示すように、PチャネルM O S領域P Rにおいては、S O I層102の表面内に、図に向かって左側からN型ウエル領域4、P型ウエル領域321( $P^+$ )がそれぞれ独立して配設されている。

【0121】

また、P型ウエル領域321とN型ウエル領域4との間には、P型ウエル領域321に連続するようにP型ドレイン領域7( $P^-$ )が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域321よりも浅い。

10

【0122】

そして、N型ウエル領域4の表面内には、図に向かって左側からN型拡散領域62( $N^+$ )およびP型拡散領域52( $P^+$ )が隣接して配設されている。なお、N型ウエル領域4およびN型拡散領域62( $N^+$ )は必ずしも配設する必要はないので破線で示している。

【0123】

また、S O I層102の第1の主面上には、P型拡散領域52およびN型拡散領域62を短絡するように接觸して形成されたソース電極91A、P型ウエル領域321上に接觸して形成された第2ドレイン電極13A、さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)S O I層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10Aが配設されている。

20

【0124】

NチャネルM O S領域N Rにおいては、S O I層102の表面内に、図に向かって右側からN型ウエル領域611( $N^+$ )、P型ウエル領域322( $P^+$ )がそれぞれ独立して配設されている。

【0125】

また、P型ウエル領域322の表面内には、N型拡散領域62( $N^+$ )が配設されている。

30

【0126】

また、S O I層102の第1の主面上には、N型拡散領域62およびP型ウエル領域322を短絡するように接觸して形成されたソース電極92A、N型ウエル領域611上に接觸して形成された第1ドレイン電極12A、さらに、絶縁ゲート電極として、N型拡散領域62の端縁部上から、P型ウエル領域322上およびS O I層102上をカバーするように第2ゲート電極11Aが配設されている。

【0127】

なお、P型ウエル領域322とN型ウエル領域611との間のS O I層102の表面上にはフィールド酸化膜が配設され、当該フィールド酸化膜は、P型ドレイン領域7およびP型ウエル領域32の表面上にも配設され、それらの上部にはマルチフィールドプレートが配設されているが、図示は省略する。

40

【0128】

また、NチャネルM O S領域N RとPチャネルM O S領域P Rとの間のトレンチ分離壁610は、S O I層102を貫通して埋め込み酸化膜101に達するトレンチの内壁を内壁酸化膜601で覆い、内壁酸化膜601で囲まれる領域にドープトポリシリコン等の導電体602が埋め込まれた構成となっている。そして、トレンチ分離壁610の上部にはフィールド酸化膜F L Xが配設されている。この構造は、トレンチ分離壁620および630においても同様である。

【0129】

なお、トレンチ分離壁610の両側面は、埋め込み酸化膜101に達するP型ウエル領域321および322で覆われているが、これは、トレンチ近傍で発生する結晶欠陥を覆い

50

、デバイス内に結晶欠陥に起因するリーク電流が流れないようにするための構成である。

【0130】

< B - 2 . 動作 >

次に図16および図17を用いてPチャネルDAD2000の動作について説明する。

【0131】

PチャネルDAD2000のオン動作は、ハイサイド領域HRからのゲート信号が第1ゲート電極10Aに与えられると、まずPチャネルMOS領域PRにおいて、第1ゲート電極10A直下のN型ウエル領域4およびSOI層102の表面内で形成されるP型チャネルを通って、P型拡散領域52からP型ドレイン領域7に向かってホールが注入される。ホールは、第2ドレイン電極13Aに流れ込み、第2ドレイン電極13Aから第2ドレイン配線D2を通ってソース電極92Aに流れる。 10

【0132】

一方、ホール電流によって抵抗R1およびR2中にて発生した電位差が所定の値になると、第2ゲート電極11Aがゲートとして機能し、その直下のP型ウエル領域322の表面内に形成されたN型チャネルを通ってN型拡散領域62からSOI層102に向かって電子が注入され、注入された電子はN型ウエル領域611を経由して第1ドレイン電極12Aに到達し、図示しないローサイド(低電位)領域に電気的に接続された第1ドレイン電極12Aの電位が制御されることになる。

【0133】

このように、PチャネルMOS領域PRとNチャネルMOS領域NRとは電気的に分離されホールは直接にNチャネルMOS領域NRを流れることなく、また電子もPチャネルMOS領域PRを直接に流れることないので、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。 20

【0134】

なお、図17に示すように、PチャネルMOS領域PRにもNチャネルMOS領域NRにも寄生サイリスタ構造が存在しないので、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。

【0135】

< C . 実施の形態3 >

< C - 1 . 装置構成 >

30

本発明に係る実施の形態3として、図18および図19を用いてPチャネルDAD3000の構成について説明する。

【0136】

< C - 1 - 1 . 平面構成 >

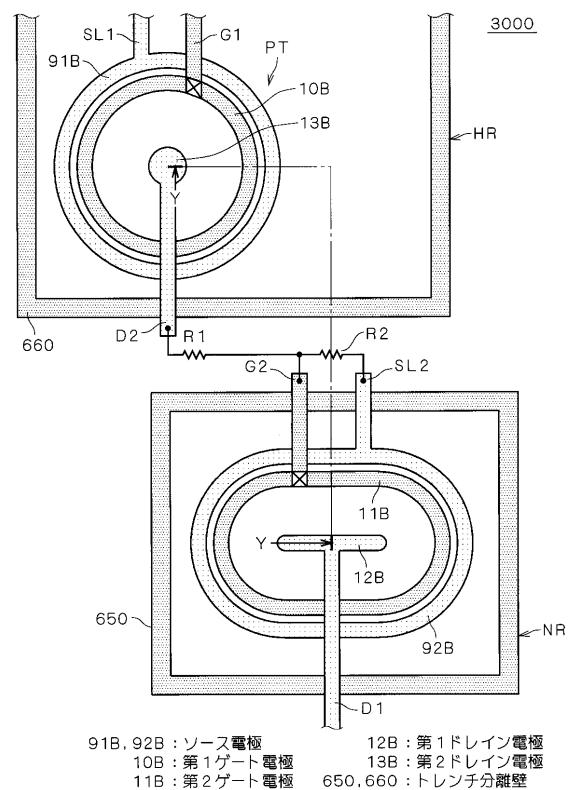

図18はPチャネルDAD3000の平面構成を示す図である。図18に示すように、PチャネルDAD3000は、NチャネルMOS領域NRがトレンチ分離壁650(第2のトレンチ分離壁)によって囲まれて独立し、また、PチャネルMOSトランジスタPTがハイサイド領域HRに形成され、ハイサイド領域HRもトレンチ分離壁640(第1のトレンチ分離壁)によって囲まれて独立している。なお、トレンチ分離壁640および650は、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとを電気的に分離するので、分離構造と呼称することができる。 40

【0137】

PチャネルMOSトランジスタPTは、円形のドレイン電極13Bを中心部に有し、ドレイン電極13Bを取り囲むように、円環状の第1ゲート電極10Bが配設され、第1ゲート電極10Bを取り囲むように、円環状のソース電極91Bが配設されて構成されている。

【0138】

そして、ソース電極91B、第1ゲート電極10Bおよび第2ドレイン電極13Bにはそれぞれソース配線SL1、第1ゲート配線G1、第2ドレイン配線D2が接続されている。 50

## 【0139】

ソース配線 S L 1 および第 1 ゲート配線 G 1 は、例えば第 2 層アルミ配線で構成され、第 1 ゲート配線 G 1 はソース電極 9 1 B 上をオーバーラップして、ハイサイド領域 H R 内に延在している。

## 【0140】

また、第 2 ドレイン配線 D 2 は、例えば第 1 層アルミ配線で構成され、第 1 ゲート電極 1 0 B、ソース電極 9 1 B およびトレンチ分離壁 6 2 0 上をオーバーラップして、N チャネル MOS 領域 N R 側のハイサイド領域 H R 外部に延在している。

## 【0141】

N チャネル MOS 領域 N R においては、直線状の第 1 ドレイン電極 1 2 B を中央部に有し、第 1 ドレイン電極 1 2 B を取り囲むように、長円環状の第 2 ゲート電極 1 1 B が配設され、第 2 ゲート電極 1 1 B を取り囲むように、長円環状のソース電極 9 2 B が配設されて N チャネル MOS トランジスタを構成している。 10

## 【0142】

そして、第 1 ドレイン電極 1 2 B、第 2 ゲート電極 1 1 B およびソース電極 9 2 B には、それぞれ第 1 ドレイン配線 D 1、第 2 ゲート配線 G 2 およびソース配線 S L 2 が接続されている。

## 【0143】

ソース配線 S L 2 および第 2 ゲート配線 G 2 は、例えば第 2 層アルミ配線で構成され、ソース配線 S L 2 はトレンチ分離壁 6 5 0 上をオーバーラップし、第 2 ゲート配線 G 2 はソース電極 9 2 B 上およびトレンチ分離壁 6 5 0 上をオーバーラップして、ハイサイド領域 H R 側の N チャネル MOS 領域 N R 外部に延在している。 20

## 【0144】

また、第 1 ドレイン配線 D 1 は、例えば第 1 層アルミ配線で構成され、第 2 ゲート電極 1 1 B およびソース電極 9 2 B 上をオーバーラップし、さらにトレンチ分離壁 6 5 0 上をオーバーラップして、ハイサイド領域 H R とは反対側の N チャネル MOS 領域 N R 外部に延在している。

## 【0145】

なお、第 1 ゲート電極 1 0 B および第 2 ゲート電極 1 1 B はドープトポリシリコンで構成され、第 1 ゲート配線 G 1 および第 2 ゲート配線 G 2 とはコンタクトホールにより接続される構成となっている。 30

## 【0146】

そして、第 2 ドレイン配線 D 2 と第 2 ゲート配線 G 2 とは抵抗 R 1 を介して電気的に接続され、第 2 ゲート配線 G 2 とソース配線 S L 2 とは抵抗 R 2 を介して電気的に接続されている。

## 【0147】

なお、以上の説明においては、N チャネル MOS トランジスタは、長円環状の同心形状を有するものとして説明したが、この形状に限定されるものではなく、円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

## 【0148】

また、P チャネル MOS トランジスタは、円環の同心形状を有するものとして説明したが、この形状に限定されるものではなく、長円環状の同心形状、あるいは矩形環状の同心形状であっても良い。 40

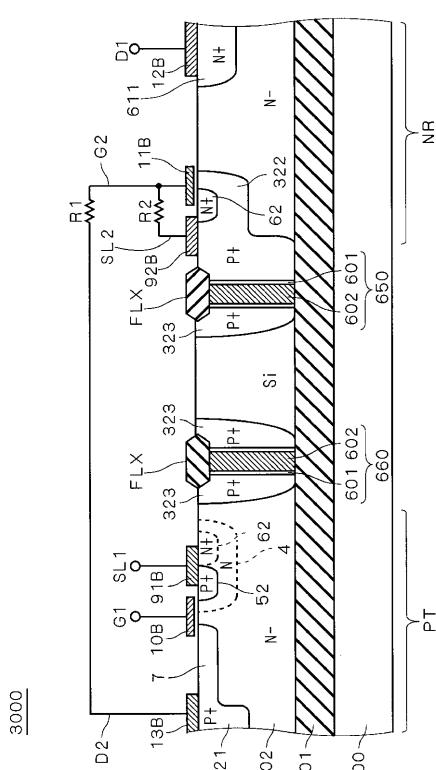

## 【0149】

< C - 1 - 2 . 主要部断面構成 >

図 18 における Y - Y 線での断面構成を図 19 に示す。図 19 に示すように P チャネル D A D 3 0 0 0 は、シリコン基板等の支持基板 1 0 0 上に、埋め込み酸化膜 1 0 1 および S O I 層 1 0 2 (N<sup>-</sup>) が配設された S O I 基板上に形成される。

## 【0150】

図 19 に示すように、P チャネル MOS トランジスタ P T においては、S O I 層 1 0 2 の 50

表面内に、図に向かって左側から P 型ウエル領域 321 (P<sup>+</sup>)、N 型ウエル領域 4 がそれぞれ独立して配設されている。

【0151】

また、P 型ウエル領域 321 と N 型ウエル領域 4 との間には、P 型ウエル領域 321 に連続するように P 型ドレイン領域 7 (P<sup>-</sup>) が形成されている。なお、P 型ドレイン領域 7 の形成深さは、P 型ウエル領域 321 よりも浅い。

【0152】

そして、N 型ウエル領域 4 の表面内には、図に向かって左側から P 型拡散領域 52 (P<sup>+</sup>) および N 型拡散領域 62 (N<sup>+</sup>) が隣接して配設されている。なお、N 型ウエル領域 4 および N 型拡散領域 62 (N<sup>+</sup>) は必ずしも配設する必要はないので破線で示している。

10

【0153】

また、SOI 層 102 の第 1 の主面上には、P 型拡散領域 52 および N 型拡散領域 62 を短絡するように接觸して形成されたソース電極 91B、P 型ウエル領域 321 上に接觸して形成された第 2 ドレイン電極 13B、さらに、絶縁ゲート電極として、P 型ドレイン領域 7 の端縁部上から、(P 型ドレイン領域 7 と N 型ウエル領域 4 との間の) SOI 層 102 上、N 型ウエル領域 4 上および P 型拡散領域 52 の端縁部上をカバーするように第 1 ゲート電極 10B が配設されている。

【0154】

N チャネル MOS 領域 NR においては、SOI 層 102 の表面内に、図に向かって右側から N 型ウエル領域 611 (N<sup>+</sup>)、P 型ウエル領域 322 (P<sup>+</sup>) がそれぞれ独立して配設されている。

20

【0155】

また、P 型ウエル領域 322 の表面内には、N 型拡散領域 62 (N<sup>+</sup>) が配設されている。

【0156】

また、SOI 层 102 の第 1 の主面上には、N 型拡散領域 62 および P 型ウエル領域 322 を短絡するように接觸して形成されたソース電極 92B、N 型ウエル領域 611 上に接觸して形成された第 1 ドレイン電極 12B、さらに、絶縁ゲート電極として、N 型拡散領域 62 の端縁部上から、P 型ウエル領域 322 上および SOI 层 102 上をカバーするように第 2 ゲート電極 11B が配設されている。

30

【0157】

なお、P 型ウエル領域 322 と N 型ウエル領域 611 との間の SOI 层 102 の表面上にはフィールド酸化膜が配設され、当該フィールド酸化膜は、P 型ドレイン領域 7 および P 型ウエル領域 322 の表面上にも配設され、それらの上部にはマルチフィールドプレートが配設されているが、図示は省略する。

【0158】

また、トレンチ分離壁 650 および 660 は、SOI 层 102 を貫通して埋め込み酸化膜 101 に達するトレンチの内壁を内壁酸化膜 601 で覆い、内壁酸化膜 601 で囲まれる領域にドープトポリシリコン等の導電体 602 が埋め込まれた構成となっている。そして、トレンチ分離壁 650 および 660 の上部にはフィールド酸化膜 FLX が配設されている。

40

【0159】

なお、トレンチ分離壁 660 の両側面は、埋め込み酸化膜 101 に達する P 型ウエル領域 323 で覆われ、トレンチ分離壁 650 の両側面は、埋め込み酸化膜 101 に達する P 型ウエル領域 322 および 323 で覆われているが、これは、トレンチ近傍で発生する結晶欠陥を覆い、デバイス内に結晶欠陥に起因するリーク電流が流れないようにするための構成である。

【0160】

< C - 2 . 動作 >

次に図 18 および図 19 を用いて P チャネル DAD3000 の動作について説明する。

50

## 【0161】

PチャネルMOSトランジスタPTのオン動作は、ゲート信号が第1ゲート電極10Bに与えられると、まずPチャネルMOSトランジスタPTにおいて、第1ゲート電極10B直下のN型ウエル領域4およびSOI層102の表面内で形成されるP型チャネルを通って、P型拡散領域52からP型ドレイン領域7に向かってホールが注入される。ホールは、第2ドレイン電極13Bに流れ込み、第2ドレイン電極13Bから第2ドレイン配線D2を通ってソース電極92Bに流れる。

## 【0162】

一方、ホール電流によって抵抗R1およびR2中にて発生した電位差が所定の値になると、第2ゲート電極11Bがゲートとして機能し、その直下のP型ウエル領域322の表面内に形成されたN型チャネルを通ってN型拡散領域62からSOI層102に向かって電子が注入され、注入された電子はN型ウエル領域611を経由して第1ドレイン電極12Bに到達し、図示しないローサイド(低電位)領域に電気的に接続された第1ドレイン電極12Bの電位が制御されることになる。

10

## 【0163】

このように、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとは電気的に分離されホールは直接にNチャネルMOS領域NRを流れることができなく、また電子もPチャネルMOS領域PRを直接に流れることができないので、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

20

## 【0164】

なお、図19に示すように、PチャネルMOSトランジスタPTにもNチャネルMOS領域NRにも寄生サイリスタ構造が存在しないので、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。

## 【0165】

また、PチャネルMOSトランジスタPTがハイサイド領域HR内に形成されているので、PチャネルMOSトランジスタPTをNチャネルMOS領域NRから電気的に分離する専用のトレンチ分離壁が不要となり、半導体装置の集積度を上げることができる。

## 【0166】

<D. 実施の形態4>

<D-1. 装置構成>

30

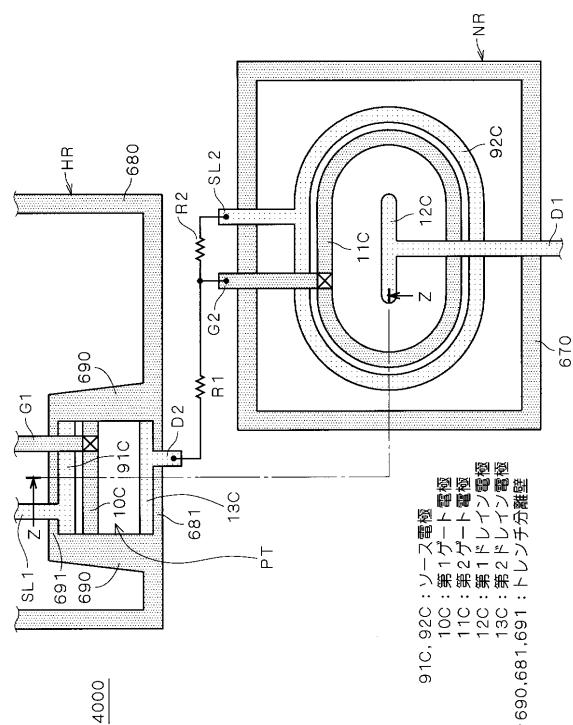

本発明に係る実施の形態4として、図20および図21を用いてPチャネルDAD4000の構成について説明する。

## 【0167】

<D-1-1. 平面構成>

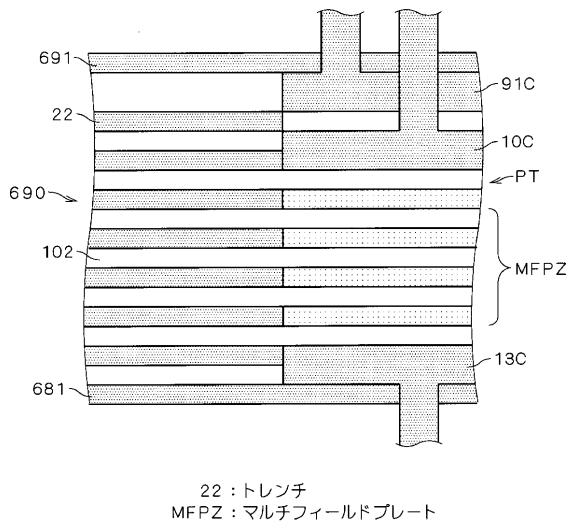

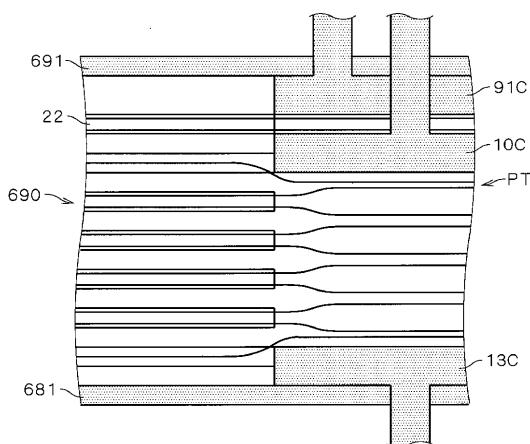

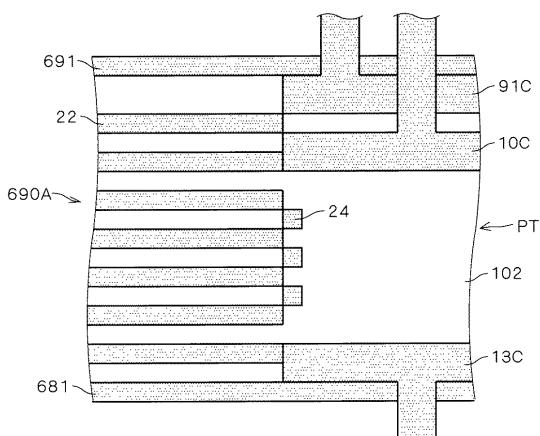

図20はPチャネルDAD4000の平面構成を示す図である。図20に示すように、PチャネルDAD4000は、NチャネルMOS領域NRがトレンチ分離壁670(第2のトレンチ分離壁)によって囲まれて独立し、また、PチャネルMOSトランジスタPTがハイサイド領域HR内に形成され、ハイサイド領域HRを囲むトレンチ分離壁680(第1のトレンチ分離壁)と一体になったトレンチ分離壁690(側面分離壁)、691(第1の分離壁)および681(第2の分離壁)によって囲まれて独立している。なお、トレンチ分離壁670～690、691および681は、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとを電気的に分離するので、分離構造と呼称することができる。

40

## 【0168】

PチャネルMOSトランジスタPTは、ハイサイド領域HRの内部側から順に平行に配設された、直線状のソース電極91C、第1ゲート電極10Cおよび第2ドレイン電極13Cで構成されている。

## 【0169】

そして、ソース電極91C、第1ゲート電極10Cおよび第2ドレイン電極13Cの各自的の両端部にはトレンチ分離壁690が配設され、ソース電極91Cよりもハイサイド領

50

域 H R の内部側にはトレンチ分離壁 6 9 1 が配設され、第 2 ドレイン電極 1 3 C よりも外部側にはトレンチ分離壁 6 8 1 が配設されている。

【 0 1 7 0 】

そして、ソース電極 9 1 C 、第 1 ゲート電極 1 0 C および第 2 ドレイン電極 1 3 C にはそれぞれソース配線 S L 1 、第 1 ゲート配線 G 1 、第 2 ドレイン配線 D 2 が接続されている。

【 0 1 7 1 】

ソース配線 S L 1 および第 1 ゲート配線 G 1 は、例えば第 2 層アルミ配線で構成され、第 1 ゲート配線 G 1 はソース電極 9 1 C 上をオーバーラップして、ハイサイド領域 H R 内に延在し、ソース配線 S L 1 は、トレンチ分離壁 6 9 1 上をオーバーラップして、ハイサイド領域 H R 内に延在している。

【 0 1 7 2 】

また、第 2 ドレイン配線 D 2 は、例えば第 1 層アルミ配線で構成され、トレンチ分離壁 6 8 0 上をオーバーラップして、N チャネル M O S 領域 N R 側のハイサイド領域 H R 外部に延在している。

【 0 1 7 3 】

N チャネル M O S 領域 N R においては、直線状の第 1 ドレイン電極 1 2 C を中央部に有し、第 1 ドレイン電極 1 2 C を取り囲むように、長円環状の第 2 ゲート電極 1 1 C が配設され、第 2 ゲート電極 1 1 C を取り囲むように、長円環状のソース電極 9 2 C が配設されて N チャネル M O S トランジスタを構成している。

【 0 1 7 4 】

そして、第 1 ドレイン電極 1 2 C 、第 2 ゲート電極 1 1 C およびソース電極 9 2 C には、それぞれ第 1 ドレイン配線 D 1 、第 2 ゲート配線 G 2 およびソース配線 S L 2 が接続されている。

【 0 1 7 5 】

ソース配線 S L 2 および第 2 ゲート配線 G 2 は、例えば第 2 層アルミ配線で構成され、ソース配線 S L 2 はトレンチ分離壁 6 7 0 上をオーバーラップし、第 2 ゲート配線 G 2 はソース電極 9 2 C 上およびトレンチ分離壁 6 7 0 上をオーバーラップして、ハイサイド領域 H R 側の N チャネル M O S 領域 N R 外部に延在している。

【 0 1 7 6 】

また、第 1 ドレイン配線 D 1 は、例えば第 1 層アルミ配線で構成され、第 2 ゲート電極 1 1 C およびソース電極 9 2 C 上をオーバーラップし、さらにトレンチ分離壁 6 7 0 上をオーバーラップして、ハイサイド領域 H R とは反対側の N チャネル M O S 領域 N R 外部に延在している。

【 0 1 7 7 】

なお、第 1 ゲート電極 1 0 C および第 2 ゲート電極 1 1 C はドープトポリシリコンで構成され、第 1 ゲート配線 G 1 および第 2 ゲート配線 G 2 とはコンタクトホールにより接続される構成となっている。

【 0 1 7 8 】

そして、第 2 ドレイン配線 D 2 と第 2 ゲート配線 G 2 とは抵抗 R 1 を介して電気的に接続され、第 2 ゲート配線 G 2 とソース配線 S L 2 とは抵抗 R 2 を介して電気的に接続されている。

【 0 1 7 9 】

なお、以上の説明においては、N チャネル M O S トランジスタは、長円環状の同心形状を有するものとして説明したが、この形状に限定されるものではなく、円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

【 0 1 8 0 】

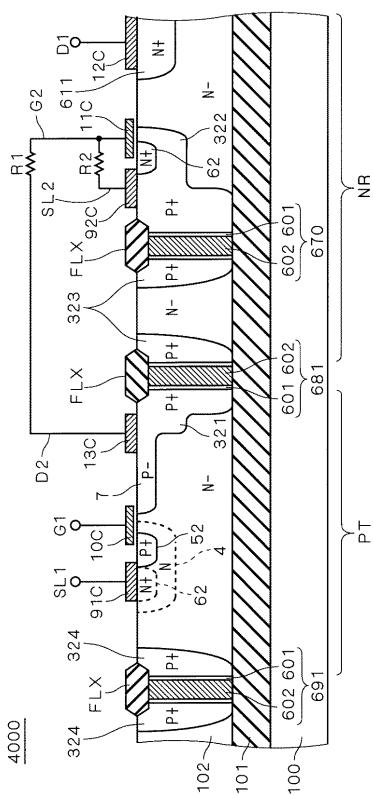

< D - 1 - 2 . 主要部断面構成 >

図 2 0 における Z - Z 線での断面構成を図 2 1 に示す。図 2 1 に示すように P チャネル D A D 4 0 0 0 は、シリコン基板等の支持基板 1 0 0 上に、埋め込み酸化膜 1 0 1 および S

10

20

30

40

50

SOI層102(N<sup>-</sup>)が配設されたSOI基板上に形成される。

【0181】

図21に示すように、PチャネルMOSトランジスタPTにおいては、SOI層102の表面内に、図に向かって左側からN型ウエル領域4、P型ウエル領域321(P<sup>+</sup>)がそれぞれ独立して配設されている。

【0182】

また、P型ウエル領域321とN型ウエル領域4との間には、P型ウエル領域321に連続するようにP型ドレイン領域7(P<sup>-</sup>)が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域321よりも浅い。

【0183】

そして、N型ウエル領域4の表面内には、図に向かって左側からN型拡散領域62(N<sup>+</sup>)およびP型拡散領域52(P<sup>+</sup>)が隣接して配設されている。なお、N型ウエル領域4およびN型拡散領域62(N<sup>+</sup>)は必ずしも配設する必要はないので破線で示している。

【0184】

また、SOI層102の第1の主面上には、P型拡散領域52およびN型拡散領域62を短絡するように接触して形成されたソース電極91C、P型ウエル領域321上に接触して形成された第2ドレイン電極13C、さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)SOI層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10Cが配設されている。

【0185】

NチャネルMOS領域NRにおいては、SOI層102の表面内に、図に向かって右側からN型ウエル領域611(N<sup>+</sup>)、P型ウエル領域322(P<sup>+</sup>)がそれぞれ独立して配設されている。

【0186】

また、P型ウエル領域322の表面内には、N型拡散領域62(N<sup>+</sup>)が配設されている。

【0187】

また、SOI層102の第1の主面上には、N型拡散領域62およびP型ウエル領域322を短絡するように接触して形成されたソース電極92C、N型ウエル領域611上に接触して形成された第1ドレイン電極12C、さらに、絶縁ゲート電極として、N型拡散領域62の端縁部上から、P型ウエル領域322上およびSOI層102上をカバーするように第2ゲート電極11Cが配設されている。

【0188】

なお、P型ウエル領域322とN型ウエル領域611との間のSOI層102の表面上にはフィールド酸化膜が配設され、当該フィールド酸化膜は、P型ドレイン領域7およびP型ウエル領域322の表面上にも配設され、それらの上部にはマルチフィールドプレートが配設されているが、図示は省略する。

【0189】

また、トレンチ分離壁691、681および670は、SOI層102を貫通して埋め込み酸化膜101に達するトレンチの内壁を内壁酸化膜601で覆い、内壁酸化膜601で囲まれる領域にドープトポリシリコン等の導電体602が埋め込まれた構成となっている。そして、トレンチ分離壁691、681および670の上部にはフィールド酸化膜FLXが配設されている。

【0190】

なお、トレンチ分離壁691の両側面は、埋め込み酸化膜101に達するP型ウエル領域324で覆われ、トレンチ分離壁681の両側面は、埋め込み酸化膜101に達するP型ウエル領域321および323で覆われ、トレンチ分離壁670の両側面は、埋め込み酸化膜101に達するP型ウエル領域322および323で覆われているが、これは、トレンチ近傍で発生する結晶欠陥を覆い、デバイス内に結晶欠陥に起因するリーク電流が流

10

20

30

40

50

れないようにするための構成である。

【0191】

< D - 1 - 3 . トレンチ分離壁の構成および機能 >

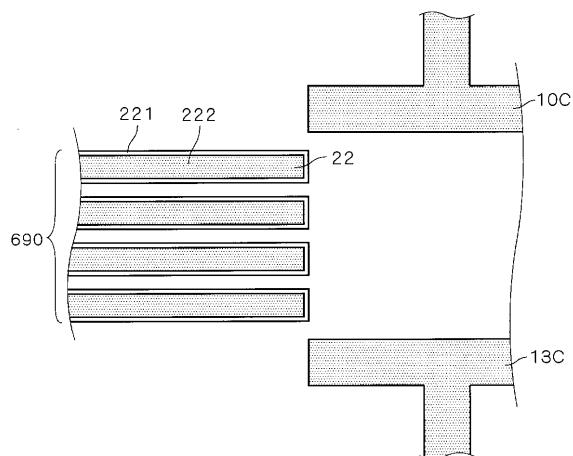

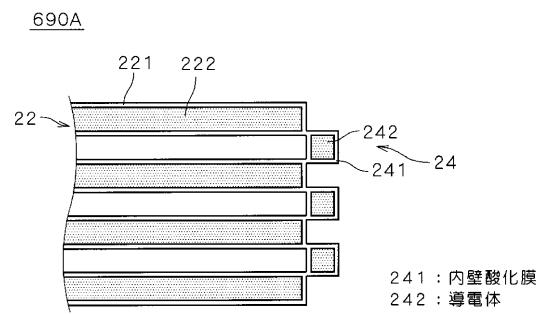

ここで、トレンチ分離壁 690 の構成および機能について図 22 ~ 図 26 を用いて説明する。

【0192】

図 22 はトレンチ分離壁 690 と、その近傍の P チャネル MOS トランジスタ PT の詳細構成を示す平面図である。

【0193】

図 22 に示すように、トレンチ分離壁 690 は P チャネル MOS トランジスタ PT の各電極に平行に配設された複数のトレンチ 22 で構成されるマルチトレンチ構造を有している。なお、トレンチ 22 間は SOI 層 102 であることは言うまでもない。

【0194】

また、P チャネル MOS トランジスタ PT における第 1 ゲート電極 10C と、第 2 ドレイン電極 13C との間の SOI 層 102 の上部には、マルチフィールドプレート MFPZ が配設されている。

【0195】

そして、マルチフィールドプレート MFPZ の配列方向に沿ったプレート幅（ライン）およびプレート間隔（スペース）は、マルチトレンチ構造のトレンチ幅（ライン）およびトレンチ間隔（スペース）と一致するように構成されている。

【0196】

このように構成することで、ソース・ドレイン間の電位分布を均一化して、トレンチ分離壁 690 と P チャネル MOS トランジスタ PT との境界部での電界集中を抑制することができる。

【0197】

その仕組みについて図 23 ~ 図 25 を用いて説明する。

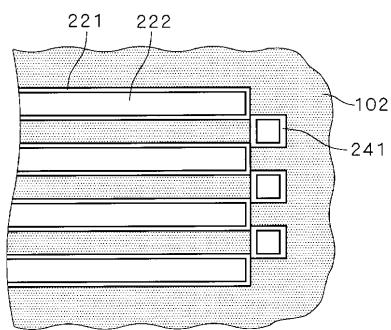

図 23 はトレンチ 22 の構成を詳細に示す図であり、図 22 に示す構成において、トレンチ 22 を拡大して示し、マルチフィールドプレート MFPZ 等は省略している。

【0198】

図 23 に示すように、各トレンチ 22 のそれぞれは、内壁酸化膜 221 によって壁面が覆われ、内壁酸化膜 221 で囲まれた領域にドープトポリシリコン等の導電体 222 が埋め込まれた構成となっている。なお、充填された各導電体は他の特定の部位と電気的に接続されることなく形成されている。

【0199】

図 24 は順方向阻止電圧印加時にソース・ドレイン間で発生する電界分布を示す図であり、ソース・ドレイン間で発生する電界は、トレンチ 22 の内壁酸化膜 221 を通って P チャネル MOS トランジスタ PT のソース電極 91C と第 2 ドレイン電極 13C との間の領域に分布しており、電界の集中部が存在せず、ほぼ均一な分布となっている。

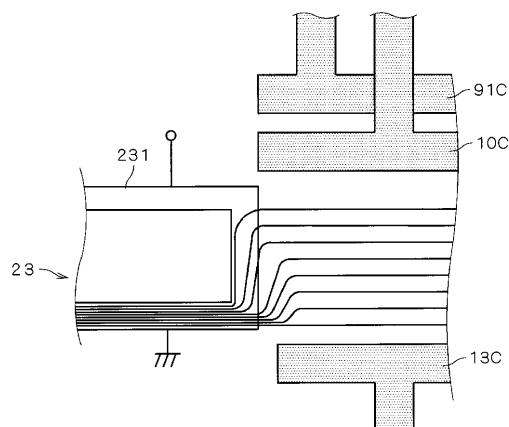

【0200】

一方、電界が集中する構成の一例を図 25 に示す。図 25 は複数のトレンチ 22 で構成されるトレンチ分離壁 690 の代わりに、MOS トランジスタ PT のソース・ドレイン間の距離にほぼ一致するトレンチ幅を有する単一のトレンチ 23 を配設した構成を示している。

【0201】

図 25においてはトレンチ 23 の内壁酸化膜 231 だけを示しており、内壁酸化膜 231 のソース電極 91C 側の一辺にはソース電圧（正電位）が与えられ、第 2 ドレイン電極 13C 側の一辺は接地電位となっている。

【0202】

このような構成において、内壁酸化膜 231 で囲まれた領域の導電体内では同電位となるので、ソース・ドレイン間で発生する電界は、内壁酸化膜 231 の第 2 ドレイン電極 13

10

20

30

40

50

C側の一辺において集中し、酸化膜の絶縁破壊電圧の超過による絶縁破壊や、シリコンの物性値である臨界電界強度(  $V/cm$  )を超えた電界がシリコン中で発生すると、アバランシェ電流が誘起され、空乏層中の空間電荷を補償して、阻止特性( 電圧を印加しても電流を流さない特性 )を消失させる現象が発生し、所定の耐圧特性が得られなくなる。

【 0 2 0 3 】

しかし、マルチトレンチ構造を有するトレンチ分離壁 690においては、上述したように電界集中を防止できるので、耐圧特性が低下することはない。

【 0 2 0 4 】

また、マルチフィールドプレート MFPZ のラインおよびスペースは、マルチトレンチ構造のラインおよびスペースと一致しているので、PチャネルMOSトランジスタPTのソース電極 91C と第2ドレイン電極 13C との間の領域の電界分布を整えることができる。

10

【 0 2 0 5 】

< D - 2 . 動作 >

PチャネルDAD4000の動作は、図18および図19を用いて説明したPチャネルDAD3000と同様であり、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとは電気的に分離されホールは直接にNチャネルMOS領域NRを流れることができなく、また電子もPチャネルMOS領域PRを直接に流れることができないので、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

【 0 2 0 6 】

20

なお、図21に示すように、PチャネルMOSトランジスタPTにもNチャネルMOS領域NRにも寄生サイリスタ構造が存在しないので、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。

【 0 2 0 7 】

また、PチャネルMOSトランジスタPTがハイサイド領域HR内に形成されているので、PチャネルMOSトランジスタPTをNチャネルMOS領域NRから電気的に分離する専用のトレンチ分離壁が不要となり、半導体装置の集積度を上げることができる。

【 0 2 0 8 】

なお、PチャネルDAD4000においては、PチャネルMOSトランジスタPTをトレンチ分離壁 690、691 および 681 が近接して取り囲み、トレンチ分離壁内に埋め込まれるように構成されるので、PチャネルMOSトランジスタPTが占有する面積が縮小され、半導体装置の集積度を上げることができる。

30

【 0 2 0 9 】

< D - 3 . 変形例 >

図22を用いて説明したトレンチ分離壁 690においては、PチャネルMOSトランジスタPTの各電極に平行に複数のトレンチ 22 が配設されている構成を示した。そして、トレンチ間にはSOI層102が存在し、当該トレンチ間のSOI層102は、PチャネルMOSトランジスタPTのソース・ドレイン間のSOI層102に連続する構成を示した。

【 0 2 1 0 】

40

しかし、この構成ではPチャネルDAD4000のオン動作において、PチャネルMOSトランジスタPTのソース・ドレイン間を流れるホールキャリアが、トレンチ 22 間のSOI層102に拡散して蓄積し、スイッチング損失の増大を招く可能性がある。

【 0 2 1 1 】

これを防止するための構成が、図26に示すトレンチ分離壁 690A である。図26は図22に対応する図であり、同一の構成について同一の符号を付し、重複する説明は省略する。また、便宜的にマルチフィールドプレート MFPZ も省略している。

【 0 2 1 2 】

図26において、各トレンチ 22 の間のSOI層102のPチャネルMOSトランジスタPT側の端部には、トレンチ 24 が配設され、両サイドのトレンチ 22 と接触するように

50

配設されている。

【0213】

図27にトレンチ分離壁690Aの詳細部分構成を示す。図27に示すように、トレンチ24の第1の辺はトレンチ22間の長さにほぼ等しく、それに直交する第2の辺は、上記第1の辺とほぼ同じ長さであり、平面視形状は矩形となっている。

【0214】

構造的にはトレンチ22と同様であり、内壁酸化膜241によって壁面が覆われ、内壁酸化膜241で囲まれた領域にドープトポリシリコン等の導電体242が埋め込まれた構成となっている。

【0215】

そして、トレンチ24は、その内壁酸化膜241が両サイドのトレンチ22の内壁酸化膜221と接触して一体となるように配設され、トレンチ22の間のSOI層102にPチャネルMOSトランジスタPTからホールキャリアが流入することを防止する構成となっている。

【0216】

なお、トレンチ分離壁690Aに対向するPチャネルMOSトランジスタPTのSOI層102は、正確には図21に示すP型ドレイン領域7(ドリフト領域)であり、ホールキャリアが移動する領域である。

【0217】

トレンチ24の存在により、トレンチ22間のSOI層102にホールキャリアが蓄積することなく、スイッチング損失の増大を招くことが防止できる。

【0218】

なお、トレンチ分離壁690と同様に、トレンチ分離壁690Aによっても電界集中を防止して、安定した耐圧特性を得ることができることは言うまでもない。

【0219】

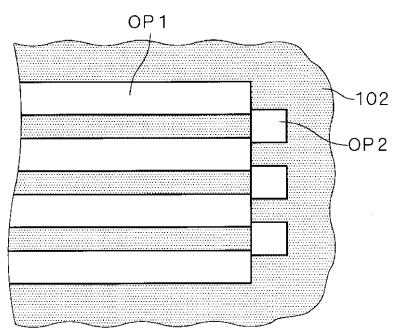

次に、図28および図29を用いてトレンチ分離壁690Aの製造方法について説明する。

【0220】

まず、図28に示すように、SOI層102の第1の主面に、トレンチ22および24に対応する開口部OP1およびOP2を形成する。なお、開口部OP1間の間隔は2~3μm程度である。

【0221】

次に、開口部OP1およびOP2の内面を酸化して、厚さ0.1~0.2μm(1000~2000オングストローム)程度の内壁酸化膜221および241を形成する。このとき、内壁酸化膜221および241が一体化することになる。

【0222】

その後、内壁酸化膜221および241で囲まれる領域に、ドープトポリシリコン等の導電体222および242を埋め込むことで、トレンチ分離壁690Aを得ることができる。

【0223】

【発明の効果】

本発明に係る請求項1記載の半導体装置によれば、第1のMOSトランジスタの主電流が、第2のMOSトランジスタの形成領域を通過して第1の主電極に流入することを防止するように分離構造が設けられているので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制でき、寄生サイリスタのラッチアップを防止できる。また、第1のMOSトランジスタが第2のMOSトランジスタの形成領域に内包されるような形状において、分離領域のPN接合分離のための不純物領域内に、第1のMOSトランジスタの第1の主電極側から第2の主電極側に向けて少なくとも一列に配列された複数のトレンチを備えているので、順方向阻止電圧印加時に第1および第2の主

10

20

30

40

50

電極間で発生する電界は、各トレンチの内壁酸化膜を通って分布することになり、電界を各トレンチごとに分担することができ、分離領域における電界集中を緩和して、耐圧特性を安定化できる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

#### 【0225】

本発明に係る請求項2記載の半導体装置によれば、複数のトレンチの配列方向に沿ったトレンチ幅およびトレンチ間隔は、マルチフィールドプレートの配列方向に沿ったプレート幅およびプレート間隔にほぼ一致するように設定されるので、複数のトレンチで分配された電界分布はマルチフィールドプレートによっても維持され、マルチフィールドプレートと組み合わせて用いることで、分離領域における電界集中をさらに緩和することができる。

10

#### 【0226】

本発明に係る請求項3記載の半導体装置によれば、第1および第2のMOSトランジスタを独立して配設し、第1および第2のトレンチ分離壁によって第1および第2のMOSトランジスタを電気的に分離するので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。また、第1および第2のMOSトランジスタを独立して配設し、電気的に分離することで、寄生サイリスタ構造が存在せず、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

20

#### 【0227】

本発明に係る請求項4記載の半導体装置によれば、第1および第2のMOSトランジスタを独立して配設し、第1のMOSトランジスタは第1のトレンチ分離壁で囲まれるハイサイド領域内に配設され、第2のMOSトランジスタは第2のトレンチ分離壁で囲まれて電気的に分離されるので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。また、第1および第2のMOSトランジスタを独立して配設し、電気的に分離することで、寄生サイリスタ構造が存在せず、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。また、第1のMOSトランジスタがハイサイド領域に形成されるので、第1のMOSトランジスタを電気的に分離する専用のトレンチ分離壁が不要となり、半導体装置の集積度を上げることができる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

30

#### 【0228】

本発明に係る請求項5記載の半導体装置によれば、第1および第2のMOSトランジスタを独立して配設し、第1のMOSトランジスタは第1のトレンチ分離壁で囲まれるハイサイド領域内において、第1のトレンチ分離壁内に埋め込まれるように配設されて電気的に分離されるので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。また、第1および第2のMOSトランジスタを独立し

40

50

て配設し、電気的に分離することで、寄生サイリスタ構造が存在せず、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。また、第1のMOSトランジスタは第1のトレンチ分離壁内に埋め込まれるように配設されるので、第1のMOSトランジスタが占有する面積が縮小され、半導体装置の集積度を上げることができる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

【0229】

10

本発明に係る請求項6記載の半導体装置によれば、順方向阻止電圧印加時に第1および第2の主電極間で発生する電界は、側面分離壁を構成する各トレンチの内壁酸化膜を通じて分布することになり、第1のMOSトランジスタの第1および第2の主電極間において、ほぼ均一に分布し、側面分離壁において電界の集中部が存在せず、電界集中を緩和して、耐圧特性を安定化できる。

【0230】

本発明に係る請求項7記載の半導体装置によれば、複数の第2のトレンチが複数の第1のトレンチ間のSOI層の端部を塞ぐように配列され、複数の第1のトレンチの内壁酸化膜と複数の第2のトレンチの内壁酸化膜とが互いに接合して一体化しているので、オン動作において、第1のMOSトランジスタの第1および第2の主電極間を流れるキャリアが、複数の第1のトレンチ間のSOI層に拡散することが防止され、スイッチング損失の増大を招くことを防止できる。

20

【図面の簡単な説明】

【図1】 本発明に係る実施の形態1の半導体装置の平面構成を示す図である。

【図2】 本発明に係る実施の形態1の半導体装置の断面構成を示す図である。

【図3】 本発明に係る実施の形態1の半導体装置の部分断面構成を示す図である。

【図4】 本発明に係る実施の形態1の半導体装置の部分構成を示す斜視図である。

【図5】 本発明に係る実施の形態1の半導体装置の効果を説明する図である。

【図6】 マルチトレンチの製造工程を示す断面図である。

【図7】 マルチトレンチの製造工程を示す断面図である。

30

【図8】 マルチトレンチの製造工程を示す断面図である。

【図9】 マルチトレンチの製造工程を示す断面図である。

【図10】 マルチフィールドプレートが1層の場合の構成を示す図である。

【図11】 マルチフィールドプレートの効果を説明する模式図である。

【図12】 マルチフィールドプレートが2層の場合の構成を示す図である。

【図13】 マルチフィールドプレートの効果を説明する模式図である。

【図14】 マルチフィールドプレートの配設状態の一例を示す平面図である。

【図15】 マルチフィールドプレートの配設状態の変形例を示す平面図である。

【図16】 本発明に係る実施の形態2の半導体装置の平面構成を示す図である。

40

【図17】 本発明に係る実施の形態2の半導体装置の断面構成を示す図である。

【図18】 本発明に係る実施の形態3の半導体装置の平面構成を示す図である。

【図19】 本発明に係る実施の形態3の半導体装置の断面構成を示す図である。

【図20】 本発明に係る実施の形態4の半導体装置の平面構成を示す図である。

【図21】 本発明に係る実施の形態4の半導体装置の断面構成を示す図である。

【図22】 本発明に係る実施の形態4の半導体装置の部分平面構成を示す図である。

【図23】 本発明に係る実施の形態4の半導体装置の部分平面構成を示す図である。

【図24】 本発明に係る実施の形態4の半導体装置の効果を説明する図である。

【図25】 本発明に係る実施の形態4の半導体装置の構成を適用しない場合の問題点を説明する図である。

【図26】 本発明に係る実施の形態4の半導体装置の変形例の部分平面構成を示す図で

50

ある。

【図27】 本発明に係る実施の形態4の半導体装置の変形例の部分平面構成を示す図である。

【図28】 本発明に係る実施の形態4の半導体装置の変形例の製造工程を示す図である。

【図29】 本発明に係る実施の形態4の半導体装置の変形例の製造工程を示す図である。

【図30】 従来のDADの平面構成を示す図である。

【図31】 従来のDADの断面構成を示す図である。

【図32】 従来のDADの等価回路を示す図である。

【符号の説明】

9, 9A, 9B, 91C, 92C ソース電極、10A, 10B, 10C 第1ゲート電極、11A, 11B, 11C 第2ゲート電極、12A, 12B, 12C 第1ドレイン電極、13A, 13B, 13C 第2ドレイン電極、20 分離領域、21, 22, 24 トレンチ、MFP1, MFP2, MFPZ マルチフィールドプレート、610~690, 681, 691 トレンチ分離壁、211, 221, 241 内壁酸化膜、212, 222, 242 導電体。 10

【図1】

9: ソース電極

10: 第1ゲート電極

11: 第2ゲート電極

12: 第1ドレイン電極

13: 第2ドレイン電極

20: 分離領域

21: トレンチ

【図2】

MFP2: マルチフィールドプレート

【図3】

211：内壁酸化膜

212：導電体

MFP1：マルチフィールドプレート

【 四 4 】

【図5】

【 6 】

【 四 7 】

( 8 )

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図17】

【図18】

【図19】

【図20】

【図21】

## 【図22】

22 : トレーナー

MFPZ : マルチフィールドプレート

### 【図23】

221：内壁酸化膜

222：導電体

【図24】

【図25】

【図26】

22 : レンチ

【図27】

241 : 内壁酸化膜

242 : 導電体

【図29】

【図28】

【図30】

【図31】

【図32】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/78 6 1 6 T

H 0 1 L 29/78 6 1 7 K

H 0 1 L 27/08 3 3 1 E

(56)参考文献 特開平05-029615 (JP, A)

特開平11-145277 (JP, A)

特開2000-022163 (JP, A)

特開平09-074133 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/76

H01L 21/8238

H01L 27/08

H01L 27/092