## 【特許請求の範囲】

## 【請求項 1】

SiCを適用した電圧駆動型の半導体素子を駆動するゲート駆動回路において、前記ゲート駆動回路が、P型MOSFETおよびN側MOSFETが直列に接続され、且つ前記N側MOSFETが負側電源に直接接続されて構成され、前記P型MOSFETと前記N側MOSFETの中間にある出力段が、前記半導体素子のオフ中に負バイアスとなるように前記P型MOSFETおよび前記N型MOSFETを相補的にオンオフすることを特徴とするゲート駆動回路。

## 【請求項 2】

請求項1に記載のゲート駆動回路において、前記半導体素子のオフ中に出力段を負バイアスに維持する電圧維持手段を有することを特徴とするゲート駆動回路。

## 【請求項 3】

請求項2に記載のゲート駆動回路において、前記電圧維持手段が、前記出力部と前記負側電源の間に前記N型MOSFETと並列に接続されたダイオードを含むことを特徴とするゲート駆動回路。

## 【請求項 4】

請求項3に記載のゲート駆動回路において、前記ダイオードが、ショットキーバリアダイオード、ツェナーダイオード、またはPNダイオードであることを特徴とするゲート駆動回路。

## 【請求項 5】

請求項2に記載のゲート駆動回路において、前記電圧維持手段が、前記出力段とN側MOSFETの中間にあるオフ側ゲート抵抗に並列接続された並列化抵抗と、前記並列化抵抗に直列接続されたスイッチと、前記半導体素子がオフ状態の場合に前記スイッチをオンとする判定部を含むことを特徴とするゲート駆動回路。

## 【請求項 6】

請求項2に記載のゲート駆動回路において、前記電圧維持手段が、前記出力段と前記負側電源の間で前記N側MOSFETと並列に接続されたMOSFETと、前記半導体素子がオフ状態の場合に前記MOSFETを短絡させる判定部を含むことを特徴とするゲート駆動回路。

## 【請求項 7】

請求項1乃至6のいずれかに記載のゲート駆動回路において、前記半導体素子が、ノーマリオフの半導体素子であることを特徴とするゲート駆動回路。

## 【請求項 8】

請求項1乃至7のいずれかに記載のゲート駆動回路において、前記負側電源の電圧生成に、絶縁型電源トランス、または絶縁側DCDCコンバータが用いられるこれを特徴とするゲート駆動回路。

## 【請求項 9】

請求項1乃至8のいずれかに記載のゲート駆動回路を搭載した3相交流インバータ。

## 【請求項 10】

SiCを適用した電圧駆動型の半導体素子のゲート駆動方法において、P側MOSFET、および負極電源に直接接続されたN側MOSFETを相補的にオンオフして、直列に接続されている前記P型MOSFETと前記N側MOSFETの中間にある出力段を、前記半導体素子のオフ中に負バイアスとすることを特徴とするゲート駆動方法。

## 【請求項 11】

請求項10記載のゲート駆動方法において、

電圧維持手段により、前記半導体素子のオフ中に出力段を負バイアスに維持することを

10

20

30

40

50

特徴とするゲート駆動方法。

【請求項 1 2】

請求項 1 1 に記載のゲート駆動方法において、

前記電圧維持手段が、前記出力部と前記負側電源の間に前記 N 型 M O S F E T と並列に接続されたダイオードを含むことを特徴とするゲート駆動方法。

【請求項 1 3】

請求項 1 2 に記載のゲート駆動方法において、

前記ダイオードが、ショットキーバリアダイオード、ツェナーダイオード、または P N ダイオードであることを特徴とするゲート駆動方法。

【請求項 1 4】

請求項 1 1 に記載のゲート駆動方法において、

前記半導体素子がオフ状態の場合に、前記出力段と N 側 M O S F E T の中間にあるオフ側ゲート抵抗に並列接続された並列化抵抗に直列接続されたスイッチをオンとすることを特徴とするゲート駆動方法。

【請求項 1 5】

請求項 1 1 に記載のゲート駆動方法において、

前記半導体素子がオフ状態の場合に、前記出力段と前記負側電源の間で前記 N 側 M O S F E T と並列に接続された M O S F E T を短絡させることを特徴とするゲート駆動方法。

【請求項 1 6】

請求項 1 1 乃至 1 5 のいずれかに記載のゲート駆動方法において、

前記半導体素子が、ノーマリオフの半導体素子であることを特徴とするゲート駆動方法

。

【請求項 1 7】

請求項 1 1 乃至 1 6 のいずれかに記載のゲート駆動方法において、

絶縁型電源トランジスタ、または絶縁側 D C D C コンバータにより、前記負側電源の電圧を生成することを特徴とするゲート駆動方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、 S i C - M O S F E T など、 S i C を適用した電圧駆動型の半導体素子のゲート駆動回路に関する。

【背景技術】

【0 0 0 2】

高速にスイッチングが可能で、かつ大電力を制御できる I G B T ( Insulated Gate Bipolar Transistor : 絶縁ゲートバイポーラトランジスタ ) が、家庭用の小容量インバータから鉄道などで用いられる大容量のインバータまで、幅広く利用されている。 I G B T など電圧駆動型の半導体素子を駆動する回路として、ゲートに印可する電圧を制御することにより半導体素子のオン・オフを制御するゲートドライバなどのゲート駆動回路が使われている。近年では、 S i の I G B T に代わって、低損失な S i C を適用した M O S F E T ( Metal-Oxide-Semiconductor Field Effect Transistor : 金属 - 絶縁体 - 半導体電界効果トランジスタ ) を適用したインバータが普及しつつあり、鉄道用途でも S i C - M O S F E T の駆動に適したゲートドライバが求められている。

【先行技術文献】

【特許文献】

【0 0 0 3】

【特許文献 1】特開 2 0 1 2 - 9 9 6 2 号公報

【特許文献 2】特開 2 0 1 4 - 5 7 4 9 1 号公報

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 4】

10

20

30

40

50

本願発明者が、SiC-MOSFETなど、SiCを適用した電圧駆動型の半導体素子を駆動させるための、ゲート駆動回路を鋭意検討した結果、次の知見を得るに至った。

#### 【0005】

SiC-MOSFETなど、SiCを適用した電圧駆動型の半導体素子の特徴のひとつとして、現状では、ゲートに印加される電界ストレスに対する耐性がSi-IGBTに比較して低いことがわかった。たとえば、SiC-MOSFETにおいても、ゲート酸化膜の材料はSi-IGBTと同じ二酸化シリコン(SiO<sub>2</sub>)であるが、製造プロセスや基板材料由来の欠陥によって、SiC素子ではSi素子と比較してゲート電界ストレスの印加による素子特性の変動が顕著である。したがって、ゲートドライバの出力電圧が半導体素子のゲート-ソース間の定格電圧を超えて出力された場合、ゲートドライバに接続される半導体素子のゲート-ソース間電圧も定格電圧を超えるため、素子特性の変動やゲート酸化膜の信頼性低下などの懸念がある。そこで、ゲートドライバの出力電圧は、半導体素子のゲート-ソース間の定格電圧未満の電圧で安定していることが望ましい。

10

#### 【0006】

SiC-MOSFETの別の特徴として、ゲート-ドレイン間の帰還容量が大きく、スイッチング速度(dV/dt)が大きいことが挙げられる。したがって、MOSFETのゲート-ソース間電圧の変動(持ち上がり)に伴う誤オンが起こりやすいという課題がある。すなわち、MOSFETのドレイン-ソース間に高いdV/dtが印加した際に、帰還容量を介した変異電流(Cgd\*dV/dt)がMOSFET側からゲートドライバ側に向かって流れるため、この電流がゲート配線のインダクタンス成分やゲートドライバ回路内の抵抗成分に流れる効果により、SiC-MOSFETのゲートの電位が持ち上がり易くなる。その結果、SiC-MOSFETのゲート-ソース間電圧が閾値電圧を超えて誤オン状態となった場合、たとえば、アーム短絡等を引き起こす懸念がある。なお、SiC-MOSFETの帰還容量がSi-IGBTに比較して一般的に大きくなる理由は、SiC-MOSFETがユニポーラ素子であり基板のドーピング濃度が高いため、空乏層の幅が広がりにくくことに起因する。

20

#### 【0007】

以上のSiC-MOSFETの2つの特徴のため、それを駆動するゲートドライバとしては、SiC-MOSFETのゲート-ソース間電圧の変動を抑制できるという特性を有することが望ましい。

30

#### 【0008】

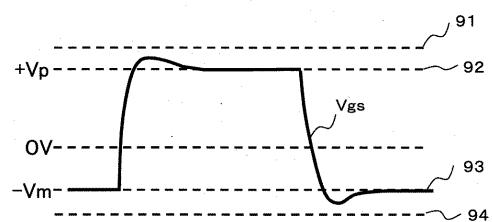

特許文献1に記載されているようなバイポーラトランジスタを用いたプッシュプル回路で出力段が構成されるゲートドライバを用いてSiC-MOSFETをオン・オフ駆動する場合、バイポーラトランジスタの過度インピーダンスが大きいために、ゲートドライバの出力電圧がゲートドライバ回路の電源電圧を超えて変動する結果、SiC-MOSFETのゲート-ソース間電圧も電源電圧を超えることになる。すなわち、図9に示すように、MOSFETのターンオン時にはゲート-ソース間電圧(V<sub>gs</sub>)がゲートドライバ回路の正側電源電圧(+V<sub>p</sub>)を過度的に上回るオーバーシュートが発生し、MOSFETのターンオフ時には負側電源電圧(-V<sub>m</sub>)を過度的に下回るアンダーシュートが発生する。本現象により、MOSFETのゲート-ソース間電圧が定格電圧を超える、もしくは定格電圧までのマージンが減少するため、ゲート酸化膜の信頼性の確保の観点から懸念がある。

40

#### 【0009】

また、SiC-MOSFETのターンオフ時には、ターンオフする側のSiC-MOSFETではドレイン-ソース間に正のdV/dt(>0)が印加し、ターンオフする側と対側のSiC-MOSFETでは、負のdV/dt(<0)が印加する。このとき、対側のSiC-MOSFETのゲート-ソース間電圧(V<sub>gs</sub>)がゲートドライバの負側電源電圧(-V<sub>m</sub>)を下回って沈み込む現象が発生する。

#### 【0010】

特許文献2では、ゲートドライバの負側電源にダイオードを介して出力段のMOSF

50

Tが接続されているが、その構成では、V<sub>gs</sub>が沈み込む時に、ゲートドライバの負側電源とSiC-MOSFETのゲート端子との間に上記ダイオードの容量成分が介在するために、SiC-MOSFETのV<sub>gs</sub>が安定せず、ゲート-ソース間の電圧変動を抑制できない。

#### 【0011】

本発明の目的は、SiCを適用した電圧駆動型の半導体素子をゲート駆動回路においてゲート-ソース間電圧の変動を抑制することに関する。

#### 【課題を解決するための手段】

#### 【0012】

本発明は、ゲート駆動回路が、P型MOSFETおよびN側MOSFETが直列に接続され、且つN側MOSFETが負側電源に直接接続されて構成され、P型MOSFETとN側MOSFETの中間にある出力段が、SiCを適用した電圧駆動型の半導体素子のオフ中に負バイアスとなることに関する。

10

#### 【発明の効果】

#### 【0013】

本発明によれば、過渡インピーダンスの小さいMOSFETで出力段が構成されるため、SiCを適用した電圧駆動型の半導体素子の駆動時のゲート-ソース間電圧の変動を抑制でき、SiCを適用した電圧駆動型の半導体素子のオフ中にゲートを負バイアスするため、誤オンを防止できる。したがって、SiC素子の駆動に適した高信頼性なゲート駆動回路を提供できる。

20

#### 【図面の簡単な説明】

#### 【0014】

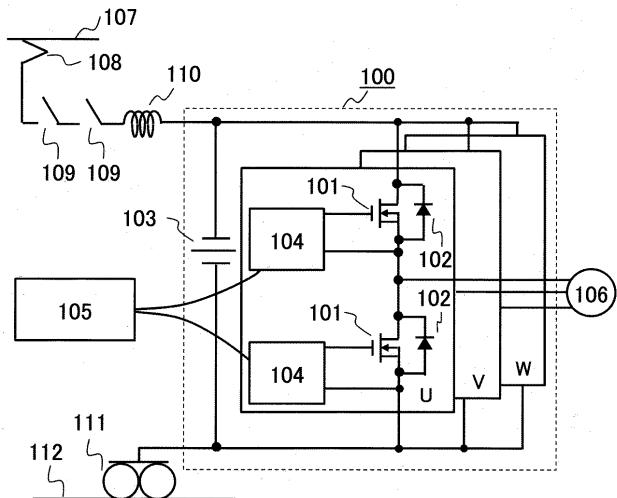

【図1】実施例1にかかる鉄道用インバータシステムの構成図

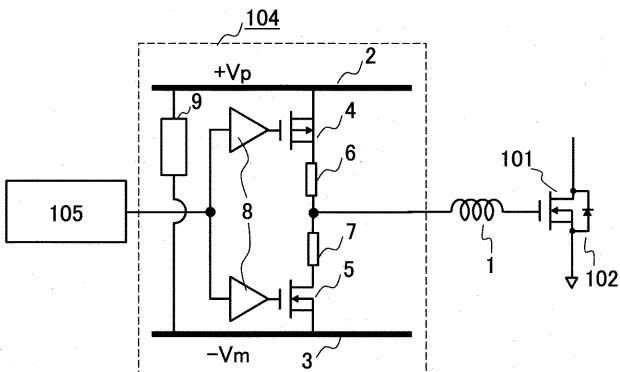

【図2】実施例1にかかるゲートドライバの構成図

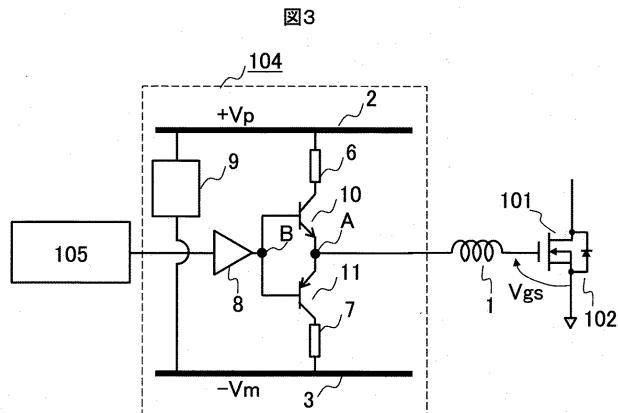

【図3】出力段の素子がバイポーラトランジスタであるゲートドライバの構成図

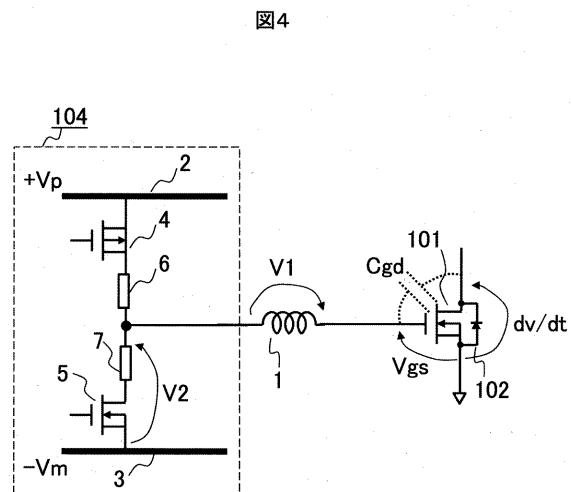

【図4】ゲート-ソース間電圧の持ち上がり現象の説明図

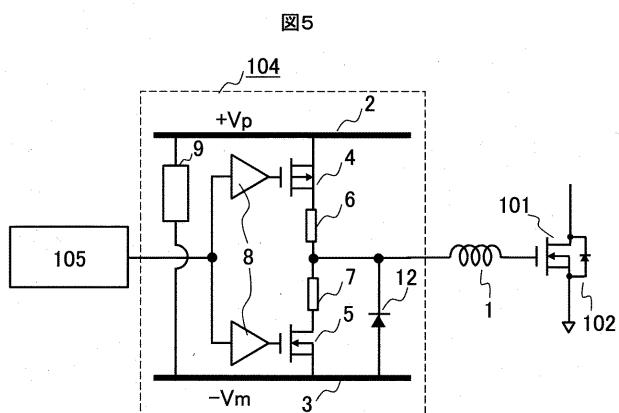

【図5】実施例2にかかるゲートドライバの構成図

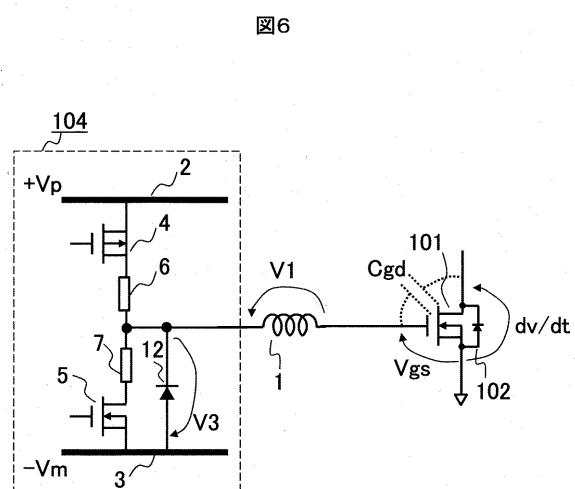

【図6】ゲート-ソース間電圧の沈み込み現象の説明図

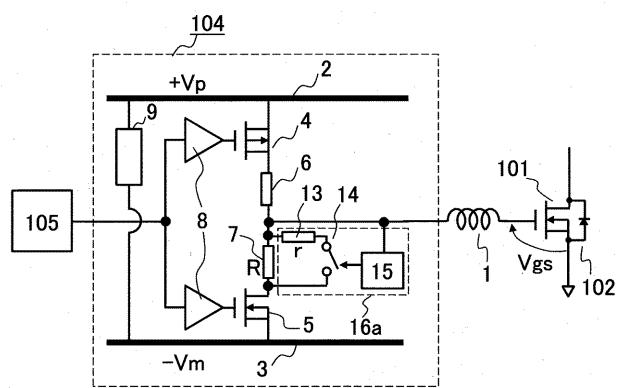

【図7】実施例3にかかるゲートドライバの構成図

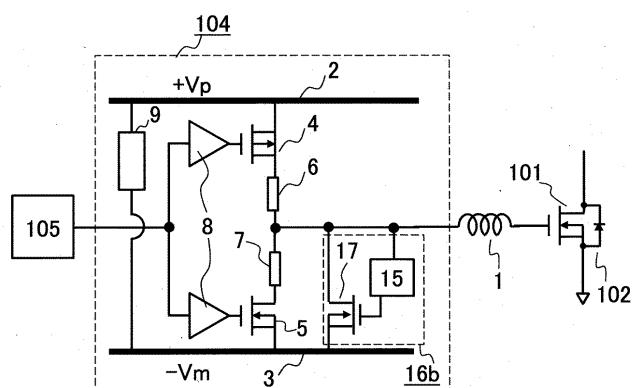

【図8】実施例4にかかるゲートドライバの構成図

30

【図9】ゲートドライバの出力段の素子がバイポーラトランジスタの場合のゲート-ソース間電圧波形の模式図

#### 【発明を実施するための形態】

#### 【0015】

実施例では、SiCを適用した電圧駆動型の半導体素子を駆動するゲート駆動回路において、ゲート駆動回路が、P型MOSFETおよびN側MOSFETが直列に接続され、且つN側MOSFETが負側電源に直接接続されて構成され、P型MOSFETとN側MOSFETの中間にある出力段が、半導体素子のオフ中に負バイアスとなるようにP型MOSFETおよびN型MOSFETを相補的にオンオフするものを開示する。

40

#### 【0016】

また、実施例では、SiCを適用した電圧駆動型の半導体素子のゲート駆動方法において、P側MOSFET、および負極電源に直接接続されたN側MOSFETを相補的にオンオフして、直列に接続されているP型MOSFETとN側MOSFETの中間にある出力段を、半導体素子のオフ中に負バイアスとするものを開示する。

#### 【0017】

また、実施例では、半導体素子のオフ中に出力段を負バイアスに維持する電圧維持手段を有するゲート駆動回路を開示する。また、電圧維持手段により、半導体素子のオフ中に出力段を負バイアスに維持するゲート駆動方法を開示する。また、

また、実施例では、電圧維持手段が、出力部と負側電源の間にN型MOSFETと並列に接続されたダイオードを含むことを開示する。また、ダイオードが、ショットキーバリ

50

アダイオード、ツェナーダイオード、またはPNダイオードであることを開示する。

【0018】

また、実施例では、電圧維持手段が、出力段とN側MOSFETの中間にあるオフ側ゲート抵抗に並列接続された並列化抵抗と、並列化抵抗に直列接続されたスイッチと、半導体素子がオフ状態の場合にスイッチをオンとする判定部を含むゲート駆動回路を開示する。また、半導体素子がオフ状態の場合に、出力段とN側MOSFETの中間にあるオフ側ゲート抵抗に並列接続された並列化抵抗に直列接続されたスイッチをオンとするゲート駆動方法を開示する。

【0019】

また、実施例では、電圧維持手段が、出力段と負側電源の間でN側MOSFETと並列に接続されたMOSFETと、半導体素子がオフ状態の場合にMOSFETを短絡させる判定部を含むゲート駆動回路を開示する。また、半導体素子がオフ状態の場合に、出力段と負側電源の間でN側MOSFETと並列に接続されたMOSFETを短絡させるゲート駆動方法を開示する。

10

【0020】

また、実施例では、電圧駆動型の半導体素子が、ノーマリオフの半導体素子であることを開示する。

【0021】

また、実施例では、負側電源の電圧生成に、絶縁型電源トランス、または絶縁側DCDCコンバータが用いられるゲート駆動回路を開示する。また、絶縁型電源トランス、または絶縁側DCDCコンバータにより、負側電源の電圧を生成するゲート駆動方法を開示する。

20

【0022】

また、実施例では、ゲート駆動回路を搭載した三相交流インバータを開示する。

【0023】

以下、上記およびその他の本発明の新規な特徴と効果について図面を参照して説明する。なお、図面は専ら発明理解のために用いるものであり、権利範囲を減縮するものではない。

【実施例1】

【0024】

30

図1は、本実施例にかかる鉄道用インバータシステムの構成図である。

【0025】

本実施例にかかる鉄道用インバータシステムでは、MOSFET101とフィルタコンデンサ103によりパワーユニット100を構成する。UVW相それぞれにおいて、MOSFET101が直列に接続されており、各MOSFET101には、通流方向が逆方向となるように還流ダイオード102が並列接続されている。また、各MOSFET101には、指令論理部105からの指令に従い、MOSFETを駆動させるゲート駆動回路104が配置されている。UVW相それぞれの上側MOSFET(上アーム)と下側MOSFET(下アーム)の接続点は、パワーユニット100の出力としてモータ106と接続されている。

40

【0026】

架線107からの直流電力は、集電装置108、複数の遮断機109およびフィルタリクトル110を介して、平滑化され、ノイズを除去するためのフィルタコンデンサ103の高圧側に入力される。なお、フィルタコンデンサ103の低圧側は、車輪111を介して、電気的なグラウンドであるレール112に接続されている。そして、鉄道用インバータシステムは、パワーユニット内のUVW相のMOSFETを交互にスイッチングすることにより3相交流を生成してモータ106に送る。MOSFET101やフィルタコンデンサ103とともにパワーユニット100内に配置されているゲート駆動回路104は、指令論理部105からの指令に従い、MOSFET101を駆動する。指令論理部105は、演算装置、メモリおよび入出力手段を備え、所定のプログラムに従ってMOSF

50

Tを駆動する指令を出力する。なお、本実施例にかかるゲート駆動回路では、半導体素子としてMOSFETを駆動する例を説明するが、半導体素子はMOSFETに限らず電圧駆動型の素子であれば良く、例えばIGBTでも良い。

#### 【0027】

図2は、本実施例にかかるゲート駆動回路の構成図である。図2に示すように、ゲート駆動回路104は、正側電源2、負側電源3、P型MOSFET4、N型MOSFET5、オン側ゲート抵抗6、オフ側ゲート抵抗7、駆動制御装置8、電源生成部9から構成され、相補型の対のMOSFETを用いたプッシュプル構成となっている。電源生成部9は、正側電源2および負側電源3に接続される。P型MOSFET4のソースは正側電源2に、ドレインはオン側ゲート抵抗6に接続される。N型MOSFET5のソースは負側電源3に、ドレインはオフ側ゲート抵抗7に接続される。このとき、図2に示すように、N型MOSFET5のソースと負側電源3とが直接接続される構成が好ましい。オン側ゲート抵抗6とオフ側ゲート抵抗7の接続点がゲート駆動回路104の出力部となり、ゲート配線1を介して半導体素子101のゲートに接続される。P型MOSFET4およびN型MOSFET5のゲートは、ともに駆動制御装置8の出力部に接続される。駆動制御装置8の入力部には、指令論理部105が接続される。

#### 【0028】

電源生成部9から、正負の電源電圧がそれぞれ正側電源2および負側電源3に供給される。指令論理部105からゲート駆動指令が駆動制御装置8に入力すると、駆動制御装置8はゲート駆動回路の出力段にあるP型MOSFET4とN型MOSFET5を相補的にオン・オフさせるように制御することにより、ゲート配線1を介して半導体素子101のゲートに電荷を充電または放電する。充電または放電の速度は、それぞれオン側ゲート抵抗6、オフ側ゲート抵抗7で制御できる。

#### 【0029】

図3は、図2に示すゲート駆動回路の出力段の素子をMOSFET(P型MOSFET4およびN型MOSFET5)からバイポーラトランジスタ(NPNトランジスタ10およびPNPトランジスタ11)に置き換えた場合のゲート駆動回路の構成図であり、本実施例に対する比較例である。

#### 【0030】

NPNトランジスタ10のコレクタは、オン側ゲート抵抗6を介して正側電源2に接続される。PNPトランジスタ11のコレクタはオフ側ゲート抵抗7を介して負側電源3に接続される。NPNトランジスタ10とPNPトランジスタ11はそれぞれのエミッタが図3のA点で互いに接続されてゲート駆動回路104の出力部となり、ゲート配線1を介して半導体素子101のゲートに接続される。NPNトランジスタ10とPNPトランジスタ11のベースは、ともに駆動制御装置8の出力部に接続される。その他の接続様態は、図2と同じである。

#### 【0031】

図3に示すように、ゲート駆動回路の出力段の素子がバイポーラトランジスタで構成される場合、駆動制御装置8が、NPNトランジスタ10とPNPトランジスタ11を相補的にオン・オフさせるように制御する際に、NPNトランジスタ10とPNPトランジスタ11が同時にオフになる期間が不可避的に発生する。これは、駆動制御装置8の出力部(図3のB点)の電位が、NPNトランジスタ10とPNPトランジスタ11のベース-エミッタ間電圧がどちらも順バイアスされないような電位となる動作点が必ず発生するためである。このときゲート駆動回路の出力部(図3のA点)から半導体素子101に至る経路には電流が流れにくくなり、過渡的に高インピーダンス状態となる。その結果、ゲート駆動回路104の出力電圧がゲート駆動回路の電圧電源(図3の+Vp、-Vm)を超えて変動し、半導体素子101のゲート電圧も電圧電源を超えて変動する。すなわち、半導体素子101のオン時にはゲート-ソース間電圧(Vgs)がゲート駆動回路の電圧電源を過度的に超えるオーバーシュート(Vgs > +Vp)が発生し、半導体素子101のオフ時にはアンダーシュート(Vgs < -Vm)が発生する(図9参照)。

10

20

30

40

50

## 【0032】

そこで、図2に示すように、ゲート駆動回路の出力段の素子をMOSFETで構成することにより、半導体素子101のゲート-ソース間電圧が電圧電源を超えて変動する現象を抑制できる。これは、バイポーラトランジスタは電流注入制御のため、NPNおよびPNPトランジスタのオン・オフ切り替え時には、ベースに電荷が十分蓄積されるまでに、ある程度の時間を要するのに対し、MOSFETは電圧印加制御のため、オン・オフ切り替えが本質的に早く、上述のような過渡的な高インピーダンス状態にはならずゲートの電位が安定化するためである。

## 【0033】

次に、ゲート電圧の持ち上がり現象について説明する。図4は、ゲート ソース間電圧の持ち上がり現象の説明図である。図4に示すように、対アーム側（図4の半導体素子101が下アームのMOSFETである場合は上アーム側）の半導体素子がターンオンする際、半導体素子101はオフ状態であり、並列接続されている還流ダイオード102がリバースリカバリー動作をする。この時、半導体素子101のドレイン ソース間電圧が増加するため  $dV/dt > 0$  であるから、半導体素子101からゲート駆動回路104に向かって変異電流 ( $Cgd * dV/dt$ ) が流れる。ここで、 $dV/dt$  はドレイン ソース間電圧の時間変化率、 $Cgd$  は半導体素子101のゲート ドレイン間容量（帰還容量）を示す。

10

## 【0034】

この変異電流は、半導体素子101、ゲート配線1、オフ側ゲート抵抗7、N型MOSFET5を経由してゲート駆動回路の負側電源3に流れ込む。このとき、図4に示すように、電流経路上の回路インピーダンスに応じて、半導体素子101のゲート端子とゲート駆動回路の負側電源3との間には電位差が生じる。したがって、この電位差の分だけ、半導体素子101のゲート ソース間電圧 ( $Vgs$ ) はゲート駆動回路の負側電源3の電圧 ( $-Vm$ ) よりも高く持ち上がる。すなわち、（式1）で表されるように  $V1 + V2$  の電位差が生じる。ここで、 $V1$  はゲート配線1の寄生インダクタンスに起因した電位差、 $V2$  はオフ側ゲート抵抗7およびN型MOSFET5の寄生抵抗に起因した電位差である。

20

$$Vgs = -Vm + (V1 + V2) \quad (\text{式1})$$

## 【0035】

30

上述のゲート電圧の持ち上がりにより、半導体素子101の  $Vgs$  がその閾値電圧 ( $Vth$ ) を超えて誤オン状態となるとアーム短絡を起こす懸念がある。

## 【0036】

40

鉄道用途では一般的に半導体素子101としてノーマリオフ型の素子を用いるため、オフ時の  $Vgs$  は  $0V$  でも動作原理上は問題ないが、本実施例では、ゲート駆動回路に負側電源3を設けることにより、オフ時の  $Vgs$  を負（例えば  $Vgs = -10V$ ）としている。これにより、オフ時にゲート電圧に持ち上がりが発生しても  $Vth$  に達するまでの電位差マージンが拡大するため、誤オンを防止できる。仮に半導体素子101がノーマリオン型の素子であっても、ゲート電圧に持ち上がりが発生してもオフ時の  $Vgs$  が  $Vth$  に達しないように負バイアス電圧を設計することにより、誤オンを防止できる。

## 【0037】

40

負電源電圧を生成する方法としては、たとえば、図2の電源生成部9として絶縁型電源トランスを用いる。すなわち、2次側の巻線コイルを2系統設け、一方を正側電源電圧 ( $+Vp$ ) 生成用、他方を負側電源電圧 ( $-Vm$ ) 生成用として各々の巻線比を設計する方法である。あるいは、絶縁型電源トランスの代わりに絶縁型DCDCコンバータを用いて正負両電源を生成しても良い。

## 【実施例2】

## 【0038】

本実施例は、実施例1のゲート駆動回路の構成に対し、半導体素子のゲート端子の電位が沈み込んだ時にゲート電位をゲート駆動回路の負側電源に接続する手段を有する点が異

50

なる。以下、実施例 1 との相違点を中心に説明する。

【0039】

図 5 は、本実施例にかかるゲート駆動回路の構成図を示す。ゲート駆動回路 104 の出力部、すなわちオン側ゲート抵抗 6 とオフ側ゲート抵抗 7 の接続点にダイオード 12 のカソードが接続されている。ダイオード 12 のアノードは、ゲート駆動回路の負側電源 3 に接続されている。その他の接続様態は、実施例 1 と同じである。

【0040】

ダイオード 12 を設けることにより、半導体素子 101 のゲート端子の電位が沈み込んだ時にゲート駆動回路 104 の出力部がゲート駆動回路の負側電源 3 に低インピーダンスで接続されるため、ゲート電圧の変動（沈み込み）を抑制できる。

10

【0041】

図 6 は、ゲート電圧の沈み込み現象の説明図である。図 6 に示すように、対アーム側の半導体素子がターンオフする際、半導体素子 101 はオフ状態であり、並列接続されている還流ダイオード 102 がフォワードリカバリー動作をする。この時、半導体素子 101 のドレイン ソース間電圧が減少するため、 $dV/dt < 0$  であるから、ゲート駆動回路 104 から半導体素子 101 に向かって変異電流 ( $Cgd * dV/dt$ ) が流れる。

【0042】

この変異電流は、ゲート駆動回路の負側電源 3 、ダイオード 12 、ゲート配線 1 を経由して半導体素子 101 に流れ込む。このとき、図 6 に示すように、電流経路上の回路インピーダンスに応じて半導体素子 101 のゲート端子とゲート駆動回路の負側電源 3 との間に電位差が生じ、半導体素子 101 の  $V_{gs}$  はゲート駆動回路の負側電源 3 の電圧 ( $-V_m$ ) よりも低く沈み込む。すなわち、(式 2) で表されるように  $V_1 + V_3$  の電位差が生じる。ここで、 $V_3$  はダイオード 12 の導通に起因した電位差であり、ダイオード 12 の順方向電圧に等しい。

20

$$V_{gs} = -V_m - (V_1 + V_3) \quad (式 2)$$

【0043】

ゲート電圧の沈み込み現象により、半導体素子 101 の  $V_{gs}$  がその定格電圧の下限値（たとえば -20V）を下回るとゲート酸化膜の信頼性低下が懸念されるが、本実施例では、沈み込み時に電流がダイオード 12 を経由することにより、ゲート駆動回路の負側電源 3 からの電圧降下 ( $V_1 + V_3$ ) を抑制でき、ゲート酸化膜の信頼性を確保できる。したがって、ダイオード 12 の候補としては、順方向電圧 ( $V_3$ ) の小さいショットキーバリアダイオードなど望ましいが、ツェナーダイオードや PN ダイオードでも良い。

30

【0044】

また、(式 1) (式 2) より、ゲート電圧の変動量（持ち上がり、沈み込み）を抑制するためには、ゲート配線 1 で発生する電位差 ( $V_1$ ) を低減することも有効であり、ゲート配線 1 の寄生インダクタンス ( $L_g$ ) を低減することが望ましい。 $L_g$  を低減する手法としては、ゲート配線長を最小化する手法や、ゲート電流による磁場が効果的に打ち消しあうようにラミネートブスバー構造等を適用する手法がある。

40

【実施例 3】

【0045】

図 7 は、本実施例にかかるゲート駆動回路の構成図を示す。ゲート電位をゲート駆動回路の負側電源に接続する手段として、実施例 2 では、ダイオード 12 を用いたが、本実施例では、低インピーダンス化回路 16a を用いている点が異なる。以下、実施例 1 乃至 2 との相違点を中心に説明する。

【0046】

低インピーダンス化回路 16a は、並列化抵抗 13 、アナログスイッチ 14 、およびゲートオフ判定部 15 から構成される。並列化抵抗 13 は、アナログスイッチ 14 を介してオフ側ゲート抵抗 7 に並列に接続される。ゲートオフ判定部 15 は、ゲート駆動回路 104 の出力部とアナログスイッチ 14 の間に接続される。

50

## 【0047】

ゲートオフ判定部15は、半導体素子101のゲートソース間電圧( $V_{gs}$ )をモニタしており、半導体素子101がオフ状態であることを $V_{gs}$ の値から判定する。ゲートオフ判定部15は、半導体素子101がオフ状態であることを判定すると、アナログスイッチ14が閉じられ、オフ側ゲート抵抗7(抵抗値 $R$ )と並列化抵抗13(抵抗値 $r$ )が並列接続される。並列接続時の抵抗は、 $R$ から $R / (1 + R / r) (< R)$ に減少する。したがって、半導体素子101のオフ中に、ゲートの電位が沈み込んだ時にゲート駆動回路104の出力部がゲート駆動回路の負側電源3に低インピーダンスで接続されるため、ゲート電圧の変動(沈み込み)を抑制できる。

## 【0048】

10

実施例2では、ダイオード12の整流作用から、ゲートが沈み込むときのみ変動抑制効果があるのに対し、本実施例では、低インピーダンス化回路16aの双方向性から、ゲートの沈み込みと持ち上がりの両方に変動抑制効果がある点で優位である。ゲート電圧の持ち上がり量の抑制により、半導体素子101のオフ時において、半導体素子101のゲート-ソース間電圧が閾値電圧( $V_{th}$ )まで持ち上がるまでの電位差マージンが大きくなるため、誤オンを防止できる。

## 【実施例4】

## 【0049】

20

図8は、本実施例にかかるゲート駆動回路の構成図を示す。本実施例では、低インピーダンス化回路として、アナログスイッチでなく、MOSFETを用いている点が異なる。以下、実施例1乃至3との相違点を中心に説明する。

## 【0050】

低インピーダンス化回路16bは、電圧クランプ用MOSFET17、およびゲートオフ判定部15から構成される。電圧クランプ用MOS17は、ゲート駆動回路104の出力部とゲート駆動回路の負側電源3の間に接続される。ゲートオフ判定部15は、ゲート駆動回路104の出力部と電圧クランプ用MOS17のゲート端子との間に接続される。

## 【0051】

30

ゲートオフ判定部15は、半導体素子101がオフ状態であることを判定すると、電圧クランプ用MOS17をオンさせ、ゲート駆動回路104の出力部とゲート駆動回路の負側電源3とを短絡させる。したがって、半導体素子101のオフ中にゲートの電位が沈み込んだ時に、ゲート駆動回路104の出力部がゲート駆動回路の負側電源3に極めて低インピーダンスで接続されるため、ゲート電圧の変動(沈み込み)を効果的に抑制できる。

## 【0052】

本実施例では、ゲート駆動回路104の出力部とゲート駆動回路の負側電源3の間に介在するインピーダンス成分が、電圧クランプ用MOSFET17のオン抵抗のみとなって小さくなるため(たとえば数十mΩ)、実施例3に比べて、より効果的にゲートの変動(沈み込み、持ち上がり)を抑制できる利点がある。

## 【符号の説明】

## 【0053】

40

- 1 : ゲート配線

- 2 : ゲート駆動回路の正側電源

- 3 : ゲート駆動回路の負側電源

- 4 : P型MOSFET

- 5 : N型MOSFET

- 6 : オン側ゲート抵抗

- 7 : オフ側ゲート抵抗

- 8 : 駆動制御装置

- 9 : 電源生成部

- 10 : NPNトランジスタ

- 11 : PNPトランジスタ

50

- 1 2 : ダイオード

1 3 : 並列化抵抗

1 4 : アナログスイッチ

1 5 : ゲートオフ判定部

1 6 a : 低インピーダンス化回路

1 6 b : 低インピーダンス化回路

1 7 : 電圧クランプ用 M O S F E T

9 1 : 定格電圧 ( 上限値 )

9 2 : 正側電圧電源

9 3 : 負側電圧電源

9 4 : 定格電圧 ( 下限値 )

1 0 0 : パワーユニット

1 0 1 : 電圧駆動型の半導体素子 ( IGBT、MOSFETなど )

1 0 2 : 還流ダイオード

1 0 3 : フィルタコンデンサ

1 0 4 : ゲート駆動回路

1 0 5 : 指令論理部

1 0 6 : モータ

1 0 7 : 架線

1 0 8 : 集電装置

1 0 9 : 遮断機

1 1 0 : フィルタリアクトル

1 1 1 : 車輪

1 1 2 : レール

【図1】

図 1

【 図 2 】

図2

【 図 3 】

【 図 4 】

【図5】

【 四 6 】

【 図 7 】

【 図 8 】

図7

図8

【 図 9 】

図9

---

フロントページの続き

F ターム(参考) 5J055 AX33 AX34 BX16 CX07 CX20 DX13 DX22 DX59 EX07 EX20

EY01 EY05 EY07 EY10 EY12 EY13 EY17 EY21 EY29 EZ14

EZ53 EZ63 GX01 GX02 GX04