(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0060997

(43) 공개일자 2016년05월31일

(51) 국제특허분류(Int. Cl.)

*H01L 27/146* (2006.01)

(21) 출원번호 10-2014-0163321

(22) 출원일자 2014년11월21일

심사청구일자 없음

(71) 출원인

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

오동연

서울특별시 광진구 광나루로 56길 29, 11동 101호

(현대프라임)

(74) 대리인

특허법인신성

전체 청구항 수 : 총 27 항

(54) 발명의 명칭 수직 전송 게이트를 갖는 이미지 센서 및 이를 구비한 전자장치

### (57) 요 약

본 기술은 수직 전송 게이트를 갖는 이미지 센서 및 이를 구비한 전자장치를 제공하기 위한 것으로, 광전변환소자; 상기 광전변환소자 상에 형성된 전송 게이트; 상기 전송 게이트를 관통하여 상기 광전변환소자에 전기적으로 연결된 복수의 활성필라; 상기 복수의 활성필라에 연결된 리셋 트랜지스터; 및 상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터를 포함할 수 있다.

대 표 도 - 도3a

## 명세서

### 청구범위

#### 청구항 1

광전변환소자;

상기 광전변환소자 상에 형성된 전송 게이트;

상기 전송 게이트를 관통하여 상기 광전변환소자에 전기적으로 연결된 복수의 활성필라;

상기 복수의 활성필라에 연결된 리셋 트랜지스터; 및

상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터

를 포함하는 이미지 센서.

#### 청구항 2

제1항에 있어서,

상기 광전변환소자로 입사광이 유입되는 입사면 상에 형성된 컬러필터층; 및

상기 컬러필터층 상의 마이크로렌즈

를 더 포함하는 이미지 센서.

#### 청구항 3

제1항에 있어서,

상기 전송 게이트는,

상기 광전변환소자 상에 형성된 게이트전극; 및

상기 게이트전극과 상기 복수의 활성필라 및 상기 광전변환소자 사이에 게재된 전하차단막

을 포함하는 이미지 센서.

#### 청구항 4

제3항에 있어서,

상기 게이트전극은 상기 복수의 활성필라 측벽 모두를 둘러싸는 이미지 센서.

#### 청구항 5

제3항에 있어서,

상기 게이트전극은,

상기 소스팔로워 트랜지스터의 게이트가 연결된 복수의 활성필라 중 어느 하나 이상의 활성필라 측벽 모두를 둘러싸는 제1게이트전극; 및

상기 복수의 활성필라 중 어느 하나 이상의 활성필라를 제외한 나머지 활성필라 측벽 모두를 둘러싸는 제2게이트전극

을 포함하는 이미지 센서.

#### 청구항 6

제1항에 있어서,

상기 전송 게이트는 상기 광전변환소자에 입사광이 유입되는 입사면의 대향면 상에 형성되는 이미지 센서.

#### 청구항 7

제1항에 있어서,

상기 리셋 트랜지스터는,

상기 소스팔로워 트랜지스터의 게이트가 연결된 복수의 활성필라 중 어느 하나 이상의 활성필라에 전기적으로 연결된 제1리셋 트랜지스터; 및

상기 복수의 활성필라 중 어느 하나 이상의 활성필라를 제외한 나머지 활성필라에 전기적으로 연결된 제2리셋 트랜지스터

를 포함하는 이미지 센서.

#### 청구항 8

제1항에 있어서,

상기 복수의 활성필라 각각은 평형상태에서 완전공핍이 가능한 선폭을 갖는 이미지 센서.

#### 청구항 9

제1항에 있어서,

상기 복수의 활성필라 각각은,

상기 광전변환소자에 연결되고, 상기 전송 게이트가 둘러싸는 채널영역; 및

상기 채널영역과 연결되고, 상기 전송 게이트 위로 돌출된 플로팅디퓨전영역

을 포함하는 이미지 센서.

#### 청구항 10

제9항에 있어서,

상기 채널영역은 불순물이 도핑되지 않은 언도프드 상태인 이미지 센서.

#### 청구항 11

제9항에 있어서,

상기 채널영역은 불순물이 도핑된 도프드 상태를 갖되, 상기 플로팅디퓨전영역과 동일한 도전형을 갖고, 상기 채널영역의 불순물 도핑농도가 상기 플로팅디퓨전영역의 불순물 도핑농도보다 작은 이미지 센서.

### 청구항 12

제1항에 있어서,

상기 광전변환소자는 수직적으로 중첩되고 서로 다른 도전형을 갖는 제1불순물영역 및 제2불순물영역을 포함하고, 상기 제1불순물영역 상기 복수의 활성필라와 전기적으로 연결된 이미지 센서.

### 청구항 13

광전변환소자;

상기 광전변환소자 상에 형성되어 상기 광전변환소자와 전기적으로 연결된 복수의 활성필라;

상기 광전변환소자 상에 형성되어 상기 복수의 활성필라를 둘러싸는 전송 게이트;

상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 전기적으로 연결된 제1리셋 트랜지스터; 및

상기 복수의 활성필라 중 상기 어느 하나 이상의 활성필라를 제외한 나머지 활성필라에 전기적으로 연결된 제2리셋 트랜지스터

를 포함하는 이미지 센서.

### 청구항 14

제13항에 있어서,

상기 제1리셋 트랜지스터가 전기적으로 연결된 상기 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터를 더 포함하는 이미지 센서.

### 청구항 15

제13항에 있어서,

상기 전송 게이트는,

상기 광전변환소자 상에 형성된 게이트전극; 및

상기 게이트전극과 상기 복수의 활성필라 및 상기 광전변환소자 사이에 게재된 전하차단막

을 포함하는 이미지 센서.

### 청구항 16

제15항에 있어서,

상기 게이트전극은 상기 복수의 활성필라 측벽을 모두 둘러싸는 이미지 센서.

### 청구항 17

제15항에 있어서,

상기 게이트전극은,

상기 복수의 활성필라 중 상기 제1리셋 트랜지스터에 전기적으로 연결되는 상기 어느 하나 이상의 활성필라 모두의 측벽을 둘러싸는 제1게이트전극; 및

상기 복수의 활성필라 중 상기 제2리셋 트랜지스터에 전기적으로 연결되는 상기 나머지 활성필라 측벽을 모두 둘러싸는 제2게이트전극

을 포함하는 이미지 센서.

### 청구항 18

제13항에 있어서,

상기 전송 게이트는 상기 광전변환소자에 입사광이 유입되는 입사면의 대향면 상에 형성되는 이미지 센서.

### 청구항 19

제13항에 있어서,

상기 복수의 활성필라 각각은 평형상태에서 완전공핍이 가능한 선폭을 갖는 이미지 센서.

### 청구항 20

제13항에 있어서,

상기 복수의 활성필라 각각은,

상기 광전변환소자에 연결되고, 상기 전송 게이트가 둘러싸는 채널영역; 및

상기 채널영역과 연결되고, 상기 전송 게이트 위로 돌출된 플로팅디퓨전영역

을 포함하는 이미지 센서.

### 청구항 21

제20항에 있어서,

상기 채널영역은 불순물이 도핑되지 않은 언도프드 상태인 이미지 센서.

### 청구항 22

제20항에 있어서,

상기 채널영역은 불순물이 도핑된 도프드 상태를 갖되, 상기 플로팅디퓨전영역과 동일한 도전형을 갖고, 상기 채널영역의 불순물 도핑농도가 상기 플로팅디퓨전영역의 불순물 도핑농도보다 작은 이미지 센서.

### 청구항 23

제13항에 있어서,

상기 광전변환소자는 수직적으로 중첩되고 서로 다른 도전형을 갖는 제1불순물영역 및 제2불순물영역을 포함하고, 상기 제1불순물영역 상기 복수의 활성필라와 전기적으로 연결된 이미지 센서.

### 청구항 24

광전변환소자;

상기 광전변환소자를 공유하고, 하나 이상의 전송 트랜지스터가 병렬로 연결된 제1전송부 및 제2전송부;

상기 제1전송부에 연결된 제1리셋 트랜지스터;

상기 제1전송부와 상기 제1리셋 트랜지스터 사이 플로팅디퓨전노드에 게이트가 연결된 소스팔로워 트랜지스터;

및

상기 제2전송부에 연결된 제2리셋 트랜지스터

를 포함하는 이미지 센서.

### 청구항 25

제24항에 있어서,

상기 제1전송부 및 상기 제2전송부는 하나의 동일에 전송신호에 응답하거나, 또는 각각 서로 다른 전송신호에 응답하는 이미지 센서.

### 청구항 26

제24항에 있어서,

상기 제1리셋 트랜지스터 및 상기 제2리셋 트랜지스터는 하나의 동일한 리셋신호에 응답하는 이미지 센서.

### 청구항 27

광학렌즈;

복수의 단위픽셀들이 2차원 배열된 이미지 센서; 및

상기 이미지 센서로부터 출력되는 출력신호를 처리하는 신호처리회로를 포함하고,

상기 복수의 단위픽셀 각각은,

광전변환소자;

상기 광전변환소자 상에 형성된 전송 게이트;

상기 전송 게이트를 관통하여 상기 광전변환소자에 전기적으로 연결된 복수의 활성필라;

상기 복수의 활성필라에 연결된 리셋 트랜지스터; 및

상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터

를 포함하는 전자장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 반도체 장치 제조 기술에 관한 것으로, 보다 구체적으로는 수직 전송 게이트를 구비한 이미지 센서 및 이를 구비한 전자장치에 관한 것이다.

## 배경 기술

[0002] 이미지 센서(image sensor)는 광학 영상을 전기 신호로 변환시키는 소자이다. 최근 들어, 컴퓨터 산업과 통신 산업의 발달에 따라 디지털 카메라, 캠코더, PCS(Personal Communication System), 게임 기기, 경비용 카메라, 의료용 마이크로 카메라, 로보트 등 다양한 분야에서 성능이 향상된 이미지 센서의 수요가 증대되고 있다.

## 발명의 내용

## 해결하려는 과제

[0003]

본 발명의 실시예들은 성능이 향상된 이미지 센서 및 이를 구비한 전자장치를 제공한다.

## 과제의 해결 수단

[0004]

본 발명의 실시예에 따른 이미지 센서는 광전변환소자; 상기 광전변환소자 상에 형성된 전송 게이트; 상기 전송 게이트를 관통하여 상기 광전변환소자에 전기적으로 연결된 복수의 활성필라; 상기 복수의 활성필라에 연결된 리셋 트랜지스터; 및 상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스 팔로워 트랜지스터를 포함할 수 있다. 또한, 상기 광전변환소자로 입사광이 유입되는 입사면 상에 형성된 컬러 필터층; 및 상기 컬러필터층 상의 마이크로렌즈를 더 포함할 수 있다.

[0005]

상기 전송 게이트는, 상기 광전변환소자 상에 형성된 게이트전극; 및 상기 게이트전극과 상기 복수의 활성필라 및 상기 광전변환소자 사이에 게재된 전하차단막을 포함할 수 있다. 상기 게이트전극은 상기 복수의 활성필라 측벽 모두를 둘러싸는 형태를 가질 수 있다. 또한, 상기 게이트전극은, 상기 소스팔로워 트랜지스터의 게이트가 연결된 복수의 활성필라 중 어느 하나 이상의 활성필라 측벽 모두를 둘러싸는 제1게이트전극; 및 상기 복수의 활성필라 중 어느 하나 이상의 활성필라를 제외한 나머지 활성필라 측벽 모두를 둘러싸는 제2게이트전극을 포함할 수 있다. 상기 전송 게이트는 상기 광전변환소자에 입사광이 유입되는 입사면의 대향면 상에 형성될 수 있다.

[0006]

상기 리셋 트랜지스터는, 상기 소스팔로워 트랜지스터의 게이트가 연결된 복수의 활성필라 중 어느 하나 이상의 활성필라에 전기적으로 연결된 제1리셋 트랜지스터; 및 상기 복수의 활성필라 중 어느 하나 이상의 활성필라를 제외한 나머지 활성필라에 전기적으로 연결된 제2리셋 트랜지스터를 포함할 수 있다.

[0007]

상기 복수의 활성필라 각각은 평형상태에서 완전공핍이 가능한 전폭을 가질 수 있다. 상기 복수의 활성필라 각각은, 상기 광전변환소자에 연결되고, 상기 전송 게이트가 둘러싸는 채널영역; 및 상기 채널영역과 연결되고, 상기 전송 게이트 위로 돌출된 플로팅디퓨전영역을 포함할 수 있다. 상기 채널영역은 불순물이 도핑되지 않은 언도프드 상태일 수 있다. 또한, 상기 채널영역은 불순물이 도핑된 도프드 상태를 갖되, 상기 플로팅디퓨전영역과 동일한 도전형을 갖고, 상기 채널영역의 불순물 도핑농도가 상기 플로팅디퓨전영역의 불순물 도핑농도보다 작을 수 있다.

[0008]

상기 광전변환소자는 수직적으로 중첩되고 서로 다른 도전형을 갖는 제1불순물영역 및 제2불순물영역을 포함하고, 상기 제1불순물영역 상기 복수의 활성필라와 전기적으로 연결될 수 있다.

[0009]

또한, 본 발명의 실시예에 따른 이미지 센서는 광전변환소자; 상기 광전변환소자 상에 형성되어 상기 광전변환소자와 전기적으로 연결된 복수의 활성필라; 상기 광전변환소자 상에 형성되어 상기 복수의 활성필라를 둘러싸는 전송 게이트; 상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 전기적으로 연결된 제1리셋 트랜지스터; 및 상기 복수의 활성필라 중 상기 어느 하나 이상의 활성필라를 제외한 나머지 활성필라에 전기적으로 연결된 제2리셋 트랜지스터를 포함할 수 있다. 또한, 상기 제1리셋 트랜지스터가 전기적으로 연결된 상기 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터를 더 포함할 수 있다.

[0010]

상기 전송 게이트는, 상기 광전변환소자 상에 형성된 게이트전극; 및 상기 게이트전극과 상기 복수의 활성필라 및 상기 광전변환소자 사이에 게재된 전하차단막을 포함할 수 있다. 상기 게이트전극은 상기 복수의 활성필라 측벽을 모두 둘러싸는 형태를 가질 수 있다. 또한, 상기 게이트전극은, 상기 복수의 활성필라 중 상기 제1리셋 트랜지스터에 전기적으로 연결되는 상기 어느 하나 이상의 활성필라 모두의 측벽을 둘러싸는 제1게이트전극; 및 상기 복수의 활성필라 중 상기 제2리셋 트랜지스터에 전기적으로 연결되는 상기 나머지 활성필라 측벽을 모두 둘러싸는 제2게이트전극을 포함할 수 있다. 상기 전송 게이트는 상기 광전변환소자에 입사광이 유입되는 입사면의 대향면 상에 형성될 수 있다.

[0011]

상기 복수의 활성필라 각각은 평형상태에서 완전공핍이 가능한 전폭을 가질 수 있다. 상기 복수의 활성필라 각각은, 상기 광전변환소자에 연결되고, 상기 전송 게이트가 둘러싸는 채널영역; 및 상기 채널영역과 연결되고, 상기 전송 게이트 위로 돌출된 플로팅디퓨전영역을 포함할 수 있다. 상기 채널영역은 불순물이 도핑되지 않은 언도프드 상태일 수 있다. 상기 채널영역은 불순물이 도핑된 도프드 상태를 갖되, 상기 플로팅디퓨전영역과 동일한 도전형을 갖고, 상기 채널영역의 불순물 도핑농도가 상기 플로팅디퓨전영역의 불순물 도핑농도보다 작을

수 있다.

[0012] 상기 광전변환소자는 수직적으로 중첩되고 서로 다른 도전형을 갖는 제1불순물영역 및 제2불순물영역을 포함하고, 상기 제1불순물영역 상기 복수의 활성필라와 전기적으로 연결될 수 있다.

[0013] 또한, 본 발명의 실시예에 따른 이미지 센서는 광전변환소자; 상기 광전변환소자를 공유하고, 하나 이상의 전송 트랜지스터가 별별로 연결된 제1전송부 및 제2전송부; 상기 제1전송부에 연결된 제1리셋 트랜지스터; 상기 제1 전송부와 상기 제1리셋 트랜지스터 사이 플로팅디퓨전노드에 게이트가 연결된 소스팔로워 트랜지스터; 및 상기 제2전송부에 연결된 제2리셋 트랜지스터를 포함할 수 있다.

[0014] 상기 제1전송부 및 상기 제2전송부는 하나의 동일에 전송신호에 응답하거나, 또는 각각 서로 다른 전송신호에 응답할 수 있다. 상기 제1리셋 트랜지스터 및 상기 제2리셋 트랜지스터는 하나의 동일한 리셋신호에 응답할 수 있다.

[0015] 본 발명의 실시예에 따른 전자장치는, 광학렌즈; 복수의 단위픽셀들이 2차원 배열된 이미지 센서; 및 상기 이미지 센서로부터 출력되는 출력신호를 처리하는 신호처리회로를 포함하고, 상기 복수의 단위픽셀 각각은, 광전변환소자; 상기 광전변환소자 상에 형성된 전송 게이트; 상기 전송 게이트를 관통하여 상기 광전변환소자에 전기적으로 연결된 복수의 활성필라; 상기 복수의 활성필라에 연결된 리셋 트랜지스터; 및 상기 복수의 활성필라 중 어느 하나 이상의 활성필라에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터를 포함할 수 있다.

### 발명의 효과

[0016] 상술한 과제의 해결 수단을 바탕으로 하는 본 기술은 제1전송부 및 제2전송부 각각이 별별로 연결된 하나 이상의 전송 트랜지스터로 구성됨에 따라 광전변환소자에서 생성된 광전하에 대한 전달효율을 향상시킬 수 있다.

[0017] 또한, 제1전송부에 연결된 플로팅디퓨전노드에 소스팔로워 트랜지스터가 연결됨에 따라 요구되는 이미지 센서의 감도 및 신호대잡음비 특성을 용이하게 향상시킬 수 있다.

[0018] 또한, 복수의 활성필라 각각의 채널영역 도핑상태 및 선폭을 통해 전송 트랜지스터 턴 오프 상태에서의 누설전류 발생을 방지함으로써, 이미지 센서의 신호대잡음비 특성을 향상시킬 수 있다.

### 도면의 간단한 설명

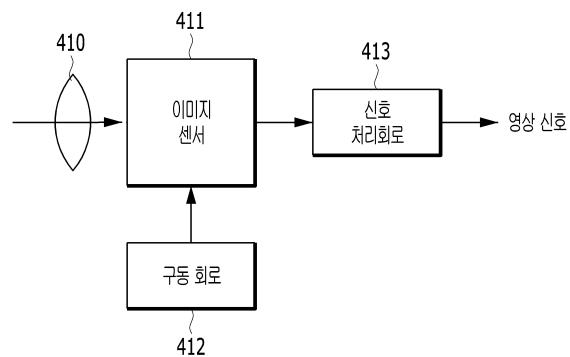

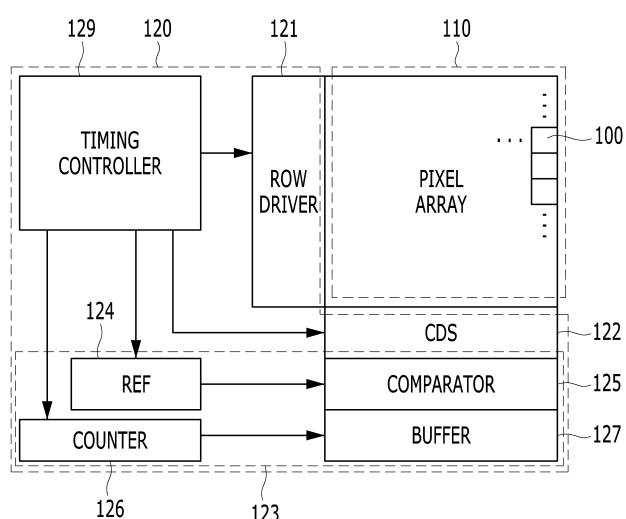

[0019] 도 1은 본 발명의 제1실시예 및 제2실시예에 따른 단위픽셀을 포함하는 이미지 센서를 간략히 도시한 블력도

도 2는 제1실시예에 따른 이미지 센서 단위픽셀을 도시한 등가회로도.

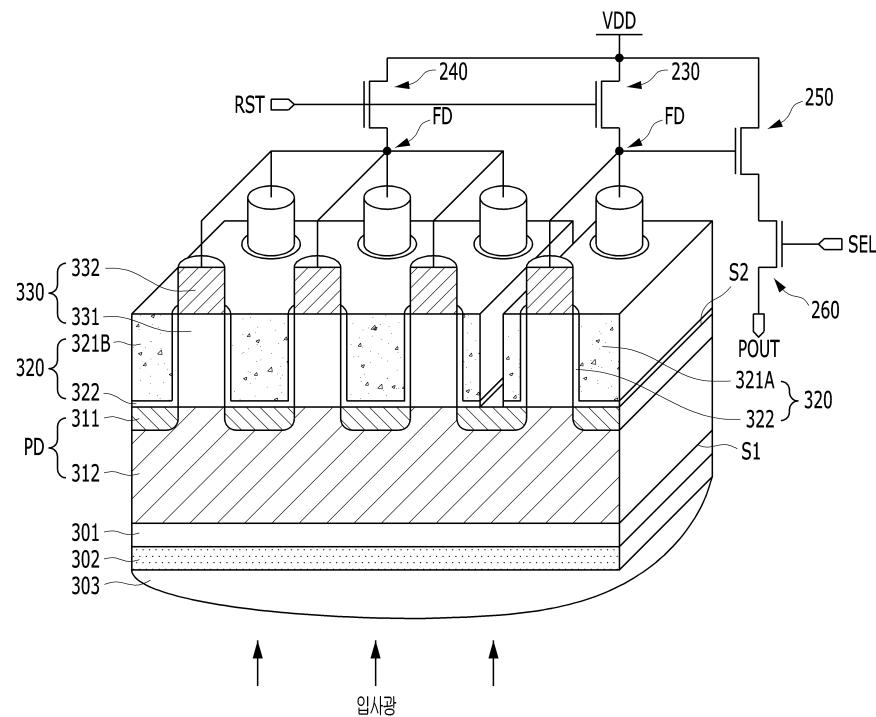

도 3a 및 도 3b는 제1실시예 및 제1실시예의 변형예에 따른 이미지 센서의 단위픽셀을 도시한 도면.

도 4는 제1실시예에 따른 이미지 센서의 단위픽셀에서 복수의 활성필라 형상에 대한 변형예들을 도시한 평면도.

도 5는 제2실시예에 따른 이미지 센서 단위픽셀을 도시한 등가회로도.

도 6은 제2실시예에 따른 이미지 센서의 단위픽셀을 도시한 도면.

도 7은 실시예에 따른 전자장치의 구성을 간략히 도시한 도면.

### 발명을 실시하기 위한 구체적인 내용

[0020] 이하 본 발명이 속하는 기술분야에서 통상의 지식을 가진자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 가장 바람직한 실시예를 도면을 참조하여 설명하기로 한다. 도면은 반드시 일정한 비율로 도시된 것이라 할 수 없으며, 몇몇 예시들에서, 실시예들의 특징을 명확히 보여주기 위하여 도면에 도시된 구조물 중 적어도 일부의 비례는 과장될 수도 있다. 도면 또는 상세한 설명에 둘 이상의

층을 갖는 다층 구조물이 개시된 경우, 도시된 것과 같은 층들의 상대적인 위치 관계나 배열 순서는 특정 실시 예를 반영할 뿐이어서 본 발명이 이에 한정되는 것은 아니며, 층들의 상대적인 위치 관계나 배열 순서는 달라질 수도 있다. 또한, 다층 구조물의 도면 또는 상세한 설명은 특정 다층 구조물에 존재하는 모든 층들을 반영하지 않을 수도 있다(예를 들어, 도시된 두 개의 층 사이에 하나 이상의 추가 층이 존재할 수도 있다). 예컨대, 도면 또는 상세한 설명의 다층 구조물에서 제1 층이 제2 층 상에 있거나 또는 기판상에 있는 경우, 제1 층이 제2 층 상에 직접 형성되거나 또는 기판상에 직접 형성될 수 있음을 나타낼 뿐만 아니라, 하나 이상의 다른 층이 제1 층과 제2 층 사이 또는 제1 층과 기판 사이에 존재하는 경우도 나타낼 수 있다.

[0021] 이미지 센서는 광학 영상을 전기 신호로 변환시키는 장치로서, CCD(Charge Coupled Device)와 CIS(CMOS Image Sensor)로 구분할 수 있다. 특히, CIS는 구동 방식이 간단하고, CMOS 공정 기술을 호환하여 사용할 수 있어 제조 단가를 낮출 수 있는 장점이 있다. 따라서, 후술하는 본 발명의 실시예들은 CIS를 예시하여 설명하기로 한다. CIS 이미지 센서는 전송 트랜지스터(transfer transistor)를 통해 광전변환소자(photoelectric conversion element)에서 생성된 광전하를 플로팅디퓨전(floating diffusion)으로 전달한다. 여기서, 전송 트랜지스터는 전송 게이트의 게이트제어력(gate controllability) 또는 온/오프 특성을 향상시키기 위해 채널영역에 소정의 불순물이 도핑된다. 일반적으로, 전송 트랜지스터로는 NMOS가 주로 사용됨에 따라 전송 트랜지스터의 채널영역에는 P형 불순물이 도핑된다.

[0022] 한편, 전송 트랜지스터의 게이트제어력 또는 온/오프 특성을 더욱더 향상시키기 위해 최근 수직 전송 게이트가 제안되었다. 수직 전송 게이트를 구현하기 위해서는 채널영역 또한 수직 구조물 형태를 가질 수 밖에 없다. 따라서, 단위픽셀의 크기가 감소할수록 채널영역에 불순물을 도핑하기 위한 도핑공정의 난이도가 급격히 증가하여 생산성이 저하되고, 도핑된 불순물의 RDF(Random Dopant Fluctuation) 현상이 심화되어 신호대잡음비(Signal to Noise Ratio, SNR)가 증가하는 단점이 있다. 아울러, 수직 전송 게이트를 구비한 전송 트랜지스터는 플로팅 디퓨전의 면적(또는 정전용량)을 감소시켜 신호대잡음비를 더욱더 증가시키는 단점이 있다.

[0023] 따라서, 후술하는 본 발명의 실시예는 수직 전송 게이트를 구비한 이미지 센서에서 신호대잡음비가 증가하는 것을 방지하여 성능이 향상된 이미지 센서 및 이를 구비한 전자장치를 제공한다.

[0024] 도 1은 본 발명의 제1실시예 및 제2실시예에 따른 단위픽셀을 포함하는 이미지 센서를 간략히 도시한 블럭도이다.

[0025] 도 1에 도시된 바와 같이, 실시예에 따른 이미지 센서는 픽셀 어레이(pixel array, 110) 및 신호 처리부(signal processing, 120)를 포함할 수 있다. 픽셀 어레이(110)는 입사광에 응답하여 전기 신호를 생성한다. 픽셀 어레이(110)는 매트릭스 형태로 2차원 배열된 복수의 단위픽셀(100)을 포함할 수 있다. 단위픽셀(100)의 물리적인 구조 및 회로적인 구조에 대해서는 후술하기로 한다.

[0026] 신호 처리부(120)는 픽셀 어레이(110)에서 생성된 전기 신호를 처리하여 이미지 데이터를 생성한다. 신호 처리부(120)는 로우 드라이버(row driver, 121), 상관 이중 샘플링(correlated double sampling, CDS)(122), 아날로그-디지털 변환(analog-to-digital converting, ADC)(123) 및 타이밍 컨트롤러(timing controller, 129)를 포함할 수 있다.

[0027] 로우 드라이버(121)는 픽셀 어레이(110)의 각 로우(row)에 연결되고, 각 로우를 구동하는 구동 신호를 생성한다. 예를 들어, 로우 드라이버(121)는 픽셀 어레이(110)에 포함된 복수의 단위픽셀(100)을 로우 단위로 구동할 수 있다.

[0028] CDS(122)는 커페시터, 스위치 등을 이용하여 단위픽셀(100)의 리셋 상태를 나타내는 기준전압과 입사광에 상응하는 신호 성분을 나타내는 출력전압의 차이를 구하여 상관 이중 샘플링을 수행하고, 유효한 신호 성분에 상응하는 아날로그 샘플링 신호를 출력한다. CDS(122)는 픽셀 어레이(110)의 컬럼 라인들과 각각 연결된 복수의 CDS 회로들을 포함하고, 유효한 신호 성분에 상응하는 아날로그 샘플링 신호를 각 컬럼마다 출력할 수 있다.

[0029] ADC(123)는 유효한 신호 성분에 상응하는 아날로그 이미지 신호를 디지털 이미지 신호로 변환한다. ADC(123)는 기준 신호 생성기(124), 비교기(125), 카운터(126) 및 버퍼(127)를 포함한다. 기준 신호 생성기(124)는 기준 신호 예컨대, 일정한 기울기를 갖는 램프 신호를 생성하고, 램프 신호를 비교기(125)에 기준 신호로서 제공한다. 비교기(125)는 CDS(122)로부터 각 컬럼마다 출력되는 아날로그 샘플링 신호와 기준 신호 생성기(124)로부터 발

생되는 램프 신호를 비교하여 유효한 신호 성분에 따른 각각의 천이 시점을 갖는 비교 신호들을 출력한다. 카운터(126)는 카운팅 동작을 수행하여 카운팅 신호를 생성하고, 카운팅 신호를 버퍼(127)에 제공한다. 버퍼(127)는 컬럼 라인들과 각각 연결된 복수의 래치 회로들을 포함하고, 각 비교 신호의 천이에 응답하여 카운터(126)로부터 출력되는 카운팅 신호를 각 컬럼마다 래치하며, 래치된 카운팅 신호를 상기 이미지 데이터로서 출력한다.

[0030] 실시예에 따라서, ADC(123)는 CDS(122)에서 출력된 샘플링 신호들을 가산하는 가산 회로를 더 포함할 수 있다. 또한, 버퍼(127)는 복수의 싱글 라인 버퍼(single line buffer)들을 더 포함할 수 있다.

[0031] 타이밍 컨트롤러(129)는 로우 드라이버(121), CDS(122), 및 ADC(123)의 동작 타이밍을 제어할 수 있다. 타이밍 컨트롤러(129)는 로우 드라이버(121), CDS(122), ADC(123)에 타이밍(timing) 신호 및 제어 신호를 제공할 수 있다.

[0032] 한편, 도 1을 참조하여 실시예들에 따른 이미지 센서가 아날로그 더블 샘플링을 수행하는 것을 설명하였으나, 실시예에 따라서 이미지 센서는 디지털 더블 샘플링(Digital Double Sampling, DDS)을 수행할 수도 있다. 디지털 더블 샘플링은 핵심을 초기화하였을 때의 리셋 성분에 대한 아날로그 신호 및 신호 성분에 대한 아날로그 신호를 각각 디지털 신호로 변환한 후에 두 개의 디지털 신호의 차이를 유효한 신호 성분으로 추출하는 것을 의미한다.

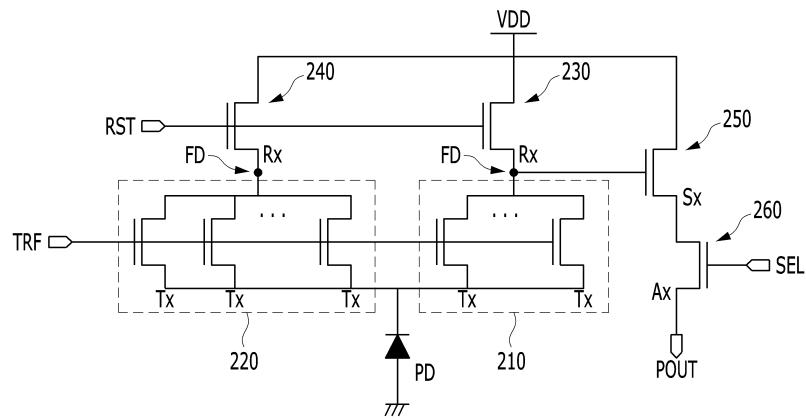

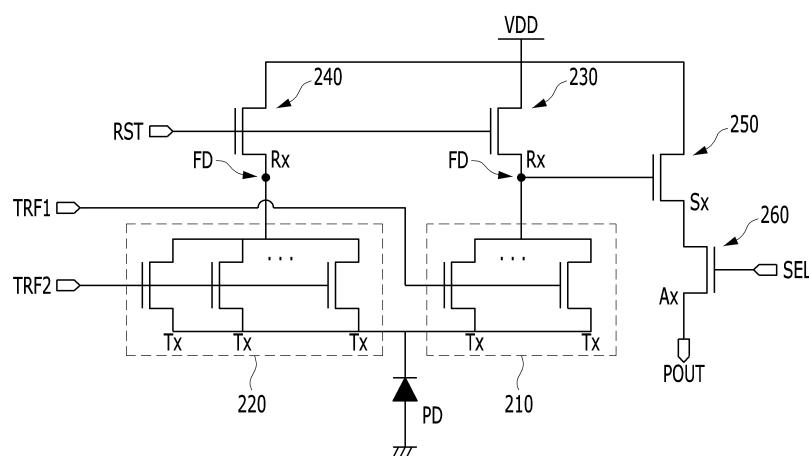

[0033] 이어서, 도 2, 도 3a, 도 3b 및 도 4를 참조하여 제1실시예에 따른 이미지 센서에 대해 상세히 설명하기로 한다. 먼저, 도 2를 참조하여 제1실시예에 따른 이미지 센서의 회로적 구성 및 동작에 대하여 설명하기로 한다.

[0034] 도 2는 제1실시예에 따른 이미지 센서 단위픽셀을 도시한 등가회로도이다.

[0035] 도 2에 도시된 바와 같이, 제1실시예에 따른 이미지 센서의 단위픽셀은 광전변환소자(PD), 전송 트랜지스터(Tx, transfer transistor), 리셋 트랜지스터(Rx, reset transistor), 소스팔로워 트랜지스터(Sx, source follower transister)(250) 및 액세스 트랜지스터(Ax, access transistor)(260)를 포함할 수 있다. 여기서, 전송 트랜지스터(Tx)는 복수개가 구비되며, 제1전송부(210) 및 제2전송부(220)는 하나 이상의 전송 트랜지스터(Tx)로 구성될 수 있다. 그리고, 리셋 트랜지스터(Rx)는 제1전송부(210)에 연결된 제1리셋 트랜지스터(230) 및 제2전송부(220)에 연결된 제2리셋 트랜지스터(240)를 포함할 수 있다.

[0036] 광전변환소자(PD)는 포토다이오드(photo diode)일 수 있다. 광전변환소자(PD)의 일측은 그라운드에 연결될 수 있고, 타측은 제1전송부(210) 및 제2전송부(220)에 연결될 수 있다.

[0037] 제1전송부(210) 및 제2전송부(220)를 구성하는 복수의 전송 트랜지스터(Tx)의 일측(예컨대, 소스)은 광전변환소자(PD)에 연결되고, 타측(예컨대, 드레인)은 플로팅디퓨전노드(FD)에 연결될 수 있다. 제1전송부(210) 및 제2전송부(220)는 하나의 광전변환소자(PD)를 공유하는 형태를 가질 수 있다. 제1전송부(210) 및 제2전송부(220)를 구성하는 복수의 전송 트랜지스터(Tx) 각각은 모두 동일한 형태 또는 동작 특성을 가질 수 있다. 아울러, 플로팅디퓨전노드(FD)는 리셋 트랜지스터(Rx)의 일측에 연결될 수 있다.

[0038] 제1전송부(210) 및 제2전송부(220)는 각각 하나 이상의 전송 트랜지스터(Tx)가 병렬로 연결된 형태를 가질 수 있다. 제1전송부(210) 및 제2전송부(220)를 구성하는 전송 트랜지스터(Tx)의 갯수는 요구되는 특성에 따라 조절할 수 있다. 특히, 제1전송부(210)를 구성하는 전송 트랜지스터(Tx)의 갯수를 조절하여 이미지 센서의 감도 및 신호대잡음비 특성을 제어할 수 있다. 예컨대, 제1전송부(210)의 전송 트랜지스터(Tx)가 5개인 경우를 기준으로, 향상된 신호대잡음비 특성이 요구되는 경우에는 전송 트랜지스터(Tx)의 갯수를 5개 이상으로 증가시켜 신호대잡음비 특성을 향상시킬 수 있다. 반대로, 향상된 감도가 요구되는 경우에는 전송 트랜지스터(Tx)의 갯수를 5개 이하로 감소시켜 감도를 향상시킬 수 있다.

[0039] 제1전송부(210) 및 제2전송부(220)는 하나의 전송신호(TRF)에 응답할 수 있다. 즉, 제1전송부(210) 및 제2전송부(220)를 구성하는 복수의 전송 트랜지스터(Tx)는 하나의 전송 게이트를 공유한 형태를 갖거나, 복수의 전송 트랜지스터(Tx) 각각의 전송 게이트가 하나의 도전라인에 모두 연결된 형태를 가질 수 있다.

[0040] 제1리셋 트랜지스터(230)의 일측은 제1전송부(210)에 연결될 수 있고, 제2리셋 트랜지스터(240)의 일측은 제2전송부(220)에 연결될 수 있다. 제1리셋 트랜지스터(230)의 타측 및 제2리셋 트랜지스터(240)의 타측은 전원전압단(VDD)에 연결될 수 있다. 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)는 하나의 리셋신호(RST)에 응답할 수 있다. 예컨대, 제1리셋 트랜지스터(230)의 게이트 및 제2리셋 트랜지스터(240)의 게이트는 하나의 도전라인에 연결된 형태를 가질 수 있다.

[0041] 소스팔로워 트랜지스터(250)의 일측은 전원전압단(VDD)에 연결될 수 있고, 타측은 액세스 트랜지스터(260)에 연

결될 수 있다. 소스팔로워 트랜지스터(250)의 게이트는 제1전송부(210)에 연결된 플로팅디퓨전노드(FD)에 연결될 수 있다. 즉, 제2전송부(220)에 연결된 플로팅디퓨전노드(FD)에는 소스팔로워 트랜지스터(250)가 연결되지 않는다. 이를 통해, 제1전송부(210)를 구성하는 전송 트랜지스터(Tx)의 갯수를 조절하는 방법으로 이미지 센서의 감도 및 신호대잡음비를 제어할 수 있다.

[0042] 액세스 트랜지스터(260)의 일측은 소스팔로워 트랜지스터(250)에 연결될 수 있고, 타측을 통해 핵셀신호(POUT)가 출력될 수 있다.

[0043] 이어서, 도 2를 참조하여 제1실시예에 따른 이미지 센서의 단위픽셀 구동방법을 살펴보면 다음과 같다.

[0044] 먼저, 입사광이 차단된 상태에서 제1전송부(210) 및 제2전송부(220)에 전송신호(TRF)를 인가하고, 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)에 리셋신호(RST)를 인가하여 각각을 턴 온 시킨다. 제1전송부(210), 제2전송부(220), 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)가 턴 온 되면서 플로팅디퓨전노드(FD)에 잔류하는 전하를 방출시켜 플로팅디퓨전노드(FD)를 리셋시킨다. 여기서, 전송신호(TRF) 및 리셋신호(RST)는 트랜지스터의 턴 온/턴 오프를 제어하는 펄스전압신호일 수 있다.

[0045] 다음으로, 제1전송부(210), 제2전송부(220), 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)를 턴 오프시킨 상태에서 일정 시간 동안 입사광을 광전변환소자(PD)에 입사시킨다. 입사광에 의해 광전변환소자(PD)에서 전자-정공 쌍(Electrin-Hole Pair, EHP) 즉, 광전하가 생성되고, 생성된 광전하는 광전변환소자(PD)에 축적된다. 광전변환소자(PD)에 광전하가 축적되는 시간을 광전변환소자(PD)의 인티그레이션 타입(integration time)이라 한다.

[0046] 한편, 플로팅디퓨전노드(FD)를 리셋시킨 이후에도 인티그레이션 타입 동안 지속적으로 리셋신호(RST)를 인가하여 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)의 턴 온 상태를 유지할 수도 있다. 이 경우, 리셋되지 않고 플로팅디퓨전노드(FD)에 전하가 잔류하는 것을 방지할 수 있다. 또한, 인티그레이션 타입 동안 플로팅디퓨전노드(FD)의 전위가 변화하는 것을 방지할 수 있다. 참고로, 인티그레이션 타입 동안 플로팅디퓨전노드(FD)의 전위가 변화하면 신호대잡음비 특성이 열화될 수 있다.

[0047] 다음으로, 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)가 턴 오프된 상태에서 전송신호(RTF)를 인가하여 인티그레이션 타입 동안 광전변환소자(PD)에 축적된 광전하를 플로팅디퓨전노드(FD)에 전달시킨다. 플로팅디퓨전노드(FD)로 전달된 광전하량에 비례하여 소스팔로워 트랜지스터(250)의 게이트 바이어스가 변화하게 되고, 소스팔로워 트랜지스터(250)의 소스 전위가 변화하게 된다. 여기서, 전송신호(RTF)에 응답하여 제1전송부(210) 및 제2전송부(220) 모두 턴 온된다. 그러나, 소스팔로워 트랜지스터(250)의 게이트는 제1전송부(210)에 연결된 플로팅디퓨전노드(FD)에 연결되어 있기 때문에 제1전송부(210)를 통해 플로팅디퓨전노드(FD)로 전달된 광전하에만 소스팔로워 트랜지스터(250)가 응답하여 소스 전위가 변화하게 된다.

[0048] 소스팔로워 트랜지스터(250)의 소스 전위가 변화되는 시점에서 액세스 트랜지스터(260)에 선택신호(SEL)를 인가하여 액세스 트랜지스터(260)를 턴 온 시키면 핵셀신호(POUT)가 출력된다. 선택신호(SEL)는 트랜지스터의 턴 온/턴 오프를 제어하는 펄스전압신호일 수 있다.

[0049] 상술한 바와 같이, 제1실시예에 따른 이미지 센서는 제1전송부(210) 및 제2전송부(220) 각각이 병렬로 연결된 하나 이상의 전송 트랜지스터(Tx)로 구성됨에 따라 광전변환소자(PD)에서 생성된 광전하에 대한 전달효율을 향상시킬 수 있다.

[0050] 또한, 제1전송부(210)에 연결된 플로팅디퓨전노드(FD)에만 소스팔로워 트랜지스터(250)가 연결됨에 따라 제1전송부(210)를 구성하는 전송 트랜지스터(Tx)의 갯수를 조절하는 방법으로 요구되는 이미지 센서의 감도 및 신호대잡음비 특성을 향상시킬 수 있다.

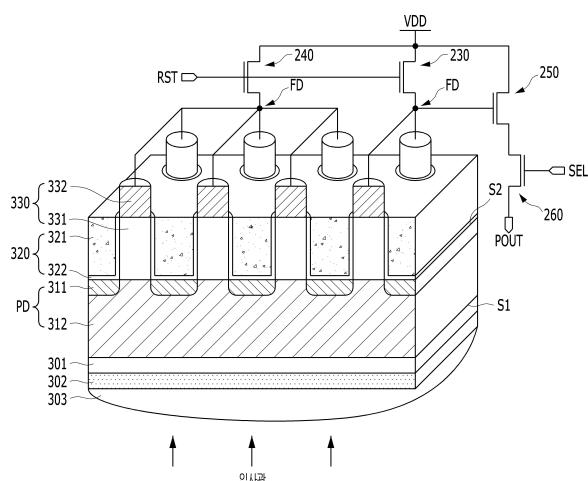

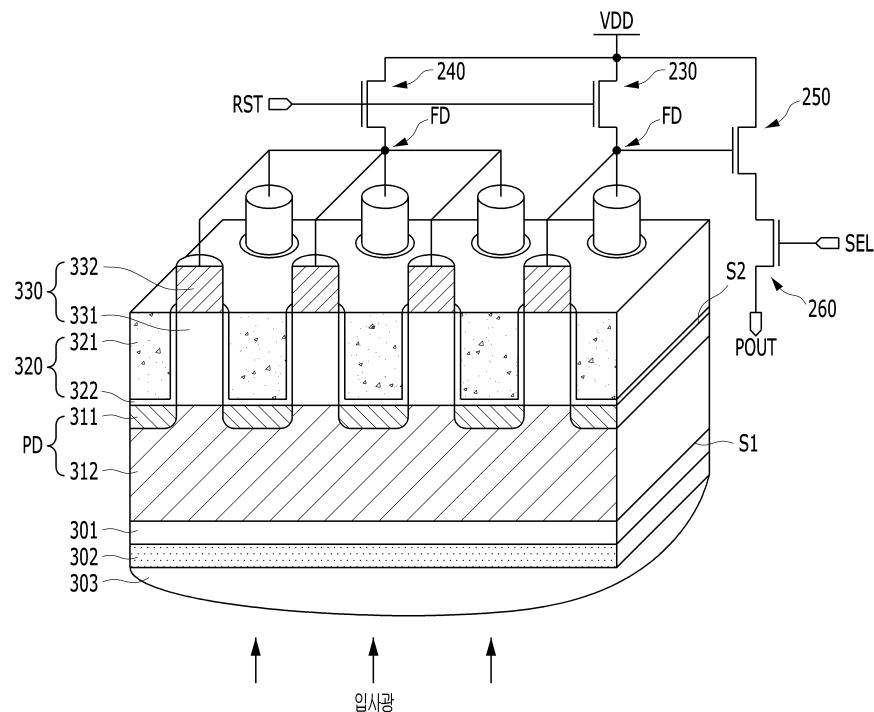

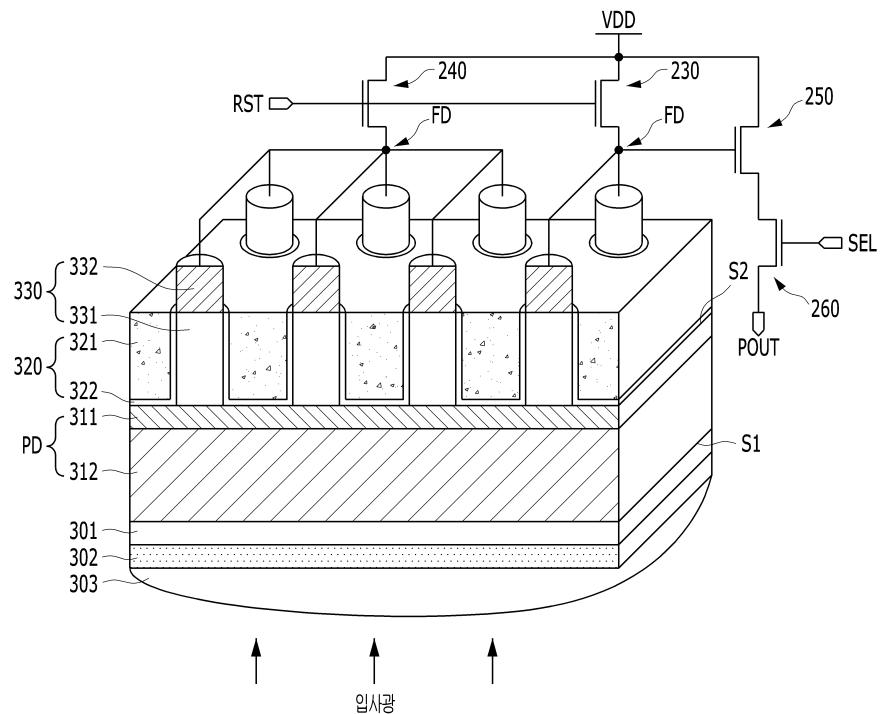

[0051] 이어서, 상술한 등가회로를 갖는 이미지 센서의 구조에 대하여 도 3a, 도 3b 및 도 4를 참조하여 상세히 설명하기로 한다. 도 3a 및 도 3b는 제1실시예 및 변형예에 따른 이미지 센서의 단위픽셀을 도시한 도면으로, 단면도를 포함한 사시도이다. 그리고, 도 4는 제1실시예에 따른 이미지 센서의 단위픽셀에서 복수의 활성필라 형상에 대한 변형예들을 도시한 평면도이다.

[0052] 도 3a 및 도 3b에 도시된 바와 같이, 제1실시예에 따른 이미지 센서의 단위픽셀은 광전변환소자(PD), 광전변환소자(PD) 상에 형성된 전송 게이트(320), 전송 게이트(320)를 관통하여 광전변환소자(PD)에 전기적으로 연결된 복수의 활성필라(330), 복수의 활성필라(330) 중 어느 하나 이상의 활성필라(330)에 전기적으로 연결된 제1리셋 트랜지스터(230), 복수의 활성필라(330) 중 어느 하나 이상의 활성필라(330)를 제외한 나머지 활성필라(330)에

전기적으로 연결된 제2리셋 트랜지스터(240) 및 어느 하나 이상의 활성필라(330)에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터(250)를 포함할 수 있다. 또한, 광전변환소자(PD)로 입사광이 유입되는 입사면(S1) 상에 형성된 컬러필터층(302) 및 컬러필터층(302) 상에 형성된 마이크로렌즈(303)를 포함할 수도 있다.

[0053] 광전변환소자(PD)는 기판(301)에 형성되거나, 또는 기판(301)상에 형성된 것일 수 있다. 광전변환소자(PD)는 단위픽셀의 평면형상에 대응하는 평판형태를 가질 수 있다. 기판(301)은 반도체 물질을 포함할 수 있다. 구체적으로, 기판(301)은 단결정 상태(Single crystal state)일 수 있으며, 실리콘 함유 재료를 포함할 수 있다.

[0054] 광전변환소자(PD)는 포토다이오드를 포함할 수 있다. 포토다이오드는 기판(301)에 형성되어 수직적으로 중첩되는 하나 이상의 광전변환부를 포함하거나, 또는 기판(301)상에 형성된 유기광전변환층(미도시)을 포함할 수 있다. 실시예에서는 광전변환소자(PD)가 기판(301)에 형성되어 수직적으로 중첩되는 하나 이상의 광전변환부를 포함하는 경우를 예시하였다. 광전변환부는 도전형이 P형인 제1불순물영역(311) 및 도전형이 N형인 제2불순물영역(312)을 포함할 수 있다. 제1불순물영역(311) 및 제2불순물영역(312)은 기판(301)에 불순물을 이온주입하여 형성된 것일 수 있다. 제2불순물영역(312)은 전송 트랜지스터(Tx)의 접합영역으로 작용할 수 있다. 여기서, 제1불순물영역(311)은 복수의 활성필라(330) 사이의 기판(301)에 형성되어 복수의 활성필라(330)와 중첩되지 않을 수 있다(도 3a 참조). 이 경우, 복수의 활성필라(330) 각각은 제1불순물영역(311)은 전기적으로 연결되지 않을 수 있다. 또한, 제1불순물영역(311)은 기판(301) 전면상에 형성되어 복수의 활성필라(330)와 중첩될 수 있다(도 3b 참조). 이 경우, 복수의 활성필라(330) 각각은 제1불순물영역(311)과 전기적으로 연결될 수 있다. 참고로, 제1불순물영역(311)이 기판(301) 전면상에 형성되어 복수의 활성필라(330)와 중첩되더라도, 제1불순물영역(311)이 복수의 활성필라(330)와 중첩되지 않는 구조와 유사한 특성을 구현할 수 있다. 이는, 제1불순물영역(311)은 그 자신과 접하는 다른 불순물영역들 대비 상대적으로 작은 두께와 작은 불순물 도핑농도를 갖기 때문이다.

[0055] 전송 게이트(320)는 광전변환소자(PD)에 입사광이 유입되는 입사면(S1)의 반대편인 대향면(S2) 상에 형성될 수 있다. 전송 게이트(320)는 광전변환소자(PD) 상에 형성된 평판형태를 가질 수 있다. 이때, 전송 게이트(320)는 광전변환소자(PD)의 대향면(S2)을 덮는 형태를 가질 수 있다(도 4 참조). 여기서, 전송 게이트(320)는 광전변환소자(PD)를 관통하여 외부로 빠져나가는 입사광을 다시 광전변환소자(PD) 쪽으로 반사시키는 반사층으로 작용하여 광전변환소자(PD)의 양자효율을 증대시킬 수 있다. 따라서, 전송 게이트(320)가 광전변환소자(PD)의 대향면(S2)을 덮는 형태를 가짐으로써, 광전변환소자(PD)의 양자효율을 효과적으로 증대시킬 수 있다. 반사층으로서 작용이 용이하도록 전송 게이트(320)는 금속성물질을 포함할 수 있다.

[0056] 전송 게이트(320)는 광전변환소자(PD) 상에서 복수의 활성필라(330)의 측벽 모두를 둘러싸는 게이트전극(321) 및 게이트전극(321)과 광전변환소자(PD) 및 복수의 활성필라(330) 사이에 게재된 전하차단막(322)을 포함할 수 있다. 복수의 활성필라(330)를 하나의 게이트전극(321)이 모두 둘러싸는 형태를 갖기 때문에 전송신호(TRF)에 복수의 전송 트랜지스터(Tx) 모두가 응답할 수 있다. 게이트전극(321)은 금속성물질을 포함할 수 있고, 전하차단막(322)은 절연물질을 포함할 수 있다.

[0057] 복수의 활성필라(330) 각각은 광전변환소자(PD)에 전기적으로 연결되고 전송 게이트(320)가 둘러싸는 채널영역(331) 및 채널영역(331)에 전기적으로 연결되어 전송 게이트(320) 위로 돌출된 플로팅디퓨전영역(332)을 포함할 수 있다.

[0058] 복수의 활성필라(330) 각각은 기판(301)과 동일한 물질을 포함할 수 있다. 예컨대, 복수의 활성필라(330) 각각은 기판(301)을 식각하여 형성된 것일 수 있으며, 단결정의 실리콘 함유 물질을 포함할 수 있다. 복수의 활성필라(330) 각각은 다양한 형상을 가질 수 있다. 예컨대, 도 4를 참조하여 복수의 활성필라(330) 각각은 사각형 기둥, 사각형 이상의 다각형 기둥, 원형기둥, 타원형기둥, 도넛형기둥 및 십자형기둥을 포함한 다양한 기하학적 형태를 가질 수 있다. 이때, 복수의 활성필라(330) 각각은 서로 동일한 형상을 갖거나, 또는 서로 상이한 형상을 가질 수 있다. 이처럼, 다양한 형상을 갖는 복수의 활성필라(330) 각각은 전송 트랜지스터(Tx)의 턴 오프 상태에서 채널영역(331)의 완전공핍(fully depletion)이 가능한 선폭을 가질 수 있다. 여기서, 전송 트랜지스터(Tx)의 턴 오프 상태는 전송 게이트(320)에 바이어스가 인가되지 않은 평형상태를 의미한다. 예컨대, 복수의 활성필라(330) 각각이 원형기둥 형상일 때, 원형기둥은 완전공핍이 가능하도록 30nm 이하의 직경을 가질 수 있다. 이는, 전송 트랜지스터(Tx)의 턴 오프 상태에서 누설전류가 발생하는 것을 방지하기 위함이다. 즉, 노이즈 발생을 방지하여 신호대잡음비 특성을 향상시키기 위함이다.

[0059] 플로팅디퓨전영역(332)은 복수의 활성필라(330) 각각의 상부영역에 형성된 불순물영역일 수 있다. 하나 이상의 플로팅디퓨전영역(332)이 서로 연결되어 플로팅디퓨전노드(FD)로 작용할 수 있다. 즉, 각각 플로팅디퓨전영역(332)을 포함한 복수의 활성필라(330) 중 어느 하나 이상의 활성필라(330)는 제1리셋 트랜지스터(230)에 연결될

수 있다. 제1리셋 트랜지스터(230)에 연결된 나머지 활성필라(330)는 제2리셋 트랜지스터(240)에 연결될 수 있다. 제1리셋 트랜지스터(230)에 연결된 하나 이상의 플로팅디퓨전영역(332)은 소스팔로워 트랜지스터(250)의 턴 온/턴 오프를 제어하는 플로팅디퓨전노드(FD)로 작용할 수 있다. 플로팅디퓨전영역(332)은 광전변환소자(PD)의 제2불순물영역(312)과 동일한 도전형을 가질 수 있다. 예컨대, 플로팅디퓨전영역(332)은 N형 불순물이 도핑된 N형 불순물영역일 수 있다.

[0060] 복수의 활성필라(330) 각각에서 채널영역(331)은 불순물이 도핑되지 않은 언도프트 상태일 수 있다. 예컨대, 채널영역(331)은 진성 반도체일 수 있다. 반면에, 복수의 활성필라(330) 각각에서 채널영역(331)은 불순물이 도핑된 도프트 상태일 수 있으며, 채널영역(331)의 도전형은 플로팅디퓨전영역(332)의 도전형과 동일할 수 있다. 이 때, 채널영역(331)의 불순물 도핑농도는 플로팅디퓨전영역(332)의 불순물 도핑농도보다 작을 수 있다. 여기서, 채널영역(331)이 언도프트 상태를 갖거나, 또는 플로팅디퓨전영역(332)과 동일한 도전형을 갖는 불순물이 도핑된 도프트 상태를 가짐으로써, 전송 트랜지스터(Tx)의 턴 오프 상태에서 누설전류가 발생하는 것을 방지할 수 있다. 즉, 노이즈 발생을 방지하여 신호대잡음비 특성을 향상시키기 위함이다.

[0061] 상술한 구조를 갖는 제1실시예에 따른 이미지 센서의 단위픽셀은 복수의 활성필라(330) 각각의 채널영역(331) 도핑상태 및 선택을 통해 전송 트랜지스터(Tx) 턴 오프 상태에서의 누설전류 발생을 방지함으로써, 이미지 센서의 신호대잡음비 특성을 향상시킬 수 있다.

[0062] 이하에서는, 도 5 및 도 6을 참조하여 제2실시예에 따른 이미지 센서에 대하여 상세히 설명하기로 한다. 설명의 편의를 위해 제1실시예와 동일한 구성에 대해서는 동일한 도면부호를 사용하고, 동일한 구성에 대하여 상세한 설명을 생략하기로 한다. 즉, 제1실시예와 제2실시예 사이의 차이점을 중심으로 설명하기로 한다.

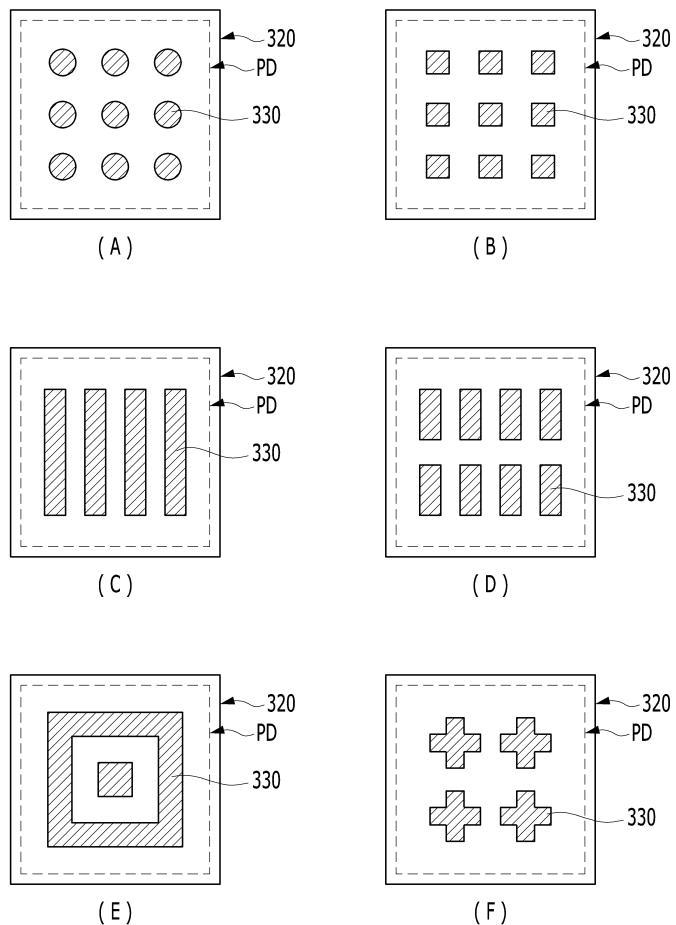

[0063] 도 5는 제2실시예에 따른 이미지 센서 단위픽셀을 도시한 등가회로도이고, 도 6은 제2실시예에 따른 이미지 센서의 단위픽셀을 도시한 도면으로, 단면도를 포함한 사시도이다.

[0064] 도 5 및 도 6에 도시된 바와 같이, 제2실시예에 따른 이미지 센서의 단위픽셀은 제1전송부(210) 및 제2전송부(220)가 각각 서로 다른 전송신호(TRF1, TRF2)에 응답하는 점에서 제1실시예와 상이하다. 구체적으로, 제1전송부(210)는 제1전송신호(TRF1)에 응답할 수 있고, 제2전송부(220)는 제2전송신호(TRF2)에 응답할 수 있다. 따라서, 제1전송부(210)를 구성하는 복수의 전송 트랜지스터(Tx)는 하나의 전송 게이트를 공유한 형태를 갖거나, 복수의 전송 트랜지스터(Tx) 각각의 전송 게이트가 하나의 도전라인에 모두 연결된 형태를 가질 수 있다. 그리고, 제2전송부(220)를 구성하는 복수의 전송 트랜지스터(Tx)는 하나의 전송 게이트를 공유한 형태를 갖거나, 복수의 전송 트랜지스터(Tx) 각각의 전송 게이트가 하나의 도전라인에 모두 연결된 형태를 가질 수 있다.

[0065] 이어서, 도 5를 참조하여 제2실시예에 따른 이미지 센서의 단위픽셀 구동방법을 살펴보면 다음과 같다.

[0066] 먼저, 입사광이 차단된 상태에서 제1전송부(210) 및 제2전송부(220)에 각각 제1전송신호(TRF1) 및 제2전송신호(TRF2)를 인가하고, 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)에 리셋신호(RST)를 인가하여 각각을 턴 온 시킨다. 제1전송부(210), 제2전송부(220), 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)가 턴 온되면서 플로팅디퓨전노드(FD)에 잔류하는 전하를 방출시켜 플로팅디퓨전노드(FD)를 리셋시킨다. 여기서, 제1전송신호(TRF1), 제2전송신호(TRF2) 및 리셋신호(RST)는 트랜지스터의 턴 온/턴 오프를 제어하는 펄스전압신호일 수 있다. 제1전송신호(TRF1) 및 제2전송신호(TRF2)는 동일한 신호일 수 있다.

[0067] 다음으로, 제1전송부(210), 제2전송부(220), 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)를 턴 오프시킨 상태에서 일정 시간 동안 입사광을 광전변환소자(PD)에 입사시킨다. 입사광에 의해 광전변환소자(PD)에서 전자-정공 쌍(Electrin-Hole Pair, EHP) 즉, 광전하가 생성되고, 생성된 광전하는 광전변환소자(PD)에 축적된다. 광전변환소자(PD)에 광전하가 축적되는 시간을 광전변환소자(PD)의 인티그레이션 타입(integration time)이라 한다.

[0068] 한편, 플로팅디퓨전노드(FD)를 리셋시킨 이후에도 인티그레이션 타입 동안 지속적으로 리셋신호(RST)를 인가하여 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)의 턴 온 상태를 유지할 수도 있다. 이 경우, 리셋되지 않고 플로팅디퓨전노드(FD)에 전하가 잔류하는 것을 방지할 수 있다. 또한, 인티그레이션 타입 동안 플로팅디퓨전노드(FD)의 전위가 변화하는 것을 방지할 수 있다. 참고로, 인티그레이션 타입 동안 플로팅디퓨전노드(FD)의 전위가 변화하면 신호대잡음비 특성이 열화될 수 있다.

[0069] 다음으로, 제1리셋 트랜지스터(230) 및 제2리셋 트랜지스터(240)가 턴 오프된 상태에서 제1전송신호(RTF1) 만을

인가하여 제1전송부(210)를 통해 인터그레이션 탑입 동안 광전변환소자(PD)에 축적된 광전하를 플로팅디퓨전노드(FD)에 전달시킨다. 이때, 제2전송신호(TRF2)를 인가하지 않기 때문에 제2전송부(220) 내 복수의 전송 트랜지스터(Tx) 채널영역은 모두 완전공핍상태를 유지할 수 있다. 플로팅디퓨전노드(FD)로 전달된 광전하량에 비례하여 소스팔로워 트랜지스터(250)의 게이트 바이어스가 변화하게 되고, 소스팔로워 트랜지스터(250)의 소스 전위가 변화하게 된다. 여기서, 제1전송신호(TRF1) 만을 인가함에 따라 제1전송부(210)를 통해 플로팅디퓨전노드(FD)로 전달된 광전하에만 소스팔로워 트랜지스터(250)가 응답하여 소스 전위가 변화하게 된다. 소스팔로워 트랜지스터(250)의 게이트가 연결된 플로팅디퓨전노드(FD)로 광전하를 전달하는 제1전송부(210)만이 턴 온되기 때문에 광전하 전달효율 및 광전하에 대한 소스팔로워 트랜지스터의 반응성을 향상시킬 수 있다.

[0070] 소스팔로워 트랜지스터(250)의 소스 전위가 변화되는 시점에서 액세스 트랜지스터(260)에 선택신호(SEL)를 인가하여 액세스 트랜지스터(260)를 턴 온 시키면 핀셀신호(POUT)가 출력된다. 선택신호(SEL)는 트랜지스터의 턴 온/턴 오프를 제어하는 펄스전압신호일 수 있다.

[0071] 상술한 바와 같이, 제2실시예에 따른 이미지 센서는 제1전송부(210) 및 제2전송부(220) 각각이 병렬로 연결된 하나 이상의 전송 트랜지스터(Tx)로 구성됨에 따라 광전변환소자(PD)에서 생성된 광전하에 대한 전달효율을 향상시킬 수 있다.

[0072] 또한, 제1전송부(210)에 연결된 플로팅디퓨전노드(FD)에만 소스팔로워 트랜지스터(250)가 연결됨에 따라 제1전송부(210)를 구성하는 전송 트랜지스터(Tx)의 갯수를 조절하는 방법으로 요구되는 이미지 센서의 감도 및 신호대잡음비 특성을 향상시킬 수 있다.

[0073] 또한, 제1전송부(210) 및 제2전송부(220)가 개별적인 전송신호(TRF1, TRF2)에 응답하기 때문에 보다 다양한 동작 특성을 확보함과 동시에 소비전력을 감소시킬 수 있다.

[0074] 이어서, 도 6을 참조하여 등가회로를 갖는 이미지 센서의 구조에 대하여 설명하기로 한다.

[0075] 제2실시예에 따른 이미지 센서의 단위픽셀은 광전변환소자(PD), 광전변환소자(PD) 상에 형성된 전송 게이트(320), 전송 게이트(320)를 관통하여 광전변환소자(PD)에 전기적으로 연결된 복수의 활성필라(330), 복수의 활성필라(330) 중 어느 하나 이상의 활성필라(330)에 전기적으로 연결된 제1리셋 트랜지스터(230), 복수의 활성필라(330) 중 어느 하나 이상의 활성필라(330)를 제외한 나머지 활성필라(330)에 전기적으로 연결된 제2리셋 트랜지스터(240) 및 어느 하나 이상의 활성필라(330)에 게이트가 전기적으로 연결된 소스팔로워 트랜지스터(250)를 포함할 수 있다. 또한, 광전변환소자(PD)로 입사광이 유입되는 입사면(S1) 상에 형성된 컬러필터층(302) 및 컬러필터층(302) 상에 형성된 마이크로렌즈(303)를 포함할 수도 있다.

[0076] 여기서, 전송 게이트(320)가 복수의 활성필라(330) 중 일부와 그외 나머지를 둘러싸는 제1게이트전극(321A)과 제2게이트전극(321B)으로 분리되어 구성된 측면에서 제1실시예와 상이하다. 구체적으로, 전송 게이트(320)는 광전변환소자(PD) 상에서 복수의 활성필라(330) 중 제1리셋 트랜지스터(230)에 연결된 활성필라(330)의 측벽 모두를 둘러싸는 제1게이트전극(321A), 복수의 활성필라(330) 중 제2리셋 트랜지스터(240)에 연결된 활성필라(330)의 측벽 모두를 둘러싸는 제2게이트전극(321B), 제1게이트전극(321A) 및 제2게이트전극(321B)과 광전변환소자(PD) 및 복수의 활성필라(330) 사이에 게재된 전하차단막(322)을 포함할 수 있다. 제1게이트전극(321A)이 둘러싸는 어느 하나 이상의 활성필라(330)를 포함하는 전송 트랜지스터(Tx)는 제1전송신호(TRF1)에 응답하고, 제2게이트전극(321B)이 둘러싸는 나머지 활성필라(330)를 포함하는 전송 트랜지스터(Tx)는 제2전송신호(TRF2)에 응답할 수 있다. 제1게이트전극(321A) 및 제2게이트전극(321B)는 금속성물질을 포함할 수 있고, 전하차단막(322)은 절연물질을 포함할 수 있다.

[0077] 상술한 구조를 갖는 제2실시예에 따른 이미지 센서의 단위픽셀은 복수의 활성필라(330) 각각의 채널영역(331) 도핑상태 및 선택을 통해 전송 트랜지스터(Tx) 턴 오프 상태에서의 누설전류 발생을 방지함으로써, 이미지 센서의 신호대잡음비 특성을 향상시킬 수 있다.

[0078] 상술한 제1실시예 및 제2실시예에 따른 이미지 센서는 다양한 전자장치에 응용될 수 있다. 이하, 도 7을 참조하여 실시예에 따른 이미지 센서를 구비한 전자장치의 일례를 설명하기로 한다. 도 7은 정지 이미지 촬영이 가능한 디지털 스틸 카메라를 예로 한 것이다.

[0079] 도 7은 실시예에 따른 전자장치의 구성을 간략히 도시한 도면이다.

[0080] 도 7에 도시된 바와 같이, 실시예에 따른 전자장치는 광학렌즈(410), 이미지 센서(411), 구동회로(412) 및 신호

처리회로(413)를 포함할 수 있다. 이미지 센서(411)는 본 발명의 제1실시예 및 제2실시예에 따른 것일 수 있다.

[0081] 광학렌즈(110)는 피사체로부터의 입사광을 이미지 센서(411)의 활성면에 결상시킨다. 이로써 이미지 센서(411) 내에 일정 기능 해당 신호에 대응하는 전하가 축적된다. 구동회로(412)는 이미지 센서(411)의 전송 동작 신호를 공급한다. 구동회로(412)로부터 공급되는 구동 신호(또는 타이밍 신호)에 의해, 이미지 센서(411)의 신호 전송이 진행된다. 신호처리회로(413)는 각종의 신호 처리를 행한다. 신호 처리가 행하여진 영상 신호는 메모리 등의 기억 매체에 기억되거나, 또는 모니터에 출력된다.

[0082] 본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기 실시예는 그 설명을 위한 것이며, 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술분야의 통상의 전문가라면 본 발명의 기술사상의 범위내의 다양한 실시예가 가능함을 이해할 수 있을 것이다.

### 부호의 설명

210 : 제1전송부 220 : 제2전송부

230 : 제1리셋 트랜지스터 240 : 제2리셋 트랜지스터

250, Sx : 소스팔로워 트랜지스터 260, Ax : 액세스 트랜지스터

Rx : 리셋 트랜지스터 Tx : 전송 트랜지스터

PD : 광전변환소자 301 : 기판

302 : 컬러필터층 303 : 마이크로렌즈

311 : 제1불순물영역 312 : 제2불순물영역

320 : 전송 케이트 321 : 케이트전극

322 : 전하차단막 330 : 활성필라

331 : 채널영역 332 : 플로팅디퓨전영역

### 도면

#### 도면1

## 도면2

## 도면3a

## 도면3b

## 도면4

## 도면5

도면6

도면7