(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4036552号

(P4036552)

(45) 発行日 平成20年1月23日(2008.1.23)

(24) 登録日 平成19年11月9日(2007.11.9)

(51) Int.C1.

F 1

|                       |                  |              |       |

|-----------------------|------------------|--------------|-------|

| <b>G 11 C 16/02</b>   | <b>(2006.01)</b> | G 11 C 17/00 | 601 P |

| <b>G 11 C 16/04</b>   | <b>(2006.01)</b> | G 11 C 17/00 | 613   |

| <b>HO 1 L 21/8247</b> | <b>(2006.01)</b> | G 11 C 17/00 | 621 A |

| <b>HO 1 L 27/115</b>  | <b>(2006.01)</b> | HO 1 L 27/10 | 434   |

| <b>HO 1 L 27/10</b>   | <b>(2006.01)</b> | HO 1 L 27/10 | 481   |

請求項の数 3 (全 11 頁) 最終頁に続く

(21) 出願番号

特願平10-358731

(22) 出願日

平成10年12月17日(1998.12.17)

(65) 公開番号

特開2000-182386 (P2000-182386A)

(43) 公開日

平成12年6月30日(2000.6.30)

審査請求日

平成17年7月8日(2005.7.8)

前置審査

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100094525

弁理士 土井 健二

(74) 代理人 100094514

弁理士 林 恒徳

(72) 発明者 福岡 郁人

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 高野 芳徳

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

フロー・ティングゲートに電荷を蓄積することによりデータを記憶する複数のメモリセルを有し、前記メモリセルは前記フロー・ティングゲート上にコントロールゲートを有する不揮発性半導体記憶装置において、

前記フロー・ティングゲートの電荷の交換について第1の電荷交換能力を有する第1のメモリセル群と、

前記第1の交換能力より高い第2の電荷交換能力を有する第2のメモリセル群と、

前記第1及び第2のメモリセル群のメモリセルのフロー・ティングゲートに電荷を注入する書き込みを行った後の第1の読み出し時に、前記フロー・ティングゲートへの電荷の注入の有無による閾値電圧の違いに対応する第1の読み出し電位を前記コントロールゲートに印加し、前記第1及び第2のメモリセル群のメモリセルに全面プログラム後に全面消去、又は全面消去後に全面プログラムした後の第2の読み出し時に、前記第1及び第2の電荷交換能力による閾値電圧の違いに対応する第2の読み出し電位を前記コントロールゲートに印加する読み出しレベル生成回路とを有することを特徴とする不揮発性半導体記憶装置。

## 【請求項 2】

フロー・ティングゲートに電荷を蓄積することによりデータを記憶する複数のメモリセルを有し、前記メモリセルは前記フロー・ティングゲート上にコントロールゲートを有する不揮発性半導体記憶装置において、

前記フローティングゲートの電荷の交換について第1の電荷交換能力を有する第1のメモリセルと、前記第1の交換能力より高い第2の電荷交換能力を有する第2のメモリセルとを有する第1のメモリ領域と、

前記第1または第2の電荷交換能力のいずれか一方を有するメモリセルを有する第2のメモリ領域と、

前記第1のメモリ領域内の第1及び第2のメモリセルのフローティングゲートに電荷を注入する書き込みを行った後の第1の読み出し時に、前記フローティングゲートへの電荷の注入の有無による閾値電圧の違いに対応する第1の読み出し電位を前記コントロールゲートに印加し、前記第1のメモリ領域内の第1及び第2のメモリセルに全面プログラム後に全面消去、又は全面消去後に全面プログラムした後の第2の読み出し時に、前記第1及び第2の電荷交換能力による閾値電圧の違いに対応する第2の読み出し電位を前記コントロールゲートに印加する読み出しレベル生成回路とを有することを特徴とする不揮発性半導体記憶装置。10

### 【請求項3】

フローティングゲートに電荷を蓄積することによりデータを記憶する複数のメモリセルを有する不揮発性メモリ領域を有するマイクロプロセッサにおいて、

前記不揮発性メモリ領域は、前記フローティングゲートの電荷の交換について第1の電荷交換能力を有する第1のメモリセルと、前記第1の交換能力より高い第2の電荷交換能力を有する第2のメモリセルとを有する第1のメモリ領域と、前記第1または第2の電荷交換能力を有するメモリセルを有する第2のメモリ領域とを有し、20

前記第1のメモリ領域内に、前記第1及び第2のメモリセルの組み合わせによってブート用プログラムが記録され、

更に、前記第1のメモリ領域内の第1及び第2のメモリセルのフローティングゲートに電荷を注入する書き込みを行った後の第1の読み出し時に、前記フローティングゲートへの電荷の注入の有無による閾値電圧の違いに対応する第1の読み出し電位を前記コントロールゲートに印加し、前記第1のメモリ領域内の第1及び第2のメモリセルに全面プログラム後に全面消去、又は全面消去後に全面プログラムした後の第2の読み出し時に、前記第1及び第2の電荷交換能力による閾値電圧の違いに対応する第2の読み出し電位を前記コントロールゲートに印加する読み出しレベル生成回路を有することを特徴とするマイクロプロセッサ。30

### 【発明の詳細な説明】

#### 【0001】

#### 【発明の属する技術分野】

本発明は、フローティングゲートに電荷を蓄積するまたは蓄積しないことによりデータの記憶を行う不揮発性半導体記憶装置に関し、特に、通常の書き込みや消去動作を行っても、所定の初期データを再度読み出すことが可能な不揮発性半導体記憶装置に関する。

#### 【0002】

#### 【従来の技術】

フローティングゲートを有するEEPROMは、電源が切斷されても記憶が失われないことから、不揮発性半導体記憶装置として長期に渡り保存すべきデータやプログラム等の記憶に利用される。かかるEEPROMは、所定のブロック毎の消去を行うフラッシュメモリとしても利用され、かかるフラッシュメモリは、例えばマイクロプロセッサに内蔵されるプログラム用のメモリとして利用される。40

#### 【0003】

マイクロプロセッサなどに内蔵される不揮発性半導体記憶装置（以下簡単のために例示的にフラッシュメモリとする）に、データやプログラムを書き込む為には、第1に、外付けの書き込み装置を使用して書き込む方法、第2に、外付けの書き込み装置を利用して一旦ブートプログラムを書き込み、その後このブートプログラムを利用して本来のデータやプログラムを書き込む（ダウンロード）方法、第3に、上記のブートプログラムを記録したROMを別途設け、そのROM内のブートプログラムを利用して本来のデータやプログラ50

ムを書き込む（ダウンロード）方法などがある。

【0004】

上記の第1の方法は、書き込みに要する工数が多く現実的ではない。また、第3の方法は、データやプログラムのダウンロード用のブートプログラムを格納したROMを別途設ける必要があり、好ましくない。従って、上記の第2の方法が、最も効率的で低成本である。

【0005】

【発明が解決しようとする課題】

しかしながら、フラッシュメモリの記憶容量を最大限利用して大容量のデータやプログラムをダウンロードするためには、予め格納されているブートプログラムを記憶している領域に上書きを行う必要がある。このブートプログラムは、一旦データやプログラムがダウンロードされると、その後は利用されないプログラムであるので、このような上書きを行っても何ら支障はないはずである。

10

【0006】

ただし、例えばブートプログラムを記憶している領域に上書きをした後に、その書き込んだデータやプログラムの変更が必要になる場合がある。或いは、ダウンロードの途中に何らかの動作の不具合が発生し、ブートプログラムは消失したが正常にダウンロードを完了することができない場合がある。そのような場合、すでにブートプログラムは消失してしまっているので、再度データやプログラムをダウンロードしようとしても、そのためのブートプログラムが存在せず、マイクロプロセッサへのデータやプログラムの書き込みが行えなくなるという課題がある。

20

【0007】

そこで、本発明の目的は、誤ってブートプログラム等の初期データを消去してしまっても、後でその初期データを読み出すことができる不揮発性半導体記憶装置を提供することにある。

【0008】

更に、本発明の目的は、所定のデータ等が上書きされた後に、メモリセルを上書き前の状態に復帰させることができ、上書き前の記憶データの読み出しが可能な不揮発性半導体記憶装置を提供することにある。

30

【0009】

更に、本発明の目的は、上記の目的の不揮発性半導体記憶装置を有するマイクロプロセッサを提供することにある。

【0010】

【課題を解決するための手段】

上記の目的を達成するために、本発明は、フローティングゲートに電子などの電荷を蓄積するまたはしないことによりデータを記憶するメモリセルを有する半導体記憶装置において、更に、そのメモリセルを第1の電荷交換能力を持つ第1のメモリセルと第2の電荷交換能力を持つ第2のメモリセルにすることで、復活させたいデータを記憶させることを特徴とする。メモリセルへの全面消去または全面書き込み（プログラム）を行うことにより、メモリセルの異なる電荷交換能力に従って、異なる閾値電圧状態にすることにより、復活させたいデータの読み出しが可能になる。

40

【0011】

上記の目的を達成するために、本発明は、フローティングゲートに電荷を蓄積することによりデータを記憶する複数のメモリセルを有する不揮発性半導体記憶装置において、前記フローティングゲートの電荷の交換について第1の電荷交換能力を有する第1のメモリセル群と、

前記第1の交換能力より高い第2の電荷交換能力を有する第2のメモリセル群とを有することを特徴とする。

【0012】

上記の発明において、前記メモリセルは、第1の導電型の半導体基板表面に形成され、当

50

該半導体基板表面に形成された第2の導電型のソース領域およびドレイン領域と、前記ソース、ドレイン領域の間の前記第1の導電型のチャネル領域上に形成された前記フローティングゲートと、該フローティングゲート上に形成されたコントロールゲートとを有し、前記第1のメモリセル群の前記チャネル領域は、前記第2のメモリセル群の前記チャネル領域と不純物濃度が異なることを特徴とする。

#### 【0013】

更に、上記の発明において、

前記メモリセルは、前記フローティングゲート上にコントロールゲートを有し、

更に、第1の読み出し時に、前記コントロールゲートに第1の読み出し電位を印加し、前記第1の読み出し時と異なる第2の読み出し時に、前記コントロールゲートに前記第1の読み出し電位と異なる第2の読み出し電位を印加する読み出しレベル生成回路を有することを特徴とする。

10

#### 【0014】

上記の目的を達成するために、本発明は、フローティングゲートに電荷を蓄積することによりデータを記憶する複数のメモリセルを有する不揮発性半導体記憶装置において、前記フローティングゲートの電荷の交換について第1の電荷交換能力を有する第1のメモリセルと、前記第1の交換能力より高い第2の電荷交換能力を有する第2のメモリセルとを有する第1のメモリ領域と、

前記第1または第2の電荷交換能力のいずれか一方を有するメモリセルを有する第2のメモリ領域とを有することを特徴とする。

20

#### 【0015】

上記の発明において、

前記メモリセルは、前記フローティングゲート上にコントロールゲートを有し、

第1の読み出し時に、前記コントロールゲートに第1の読み出し電位を印加して前記第1のデータを読み出し、前記第1の読み出し時と異なる第2の読み出し時に、前記コントロールゲートに前記第1の読み出し電位と異なる第2の読み出し電位を印加して、前記フローティングゲートの電荷蓄積状態に応じた第2のデータを読み出すことを特徴とする。

#### 【0016】

更に、上記の発明において、前記第1のデータはエラー検出コードを有し、前記第1のデータの読み出し時において、当該エラー検出コードを利用して該第1のデータが読み出されることを特徴とする。

30

#### 【0017】

上記の目的を達成するために、本発明は、フローティングゲートに電荷を蓄積することによりデータを記憶する複数のメモリセルを有する不揮発性メモリ領域を有するマイクロプロセッサにおいて、

前記不揮発性メモリ領域は、前記フローティングゲートの電荷の交換について第1の電荷交換能力を有する第1のメモリセルと、前記第1の交換能力より高い第2の電荷交換能力を有する第2のメモリセルとを有する第1のメモリ領域と、前記第1または第2の電荷交換能力を有するメモリセルを有する第2のメモリ領域とを有し、

前記第1のメモリ領域内に、前記第1及び第2のメモリセルの組み合わせによってブート用プログラムが記録されることを特徴とする。

40

#### 【0018】

上記の発明によれば、上書きされてもブート用プログラムを復活させることができる。

#### 【0019】

##### 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態例を説明する。しかしながら、かかる実施の形態例が、本発明の技術的範囲を限定するものではない。

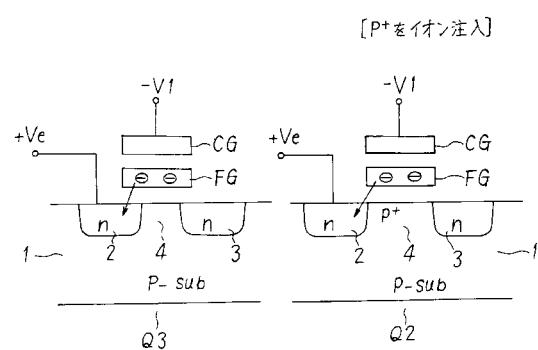

#### 【0020】

図1は、本実施の形態例の電荷交換能力が異なるメモリセルの例を示す断面図である。図1に併記されたメモリセルQ2, Q3は、いずれも、P型の半導体基板10の表面に、N

50

型のソース領域 2 とドレイン領域 3 とが設けられる。そして、それらの領域間のチャネル領域 4 上に、絶縁膜を介してフローティングゲート F G が設けられ、更にその上に別の絶縁膜を介してコントロールゲート C G が設けられる。

【 0 0 2 1 】

これらのメモリセル Q 2 , Q 3 のフローティングゲート F G には、例えば電子が注入されることによりメモリセルのトランジスタとしての閾値電圧が高くなり、注入された電子が抜き取られることにより閾値電圧が低くなる。電子を注入する場合は、ドレイン領域 3 を高い電圧にし、ソース領域 2 をグランド電位にし、コントロールゲート C G を高い電圧にすることで、チャネル領域からフローティングゲート F G 内に電子を注入する。かかる動作は、書き込み動作またはプログラム動作であり、メモリセルは、電子が注入されることで、その閾値電圧が高くなるデータ「 0 」の状態になる。また、電子を引き抜く場合は、ドレイン領域 3 をフローティングにし、ソース領域 2 を高い電位にし、コントロールゲート C G を低い電位または負の電位にする。その結果、フローティングゲート F G に蓄積された電子がソース領域 2 側に引き抜かれ、閾値が低くなる。この動作は、消去動作であり、メモイリセルは、電子が引き抜かれることにより、データ「 1 」の状態になる。

【 0 0 2 2 】

図 1 に示されたメモリセル Q 2 , Q 3 は、その電荷交換能力に差がある。即ち、フローティングゲートから電荷を引き抜く能力または電荷を注入する能力に差がある。図 1 の例では、メモリセル Q 2 のチャネル領域 4 に P 型の不純物が追加的にイオン注入され、例えばソース領域 2 とフローティングゲート F G との重なりの面積が、メモリセル Q 3 よりも小さく形成される。かかる不純物濃度の違いに伴う構成の違いから、例えばフローティングゲート F G 内の電荷である電子が、ソース領域 2 側に引き抜かれる速度、即ち電荷交換能力に差が生じることになる。即ち、上記したソース領域を高い電位にし、コントロールゲート D G を低いまたは負の電位にする消去パルスを、データ「 0 」の状態から両方のメモリセルに印加した場合、同じ回数の消去パルスを印加した結果、両メモリセル Q 2 , Q 3 の間で引き抜かれた電子の量に差が生じる。従って、そのフローティングゲート F G 内の電子の量の差を閾値の差として読み出すことが可能になる。

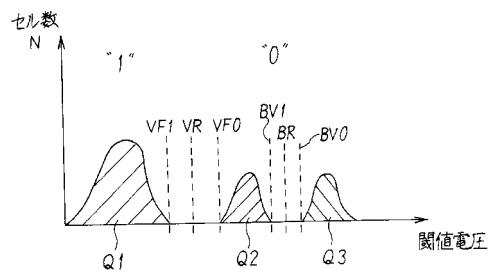

【 0 0 2 3 】

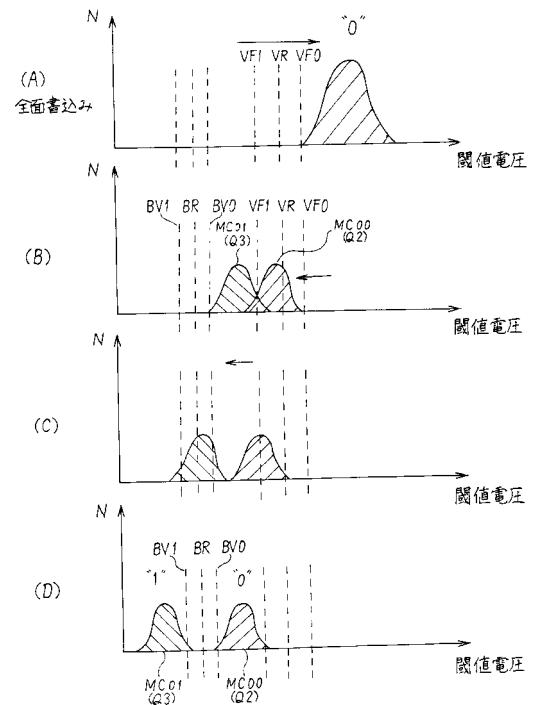

図 2 は、電荷交換能力の異なるメモリセルと通常のプログラム状態または消去状態のメモリセルの閾値分布を示す図である。図 2 の横軸はメモリセルの閾値電圧を示し、縦軸はメモリセルの数を示す。図 2 には、通常の読み出し電圧 V R 、書き込みベリファイレベル V F 0 、消去ベリファイレベル V F 1 、及び電荷交換能力による初期データに対する読み出し電圧 B R 、「 0 」ベリファイレベル B V 0 、「 1 」ベリファイレベル B V 1 とが示される。

【 0 0 2 4 】

図 1 に示したメモリセルは、いずれの場合も、プログラムされることによりフローティングゲートに電子が注入されて閾値電圧が高いデータ「 0 」の状態と、消去されることによりフローティングゲートの電子が引き抜かれて閾値電圧が低いデータ「 1 」の状態とを持つ。即ち、分布 Q 1 のメモリセルは、その閾値電圧が「 0 」書き込みのベリファイレベル V F 0 より高い状態である。更に、分布 Q 2 , Q 3 のメモリセルは、その閾値電圧が「 1 」消去のベリファイレベル V F 1 よりも低い状態である。従って、通常の読み出し電圧 V R をコントロールゲート C G に印加することにより、記憶されたデータに従って、メモリセルを導通と非導通状態に区別することができる。

【 0 0 2 5 】

更に、メモリセル Q 2 , Q 3 に一旦「 0 」書き込みを行い、その後フローティングゲートから電子を引き抜く消去パルスを同じだけ印加すると、両メモリセルの電荷引き抜き能力の違いにより、メモリセル Q 2 は、図 2 中の閾値電圧が高い分布に含まれ、メモリセル Q 3 は、図 2 中の閾値電圧が低い分布に含まれる。これらの閾値の違いを利用し、別の読み出し電圧 B R をコントロールゲートに印加することにより、電荷交換能力の違いにより記憶されたデータに従って、メモリセルを導通と非導通状態に区別することができる。

10

20

30

40

50

## 【0026】

即ち、全面書き込み後に全面消去した状態では、電荷交換能力に応じた記憶データを読み出すことができ、通常のプログラムまたは消去された状態の記憶データも、通常の読み出し電圧VRを印加することにより読み出すことができる。そして、通常のプログラム動作をした後でも、全面書き込み後に全面消去を行うことで、電荷交換能力に応じた記憶データを復活させることができる。

## 【0027】

図1のメモリセルQ2, Q3は、フローティングゲートへの電子の注入能力の違いを利用して、永久に保存しておきたいデータを記憶させることも可能である。

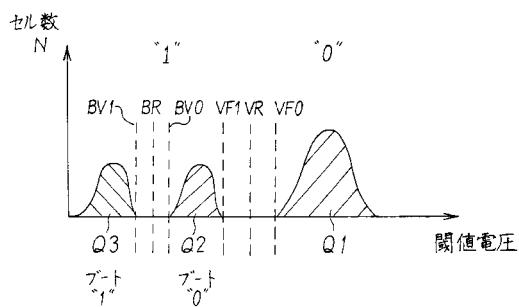

## 【0028】

図3は、電子の注入能力の違いを利用してした場合の閾値電圧の分布を示す図である。この例では、通常の書き込みによりデータ「0」が記憶された状態が、分布Q2, Q3のメモリセルであり、通常の消去によりデータ「1」が記憶された状態が、分布Q1のメモリセルである。これらのデータは、通常の読み出し電位VRをコントロールゲートに印加することで読み出し可能である。

## 【0029】

そして、上書きされた初期データを復活させる為には、両メモリセルQ2, Q3に対して同様に消去を行い、図3のQ1の分布の状態から、両メモリセルQ2, Q3に対して同じだけの書き込みパルスを印加する。その場合、メモリセルQ2は電子の注入能力が低く閾値電圧の変化が小さいのに対して、メモリセルQ3は電子の注入能力が高く閾値電圧の変化が大きい。その閾値電圧の変化の差を利用して、読み出し電位BRをコントロールゲートに印加することで、初期データを読み出すことができる。

## 【0030】

この様に、電荷交換能力と称する場合、本実施の形態例においては、フローティングゲートから電子を引き抜く能力、または電子を注入する能力という意味が含まれる。そして、例えばチャネル領域の不純物濃度を異ならせることで、電子を引き抜く能力、または注入する能力を異ならせることができる。

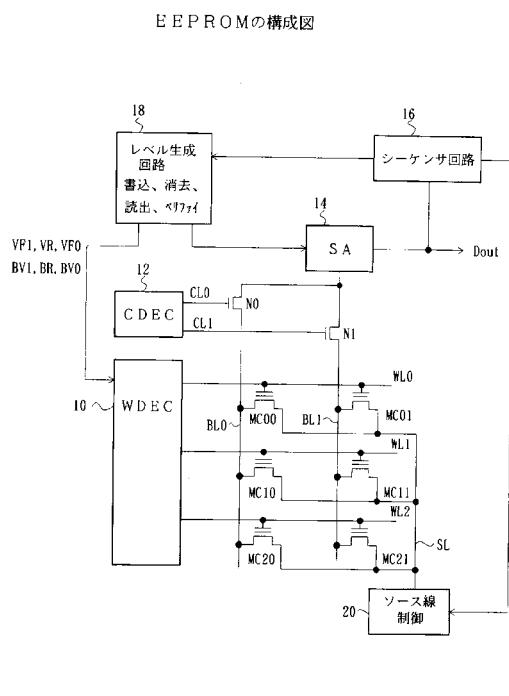

## 【0031】

図4は、本実施の形態例のフラッシュメモリの構成図である。このフラッシュメモリは、フローティングゲートを有するEEPROMで構成される。複数のワード線WL0~WL2と複数のビット線BL0, BL1との交差位置に、フローティングゲートを有するメモリセルMC00~MC21が設けられる。メモリセルのコントロールゲートはワード線WL0~WL2に接続され、ドレインはビット線BL0, 1に接続され、ソースは共通のソース線SLに接続される。

## 【0032】

ワード線WLは、ワードデコーダ10により選択され、レベル生成回路18から与えられる電位に駆動される。また、ビット線BLは、コラムゲートトランジスタN0, 1を介して、センスアンプ14に接続される。コラムデコーダ12により選択されるコラム選択信号CL0, 1に応答して、コラムゲートトランジスタN0, 1のいずれかが導通し、ビット線BLに流れる電流状態が、センスアンプ14により検出される。ソース線SLは、ソース線制御回路20により所定の電位に制御される。

## 【0033】

シーケンサ回路16は、フラッシュメモリの書き込み(プログラム)、消去、読み出し動作の制御を、レベル生成回路18とソース線制御回路20などに対して行う。また、シーケンサ回路16は、初期データ復活の為の全面書き込み、消去、読み出し動作の制御を行う。この場合の読み出し動作におけるワード線WLの電位BRは、通常の読み出し時の読み出し電圧VRとは異なる。更に、ワード線に印加される書き込みペリファイレベルや消去ペリファイレベルも、図2, 3に示した通り異なる。

## 【0034】

図5は、初期データを復活する場合の閾値分布の変化を示す図である。図5の例は、上記

10

20

30

40

50

の図 2 の場合に適用される。図 4 に示したフラッシュメモリにおいて、例えば、メモリセル M C 00 を図 2 のセル Q 2 のような電荷交換能力が低い状態にし、メモリセル M C 01 を図 2 のセル Q 3 のような電荷交換能力が高い状態にする。即ち、メモリセル M C 00、M C 01 には、初期データ「0, 1」が記憶される。それ以外のメモリセル M C 10 ~ M C 21 は、セル Q 3 の状態にする。従って、上記した例では、メモリセル M C 00 のチャネル領域に P 型の不純物をイオン注入する。残りのメモリセルは、従来と同様の構成にする。

#### 【0035】

通常の書き込みまたは消去は、フローティングゲート F G に電子を注入して閾値電圧を高くし、または電子を引き抜いて閾値電圧を低くする。その場合のベリファイレベルは、図 2 に示される「0」ベリファイレベル V F 0 と「1」ベリファイレベル V F 1 とが利用される。

10

#### 【0036】

メモリセル M C 00, M C 01 に対しても書き込み動作を行って、最初の初期データが失われたとする。この初期データ「0, 1」を復活するために、図 5 (A) に示される通り、先ず全面に書き込みを行い、閾値電圧を書き込みベリファイレベル V F 0 以上にする。次に、図 5 (B) に示される通り、復活したい初期データが記憶されたメモリセル M C 00, M C 01 に対して、同じ消去パルスを印加する。その結果、両メモリセルは電子の引き抜き能力の違いから、メモリセル M C 01 はより低い閾値電圧に変化し、メモリセル M C 00 はそれより高い閾値電圧に変化する。

#### 【0037】

更に、消去パルスを印加し続けると、図 5 (C) に示した如く閾値電圧の違いは大きくなりながら低下し、最後に、図 5 (D) に示した通り、メモリセル M C 01 の閾値電圧はベリファイレベル B V 1 よりも低く、メモリセル M C 00 の閾値電圧はベリファイレベル B V 0 よりも高くなる。

20

#### 【0038】

そこで、ワード線 W L 0 に読み出し電圧 B R を印加すると、メモリセル M C 00 は導通せず、メモリセル M C 01 は導通する。この導通、非導通によるビット線の電流によって、センスアンプ 1 4 は初期データを検出することができる。

#### 【0039】

上記の例では、図 5 (D) の状態で初期データを読み出す。従って、初期データを読み出すためには、通常の読み出しレベル V R やベリファイレベル V F 0, V F 1 とは異なるレベル B R, B V 0, B V 1 などを生成する必要がある。そのためには、センスアンプ 1 4 内の図示しないレファレンス用のトランジスタも増やす必要がある。

30

#### 【0040】

初期データの別の読み出し方法として、図 5 (B) に示される状態で、消去ベリファイレベル V F 1 を利用して、読み出しを行うこともできる。但し、その場合は、初期データが書き込まれたメモリセルの閾値電圧の分布の重なりが存在するので、読み出されたデータにエラーが含まれる可能性が高い。そこで、その場合は、初期データの記憶に加えて誤り訂正コード (ECC) も記憶させることで、かかるエラーの発生を防止することができる。単に誤り検出を行うパリティコードだけでなく、誤りを訂正できるコードを追加して記憶させることがほしい。

40

#### 【0041】

また、図 5 (D) の状態で両分布に重なりが存在する場合も、上記と同様に誤り訂正コードを利用して、読み出しデータのエラーの発生を防止することができる。

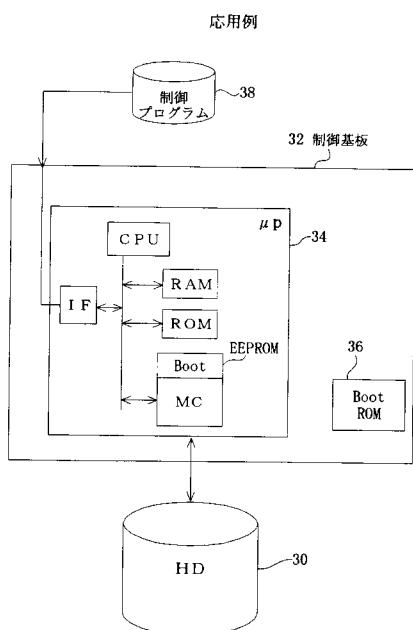

#### 【0042】

図 6 は、本実施の形態例のフラッシュメモリの応用例を示す図である。この応用例は、ハードディスクなどの大容量記録媒体 3 0 の制御用のマイクロプロセッサ 3 4 内に、フラッシュメモリ (EEPROM) を内蔵させた例である。ハードディスク 3 0 の制御基板 3 2 上に、制御用のマイクロプロセッサ 3 4 が搭載される。このマイクロプロセッサ 3 4 内は、CPU、RAM、ROM に加えてフラッシュメモリ EEPROM が内蔵される。そして、フラ

50

ツシュメモリ内には制御プログラムをダウンロードする時に起動するブートプログラムBootが格納される。このブートプログラムは、上書きされた後も復帰可能なメモリセル領域に書き込まれている。また、フラッシュメモリには、通常のメモリセル領域MCも含まれる。

#### 【0043】

そして、かかる制御用のマイクロプロセッサ34に、開発された制御用プログラム38がフラッシュメモリEEPROM内にダウンロードされる。ダウンロードのために、CPUがフラッシュメモリ内に格納されたブートプログラムを起動し、そのブートプログラムを実行する。このブートプログラムの実行に応答して、開発された制御プログラム38がフラッシュメモリにダウンロードされる。この場合、制御プログラム38はフラッシュメモリの容量程度のデータ量を有し、ダウンロードに際しブートプログラムBoot領域上にも上書きされる。

#### 【0044】

そこで、ダウンロード済の制御プログラムに変更を与える必要がある場合は、初期データであるブートプログラムの情報を復活させる必要がある。通常、マイクロプロセッサ34を電装基板32に搭載した後は、外付けのライターを利用して書き込むことができないからである。

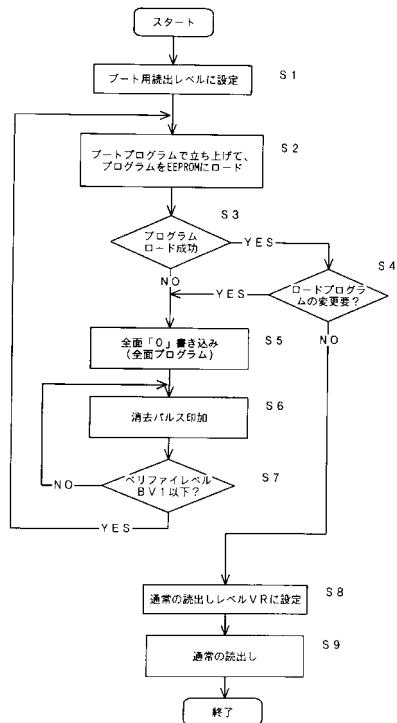

#### 【0045】

図7は、図6の応用例において、ブートプログラムを復活させる時のフローチャート図である。フラッシュメモリは、図5(D)の状態にあり、初期データとしてブートプログラムが格納されている。最初は、フラッシュメモリ内のブートプログラムを読み出すために、ブートデータの読み出しのための読み出しレベルBRに設定する(S1)。次に、CPUはブートプログラムを読み出して、制御プログラム38をダウンロードする(S2)。このダウンロードが成功しない場合(S3)、または成功してもあとでプログラムの変更が必要になる場合(S4)、フラッシュメモリのブートプログラム記憶領域について、全面書き込みを実行する(S5)。その結果、図5(A)の状態になる。

#### 【0046】

そして、その領域に消去パルスを少しづつ印加し(S6)、所定のベリファイレベル以下になるまで消去を実行する(S7)。その結果、図5(D)の状態に復活させることができる。そして、再度、ブートプログラムを読み出して実行することにより、変更すべき制御プログラムまたはダウンロードを失敗した制御プログラム38を再度ダウンロードする。

#### 【0047】

制御プログラムのダウンロードが成功し、制御プログラムの変更が不要になると、フラッシュメモリは、通常の読み出し動作が行われる。そのために、通常の読み出しレベルに設定され(S8)、通常の読み出しが行われる(S9)。

#### 【0048】

以上の通り、本実施の形態例のフラッシュメモリを利用することにより、重ね書きされた初期データを簡単に復活することができる。従って、ブートプログラム等の最初の段階においてだけ使用され後に上書きされるプログラムやデータを記録する場合に、有効である。

#### 【0049】

##### 【発明の効果】

以上、本発明によれば、初期データが格納されている領域に別のデータが上書きされても、簡単に初期データを復活させることができる不揮発性半導体記憶装置が提供される。

##### 【図面の簡単な説明】

【図1】本実施の形態例の電荷交換能力が異なるメモリセルの例を示す断面図である。

【図2】電荷交換能力の異なるメモリセルと通常のプログラム状態または消去状態のメモリセルの閾値分布を示す図である。

【図3】電子の注入能力の違いを利用した場合の閾値電圧の分布を示す図である。

10

20

30

40

50

【図4】本実施の形態例のフラッシュメモリの構成図である。

【図5】初期データを復活する場合の閾値分布の変化を示す図である。

【図6】本実施の形態例のフラッシュメモリの応用例を示す図である。

【図7】図6の応用例において、ブートプログラムを復活させる時のフローチャート図である。

【符号の説明】

|           |                 |

|-----------|-----------------|

| M C       | メモリセル           |

| C G       | コントロールゲート       |

| F G       | フローティングゲート      |

| Q 2 , Q 3 | 電荷交換能力が異なるメモリセル |

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 29/788 (2006.01)

H 01 L 29/78 371

H 01 L 29/792 (2006.01)

(56)参考文献 特開平10-308462 (JP, A)

特開平08-180696 (JP, A)

特開平11-265993 (JP, A)

特開平05-275657 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02

G11C 16/04

H01L 27/115

G06F 11/00

G06F 9/06