## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) Int. Cl.<sup>6</sup>

H04N 9/64

(45) 공고일자 1999년07월 15일

(11) 등록번호 10-0208552

(24) 등록일자 1999년04월 16일

|            |                                                              |             |                |

|------------|--------------------------------------------------------------|-------------|----------------|

| (21) 출원번호  | 10-1996-0035943                                              | (65) 공개번호   | 특 1997-0014408 |

| (22) 출원일자  | 1996년08월28일                                                  | (43) 공개일자   | 1997년03월29일    |

| (30) 우선권주장 | 8/523,396 1995년08월31일 미국(US)                                 |             |                |

| (73) 특허권자  | 제너럴 인스트루먼트 코오포레이션 오브 델라웨어<br>미국 펜실베니아 핫보로 바이베리 로드 2200       | 로버트 에이. 스코트 |                |

| (72) 발명자   | 도날드 에스. 버틀러<br>미국 애리조나 스콧츠데일 노스 93 스트리트 22400<br>리차드 에스. 아마노 |             |                |

| (74) 대리인   | 미국 애리조나 스콧츠데일 이스트우드 드라이브 9409<br>나영환, 이상섭                    |             |                |

**심사관 : 김희고****(54) 막싱된 YUV 및 컬러 파렛트화된 비디오 신호를 처리하는 장치****요약**

본 발명의 장치는 그래픽 메모리에 하나이상의 스프라이트의 제1 및 제2필드를 기억함으로써 비율주사식 NTSC 또는 PAL 텔레비전 수상기상에 디스플레이하기 위해 막싱된 YUV 및 컬러 파렛트화된 비디오 신호를 처리한다. 스프라이트는 YUV 또는 컬러 파렛트화된 데이터로서 기억되며, 각 스프라이트에는 우선순위가 주어진다. 스프라이트가 겹쳐질때 높은 우선순위의 스프라이트는 낮은 우선순위의 스프라이트의 픽셀 데이터위에 겹쳐 쓴다. 제1 및 제2필드의 픽셀 데이터의 제1 및 제2인접 수평 라인은 각 라인 주기 동안 픽셀 어셈블리 버퍼의 제1 및 제2더블 버퍼 각각에 동시에 기억된다. 자연 버퍼 및 제1 및 제2더블 버퍼는 픽셀 어셈블리 버퍼의 출력에서 픽셀 데이터의 제1, 제2 및 제3인접 수평 라인을 각각 발생하고, 픽셀 데이터의 제3 및 제4인접 수평 라인이 제1 및 제2더블 버퍼로 입력된다. 컨벌빙 수단은 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3출력 신호를 수신하여 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있을때 텔레비전 수상기로의 전송을 위해 미리 결정된 소정의 픽셀 데이터의 매트릭스의 중심 픽셀에 가중 평균을 제공하는 출력신호를 발생한다. 라이브 비디오 신호는 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있지 않을때 텔레비전 수상기의 디스플레이로 전송된다.

**대표도****명세서****도면의 간단한 설명**

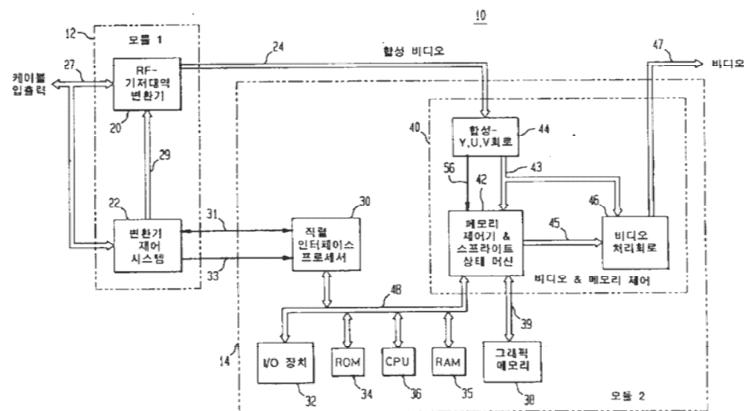

제1도는 본 발명에 따른 가입자 케이블 박스 유닛의 블록도.

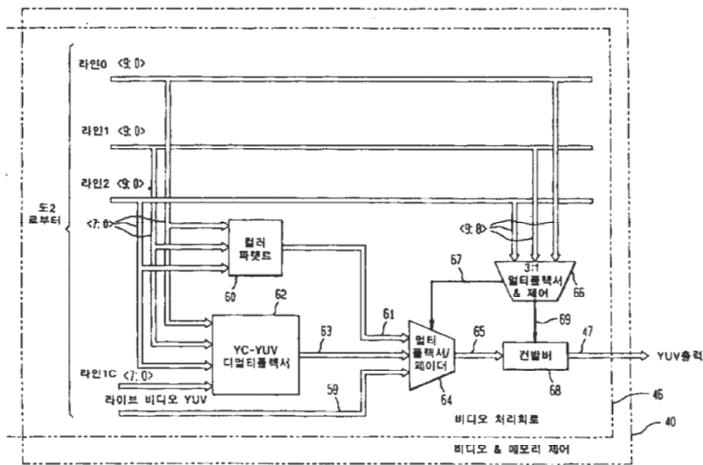

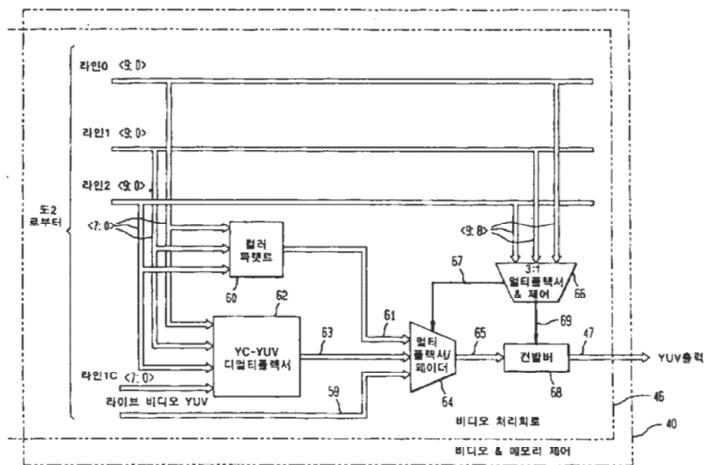

제2도는 본 발명에 따라 제1도의 가입자 케이블 박스 유닛에 설치된 비디오 처리회로의 제1부의 블록도.

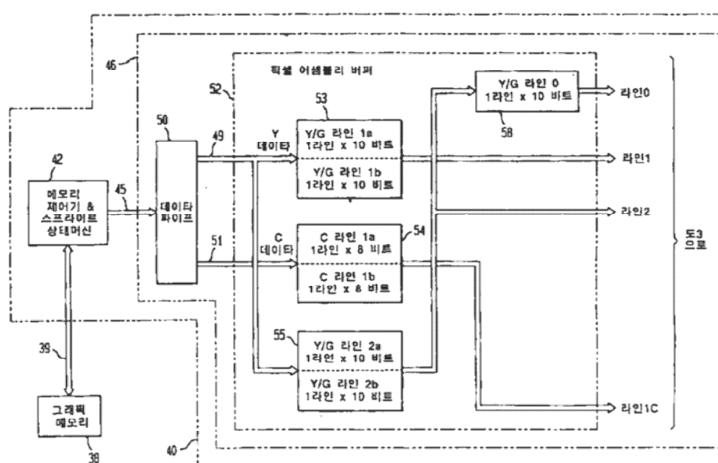

제3도는 본 발명에 따라 제1도의 가입자 케이블 박스 유닛에 설치된 비디오 처리 회로의 제2부의 블록도.

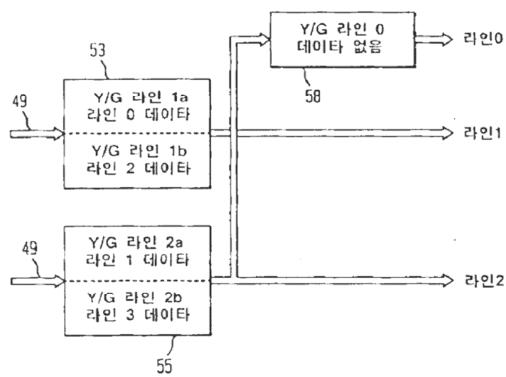

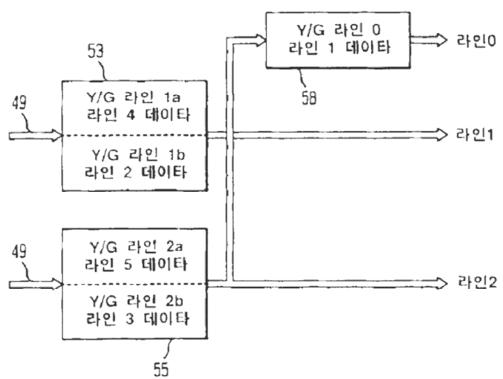

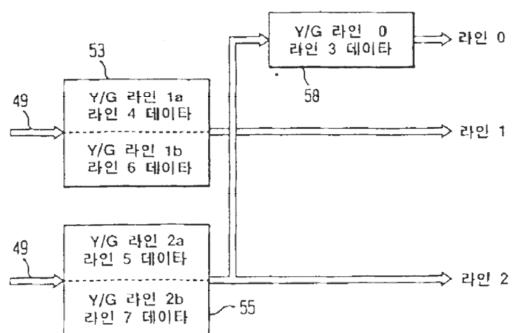

제4도, 제5도 및 제6도는 본 발명에 따라 제3도의 비디오 처리회로의 제1부의 일부분을 형성하는 픽셀 어셈블리 버퍼의 동작을 설명하는 도면.

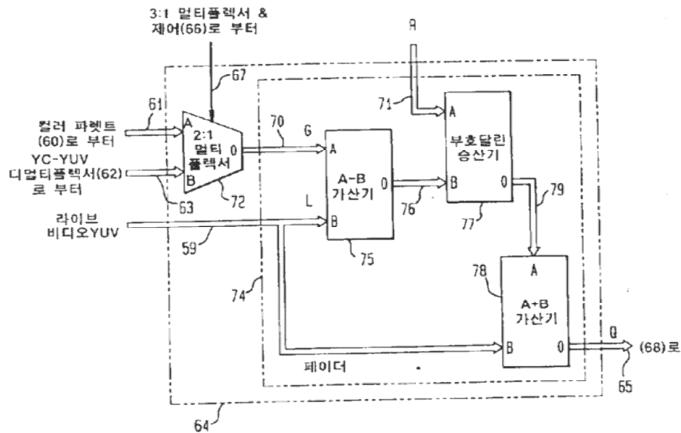

제7도는 제3도에 도시한 비디오 처리 회로의 제2부의 일부분을 형성하는 예시적인 멀티플렉서/페이더의 블록도.

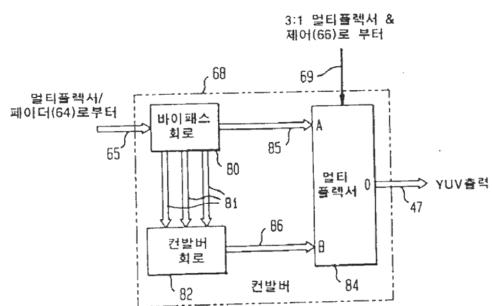

제8도는 제3도에 도시한 비디오 처리회로의 제2부의 일부분을 형성하는 컨발버의 예시적인 구성에 대한 블록도.

#### \* 도면의 주요부분에 대한 부호의 설명

|                                      |                        |

|--------------------------------------|------------------------|

| 10 : 가입자 케이블 박스 유닛                   | 30 : 직렬 인터페이스 프로세스     |

| 38 : 그래픽 메모리                         | 40 : 비디오 및 메모리 제어 집적회로 |

| 42 : 메모리 제어기 및 스프라이트 상태 머신           |                        |

| 46 : 비디오 처리회로                        | 50 : 데이터 파이프           |

| 52 : 픽셀 어셈블리 버퍼                      | 53,54,55 : 더블 라인 버퍼    |

| 60 : 컬러 파렛트 회로                       |                        |

| 64 : 멀티플렉서/페이더(multiplexer/fader) 회로 | 68 : 컨발버(convolver)    |

#### 발명의 상세한 설명

##### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 본 발명의 양수인에게 양도되었으며 발명자가 동일하며 동일자로 출원되어 함께 계류중인 2차원 비디오 콘볼빙 실행 방법 및 장치라는 명칭의 미국 특허 출원 제08/523,395(G1D872)호, 비디오 확대 장치라는 명칭의 미국 특허 출원 제08/523,789(G1D907) 호 및 TV 수상기를 위한 비디오 그래픽 처리에 관련하여 메모리 제어 테이블을 사용하는 장치라는 명칭의 미국 특허 출원 제08/523,394(G1D908) 호와 관련된다.

본 발명은 막상된 YUV 및 컬러 파렛트화된 그래픽 비디오 신호를 처리하고 상기 그래픽 비디오 신호를 독립적으로 디스플레이하거나 요망될시에 원격 소스로부터 수신된 라이브 텔레비전 신호상에 상기 막상된 그래픽 비디오 신호를 중첩시키는 장치에 관한 것이다.

개인용 컴퓨터와 같이 일부 상업적으로 유용한 컴퓨터는 합성 비디오 신호(예컨대, 전국 텔레비전 표준 위원회 신호:National Television Standard Committee signal)와 통상적으로 적색, 녹색, 청색(RGB)와 같은 컴퓨터에서 발생된 비디오 그래픽 디스플레이 신호를 융합시키는 회로를 제공한다. 특히, 근래 비디오 그래픽 장치는 배경, 문자, 기호 및 다른 회화적 표현을 할 수 있으며 작동자가 선택한 크기, 모양 및 컬러로 배치할 수 있는 능력을 가지고 있다.

1988년 4월 12일에 등록된 미국 특허 제4,737,772호(Nishi et al.)는 비디오 디스플레이 프로세서(VDP), 중앙처리장치(CPU), 메모리 및 비디오 랜덤 액세스 메모리(VRAM)를 포함하는 비디오 디스플레이 제어기를 개시하고 있다. 메모리는 CPU에 의해 실행되는 프로그램과 다양한 종류의 이미지 데이터를 기억한다. VRAM은 VDP에 의해 변경되어 음극선관(CRT) 표시장치의 스크린상에 디스플레이하기 위해 외부로 전송되는 이미지 데이터를 기억한다. VDP에서, 타이밍 신호 발생기는 이미지 데이터 처리회로(IDPC)에서 처리하는 데이터를 동기화시키어 CRT 표시장치의 스크린상에 처리된 데이터를 정확하게 디스플레이하기 위해 수평 및 수직 카운터 및 CRT 표시장치에 의해 사용되며 디스플레이될 화상의 화소를 정확하게 주사하는 타이밍 신호를 발생한다. 비디오 디지타이저(digitizer)는 외부에서 공급된 아날로그 비디오 신호를 샘플링하고 상기 아날로그 비디오 신호의 신호 레벨 또는 진폭을 2 또는 4비트로 구성된 디지털 데이터로 변환한다. 비디오 디지타이저에 의해 디지털화된 진폭 출력 데이터는 정지 이미지를 표현하며 IDPC로 공급된다. IDPC는 비디오 디지타이저 출력 데이터 및 CPU로부터 공급된 컬러 코드를 인터페이스 회로를 통하여 VRAM에 선택적으로 기억한다. CPU로부터의 각 컬러 코드는 스크린상의 정지 이미지를 구성하는 각각의 화소(즉, 픽셀)의 컬러를 나타낸다. 동작시, CPU로부터의 디스플레이 명령에 응답하여 IDPC는 CRT 표시장치상의 주사위치와 동기하여 VRAM으로부터 도트 데이터를 순차적으로 판독하고 상기 도트 데이터를 컬러 파렛트 회로로 출력한다. 이와 동시에, IDPC는 VRAM으로부터의 애니메이션 이미지를 디스플레이하는데 필요한 데이터를 계산하여 판독하고 컬러 코드를 컬러 파렛트 회로에 공급한다. 애니메이션 이미지 및 정지 이미지가 CRT 표시장치의 스크린상의 동일한 디스플레이 위치에 위치하면 애니메이션 이미지는 완벽하게 디스플레이된다. 컬러 파렛트 회로는 각 컬러 코드를 각각 3비트로 된 적색, 녹색 및 청색에 대한 3개의 컬러 데이터로 변환한다. 디지털/아날로그 변환기(DAC)는 컬러 파렛트 회로로부터의 컬러 데이터를 CRT 표시장치에 제공되는 R, G 및 B 신호로 변환한다. 1994년 10월 11일에 등록된 미국 특허 제5,355,175호(Okada et al.)는 하나의 이미지 평면에서 복수의 막상비로 그래픽 비디오 이미지와 재생 비디오 이미지를 막상하는 비디오 막상 장치를 개시하고 있다. 재생 비디오 신호의 적어도 한 라인과 그래픽 비디오 신호와의 막상비를 나타내는 페이드 데이터는 미리 결정된 소정의 순서에 따라 순차적으로 발생된다. 페이드 데이터는 헐딩 수단에서 유지되어 수평 동기신호와 동기하여 헐딩 수단으로부터 출력된다. 재생 비디오 신호 및 그래픽 비디오 신호의 레벨은 헐딩 수단으로부터 출력된 페이드 데이터에 따라 개별적으로 조절되며 상기 조절된 신호는 서로 합쳐진다. 재생 비디오 신호와 그래픽 비디오 신호는 하나의 이미지 평면상에서 매라인마다 설정된 막상비로 막상되어 상기 장치로부터의 비디오 출력 신호를 생성한다.

1983년 12월 13일에 등록된 미국 특허 제4,420,770호(Rahman)는 조작자가 선택한 비디오 속성을 갖는 사각형의 비디오 패턴을 발생시키는 비디오 배경 발생 시스템을 개시하고 있다. 상기 시스템은 수평 비트 메모리 및 수직 비트 메모리를 포함하는데, 각 메모리는 16개의 배경 엔티티에 대한 정보를 기억하는 16 엔티티 메모리이다. 각 배경 엔티티용 메모리는 스크린상의 엔티티에 대한 배경 영역의 대향 코너를 정의한다. 제2도에 도시된 바와같이, 제1엔티티는 제1사각형 영역을 정의하고 높은 우선순위의 제2엔티티는 부분적으로 겹쳐진 제2사각형 영역을 정의한다. 속성 조사 테이블은 엔티티에 대한 컬러 비디오 출력(적색, 녹색, 청색)에 관계된 각 엔티티에 대한 정보를 기억한다. 생성되고 있는 화상의 라인을 주사하는 동안, 제1엔티티는 자신의 정의된 영역에서 생성되고, 제2엔티티도 자신의 정의된 영역에서 생성된다. 그러나, 제2엔티티는 높은 우선순위를 가지므로 두 엔티티의 겹쳐진 영역은 기억된 제2엔티티의 속성에 의해 표현된다.

1986년 4월 1 일 등록된 미국 특허 제4,580,165호(Patton et al.)는 컬러 그래픽 모듈을 외부에서 수신된 비디오 신호와 수평 및 수직으로 동기화하는 그래픽 비디오 오버레이(overlay) 시스템을 개시하고 있다. 특히, 상기 시스템은 비디오 이미지상에 놓이는 그래픽 이미지를 제공하기 위해 서로 결합된 컬러 그래픽 모듈 및 비디오 막상 모듈을 포함한다. 컬러 그래픽 모듈은 컬러 그래픽 수평 및 수직 동기 필스를 생성하는 타이밍 수단을 포함한다. 비디오 막상 모듈은 비디오 디코더 및 동기 프로세서 수단을 포함한다. 비디오 디코더는 외부에서 수신된 비디오 신호를 적색, 녹색 및 청색(RGB) 성분으로 분리하여 외부 비디오 합성 동기 신호를 발생한다. 동기 프로세서 수단은 컬러 그래픽 신호를 비디오 합성 동기 신호와 수평 및 수직으로 동기화하는 수평 및 수직 동기 프로세서 수단을 포함한다. 수평 동기 프로세서 수단은 외부 비디오 합성 동기 신호를 필터링하여 위상 조절 가능한 처리된 수평 동기 필스를 발생한다. 수직 동기 프로세서 수단은 비디오 이미지와 컬러 그래픽 이미지를 수직으로 동기화하기 위한 외부 비디오 수직 동기 신호를 발생하기 위해 외부 비디오 합성 동기 신호를 이용한다. 멀티플렉서는 비디오 이미지와 컬러 그래픽 이미지를 결합하여 합성 이미지 출력 신호를 제공한다.

현재, 완전히 새로운 종류의 서비스가 케이블 텔레비전 네트워크를 통하여 가정에 전달될 수 있도록 할 수 있는 대화형 비디오 그래픽에 대한 필요성이 부상되고 있다. 이러한 새로운 서비스는 향상된 서비스를 제공하면서 종래의 많은 텔레비전 프로그램에 대한 시청 경험을 증대시키게 된다. 그러나, NTSC 및 위상 교호 라인(PAL) 텔레비전 수상기는 컴퓨터 모니터와는 달리 매우 낮은 비디오 대역폭을 가지며, 점진적인 주사가 아닌 비율주사식 디스플레이를 사용한다. 이러한 제한사항은 인공물을 없는 고해상도의 합성 비디오 신호의 발생을 매우 제한하게 된다. 통상적으로, 비디오 게임기와 같은 소비자는 저해상도의 비비율주사식(non-interlaced) 비디오 신호를 발생시킴으로써 이러한 문제점들을 피한다. 이러한 방법은 저화질의 이미지가 농담이 고르지않게 되는(blocky) 현상이 나타나며 컬러 선택에서도 제한되며 만화 같은 형상을 띠는 이미지가 되게 한다. 방송용 화질에 근접하는 합성 비디오 신호의 생성은 발생된 합성 신호가 장면을 주사하는 비디오 카메라의 합성 신호를 에뮬레이팅하고 상기 비디오 카메라 신호를 위한 아날로그 신호 처리를 필요로 한다. 따라서, 표준 NTSC 또는 PAL 표준 비율주사식 텔레비전 수상기 상에서 시청하기 위해 양질의 합성 비디오 그래픽이 라이브 텔레비전 프로그래밍의 최상부상에 오버레이될 수 있도록 하는 비교적 값싼 장치를 제공하는 것이 바람직하다.

### 발명이 이루고자 하는 기술적 과제

본 발명은 막상된 YUV 및 컬러 패랫화된 그래픽 비디오 신호를 처리하고 상기 비디오 신호를 독립적으로 디스플레이하거나 요망될시에 비율주사식 텔레비전 수상기 상에서 원격 소스로부터 수신된 라이브 텔레비전 신호상에 상기 막상된 그래픽 비디오 신호를 중첩시키는 장치를 제공하는 것이다.

### 발명의 구성 및 작용

본 발명의 한 측면에서, 본 발명은 표준 비율주사식 텔레비전 수상기상에 디스플레이하기 위해 막상된 비디오 및 그래픽 신호를 처리하는 장치이다. 상기 장치는 버퍼링 및 프로세싱 수단과 컨벌빙(convolving) 수단을 포함한다. 버퍼링 및 프로세싱 수단은 표준 비율주사식 텔레비전 수상기의 독립적으로 선택된 소정의 디스플레이 영역에 선택적으로 디스플레이될 하나이상의 각 스프라이트의 제1 및 제2필드로부터 스프라이트 픽셀 데이터의 제1 및 제2수평라인의 수신에 응답한다. 버퍼링 및 프로세싱 수단은 하나이상의 각 스프라이트의 제1 및 제2필드로부터의 스프라이트 픽셀 데이터로부터 텔레비전 수상기상에 디스플레이하기 위한 화상의 인접하는 3개의 수평라인에 대한 순차적인 스프라이트 픽셀 데이터를 포함하는 제1, 제2 및 제3출력 신호를 발생한다. 상기 제1, 제2 및 제3출력 신호의 발생시, 스프라이트들이 텔레비전 수상기상의 디스플레이 영역상에서 겹치게 될때 최상위 우선수위 스프라이트에 대한 픽셀 데이터는 언제든지 제1, 제2 및 제3출력신호의 각 픽셀 위치로 출력된다. 또한, 제1 및 제3 출력 신호는 제1 및 제2필드중 하나의 라인에 대한 스프라이트 픽셀 데이터를 포함하고, 제2출력 신호는 제1 및 제2필드중 나머지 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고 스프라이트 데이터가 트루 컬러 포맷(true color format)에 관련될때 색도 데이터를 포함한다. 컨벌빙 수단은 버퍼링 및 프로세싱 수단으로부터 제1, 제2 및 제3출력신호를 수신하여 미리 결정된 소정의 픽셀 데이터 매트릭스의 중심 픽셀에 가중 평균을 제공하는 출력신호를 발생한다. 상기 출력 신호는 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있을때 텔레비전 수상기로 전송되며, 상기 중심 픽셀은 버퍼링 및 프로세싱 수단으로부터의 제2출력 신호의 일부분이다. 또한, 컨벌빙 수단은 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있지 않을때 라이브 비디오 신호를 텔레비전 수상기의 디스플레이로 전송한다.

또 다른 측면에서, 본발명은 표준 비율주사식 텔레비전 수상기상에 디스플레이하기 위해 막상된 비디오 및 그래픽 신호를 처리하는 장치이다. 상기 장치는 디지털 메모리 수단, 버퍼링 및 프로세싱 수단 및 컨벌빙 수단을 포함한다. 디지털 메모리 수단은 표준 비율주사식 텔레비전 수상기의 선택된 소정의 디스플레이 영역에 선택적으로 디스플레이될 하나이상의 각 스프라이트에 대한 스프라이트 데이터를 포함하는 출력 신호를 기억하여 연속적으로 전송한다. 스프라이트 데이터는 텔레비전 수상기상에 디스플레이될 스프라이트 화상의 제1 및 제2필드에 대한 트루 컬러 비디오 또는 컬러 패랫 데이터 포맷중 하나를 포함하며, 하나이상의 스프라이트가 존재할때 하나이상의 각 스프라이트는 미리 결정된 소정의 우선

순위를 갖는다. 버퍼링 및 프로세싱 수단은 디지털 메모리 수단으로부터의 출력신호에 응답하여 제1, 제2 및 제3출력 신호를 발생한다. 이 세 출력 신호는 텔레비전 수상기상에 디스플레이하기 위한 화상의 인접하는 3 수평라인에 대한 순차적인 스프라이트 픽셀 데이터를 포함한다. 또한, 스프라이트들이 텔레비전 수상기상의 디스플레이 영역상에서 겹쳐질때 최상위 우선순위의 스프라이트에 대한 픽셀 데이터는 제1, 제2 및 제3출력 신호의 각 픽셀 위치를 향해 언제든지 출력된다. 또한, 제1 및 제3출력 신호는 제1 및 제2필드중 한 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하여, 제2출력 신호는 제1 및 제2필드중 다른 한 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고 상기 스프라이트 데이터는 트루 컬러 포맷과 관련될때 색도 데이터를 포함한다. 컨발빙 수단은 버퍼링 및 프로세싱 수단으로부터 제1, 제2 및 제3출력신호를 수신하여 텔레비전 수상기로 전송하기 위해 미리 결정된 소정의 픽셀 데이터의 매트릭스의 중심 픽셀에 가중 평균을 제공하는 출력신호를 발생한다. 이 출력 신호는 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있을때 텔레비전 수상기로 전송되며, 중심 픽셀은 버퍼링 및 프로세싱 수단으로부터의 제2출력 신호의 일부분이다. 또한, 컨발빙 수단은 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있지 않을때 라이브 비디오 신호를 텔레비전 수상기의 디스플레이로 전송한다.

또다른 측면에서, 본 발명은 표준 비율주사식 텔레비전 수상기상에 디스플레이하기 위해 익상된 비디오 및 그래픽 신호를 처리하는 장치이다. 상기 장치는 디지털 메모리 수단, 메모리 제어기, 버퍼링 및 프로세싱 수단 및 컨발빙 수단을 포함한다. 디지털 메모리 수단은 표준 비율주사식 텔레비전 수상기의 선택된 소정의 디스플레이 영역에서 선택적으로 디스플레이될 하나이상의 각 스프라이트에 대한 스프라이트 데이터를 포함하는 스프라이트 데이터를 기억하여 상기 스프라이트 데이터를 포함하는 출력 신호를 전송한다. 스프라이트 데이터는 텔레비전 수상기상에 디스플레이될 스프라이트 화상의 제1 및 제2필드에 대한 트루 컬러 비디오 또는 컬러 패랫트 데이터 포맷중 하나를 포함하며, 하나이상의 스프라이트가 존재할때 하나이상의 각 스프라이트는 미리 결정된 소정의 우선순위를 갖는다. 메모리 제어기는 제1 및 제2필드의 스프라이트 데이터가 디지털 메모리 수단의 소정의 위치로 판독되게 하여 제1필드의 스프라이트 데이터의 수평 라인 및 제2필드의 스프라이트 데이터의 인접한 라인을 포함하는 메모리 출력 신호로서 디지털 메모리 수단으로부터 선택적으로 판독되게 한다. 버퍼링 및 프로세싱 수단은 메모리 제어기로부터의 메모리 출력신호에 응답하여 텔레비전 수상기상에 디스플레이하기 위한 화상의 인접한 세 수평 라인에 대한 순차적인 스프라이트 픽셀 데이터를 포함하는 제1, 제2 및 제3출력신호를 발생한다. 또한, 스프라이트들이 텔레비전 수상기상의 디스플레이 영역상에서 겹쳐질때 최우선순위의 스프라이트에 대한 픽셀 데이터는 언제든지 제1, 제2 및 제3출력신호의 각 픽셀 위치로 출력된다. 또한, 제1 및 제3출력신호는 제1 및 제2필드중 한 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고, 제2출력신호는 제1 및 제2필드중 나머지 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하며 스프라이트 데이터가 트루 컬러 포맷과 관련될때 색도 데이터를 포함한다. 컨발빙 수단은 버퍼링 및 프로세싱 수단으로부터 제1, 제2 및 제3출력신호를 수신하여 텔레비전 수상기로 전송하기 위해 미리 결정된 소정의 픽셀 데이터 매트릭스중 중심 픽셀에 가중 평균을 제공하는 출력 신호를 발생한다. 이 출력 신호는 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있을때 텔레비전 수상기로 전송되며, 중심 픽셀은 버퍼링 및 프로세싱 수단으로부터의 제2출력 신호의 일부분이다. 또한, 컨발빙 수단은 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있지 않을때 라이브 비디오 신호를 텔레비전 수상기의 디스플레이로 전송한다. 본 발명은 첨부된 도면을 참조한 이하 설명으로부터 더욱 잘 이해할 수 있을 것이다.

각 도면에서 동일한 기능을 수행하는 대응 구성요소는 동일한 도면부호를 갖는다.

제1도를 참조하면, 대화형 비디오 처리를 제공하며 가입자의 집에 설치될 수 있는 본 발명에 따른 가입자 케이블 박스 유닛(10)의 블록도가 도시되어 있다. 가입자 케이블 박스 유닛(10)은 제1모듈(MODULE 1)(12)(제1점선 사각형내에 도시함) 및 제2모듈(MODULE 2)(14)(제2점선 사각형내에 도시함)을 포함한다. 제1모듈(12)은 각각 공지된 라디오 주파수(RF)-기저대역 변환기(20) 및 변환기 제어 시스템(22)을 포함하는 종래의 구조이다. RF-기저대역 변환기(20)는 원격 케이블 회사의 본사(도시생략)로부터 케이블(27)을 타고 전파하는 NTSC 또는 PAL 표준 포맷의 멀티플렉싱된 RF 텔레비전 채널 신호를 수신하여 상기 멀티플렉싱된 RF 텔레비전 채널 신호를 멀티플렉싱된 채널 주파수로부터 기저대역 주파수로 선택적으로 변환한다. RF-기저대역 변환기(20)는 상기 변환처리로 인한 결과 기저대역 합성 비디오 출력 신호를 버스(24)를 통하여 제2모듈(14)로 전송한다. 변환기 제어 시스템(22)은 공지된 바와같이 통상적으로 적외선 원격 제어장치 또는 케이블 박스상의 키패드에 의한 사용자(가입자)의 조작에 의해 제어된다. 변환기 제어 시스템(22)은 원격 케이블 회사 본사로 또는 상기 본사로부터 케이블(27)을 통하여 허가 및 액세스 제어 신호를 수신 및/또는 전송하고, 기저대역 비디오 스크램블링 또는 디스크램블링을 가동시키며, 온 스크린 디스플레이(OSD:On Screen Display) 메세지를 생성하는 역할을 한다. 변환기 제어 시스템(22)은 리드선(31,33)을 통하여 제2모듈(14)로 요망되는 채널 프로그래밍과 다양한 제어 및 복호된 데이터 신호(즉, 제어 및 업스트림 데이터 출력 신호, 적외선 수신 및 전송 신호 및 복호된 T1 4상 위상 시프트 키잉 데이터 신호)를 선택하기 위해 버스(29)를 통하여 RF-기저대역 변환기(20)로 제어신호를 출력한다.

제2모듈(14)은 직렬 인터페이스 프로세서(SIP)(30), 입력/출력(I/O) 장치(32), 판독전용 메모리(ROM)(34), 랜덤 액세스 메모리(RAM)(35), 중앙처리장치(CPU)(36), 그래픽 메모리(38) 및 비디오 및 메모리 제어(VIDEO & MEM. CONT.) 접적회로(40)(점선 사각형내에 도시함)을 포함한다. SIP(30), I/O 장치(32), ROM(34), RAM(35), CPU(36) 및 비디오 및 메모리 제어기 접적회로(40)의 메모리 제어기 및 스프라이트 상태 머신(Memory Controller and Sprite State Machine)(MACH)(42)이 데이터 버스(48)에 의해 상호접속되어 있다. CPU(36)는 어떠한 적절한 처리장치도 포함할 수 있으며, 본 발명에 따르면 비교적 산 386형 CPU이다. ROM(34)은 초기화 및 CPU(36) 프로그래밍용 EPROM과 같은 어떠한 적절한 메모리도 포함할 수 있다. ROM(35)은 예컨대 CPU(36)용 스크래치패드 메모리로서 사용되는 512K~~16~~비트 RAM 구조를 제공하기 위해 직렬로 접속된 2개의 256킬로바이트~~16~~비트 DRAM과 같은 어떠한 적절한 메모리도 포함할 수 있다. 그래픽 메모리(38)는 예컨대, 32비트 와이드 RAM 영역 또는 바람직하게는 32비트 와이드 버스와 함께 사용하기 위해 병렬로 배치된 2개의 256K~~16~~비트 DRAM과 같은 어떠한 적절한 메

모리도 포함할 수 있다. 그래픽 메모리(38)는 그래픽 및 비디오 화상에 관한 스프라이트 데이터를 기억하는데 사용된다. 32비트 와이드 버스(39)를 사용함으로써 메모리 제어기 및 스프라이트 상태 머신(42)과 비디오 및 메모리 제어기(40)의 일부를 형성하는 블록 메모리 무버(block memory mover)(도시생략)에 대한 고속-페이지 모드 메모리 어드레싱의 사용을 가능하게 한다. 이러한 중요한 블록 모드 메모리 어드레싱의 사용에 의해 대략 52나노초의 평균 데이터 전송률을 얻을 수 있으며, 상기 전송률은 대략 초당 대략 77백만 바이트 데이터를 처리하는 것에 해당한다.

SIP(30)는 제1모듈(12)과 제2모듈(14)간의 데이터 통신을 처리하는 역할을 한다. 특히, SIP(30)는 제2모듈과 제1모듈(12)의 변환기 제어 시스템(22)간의 모든 데이터 전송 신호를 처리한다. 상기 데이터 전송 신호는 예컨대 통신 전송의 대부분과 관련되는 1.5 Mbit/s의 T1형 데이터 스트림과 같은 포맷과 변환기 제어 시스템(22)의 적외선 수신기(도시생략)로부터의 그대로의(raw) 데이터를 가질 수 있다. SIP(30)는 앞으로의 확장을 위해 전이종 동기 직렬 포트(도시생략)를 포함할 수도 있다. 이러한 데이터 전송 신호 포맷은 제2모듈(14)에서 요망되는 액션을 가능시키기 위해 제1모듈(12)상의 변환기 제어 시스템(22)과 제2모듈(14)의 CPU(36)간에 통신하는데 사용된다.

비디오 및 메모리 제어 집적 회로(40)는 메모리 제어기 및 스프라이트 상태 머신(42), 합성-YUV 회로(44) 및 비디오 처리(Proc.) 회로(46)를 포함한다. 메모리 제어기 및 스프라이트 상태 머신(42)은 데이터 버스(39)에 의해 그래픽 메모리(38)에 접속되고 데이터 버스(45)에 의해 비디오 처리회로(46)에 접속된다. 합성-YUV 회로(44)는 버스(24)로부터 기저대역 합성 비디오 신호를 수신하고 버스(43)상으로 결과 YUV 비디오 신호를 메모리 제어기 및 스프라이트 상태 머신(42)에 출력한다. 비디오 처리회로(46)는 데이터 버스(45)상으로 메모리 제어기 스프라이트 상태 머신(44)으로부터 비디오 신호를 수신하고, 버스(47)상으로 NTSC 또는 PAL 표준 비디오 신호를 원격 텔레비전 수상기(도시생략) 또는 추가 처리회로(도시생략)로 출력한다. 본 발명은 비디오 및 메모리 제어 집적회로(40)와 그래픽 메모리(38) 분야에 있다는 것을 이해할 수 있을 것이다. 제1모듈(12) 및 제2모듈(14)의 구성 요소들은 본 발명이 대화형 가입자 케이블 박스유닛(10)에 설치되는 방법을 보다 잘 이해할 수 있도록 하기위해 설명하였다.

제2도 및 제3도를 참조하면, 본 발명에 따라 제1도의 가입자 케이블 박스 유닛(10)의 제2모듈(14)에 설치된 비디오 처리 회로(46)(점선 사각형내에 도시됨)의 제1부 및 제2부 각각의 블록도가 도시되어 있다. 제2도에 도시한 바와같이, 제1도의 제2모듈(14)의 구성요소를 형성하는 그래픽 메모리(38)는 제1도의 제2모듈(14)의 비디오 및 메모리 제어기(40)(점선 사각형내에 도시됨)의 일부분인 메모리 제어기 및 스프라이트 상태 머신(42)에 데이터 버스(39)를 통하여 접속된다. 비디오 처리 회로(46)의 제1부는 데이터 파이프(50) 및 픽셀 어셈블리 버퍼(52)(점선 사각형내에 도시됨)를 포함한다. 데이터 파이프(50)는 픽셀 어셈블리 버퍼(52)로의 전송을 위해 메모리 제어기 및 스프라이트 상태 머신(42)에 의해 얻은 그래픽 메모리(38)로부터의 특정 스프라이트에 대한 데이터를 버스(45)를 통하여 수신한다. 특히, 데이터 파이프(50)는 메모리 제어기 및 스프라이트 상태 머신(42)을 통하여 그래픽 메모리(38)로부터 스프라이트에 대한 데이터를 수신하며 픽셀 어셈블리 버퍼(52)로의 전송을 위해 휴도 데이터(y 데이터) 및 색도 데이터(c 데이터)에 대한 독립적인 출력을 제공한다.

픽셀 어셈블리 버퍼(52)는 제1, 제2 및 제3더블 라인 버퍼(53,54,55)와 Y/G 라인 0 버퍼(58)를 포함한다. 제1더블 라인 버퍼(53)는 데이터 파이프(50)로부터 버스(49)를 통하여 수신된 스프라이트 화상의 제1필드의 제1 및 제2라인에 대한 Y/G(휴도) 라인 1a 데이터 및 Y/G 라인 1b 데이터를 기억하는데 사용된다. 라인 휴도 데이터는 10 비트(비트 9-0) 데이터와 각 라인 픽셀에 대한 제어를 포함한다. 제2더블 라인 버퍼(54)는 데이터 파이프(50)로부터 버스(51)를 통하여 수신된 스프라이트 화상의 제1필드의 제1 및 제2라인의 C(색도) 라인 1a 및 C 라인 1b 데이터를 기억하는데 사용된다. 라인 색도 데이터는 라인의 각 픽셀에 대해 8 비트(비트 7-0) 데이터를 포함한다. 제3더블 라인 버퍼(55)는 데이터 파이프(50)로부터 버스(49)를 통하여 수신된 스프라이트 화상의 제2필드의 제1 및 제2라인의 Y/G(휴도) 라인 2a 데이터 및 Y/G 라인 2b 데이터를 기억하는데 사용된다. 라인 휴도 데이터는 10 비트(비트 9-0) 데이터와 라인의 각 픽셀에 대한 제어를 포함한다. 제1 및 제3더블 라인 버퍼(53,55)의 라인 1a 및 2a는 픽셀 데이터의 제1 및 제2수평 라인을 각각 기억하는데, 픽셀 데이터의 제1 및 제2수평라인은 비월주사식 디스플레이 포맷의 스프라이트 화상의 분리된 필드내에서 인접한 라인들임을 이해할 수 있을 것이다. 이와 유사하게, 제1 및 제3더블 라인 버퍼(53,55)의 라인 1b 및 2b가 픽셀 데이터의 제3 및 제4수평 라인을 각각 기억하는데, 픽셀 데이터의 제3 및 제4수평라인은 비월주사식 디스플레이 포맷의 스프라이트 화상의 분리된 필드내에서 인접한 라인들임을 이해할 수 있을 것이다. 즉, 제1 및 제3더블 라인 버퍼(53,55)는 예컨대 비월주사식 디스플레이 포맷의 주사동안 스프라이트 화상의 제1 및 제2필드의 각 출수 및 짹수 라인쌍(또는 역으로도 동일함)의 픽셀에 대한 휴도 데이터 및 제어를 순차적으로 기억한다. 제2더블 라인 버퍼(54)는 더블 라인 버퍼(53)에 기억된 라인 데이터에 대한 색도 데이터를 기억한다. 더블 라인 버퍼(54)와 유사한 색도 더블 라인 버퍼(도시생략)가 더블 라인 버퍼(55)용으로 제공될 수 있으나, 경제적인 이유와 차후 설명되는 컨발버에서 중요하지 않으므로 필요하지 않다.

제1더블 라인 버퍼(53)로부터의 출력 데이터는 라인 1로 지정된 버스상으로 각 픽셀에 대한 병렬로 제3도의 회로에 출력되며 상기 버퍼에 기억된 라인들의 각 픽셀에 대한 10 비트의 휴도 데이터 및 제어를 포함한다. 제2더블 라인 버퍼(54)로부터의 출력 데이터는 라인 1c로 지정된 버스상으로 각 픽셀에 대해 병렬로 제3도의 회로에 출력되며 상기 버퍼에 기억된 라인들의 각 픽셀에 대한 8 비트 색도 데이터를 포함한다. 제3더블 라인 버퍼(55)로부터의 출력 데이터는 라인 2로 지정된 버스상으로 각 픽셀에 대해 병렬로 제3도의 회로 및 Y/G 라인 0 버퍼(58)에 출력되며 상기 버퍼에 기억된 라인들의 각 픽셀에 대한 10 비트 휴도 데이터 및 제어를 포함한다. Y/G 라인 0 버퍼(58)는 라인 0로 지정된 버스상으로 병렬로 제3도의 회로에 출력되며 버퍼(55)에 기억된 라인의 각 픽셀에 대한 10 비트 휴도 데이터 및 제어를 포함하는 자연된 라인 출력을 제공하기 위해 제3더블 라인 버퍼(55)에 의해 출력된 라인 데이터를 하나의 수평 라인 주기만큼 자연시키는 역할을 한다. NTSC 표준 텔레비전 디스플레이를 위한 13.5 MHz의 샘플링률에 서는 화상라인당 858 픽셀이 있는데, 그중에서 대략 704 픽셀만이 실제로 디스플레이되고, 화상의 두 필드에 픽셀의 525 수평라인이 있는데, 사용되는 텔레비전 수상기에 따라 그중에서 대략 440-500라인이 보통 보여진다.

제4도, 제5도 및 제6도를 참조하면, 본 발명에 따라 제2도의 픽셀 어셈블리 버퍼(52)의 제1 및 제3더블

라인 버퍼(53,55) 및 Y/G 라인 0 버퍼(58)의 예시적인 동작 시퀀스가 도시되어 있다. 더블 라인 버퍼(53,55)의 정상적인 동작시, 제1필드의 픽셀 데이터의 수평라인이 제1더블 라인 버퍼(53)의 1/2로 입력되는 동시에 제2필드의 픽셀 데이터의 수평라인은 제3더블 라인 버퍼(55)의 1/2로 입력됨을 이해할 수 있을 것이다. 픽셀 데이터의 수평라인이 제1 및 제3더블 라인 버퍼(53,55)의 제1의 1/2로 입력되는 동시에, 제1 및 제3더블 라인 버퍼(53,55)의 나머지 1/2에 이전에 기억된 픽셀 데이터의 수평라인은 출력 라인 1 및 2상에서 독출된다. 즉, 제1더블 라인 버퍼(53)에 대해 제1필드로부터의 픽셀 데이터의 제1수평 라인은 예컨대 제1더블 라인 버퍼(53)의 Y/G 라인 1a 부로 입력되고, 다음 수평 라인 주기동안 프레임의 제1필드로부터의 픽셀 데이터의 제2수평 라인은 제1더블 라인 버퍼(53)의 Y/G 라인 1b부로 입력되고 Y/G 라인 1a로부터의 픽셀 데이터의 제1수평 라인은 출력 라인 1상으로 독출된다. 다음 수평 라인 주기동안, 제1필드로부터의 픽셀 데이터의 제3수평 라인은 제1더블 라인 버퍼(53)의 Y/G 라인 1a부로 입력되고, Y/G 라인 1b로부터의 픽셀 데이터의 제2수평 라인은 출력 라인 1상으로 독출된다. 동시에, 프레임의 제2필드로부터의 픽셀 데이터의 제1, 제2 및 제3수평 라인은 제3더블 라인 버퍼(55)로 판독되어 출력 라인 2상으로 출력된다.

제4도는 제1도의 가입자 케이블 박스 유닛(10)이 먼저 턴온된 후 픽셀 어셈블리 버퍼(52)의 초기화단의 말단지점을 도시하고 있다. 특히, 턴온시 제1필드의 수평 라인 0에 대한 픽셀 데이터 및 제2필드의 수평라인 1에 대한 픽셀 데이터는 제1수평 라인 주기동안 제1더블 라인 버퍼(53)의 Y/G 라인 1a 부 및 제3더블 라인 버퍼(55)의 Y/G 라인 2a 부로 각각 입력된다. 제2수평 라인 주기동안, 제1필드의 수평 라인 2에 대한 픽셀 데이터 및 제2필드의 수평라인 3에 대한 픽셀 데이터는 제1더블 라인 버퍼(53)의 Y/G 라인 1b 부 및 제3더블 라인 버퍼(55)의 Y/G 라인 2b 부로 각각 입력되고, 수평 라인 0 및 1에 대한 픽셀 데이터는 각 출력 라인 1 및 2상으로 제1더블 라인 버퍼(53)의 Y/G 라인 1a 부 및 제3더블 라인 버퍼(55)의 Y/G 라인 2a 부로부터 판독된다. 이와 동시에, 제3더블 라인 버퍼(55)의 Y/G 라인 2a 부로부터의 수평라인 1에 대한 픽셀 데이터는 Y/G 라인 0 버퍼(58)로 입력된다. Y/G 라인 0 버퍼(58)는 한 수평라인 주기만큼 상기 버퍼에 기억된 수평 라인 데이터를 지연시키는 역할을 하고, 상기 버퍼(58)는 초기화시 기억하고 있는 데이터가 없기 때문에, 출력 라인 0상의 출력은 유효한 데이터를 포함하고 있지 않다.

제5도는 제4도에 도시한 초기화 단계이후의 계속되는 로딩 및 출력 처리를 도시한다. 특히, 제1필드의 수평 라인 4에 대한 픽셀 데이터 및 제2필드의 수평 라인 5에 대한 픽셀 데이터는 제3수평 라인 주기동안 제1더블 라인 버퍼(53)의 Y/G 라인 1a 부 및 제3더블 라인 버퍼(55)의 Y/G 라인 2a 부로 각각 입력된다. 이와 동시에, 수평 라인 2 및 3에 대한 픽셀 데이터는 각 출력 라인 1 및 2상으로 제1더블 라인 버퍼(53)의 Y/G 라인 1b 부 및 제3더블 라인 버퍼(55)의 Y/G 라인 2b 부로부터 판독된다. 이와 동시에, 제3더블 라인 버퍼(55)의 Y/G 라인 2b로부터의 수평 라인 3에 대한 픽셀 데이터는 Y/G 라인 0 버퍼(58)로 입력되고, 수평 라인 0 데이터에 대한 이전에 기억된 픽셀 데이터는 출력 라인 0상으로 출력된다. 따라서, 버퍼(58,53,55)는 제3수평 라인 주기동안 각 출력 라인 0, 1 및 2상으로 스프라이트의 수평 라인 1, 2 및 3에 대한 픽셀 데이터를 출력하는데, 수평 라인 1 및 3에 대한 픽셀 데이터는 그래픽 메모리(38)(제1도 및 제2도에 도시함)에 기억되었던 스프라이트 화상의 제2필드의 일부분이고 수평 라인 2에 대한 픽셀 데이터는 제1필드의 일부분이다.

제6도는 제5도에 도시한 단계이후의 계속적인 로딩 및 출력 처리를 도시한다. 특히, 스프라이트의 제1필드의 수평 라인 6에 대한 픽셀 데이터 및 제2필드의 수평 라인 7에 대한 픽셀 데이터는 제4수평 라인 주기동안 제1더블 라인 버퍼(53)의 Y/G 수평 라인 1b 부 및 제3더블 라인 버퍼(55)의 Y/G 수평 라인 2b 부로 각각 입력된다. 이와 동시에, 스프라이트의 수평 라인 4 및 5에 대한 픽셀 데이터는 각 출력 라인 1 및 2상으로 제1더블 라인 버퍼(53)의 Y/G 수평 라인 1a 부 및 제3더블 라인 버퍼(55)의 Y/G 수평 라인 2a 부로부터 판독된다. 이와 동시에, 제3더블 라인 버퍼(55)의 Y/G 라인 2a 부로부터의 수평 라인 5에 대한 픽셀 데이터는 Y/G 라인 0 버퍼(58)로 입력되고, 이전에 기억된 수평 라인 3 데이터에 대한 픽셀 데이터는 출력 라인 0상으로 출력된다. 따라서, 버퍼(58,53,55)는 제4수평 라인 주기동안 각 출력 라인 0, 1 및 2상으로 수평 라인 3, 4, 및 5에 대한 픽셀 데이터를 출력하는데, 수평 라인 3 및 5에 대한 데이터는 스프라이트 화상의 제2필드의 일부분이고 수평 라인 4에 대한 데이터는 그래픽 메모리(38)(제1도 및 제2도에 도시함)에 기억되었던 스프라이트 화상의 제1필드로부터 얻어진다.

제5도 및 제6도로부터, 초기화(제4도)이후에 출력 라인 1상의 픽셀 데이터가 NTSC 비율주사식 디스플레이를 위한 프레임의 두 필드중 제1필드의 순차적인 수평라인(예컨대 NTSC 표준 화상의 짹수번 수평라인(0~254))에 대한 데이터를 표현함을 알 수 있다. 제1필드의 짹수번 수평라인이 순차적인 수평라인 주기동안 출력 라인 1상으로 순차적으로 출력된 후, 출력은 비율주사식 디스플레이를 주사하는 방식으로 프레임의 제2필드의 순차적인 번호의 수평 라인(예컨대, NTSC 표준 화상의 홀수번의 수평라인 1~255)으로 계속 이어진다. 제4~6도에 도시하지는 않았지만, 색도 데이터가 제2도에 도시한 제2더블 라인 버퍼(54)로부터 출력 라인 1c 상으로 출력되고 이와 동시에 각 수평라인에 대한 관련 휘도 픽셀 데이터가 출력 라인 1상으로 출력됨을 이해할 수 있을 것이다.

제3도를 참조하면, 본 발명에 따라 제1도의 가입자 케이블 박스 유닛(10)에 설치된 비디오 처리회로(46)의 제2부의 블록도가 도시되어 있다. 비디오 처리 회로(46)의 제2부는 컬러 파렛트 회로(60), YC-YUV 디멀티플렉서(62), 멀티플렉서/페이더(MUX./FADER)(64), 3:1 멀티플렉서 및 제어(3:1 MUX. & CONT.)(66) 및 컨발버(68)를 포함한다. 스프라이트 화상의 인접한 3개의 수평라인의 대응 픽셀에 대해 제2도의 픽셀 어셈블리 버퍼(52)의 출력으로부터 각 라인 0, 1, 2를 따라 전달되는 10비트 픽셀 데이터(비트 9:0)는 컬러 파렛트 회로(60), YC-YUV 디멀티플렉서(62) 및 3:1 멀티플렉서 및 제어(66) 각각의 입력에서 수신된다. 특히, 각 출력 라인 0, 1 및 2에 대한 픽셀 어셈블리 버퍼(52)로부터의 병렬의 10비트/픽셀 출력의 비트 9:0은 컬러 파렛트 회로(60) 및 YC-YUV 디멀티플렉서(62)의 입력에서 수신되며, 각 출력 라인 0, 1 및 2에 대한 픽셀 어셈블리 버퍼(52)로부터의 병렬의 10비트/픽셀 출력의 비트 9 및 8은 3:1 멀티플렉서 및 제어(66)의 입력에서 수신된다. 또한, 스프라이트 픽셀 데이터가 트루 컬러 스프라이트 신호에 관계될 때 색도 데이터만이 사용되므로 YC-YUV 디멀티플렉서(62)는 픽셀 어셈블리 버퍼(52)로부터 출력 라인 1c상으로 병렬로 출력된 색도 데이터 비트 7-0을 수신한다. 특히, 스프라이트 데이터가 컬러 파렛트 신호로서 엔코드되는 경우에, 코드 자체가 컬러를 정의하고, 트루 컬러 비디오 신호에

필요한 색도 데이터는 요구되지 않는다.

컬러 파렛트 회로(60)는 각 출력 라인 0, 1 및 2상에서 병렬로 수신된 8비트(비트 7:0) 픽셀 데이터가 컬러 파렛트의 특정 컬러에 대한 별도의 코드를 표현하는 때를 검출하고 상기 컬러 파렛트 코드를 상기 세 라인용으로 수신된 3개의 8비트 픽셀 데이터에 대한 24비트 YUV 멀티플렉싱된 컬러 파렛트 신호를 표현하는 버스(61)상의 출력 신호로 변환하는 역할을 한다. 컬러 파렛트 회로(60)는 공지된 장치이며, 따라서 적절한 어떠한 회로도 사용될 수 있다. YC-YUV 디멀티플렉서(62)는 픽셀 어셈블리 버퍼(52)로부터 각 출력 라인 0, 1 및 2상에서 병렬로 수신된 픽셀에 대한 8비트(비트 7:0) 데이터가 트루 컬러 데이터(즉, 텔레비전 화상으로부터 직접 얻은 스프라이트)를 표현하는 때를 검출하여, 픽셀 어셈블리 버퍼(52)로부터 출력 라인 1c를 통하여 얻은 8비트 색도 데이터를 사용하여 버스(63)으로의 전송을 위해 상기 세 라인의 픽셀에 대한 24비트 트루 컬러 YUV 출력 신호를 발생시킨다.

멀티플렉서/페이더(MUX./FADER)(64)는 분리된 입력에서 컬러 파렛트 회로(60)로부터 버스(61)상으로 전달되는 24비트 컬러 파렛트 YUV 데이터 신호, YC-YUV 디멀티플렉서(62)로부터 버스(63)상으로 전달되는 24비트 트루 컬러 YUV 데이터 신호 및 버스(59)상의 24비트 YUV 라이브 비디오 신호를 각각 수신한다. 멀티플렉서/페이더(64)는 리드선(67)상의 3:1 멀티플렉서 및 제어(66)로부터의 제어 신호에 응답하여 버스(65)상의 디지털화된 YUV 멀티플렉서로부터 각 픽셀 주기동안 멀티플렉서/페이더(64)에서 수신된 3개의 입력 신호(24비트 컬러 파렛트 YUV, 24비트 트루 컬러 YUV 또는 24비트 라이브 비디오 YUV)중 하나를 출력한다. 특히, 3:1 멀티플렉서 및 제어(66)는 픽셀 어셈블리 버퍼(52)로부터 출력 라인 0, 1 및 2상으로 수신된 비트 9 및 8로부터 출력 라인 0, 1 및 2상의 픽셀 어셈블리 버퍼로부터의 픽셀 데이터가 컬러 파렛트 데이터, 트루 컬러 데이터 또는 라이브 비디오 신호상에 걸쳐지게 될 스프라이트의 일부가 아닌 픽셀에 대한 데이터(무효 데이터)를 나타내고 있는지를 판별하며, 이에 따라서 라이브 비디오 신호는 픽셀 어셈블리 버퍼(52)로부터 수신된 컬러 파렛트 또는 트루 컬러 데이터 대신에 상기 픽셀용으로 사용되어야 한다. 픽셀 어셈블리 버퍼(52)로부터의 출력 라인 0, 1 및 2의 비트 9 및 8로부터 얻어진 제어 정보로 인하여, 원격 NTSC 및 PAL 텔레비전 수상기(도시생략)상에 디스플레이될 화상의 각 픽셀에 대한 정확한 입력 데이터를 선택하기 위해 3:1 멀티플렉서 및 제어(66)는 제어 신호를 리드선(67)상으로 멀티플렉서/페이더(64)로 전송한다. 텔레비전 화상의 인접하는 세 라인의 대응 픽셀의 3×3 매트릭스에서 중앙 픽셀에 대한 픽셀 데이터에 8비트 가중치 출력 신호를 제공하거나 또는 리드선(69)상으로 3:1 멀티플렉서 및 제어(66)로부터의 제어신호에 따라 버스(47)상의 YUV 출력 신호로서 버스(65)상으로 멀티플렉서/페이더(64)로부터의 신호를 제공하기 위해 컨발버(68)는 버스(65)상으로 멀티플렉서/페이더(64)로부터의 신호에서 수신된 순차적인 일련의 픽셀 데이터 값을 사용한다.

제7도를 참조하면, 2:1 멀티플렉서(MUX.)(72) 및 페이더(74)(점선 사각형내에 도시됨)를 포함하는 예시적인 멀티플렉서/페이더 회로(64)(점선 사각형내에 도시됨)의 블록도가 도시되어 있다. 페이더(74)는 A-B 가산기(75), 부호달린 승산기(SIGNED NULT.)(77) 및 A+B 가산기(78)를 포함한다. 2:1 멀티플렉서는 제1입력 단자(A)에서 버스(61)상으로 컬러 파렛트(60)로부터 각 그래픽 데이터 신호와 제2입력 단자(B)에서 버스(63)상으로 YC-YUV 디멀티플렉서(62)로부터 그래픽 데이터 신호를 수신한다. 리드선(67)상의 3:1 멀티플렉서 및 제어(66)로부터의 제어 신호는 (입력 단자 A 또는 B로부터의) 2개의 그래픽 입력 신호중에서 출력 단자(0)에서 2:1 멀티플렉서(72)로부터 출력될 입력신호를 선택한다. 버스(70)상의 2:1 멀티플렉서(72)(G)의 출력 단자(0)로부터의 픽셀 그래픽 출력신호(Y,U 또는 V)는 페이더(74)의 A-B 가산기(75)의 제1입력 단자(A)에서 수신된다. 라이브 비디오 YUV 신호(Y,U 또는 V)(L)는 A-B 가산기(75)의 제2입력 단자(B)에서 버스(59)로부터 수신된다. 2:1 멀티플렉서(72)로부터의 A 단자 입력 데이터의 픽셀 데이터 값으로부터 B 입력 단자에서 수신된 라이브 비디오 YUV 픽셀 데이터의 데이터 값을 제외한 값이 A-B 가산기(75)의 출력 단자(0)에서 출력으로서 제공된다. 부호달린 승산기(77)는 버스(71)상으로 제1입력 단자(A)에서 예컨대 레지스터(도시생략)로부터 변경가능한 9비트 비율 제어 값(R)을 수신하고, 버스(71)상으로 제2입력 단자(B)에서 A-B 가산기(75)로부터의 출력을 수신한다. 버스(71)상의 비율 제어값(R)과 버스(76)상의 A-B 가산기(75)로부터의 그래픽 신호 출력 데이터의 승산된 결과값은 출력 단자(0)에서 버스(79)상으로 AB 가산기(78)의 제1입력 단자(A)로 출력된다. 버스(59)상의 라이브 비디오 신호(Y,U 또는 V)는 A+B 가산기(78)의 제2입력 단자(B)에서 수신되고, 이를 두 입력 신호값의 합은 출력 신호(Q)로서 버스(65)상으로 컨발버(68)(제3도에 도시됨)로 제공된다.

페이더(74)는 스프라이트에 대한 그래픽 신호를 페이드인 또는 페이드아웃하여 그래픽이 라이브 비디오 신호에 대해서 순간적으로 나타나거나 사라지지 않도록 하는 역할을 한다. 즉, 그래픽 페이드인에 있어서, 페이더(74)는 그래픽이 텔레비전 수상기상에 증가하는 명암으로 나타나게 하는 반면에, 라이브 비디오 신호는 단기간에 걸쳐 그래픽 영역에서 명암이 감소하여 그래픽이 전체적으로 보이게 된다. 이와 유사하게, 그래픽 페이드아웃에 있어서, 페이더(74)는 그래픽이 텔레비전 수상기상에서 감소하는 명암으로 나타나게 하는 반면에, 라이브 비디오 신호는 그래픽이 사라질 때까지 단기간에 걸쳐 그래픽의 영역에서 명암이 증가한다. 페이더(74)의 동작은 다음의 알고리듬에 따라 설명될 수 있다. 다음의 설명을 위해, 버스(71)상으로 제공되는 예시적인 9비트 페이드 승수(R)는 다음과 같이 정의된다. R은 페이드 제어 값이고, 0-256 범위이다. 상기 정의로부터

$$Q = [(R/256)*G] + [(1-R/256)*L]$$

$$= L + [(G-L)*R] / 256$$

여기서 L은 라이브 비디오의 픽셀값이고, G는 스프라이트 오버레이의 픽셀값이며, 기호 \*는 곱함수를 나타낸다. 상기 식(1)로부터 승산값 R에 대해 사용되는 비율이 변함에 따라, 그래픽 및 라이브 비디오 신호의 명암이 반대 방향으로 변한다.

제8도를 참조하면, 제3도에 도시한 컨발버(68)의 블록도가 도시되어 있다. 컨발버(68)(점선 사각형내에 도시됨)는 바이패스 회로(80), 컨발버 회로(82) 및 멀티플렉서(MUX.)(84)를 포함한다. 바이패스

회로(80)는 버스(65)상으로 멀티플렉서/페이지(64)(제3도 및 제7도에 도시됨)로부터 순차적인 픽셀 데이터를 수신하는 동시에 텔레비전 수상기상에 디스플레이될 스프라이트의 수직방향으로의 세 픽셀에 대한 데이터를 버스(81)상으로 발생한다. 특히, 상기 세 픽셀은 스프라이트 화상을 구성하는 프레임의 두 필드의 인접한 세 라인의 대응 픽셀들로부터 얻어진다. 이들 세 픽셀 데이터 값은 한 픽셀 클록 또는 3배 픽셀 클록에 의해 동작하는 다수의 지연회로와 같은 적절한 장치에 의해 얻어진다. 세 픽셀 데이터 값은 버스(81)를 통하여 컨발버 회로(82)에 의해 수신된다. 멀티플렉서/페이지(64)로부터의 순차적인 픽셀 데이터는 버스(65)상으로 바이패스 회로(80)에 의해 수신된다. 멀티플렉서/페이지(64)로부터의 순차적인 픽셀 데이터는 바이패스 회로(80)를 통하여 버스(85)를 통하여 멀티플렉서(84)의 제1입력(A)에 제공된다. 또한, 바이패스 회로(80)는 상기 회로의 분리된 출력으로부터 컨발버 회로(82)의 분리된 입력으로 버스(81)를 따라 순차적인 일련의 세 픽셀 데이터 값을 전송한다. 컨발버 회로(82)는 출력에서 텔레비전 화상의 인접한 세 라인에서 대응 픽셀의  $3 \times 3$  매트릭스의 중앙 픽셀의 픽셀 데이터에 대한 8비트 가중 출력 신호를 버스(86)를 통하여 멀티플렉서(84)의 제2입력(B)에 제공한다. 멀티플렉서(84)는 리드선(69)을 따라 3:1 멀티플렉서 및 제어(66)로부터의 제어 신호에 따라 출력 단자(0) 및 버스(47)로 전송하기 위한 제1(A) 또는 제2(B) 입력의 신호를 선택한다.

상기한 본발명의 특정 실시예에는 본 발명의 일반적인 원리를 설명하고 있을 뿐임을 이해할 수 있을 것이다. 원리가 본 발명과 일치하는 다양한 변경이 당업자에 의해 이루어질 수 있다. 예컨대, 본 발명이 가입자 케이블 박스 유닛(10)내에서 사용되는 것에 대해 기술하였지만, 본 발명은 예컨대 텔레비전 신호가 방송되기 이전의 제작 편집국에서 사용될 수 있음을 이해할 수 있을 것이다. 즉, 본 발명은 후에 원격 가입자 위치에서 텔레비전 신호를 조작하기 보다 방송되기 이전의 최초의 제작물을 제작하기 위한 텔레비전 제작시 사용될 수 있다. 이는 화상의 화질 및 해상도는 편집이 제작시 또는 이후의 가입자 위치에서 행해졌는가의 여부에 관계없이 동일하므로 가능하다. 따라서, 제작물이 가입자의 비월주사식 텔레비전 세트상에 보여지기 전에 편집이 어디에선가 행해진다면 화질 또는 해상도가 편집되지 않은 텔레비전 제작물에서 더 양호할 수도 있다는 따위는 문제가 되지 않는다.

### 발명의 효과

본 발명은 막상된 YUV 및 컬러 패렛트화된 그래픽 비디오 신호를 처리하여 상기 비디오 신호를 독립적으로 디스플레이하고, 또한 원격 소스로부터 수신된 라이브 텔레비전 신호상에 상기 그래픽 비디오 신호를 중첩시킬 수도 있다.

### (57) 청구의 범위

#### 청구항 1

표준 비월주사식 텔레비전 수상기상에 디스플레이하기 위해 막상된 비디오 및 그래픽 신호를 처리하는 장치에 있어서, 표준 비월주사식 텔레비전 수상기의 디스플레이의 선택된 소정의 구별된 영역에 선택적으로 디스플레이될 하나이상의 각 스프라이트의 제1 및 제2필드 각각으로부터의 스프라이트 픽셀 데이터의 제1 및 제2수평 라인의 수신에 응답하여 텔레비전 수상기상에 디스플레이하기 위한 화상의 인접한 세 수평라인에 대한 순차적인 스프라이트 픽셀 데이터를 포함하는 제1, 제2 및 제3출력신호를 발생하는 버퍼링 및 프로세싱 수단을 포함하는데, 스프라이트들이 텔레비전 수상기상의 디스플레이 영역상에서 겹쳐질때 최우선순위의 스프라이트에 대한 픽셀 데이터는 언제든지 제1, 제2 및 제3출력 신호의 각 픽셀 위치로 출력되며, 상기 제1 및 제3출력 신호는 제1 및 제2필드중 한 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고, 상기 제2출력 신호는 제1 및 제2필드중 나머지 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고 스프라이트 데이터가 트루 컬러 포맷과 관련될때 색도 데이터를 포함하며; 상기 버퍼링 및 프로세싱 수단으로부터 제1, 제2 및 제3출력 신호를 수신하여, 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함된 경우에 텔레비전 수상기로의 전송을 위해 미리 결정된 소정의 픽셀 데이터의 매트릭스의 중심 픽셀에 가중 평균을 제공하는 출력 신호를 생성하며, 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되지 않은 경우에 텔레비전 수상기의 디스플레이로 라이브 비디오 신호를 전송하는 컨발빙 수단을 포함하는데, 상기 중심 픽셀은 상기 버퍼링 및 프로세싱 수단으로부터의 제2출력 신호의 일부분인 것을 특징으로 하는 장치.

#### 청구항 2

제1항에 있어서, 표준 비월주사식 텔레비전 수상기의 디스플레이의 선택된 소정의 영역에 선택적으로 디스플레이될 하나이상의 각 스프라이트에 대한 스프라이트 데이터를 기억하여 상기 스프라이트 데이터를 포함하는 출력신호를 전송하는 디지탈 메모리 수단을 추가로 포함하는데, 상기 스프라이트 데이터는 텔레비전 수상기 상에 디스플레이될 스프라이트 화상의 제1 및 제2필드에 대한 트루 컬러 비디오 또는 컬러 패렛트 데이터 포맷중 하나를 포함하며, 하나이상의 스프라이트가 존재할때 하나이상의 각 스프라이트는 미리 결정된 소정의 우선순위를 갖는 것을 특징으로 하는 장치.

#### 청구항 3

제1항에 있어서, 상기 버퍼링 및 프로세싱 수단은 상기 디지탈 메모리 수단으로부터 제1 및 제2라인상에 디스플레이될 하나이상의 각 스프라이트에 대한 픽셀 데이터의 인접한 수평라인중 제1 및 제2수평라인을 동시에 판독하여 하나이상의 스프라이트중 최우선순위를 갖는 스프라이트의 일부분을 형성하는 라인들중 제1 및 제2라인의 각 픽셀에 대한 픽셀 데이터를 출력하는 수단을 포함하는데, 제1라인은 제1 및 제2필드중 한 필드로부터의 라인이고 제2라인은 제1 및 제2필드중 나머지 필드로부터의 라인이며, 상기 제1 및 제2필드중 한 필드 및 다른 필드의 라인들의 제1 및 제2라인은 각각 순차적으로 출력되는 것을 특징으로 하는 장치.

#### 청구항 4

제3항에 있어서, 상기 버퍼링 및 프로세싱 수단은 픽셀 어셈블리 버퍼를 추가로 포함하는데, 상기 픽셀

어셈블리 버퍼는 순차적으로 수신되는 수평라인의 제1라인들중 제1 및 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 픽셀 데이터를 기억하며 수평라인의 제1라인의 다음 순서의 라인이 수신되고 있는 가운데 제1출력 버스상으로 상기 컨발빙 수단으로 이전에 순차적으로 수신된 수평라인의 제1라인의 픽셀 데이터를 출력하는 제1더블 버퍼링 수단과, 순차적으로 수신한 수평 라인의 2개의 제2라인들의 하나이상의 스프라이트의 각 픽셀에 대해 최우선순위를 갖는 픽셀 데이터를 기억하며 수평라인중 제2라인의 다음 순서의 라인이 수신되고 있는 가운데 제2출력 버스상으로 상기 컨발빙 수단으로 이전에 순차적으로 수신된 수평라인의 제2라인에 대한 픽셀 데이터를 출력하는 제2더블 버퍼링 수단과, 상기 제2출력 버스상으로 상기 제2더블 버퍼링 수단에 의해 출력되고 있는 수평라인의 제2라인에 대한 픽셀 데이터를 수신하는 동시에 상기 제2더블 버퍼링 수단으로부터 수평라인의 또다른 제2라인을 수신하면서 제3버스상으로 상기 컨발빙 수단으로 수평 라인의 기억된 제2라인에 대한 기억된 픽셀 데이터를 전송하기 이전에 수평라인의 수신된 제2라인을 기억하여 한 수평 라인 주기만큼 지연시키는 지연 버퍼링 수단을 포함하는 것을 특징으로 하는 장치.

#### 청구항 5

제4항에 있어서, 상기 제1 및 제2더블 버퍼링 수단은 수평라인의 제1 및 제2라인의 각 픽셀의 휘도(Y) 성분에 관한 픽셀 데이터를 각각 기억하는 것을 특징으로 하는 장치.

#### 청구항 6

제5항에 있어서, 상기 픽셀 어셈블리 버퍼는 스프라이트 데이터가 트루 컬러 비디오 포맷으로 기억되어 있을때 순차적으로 수신한 수평 라인의 제1라인들중 제1 및 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 색도(C) 픽셀 데이터를 기억하며 수평라인의 제1라인의 다음 순서의 라인에 대한 색도 픽셀 데이터가 수신되고 있는 가운데 제4출력 버스를 통하여 이전에 순차적으로 수신한 수평라인의 제1라인에 대한 색도 픽셀 데이터를 출력하는 제3더블 버퍼링 수단을 추가로 포함하는 것을 특징으로 하는 장치.

#### 청구항 7

제6항에 있어서, 상기 버퍼링 및 프로세싱 수단은 상기 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3버스상으로의 수평 라인 신호에 응답하여 컬러 파렛트 포맷의 픽셀 데이터를 YUV 컬러 파렛트 출력 신호로 변환하는 컬러 파렛트 변환수단과, 상기 픽셀 어셈블리 버퍼로부터 제1, 제2, 제3 및 제4버스상으로의 휘도 및 색도 수평라인 신호에 응답하여 트루 컬러 YC 포맷의 픽셀 데이터를 트루 컬러 YUV 출력 신호로 변환하는 YC-YUV 디멀티플렉서와, 상기 컬러 파렛트 변환 수단 및 YC-YUV 디멀티플렉서로부터의 출력 신호와 라이브 비디오 신호에 응답하여 상기 픽셀 어셈블리 버퍼로부터 상기 제1, 제2 및 제3버스상으로 수신된 각 픽셀에 제공된 데이터에 따라 상기 컨발빙 수단으로의 전송을 위해 제1 및 제2필드의 데이터의 인접한 세 수평라인 각각의 각 픽셀에 대한 세 신호중 하나를 선택하는 멀티플렉싱 수단을 추가로 포함하는 것을 특징으로 하는 장치.

#### 청구항 8

제7항에 있어서, 하나이상의 스프라이트에 대한 수평라인 데이터의 각 픽셀의 휘도값은 픽셀 데이터 워드의 제1다수 비트로서 상기 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3버스상으로 전송되고, 하나이상의 스프라이트의 각 픽셀이 컬러 파렛트로 코딩되는지 또는 트루 컬러 포맷으로 코딩되는지의 여부 및 픽셀이 하나 이상의 스프라이트의 일부분을 형성하는지의 여부에 대한 지시는 픽셀 데이터 워드의 제2다수 비트로 코딩되며, 상기 픽셀 데이터 워드의 제2다수 비트는 상기 컨발빙 수단으로의 전송을 위해 상기 멀티플렉싱 수단에 의해 상기 컬러 파렛트 변환 수단 및 상기 YC-YUV 디멀티플렉서로부터의 출력신호와 라이브 비디오 신호중 하나를 선택하는데 사용되는 것을 특징으로 하는 장치.

#### 청구항 9

표준 비율주사식 텔레비전 수상기상에 디스플레이하기 위해 막싱된 비디오 및 그래픽 신호를 처리하기 위한 장치에 있어서, 표준 비율주사식 텔레비전 수상기의 디스플레이의 선택된 소정의 영역에 선택적으로 디스플레이될 하나이상의 각 스프라이트에 대한 스프라이트 데이터를 기억하여 상기 스프라이트 데이터를 포함하는 출력 신호를 전송하는 디지털 메모리 수단을 포함하는데, 스프라이트 데이터는 표준 텔레비전 수상기상에 디스플레이될 스프라이트 화상의 제1 및 제2필드에 대한 트루 컬러 비디오 또는 컬러 파렛트 데이터 포맷중 하나를 포함하고, 하나이상의 스프라이트가 존재할때 하나이상의 각 스프라이트는 미리 결정된 소정의 우선순위를 가지며, 상기 디지털 메모리 수단으로부터의 출력신호에 응답하여 텔레비전 수상기상에 디스플레이하기 위한 화상의 인접한 세 수평 라인에 대한 순차적인 스프라이트 픽셀 데이터를 포함하는 제1, 제2 및 제3출력 신호를 발생하는 버퍼링 및 프로세싱 수단을 포함하는데, 스프라이트들이 텔레비전 수상기상의 디스플레이 영역상에서 겹쳐질때 최우선순위의 스프라이트에 대한 픽셀 데이터는 언제든지 제1, 제2 및 제3출력 신호의 각 픽셀 위치로 출력되며, 상기 제1 및 제3출력신호는 제1 및 제2필드중 한 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고, 제2출력 신호는 제1 및 제2필드중 나머지 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고 스프라이트 데이터가 트루 컬러 포맷에 관련될때 색도 데이터를 포함하며, 상기 버퍼링 및 프로세싱 수단으로부터 제1, 제2 및 제3출력 신호를 수신하고 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있을때 텔레비전 수상기로 전송하기 위해 미리 결정된 소정의 픽셀 데이터의 매트릭스의 중심 픽셀에 가중평균을 제공하는 출력 신호를 발생하고 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있지 않을때 텔레비전 수상기의 디스플레이로 라이브 비디오 신호를 전송하는 컨발빙 수단을 포함하는데, 상기 중심 픽셀은 상기 버퍼링 및 프로세싱 수단으로부터의 제2출력 신호의 일부분인 것을 특징으로 하는 장치.

#### 청구항 10

제9항에 있어서, 상기 버퍼링 및 프로세싱 수단은 상기 디지털 메모리 수단으로부터 제1 및 제2라인상에

디스플레이될 하나이상의 각 스프라이트에 대한 픽셀 데이터의 인접한 수평 라인의 제1 및 제2라인을 판독하는 동시에 하나이상의 스프라이트중 최우선순위를 갖는 스프라이트의 일부분을 형성하는 라인의 제1 및 제2라인의 각 픽셀에 대한 픽셀 데이터를 출력하는 수단을 포함하는데, 제1라인은 제1 및 제2필드중 한 필드로부터의 라인이고 제2라인은 제1 및 제2필드중 나머지 필드로부터의 라인이며, 제1 및 제2필드 중 상기 한 필드 및 상기 나머지 필드의 라인중 제1 및 제2라인 각각은 순차적으로 출력되는 것을 특징으로 하는 장치.

#### 청구항 11

제10항에 있어서, 상기 버퍼링 및 프로세싱 수단은 픽셀 어셈블리 버퍼를 추가로 포함하는데, 상기 픽셀 어셈블리 버퍼는 순차적으로 수신된 수평라인의 제1라인들중 제1 및 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 픽셀 데이터를 기억하고 수평라인의 제1라인의 다음 순서의 라인이 수신되고 있는 동시에 제1출력 버스상으로 상기 컨발빙 수단으로 이전에 순차적으로 수신된 수평라인의 제1라인에 대한 픽셀 데이터를 출력하는 제1더블 버퍼링 수단과, 순차적으로 수신한 수평 라인의 2개의 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 픽셀 데이터를 기억하며 수평라인의 제2라인의 다음 순서의 라인이 수신되고 있는 동시에 제2출력 버스상으로 상기 컨발빙 수단으로 이전에 순차적으로 수신한 수평 라인의 제2라인에 대한 픽셀 데이터를 출력하는 제2더블 버퍼링 수단과, 제2출력 버스상으로 상기 제2더블 버퍼링 수단에 의해 출력되고 있는 수평라인의 제2라인에 대한 픽셀 데이터를 수신하는 동시에 상기 제2더블 버퍼링 수단으로부터 수평라인의 또다른 제2라인을 수신하면서 제3버스상으로 상기 컨발빙 수단으로 수평라인의 기억된 제2라인에 대한 기억된 픽셀 데이터를 전송하기 이전에 수평 라인의 수신된 제2라인을 기억하여 하나의 수평 라인 주기만큼 지연시키는 지연 버퍼링 수단을 포함하는 것을 특징으로 하는 장치.

#### 청구항 12

제11항에 있어서, 상기 제1 및 제2더블 버퍼링 수단은 수평 라인의 제1 및 제2라인의 각 픽셀의 휘도(Y) 성분에 관한 픽셀 데이터를 기억하는 것을 특징으로 하는 장치.

#### 청구항 13

제12항에 있어서, 상기 픽셀 어셈블리 버퍼는 스프라이트 데이터가 트루 컬러 비디오 포맷으로 기억될 때 순차적으로 수신된 수평 라인의 제1라인들중 제1 및 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 색도(C) 픽셀 데이터를 기억하며 수평 라인의 제1라인의 다음 순서의 라인에 대한 색도 픽셀 데이터가 수신되고 있는 가운데 제4출력 버스상으로 이전에 순차적으로 수신된 수평 라인의 제1라인에 대한 색도 픽셀 데이터를 출력하는 제3더블 버퍼링 수단을 추가로 포함하는 것을 특징으로 하는 장치.

#### 청구항 14

제13항에 있어서, 상기 버퍼링 및 프로세싱 수단은 상기 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3버스상으로의 수평 라인 신호에 응답하여 컬러 파렛트 포맷의 픽셀 데이터를 YUV 컬러 파렛트 출력 신호로 변환하는 컬러 파렛트 변환수단과, 상기 픽셀 어셈블리 버퍼로부터 제1, 제2, 제3 및 제4버스상으로의 휘도 및 색도 수평라인 신호에 응답하여 트루 컬러 YC 포맷의 픽셀 데이터를 트루 컬러 YUV 출력 신호로 변환하는 YC-YUV 디멀티플렉서와, 상기 컬러 파렛트 변환 수단 및 YC-YUV 디멀티플렉서로부터의 출력 신호와 라이브 비디오 신호에 응답하여 상기 픽셀 어셈블리 버퍼로부터 상기 제1, 제2 및 제3버스상으로 수신된 각 픽셀에 제공된 데이터에 따라 상기 컨발빙 수단으로의 전송을 위해 제1 및 제2필드 데이터의 인접한 세 수평라인 각각의 각 픽셀에 대한 세 신호중 하나를 선택하는 멀티플렉싱 수단을 추가로 포함하는 것을 특징으로 하는 장치.

#### 청구항 15

제14항에 있어서, 하나이상의 스프라이트에 대한 수평라인 데이터의 각 픽셀의 휘도값은 픽셀 데이터 워드의 제1다수 비트로서 상기 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3버스상으로 전송되고, 하나이상의 스프라이트의 각 픽셀이 컬러 파렛트로 코딩되는지 또는 트루 컬러 포맷으로 코딩되는지의 여부 및 픽셀이 하나이상의 스프라이트의 일부분을 형성하는지의 여부에 대한 지시는 픽셀 데이터 워드의 제2다수 비트로 코딩되며, 상기 픽셀 데이터 워드의 제2다수 비트는 상기 컨발빙 수단으로의 전송을 위해 상기 멀티플렉싱 수단에 의해 상기 컬러 파렛트 변환 수단 및 상기 YC-YUV 디멀티플렉서로부터의 출력신호와 라이브 비디오 신호중 하나를 선택하는데 사용되는 것을 특징으로 하는 장치.

#### 청구항 16

표준 비율주사식 텔레비전 수상기상에 디스플레이하기 위해 막싱된 비디오 및 그래픽 신호를 처리하기 위한 장치에 있어서, 표준 비율주사식 텔레비전 수상기의 디스플레이의 선택된 소정의 영역에 선택적으로 디스플레이될 하나이상의 각 스프라이트에 대한 스프라이트 데이터를 기억하여 상기 스프라이트 데이터를 포함하는 출력 신호를 전송하는 디지탈 메모리 수단을 포함하는데, 스프라이트 데이터는 표준 텔레비전 수상기상에 디스플레이될 스프라이트 화상의 제1 및 제2필드를 위해 트루 컬러 비디오 또는 컬러 파렛트 데이터 포맷중 하나를 포함하고 하나이상의 스프라이트가 존재할 때 하나이상의 각 스프라이트는 미리 결정된 소정의 우선순위를 가지며, 제1 및 제2필드의 스프라이트 데이터가 상기 디지탈 메모리 수단의 미리 결정된 소정의 위치로 판독되게 하여 제1필드의 스프라이트 데이터의 수평 라인과 제2필드로부터의 스프라이트 데이터의 인접하는 라인을 포함하는 메모리 출력 신호로서 상기 디지탈 메모리 수단으로부터 선택적으로 판독되게 하는 메모리 제어기와, 상기 메모리 제어기로부터의 메모리 출력신호에 응답하여 텔레비전 수상기상에 디스플레이하기 위한 화상의 인접한 세 수평 라인에 대한 순차적인 스프라이트 픽셀 데이터를 포함하는 제1, 제2 및 제3출력 신호를 발생하는 버퍼링 및 프로세싱 수단을 포함하는데, 스프라이트들이 텔레비전 수상기상의 디스플레이 영역상에서 겹쳐질 때 최우선순위의 스프라이트에 대한 픽셀 데이터는 제1, 제2 및 제3출력 신호의 각 픽셀 위치로 언제든지 출력되며, 상기 제1 및

제3출력신호는 제1 및 제2필드중 한 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고, 제2출력신호는 제1 및 제2필드중 나머지 필드의 라인에 대한 스프라이트 픽셀 데이터를 포함하고 스프라이트 데이터가 트루 컬러 포맷에 관련될 때 색도 데이터를 포함하며, 상기 버퍼링 및 프로세싱 수단으로부터 제1, 제2 및 제3출력 신호를 수신하여 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있을 때 텔레비전 수상기로 전송하기 위해 미리 결정된 소정의 픽셀 데이터의 매트릭스의 중심 픽셀에 가중평균을 제공하는 출력 신호를 발생하고 스프라이트가 텔레비전 수상기의 디스플레이의 픽셀 영역에 포함되어 있지 않을 때 텔레비전 수상기의 디스플레이로 라이브 비디오 신호를 전송하는 컨벌빙 수단을 포함하는데, 상기 중심 픽셀은 상기 버퍼링 및 프로세싱 수단으로부터의 제2출력 신호의 일부분인 것을 특징으로 하는 장치.

#### 청구항 17

제16항에 있어서, 상기 버퍼링 및 프로세싱 수단은 상기 디지털 메모리 수단으로부터 제1 및 제2라인상에 디스플레이될 하나이상의 각 스프라이트에 대한 픽셀 데이터의 인접한 수평 라인의 제1 및 제2라인을 판독하는 동시에 하나이상의 스프라이트중 최우선순위를 갖는 스프라이트의 일부분을 형성하는 라인들중 제1 및 제2라인의 각 픽셀에 대한 픽셀 데이터를 출력하는 수단을 포함하는데, 제1라인은 제1 및 제2필드중 한 필드로부터의 라인이고 제2라인은 제1 및 제2필드중 나머지 필드로부터의 라인이며, 제1 및 제2필드중 상기 한 필드 및 상기 나머지 필드의 라인들중 제1 및 제2라인 각각은 순차적으로 출력되는 것을 특징으로 하는 장치.

#### 청구항 18

제17항에 있어서, 상기 버퍼링 및 프로세싱 수단은 픽셀 어셈블리 버퍼를 추가로 포함하는데, 상기 픽셀 어셈블리 버퍼는 순차적으로 수신된 수평라인의 제1라인들중 제1 및 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 픽셀 데이터를 기억하고 수평라인의 제1라인의 다음 순서의 라인에 수신되고 있는 가운데 제1출력 버스상으로 상기 컨벌빙 수단으로 이전에 순차적으로 수신된 수평라인의 제1라인에 대한 픽셀 데이터를 출력하는 제1더블 버퍼링 수단과, 순차적으로 수신한 수평 라인의 2개의 제2라인들의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 픽셀 데이터를 기억하며 수평라인의 제2라인의 다음 순서의 라인에 수신되고 있는 가운데 제2출력 버스상으로 상기 컨벌빙 수단으로 이전에 순차적으로 수신한 수평 라인의 제2라인에 대한 픽셀 데이터를 출력하는 제2더블 버퍼링 수단과, 제2출력 버스상으로 제2더블 버퍼링 수단에 의해 출력되고 있는 수평라인의 제2라인에 대한 픽셀 데이터를 수신하는 동시에 상기 제2더블 버퍼링 수단으로부터 수평라인의 또다른 제2라인을 수신하면서 제3버스상으로 상기 컨벌빙 수단으로 수평라인의 기억된 제2라인에 대한 기억된 픽셀 데이터를 전송하기 이전에 수평 라인의 수신된 제2라인을 기억하여 하나의 수평 라인 주기만큼 지연시키는 지연 버퍼링 수단을 포함하는 것을 특징으로 하는 장치.

#### 청구항 19

제18항에 있어서, 상기 제1 및 제2더블 버퍼링 수단은 수평 라인의 제1 및 제2라인의 각 픽셀의 휘도(Y) 성분에 관한 픽셀 데이터를 기억하는 것을 특징으로 하는 장치.

#### 청구항 20

제19항에 있어서, 상기 픽셀 어셈블리 버퍼는 스프라이트 데이터가 트루 컬러 비디오 포맷으로 기억될 때 순차적으로 수신된 수평 라인의 제1라인들중 제1 및 제2라인의 하나이상의 스프라이트의 각 픽셀에 대한 최우선순위를 갖는 색도(C) 픽셀 데이터를 기억하며 수평 라인의 제1라인의 다음 순서의 라인에 대한 색도 픽셀 데이터가 수신되고 있는 가운데 제4출력 버스상으로 이전에 순차적으로 수신된 수평 라인의 제1라인에 대한 색도 픽셀 데이터를 출력하는 제3더블 버퍼링 수단을 추가로 포함하는 것을 특징으로 하는 장치.

#### 청구항 21

제20항에 있어서, 상기 버퍼링 및 프로세싱 수단은 상기 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3버스상으로의 수평 라인 신호에 응답하여 컬러 파렛트 포맷의 픽셀 데이터를 YUV 컬러 파렛트 출력 신호로 변환하는 컬러 파렛트 변환수단과, 상기 픽셀 어셈블리 버퍼로부터 제1, 제2, 제3 및 제4버스상으로의 휘도 및 색도 수평라인 신호에 응답하여 트루 컬러 YC 포맷의 픽셀 데이터를 트루 컬러 YUV 출력 신호로 변환하는 YC-YUV 디멀티플렉서와, 상기 컬러 파렛트 변환 수단 및 YC-YUV 디멀티플렉서로부터의 출력 신호와 라이브 비디오 신호에 응답하여 상기 픽셀 어셈블리 버퍼로부터 상기 제1, 제2 및 제3버스상으로 수신된 각 픽셀에 제공된 데이터에 따라 상기 컨벌빙 수단으로의 전송을 위해 제1 및 제2필드 데이터의 인접한 세 수평라인 각각의 각 픽셀에 대한 세 신호중 하나를 선택하는 멀티플렉싱 수단을 추가로 포함하는 것을 특징으로 하는 장치.

#### 청구항 22

제21항에 있어서, 하나이상의 스프라이트에 대한 수평라인 데이터의 각 픽셀의 휘도값은 픽셀 데이터 워드의 제1다수 비트로서 상기 픽셀 어셈블리 버퍼로부터 제1, 제2 및 제3버스상으로 전송되고, 하나이상의 스프라이트의 각 픽셀이 컬러 파렛트로 코딩되는지 또는 트루 컬러 포맷으로 코딩되는지의 여부 및 픽셀이 하나이상의 스프라이트의 일부분을 형성하는지의 여부에 대한 지시는 픽셀 데이터 워드의 제2다수 비트로 코딩되며, 상기 픽셀 데이터 워드의 제2다수 비트는 상기 컨벌빙 수단으로의 전송을 위해 상기 멀티플렉싱 수단에 의해 상기 컬러 파렛트 변환 수단 및 상기 YC-YUV 디멀티플렉서로부터의 출력신호와 라이브 비디오 신호중 하나를 선택하는데 사용되는 것을 특징으로 하는 장치.

#### 도면

## 도면1

## 도면2

### 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8