(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6305829号

(P6305829)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

G 11 C 11/4091 (2006.01)

G 11 C 11/405 (2006.01)G 11 C 11/4091 150

G 11 C 11/405

請求項の数 6 (全 37 頁)

(21) 出願番号 特願2014-110882 (P2014-110882)

(22) 出願日 平成26年5月29日 (2014.5.29)

(65) 公開番号 特開2015-8030 (P2015-8030A)

(43) 公開日 平成27年1月15日 (2015.1.15)

審査請求日 平成29年5月17日 (2017.5.17)

(31) 優先権主張番号 特願2013-114562 (P2013-114562)

(32) 優先日 平成25年5月30日 (2013.5.30)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2013-114564 (P2013-114564)

(32) 優先日 平成25年5月30日 (2013.5.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 井上 広樹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 松崎 隆徳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 熱海 知昭

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】半導体装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタ、第2のトランジスタおよび第3のトランジスタを有し、

前記第1のトランジスタのゲートは書き込みワード線に電気的に接続され、

前記第1のトランジスタのソースおよびドレインの一方は第1のビット線に電気的に接続され、

前記第1のトランジスタのソースおよびドレインの他方は、前記第2のトランジスタのゲートに電気的に接続され、

前記第2のトランジスタのソースおよびドレインの一方は、電位V1が供給されるよう

に設定された第1の配線に電気的に接続され、

前記第2のトランジスタのソースおよびドレインの他方は前記第2のビット線に電気的に接続され、

前記第2のトランジスタと前記第2のビット線の間、あるいは前記第2のトランジスタと前記第1の配線の間に前記第3のトランジスタが電気的に接続され、

前記第3のトランジスタのゲートは読み出しワード線に接続された半導体装置において、

前記第1のビット線の電位を電位VHまたは電位VL (VH > VL) とし、かつ、前記第1のトランジスタをオンにし、

前記第1のトランジスタをオフにし、

前記第2のビット線の電位を第2の電位V2とした状態で、浮遊状態とした後、

10

20

前記第3のトランジスタをオンとする駆動方法であり、

前記第2のトランジスタのしきい値をV<sub>t h</sub>、

前記第1のビット線の電位を電位V<sub>H</sub>としたときの、第1のトランジスタをオンする動作と前記第2のビット線を浮遊状態とする動作の間である保持期間の前記第2のトランジスタのゲートの電位をV<sub>3</sub> (< V<sub>H</sub>) とするとき、

V<sub>2</sub> < V<sub>1</sub> < V<sub>3</sub> - V<sub>t h</sub>、であることを特徴とする半導体装置の駆動方法。

【請求項2】

請求項1において、

前記V<sub>H</sub>と前記V<sub>L</sub>の平均値は前記V<sub>1</sub>よりも低いことを特徴とする半導体装置の駆動方法。

10

【請求項3】

請求項1乃至2のいずれか一項において、

前記V<sub>3</sub>は前記V<sub>H</sub>の40%以下であることを特徴とする半導体装置の駆動方法。

【請求項4】

請求項1乃至3のいずれか一項において、

前記第3のトランジスタがN型であるとき、前記第3のトランジスタをオンとするために前記読み出しワード線の電位が前記V<sub>H</sub>に設定されることを特徴とする半導体装置の駆動方法。

【請求項5】

請求項1乃至4のいずれか一項において、

20

さらに前記第2のビット線に接続された第2の配線を有し、前記データを読み出す動作において、前記第2の配線の電位を参照電位とした状態で、浮遊状態とした後、センスアンプによって、前記第2のビット線と前記第2の配線の電位差を增幅し、前記第2の配線の電位を読み出し出力することを特徴とする半導体装置の駆動方法。

【請求項6】

請求項5において、

前記参照電位は、前記V<sub>H</sub>と前記V<sub>L</sub>の平均値であることを特徴とする半導体装置の駆動方法。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、物、方法、または、製造方法に関する。本発明は、例えば、半導体装置、表示装置、発光装置、蓄電装置、それらの駆動方法、または、それらの製造方法に関する。本発明は、例えば、酸化物半導体を有する半導体装置に関する。

【背景技術】

【0002】

特許文献1には酸化物半導体膜を用いたトランジスタと、単結晶シリコンを用いたトランジスタを有する半導体装置が記載されている。また酸化物半導体膜を用いたトランジスタは、オフリーク電流が極めて小さいことが記載されている。

【先行技術文献】

40

【特許文献】

【0003】

【特許文献1】特開2012-256400号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一態様は、誤読み出しの少ない半導体装置を提供する。または、本発明の一態様は、高い保持特性を有し、高信頼性を有する半導体装置の駆動方法を提供する。

【0005】

本発明の一態様は、オフ電流の低い(オフ抵抗の高い)半導体装置の駆動方法などを提供

50

することを課題とする。または、本発明の一態様は、消費電力の低い半導体装置の駆動方法などを提供することを課題とする。または、本発明の一態様は、信頼性の高い半導体層を用いた半導体装置の駆動方法などを提供することを課題とする。

【0006】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0007】

本発明の一態様は、N型あるいはP型の第1のトランジスタ、P型の第2のトランジスタおよび、N型あるいはP型の第3のトランジスタを有し、第1のトランジスタのチャネルが形成される領域は酸化物半導体膜を有し、第1のトランジスタのゲートは書き込みワード線に電気的に接続され、第1のトランジスタのソースおよびドレインの一方は書き込みビット線に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は、第2のトランジスタのゲートに電気的に接続され、第2のトランジスタのソースおよびドレインの一方は一定の電位V1が供給されるように設定された電源線に電気的に接続され、第2のトランジスタのソースおよびドレインの他方は読み出しビット線に電気的に接続され、第2のトランジスタと読み出しビット線の間、あるいは第2のトランジスタと電源線の間に第3のトランジスタが設けられ、第3のトランジスタのゲートは読み出しワード線に電気的に接続された半導体装置において、データを書き込む動作は、書き込みビット線の電位を電位VHまたは電位VL( $VH > VL$ )とし、かつ、第1のトランジスタをオンにし、データを保持する動作は、第1のトランジスタをオフにし、データを読み出す動作は、読み出しビット線の電位を第2の電位V2とした状態で、浮遊状態とし、その後、第3のトランジスタをオンとする駆動方法であり、第2のトランジスタのしきい値をVth、書き込みビット線の電位を電位VHとした場合のデータを保持する動作とデータを読み出す動作の間であるデータ保持期間後の第2のトランジスタのゲートの電位をV3( $< VH$ )とするとき、 $V2 < V1 < V3 - Vth$ 、である。

【0008】

本発明の一態様は、N型あるいはP型の第1のトランジスタ、P型の第2のトランジスタおよびN型あるいはP型の第3のトランジスタを有し、第1のトランジスタのチャネルが形成される領域は酸化物半導体膜を有し、第1のトランジスタのゲートは書き込みワード線に電気的に接続され、第1のトランジスタのソースおよびドレインの一方はビット線に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は、第2のトランジスタのゲートに電気的に接続され、第2のトランジスタのソースおよびドレインの一方は一定の電位V1が供給されるように設定された電源線に電気的に接続され、第2のトランジスタのソースおよびドレインの他方はビット線に電気的に接続され、第2のトランジスタとビット線の間、あるいは第2のトランジスタと電源線の間に第3のトランジスタが設けられ、第3のトランジスタのゲートは読み出しワード線に電気的に接続された半導体装置において、データを書き込む動作は、ビット線の電位を電位VHまたは電位VL( $VH > VL$ )とし、かつ、第1のトランジスタをオンにし、データを保持する動作は、第1のトランジスタをオフにし、データを読み出す動作は、ビット線の電位を第2の電位V2とした状態で、浮遊状態とし、その後、第3のトランジスタをオンとする駆動方法であり、第2のトランジスタのしきい値をVth、ビット線の電位を電位VHとした場合のデータを保持する動作とデータを読み出す動作の間であるデータ保持期間後の第2のトランジスタのゲートの電位をV3( $< VH$ )とするとき、 $V2 < V1 < V3 - Vth$ 、である。

【0009】

本発明の一態様は、N型あるいはP型の第1のトランジスタ、P型の第2のトランジスタ、N型あるいはP型の第3のトランジスタおよび容量素子を有し、第1のトランジスタのチャネルが形成される領域は酸化物半導体膜を有し、第1のトランジスタのゲートは書き

10

20

30

40

50

込みワード線に電気的に接続され、第1のトランジスタのソースおよびドレインの一方はビット線に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は、第2のトランジスタのゲートと容量素子の一方の電極に電気的に接続され、第2のトランジスタのソースおよびドレインの一方は一定の電位V1が供給されるように設定された電源線に電気的に接続され、第2のトランジスタのソースおよびドレインの他方はビット線に電気的に接続され、第2のトランジスタとビット線の間、あるいは第2のトランジスタと電源線の間に第3のトランジスタが設けられ、第3のトランジスタのゲートは読み出しワード線に電気的に接続され、容量素子の他方の電極は容量線に電気的に接続された半導体装置において、データを書き込む動作は、ビット線の電位を電位VHまたは電位VL (VH > VL) とし、かつ、第1のトランジスタをオンにし、データを保持する動作は、第1のトランジスタをオフにし、データを読み出す動作は、ビット線の電位を第2の電位V2とした状態で、浮遊状態とし、その後、第3のトランジスタをオンとするとともに、容量線の電位を電位V3まで上昇させる駆動方法である。

【0010】

また、上記において、電位VHを電位V1、電位VLを電位V2とし、第2のトランジスタのしきい値をVth、ビット線の電位を電位VHとした場合のデータを保持する動作とデータを読み出す動作の間であるデータ保持期間後の第2のトランジスタのゲートの電位の低下分をV(0 < V < V1)とするとき、V2 + V + Vth < V3 < V1 + Vth、あることを特徴とする駆動方法である。

【発明の効果】

【0011】

本発明の一態様である半導体装置は、第2のトランジスタのゲートの電位が、データ保持動作中に変動しても誤読み出しを防止できる。または、本発明の一態様である半導体装置は、高い保持特性を有し、高信頼性を有する。

【図面の簡単な説明】

【0012】

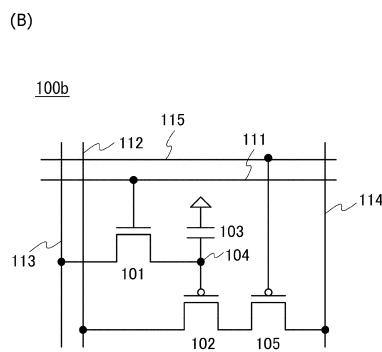

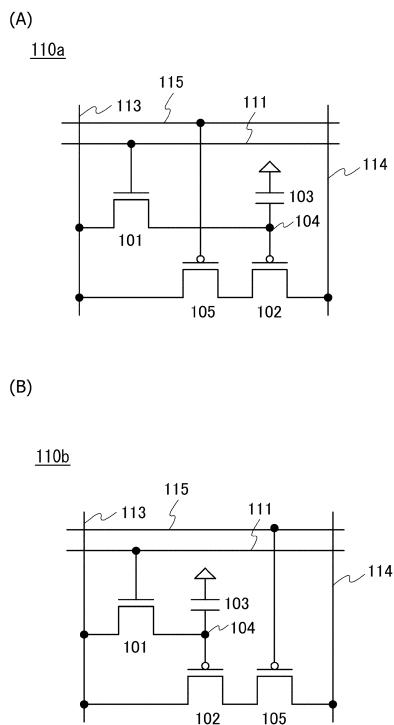

【図1】メモリセルの回路図。

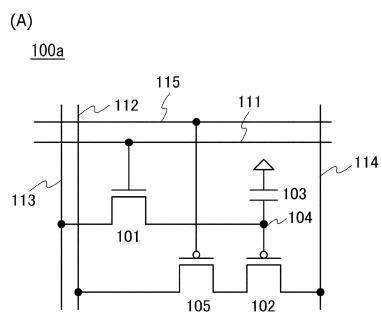

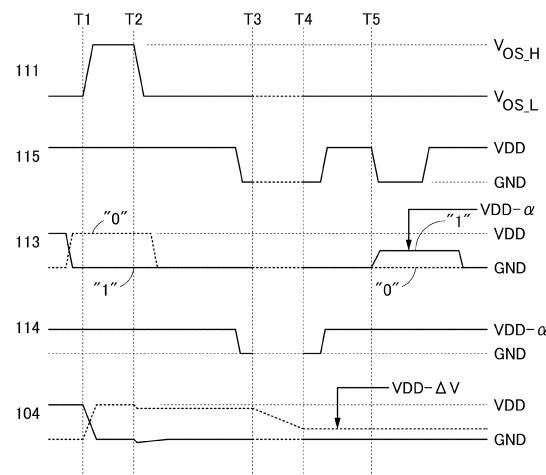

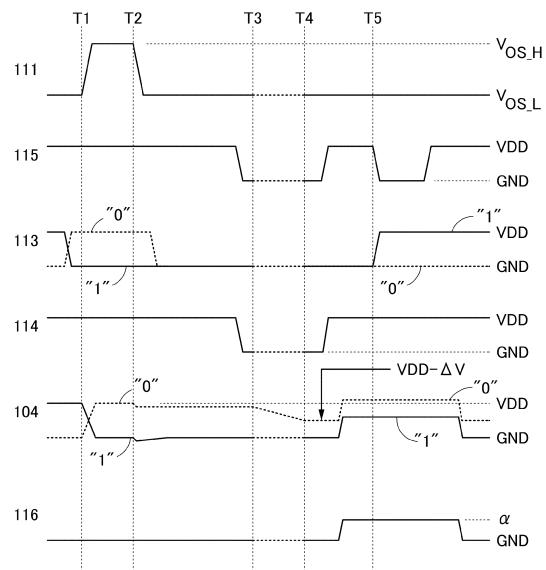

【図2】タイミングチャート。

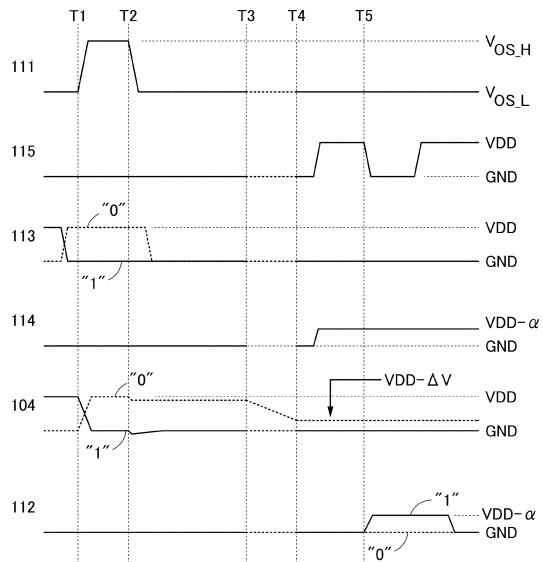

【図3】メモリセルの回路図。

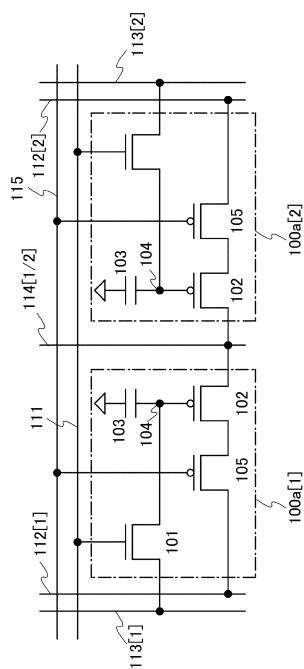

【図4】メモリセルの回路図。

【図5】タイミングチャート。

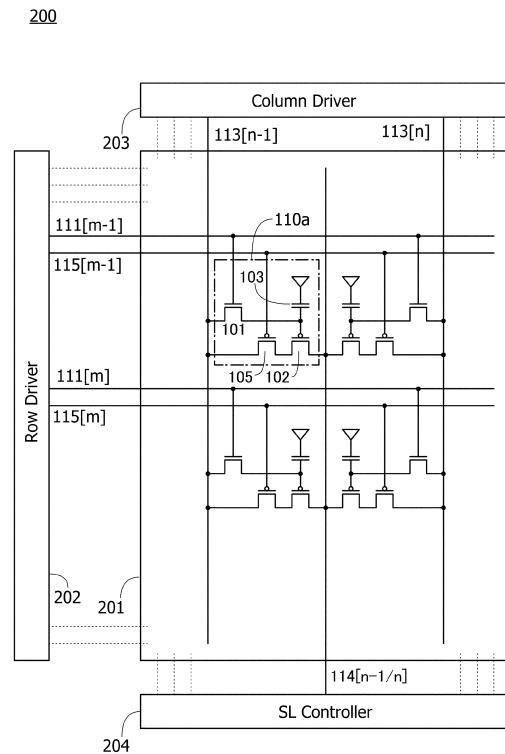

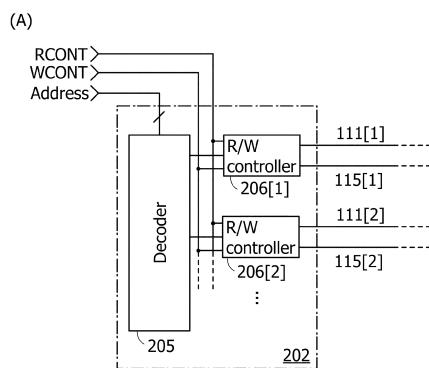

【図6】半導体装置の回路ブロック図。

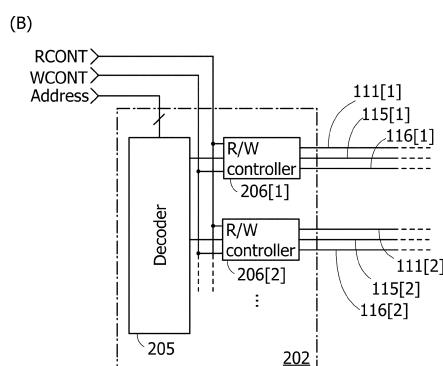

【図7】行ドライバの回路ブロック図。

【図8】列ドライバの回路ブロック図。

【図9】半導体装置の回路ブロック図。

【図10】列ドライバの回路ブロック図。

【図11】タイミングチャート。

【図12】メモリセルの回路図。

【図13】タイミングチャート。

【図14】メモリセルの回路図。

【図15】メモリセルの回路図。

【図16】タイミングチャート。

【図17】メモリセルの回路図。

【図18】メモリセルの回路図。

【図19】タイミングチャート。

【図20】半導体装置の回路ブロック図。

【図21】トランジスタの断面図。

【図22】半導体装置の作製工程を示す断面図。

【図23】電子機器。

【発明を実施するための形態】

10

20

30

40

50

**【 0 0 1 3 】**

本発明の実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いることがある。

**【 0 0 1 4 】**

本明細書に添付した図面では、構成要素を機能ごとに分類し、互いに独立したブロックとしてブロック図を示しているが、実際の構成要素は機能ごとに完全に切り分けることが難しく、一つの構成要素が複数の機能に係わることもあり得る。

10

**【 0 0 1 5 】**

なお、トランジスタのソースとは、活性層として機能する半導体の一部であるソース領域、或いは上記半導体に電気的に接続されたソース電極も意味する。同様に、トランジスタのドレインとは、活性層として機能する半導体の一部であるドレイン領域、或いは上記半導体に電気的に接続されたドレイン電極も意味する。また、ゲートはゲート電極も意味する。

**【 0 0 1 6 】**

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、または／および、一つもしくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、または置き換えなどをおこなうことが出来る。

20

**【 0 0 1 7 】**

なお、図は、理想的な例を模式的に示したものであり、図に示す形状または値などに限定されない。例えば、製造技術による形状のばらつき、誤差による形状のばらつき、ノイズによる信号、電圧、もしくは電流のばらつき、または、タイミングのずれによる信号、電圧、もしくは電流のばらつきなどを含むことが可能である。

**【 0 0 1 8 】**

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」又は「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

30

**【 0 0 1 9 】****（実施の形態1）**

図1(A)にメモリセル100aを示す。なお、本明細書では、メモリセルとはメモリ機能を有する半導体装置という意味であるので、メモリ機能以外の機能を有してもよい。メモリセル100aは、トランジスタ101、トランジスタ102、容量素子103、トランジスタ105を有する。

**【 0 0 2 0 】**

トランジスタ101のチャネルが形成される領域は酸化物半導体膜を有している。したがって、トランジスタ101はオフ電流が極めて低い（オフ抵抗が極めて高い）という特性を有する。トランジスタ101はデータの書き込みの際にオンとなることから書き込みトランジスタとも呼ばれる。トランジスタ101はN型またはP型のトランジスタであるが、以下ではN型であるとして説明する。

40

**【 0 0 2 1 】**

トランジスタ101のゲートは配線111に電気的に接続される。配線111は書き込みワード線として機能することができる。なお、トランジスタ101が薄膜トランジスタである場合、薄膜半導体層の両面にゲート電極を有してもよい。また、それらのゲート電極の一方が常に一定の電位に保持される構造であってもよい。

**【 0 0 2 2 】**

50

トランジスタ101のソースおよびドレインの一方は配線113に電気的に接続される。配線113は書き込みビット線として機能することができる。

【0023】

トランジスタ101のソースおよびドレインの他方は容量素子103の一方の電極に電気的に接続される。容量素子103の他方の電極は一定の電位に保持されることが好ましい。また、トランジスタ101のソースおよびドレインの他方はトランジスタ102のゲートに電気的に接続される。なお、容量素子は意図的に設けなくてもよいことがある。

【0024】

トランジスタ102はP型のトランジスタである。トランジスタ102のチャネルが形成される領域は酸化物半導体、シリコンなど、様々な材料を用いることができる。トランジスタ102のソースおよびドレインの一方は、トランジスタ105のソースまたはドレインの一方に電気的に接続される。トランジスタ102のソースおよびドレインの他方は配線114に電気的に接続される。

【0025】

トランジスタ105のソースおよびドレインの他方は配線112に電気的に接続される。配線112は読み出しひット線として機能することができる。トランジスタ105のゲートは配線115に電気的に接続される。トランジスタ105は、データの読み出しの際に、トランジスタ102と配線112とを導通させるためのもので、選択トランジスタとも呼ばれる。

【0026】

配線114はソース線または電源線として機能することができる。配線114は一定の電位に保持されることが好ましい。ただし、電源の遮断投入の際に電位の変動があっても構わない。

【0027】

なお、図1(B)に示すメモリセル100bのように、トランジスタ105のソースとドレインをトランジスタ102と配線114の間に配置してもよい。

【0028】

図1(A)のメモリセル100aにおいて、データはノード104の電位として保持される。トランジスタ101のオフ抵抗が十分に高ければ、かなりの長期にわたってデータを保持することができる。理論的には、データの保持期間は、ノード104とその他のノードとの間のすべての容量(容量素子103を含む)と、ノード104とその他のノードとの間のすべての抵抗(トランジスタ101のオフ抵抗を含む)とによって決定される。

【0029】

例えば、容量が30fF、抵抗が $1 \times 10^{-2}$ Ωであれば、時定数は9.5年であるので、10年後には、ノード104の電位(と基準となる電位との差)は当初の35%程度まで低下している。このように電位が低下した場合でも、データの読み出しを誤らない読み出し方法が求められる。

【0030】

以下、図2を用いて、メモリセル100aへのデータの書き込み動作およびメモリセル100aからのデータの読み出し動作を説明する。なお、トランジスタ102、トランジスタ105のしきい値は0未満かつ、-VDDより大きいものとする。

【0031】

(書き込み動作)

データの書き込みは、書き込みビット線である配線113の電位をデータに応じたものにした後、トランジスタ101をオンからオフにすることでおこなわれる。基本的にはDRAMへのデータの書き込み方法と同様である。トランジスタ101は、トランジスタ102やトランジスタ105とはしきい値等が異なるので、ここでは、トランジスタ101をオンとするときには、そのゲートの電位(配線111の電位)をV<sub>os\_H</sub>、トランジスタ101をオフとするときには、そのゲートの電位をV<sub>os\_L</sub>とする、なお、V<sub>os\_L</sub> = GND (< VDD) でもよい。

10

20

30

40

50

## 【0032】

ここでは、データ”1”（二値のうちの一）を書き込むときには配線113の電位をGND、データ”0”（二値のうちの他）を書き込むときには配線113の電位をVDDとする。図2の時間T1で配線111の電位が上昇をはじめ、トランジスタ101がオンとなる。その結果、ノード104の電位は、データに応じたものとなる。例えば、データ”1”を書き込む場合は、GNDに、データ”0”を書き込む場合は、VDDになる。時間T2に配線111の電位が低下をはじめ、トランジスタ101がオフとなり、書き込みは終了する。なお、トランジスタ101がオフとなる際に、トランジスタ101のゲート（および配線111）とノード104との間の容量結合によって、ノード104の電位が若干下降する。

10

## 【0033】

なお、書き込みの際には、配線112、配線114、配線115の電位はどのようなものでもよいが、配線112と配線114の間に電流が流れないようなものとすることが好ましい。例えば、配線112と配線114の間に電位差がある場合には、配線115の電位をトランジスタ105がオフとなるような電位とするといい。例えば、配線112、配線114とも電位がGND以上VDD以下であれば、配線115はVDDとしておくといい。あるいは、配線112と配線114の間の電位差をなくしてもよい。ここでは、配線112、配線114、配線115いずれもGNDとする。

## 【0034】

## （保持動作）

20

データの保持の際には、トランジスタ101をオフとする。図2の時間T3から時間T4が、電源が遮断された状態でのデータを保持している期間（スタンバイ期間）を示す。なお、スタンバイ期間では、すべての配線の電位が同一（ここでは、GND）となる。ここで、ノード104の電位がGNDより高かった場合には、ノード104の電位は徐々に低下する。

## 【0035】

データ”1”が書き込まれていた場合には、ノード104の電位はGNDに近い値であるので、変動は問題とならない。しかし、データ”0”が書き込まれていた場合には、当初は、VDDに近い値であるが、時間の経過とともに低下する。電位の低下分をV(>0)とする。つまり、データ保持期間後のノード104の電位（トランジスタ102のゲートの電位）は(VDD - V)である。上記の条件では、保持の期間が1年程度であれば、電位の低下は10%程度であるが、10年後だと、上記のように当初の35%まで低下してしまう。すなわち、V = 0.65 × VDD、である。ここでは、データ保持を保証する期間経過後に、ノード104の電位がもっとも低下する場合には、(VDD - V<sub>M<sub>A</sub>X</sub>)となるとする。

30

## 【0036】

## （読み出し動作）

データを読み出す動作は、配線112と配線114の電位を異なるものとし、その後、トランジスタ105をオンとすることで、トランジスタ102のソースとドレイン間に電流が流れるか否かで判断する。ノード104の電位により、トランジスタ102の導通状態が異なることで、書き込まれていたデータを判断できる。

40

## 【0037】

具体的には、配線115の電位を適切な値（ここではVDD）としてトランジスタ105をオフとし、また、配線114の電位は(VDD - )(>GND)とする。ただし、は0以上VDD未満である。詳細は後述する。配線112を適切な電位（ここではGND）にプリチャージしたのち、浮遊状態にする。そして、時間T5に、配線115の電位を適切な値（ここではGND）としてトランジスタ105をオンとする。

## 【0038】

データ”1”が書き込まれていた場合には、ノード104の電位はGNDに近い値であるので、トランジスタ102はオンであり、配線112の電位が(VDD - )になる。—

50

方、データ”0”が書き込まれていた場合には、トランジスタ102はオフで、配線112の電位がほとんど変動しない。

【0039】

ここで、問題となるのは、スタンバイ期間の間の電位の降下である。データ”0”が書き込まれていた場合の、ノード104のもっとも低い電位は( $V_{DD} - V_{MAX}$ )であるが、このとき、配線114の電位によっては、トランジスタ102がオンとなり、配線112の電位が( $V_{DD} - \dots$ )になる。

【0040】

このような場合には、データ”0”が書き込まれていたにも関わらず、配線112の電位がデータ”1”が書き込まれていた場合と同じとなるため、データ”1”が書き込まれていたと、誤って判断される。

10

【0041】

したがって、配線114の電位は、トランジスタ102がオンとならないものである必要がある。すなわち、トランジスタ102のしきい値を $V_{th}$ とするとき、 $V_{th} + V_{MAX} < \dots$ 、あればよい。

【0042】

例えば、 $V_{DD} = +1.8 [V]$ 、 $GND = 0 [V]$ 、 $V_{th} = -0.5 [V]$ 、 $V_{MAX} = 1.2 [V]$ とするとき、 $> 0.7 [V]$ とすればよい。この条件では、データ”0”的きの配線112の電位は0[V]のままであり、データ”1”的きの電位は配線114の電位(+1.1[V]未満)まで上昇する。あるいは、 $V_{DD} = +0.9 [V]$ 、 $GND = 0 [V]$ 、 $V_{th} = -0.4 [V]$ 、 $V_{MAX} = 0.6 [V]$ とするとき、 $> 0.2 [V]$ とすればよい。この条件では、データ”0”的きの配線112の電位は0[V]のままであり、データ”1”的きの電位は配線114の電位(+0.7[V]未満)まで上昇する。

20

【0043】

なお、上記の条件であれば、 $V$ (ただし、 $0 < V < V_{MAX}$ )がいかなる場合にも誤読み出しは発生しない。

【0044】

このようにスタンバイ期間において、ノード104の電位が、当初より60%以上低下する場合(当初の電位の40%以下である場合)には、配線114の電位を $V_{DD}$ よりも低いものとすることが好ましい。

30

【0045】

なお、データ”0”的きに当初書き込んだ電位が $V_{DD}$ であるのに、配線112に出力される電位は $GND$ である。このようにデータが反転されて出力されることに注意する必要がある。また、出力電位は $V_{DD}$ よりも低いので、インバータあるいは、後述するセンスアンプを用いて増幅するとよい。

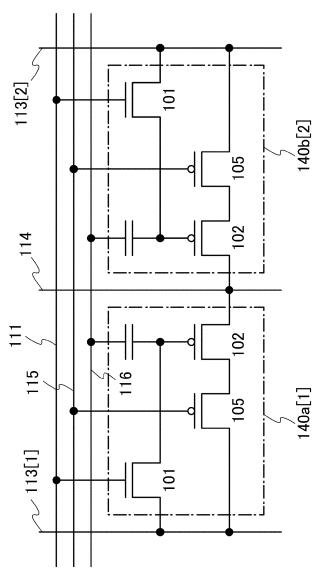

【0046】

上記の説明から明らかであるが、配線114の電位はデータの読みだし時には、特定の値とすることが求められる。なお、図3に示すように2つのメモリセル100a[1]および100a[2]で共有してもよい。また、3つ以上のメモリセルで共有してもよい。また、配線114は、配線112と平行であるだけでなく、直角その他の角度で交差してもよいし、マトリクス状であってもよい。

40

【0047】

(実施の形態2)

図4(A)にメモリセル110aを示す。メモリセル110aは、トランジスタ101、トランジスタ102、容量素子103、トランジスタ105を有する。これらは実施の形態1で説明したものと同様である。

【0048】

トランジスタ101のゲートは配線111に電気的に接続される。トランジスタ101のソースおよびドレインの一方は配線113に電気的に接続される。トランジスタ101の

50

ソースおよびドレインの他方は容量素子 103 の一方の電極に電気的に接続される。トランジスタ 101 のソースおよびドレインの他方はトランジスタ 102 のゲートにも電気的に接続される。

【0049】

トランジスタ 102 のソースおよびドレインの一方は、トランジスタ 105 のソースまたはドレインの一方に電気的に接続される。トランジスタ 102 のソースおよびドレインの他方は配線 114 に電気的に接続される。トランジスタ 105 のソースおよびドレインの他方は配線 113 に電気的に接続される。トランジスタ 105 のゲートは配線 115 に電気的に接続される。

【0050】

配線 111、配線 114、配線 115 の機能は実施の形態 1 で説明したものと同様である。メモリセル 110a では、配線 112 の機能を配線 113 が実施することができる。すなわち、メモリセル 110a では、配線 113 は書き込みビット線でもあり、読み出しビット線でもある。

【0051】

なお、図 4 (B) に示すメモリセル 110b のように、トランジスタ 105 をトランジスタ 102 と配線 114 の間に配置してもよい。

【0052】

以下、図 5 を用いて、メモリセル 110a へのデータの書き込み動作およびメモリセル 110a からのデータの読み出し動作を説明する。なお、トランジスタ 102、トランジスタ 105 のしきい値は 0 未満かつ、-VDD より大きいものとする。実施の形態 1 と同様な操作については詳細な説明は省略することがある。

【0053】

(書き込み動作)

時間 T1 から、配線 111 の電位を上昇させ、 $V_{OS\_H}$  として、トランジスタ 101 をオンとする。また、配線 113 の電位は、GND または VDD とする。実施の形態 1 と同様に、データ "1" を書き込むときには配線 113 の電位を GND、データ "0" を書き込むときには配線 113 の電位を VDD とする。

【0054】

なお、この際、配線 113 と配線 114 の間に電流が流れないようにすることが好ましい。例えば、配線 113 と配線 114 の間に電位差をなくしてもよい。すなわち、配線 114 の電位を配線 113 と同様、データに応じて変動させるとよい。

【0055】

より効果的な方法は、配線 115 の電位をトランジスタ 105 がオフとなるような電位とすることである。ここでは、配線 113、配線 114 の電位は VDD 以下なので、配線 115 の電位は VDD とする。なお、本実施の形態では配線 114 の電位は、スタンバイ期間以外は、(VDD - ) に維持されるとする。なお、 は実施の形態 1 で説明したものと同じである。

【0056】

(保持動作)

トランジスタ 101 をオフとする。図 5 の時間 T3 から時間 T4 がスタンバイ期間を示す。なお、スタンバイ期間では、すべての配線の電位が同一 (ここでは、GND) となる。

【0057】

(読み出し動作)

配線 114 の電位は、スタンバイ期間が終了したことから、(VDD - ) となる。まず、配線 115 の電位を VDD としてトランジスタ 105 をオフとし、また、配線 113 を GND にプリチャージしたのち、浮遊状態にする。そして、配線 115 の電位を GND としてトランジスタ 105 をオンとする。

【0058】

を実施の形態 1 で示したものとすることで、データ "1" が書き込まれていた場合には

10

20

30

40

50

、ノード104の電位GNDに近い値であるので、トランジスタ102はオンであり、配線113の電位が(VDD-)になる。一方、データ"0"が書き込まれていた場合には、トランジスタ102はオフで、配線113の電位がほとんど変動しない。

【0059】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

【0060】

(実施の形態3)

本実施の形態では、図1、図3、図4で説明したメモリセルを適用できる半導体装置の例について図6、図7(A)、図8乃至図11を用いて説明する。

10

【0061】

(半導体装置200の構成例)

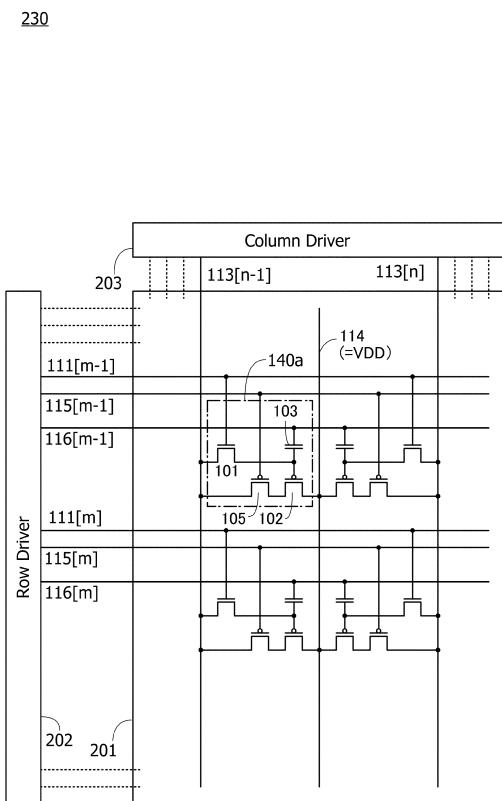

図6は、図4(A)で説明したメモリセル110aを有する半導体装置200の構成例を示すブロック図である。

【0062】

図6に示す半導体装置200は、メモリセルアレイ201、行ドライバ202、列ドライバ203、電源線制御回路204を有する。また、図6では、配線111、配線113、配線114、配線115として、(m-1)行目の配線111[m-1]、配線115[m-1]、m行目の配線111[m]、配線115[m]、(n-1)列目の配線113[n-1]、n列目の配線113[n]、(n-1)列目とn列目で共有される配線114[n-1/n]を示している。

20

【0063】

図6に示すメモリセルアレイ201は、図4(A)で説明したメモリセル110aが、マトリクス状に設けられている。なお、図3に関して説明したように、隣接する2つのメモリセル110aが1つの配線114を共有する。また、メモリセル110aが有する各構成の説明は、図4(A)と同様であり、図4(A)での説明を援用するものとして説明を省略する。

【0064】

行ドライバ202は、メモリセル110aの各行におけるトランジスタ101、トランジスタ105を選択的に導通状態とする機能を備えた回路である。具体的には、配線111、配線112、配線115に信号を与える回路である。行ドライバ202を備えることで、半導体装置200は、メモリセル110aへのデータの書き込みおよび読み出しを行ごとに選択しておこなうことができる。

30

【0065】

列ドライバ203は、メモリセル110aの配線113の電位をプリチャージする機能、配線113を電気的に浮遊状態とする機能、配線113にデータに応じた電位を供給する機能、メモリセル110aに保持されたデータに応じた電位となった配線113の電位を外部へ出力する機能、を備えた回路である。列ドライバ203を備えることで、半導体装置200は、メモリセル110aへのデータの書き込みおよび読み出しをおこなうことができる。

40

【0066】

電源線制御回路204は、メモリセル110aからデータを読み出す際に、配線114の電位を読み出しに適した値(実施の形態1の電位(VDD-)に相当)とするための機能を備えた回路である。なお、半導体装置200に電源が供給される際には、常に、配線114の電位が読み出しに適した値となるように設計されている場合には、定電圧電源で代用できる。

【0067】

(行ドライバ202の構成例)

図7(A)は、図6で説明した行ドライバ202の構成例を示すブロック図である。

【0068】

50

図7(A)に示す行ドライバ202は、デコーダ205、および制御回路206を有する。制御回路206は行ごとに設けられる。1行目には制御回路206[1]が設けられ、2行目には制御回路206[2]が設けられる。また各行の制御回路206は、配線111、配線115に接続される。

【0069】

デコーダ205は、アドレス信号Addressに応じた行を選択するための信号を出力する機能を備えた回路である。

【0070】

制御回路206は、デコーダ205で選択された行へ、書き込み制御信号WCONTあるいは読み出し制御信号RCONTに応じた信号を配線111、配線115に出力する機能を備えた回路である。 10

【0071】

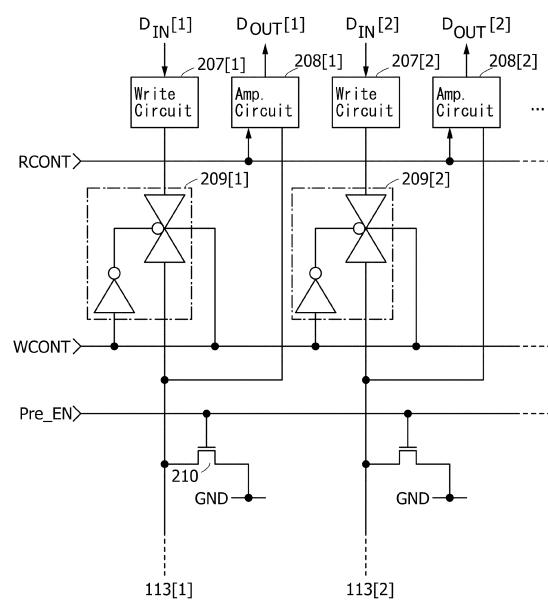

(列ドライバ203の構成例)

図8は、図6で説明した列ドライバ203の一部を示すブロック図である。

【0072】

図8に示す列ドライバ203は、書き込み回路207、増幅回路208、スイッチ回路209、トランジスタ210を有する。前述の各回路およびトランジスタは、列ごとに設けられる。また各列のスイッチ回路209、トランジスタ210は、配線113に接続される。 20

【0073】

書き込み回路207は当該列に入力されるデータD<sub>IN</sub>に応じた電位をスイッチ回路209に出力する回路である。

【0074】

増幅回路208は、配線113の電位を増幅し、データD<sub>OUT</sub>を出力する回路である。例えば、インバータやセンスアンプ等を用いることができる。好ましくは、増幅回路208は、読み出し制御信号RCONTによって動作が制御されるとよい。例えば、クロックドインバータを用いることができる。 20

【0075】

スイッチ回路209は、書き込み回路207と配線113を接続する機能、および配線113を電気的に浮遊状態とする機能を備えた回路である。具体的には、書き込み制御信号WCONTにより、配線113と書き込み回路207とを接続する、あるいは配線113を電気的に浮遊状態とする。図では、アナログスイッチとインバータを備えている回路を示すが、これに限られない。 30

【0076】

トランジスタ210は、プリチャージ電位GNDを配線113に与える機能、および配線113を電気的に浮遊状態とする機能を備えた回路である。具体的には、プリチャージ制御信号Pre\_ENにより、オンとなることで、プリチャージ電位GNDを配線113に与え、その後、オフとなることで、配線113を電気的に浮遊状態とするスイッチである。トランジスタ210を備えることで、列ドライバ203は、プリチャージ電位GNDを配線113に与えた後、配線113を電気的に浮遊状態に保持することができる。 40

【0077】

なお、列ごとに入力するデータD<sub>IN</sub>を振り分けたり、それぞれの列から出力されるデータD<sub>OUT</sub>をまとめたりするためにデコーダを用いてもよい。あるいはシフトレジスタ等のシリアルインパラレルアウト回路(あるいはパラレルインシリアルアウト回路)を用いてもよい。

【0078】

(半導体装置220の構成例)

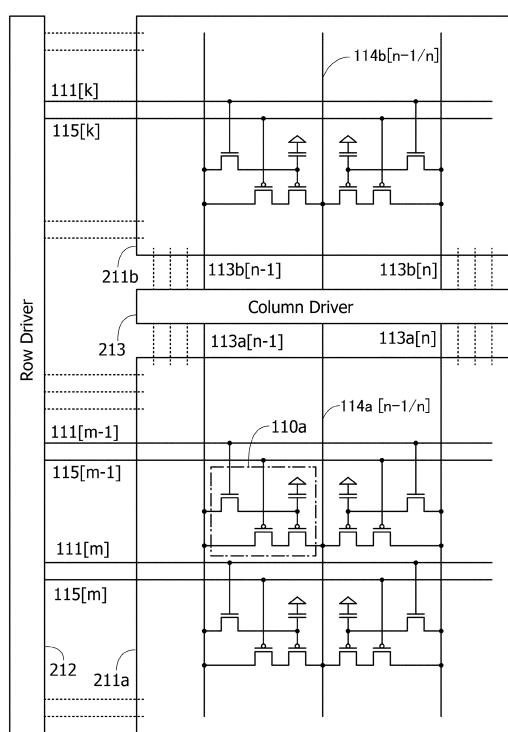

図9は、図4(A)で説明したメモリセル110aを有する半導体装置220の構成例を示すブロック図である。

【0079】

図9に示す半導体装置220は、メモリセルアレイ211a、メモリセルアレイ211b、行ドライバ212、列ドライバ213を有する。メモリセルアレイ211aとメモリセルアレイ211bはほぼ同程度の規模が好ましい。

【0080】

図9に示すメモリセルアレイ211a、メモリセルアレイ211bは、図4(A)で説明したメモリセル110aが、マトリクス状に設けられている。なお、図3に関して説明したように、隣接する2つのメモリセル110aが1つの配線114を共有する。また、メモリセル110aが有する各構成の説明は、図4(A)と同様であり、図4(A)での説明を援用するものとして説明を省略する。

【0081】

また、図9では、配線111、配線113、配線114、配線115として、k行目の配線111[k]、配線115[k]、(m-1)行目の配線111[m-1]、配線115[m-1]、m行目の配線111[m]、配線115[m]、(n-1)列目の配線113a[n-1]、配線113b[n-1]、n列目の配線113a[n]、配線113b[n]、(n-1)列目とn列目で共有される配線114a[n-1/n]、配線114b[n-1/n]を示す。さらに、それらの配線の交点にあるメモリセル110aを示す。

10

【0082】

なお、配線111[k]、配線115[k]、配線113b[n-1]、配線113b[n]、配線114b[n-1/n]はメモリセルアレイ211bに、配線111[m-1]、配線115[m-1]、配線111[m]、配線115[m]、配線113a[n-1]、配線114a[n-1/n]はメモリセルアレイ211aにある。

20

【0083】

行ドライバ212は図6および図7(A)で説明される行ドライバ202と同様な構成とすればよい。

【0084】

列ドライバ213は、配線113a、配線113bの電位をデータに応じた電位とする機能、配線113aと配線113bをプリチャージする機能、配線113aと配線113bを電気的に浮遊状態とする機能、配線114a、配線114bを特定の電位とする機能、および、配線113aと配線113bの間の電位の差を増幅する機能、を備えた回路である。列ドライバ213を備えることで、半導体装置220は、メモリセル110aへのデータの書き込みおよび読み出しをおこなうことができる。

30

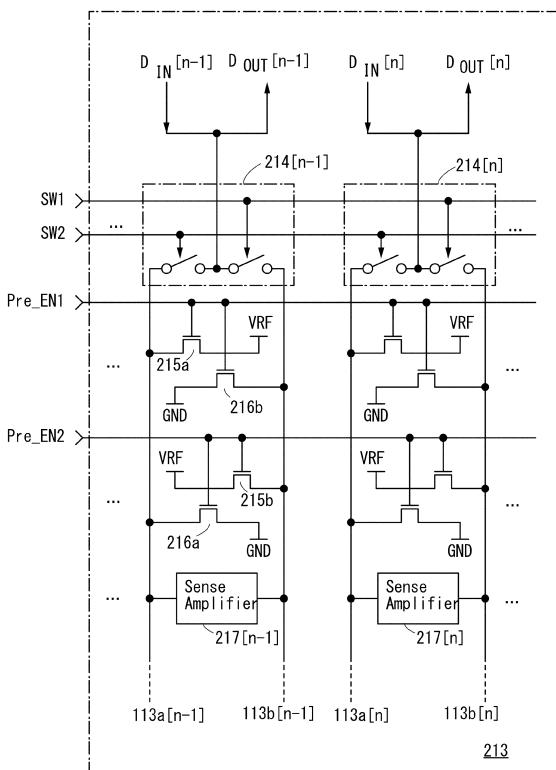

【0085】

図10は、図9で説明した列ドライバ213の構成例を示すブロック図である。図10に示す列ドライバ213は、スイッチ回路214、トランジスタ215a、トランジスタ215b、トランジスタ216a、トランジスタ216b、センスアンプ217を有する。なお、図示していないが、列ドライバ213は、読み出しに適した電位(実施の形態1で説明した電位(VDD- )に相当)を配線114a、配線114bに与える機能を有する。

40

【0086】

各列のスイッチ回路214、トランジスタ215a、トランジスタ215b、トランジスタ216a、トランジスタ216bは、配線113aまたは配線113bの一方または双方に接続される。センスアンプ217は配線113aと配線113bの双方に接続される。

【0087】

スイッチ回路214は、配線113aまたは配線113bの一方または双方とデータの出入力にかかわる回路(図示せず)との導通を制御する機能、および配線113aまたは配線113bを電気的に浮遊状態とする機能を備えた回路である。例えば、アナログスイッチとインバータを備える。スイッチ制御信号SW1およびスイッチ制御信号SW2による

50

制御により、配線 113a あるいは配線 113b にデータ D<sub>IN</sub> を入力することや、配線 113a あるいは配線 113b からデータ D<sub>OUT</sub> を出力することや、配線 113a あるいは配線 113b の一方あるいは双方を電気的に浮遊状態にすることができる。

【0088】

トランジスタ 215a、トランジスタ 215b は、それぞれ、参照電位 VRF を配線 113a、配線 113b に与える機能を、トランジスタ 216a、トランジスタ 216b は、それぞれ、電位 GND を配線 113a、配線 113b に与える機能を有する。

【0089】

参照電位 VRF は、例えば、電位 VDD と電位 GND の平均値（以下、VDD/2、という）や電位 VDD と電位 GND の差を N 等分したものと電位 GND に足した値 (= GND + (VDD - GND) / N、(N = 3, 4, 5, ...)、以下、VDD/N、という）等を用いることができる。なお、読み出しに適切な電位 (VDD - ) としては、実施の形態 1 の条件を満たし、かつ、参照電位 VRF より高い電位であればよく、VDD/N 等を用いることができる。例えば、参照電位 VRF として、VDD/4、電位 (VDD - ) として、VDD/2 を用いてもよい。

10

【0090】

プリチャージ制御信号 Pre\_EN1 あるいはプリチャージ制御信号 Pre\_EN2 による制御で、配線 113a と配線 113b の一方には、参照電位 VRF を、他方には電位 GND を与えることができる。なお、プリチャージ制御信号 Pre\_EN1 とプリチャージ制御信号 Pre\_EN2 が同時にアクティブになることはない。

20

【0091】

例えば、プリチャージ制御信号 Pre\_EN1 がアクティブであれば、配線 113a は参照電位 VRF に、配線 113b は電位 GND にプリチャージされる。逆に、プリチャージ制御信号 Pre\_EN2 がアクティブであれば、配線 113a は電位 GND に、配線 113b は参照電位 VRF にプリチャージされる。

【0092】

プリチャージ完了後、プリチャージ制御信号 Pre\_EN1 およびプリチャージ制御信号 Pre\_EN2 が非アクティブとなることで、トランジスタ 215a、トランジスタ 215b、トランジスタ 216a、トランジスタ 216b がオフとなり、配線 113a および配線 113b を電気的に浮遊状態とできる。

30

【0093】

センスアンプ 217 は、配線 113a と配線 113b の電位差を増幅する機能を有する。センスアンプ 217 の電源電位を VDD と GND とすれば、増幅後には、配線 113a と配線 113b の電位は、一方が VDD、他方が GND となる。

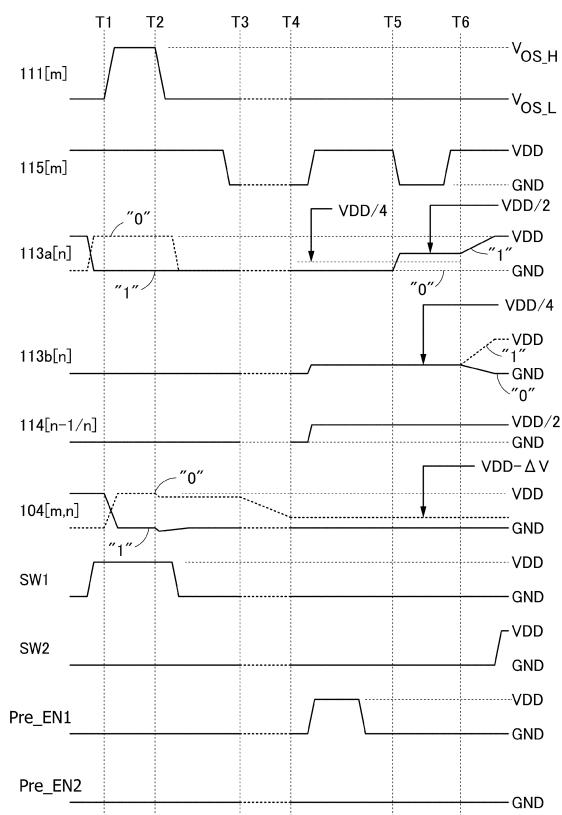

【0094】

（半導体装置 220 の駆動方法の具体例）

図 11 を用いて、半導体装置 220 の駆動方法の一例を説明する。図 11 は配線 111[m]、配線 115[m]、配線 113a[n]、配線 113b[n]、配線 114[n-1/n]、第 m 行第 n 列のメモリセル 110a[m, n] のノード 104[m, n] の電位の変動、およびスイッチ制御信号 SW1、スイッチ制御信号 SW2、プリチャージ制御信号 Pre\_EN1、プリチャージ制御信号 Pre\_EN2 の状態を示す。なお、参照電位 VRF は VDD/4 とする。

40

【0095】

時間 T1 の少し前にスイッチ制御信号 SW1 がアクティブ（電位 VDD）となり、それによって、データの入力に関わる回路（図示せず）とメモリセルアレイ 211a の配線 113a が接続される。配線 113a[n] はデータに応じた電位となる。なお、図では、時間 T1 の時点での配線 113b[n] の電位が GND であるとしているが、この時点では、配線 113b[n] は浮遊状態であり、かつ、接続しているトランジスタからのリード電流等により、実際には、VDD と GND の間の電位となっていることが多い。

【0096】

50

その後、行ドライバ212が配線111[m]を選択し、時間T1から時間T2の間に、トランジスタ101がオンとなり、メモリセル110a[m, n]にデータが書き込まれる。

【0097】

その後、時間T3から時間T4の間、半導体装置220はスタンバイ期間に入り、メモリセル110a[m, n]にデータ"0"が書き込まれていた場合には、ノード104[m, n]の電位が(VDD - V)まで低下する。

【0098】

スタンバイ期間終了後、メモリセル110a[m, n]のデータの読み出しをおこなう。まず、配線113a[n]、配線113b[n]を、それぞれ、電位GND、電位VDD/4にプリチャージする。そのために、プリチャージ制御信号Pre\_EN1をアクティブ(電位VDD)とする。また、この例では、配線114の電位はVDD/2とする。なお、 $V_{th} + V_{MAX} < VDD/2$ 、であるとする。

【0099】

プリチャージ完了後、行ドライバ212が配線115[m]を選択し、時間T5からトランジスタ105がオンとなる。ノード104[m, n]の電位がGNDであれば、配線113a[n]の電位はVDD/2となる。一方、ノード104[m, n]の電位が(VDD - V)であれば、配線113a[n]の電位はGNDのままである。

【0100】

その後、センスアンプ217で、配線113a[n]と配線113b[n]の電位差を増幅し、増幅完了後は、スイッチ制御信号SW2をアクティブ(電位VDD)として、配線113b[n]とデータの出力に関わる回路を接続し、データを取り出す。

【0101】

データ"1"が入力されていた場合、ノード104[m, n]の電位はGNDで、増幅前の配線113a[n]の電位はVDD/2であり、これは、配線113b[n]の電位VDD/4より高い。そのため、増幅によって、配線113a[n]の電位はVDDまで上昇する。一方、配線113b[n]の電位はGNDまで低下する。したがって、読み出されたデータはGNDであり、これは当初、入力されたものと同じである。

【0102】

データ"0"が入力されていた場合、ノード104[m, n]の電位は(VDD - V)で、増幅前の配線113a[n]の電位はGNDであり、これは、配線113b[n]の電位VDD/4より低い。そのため、増幅によって、配線113a[n]の電位はGNDのままである一方、配線113b[n]の電位はVDDまで上昇する。したがって、読み出されたデータはVDDであり、これは当初、入力されたものと同じである。

【0103】

以上の例では、メモリセルアレイ211aにあるメモリセル110aのデータの読み出しがあるので、プリチャージ制御信号Pre\_EN2がアクティブとなることはない。メモリセルアレイ211bにあるメモリセル110aのデータの読み出しの場合には、プリチャージ制御信号Pre\_EN2がアクティブとなる。

【0104】

上記の例では、参照電位VRFとしてVDD/4を、配線114の電位として、VDD/2を、それぞれ、用いたが、増幅が安定してできるためには、参照電位VRFは、配線114の電位より0.2V以上高いとよい。また、配線114の電位はGNDより0.2V以上高いとよい。

【0105】

このようにして、半導体装置220を動作させることができる。図9では、配線113a[n]と配線113b[n]の関係は、いわゆる、オープンビット型の配置であるが、フォールデッドビット型の配置としてもよい。一般にフォールデッドビット型の配置とするとノイズによる影響を相殺できるため誤読み出しをより低減できる。

【0106】

10

20

30

40

50

なお、半導体装置 220 の駆動方法は上記に限られない。本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

【0107】

(実施の形態4)

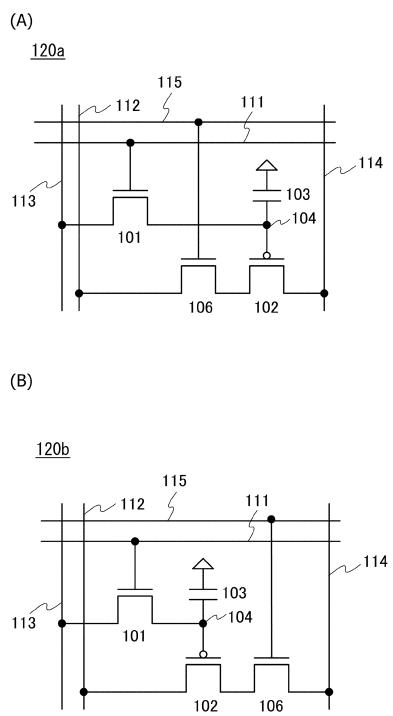

図12(A)にメモリセル120aを示す。メモリセル120aは、トランジスタ101、トランジスタ102、容量素子103、トランジスタ106を有する。メモリセル120aは、メモリセル100a(図1(A))と比較すると、トランジスタ105に相当するトランジスタ106がN型である点が異なる。N型のトランジスタを用いることで応答速度向上、あるいは、集積化が図れる。

【0108】

10

なおメモリセル120bのように、トランジスタ106をトランジスタ102と配線114の間に設けてもよい(図12(B))。メモリセル120bでは、トランジスタ106のソースおよびドレインの一方は、配線114に電気的に接続され、ソースおよびドレンの他方はトランジスタ102のソースおよびドレインの一方に電気的に接続される。

【0109】

実施の形態1で説明したように、配線114を2つのメモリセル120aで共有してもよい。また、3つ以上のメモリセルで共有してもよい。また、配線114は、配線112と平行であるだけでなく、直角その他の角度で交差してもよいし、マトリクス状であってもよい。

【0110】

20

メモリセル120aへのデータの書き込み動作およびメモリセル120aからのデータの読み出し動作を、図13を用いて説明する。なお、実施の形態1乃至3で記載した内容については省略することもある。

【0111】

(書き込み動作)

時間T1から、配線111の電位を $V_{O_S-H}$ まで上昇させて、トランジスタ101をオンとする。配線113の電位はデータに応じたものとする。ここでは、データ"1"を書き込むときには配線113の電位をGND、データ"0"を書き込むときには配線113の電位をVDDとする。その結果、ノード104の電位は、データに応じたものとなる。例えば、データ"1"を書き込む場合は、GNDに、データ"0"を書き込む場合は、VDDになる。時間T2に配線111の電位が低下はじめ、トランジスタ101がオフとなり、書き込みは終了する。

30

【0112】

なお、書き込みの際には、配線112、配線114、配線115の電位はどのようなものでもよいが、配線112と配線114の間に電流が流れないようなものとすることが好ましい。ここでは、配線112はGND、配線114は(VDD - )、配線115はGNDとする。は実施の形態1で説明したものと同じである。

【0113】

(保持動作)

トランジスタ101をオフとする。実施の形態1で説明したように、データ保持を保証する期間で、ノード104の電位がもっとも低下する場合には、(VDD -  $V_{MAX}$ )になるとする。

40

【0114】

(読み出し動作)

配線115の電位を適切な値(ここではGND)としてトランジスタ106をオフとし、また、配線114の電位は(VDD - )とする。配線112を適切な電位(ここではGND)にプリチャージした後、浮遊状態にする。そして、配線115の電位を適切な値としてトランジスタ106をオンとする。

【0115】

ここで、配線115の電位としてはVDDより高い電位(VDDH)を用いてもよい。し

50

かし、トランジスタ 106 のソースとドレインの電位は上記のように (VDD - ) であり、したがって、がトランジスタ 106 のしきい値より大きければ、配線 115 の電位を VDD としても支障はない。一般に VDD がトランジスタ 106 のしきい値より十分に高い場合には、このようなことが可能である。

【0116】

例えば、実施の形態 1 では、 $VDD = +1.8 [V]$ 、 $GND = 0 [V]$ 、 $Vth = -0.5 [V]$ 、 $V_{MAX} = 1.2 [V]$  の場合を取り上げたが、その場合では、 $> 0.7 [V]$  であるので、トランジスタ 106 のしきい値が  $+0.7 [V]$  以下であれば、配線 115 の電位を VDD とできる。

【0117】

データ "1" が書き込まれていた場合には、ノード 104 の電位が GND に近い値であるので、トランジスタ 102 はオンであり、配線 112 の電位が (VDD - ) になり、データ "0" が書き込まれていた場合には、トランジスタ 102 はオフで、配線 112 の電位がほとんど変動しない。

【0118】

なお、図 14 (A)、図 14 (B) に示すメモリセル 130a、メモリセル 130b のように、配線 112 の機能を配線 113 で実施できる構造としてもよい。動作方法については、メモリセル 120a と同様であるので省略する。

【0119】

(実施の形態 5)

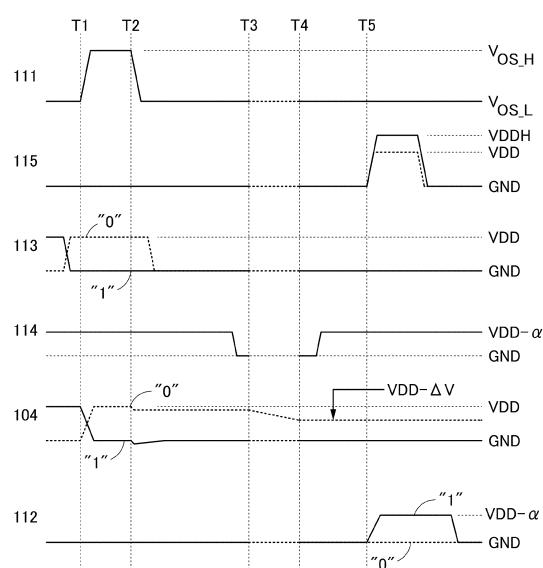

図 15 (A) にメモリセル 140a を示す。メモリセル 140a は、トランジスタ 101、トランジスタ 102、容量素子 103、トランジスタ 105 を有する。

【0120】

トランジスタ 101 のチャネルが形成される領域は酸化物半導体膜を有している。トランジスタ 101 は N 型または P 型のトランジスタであるが、以下では N 型であるとして説明する。

【0121】

トランジスタ 101 のゲートは配線 111 に電気的に接続される。配線 111 は書き込みワード線として機能することができる。なお、トランジスタ 101 が薄膜トランジスタである場合、薄膜半導体層の両面にゲート電極を有してもよい。また、それらのゲート電極の一方が常に一定の電位に保持される構造であってもよい。

【0122】

トランジスタ 101 のソースおよびドレインの一方は配線 113 に電気的に接続される。配線 113 はビット線として機能することができる。

【0123】

トランジスタ 101 のソースおよびドレインの他方は容量素子 103 の一方の電極に電気的に接続される。容量素子 103 の他方の電極は配線 116 に電気的に接続される。また、トランジスタ 101 のソースおよびドレインの他方はトランジスタ 102 のゲートに電気的に接続される。

【0124】

なお、配線 116 の電位を変動させることにより、トランジスタ 102 のゲート (ノード 104) の電位が変動する。配線 116 は容量線とも呼ばれる。

【0125】

トランジスタ 102 は P 型のトランジスタである。トランジスタ 102 のチャネルが形成される領域は酸化物半導体、シリコンなど、様々な材料を用いることができる。トランジスタ 102 のソースおよびドレインの一方は、トランジスタ 105 のソースまたはドレインの一方電気的に接続される。トランジスタ 102 のソースおよびドレインの他方は配線 114 に電気的に接続される。

【0126】

トランジスタ 105 のソースおよびドレインの他方は配線 113 に電気的に接続される。

10

20

30

40

50

トランジスタ 105 のゲートは配線 115 に電気的に接続される。トランジスタ 105 は、データの読み出しの際に、トランジスタ 102 と配線 113 とを導通させるためのもので、選択トランジスタとも呼ばれる。

【0127】

配線 114 はソース線または電源線として機能することができる。配線 114 は一定の電位に保持されることが好ましい。ただし、電源の遮断投入の際に電位の変動があつても構わない。

【0128】

なお、図 15 (B) に示すメモリセル 140b のように、トランジスタ 105 をトランジスタ 102 と配線 114 の間に配置してもよい。

10

【0129】

図 15 (A) のメモリセル 140a において、データはノード 104 の電位として保持される。トランジスタ 101 のオフ抵抗が十分に高ければ、かなりの長期にわたってデータを保持することができる。

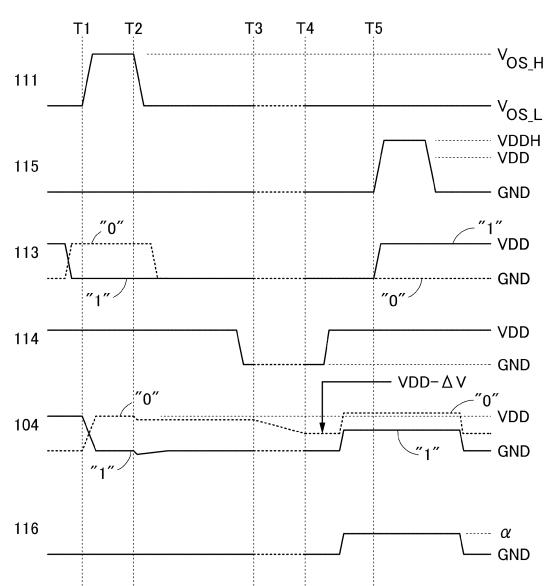

【0130】

以下、図 16 を用いて、メモリセル 140a へのデータの書き込み動作およびメモリセル 140a からのデータの読み出し動作を説明する。なお、トランジスタ 102、トランジスタ 105 のしきい値は 0 未満かつ、-VDD より大きいものとする。

【0131】

(書き込み動作)

20

トランジスタ 101 は、トランジスタ 102 やトランジスタ 105 とはしきい値等が異なるので、ここでは、トランジスタ 101 をオンとするときには、そのゲートの電位 (配線 111 の電位) を  $V_{os\_H}$ 、トランジスタ 101 をオフとするときには、そのゲートの電位を  $V_{os\_L}$  とする、なお、 $V_{os\_L} = GND (< VDD)$  でもよい。

【0132】

ここでは、データ "1" を書き込むときには配線 113 の電位を GND、データ "0" を書き込むときには配線 113 の電位を VDD とする。図 16 の時間 T1 で配線 111 の電位が上昇をはじめ、トランジスタ 101 がオンとなる。その結果、ノード 104 の電位は、データに応じたものとなる。例えば、データ "1" を書き込む場合は、GND に、データ "0" を書き込む場合は、VDD になる。時間 T2 に配線 111 の電位が低下しはじめ、トランジスタ 101 がオフとなり、書き込みは終了する。なお、トランジスタ 101 がオフとなる際に、トランジスタ 101 のゲート (および配線 111) とノード 104 との間の容量結合によって、ノード 104 の電位が若干降下する。

30

【0133】

なお、書き込みの際、配線 113 と配線 114 の間に電流が流れないようにすることができる。例えば、配線 113 と配線 114 の間の電位差をなくしてもよい。すなわち、配線 114 の電位を配線 113 と同様、データに応じて変動させるとよい。

【0134】

より効果的な方法は、配線 115 の電位をトランジスタ 105 がオフとなるような電位とすることである。ここでは、配線 113、配線 114 の電位は GND 以上 VDD 以下とする。したがって、配線 115 の電位を VDD とすれば、トランジスタ 105 がオフとなる。なお、本実施の形態では配線 114 の電位は、スタンバイ期間以外は、VDD に維持されるとするが、その他の電位でもよい。

40

【0135】

(保持動作)

データの保持の際には、トランジスタ 101 をオフとする。図 16 の時間 T3 から時間 T4 が、電源が遮断された状態でのデータを保持している期間 (スタンバイ期間) を示す。なお、スタンバイ期間では、すべての配線の電位が同一 (ここでは、GND) となる。ここで、ノード 104 の電位が GND より高かった場合には、ノード 104 の電位は徐々に低下する。

50

## 【0136】

データ”1”が書き込まれていた場合には、ノード104の電位はGNDに近い値であるので、変動は問題とならない。しかし、データ”0”が書き込まれていた場合には、当初は、VDDに近い値であるが、時間の経過とともに低下する。電位の低下分をVとする。上記の条件では、保持の期間が1年程度であれば、電位の低下は10%程度であるが、10年後だと、上記のように当初の35%まで低下してしまう。すなわち、 $V = 0.65 \times VDD$ 、である。ここでは、データ保持を保証する期間経過後に、ノード104の電位がもっとも低下する場合には、 $(VDD - V_{MAX})$ になるとする。

## 【0137】

(読み出し動作)

10

データを読み出す動作は、配線113と配線114の電位を異なるものとし、その後、トランジスタ105をオンとすることで、トランジスタ102のソースとドレイン間に電流が流れるか否かで判断する。ノード104の電位により、トランジスタ102の導通状態が異なることで、書き込まれていたデータを判断できる。

## 【0138】

具体的には、配線115の電位を適切な値（ここではVDD）としてトランジスタ105をオフとし、また、配線114の電位はVDDとする。配線113を適切な電位（ここではGND）にプリチャージしたのち、浮遊状態にする。そして、配線116の電位を適切な値（ここでは、ただし、 $GND < V < VDD$ ）とする。

## 【0139】

20

この直前まで、データ”1”が書き込まれていた場合には、ノード104の電位はGNDに近い値であるが、配線116の電位がGNDから上昇したことにより、容量素子103を介した容量結合により、電位はほぼとなる。また、データ”0”が書き込まれていた場合には、ノード104の電位はほぼ $(VDD - V_+ - GND)$ となる。その後、時間T5に、配線115の電位を適切な値（ここではGND）としてトランジスタ105をオンとする。

## 【0140】

ここで、データが正しく読み出されるためには、データ”1”が書き込まれていた場合には、トランジスタ102はオンであり、配線113の電位がGNDからVDDまで上昇することが求められ、データ”0”が書き込まれていた場合には、オフであり、配線113の電位がGNDのままであることが求められる。

30

## 【0141】

このためには、トランジスタ102のしきい値をVthとすると、 $V < VDD + Vth$ 、 $VDD - V_+ - GND > VDD + Vth$ 、という2つの不等式を満たすことが求められる。すなわち、 $GND + V_+ + Vth > GND + V_{MAX} + Vth > VDD + Vth$ である。

## 【0142】

例えば、 $VDD = +1.8[V]$ 、 $GND = 0[V]$ 、 $Vth = -0.5[V]$ 、 $V_{MAX} = 1.2[V]$ とするとき、 $0.7[V] < 1.3[V]$ とすればよい。あるいは、 $VDD = +0.9[V]$ 、 $GND = 0[V]$ 、 $Vth = -0.4[V]$ 、 $V_{MAX} = 0.6[V]$ とするとき、 $0.2[V] < 0.5[V]$ とすればよい。

40

## 【0143】

なお、は要求される範囲内の任意の値とできるが、VDDとGNDの平均値 $(VDD/2$ 、ともいう)、あるいは、VDDとGNDの差をN等分したものとGNDとの和 $(VDD/N$ 、ともいう、ただし、 $N = 3, 4, 5, \dots$ )を用いてもよい。前者の例では、 $VDD/2$ は $0.9[V]$ であり、後者の例では、 $VDD/3$ は、 $0.3[V]$ である。いずれも要求される数値範囲内にある。

## 【0144】

このようにスタンバイ期間において、ノード104の電位が、当初より60%以上低下する場合（当初の電位の40%以下である場合）には、読み出し時に配線116の電位を適

50

度に上昇させることにより、ノード 104 の電位を上昇させることが好ましい。

【0145】

なお、データ "0" のときに当初書き込んだ電位が VDD であるのに、配線 116 に出力される電位は GND である。このようにデータが反転されて出力されることに注意する必要がある。

【0146】

上記の説明から明らかであるが、配線 114 は、図 17 に示すように 2 つのメモリセル 140a [1] および 140a [2] で共有してもよい。また、3 つ以上のメモリセルで共有してもよい。また、配線 114 は、配線 113 と平行であるだけでなく、直角その他の角度で交差してもよいし、マトリクス状であってもよい。

10

【0147】

(実施の形態 6)

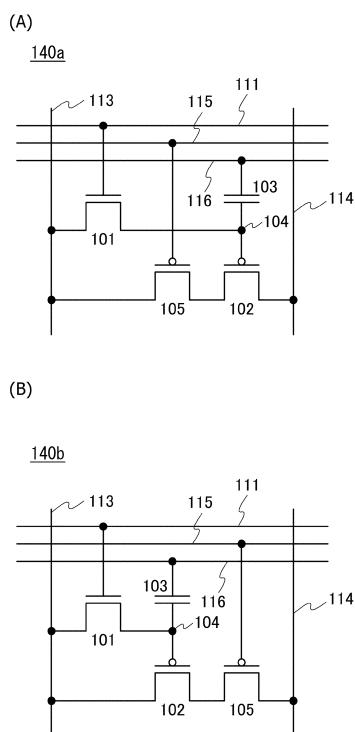

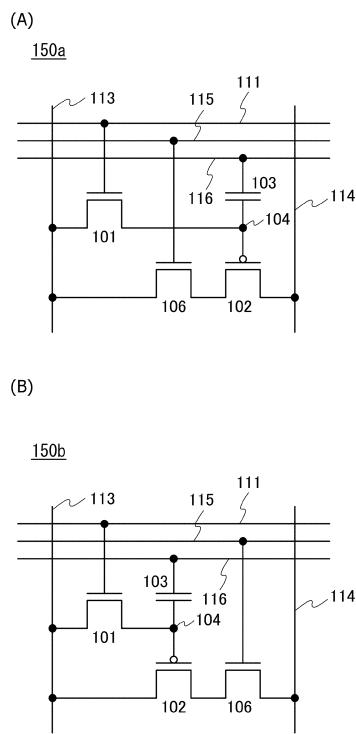

図 18 (A) にメモリセル 150a を示す。メモリセル 150a は、トランジスタ 101、トランジスタ 102、容量素子 103 を有する。これらは実施の形態 5 で説明したものと同様である。メモリセル 150a では、実施の形態 5 のメモリセル 140a のトランジスタ 105 の代わりに N 型のトランジスタ 106 を有する。N 型のトランジスタを用いることで応答速度向上、あるいは、集積化が図れる。

【0148】

なお、図 18 (B) に示すメモリセル 150b のように、トランジスタ 106 をトランジスタ 102 と配線 114 の間に配置してもよい。メモリセル 150b では、トランジスタ 106 のソースおよびドレインの一方は、配線 114 に電気的に接続され、ソースおよびドレインの他方はトランジスタ 102 のソースおよびドレインの一方に電気的に接続される。

20

【0149】

以下、図 19 を用いて、メモリセル 150a へのデータの書き込み動作およびメモリセル 150a からのデータの読み出し動作を説明する。なお、トランジスタ 102 のしきい値は 0 未満かつ、-VDD より大きく、トランジスタ 106 のしきい値は 0 より大きいものとする。実施の形態 1 と同様な操作については詳細な説明は省略することができる。

【0150】

(書き込み動作)

30

時間 T1 から、配線 111 の電位を  $V_{OS-H}$  まで上昇させて、トランジスタ 101 をオンとする。また、配線 113 の電位は、GND または VDD とする。実施の形態 1 と同様に、データ "1" を書き込むときには配線 113 の電位を GND、データ "0" を書き込むときには配線 113 の電位を VDD とする。時間 T2 で配線 111 の電位が低下することで、トランジスタ 101 がオフとなり、書き込みは終了する。

【0151】

なお、書き込みの際には、配線 114、配線 115、配線 116 の電位はどのようなものでもよいが、配線 113 と配線 114 の間に電流が流れないようなものとすることが好ましい。ここでは、配線 113 は GND、配線 114 は VDD、配線 115 は GND とする。

40

【0152】

(保持動作)

トランジスタ 101 をオフとする。図 19 の時間 T3 から時間 T4 がスタンバイ期間を示す。なお、スタンバイ期間では、すべての配線の電位が同一（ここでは、GND）となる。実施の形態 1 で説明したように、データ保持を保証する期間で、ノード 104 の電位がもっとも低下する場合には、(VDD - V<sub>MAX</sub>) になるとする。

【0153】

(読み出し動作)

配線 115 の電位を適切な値（ここでは GND）としてトランジスタ 106 をオフとし、また、配線 114 の電位は VDD とする。配線 113 を適切な電位（ここでは GND）に

50

プリチャージした後、浮遊状態にする。そして、配線 116 の電位を実施の形態 1 で示した電位とした後に、配線 115 の電位を適切な値としてトランジスタ 106 をオンとする。

【0154】

このときの配線 115 の電位としては VDD より高い電位 (VDDH) を用いてもよい。トランジスタ 106 のしきい値を Vth106 とすれば、 $VDDH > VDD + Vth106$ 、であることが好ましい。なお、 $VDDH = Voss_H$  でもよい。

【0155】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

10

【0156】

(実施の形態 7)

本実施の形態では、図 15、図 17、図 18 で説明したメモリセルを適用できる半導体装置の例について図 7 (B)、図 20 を用いて説明する。

【0157】

(半導体装置 230 の構成例)

図 20 は、図 15 (A) で説明したメモリセル 140a を有する、半導体装置 230 の構成例を示すブロック図である。

【0158】

図 20 に示す半導体装置 230 は、図 15 (A) で説明したメモリセル 140a がマトリクス状に設けられたメモリセルアレイ 201、行ドライバ 202、列ドライバ 203 を有する。また、図 20 では、配線 111、配線 113、配線 115、配線 116 として、(m - 1) 行目の配線 111 [m - 1]、配線 115 [m - 1]、配線 116 [m - 1]、m 行目の配線 111 [m]、配線 115 [m]、配線 116 [m]、(n - 1) 列目の配線 113 [n - 1]、n 列目の配線 113 [n] を示している。

20

【0159】

なおメモリセル 140a が有する各構成の説明は、図 15 (A) と同様であり、図 15 (A) での説明を援用するものとして説明を省略する。

【0160】

行ドライバ 202 は、メモリセル 140a の各行におけるトランジスタ 101、トランジスタ 105 を選択的に導通状態とする機能、およびメモリセル 140a の各行におけるノード 104 の電位を選択的に変化させる機能、を備えた回路である。具体的には、配線 111、配線 116、配線 115 に信号を与える回路である。行ドライバ 202 を備えることで、半導体装置 230 は、メモリセル 140a へのデータの書き込みおよび読み出しを行ごとに選択しておこなうことができる。

30

【0161】

列ドライバ 203 は、メモリセル 140a の配線 113 の電位をプリチャージする機能、配線 113 を電気的に浮遊状態とする機能、配線 113 にデータに応じた電位を供給する機能、メモリセル 140a に保持されたデータに応じた電位となった配線 113 の電位を外部へ出力する機能、を備えた回路である。列ドライバ 203 を備えることで、半導体装置 230 は、メモリセル 140a へのデータの書き込みおよび読み出しをおこなうことができる。

40

【0162】

図 7 (B) は、図 20 で説明した行ドライバ 202 の構成例を示すブロック図である。

【0163】

図 7 (B) に示す行ドライバ 202 は、デコーダ 205、および制御回路 206 を有する。制御回路 206 は行ごとに設けられる。1 行目には制御回路 206 [1] が設けられ、2 行目には制御回路 206 [2] が設けられる。また各行の制御回路 206 は、配線 111、配線 116、配線 115 に接続される。

【0164】

50

デコーダ205は、アドレス信号Addressに応じた行を選択するための信号を出力する機能を備えた回路である。

【0165】

制御回路206は、デコーダ205で選択された行へ、書き込み制御信号WCONTあるいは読み出し制御信号RCONTに応じた信号を配線111、配線116、配線115に出力する機能を備えた回路である。

【0166】

なお、列ドライバは、実施の形態3で説明した図8の列ドライバ203を用いることができる。

【0167】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

10

【0168】

(実施の形態8)

実施の形態1乃至7のトランジスタ101のチャネルに適用できる酸化物半導体について説明する。

【0169】

酸化物半導体としては、少なくともインジウム(Indium)あるいは亜鉛(Zinc)を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Gallium)を有することが好ましい。また、スタビライザーとしてスズ(Silver)を有することが好ましい。また、スタビライザーとしてハフニウム(Hafnium)を有することが好ましい。また、スタビライザーとしてアルミニウム(Aluminum)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zirconium)を含むことが好ましい。

20

【0170】

酸化物半導体の中でもIn-Ga-Zn系酸化物、In-Sn-Zn系酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記In-Ga-Zn系酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

30

【0171】

また、他のスタビライザーとして、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Europium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplumbium)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)のいずれか一種または複数種を含んでいてもよい。

【0172】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いる

40

50

ことができる。

【0173】

なお、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素を含んでいてもよい。In-Ga-Zn系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

【0174】

例えば、 $In:Ga:Zn = 1:1:1$  ( $= 1/3:1/3:1/3$ ) あるいは  $In:Ga:Zn = 2:2:1$  ( $= 2/5:2/5:1/5$ ) の原子比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In:Sn:Zn = 1:1:1$  ( $= 1/3:1/3:1/3$ )、 $In:Sn:Zn = 2:1:3$  ( $= 1/3:1/6:1/2$ ) あるいは  $In:Sn:Zn = 2:1:5$  ( $= 1/4:1/8:5/8$ ) の原子比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

10

【0175】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0176】

以下では、酸化物半導体膜の構造について説明する。

【0177】

20

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜などをいう。

【0178】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

【0179】

微結晶酸化物半導体膜は、例えば、1 nm以上10 nm未満の大きさの微結晶(ナノ結晶ともいう。)を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

30

【0180】

CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一边が100 nm未満の立方体内に収まる大きさである。従って、CAAC-OS膜に含まれる結晶部は、一边が10 nm未満、5 nm未満または3 nm未満の立方体内に収まる大きさの場合も含まれる。CAAC-OS膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、CAAC-OS膜について詳細な説明をおこなう。

40

【0181】

CAAC-OS膜を透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって観察すると、結晶部同士の明確な境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

【0182】

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察(断面TEM観察)すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-OS膜の被形成面または上面と平行に配列する。

50

## 【0183】

一方、C A A C - O S 膜を、試料面と概略垂直な方向から T E M によって観察（平面 T E M 観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

## 【0184】

断面 T E M 観察および平面 T E M 観察より、C A A C - O S 膜の結晶部は配向性を有していることがわかる。

## 【0185】

C A A C - O S 膜に対し、X線回折（X R D : X - R a y D i f f r a c t i o n ）装置を用いて構造解析をおこなうと、例えば I n G a Z n O <sub>4</sub> の結晶を有する C A A C - O S 膜の o u t - o f - p l a n e 法による解析では、回折角（2θ）が 31° 近傍にピークが現れる場合がある。このピークは、I n G a Z n O <sub>4</sub> の結晶の（009）面に帰属されることから、C A A C - O S 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。10

## 【0186】

一方、C A A C - O S 膜に対し、c 軸に概略垂直な方向から X 線を入射させる i n - p l a n e 法による解析では、2θ が 56° 近傍にピークが現れる場合がある。このピークは、I n G a Z n O <sub>4</sub> の結晶の（110）面に帰属される。I n G a Z n O <sub>4</sub> の単結晶酸化物半導体膜であれば、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸（c 軸）として試料を回転させながら分析（スキャン）をおこなうと、（110）面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、C A A C - O S 膜の場合は、2θ を 56° 近傍に固定して スキャンした場合でも、明瞭なピークが現れない。20

## 【0187】

以上のことから、C A A C - O S 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 T E M 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。

## 【0188】

なお、結晶部は、C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、C A A C - O S 膜の形状をエッチングなどによって変化させた場合、結晶の c 軸が C A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。30

## 【0189】

また、C A A C - O S 膜中の結晶化度が均一でなくてもよい。例えば、C A A C - O S 膜の結晶部が、C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。40

## 【0190】

なお、I n G a Z n O <sub>4</sub> の結晶を有する C A A C - O S 膜の o u t - o f - p l a n e 法による解析では、2θ が 31° 近傍のピークの他に、2θ が 36° 近傍にもピークが現れる場合がある。2θ が 36° 近傍のピークは、C A A C - O S 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。C A A C - O S 膜は、2θ が 31° 近傍にピークを示し、2θ が 36° 近傍にピークを示さないことが好ましい。

## 【0191】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

## 【0192】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

【0193】

C A A C - O S 膜は、例えば、多結晶である金属酸化物ターゲットを用い、スパッタリング法によって成膜する。

【0194】

また、C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

【0195】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、処理室内に存在する不純物濃度（水素、水、二酸化炭素、および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が - 80 以下、好ましくは - 100 以下である成膜ガスを用いる。

10

【0196】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状又はペレット状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

【0197】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積 % 以上、好ましくは 100 体積 % とする。

20

【0198】

また、酸化物半導体膜は、単数の金属酸化物膜で構成されているとは限らず、積層された複数の金属酸化物膜で構成されていても良い。例えば、第 1 乃至第 3 の金属酸化物膜が順に積層されている半導体膜の場合、第 1 の金属酸化物膜および第 3 の金属酸化物膜は、第 2 の金属酸化物膜を構成する金属元素の少なくとも 1 つを、その構成要素に含み、伝導帯下端のエネルギー準位が第 2 の金属酸化物膜よりも 0.05 eV 以上、0.07 eV 以上、0.1 eV 以上または 0.15 eV 以上、かつ 2 eV 以下、1 eV 以下、0.5 eV 以下または 0.4 eV 以下、真空準位に近い酸化物膜である。さらに、第 2 の金属酸化物膜は、少なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

30

【0199】

上記構成の半導体膜をトランジスタが有する場合、ゲート電極に電圧を印加することで、半導体膜に電界が加わると、半導体膜のうち、伝導帯下端のエネルギー準位が低い第 2 の金属酸化物膜にチャネル領域が形成される。即ち、第 2 の金属酸化物膜とゲート絶縁膜との間に第 3 の金属酸化物膜が設けられることによって、ゲート絶縁膜と離隔している第 2 の金属酸化物膜に、チャネル領域を形成することができる。

【0200】

また、第 3 の金属酸化物膜は、第 2 の金属酸化物膜を構成する金属元素の少なくとも 1 つをその構成要素に含むため、第 2 の金属酸化物膜と第 3 の金属酸化物膜の界面では、界面散乱が起こりにくい。従って、当該界面においてキャリアの動きが阻害されにくいため、トランジスタの電界効果移動度が高くなる。

40

【0201】

また、第 2 の金属酸化物膜と第 1 の金属酸化物膜の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、トランジスタのしきい値が変動してしまう。しかし、第 1 の金属酸化物膜は、第 2 の金属酸化物膜を構成する金属元素の少なくとも 1 つをその構成要素に含むため、第 2 の金属酸化物膜と第 1 の金属酸化物膜の界面には、界面準位が形成されにくい。よって、上記構成により、トランジスタのしきい値等の電気的特性のばらつきを、低減することができる。

【0202】

50

また、金属酸化物膜間に不純物が存在することによって、各膜の界面にキャリアの流れを阻害する界面準位が形成されることはないよう、複数の金属酸化物膜を積層させることが望ましい。積層された金属酸化物膜の膜間に不純物が存在していると、金属酸化物膜間ににおける伝導帯下端のエネルギー準位の連続性が失われ、界面近傍において、キャリアがトラップされるか、あるいは再結合により消滅してしまうからである。膜間ににおける不純物を低減させることで、主成分である一の金属を少なくとも共に有する複数の金属酸化物膜を、単に積層させるよりも、連続接合（ここでは特に伝導帯下端のエネルギー準位が各膜の間で連続的に変化するU字型の井戸構造を有している状態）が形成されやすくなる。

#### 【0203】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa程度から $1 \times 10^{-4}$  Pa程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

10

#### 【0204】

高純度の真性な酸化物半導体を得るためにには、各チャンバー内を高真空排気するのみならず、スパッタリングに用いるガスの高純度化も重要である。上記ガスとして用いる酸素ガスやアルゴンガスの露点を、-40以下、好ましくは-80以下、より好ましくは-100以下とし、使用するガスの高純度化を図ることで、酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

20

#### 【0205】

例えば、第1の金属酸化物膜または第3の金属酸化物膜は、アルミニウム、シリコン、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、スズ、ランタン、セリウムまたはハフニウムを、第2の金属酸化物膜よりも高い原子数比で含む酸化物膜であればよい。具体的に、第1の金属酸化物膜または第3の金属酸化物膜として、第2の金属酸化物膜よりも上述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物膜を用いると良い。前述の元素は酸素と強く結合するため、酸素欠損が酸化物膜に生じることを抑制する機能を有する。よって、上記構成により、第1の金属酸化物膜または第3の金属酸化物膜を、第2の金属酸化物膜よりも酸素欠損が生じにくい酸化物膜にすることができる。

30

#### 【0206】

なお、第1の金属酸化物膜および第3の金属酸化物膜の厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、第2の金属酸化物膜の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下であり、さらに好ましくは3nm以上50nm以下である。

#### 【0207】

3層構造の半導体膜において、第1の金属酸化物膜乃至第3の金属酸化物膜は、非晶質または結晶質の両方の形態を取りうる。ただし、チャネル領域が形成される第2の金属酸化物膜が結晶質であることにより、トランジスタに安定した電気的特性を付与することができるため、第2の金属酸化物膜は結晶質であることが好ましい。

40

#### 【0208】

##### （実施の形態9）

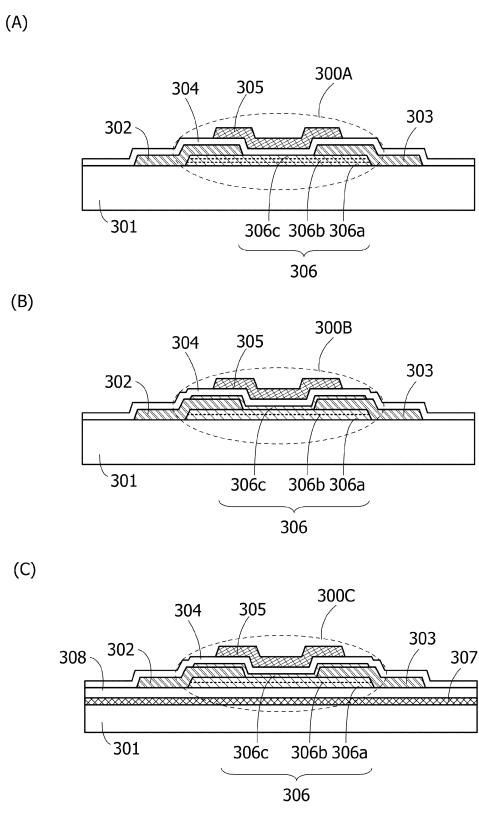

実施の形態3あるいは7で説明した半導体装置200、半導体装置220あるいは半導体装置230、および、実施の形態1乃至7に示したトランジスタ101の断面構造の例を図21および図22を用いて説明する。

#### 【0209】

図21(A)に示すトランジスタ300Aは、絶縁膜301などの上に設けられた半導体膜306と、半導体膜306と電気的に接続されている導電膜302、および導電膜30

50

3と、ゲート絶縁膜304と、ゲート絶縁膜304上に半導体膜306と重畳するように設けられたゲート電極305と、を有する。

【0210】

そして、トランジスタ300Aでは、半導体膜306として、酸化物半導体膜306a乃至酸化物半導体膜306cが、絶縁膜301側から順に積層されている。

【0211】

そして、酸化物半導体膜306aおよび酸化物半導体膜306cは、酸化物半導体膜306bを構成する金属元素の少なくとも1つを、その構成要素に含み、伝導帯下端のエネルギー準位が酸化物半導体膜306bのものよりも0.05eV以上2eV以下、または、0.07eV以上1eV以下、または、0.1eV以上0.5eV以下、または、0.15eV以上0.4eV以下の範囲において真空準位に近い酸化物膜である。さらに、酸化物半導体膜306bは、少なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

【0212】

酸化物半導体膜306cは、図21(B)に示すトランジスタ300Bのように、導電膜302および導電膜303の上層でゲート絶縁膜304と重畳させて設ける構成としてもよい。

【0213】

また、図21(C)に示すトランジスタ300Cのように、半導体膜306と絶縁膜301の間に第2ゲート絶縁膜308を介して、第2ゲート電極307を設けてもよい。

【0214】

トランジスタ300Cが、第2ゲート電極307を有している場合、ゲート電極305には導通状態または非導通状態を制御するための通常の信号が与えられ、第2ゲート電極307には、固定された電位が他から与えられている状態であってもよい。第2ゲート電極307に与える電位の高さを制御することで、トランジスタのしきい値電圧を制御することができる。また、ゲート電極305の電位が第2ゲート電極307の電位と同じとなるように与えられてもよい。

【0215】

また、図21(A)乃至図21(C)では、トランジスタ300A乃至トランジスタ300Cはシングルチャネル構造である場合を例示している。しかし、電気的に接続された複数のゲート電極を有することで、一の活性層にチャネル形成領域を複数有する、マルチチャネル構造であってもよい。

【0216】

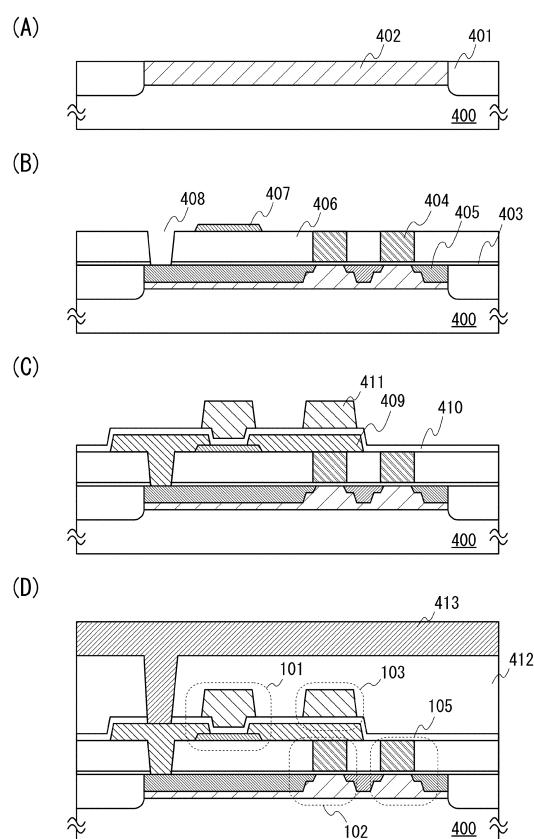

(半導体装置の作製工程例)

図22を用いて、半導体装置200の作製工程の一例を説明する。詳細は特許文献1を参照すればよい。なお、図22は積層構造をわかりやすく表現するものであり、特定の断面を指すものではない。

【0217】

単結晶、多結晶あるいは非晶質のいずれかの半導体基板400に素子分離用絶縁物401とN型のウェル402を設ける(図22(A))。

【0218】

第1ゲート絶縁膜403と第1ゲート配線404を形成し、また、ウェル402にP型の不純物領域405を設ける。不純物領域にシリサイド等のより導電性の高い材料を積層してもよい。不純物領域405はエクステンション領域を有してもよい。

【0219】

さらに、第1層間絶縁物406を設ける。第1層間絶縁物406は単層もしくは多層であり、また、上層への酸素供給能力と下層からの水素や水の上層への移動を遮断する能力を有することが好ましい。そして、第1層間絶縁物406を平坦化しつつ、エッティングする。エッティングは、第1ゲート配線404が露出した段階で停止する。

【0220】

10

20

30

40

50

第1層間絶縁物406上に酸化物半導体膜407を設ける。なお、酸化物半導体以外の半導体を用いてもよい。例えば、2nm以下の厚さのシリコン膜でもよい。さらに、第1層間絶縁物406にコンタクトホール408を形成する(図22(B))。

【0221】

導電性材料を堆積して、コンタクトホール408に導電性材料を埋め込む。このとき、酸化物半導体膜407は、導電性材料で覆われる。導電性材料は単層もしくは多層である。さらに、導電性材料の表面を平坦化する。そして、導電性材料を選択的にエッチングして、第1の配線409を形成する。なお、第1の配線409はコンタクトホール408部分にコンタクトプラグを有する構造でもよい。第1の配線409は多層の導電性材料を有してもよい。

10

【0222】

第1の配線409を覆って、第2ゲート絶縁膜410を形成する。さらに、導電性材料を堆積し、その表面を平坦化する。導電性材料は単層もしくは多層であり、また、上層からの水素や水の下層への移動を遮断する能力を有することが好ましい。表面を平坦化した導電性材料を選択的にエッチングすることで第2ゲート配線411を形成する(図22(C))。

【0223】

第2層間絶縁物412を堆積し、その表面を平坦化する。そして、第2層間絶縁物412に、第1の配線409へ到達するコンタクトホールを形成し、このコンタクトホールを導電性材料で埋め、第2の配線413を形成する。第2の配線413はコンタクトホール部分にコンタクトプラグを有する構造でもよい。第2の配線413は多層の導電性材料を有してもよい。

20

【0224】

このようにして、図22(D)に示すようなトランジスタ101、トランジスタ102、容量素子103、トランジスタ105が形成できる。容量素子103は第1の配線409と第2ゲート配線411の間に第2ゲート絶縁膜410を挟んだ構造となる。

【0225】

(実施の形態10)

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図23に示す。

30

【0226】

図23(A)は携帯型ゲーム機であり、筐体501、筐体502、表示部503、表示部504、マイクロフォン505、スピーカー506、操作キー507、スタイルス508等を有する。なお、図23(A)に示した携帯型ゲーム機は、2つの表示部503と表示部504とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

40

【0227】

図23(B)は携帯データ端末であり、第1筐体511、第2筐体512、第1表示部513、第2表示部514、接続部515、操作キー516等を有する。第1表示部513は第1筐体511に設けられており、第2表示部514は第2筐体512に設けられている。そして、第1筐体511と第2筐体512とは、接続部515により接続されており、第1筐体511と第2筐体512の間の角度は、接続部515により変更が可能である。第1表示部513における映像を、接続部515における第1筐体511と第2筐体5

50

12との間の角度に従って、切り替える構成としても良い。また、第1表示部513および第2表示部514の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

## 【0228】

図23(C)はノート型パーソナルコンピュータであり、筐体521、表示部522、キーボード523、ポインティングデバイス524等を有する。

## 【0229】

図23(D)は電気冷凍冷蔵庫であり、筐体531、冷蔵室用扉532、冷凍室用扉533等を有する。

## 【0230】

図23(E)はビデオカメラであり、第1筐体541、第2筐体542、表示部543、操作キー544、レンズ545、接続部546等を有する。操作キー544およびレンズ545は第1筐体541に設けられており、表示部543は第2筐体542に設けられている。そして、第1筐体541と第2筐体542とは、接続部546により接続されており、第1筐体541と第2筐体542の間の角度は、接続部546により変更が可能である。表示部543における映像を、接続部546における第1筐体541と第2筐体542との間の角度に従って切り替える構成としても良い。

## 【0231】

図23(F)は普通自動車であり、車体551、車輪552、ダッシュボード553、ライト554等を有する。

## 【符号の説明】

## 【0232】

|               |            |

|---------------|------------|

| A d d r e s s | アドレス信号     |

| D I N         | データ        |

| D O U T       | データ        |

| P r e _ E N   | プリチャージ制御信号 |

| P r e _ E N 1 | プリチャージ制御信号 |

| P r e _ E N 2 | プリチャージ制御信号 |

| R C O N T     | 読み出し制御信号   |

| S W 1         | スイッチ制御信号   |

| S W 2         | スイッチ制御信号   |

| V R F         | 参照電位       |

| W C O N T     | 書き込み制御信号   |

| 1 0 0 a       | メモリセル      |

| 1 0 1         | トランジスタ     |

| 1 0 2         | トランジスタ     |

| 1 0 3         | 容量素子       |

| 1 0 4         | ノード        |

| 1 0 5         | トランジスタ     |

| 1 0 6         | トランジスタ     |

| 1 0 0 b       | メモリセル      |

| 1 1 1         | 配線         |

| 1 1 2         | 配線         |

| 1 1 3         | 配線         |

| 1 1 3 a       | 配線         |

| 1 1 3 b       | 配線         |

| 1 1 4         | 配線         |

10

20

30

40

50

|         |          |    |

|---------|----------|----|

| 1 1 4 a | 配線       |    |

| 1 1 4 b | 配線       |    |

| 1 1 5   | 配線       |    |

| 1 1 6   | 配線       |    |

| 1 1 0 a | メモリセル    |    |

| 1 1 0 b | メモリセル    |    |

| 1 2 0 a | メモリセル    |    |

| 1 2 0 b | メモリセル    |    |

| 1 3 0 a | メモリセル    |    |

| 1 3 0 b | メモリセル    | 10 |

| 1 4 0 a | メモリセル    |    |

| 1 4 0 b | メモリセル    |    |

| 1 5 0 a | メモリセル    |    |

| 1 5 0 b | メモリセル    |    |

| 2 0 0   | 半導体装置    |    |

| 2 0 1   | メモリセルアレイ |    |

| 2 0 2   | 行ドライバ    |    |

| 2 0 3   | 列ドライバ    |    |

| 2 0 4   | 電源線制御回路  |    |

| 2 0 5   | デコーダ     | 20 |

| 2 0 6   | 制御回路     |    |

| 2 0 7   | 書き込み回路   |    |

| 2 0 8   | 増幅回路     |    |

| 2 0 9   | スイッチ回路   |    |

| 2 1 0   | トランジスタ   |    |

| 2 1 1 a | メモリセルアレイ |    |

| 2 1 1 b | メモリセルアレイ |    |

| 2 1 2   | 行ドライバ    |    |

| 2 1 3   | 列ドライバ    |    |

| 2 1 4   | スイッチ回路   | 30 |

| 2 1 5 a | トランジスタ   |    |

| 2 1 5 b | トランジスタ   |    |

| 2 1 6 a | トランジスタ   |    |

| 2 1 6 b | トランジスタ   |    |

| 2 1 7   | センスアンプ   |    |

| 2 2 0   | 半導体装置    |    |

| 2 3 0   | 半導体装置    |    |

| 3 0 0 A | トランジスタ   |    |

| 3 0 0 B | トランジスタ   |    |

| 3 0 0 C | トランジスタ   | 40 |

| 3 0 1   | 絶縁膜      |    |

| 3 0 2   | 導電膜      |    |

| 3 0 3   | 導電膜      |    |

| 3 0 4   | ゲート絶縁膜   |    |

| 3 0 5   | ゲート電極    |    |

| 3 0 6   | 半導体膜     |    |

| 3 0 6 a | 酸化物半導体膜  |    |

| 3 0 6 b | 酸化物半導体膜  |    |

| 3 0 6 c | 酸化物半導体膜  |    |

| 3 0 7   | 第2ゲート電極  | 50 |

|       |             |    |

|-------|-------------|----|

| 3 0 8 | 第 2 ゲート絶縁膜  |    |

| 4 0 0 | 半導体基板       |    |

| 4 0 1 | 素子分離用絶縁物    |    |

| 4 0 2 | ウェル         |    |

| 4 0 3 | 第 1 ゲート絶縁膜  |    |

| 4 0 4 | 第 1 ゲート配線   |    |

| 4 0 5 | 不純物領域       |    |

| 4 0 6 | 第 1 層間絶縁物   |    |

| 4 0 7 | 酸化物半導体膜     |    |

| 4 0 8 | コンタクトホール    | 10 |

| 4 0 9 | 第 1 の配線     |    |

| 4 1 0 | 第 2 ゲート絶縁膜  |    |

| 4 1 1 | 第 2 ゲート配線   |    |

| 4 1 2 | 第 2 層間絶縁物   |    |

| 4 1 3 | 第 2 の配線     |    |

| 5 0 1 | 筐体          |    |

| 5 0 2 | 筐体          |    |

| 5 0 3 | 表示部         |    |

| 5 0 4 | 表示部         |    |

| 5 0 5 | マイクロフォン     | 20 |

| 5 0 6 | スピーカー       |    |

| 5 0 7 | 操作キー        |    |

| 5 0 8 | スタイラス       |    |

| 5 1 1 | 筐体          |    |

| 5 1 2 | 筐体          |    |

| 5 1 3 | 表示部         |    |

| 5 1 4 | 表示部         |    |

| 5 1 5 | 接続部         |    |

| 5 1 6 | 操作キー        |    |

| 5 2 1 | 筐体          | 30 |

| 5 2 2 | 表示部         |    |

| 5 2 3 | キー ボード      |    |

| 5 2 4 | ポインティングデバイス |    |

| 5 3 1 | 筐体          |    |

| 5 3 2 | 冷蔵室用扉       |    |

| 5 3 3 | 冷凍室用扉       |    |

| 5 4 1 | 筐体          |    |

| 5 4 2 | 筐体          |    |

| 5 4 3 | 表示部         |    |

| 5 4 4 | 操作キー        | 40 |

| 5 4 5 | レンズ         |    |

| 5 4 6 | 接続部         |    |

| 5 5 1 | 車体          |    |

| 5 5 2 | 車輪          |    |

| 5 5 3 | ダッシュボード     |    |

| 5 5 4 | ライト         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

203

【図9】

220

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

---

フロントページの続き

(56)参考文献 特開2011-129900(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/4091

G 11 C 11/405