(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5191639号

(P5191639)

(45) 発行日 平成25年5月8日(2013.5.8)

(24) 登録日 平成25年2月8日(2013.2.8)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G02F 1/1368 (2006.01)**

**G09G 3/20 (2006.01)**

GO9G 3/36

GO2F 1/133 550

GO2F 1/1368

GO9G 3/20 624B

GO9G 3/20 623A

請求項の数 8 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2006-250989 (P2006-250989)

(22) 出願日

平成18年9月15日 (2006.9.15)

(65) 公開番号

特開2008-70763 (P2008-70763A)

(43) 公開日

平成20年3月27日 (2008.3.27)

審査請求日

平成21年1月22日 (2009.1.22)

(73) 特許権者 502356528

株式会社ジャパンディスプレイイースト

千葉県茂原市早野3300番地

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 盛 育子

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

(72) 発明者 小野 記久雄

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数本の映像信号線と、複数本の走査信号線と、スイッチング素子および画素電極を有し前記画素電極および液晶材料ならびに共通電極により画素容量を形成する画素とを有し、前記映像信号線の延在方向および前記走査信号線の延在方向のそれぞれに複数個ずつ前記画素を並べて構成される表示領域を有する表示パネルと、

前記複数本の映像信号線に映像信号を入力する第1の駆動回路と、

前記複数本の走査信号線に順番に走査信号を入力する第2の駆動回路と、

前記共通電極に入力する共通電圧の電位を制御する共通電圧制御回路とを有する液晶表示装置であって、

前記複数本の映像信号線は、前記走査信号線の延在方向に一列に並んだ複数の画素電極に対して、2つの隣接する画素電極毎に1本ずつ配置されており、

前記複数本の走査信号線は、前記映像信号線の延在方向に並んで隣接する2つの画素電極の間に2本ずつ配置され、かつ、前記走査信号線の延在方向に一列に並んだ複数の画素電極に対して該複数の画素電極を挟むように2本ずつ配置されており、

前記走査信号線の延在方向に一列に並んだ複数の画素は、前記複数の画素の画素電極を挟むように配置された2本の走査信号線のうちの第1の走査信号線にスイッチング素子が接続された画素と、前記2本の走査信号線のうちの第2の走査信号線にスイッチング素子が接続された画素とが、交互に配置されており、

1本の前記映像信号線を挟んで隣接する2つの画素は、各画素のスイッチング素子が前

記1本の前記映像信号線に接続されており、かつ、前記2本の走査信号線のうちの前記第1の走査信号線にスイッチング素子が接続された画素と、前記2本の走査信号線のうちの第2の走査信号線にスイッチング素子が接続された画素との位置が、前記映像信号線の延在方向に並んだ前記2つの画素の組毎に反転しており、

前記共通電圧制御回路は、前記第2の駆動回路が前記走査信号を入力する走査信号線が変わる毎に、共通電圧の電位を、第1の電位と、前記第1の電位よりも電位が高い第2の電位とに交互に切り替えて前記共通電極に入力し、

前記第1の駆動回路は、前記共通電極に前記第1の電位の共通電圧が入力されるときには前記第1の電位と同じ電位または前記第1の電位よりも高い電位の映像信号を入力し、前記共通電極に前記第2の電位の共通電圧が入力されるときには前記第2の電位と同じ電位または前記第2の電位よりも低い電位の映像信号を入力することを特徴とする液晶表示装置。

10

#### 【請求項2】

前記スイッチング素子は、TFT (Thin Film Transistor) であり、前記TFTのゲート電極は前記走査信号線に接続され、前記TFTのドレイン電極またはソース電極のいずれか一方は前記映像信号線に接続され、前記TFTのドレイン電極またはソース電極のうちの前記映像信号線に接続されていないほうは前記画素電極に接続されていることを特徴とする請求項1に記載の液晶表示装置。

#### 【請求項3】

前記表示パネルは、一対の基板を有し、前記画素電極と前記共通電極とは、同じ前記基板の上に形成されており、当該表示パネルは、横電界方式で動作することを特徴とする請求項1に記載の液晶表示装置。

20

#### 【請求項4】

前記表示パネルは、一対の基板を有し、前記画素電極と前記共通電極とは、異なる前記基板の上に形成されており、当該表示パネルは、縦電界方式で動作することを特徴とする請求項1に記載の液晶表示装置。

#### 【請求項5】

一対の基板と、前記一対の基板のうちの一方の基板に形成された複数本の映像信号線と、複数本の走査信号線と、前記映像信号線と前記走査信号線の交差位置であり、かつ画素領域のそれぞれに設けられたスイッチング素子とを有し、前記画素領域には、それぞれ画素電極と共通電極とが形成された表示パネルと、

30

前記複数本の映像信号線に映像信号を入力する第1の駆動回路と、

前記複数本の走査信号線に順番に走査信号を入力する第2の駆動回路と、

前記共通電極に入力する共通電圧の電位を制御する共通電圧制御回路とを有する液晶表示装置であって、

前記複数本の映像信号線は、前記走査信号線の延在方向に一列に並んだ複数の画素電極に対して、2つの隣接する画素電極毎に1本ずつ配置されており、

前記複数本の走査信号線は、前記映像信号線の延在方向に並んで隣接する2つの画素電極の間に2本ずつ配置されており、

1本の前記映像信号線を挟んで隣接する2つの画素電極は、各画素電極のスイッチング素子と前記1本の前記映像信号線とが接続し、

40

前記映像信号線の延在方向に配列されたそれぞれの画素電極は、それぞれの画素電極を挟むように配線された2本の前記走査信号線のうち同じ側の走査信号線とスイッチング素子を介して接続し、

前記走査信号線の延在方向に一列に並んだ複数の画素は、前記複数の画素の画素電極を挟むように配置された2本の走査信号線のうちの第1の走査信号線にスイッチング素子が接続された画素と、前記2本の走査信号線のうちの第2の走査信号線にスイッチング素子が接続された画素とが、交互に配置されており、

前記共通電圧制御回路は、前記第2の駆動回路が前記走査信号を入力する走査信号線が変わる毎に、共通電圧の電位を、第1の電位と、前記第1の電位よりも電位が高い第2の

50

電位とに交互に切り替えて前記共通電極に入力し、

前記第1の駆動回路は、前記共通電極に前記第1の電位の共通電圧が入力されるときには前記第1の電位と同じ電位または前記第1の電位よりも高い電位の映像信号を入力し、前記共通電極に前記第2の電位の共通電圧が入力されるときには前記第2の電位と同じ電位または前記第2の電位よりも低い電位の映像信号を入力することを特徴とする液晶表示装置。

#### 【請求項6】

前記スイッチング素子は、TFT (Thin Film Transistor) であり、前記TFTのゲート電極は前記走査信号線に接続され、前記TFTのドレイン電極またはソース電極のいずれか一方は前記映像信号線に接続され、前記TFTのドレイン電極またはソース電極のうちの前記映像信号線に接続されていないほうは前記画素電極に接続されていることを特徴とする請求項5に記載の液晶表示装置。10

#### 【請求項7】

前記画素電極と前記共通電極とは、同じ基板の上に形成されており、前記表示パネルは、横電界方式で動作することを特徴とする請求項5に記載の液晶表示装置。

#### 【請求項8】

前記画素電極と前記共通電極とは、異なる基板の上に形成されており、前記表示パネルは、縦電界方式で動作することを特徴とする請求項5に記載の液晶表示装置。

#### 【発明の詳細な説明】

20

#### 【技術分野】

#### 【0001】

本発明は、液晶表示装置に関し、特に、液晶テレビなどの解像度の高い液晶表示装置に適用して有効な技術に関するものである。

#### 【背景技術】

#### 【0002】

従来、アクティブマトリクス型の液晶表示装置は、たとえば、液晶テレビなどに用いられている。アクティブマトリクス型の液晶表示装置は、一対の基板の間に液晶材料を封入した液晶表示パネルを有し、前記一対の基板のうちの一方の基板に、TFTなどのスイッチング素子（アクティブ素子と呼ぶこともある）がマトリクス状に配置されている。30

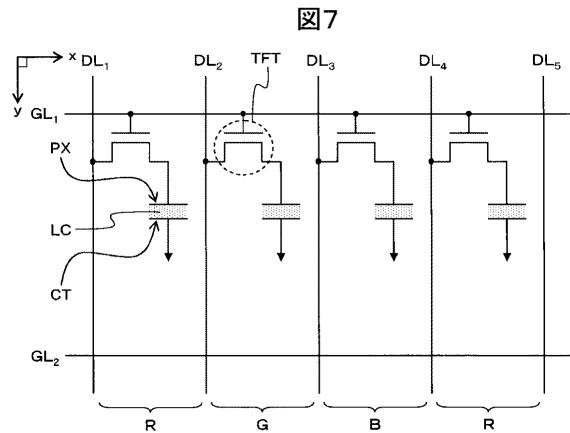

#### 【0003】

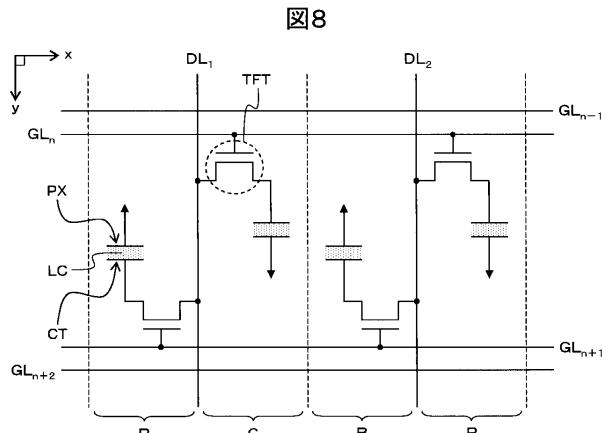

従来の液晶表示パネルは、たとえば、図7に示すような回路構成になっているのが一般的である。図7は、従来の液晶表示パネルの回路構成の一例を示す模式回路図である。なお、図7には、x方向に並んだ4つの画素の構成を示している。

#### 【0004】

従来の液晶表示パネルは、たとえば、前記一対の基板のうちの一方の基板（以下、TFT基板と呼ぶ）に、x方向に長く延びる複数本の走査信号線GL (GL<sub>1</sub>, GL<sub>2</sub>, ...)と、y方向に長く延びる複数本の映像信号線DL (DL<sub>1</sub>, DL<sub>2</sub>, DL<sub>3</sub>, DL<sub>4</sub>, DL<sub>5</sub>, ...)が設けられており、TFTおよび画素電極PXを有する画素が、x方向およびy方向にマトリクス状に配置されている。このとき、前記TFTのゲートは前記走査信号線GLに接続され、前記TFTのドレインは前記映像信号線DLに接続され、前記TFTのソースは画素電極PXに接続されている。また、画素電極PXは、液晶材料LCおよび共通電極CTとともに画素容量（液晶容量と呼ぶこともある）を形成している。40

#### 【0005】

また、液晶テレビなどに用いられるカラー表示に対応した液晶表示パネルの場合、図7に示した4つの画素は、サブ画素と呼ばれ、RGB方式のカラー液晶表示パネルの場合、R（赤色）の表示を行うサブ画素、G（緑色）の表示を行うサブ画素、B（青色）の表示を行うサブ画素の3つのサブ画素で、映像の1ドットが構成されている。このとき、x方向に並んだ複数の画素（サブ画素）は、たとえば、R（赤色）の表示を行うサブ画素、G（緑色）の表示を行うサブ画素、B（青色）の表示を行うサブ画素の順に周期配置されて50

いる。

#### 【 0 0 0 6 】

また、従来の一般的な液晶表示パネルでは、 $x$  方向に一列に並んだ複数の画素に対して 1 本ずつ走査信号線  $GL$  が配置されており、 $x$  方向に一列に並んだ複数の画素の TFT 素子は、共通の走査信号線  $GL$  ( $GL_1$ ) に接続されている。同様に、 $y$  方向に一列に並んだ複数の画素に対して 1 本ずつ映像信号線  $DL$  が配置されており、 $y$  方向に一列に並んだ複数の画素の TFT 素子は、共通の映像信号線  $DL$  に接続されている。

#### 【 0 0 0 7 】

しかしながら、図 7 に示したような画素構成の液晶表示パネルの場合、たとえば、各映像信号線  $DL$  に入力する映像信号（階調電圧）を生成する駆動回路（データドライバ）の数が多くなり、たとえば、消費電力が増加したり、データドライバの発熱量の増加にともない映像信号の電位が不安定になり画質が低下したりするという問題があった。

#### 【 0 0 0 8 】

そのため、近年の液晶表示パネルでは、たとえば、図 8 に示すように、走査信号線  $GL$  の延在方向に一列に並んだ複数の画素に対して、2 つの隣接する画素毎に映像信号線  $DL$  ( $DL_1, DL_2, \dots$ ) を 1 本ずつ配置し、前記一列に並んだ複数の画素を挟むように走査信号線  $GL$  ( $\dots, GL_{n-1}, GL_n, GL_{n+1}, GL_{n+2}, \dots$ ) を 2 本ずつ配置した 2 倍走査線方式と呼ばれる回路構成のものが提案されている。図 8 は、従来の 2 倍走査線方式の液晶表示パネルの回路構成の一例を示す模式回路図である。なお、図 8 には、 $x$  方向に並んだ 4 つの画素の構成を示している。

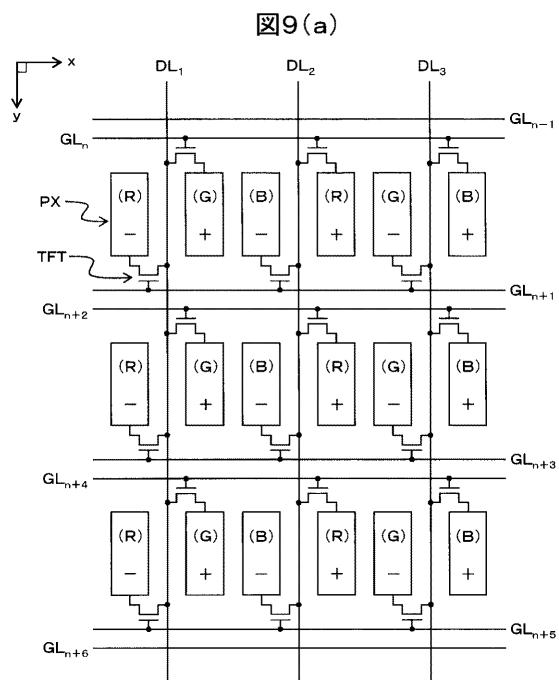

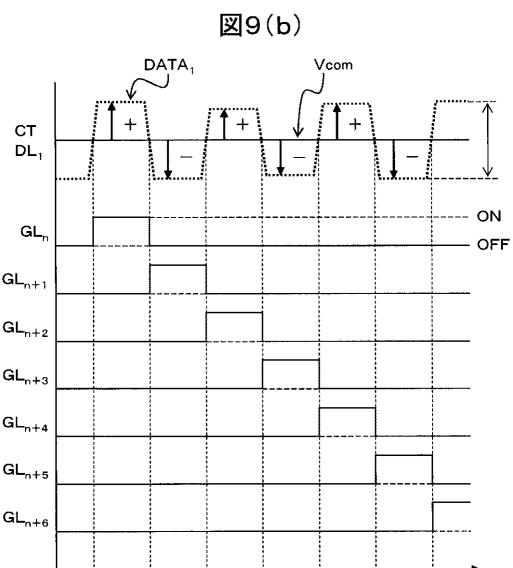

#### 【 0 0 0 9 】

このとき、 $x$  方向に並んだ複数の画素は、TFT のゲートが走査信号線  $GL_{n+1}$  に接続された画素と、TFT のゲートが走査信号線  $GL_n$  に接続された画素とが交互に配置されている。このような回路構成の液晶表示パネルにおける映像の表示方法の一例を図 9 (a) および図 9 (b) に沿って簡単に説明する。図 9 (a) は、従来の 2 倍走査線方式の液晶表示パネルの一構成例と 1 フレーム期間における画素電極の極性を示す模式回路図である。図 9 (b) は、図 9 (a) に示した構成の液晶表示パネルにおける駆動方法の一例を示す模式図である。

#### 【 0 0 1 0 】

図 8 に示したような 2 倍走査線方式の回路構成の液晶表示パネルの場合、 $x$  方向に並んだ複数の画素で構成される列を画素列とすると、たとえば、図 9 (a) に示すように、各画素の TFT と走査信号線  $GL$  および映像信号線  $DL$  との相対的な位置関係（接続関係）は、すべての画素列で一致している。このような構成の表示パネルで、1 フレーム期間分の映像データを表示するときには、たとえば、図 9 (b) に示すように、共通電極 CT に加える共通電圧  $V_{com}$  を一定にしておき、各走査信号線  $GL$  ( $\dots, GL_n, GL_{n+1}, GL_{n+2}, GL_{n+3}, GL_{n+4}, GL_{n+5}, GL_{n+6}, \dots$ ) は、一定の時間間隔で順番に走査信号を ON していく。このとき、ある映像信号線  $DL_1$  には、たとえば、図 9 (b) に示したように、 $GL_n$  の走査信号が ON になるタイミングに合わせて、共通電圧  $V_{com}$  と同じ電位または共通電圧  $V_{com}$  よりも電位の高い映像信号（正極性の階調電圧）を入力し、 $GL_{n+1}$  の走査信号が ON になるタイミングに合わせて、共通電圧  $V_{com}$  と同じ電位または共通電圧  $V_{com}$  よりも電位の低い映像信号（負極性の階調電圧）を入力する。その後、走査信号が ON になる走査信号線が変わる毎に、前記正極性の階調電圧と、前記負極性の階調電圧とを切り替えて入力していく。

#### 【 0 0 1 1 】

しかしながら、図 9 (b) に示したような方法で映像信号および走査信号を入力した場合、1 フレーム期間分の映像データを表示したときの各画素の極性は、たとえば、図 9 (a) に示したようになる。なお、図 9 (a) において、各画素電極  $PX$  に示した「+」は前記正極性の階調電圧が書き込まれていることを意味し、各画素電極  $PX$  に示した「-」は前記負極性の階調電圧が書き込まれていることを意味する。すなわち、図 9 (a) および図 9 (b) に示した構成の液晶表示装置の場合、映像信号線  $DL$  の延在方向に並

10

20

30

40

50

んだ複数の画素の画素電極は階調電圧が同じ極性になる。そのため、たとえば、縦方向の筋が見え、表示品質が低下することがある。

#### 【0012】

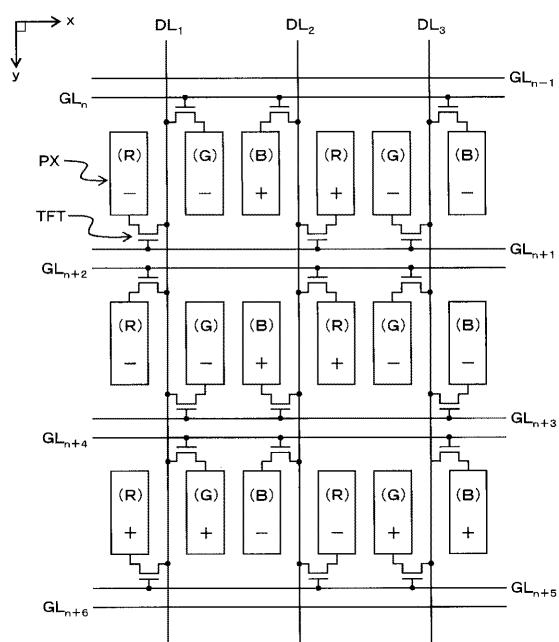

また、前記2倍走査線方式の液晶表示パネルには、たとえば、特許文献1のように、ラインクローリングと呼ばれる現象の発生を防ぎ、表示品位（表示品質）を向上させる回路構成にしたものがある。特許文献1に記載された回路構成は、たとえば、図10に示すような構成であり、映像信号線DLに沿った方向において2の倍数の画素毎に画素電極の極性が反転し、かつ、走査信号線GLに沿った方向において同一のデータ線によって制御される2画素毎に画素電極の極性が反転する液晶駆動電圧を各画素電極に付加するものである。なお、図10は、特許文献1に記載された回路構成を参考してTFTの配置および各画素電極の極性を示した模式図である。10

【特許文献1】特開平11-326869号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0013】

しかしながら、従来の2倍走査線方式の液晶表示パネルの場合、一般に、共通電極CTに加える共通電圧Vcomを一定にしているので、前記データドライバでは、共通電圧Vcomと正極性の最大階調電圧との電位差の2倍の振幅を最大振幅とする映像信号（階調電圧）を生成する必要がある。そのため、液晶テレビなどの高解像度の液晶表示装置の場合、前記2倍走査線方式であっても、データドライバの発熱量が高く、映像信号の電位が不安定になり画質が低下しやすいという問題があった。20

#### 【0014】

また、液晶表示パネルを駆動するときには、たとえば、高コントラスト、低クロストロークで高品位の表示が可能なドット反転駆動、すなわち、走査信号線の延在方向で隣接する2つの画素の画素電極に書き込まれた階調電圧の極性、および映像信号線の延在方向で隣接する2つの画素の画素電極に書き込まれた階調電圧の極性が常に逆の極性になるようにすることが望ましい。

#### 【0015】

しかしながら、たとえば、図9(a)に示したような構成の液晶表示パネルの場合、ドット反転駆動をさせるには、1本の映像信号線DL（たとえば、DL<sub>1</sub>）に加える映像信号を、正極性、負極性、負極性、正極性、正極性、負極性・・・というように、2画素毎に正極性と負極性の順番を反転させるとともに、隣接する2本の映像信号線（たとえば、DL<sub>1</sub>とDL<sub>2</sub>）に加える映像信号の極性を反転させる必要がある。そのため、極性を反転させる回数が多くなり、映像信号の電位が不安定になりやすいという問題があった。30

#### 【0016】

また、たとえば、特許文献1（図10）に示したような構成の液晶表示パネルの場合、ドット反転駆動とは別の駆動方法で表示品質を向上させており、ドット反転駆動させることは難しいという問題がある。

#### 【0017】

本発明の目的は、たとえば、液晶表示パネルに接続されるデータドライバの発熱量を低くし、画質の低下を防ぐことが可能な技術を提供することにある。40

#### 【0018】

本発明の他の目的は、たとえば、2倍走査線方式の液晶表示パネルを、容易にドット反転駆動させることができ可能な技術を提供することにある。

#### 【0019】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0020】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りで50

ある。

【0021】

(1) 複数本の映像信号線と、複数本の走査信号線と、スイッチング素子および画素電極を有し前記画素電極および液晶材料ならびに共通電極により画素容量を形成する画素とを有し、前記映像信号線の延在方向および前記走査信号線の延在方向のそれぞれに複数個ずつ前記画素を並べて構成される表示領域を有する表示パネルと、前記複数本の映像信号線に映像信号を入力する第1の駆動回路と、前記複数本の走査信号線に順番に走査信号を入力する第2の駆動回路と、前記共通電極に入力する共通電圧の電位を制御する共通電圧制御回路とを有する液晶表示装置であって、前記複数本の映像信号線は、前記走査信号線の延在方向に一列に並んだ複数の画素電極に対して、2つの隣接する画素電極毎に1本ずつ配置されており、前記複数本の走査信号線は、前記映像信号線の延在方向に並んで隣接する2つの画素電極の間に2本ずつ配置され、かつ、前記走査信号線の延在方向に一列に並んだ複数の画素電極に対して該複数の画素電極を挟むように2本ずつ配置されており、前記走査信号線の延在方向に一列に並んだ複数の画素は、前記複数の画素の画素電極を挟むように配置された2本の走査信号線のうちの第1の走査信号線にスイッチング素子が接続された画素と、前記2本の走査信号線のうちの第2の走査信号線にスイッチング素子が接続された画素とが、交互に配置されており、1本の前記映像信号線を挟んで隣接する2つの画素は、各画素のスイッチング素子が前記1本の前記映像信号線に接続されており、かつ、前記2本の走査信号線のうちの前記第1の走査信号線にスイッチング素子が接続された画素と、前記2本の走査信号線のうちの第2の走査信号線にスイッチング素子が接続された画素との位置が、前記映像信号線の延在方向に並んだ前記2つの画素の組毎に反転しており、前記共通電圧制御回路は、前記第2の駆動回路が前記走査信号を入力する走査信号線が変わる毎に、共通電圧の電位を、第1の電位と、前記第1の電位よりも電位が高い第2の電位とに交互に切り替えて前記共通電極に入力し、前記第1の駆動回路は、前記共通電極に前記第1の電位の共通電圧が入力されるときには前記第1の電位と同じ電位または前記第1の電位よりも高い電位の映像信号を入力し、前記共通電極に前記第2の電位の共通電圧が入力されるときには前記第2の電位と同じ電位または前記第2の電位よりも低い電位の映像信号を入力する液晶表示装置。10

(2) 前記(1)の液晶表示装置において、前記スイッチング素子は、TFT (Thin Film Transistor) であり、前記TFTのゲート電極は前記走査信号線に接続され、前記TFTのドレイン電極またはソース電極のいずれか一方は前記映像信号線に接続され、前記TFTのドレイン電極またはソース電極のうちの前記映像信号線に接続されていないほうは前記画素電極に接続されている液晶表示装置。30

(3) 前記(1)の液晶表示装置において、前記表示パネルは、一対の基板を有し、前記画素電極と前記共通電極とは、同じ前記基板の上に形成されており、当該表示パネルは、横電界方式で動作する液晶表示装置。

(4) 前記(1)の液晶表示装置において、前記表示パネルは、一対の基板を有し、前記画素電極と前記共通電極とは、異なる前記基板の上に形成されており、当該表示パネルは、縦電界方式で動作する液晶表示装置。

【0022】

(5) 一対の基板と、前記一対の基板のうちの一方の基板に形成された複数本の映像信号線と、複数本の走査信号線と、前記映像信号線と前記走査信号線の交差位置であり、かつ画素領域のそれぞれに設けられたスイッチング素子とを有し、前記画素領域には、それぞれ画素電極と共通電極とが形成された表示パネルと、前記複数本の映像信号線に映像信号を入力する第1の駆動回路と、前記複数本の走査信号線に順番に走査信号を入力する第2の駆動回路と、前記共通電極に入力する共通電圧の電位を制御する共通電圧制御回路とを有する液晶表示装置であって、前記複数本の映像信号線は、前記走査信号線の延在方向に一列に並んだ複数の画素電極に対して、2つの隣接する画素電極毎に1本ずつ配置されており、前記複数本の走査信号線は、前記映像信号線の延在方向に並んで隣接する2つの画素電極の間に2本ずつ配置されており、前記共通電圧制御回路は、前記第2の駆動回路4050

が前記走査信号を入力する走査信号線が変わる毎に、共通電圧の電位を、第1の電位と、前記第1の電位よりも電位が高い第2の電位とに交互に切り替えて前記共通電極に入力し、前記第1の駆動回路は、前記共通電極に前記第1の電位の共通電圧が入力されるときには前記第1の電位と同じ電位または前記第1の電位よりも高い電位の映像信号を入力し、前記共通電極に前記第2の電位の共通電圧が入力されるときには前記第2の電位と同じ電位または前記第2の電位よりも低い電位の映像信号を入力する液晶表示装置。

(6) 前記(5)の液晶表示装置において、前記スイッチング素子は、TFTであり、前記TFTのゲート電極は前記走査信号線に接続され、前記TFTのドレイン電極またはソース電極のいずれか一方は前記映像信号線に接続され、前記TFTのドレイン電極またはソース電極のうちの前記映像信号線に接続されていないほうは前記画素電極に接続されている液晶表示装置。10

(7) 前記(5)の液晶表示装置において、前記画素電極と前記共通電極とは、同じ基板の上に形成されており、前記表示パネルは、横電界方式で動作する液晶表示装置。

(8) 前記(5)の液晶表示装置において、前記画素電極と前記共通電極とは、異なる基板の上に形成されており、前記表示パネルは、縦電界方式で動作する液晶表示装置。

#### 【発明の効果】

#### 【0023】

本発明によれば、2倍走査線方式の液晶表示パネルをコモン反転駆動させることで、データドライバの発熱量を低くし、画質の低下を防ぐことができる。

#### 【0024】

また、本発明によれば、コモン反転駆動をさせることで、見かけ上はドット反転駆動になる。そのため、映像信号の極性を反転させる回数が激減し、表示画質を容易に向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下、本発明について、図面を参照して実施の形態（実施例）とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

#### 【実施例】

#### 【0026】

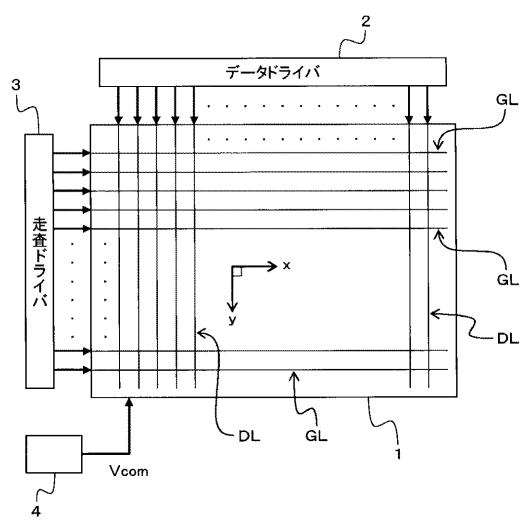

図1は、本発明による一実施例の液晶表示装置の概略構成を示す模式ブロック図である。

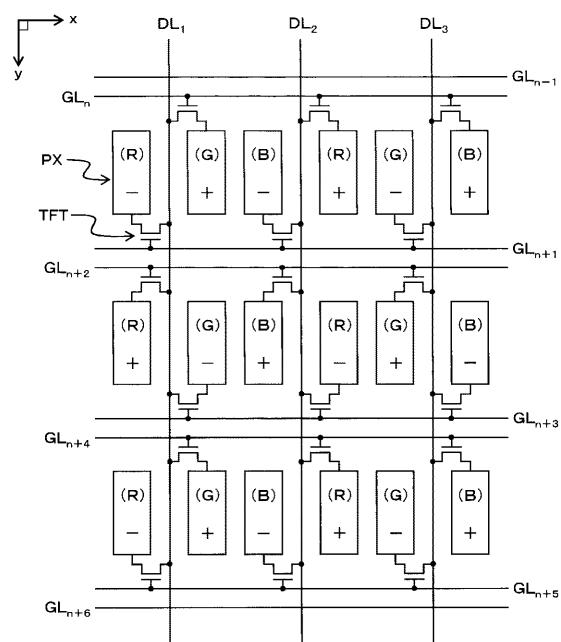

図2(a)は、本実施例の液晶表示パネルの一構成例と1フレーム期間における画素電極の極性を示す模式回路図である。図2(b)は、図2(a)に示した構成の液晶表示パネルにおける駆動方法の一例を示す模式図である。

#### 【0027】

本発明が適用される液晶表示装置は、たとえば、図1に示すように、y方向に長く延びる複数本の映像信号線DLと、x方向に長く延びる複数本の走査信号線GLとを有する液晶表示パネル1と、複数本の映像信号線DLのそれぞれに入力する映像信号（階調電圧）を生成するデータドライバ2と、複数本の走査信号線GLに走査信号を順次入力する走査ドライバ3と、液晶表示パネル1の共通電極（図示しない）に入力する共通電圧Vcomの電位を制御する共通電圧制御回路4とを有する。また、図1では省略しているが、本発明の液晶表示装置は、たとえば、データドライバ2、走査ドライバ3、共通電圧制御回路4の動作を同期させるクロック信号などを生成するタイミングコントローラや、外部システムから入力された映像データを一時的に保持するフレームメモリなどを有する。40

#### 【0028】

液晶表示パネル1は、一対の基板の間に液晶材料を封入した表示パネルであり、前記一対の基板のうちの一方の基板には、図2(a)に示すように、スイッチング素子として用いるTFTと画素電極PXを有する画素がマトリクス状に配置されている。なお、図2(50

a) では省略しているが、画素電極 P X は、液晶材料および共通電極 C T とともに画素容量（液晶容量と呼ぶこともある）を形成している。また、本実施例の液晶表示パネルにおいて、共通電極 C T は、後述するように、TFTなどを有する基板に形成されていてもよいし、もう一方の基板に形成されていてもよい。

#### 【0029】

また、液晶テレビなどに用いられるカラー表示に対応した液晶表示パネルの場合、図2(a)に示した1つの画素は、サブ画素と呼ばれ、RGB方式のカラー液晶表示パネルの場合、R(赤色)の表示を行うサブ画素、G(緑色)の表示を行うサブ画素、B(青色)の表示を行うサブ画素の3つのサブ画素で、映像の1ドットが構成されている。このとき、x方向に並んだ複数の画素(サブ画素)は、たとえば、R(赤色)の表示を行うサブ画素、G(緑色)の表示を行うサブ画素、B(青色)の表示を行うサブ画素の順に周期配置されている。10

#### 【0030】

また、本実施例の液晶表示パネルでは、映像信号線 DL(DL<sub>1</sub>, DL<sub>2</sub>, DL<sub>3</sub>, ...)は、走査信号線 GL の延在方向(x方向)に並んだ隣接する2つの画素を1組とし、その1組の画素に対して1本ずつ配置されている。このとき、1本の映像信号線 DL(たとえば、DL<sub>1</sub>)を挟んで隣接する2つの画素の TFT のドレインは、同じ映像信号線 DL<sub>1</sub> に接続される。

#### 【0031】

また、本実施例の液晶表示パネルでは、走査信号線 GL の延在方向(x方向)に並んだ複数の画素からなる列を画素列とすると、1つの画素列に対して、各画素の画素電極 P X を挟むように2本の走査信号線 GL が配置されている。またこのとき、映像信号線 DL の延在方向(y方向)で隣接する2つの画素の画素電極 P X の間には、2本の走査信号線 GL が配置されている。このとき、隣接する2本の走査信号線 GL(たとえば、GL<sub>n</sub>とGL<sub>n+1</sub>)の間に画素電極 P X が配置されている画素列は、TFTのゲートが一方の走査信号線 GL<sub>n+1</sub> に接続されている画素と、TFTのゲートが他方の走査信号線 GL<sub>n</sub> に接続されている画素とが交互に配置されている。20

#### 【0032】

また、1本の映像信号線 DL(たとえば、DL<sub>1</sub>)を挟んで隣接する2つの画素を1つの組として、映像信号線 DL<sub>1</sub> の延在方向に沿って見ると、映像信号線 DL<sub>1</sub> の入力端に近いほうの走査信号線 GL に接続された TFT を有する画素と、入力端から遠い方の走査信号線 GL に接続された TFT を有する画素の位置(向き)が、前記2つの画素の組毎に反転している。30

#### 【0033】

本実施例の液晶表示パネルは、図2(a)に示したような回路構成にし、コモン反転駆動させることで、データドライバの発熱量を低減し、かつ、ドット反転駆動を実現する。このとき、液晶表示パネルは、たとえば、図2(b)に示したような方法で駆動させる。

#### 【0034】

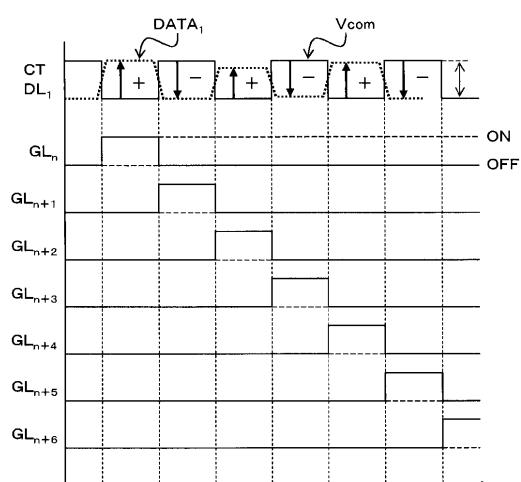

本実施例の液晶表示パネルで1フレーム期間分の映像データを表示するときには、たとえば、図2(b)に示すように、各走査信号線 GL(..., GL<sub>n</sub>, GL<sub>n+1</sub>, GL<sub>n+2</sub>, GL<sub>n+3</sub>, GL<sub>n+4</sub>, GL<sub>n+5</sub>, GL<sub>n+6</sub>, ...)に入力される走査信号を、一定の時間間隔で順番にONにしていく。この走査信号の制御は走査ドライバ3で行い、たとえば、フレームレート(リフレッシュレートと呼ぶこともある)が60Hzの場合は、タイミングコントローラからのクロック信号に基づいて、1/60秒を1周期として、各走査信号線に入力される走査信号を順番にONにしていく。40

#### 【0035】

このとき、共通電極に入力する共通電圧 V<sub>com</sub> は、走査信号をONにする走査信号線 GL を切り替えるタイミングと同期させて、第1の電位と、第1の電位よりも電位の低い第2の電位とを交互に切り替えながら入力する。この共通電圧 V<sub>com</sub> の電位の切り替えは、共通電圧制御回路4で行い、走査ドライバ3で用いるクロック信号と同期させて切り50

替える。

#### 【0036】

また、映像信号線 D L (たとえば、D L<sub>1</sub>)に入力する映像信号線 D A T A<sub>1</sub>は、共通電圧 V c o mが第1の電位で入力される期間には第1の電位と同じ電位または第1の電位よりも高い電位の階調電圧を生成し、共通電圧 V c o mが第2の電位で入力される期間には第2の電位と同じ電位または第2の電位よりも低い電位の階調電圧を生成する。この階調電圧の生成は、データドライバ2で行い、走査ドライバ3で用いるクロック信号、共通電圧制御回路4における電位と切り替えのタイミングと同期させて生成する。

#### 【0037】

このようにすると、共通電圧 V c o mが第1の電位で入力される期間に走査信号がONになる走査信号線 G L (たとえば、G L<sub>n</sub>)にTFTのゲートが接続された画素の画素電極 P Xには、共通電圧 V c o mと同じ電位または共通電圧 V c o mよりも電位の高い階調電圧、すなわち正極性の階調電圧が書き込まれる。また、共通電圧 V c o mが第2の電位で入力される期間に走査信号がONになる走査信号線 G L (たとえば、G L<sub>n+1</sub>)にTFTのゲートが接続された画素の画素電極 P Xには、共通電圧 V c o mと同じ電位または共通電圧 V c o mよりも電位の低い階調電圧、すなわち負極性の階調電圧が書き込まれる。

#### 【0038】

なお、図2(b)には、1本の映像信号線 D L<sub>1</sub>に入力される映像信号 D A T A<sub>1</sub>のみを示しているが、残りの映像信号 D L (D L<sub>2</sub>, D L<sub>3</sub>, ...)にもおなじパターンで映像信号が入力される。すなわち、たとえば、走査信号線 G L<sub>n</sub>にTFTのゲートが接続されたすべての画素の画素電極 P Xには、前記正極性の階調電圧が書き込まれる。

#### 【0039】

こうして、1フレーム期間分の階調電圧を各画素の画素電極に書き込むと、各画素電極 P Xの極性は、たとえば、図2(a)に示すようになる。なお、図2(a)では、正極性の階調電圧が書き込まれた画素電極 P Xに「+」の記号を付し、負極性の階調電圧が書き込まれた画素電極 P Xに「-」の記号を付している。

#### 【0040】

このように、本実施例の液晶表示パネルは、図2(b)に示したような画素列単位のコモン反転駆動をさせることで、ドット反転駆動と同じ反転形態を実現することができる。

#### 【0041】

また、本実施例の液晶表示パネルは、データドライバ2において各映像信号線 D Lに入力する映像信号(階調電圧)を生成するときに、各映像信号線 D Lにおける正極性、負極性の反転関係が同じ、すなわち1本の走査信号線に接続された各画素の画素電極に書き込まれる階調電圧の極性が同じ極性である。そのため、従来の2倍走査線方式の液晶表示装置に比べて、データドライバ2で映像信号の極性を反転させる回数が激減し、データドライバ2の消費電力や発熱量を低減することができる。また、コモン反転駆動をさせることで、たとえば、図9(b)に示したような駆動方式に比べ、データドライバ2で生成する階調電圧の最大振幅を半分にすることができ、データドライバ2の発熱量をさらに低減することができる。その結果、映像信号の電位を安定化でき、表示品質を向上できる。

#### 【0042】

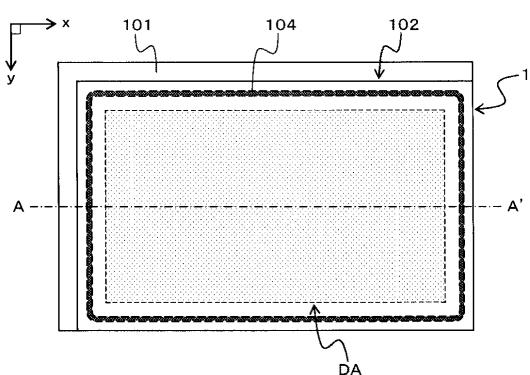

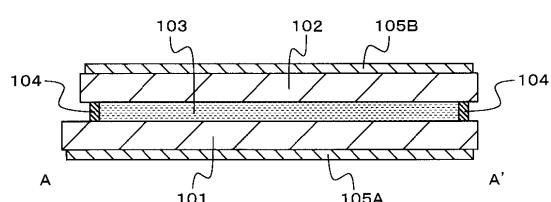

図3(a)は、液晶表示パネルの概略構成の一例を示す模式平面図である。図3(b)は、図3(a)のA-A'線における断面構成の一例を示す模式断面図である。

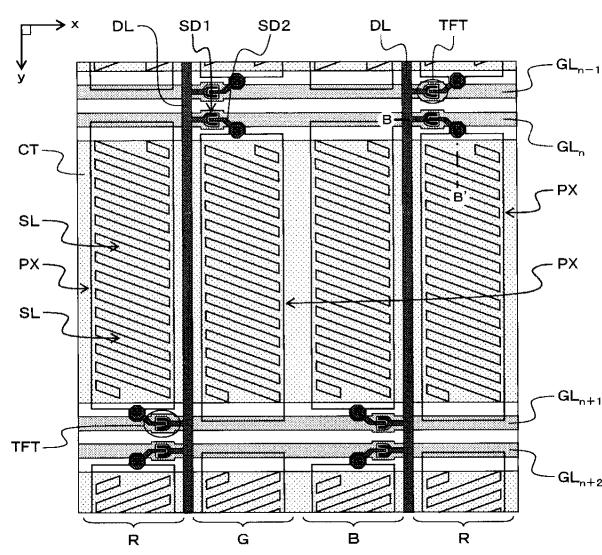

図4(a)は、図3(a)および図3(b)に示した液晶表示パネルにおけるTFT基板の第1の構成例を示す模式平面図である。図4(b)は、図4(a)のB-B'線における液晶表示パネルの断面構成の一例を示す模式断面図である。

#### 【0043】

本実施例の液晶表示パネル1は、たとえば、図3(a)および図3(b)に示すように、TFT基板101と対向基板102の一対の基板の間に液晶材料103を封入した構成になっている。このとき、TFT基板101と対向基板102は、たとえば、表示領域D

10

20

30

40

50

Aの外側に環状に設けられたシール材104で接着されており、液晶材料103は、TFT基板101および対向基板102ならびにシール材104で囲まれた空間に封入されている。

#### 【0044】

また、液晶表示パネル1が透過型または半透過型の場合、TFT基板101および対向基板102の外側を向いた面には、一対の偏光板105A, 105Bが配置されている。またこのとき、図3(b)では省略しているが、たとえば、TFT基板101と偏光板105Aとの間、対向基板102と偏光板105Bとの間のそれぞれに、1層または複数層の位相差板が配置されていることもある。

#### 【0045】

また、液晶表示パネル1が反射型の場合、たとえば、TFT基板101側に配置される偏光板105Aや位相差板などは、一般に不要である。

#### 【0046】

このような構成の液晶表示パネル1の表示領域DAには、たとえば、図2(a)に示した回路構成と等価な構成になるように映像信号線DL、走査信号線GL、TFT、画素電極PXなどが形成されている。液晶表示パネル1が、たとえば、IPS(Indium-Planar Switching)方式と呼ばれる横電界駆動方式の場合、映像信号線DL、走査信号線GL、TFT、画素電極PX、対向電極CTは、TFT基板101に形成されており、その構成は、たとえば、図4(a)および図4(b)に示すような構成になっている。

#### 【0047】

横電界駆動方式の場合、TFT基板101は、たとえば、図4(a)および図4(b)に示すように、ガラス基板などの絶縁基板SUB1の表面に、複数本の走査信号線GLおよび対向電極CTが設けられている。走査信号線GLは、たとえば、アルミなどの導体膜をエッチングして形成し、対向電極CTは、たとえば、ITOなどの光透過率が高い導体膜をエッチングして形成する。また、対向電極CTは、たとえば、1つの画素列を挟む隣接した2本の走査信号線の間(たとえば、GL<sub>n</sub>とGL<sub>n+1</sub>の間)に帯状に設けられている。また、帯状の各対向電極CTは、たとえば、表示領域DAの外側において、バスラインなどで電気的に接続されている。なお、図4(b)に示した断面構成は、たとえば、走査信号線GLと対向電極CTとを、それぞれ独立した工程で形成した場合の一構成例である。走査信号線GLと対向電極CTは、たとえば、絶縁基板SUB1の表面に前記ITO膜および前記導体膜を続けて成膜し、一括エッチングで形成することもあり、その場合は、絶縁基板SUB1と走査信号線GLとの間に、走査信号線GLとほぼ同じパターンのITO膜が介在する。

#### 【0048】

また、走査信号線GLおよび対向電極CTの上には、第1の絶縁層PAS1を介して半導体層SC、映像信号線DL(ドレイン電極SD1)、ソース電極SD2が設けられている。半導体層は、たとえば、アモルファスシリコン(a-Si)膜をエッチングした後、ドレイン領域およびソース領域に不純物を注入して形成する。映像信号線DLおよびソース電極SD2は、たとえば、アルミなどの導体膜をエッチングして形成する。また、ドレイン電極SD1は、映像信号線DLの一部を分岐させて形成するが、このとき、分岐させる方向は、たとえば、図2(a)に示した回路と等価になるようにする。なお、図4(a)に示した例では、ドレイン電極SD1は、平面形状がU字型であり、走査信号線GLの延在方向が上下方向になるように配置しているが、これに限らず、映像信号線DLの延在方向が上下方向になるように配置してもよい。またさらに、ドレイン電極SD1の平面形状は、U字型に限らず、直線状または階段状になっていてもよい。

#### 【0049】

また、映像信号線DLなどの上には、第2の絶縁層PAS2を介して画素電極PXが設けられている。画素電極PXは、たとえば、ITOなどの光透過率が高い導体膜をエッチングして形成し、スルーホールTHでソース電極SD2と接続させる。また、画素電極PX

10

20

30

40

50

Xは、平面で見て対向電極CTと重なる領域に複数のスリットSLを有する櫛歯状にする。このとき、スリットSLの数や向きなどは、適宜変更できることはもちろんである。

#### 【0050】

また、画素電極PXの上には、配向膜ORI1が設けられている。

#### 【0051】

一方、対向基板102は、ガラス基板などの絶縁基板SUB2の表面に、ブラックマトリクスと呼ばれる遮光膜BMおよびカラーフィルタCFが設けられている。遮光膜BMは、たとえば、光透過率がほぼ0の導体膜または絶縁膜をエッチングして、各画素を分離するような格子状のパターンに形成する。カラーフィルタCFは、たとえば、絶縁膜をエッチングまたは露光、現像して形成し、遮光膜BMの開口領域に、R(赤色)の表示を担うフィルタ、G(緑色)の表示を担うフィルタ、B(青色)の表示を担うフィルタが周期配列するように形成する。

10

#### 【0052】

また、遮光膜BMおよびカラーフィルタCFの上には、たとえば、オーバーコート層OCを介して、配向膜ORI2が設けられている。

#### 【0053】

このように、横電界駆動方式の液晶表示パネル1において、TFT基板101の構造を図2(a)に示した回路構成と等価な構造にし、図2(b)に示したような方法で駆動させることで、データドライバ2の発熱量を低減し、表示品質を向上させることができる。また、画素列単位のコモン反転駆動をさせることで、ドット反転駆動と同じ反転形態を容易に実現できる。

20

#### 【0054】

なお、本実施例では、横電界駆動方式の液晶表示パネル1の構成例として、図4(a)および図4(b)に示したような構成を挙げたが、これに限らず、種々の横電界駆動方式の構成を適用できることはもちろんである。またさらに、図4(a)および図4(b)には、共通電極CTと画素電極PXが絶縁層PAS1,PAS2を介して設けられており、画素電極PXがスリットSLを有する構成を挙げたが、これに限らず、共通電極CTと画素電極PXが同じ層にある構成であってもよいことはもちろんである。

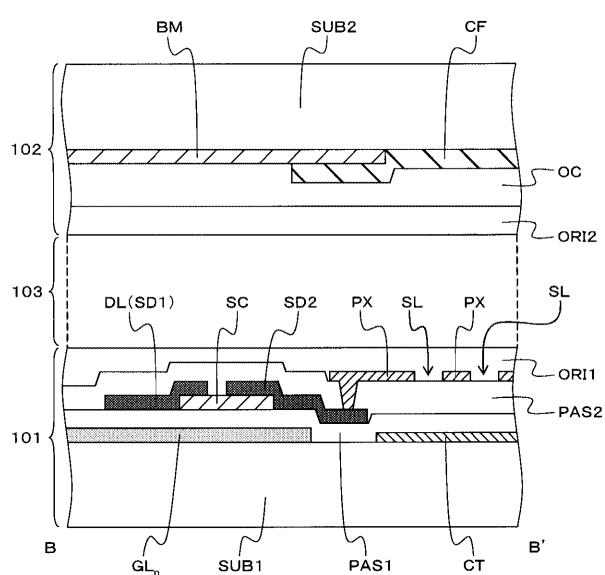

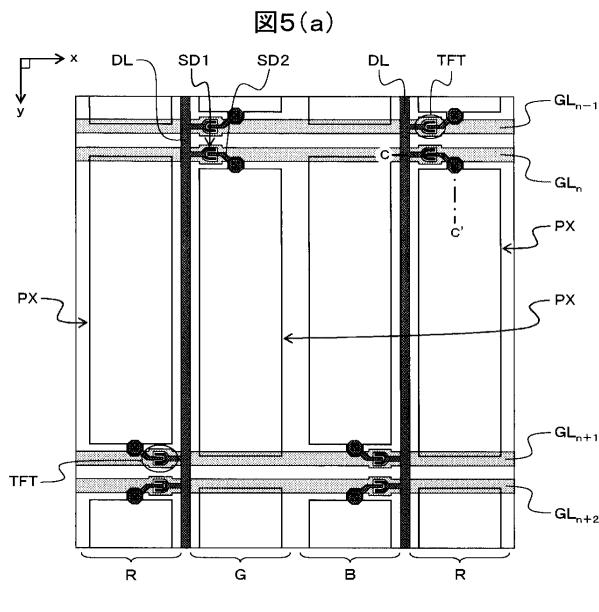

#### 【0055】

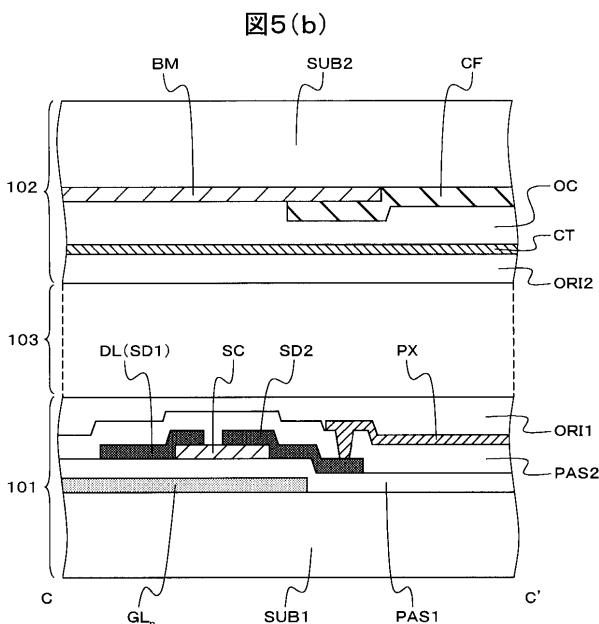

図5(a)は、図3(a)および図3(b)に示した液晶表示パネルにおけるTFT基板の第2の構成例を示す模式平面図である。図5(b)は、図5(a)のC-C'線における液晶表示パネルの断面構成の一例を示す模式断面図である。

30

#### 【0056】

本実施例の液晶表示パネル1は、表示領域DAの画素が図4(a)および図4(b)に示したような構成の横電界駆動方式のものに限らず、共通電極CTが対向基板102側に設けられた縦電界駆動方式のものであってもよい。縦電界駆動方式の液晶表示パネルの一構成例を図5(a)および図5(b)に示す。

#### 【0057】

縦電界駆動方式の場合、TFT基板101は、たとえば、図5(a)および図5(b)に示すように、ガラス基板などの絶縁基板SUB1表面には、複数本の走査信号線GLのみが設けられている。

40

#### 【0058】

また、走査信号線GLの上には、第1の絶縁層PAS1を介して半導体層SC、映像信号線DL(ドレイン電極SD1)、ソース電極SD2が設けられている。このときも、ドレイン電極SD1は、映像信号線DLの一部を分岐させて形成し、分岐させる方向は、たとえば、図2(a)に示した回路と等価になるようにする。なお、図5(a)に示した例では、ドレイン電極SD1は、平面形状がU字型であり、走査信号線GLの延在方向が上下方向になるように配置しているが、これに限らず、映像信号線DLの延在方向が上下方向になるように配置してもよい。またさらに、ドレイン電極SD1の平面形状は、U字型に限らず、直線状または階段状になっていてもよい。

50

## 【0059】

また、映像信号線 D L などの上には、第 2 の絶縁層 P A S 2 を介して画素電極 P X が設けられている。画素電極 P X は、スルーホール T H でソース電極 S D 2 と接続させる。また、縦電界駆動方式の場合、画素電極 P X は、スリット S L が不要である。またこのとき、画素電極 P X は、その一部分が、スルーホール T F で接続された T F T のゲートが接続されている走査信号線とは反対側の走査信号線と平面で見て重なるように形成し、走査信号線および画素電極 P X ならびにそれらの間に介在する絶縁層 P A S 1 , P A S 2 による保持容量を形成する。

## 【0060】

また、画素電極 P X の上には、配向膜 O R I 1 が設けられている。

10

## 【0061】

一方、対向基板 1 0 2 は、ガラス基板などの絶縁基板 S U B 2 の表面に、ブラックマトリクスと呼ばれる遮光膜 B M およびカラーフィルタ C F が設けられている。遮光膜 B M は、たとえば、光透過率がほぼ 0 の導体膜または絶縁膜をエッチングして、各画素を分離するような格子状のパターンに形成する。カラーフィルタ C F は、たとえば、絶縁膜をエッチングまたは露光、現像して形成し、遮光膜 B M の開口領域に、R (赤色) の表示を担うフィルタ、G (緑色) の表示を担うフィルタ、B (青色) の表示を担うフィルタが周期配列するように形成する。

## 【0062】

また、遮光膜 B M およびカラーフィルタ C F の上には、たとえば、オーバーコート層 O C を介して、対向電極 C T が設けられている。また、対向電極 C T の上には、配向膜 O R I 2 が設けられている。

20

## 【0063】

このように、縦電界駆動方式の液晶表示パネル 1 において、表示領域 D A の画素の構造 (配列) を図 2 ( a ) に示した回路構成と等価な構造にし、図 2 ( b ) に示したような方法で駆動させることで、データドライバ 2 の発熱量を低減し、表示品質を向上させることができる。また、画素列単位のコモン反転駆動をさせることで、ドット反転駆動と同じ反転形態を容易に実現できる。

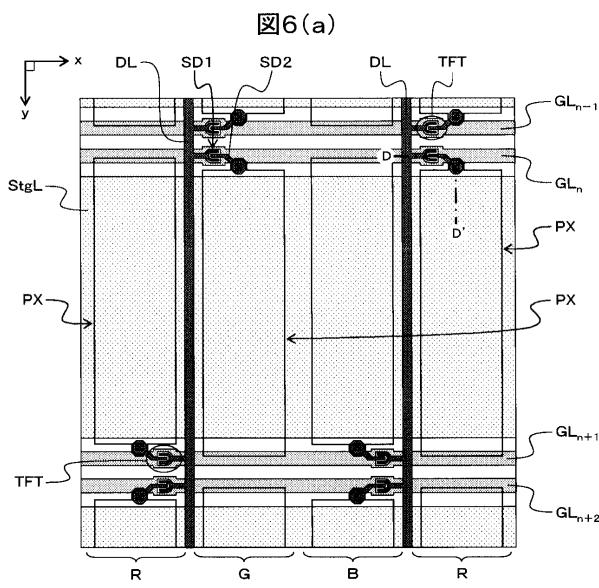

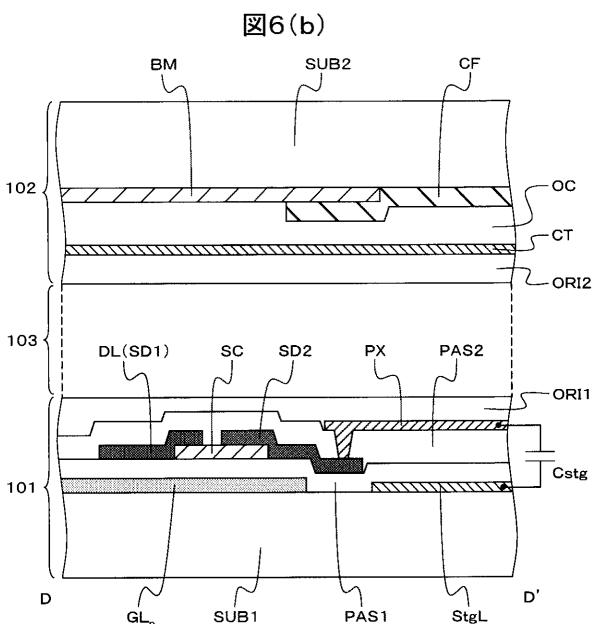

## 【0064】

図 6 ( a ) は、図 3 ( a ) および図 3 ( b ) に示した液晶表示パネルにおける T F T 基板の第 3 の構成例を示す模式平面図である。図 6 ( b ) は、図 6 ( a ) の D - D' 線における液晶表示パネルの断面構成の一例を示す模式断面図である。

30

## 【0065】

本実施例の液晶表示パネル 1 が縦電界駆動方式の場合、たとえば、図 5 ( a ) に示したように、走査信号線および画素電極 P X ならびに介在する第 1 の絶縁層 P A S 1 による保持容量を形成する代わりに、たとえば、T F T 基板 1 0 1 に、走査信号線とは別の導体層 (保持容量線) を形成してもよい。T F T 基板 1 0 1 に保持容量線を形成した縦電界駆動方式の液晶表示パネルの一構成例を図 6 ( a ) および図 6 ( b ) に示す。

## 【0066】

保持容量線を有する縦電界駆動方式の場合、T F T 基板 1 0 1 は、たとえば、図 6 ( a ) および図 6 ( b ) に示すように、ガラス基板などの絶縁基板 S U B 1 の表面に、複数本の走査信号線 G L および保持容量線 S t g L が設けられている。走査信号線 G L は、たとえば、アルミなどの導体膜をエッチングして形成し、保持容量線 S t g L は、たとえば、ITO などの光透過率が高い導体膜をエッチングして形成する。また、保持容量線 S t g L は、たとえば、1 つの画素列を挟む隣接した 2 本の走査信号線の間 (たとえば、G L<sub>n</sub> と G L<sub>n+1</sub> の間) に帯状に設けられている。また、帯状の各保持容量線 S t g L は、たとえば、表示領域 D A の外側において、バスラインなどで電気的に接続されている。

40

## 【0067】

また、走査信号線 G L および保持容量線 S t g L の上には、第 1 の絶縁層 P A S 1 を介して半導体層 S C 、映像信号線 D L (ドレン電極 S D 1 ) 、ソース電極 S D 2 が設けら

50

れている。このときも、ドレイン電極 S D 1 は、映像信号線 D L の一部を分岐させて形成するが、このとき、分岐させる方向は、たとえば、図 2 ( a ) に示した回路と等価になるようとする。なお、図 6 ( a ) に示した例では、ドレイン電極 S D 1 は、平面形状が U 字型であり、走査信号線 G L の延在方向が上下方向になるように配置しているが、これに限らず、映像信号線 D L の延在方向が上下方向になるように配置してもよい。またさらに、ドレイン電極 S D 1 の平面形状は、U 字型に限らず、直線状または階段状になっていてもよい。

#### 【 0 0 6 8 】

また、映像信号線 D L などの上には、第 2 の絶縁層 P A S 2 を介して画素電極 P X が設けられている。画素電極 P X は、スルーホール T H でソース電極 S D 2 と接続される。このとき、画素電極 P X は、平面で見て保持容量線 S t g L と重なる部分があり、画素電極 P X および保持容量線 S t g L ならびにそれらの間に介在する絶縁層 P A S 1 , P A S 2 による保持容量 C s t g が形成される。このとき、保持容量線 S t g L の幅や、平面で見て画素電極 P X と重なる部分の形状を変えることで、保持容量の大きさを容易に変えることができる。

#### 【 0 0 6 9 】

また、画素電極 P X の上には、配向膜 O R I 1 が設けられている。

#### 【 0 0 7 0 】

一方、対向基板 1 0 2 は、ガラス基板などの絶縁基板 S U B 2 の表面に、ブラックマトリクスと呼ばれる遮光膜 B M およびカラーフィルタ C F が設けられている。遮光膜 B M は、たとえば、光透過率がほぼ 0 の導体膜または絶縁膜をエッチングして、各画素を分離するような格子状のパターンに形成する。カラーフィルタ C F は、たとえば、絶縁膜をエッチングまたは露光、現像して形成し、遮光膜 B M の開口領域に、R ( 赤色 ) の表示を担うフィルタ、G ( 緑色 ) の表示を担うフィルタ、B ( 青色 ) の表示を担うフィルタが周期配列するように形成する。

#### 【 0 0 7 1 】

また、遮光膜 B M およびカラーフィルタ C F の上には、たとえば、オーバーコート層 O C を介して、対向電極 C T が設けられている。また、対向電極 C T の上には、配向膜 O R I 2 が設けられている。

#### 【 0 0 7 2 】

このように、縦電界駆動方式の液晶表示パネル 1 において、T F T 基板 1 0 1 の構造を図 2 ( a ) に示した回路構成と等価な構造にし、図 2 ( b ) に示したような方法で駆動させることで、データドライバ 2 の発熱量を低減し、表示品質を向上させることができる。また、画素列単位のコモン反転駆動をさせることで、ドット反転駆動と同じ反転形態を容易に実現できる。なお、図 6 ( a ) および図 6 ( b ) に示したような構成の場合、共通電極 C T に加える共通電圧 V c o m の電位の切り替えと同期して、保持容量配線 S t g L の電位を切り替えることが望ましい。

#### 【 0 0 7 3 】

なお、本実施例では、縦電界駆動方式の液晶表示パネル 1 の構成例として、図 5 ( a ) および図 5 ( b ) に示したような構成、図 6 ( a ) および図 6 ( b ) に示したような構成を挙げたが、これに限らず、種々の縦電界駆動方式の構成を適用できることはもちろんである。

#### 【 0 0 7 4 】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

#### 【 図面の簡単な説明 】

#### 【 0 0 7 5 】

【 図 1 】本発明による一実施例の液晶表示装置の概略構成を示す模式ブロック図である。

【 図 2 ( a ) 】本実施例の液晶表示パネルの一構成例と 1 フレーム期間における画素電極

10

20

30

40

50

の極性を示す模式回路図である。

【図2( b )】図2( a )に示した構成の液晶表示パネルにおける駆動方法の一例を示す模式図である。

【図3( a )】液晶表示パネルの概略構成の一例を示す模式平面図である。

【図3( b )】図3( a )のA - A'線における断面構成の一例を示す模式断面図である。

【図4( a )】図3( a )および図3( b )に示した液晶表示パネルにおけるTFT基板の第1の構成例を示す模式平面図である。

【図4( b )】図4( a )のB - B'線における液晶表示パネルの断面構成の一例を示す模式断面図である。 10

【図5( a )】図3( a )および図3( b )に示した液晶表示パネルにおけるTFT基板の第2の構成例を示す模式平面図である。

【図5( b )】図5( a )のC - C'線における液晶表示パネルの断面構成の一例を示す模式断面図である。

【図6( a )】図3( a )および図3( b )に示した液晶表示パネルにおけるTFT基板の第3の構成例を示す模式平面図である。

【図6( b )】図6( a )のD - D'線における液晶表示パネルの断面構成の一例を示す模式断面図である。 20

【図7】従来の液晶表示パネルの回路構成の一例を示す模式回路図である。

【図8】従来の2倍走査線方式の液晶表示パネルの回路構成の一例を示す模式回路図である。 20

【図9( a )】従来の2倍走査線方式の液晶表示パネルの一構成例と1フレーム期間における画素電極の極性を示す模式回路図である。

【図9( b )】図9( a )に示した構成の液晶表示パネルにおける駆動方法の一例を示す模式図である。

【図10】特許文献1に記載された回路構成を参照してTFTの配置および各画素電極の極性を示した模式回路図である。

#### 【符号の説明】

##### 【0076】

1 ... 液晶表示パネル

101 ... TFT基板

102 ... 対向基板

103, Lc ... 液晶材料

104 ... シール材

105A, 105B ... 偏光板

SUB1, SUB2 ... 絶縁基板

DL, DL<sub>1</sub>, DL<sub>2</sub>, DL<sub>3</sub>, DL<sub>4</sub>, DL<sub>5</sub> ... 映像信号線

GL, GL<sub>1</sub>, GL<sub>2</sub>, GL<sub>n-1</sub>, GL<sub>n</sub>, GL<sub>n+1</sub>, GL<sub>n+2</sub>, GL<sub>n+3</sub>,

GL<sub>n+4</sub>, GL<sub>n+5</sub>, GL<sub>n+6</sub> ... 走査信号線

PX ... 画素電極

CT ... 対向電極

StgL ... 保持容量線

SD1 ... ドレイン電極

SD2 ... ソース電極

PAS1, PAS2 ... 絶縁層

ORI1, ORI2 ... 配向膜

BM ... 遮光膜

CF ... カラーフィルタ

OC ... オーバーコート層

2 ... データドライバ

30

40

50

3 ... 走査ドライバ

4 ... 共通電圧制御回路

【図1】

図1

【図2(a)】

図2(a)

【図2(b)】

図2(b)

【図3(a)】

図3(a)

【図3(b)】

図3(b)

【図4(a)】

図4(a)

【図4(b)】

図4(b)

【図5(a)】

【図5(b)】

【図6(a)】

【図6(b)】

【図7】

【図8】

【図9(a)】

【図9(b)】

【図10】

図10

---

フロントページの続き

(51)Int.CI.

| F I     |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 2 A |

| G 0 9 G | 3/20 | 6 2 4 C |

| G 0 9 G | 3/20 | 6 2 4 D |

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 1 M |

| G 0 9 G | 3/20 | 6 8 0 H |

| G 0 9 G | 3/20 | 6 8 0 G |

| G 0 9 G | 3/20 | 6 7 0 L |

審査官 奈良田 新一

(56)参考文献 特開平05-134629 (JP, A)

特開平10-073843 (JP, A)

特開2004-185006 (JP, A)

特開2004-240192 (JP, A)

特開平10-171412 (JP, A)

特開平11-337972 (JP, A)

特開平10-142578 (JP, A)

特開平11-326869 (JP, A)

(58)調査した分野(Int.CI., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3 , 1 / 1 3 6 8