RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 496 357**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 80 26545**

(54) Amplificateur hyperfréquence à deux transistors à effet de champ couplés par réaction capacitive.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 03 F 3/16, 3/189.

(22) Date de dépôt..... 15 décembre 1980.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 24 du 18-6-1982.

(71) Déposant : Société dite : THOMSON-CSF, société anonyme, résidant en France.

(72) Invention de : Félix Diamand.

(73) Titulaire : *Idem* (71)

(74) Mandataire :

1

AMPLIFICATEUR HYPERFREQUENCE A DEUX TRANSISTORS

A EFFET DE CHAMP

COUPLES PAR REACTION CAPACITIVE

L'invention concerne un système de deux transistors à effet de champ couplés par réaction mutuelle capacitive en vue de constituer notamment un amplificateur présentant une impédance d'entrée prédéterminée en très haute fréquence, par exemple à 10 GHz.

- 5        On sait qu'en haute fréquence, l'admittance entre grille et source d'un transistor à effet de champ est capacitive.

Or, dans les applications pratiques, on est souvent conduit à compenser cette admittance capacitive par une inductance à l'entrée grille-source d'un étage d'amplification comportant un transistor à effet de champ. Cette compensation est notamment nécessaire dans les cas suivants :

10      Premier cas : La source ou la ligne d'alimentation de l'amplificateur présente une impédance interne assimilable à une résistance pure.

Deuxième cas : On considère un étage d'amplification dont l'entrée est reliée à la sortie d'un étage précédent qui présente une admittance de sortie capacitive.

15      Une telle compensation par inductance n'est pas facile à réaliser dans la technologie des circuits intégrés à grande échelle laquelle s'accompagne d'un haut degré d'intégration des composants dans une même structure monolithique. En effet, une inductance n'est intégrable qu'en utilisant une grande surface du semiconducteur monocristallin par comparaison avec les dimensions d'un transistor à effet de champ intégré sur le même support. Ces dimensions peuvent fréquemment devenir prohibitives, notamment dans le cas des très hautes fréquences (10 GHz et au-dessus) sur arséniure de gallium, en raison du coût élevé de celui-ci et surtout des contraintes d'encombrement.

20      L'invention vise à surmonter cette difficulté en rendant possible l'adaptation de l'entrée d'un amplificateur, constitué d'au moins un transistor à effet de champ, comme c'est généralement le cas sur arséniure de gallium, aux conditions optimales d'utilisation, c'est à dire la réalisation d'une

impédance de composante réactive à volonté positive ou nulle, grâce à l'utilisation de capacités beaucoup plus faciles à intégrer que les inductances.

Les capacités sont en effet de surface réduite, de l'ordre de quelques 5 centaines de microns dans chacune des deux dimensions, soit du même ordre que les transistors à effet de champ aux fréquences considérées. L'invention permet de diminuer l'encombrement de chaque étage par adaptation de l'impédance d'entrée, en ne laissant subsister qu'une difficulté mineure la sortie du dernier étage. En effet la compensation de la capacité 10 de sortie par une inductance est plus facile à réaliser en raison du fait qu'il s'agit alors généralement d'un étage de puissance où les questions de dimensions sont moins cruciales.

L'amplificateur selon l'invention est du type comportant un premier transistor à effet de champ et un deuxième transistor à effet de champ dont 15 les sources sont reliées à un point commun (par exemple la masse de l'amplificateur), la grille du premier transistor constituant une première entrée destinée à recevoir un premier signal et la grille du deuxième transistor constituant une deuxième entrée destinée à recevoir un deuxième signal de même amplitude que le premier et de signe opposé, les drains des 20 transistors constituant deux bornes de sortie de l'amplificateur destinées à être reliées à une charge d'utilisation commune symétrique par rapport au point commun des sources.

Il est caractérisé en ce que la grille de chaque transistor est reliée au drain de l'autre par une capacité de couplage de valeur calculée de façon à 25 obtenir une impédance d'entrée prédéterminée pour l'amplificateur ainsi constitué.

L'invention sera mieux comprise, et d'autres caractéristiques apparaîtront, au moyen de la description qui suit, et des dessins qui l'accompagnent, parmi lesquels :

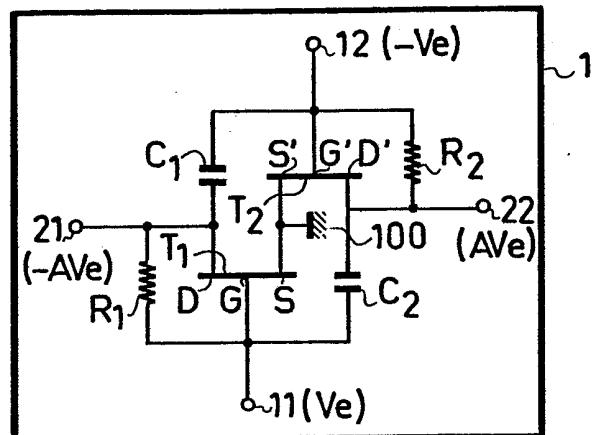

30 La figure 1 représente schématiquement un système de deux transistors couplés selon l'invention.

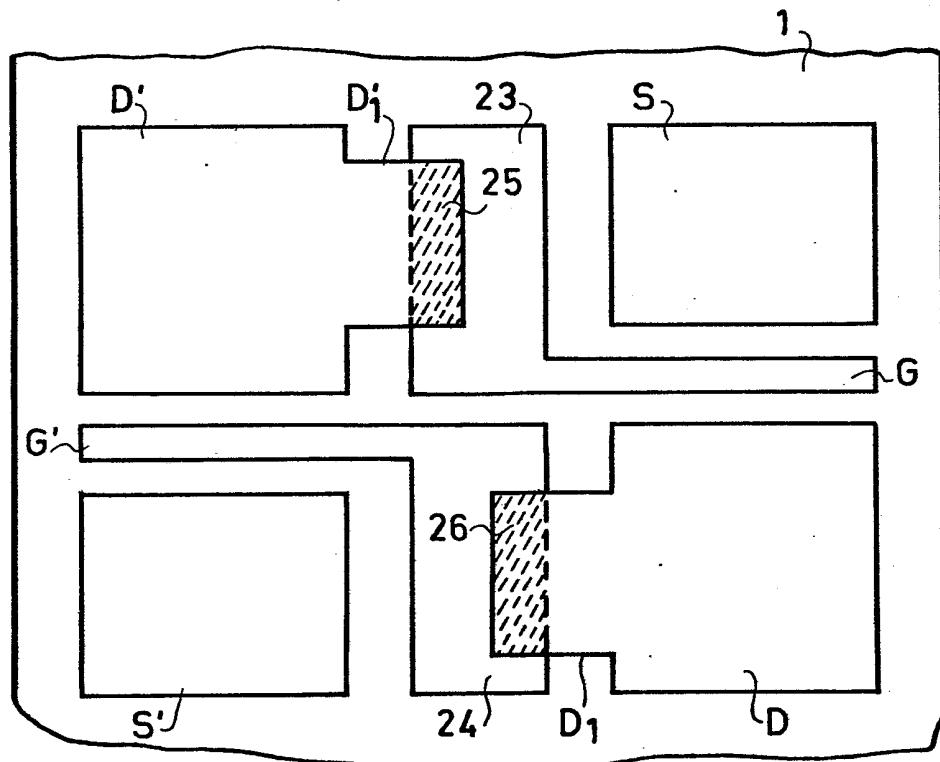

La figure 2 représente schématiquement une étape de fabrication d'un circuit intégré comportant un amplificateur selon l'invention.

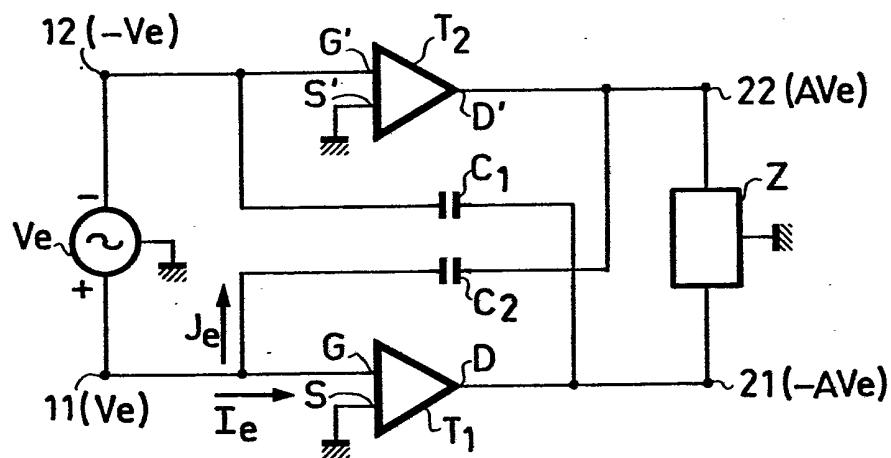

La figure 3 est un schéma théorique d'un amplificateur selon l'inven-

tion.

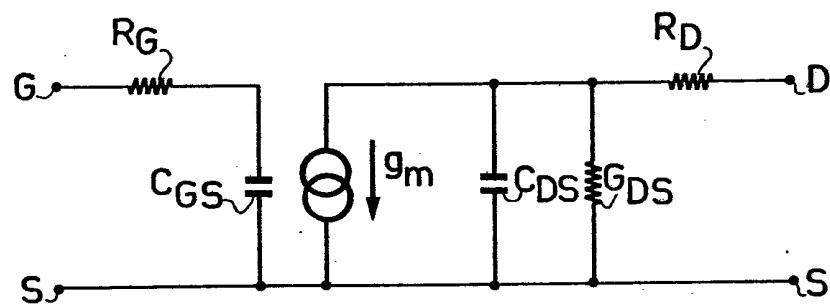

La figure 4 est un schéma équivalent simplifié d'un transistor.

Soient  $T_1$  et  $T_2$  deux transistors à effet de champ, intégrés sur un même substrat 1 semi-conducteur, par exemple en arsénure de gallium 5 monocristallin. Ils possèdent des sources S et S' connectées à une masse 100, des grilles G et G', des drains D et D'. Entre la grille de l'un et le drain de l'autre on a réalisé un couplage capacitif représenté à la figure 1 par des condensateurs  $C_1$  et  $C_2$ .

A la figure 2, on a représenté, sur le substrat 1, les métallisations de 10 deux transistors à effet de champ disposés tête bêche. En outre, pour réaliser le couplage capacitif, les métallisations de grille G et G' et de drains D et D' présentent des prolongements latéraux qui se recouvrent partiellement avec interposition de couches diélectriques. Les étapes correspondantes de fabrication comprennent donc :

15 1<sup>o</sup>/ Le dépôt des métallisations G et G' et de leurs prolongements latéraux 23 et 24 disposés avec décalage en direction de la métallisation de drain du transistor voisin.

2<sup>o</sup>/ Le dépôt d'une couche mince de diélectrique, par exemple en silice déposée par pulvérisation cathodique, sur des régions 25 et 26 des métallisations de grille 23 et 24. On les a représentées en hachures discontinues.

3<sup>o</sup>/ Le dépôt des métallisations D et D' et de leurs prolongements D<sub>1</sub> et D'<sub>1</sub> respectivement sur les régions 25 et 26.

On peut effectuer les opérations dans l'ordre inverse, en permuttant grilles et drains.

25 En outre, on a représenté, à la figure 1, des résistances R<sub>1</sub> et R<sub>2</sub> situées entre grille et drain de chaque transistor. Ces résistances non représentées figure 2, peuvent être de simples résistances de fuite entre électrodes, mais aussi peuvent être implantées à dessein.

Enfin on a représenté, à la figure 1, les entrées et les sorties de 30 l'amplificateur constitué par les deux transistors. On a fait figurer :

a) les entrées en opposition de phase 11 (signal de tension V<sub>e</sub>) et 12 (signal de tension - V<sub>e</sub>) connectées aux grilles G et G' respectivement ;

b) les sorties en opposition de phase 21 (- A V<sub>e</sub>) et 22 (A V<sub>e</sub>) où A représente approximativement le gain du transistor. On suppose que ce gain

est supérieur à 1, et que la grandeur complexe représentant le gain possède une composante réelle beaucoup plus grande que la composante imaginaire.

On observe expérimentalement les résultats suivants : si l'on choisit judicieusement des couples de valeur de résistance et de capacité pour  $R_1$  5 (ou  $R_2$ ) et  $C_1$  (ou  $C_2$ ), on obtient des admittances tantôt de valeur capacitive tantôt de valeur inductive. On peut obtenir par tâtonnement une admittance qui soit une résistance pure.

Le fonctionnement de l'amplificateur selon l'invention peut être expliqué comme suit, par un raisonnement assez simple. On a représenté à la 10 figure 3, un quadripôle intégrant deux bornes d'entrée de l'amplificateur, soit 11 et 12, et deux bornes de sortie, soit 21 et 22. Les transistors  $T_1$  et  $T_2$  sont représentés par des symboles classiques d'amplificateurs d'entrées G et G' et de sorties D et D', avec une mise à la masse par la source (S ou S') de chacun de ces amplificateurs. Le couplage capacitif est réalisé par les 15 condensateurs de capacité  $C_1$  et  $C_2$  connectés respectivement entre G' et D et entre G et D'. On a :

$$C_1 = C_2 = C.$$

On a représenté une source de signal  $V_e$  présentant deux sorties en opposition de phase (+  $V_e$  et -  $V_e$ ) reliées aux bornes d'entrée 11 et 12. Enfin 20 une charge d'utilisation Z présente deux entrées reliées aux bornes 21 et 22, la charge étant symétrique par rapport à la masse. Aux bornes de sortie on a les tensions  $-AV_e$  et  $AV_e$  par suite du changement de phase de  $180^\circ$  dans un montage du type "en source commune".

On adopte les désignations suivantes, les caractéristiques des transistors étant supposées identiques entre elles. 25

$G_e$  : conductance d'entrée de chaque transistor ;

$C_e \omega$  : susceptance d'entrée de chaque transistor à la pulsation  $\omega$  ;

$A$  : le gain de chaque transistor, avec :

$$A = -Ar + jAi$$

30 où l'on a  $Ar$  supérieur à l'unité et beaucoup plus grand qu' $Ai$ .

Y<sub>e</sub> et Y'<sub>e</sub> les admittances sans réaction et avec réaction, à l'entrée de chaque transistor ;

I<sub>e</sub> : le courant grille-source ;

J<sub>e</sub> : le courant traversant  $C_2$  dans le sens grille-drain.

On voit facilement, par un calcul élémentaire, que l'on a sensiblement :

$$Y'e = G_e + j C e \omega - j C \omega (A_r + 1) \quad (1)$$

dont la partie imaginaire s'annule pour :

5       $C = \frac{C_e}{A_r + 1} \quad (2)$

et peut devenir négative pour  $C$  supérieur à la valeur ci-dessus, ce qui correspond à une admittance inductive.

En effet, entre le courant  $I_e$  et la tension  $V_e$ , on a la relation, en tenant compte de la conductance et de la susceptance définies plus haut :

10      $I_e = (G_e + j C e \omega) V_e \quad (3)$

On voit également sur le schéma de la figure 3, que le courant  $J_e$  est donné par la formule :

$$J_e = j C \omega (V_e - A_1 V_e) \quad (4)$$

et pratiquement en négligeant  $A_1$  devant  $A_2$  :

15      $J_e = - j C \omega (1 + A_r) V_e \quad (5)$

L'admittance avec réaction est donc :

$$Y'e = \frac{I_e + J_e}{V_e} = \frac{(G_e + j C e \omega) V_e - j C \omega (1 + A_r) V_e}{V_e}$$

20     d'où l'on tire la relation (1) déjà écrite.

Une analyse plus approfondie montre que la conductance d'entrée est également réduite par la réaction, comme la susceptance, donc qu'elle aussi peut devenir négative, ce qui correspond à une instabilité. Les résistances  $R_1$  et  $R_2$  (figure 1) sont des résistances de contre réaction qui contribuent à éliminer le risque d'instabilité.

Sur la figure 3 on a représenté un schéma équivalent intrinsèque (du type à constantes localisées) d'un transistor à effet de champ, dans une hypothèse assez simplifiée. On a par exemple, pour un transistor à effet de champ à faible bruit, pouvant amplifier efficacement des signaux à 10 GHz :

30      $R_G = 3 \text{ ohms}$

$$C_{GS} = 0,2 \text{ picofarad}$$

$$g_m = 30 \text{ millimhos}$$

$$C_{DS} = 0,03 \text{ picofarad}$$

$$G_{DS} = 2,5 \text{ millimho}$$

$$R_D = 3 \text{ ohms}$$

Si l'on introduit les données résultant de ce schéma dans le circuit de la figure 1, on peut calculer l'admittance d'entrée :

5       $Y_e = G_e + j B_e$

en utilisant un calculateur de réseaux électriques de type linéaire, avec différentes valeurs des couples R et C pour les valeurs communes des résistances  $R_1$  et  $R_2$  et des capacités  $C_1$  et  $C_2$ . On obtient par exemple le tableau suivant, en prenant une valeur fixe (333 ohms) pour R et une sortie 10 en circuit ouvert :

#### TABLEAU

| 15 | C(pF) | G <sub>e</sub> (ohm) | B <sub>e</sub>       |

|----|-------|----------------------|----------------------|

| 20 | 0     | $1,64 \cdot 10^{-2}$ | $7,52 \cdot 10^{-3}$ |

|    | 0,02  | $1,19 \cdot 10^{-2}$ | $2,92 \cdot 10^{-3}$ |

|    | 0,04  | $7,7 \cdot 10^{-3}$  | $6,02 \cdot 10^{-4}$ |

| 25 | 0,06  | $2,99 \cdot 10^{-3}$ | $-1,3 \cdot 10^{-4}$ |

En ce qui concerne la facilité de réalisation d'un tel amplificateur, il suffit de remarquer qu'une résistance de 333 ohms peut être obtenue par dépôt d'une couche très mince de nickel-chrome, et que la capacité de 0,06 pF, en prenant comme diélectrique une couche de silice épaisse de 2 000 30 angströms, est réalisée par un recouvrement sur une région de 300 microns carrés.

On peut voir aussi par le calcul, tant dans le cas du schéma simplifié de la figure 4 que dans le cas d'un schéma équivalent plus complexe, que l'impédance de sortie de l'amplificateur est peu modifiée par l'adjonction du

couplage capacitif selon l'invention. Cette impédance est généralement capacitive et le couplage capacitif modifie la capacité équivalente d'une valeur moindre que la valeur de la capacité de couplage mutuel.

REVENDICATIONS

1. Amplificateur comportant deux transistors à effet de champ ( $T_1$ ,  $T_2$ ), caractérisé en ce que la grille ( $G, G'$ ) de chacun d'eux est reliée au drain de l'autre ( $D', D$ ) par une capacité de couplage ( $C_1, C_2$ ).

2. Amplificateur selon la revendication 1, caractérisé en ce que les sources des transistors sont reliées à un point commun, la grille du premier transistor constituant une première entrée (11) destinée à recevoir un premier signal et la grille du second transistor constituant une deuxième entrée (12) destinée à recevoir un deuxième signal de même amplitude que le premier et de signe opposé, les drains des transistors constituant deux bornes de sortie (21, 22) de l'amplificateur symétriques par rapport au point commun des sources.

3. Amplificateur selon la revendication 1, caractérisé en ce qu'il comporte en outre des résistances ( $R_1, R_2$ ) reliant respectivement la grille et le drain de chaque transistor.

4. Amplificateur selon l'une quelconque des revendications 1 à 3, caractérisé en ce qu'il est réalisé en circuit intégré sur un substrat semiconducteur.

5. Amplificateur selon la revendication 4, caractérisé en ce que, les transistors étant disposés tête bêche sur le substrat, chacun d'eux comporte une métallisation (25, 26) d'électrode de drain recouvrant partiellement une métallisation (23, 24) prolongeant l'électrode de grille de l'autre transistor, une couche de diélectrique séparant les deux parties des métallisations qui se recouvrent.

6. Amplificateur selon la revendication 4, caractérisé en ce que, les transistors étant disposés tête bêche sur le substrat, chacun d'eux comporte une métallisation (23, 24) prolongeant l'électrode de grille recouvrant partiellement une métallisation (25, 26) prolongeant l'électrode de drain de l'autre transistor, une couche de diélectrique séparant les deux parties des métallisations qui se recouvrent.

1/2

**FIG. 1****FIG. 2**

2/2

FIG.3

FIG.4