(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7080098号**

**(P7080098)**

(45)発行日 令和4年6月3日(2022.6.3)

(24)登録日 令和4年5月26日(2022.5.26)

(51)国際特許分類

**G 0 1 R 19/175 (2006.01)**

F I

G 0 1 R

19/175

請求項の数 3 (全16頁)

|          |                             |          |                                           |

|----------|-----------------------------|----------|-------------------------------------------|

| (21)出願番号 | 特願2018-83377(P2018-83377)   | (73)特許権者 | 715010864<br>エイブリック株式会社<br>東京都港区三田三丁目9番6号 |

| (22)出願日  | 平成30年4月24日(2018.4.24)       | (72)発明者  | 有山 稔<br>千葉県千葉市美浜区中瀬1丁目8番地<br>エイブリック株式会社内  |

| (65)公開番号 | 特開2019-190971(P2019-190971) | (72)発明者  | 岡 智博<br>千葉県千葉市美浜区中瀬1丁目8番地<br>エイブリック株式会社内  |

| A)       |                             | (72)発明者  | 江澤 祐輔<br>千葉県千葉市美浜区中瀬1丁目8番地<br>エイブリック株式会社内 |

| (43)公開日  | 令和1年10月31日(2019.10.31)      | 審査官      | 田口 孝明                                     |

| 審査請求日    | 令和3年3月9日(2021.3.9)          |          |                                           |

最終頁に続く

(54)【発明の名称】 ゼロクロス検出回路およびセンサ装置

**(57)【特許請求の範囲】****【請求項1】**

センサ素子の出力信号である入力信号n1と入力信号n2が入力され、第一比較結果を出力する第一比較回路と、

ヒステリシス機能を有し、前記入力信号n1と前記入力信号n2が入力され、第二比較結果を出力する第二比較回路と、

供給される電源電圧が所定の電圧以上になったときに検出信号を出力する電源電圧検出回路と、

前記第一比較結果と前記第二比較結果と前記検出信号に基づいてゼロクロス検出信号を出力する論理回路と、を備え

前記第二比較回路は、第一閾値及び第二閾値と、前記第一比較結果が入力される閾値選択端子とを有し、

前記第一比較結果に応じて前記第一閾値と前記第二閾値を切替える

ことを特徴とするゼロクロス検出回路。

**【請求項2】**

前記論理回路は、前記検出信号を受けたときに、

前記第一比較結果と前記第二比較結果が同じレベルであると、前記第二比較結果に基づいて決定される前記ゼロクロス検出信号を出力し、

前記第一比較結果と前記第二比較結果が異なったレベルであると、前記第一比較結果と前記第二比較結果に基づいて決定される前記ゼロクロス検出信号を出力する

ことを特徴とする請求項 1 に記載のゼロクロス検出回路。

【請求項 3】

印加される物理量の強度に応じて信号を出力するセンサ素子と、

前記センサ素子の出力する信号のゼロクロス検出を行う請求項 1 または 2 に記載のゼロクロス検出回路と、

を備えたことを特徴とするセンサ装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ゼロクロス検出回路およびセンサ装置に関する。

10

【背景技術】

【0002】

従来からゼロクロス検出回路において、ゼロクロス近傍での入力信号のノイズを防止するための技術が検討されている。

【0003】

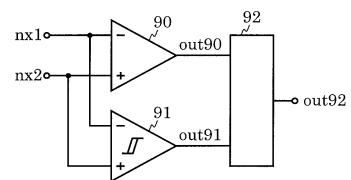

従来のゼロクロス検出回路を図 12 に示す。従来のゼロクロス検出回路は、比較回路 90 と、ヒステリシス機能を有する比較回路 91 と、論理回路 92 を備えている。比較回路 90 は、入力信号  $n \times 1$  と入力信号  $n \times 2$  のゼロクロス検出結果を  $out_{90}$  端子に電圧  $V_{out_{90}}$  として出力する。比較回路 91 は、入力信号  $n \times 1$  と入力信号  $n \times 2$  と状況によって切替えられる閾値との比較結果を  $out_{91}$  端子に電圧  $V_{out_{91}}$  として出力する。

20

論理回路 92 は、比較回路 90 が出力するゼロクロス検出結果  $V_{out_{90}}$  と比較回路 91 が出力する比較結果  $V_{out_{91}}$  の論理状態に応じて出力電圧  $V_{out_{92}}$  の論理を決定し  $out_{92}$  端子に出力する。

【0004】

より詳しくは、論理回路 92 は、 $V_{out_{91}}$  がハイレベルであるときには、 $V_{out_{90}}$  のハイレベルからローレベルの遷移によって  $V_{out_{92}}$  をハイレベルからローレベルに遷移させる。 $V_{out_{92}}$  が元々ローレベルであれば、 $V_{out_{90}}$  のハイレベルからローレベルの遷移によって  $V_{out_{92}}$  は変化せずローレベルを維持する。 $V_{out_{90}}$  のローレベルからハイレベルの遷移によって  $V_{out_{92}}$  は変化しない。また一方で、 $V_{out_{91}}$  がローレベルであるときには、 $V_{out_{90}}$  のローレベルからハイレベルの遷移によって  $V_{out_{92}}$  をローレベルからハイレベルに遷移させる。 $V_{out_{92}}$  が元々ハイレベルであれば、 $V_{out_{90}}$  のローレベルからハイレベルの遷移によって  $V_{out_{92}}$  は変化せずハイレベルを維持する。 $V_{out_{90}}$  のローレベルからハイレベルの遷移によって  $V_{out_{92}}$  は変化しない。

30

上述のようなゼロクロス検出回路は、ゼロクロス近傍での入力信号のノイズの影響を除去できるので、ゼロクロス点を高精度に検出することが可能である。また時間に依存しないヒステリシス特性を持たせているため、ロータの高速回転、すなわち高速な検出が可能である（例えば、特許文献 1 参照）。

【先行技術文献】

40

【特許文献】

【0005】

【文献】特開 2017 - 211365 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来のゼロクロス検出回路においては、回路に電源電圧が供給された直後の動作、すなわち動作開始時における動作に関して考慮されていなかった。例えば、モータ内のロータの回転位置を磁気センサで検出する場合においては、電源投入直後の位置検出は、ゼロクロス近傍の弱い磁場ではなく強い磁場の印加によって位置を検出することに

50

よって回転位置検出の確度を高め、回転開始時の動作を確実にしたいという要求がある。従来のゼロクロス検出回路では、このような要求に対応できないという課題があった。

#### 【0007】

したがって、本発明は、電源投入直後に正確な検出信号を出力することが出来るゼロクロス検出回路及びセンサ装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

従来のこのような問題点を解決するために、本発明のゼロクロス検出回路は、入力信号n1と入力信号n2が入力され、第一比較結果を出力する第一比較回路と、ヒステリシス機能を有し、入力信号n1と入力信号n2が入力され、第二比較結果を出力する第二比較回路と、供給される電源電圧が所定の電圧以上になったときに検出信号を出力する電源電圧検出回路と、第一比較結果と第二比較結果と検出信号に基づいてゼロクロス検出信号を出力する論理回路と、を備えることを特徴とする。

10

#### 【発明の効果】

#### 【0009】

本発明のゼロクロス検出回路によれば、供給される電源電圧が所定の電圧以上になったときに論理回路に検出信号を出力する電源電圧検出回路を備えたので、電源投入直後に正確な検出信号を出力することが可能になる。

#### 【図面の簡単な説明】

#### 【0010】

20

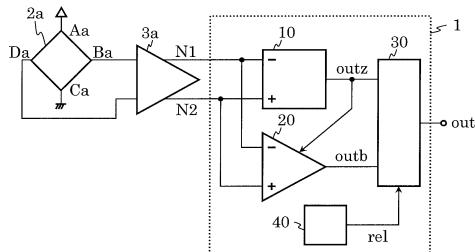

【図1】本発明の第1の実施形態のゼロクロス検出回路を備えた磁気センサ装置を示すブロック図である。

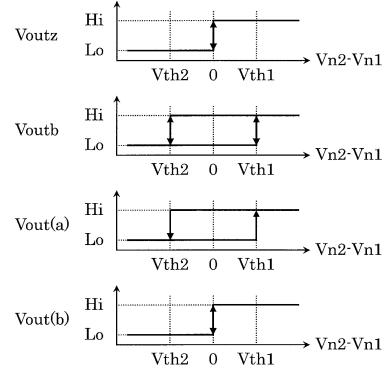

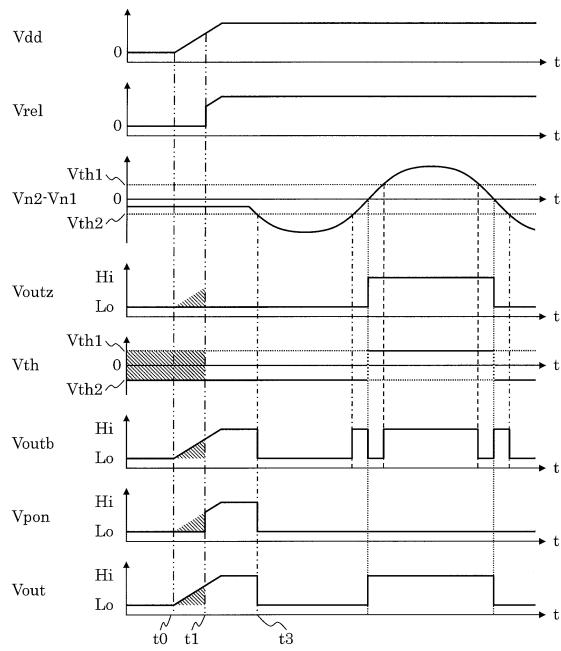

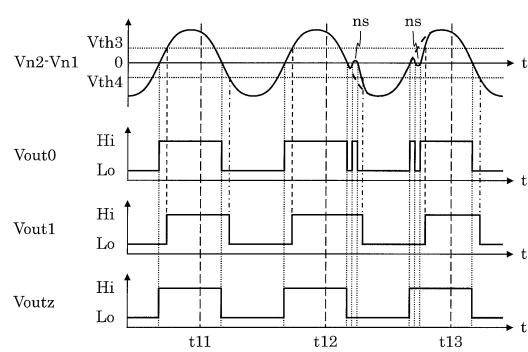

【図2】第1の実施形態のゼロクロス検出回路の各要素の動作を示す図である。

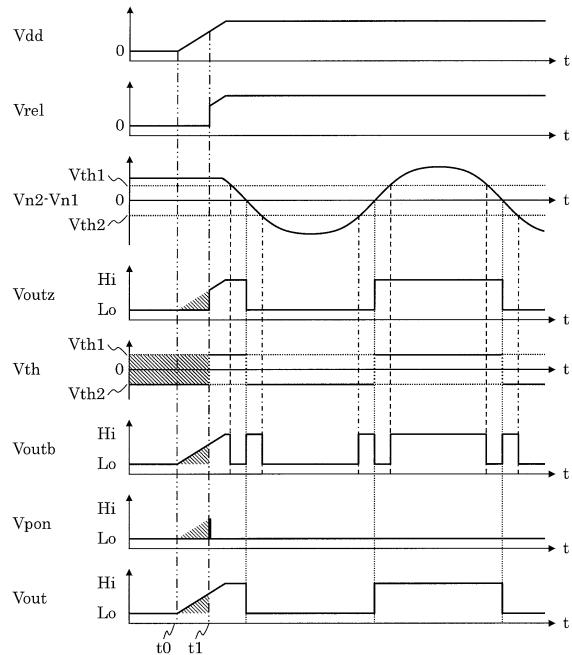

【図3】第1の実施形態のゼロクロス検出回路の動作を示す図である。

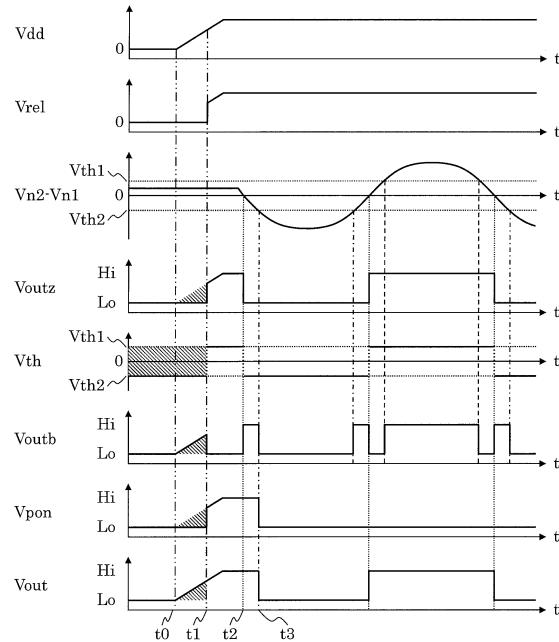

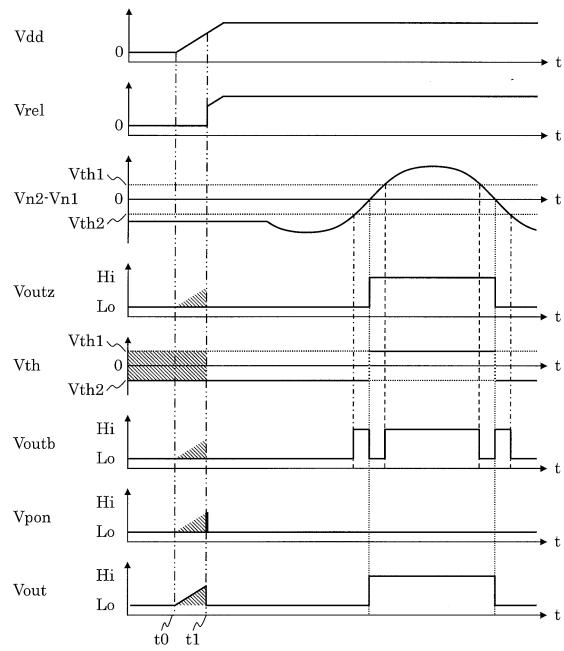

【図4】第1の実施形態のゼロクロス検出回路の動作を示す図である。

【図5】第1の実施形態のゼロクロス検出回路の動作を示す図である。

【図6】第1の実施形態のゼロクロス検出回路の動作を示す図である。

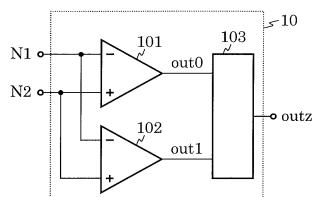

【図7】第1の実施形態のゼロクロス信号生成回路の一例である。

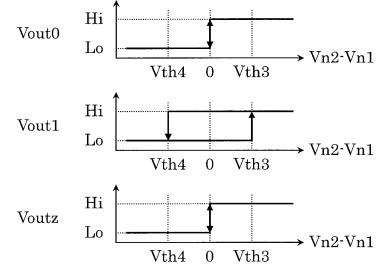

【図8】第1の実施形態のゼロクロス信号生成回路の一例の各要素の動作を示す図である。

【図9】第1の実施形態のゼロクロス信号生成回路の一例の動作を示す図である。

30

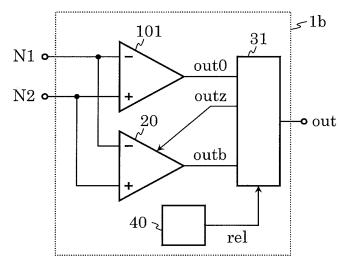

【図10】第2の実施形態のゼロクロス検出回路のブロック図である。

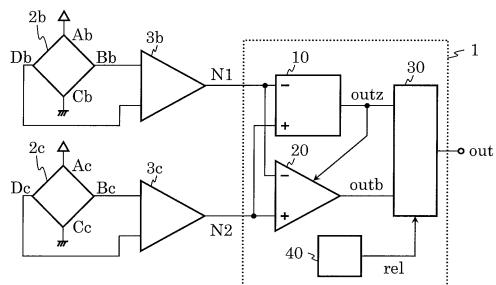

【図11】第3の実施形態のゼロクロス検出回路を備えた磁気センサ装置を示すブロック図である。

【図12】従来のゼロクロス検出回路の回路図である。

#### 【発明を実施するための形態】

#### 【0011】

本発明のゼロクロス検出回路は、半導体回路におけるゼロクロス検出回路として幅広く利用されうる。以下、本発明のゼロクロス検出回路およびセンサ装置について図面を参照して説明する。

40

#### 【0012】

#### <第1の実施形態>

図1は、本発明の実施形態のゼロクロス検出回路を備えたセンサ装置を示すブロック図である。本実施形態のセンサ装置は、ゼロクロス検出回路1と、ホール素子2aと、差動増幅回路3aを備えている。

#### 【0013】

ゼロクロス検出回路1は、ゼロクロス信号生成回路10と、比較回路20と、論理回路30と、電源電圧検出回路40を備えている。ゼロクロス信号生成回路10は反転入力端子と非反転入力端子と出力端子outzを有する。比較回路20は反転入力端子と非反転入力端子と閾値選択端子と出力端子outbを有する。ゼロクロス信号生成回路10の非反転入力端子と比較回路20の非反転入力端子は端子N2で共通に接続される。ゼロクロス

50

信号生成回路 10 の反転入力端子と比較回路 20 の反転入力端子は端子 N 1 で共通に接続される。ゼロクロス信号生成回路 10 の出力端子 out z と比較回路 20 の出力端子 out b は論理回路 30 に接続される。ゼロクロス信号生成回路 10 の出力端子 out z は比較回路 20 の閾値選択端子に接続される。電源電圧検出回路 40 は電源端子（図示せず）と出力端子 real を有する。論理回路 30 は出力端子 out z と出力端子 out b と出力端子 real を入力とし、出力端子 out から論理演算結果を出力する。

#### 【 0 0 1 4 】

ホール素子 2 a は、端子 A a、端子 B a、端子 C a、端子 D a を有する。端子 A a と端子 C a は対向した位置に配置され、端子 B a と端子 D a は対向した位置に配置される。端子 A a と端子 C a はそれぞれ異なる電位の配線に接続される。説明のために、この異なる電位を電位 V DD と、電位 V DD よりも低い電位の電位 V SS とし、端子 A a の電位を V D D、端子 C a の電位を V SS とする。

10

#### 【 0 0 1 5 】

差動増幅器 3 a は 2 つの入力端子と 2 つの出力端子を有する。2 つの入力端子には、それぞれ端子 B a、端子 D a が接続される。2 つの出力端子は、それぞれ端子 N 1、端子 N 2 に接続される。

#### 【 0 0 1 6 】

以降の説明では、端子 N 1、端子 N 2、出力端子 out z、出力端子 out b、出力端子 out、出力端子 real の各電圧をそれぞれ電圧 V n 1、電圧 V n 2、出力電圧 V out z、出力電圧 V out b、出力電圧 V out、出力電圧 V real とする。また、差動増幅器 3 a、ゼロクロス信号生成回路 10、比較回路 20、論理回路 30 および電源電圧検出回路 40 には電源電圧端子（図示せず）から電源電圧が供給される。説明のために、供給される電源電圧のうち、高い電位を V DD、もう一方の低い電位を V SS とし、電位 V SS は 0 V（ゼロボルト）とすると、回路には電位 V DD と電位 V SS = 0 V の差分である電源電圧 V dd が供給される。

20

#### 【 0 0 1 7 】

磁電変換素子であるホール素子 2 a の信号は、端子 B a と端子 D a から差動増幅器 3 a に入力され、差動増幅器 3 a はこれを増幅し、差動増幅器 3 a の出力はゼロクロス検出回路 1 の入力端子 N 1、入力端子 N 2 に接続される。ここで、端子 B a と端子 D a の電圧をそれぞれ V Ba、V Da とし、ホール素子 2 a の信号電圧を V Da - V Ba とし、差動増幅器 3 a の増幅率を G とする。

30

#### 【 0 0 1 8 】

ホール素子 2 a の信号電圧 V Da - V Ba は、ホール素子 2 a に流れる電流の向きと、印加される磁界の向きによりフレミング左手の法則に従って、その大きさと符号が変化する。仮に紙面の手前から奥の方向に磁界が印加された場合の信号電圧 V Da - V Ba の符号が正とすると、紙面の奥から手前の方向に磁界が印加された場合には信号電圧 V Da - V Ba の符号が負となる。また、印加される磁界が大きいほど、信号電圧 V Da - V Ba の大きさは大きくなる。また、ホール素子 2 a のオフセット電圧がゼロである理想的な場合には、ホール素子 2 a に印加される磁界がゼロである場合の信号電圧 V Da - V Ba はゼロとなる。以降の説明では、ホール素子 2 a のオフセット電圧がゼロの場合について説明する。ホール素子 2 a の信号電圧は差動増幅器 3 a により増幅され、

40

$$V n 2 - V n 1 = G \times (V Da - V Ba) \dots (1)$$

となる。従って、V n 2 - V n 1 はホール素子 2 a に印加される磁界に応じて、正または負またはゼロの値をとる。印加磁界が弱い場合には | V n 2 - V n 1 | の絶対値である | V n 2 - V n 1 | の値は小さく、印加磁界が強い場合には | V n 2 - V n 1 | の値は大きくなる。

#### 【 0 0 1 9 】

ゼロクロス検出回路 1 は、端子 N 1 および端子 N 2 に入力される電圧 V n 2、V n 1 に応じて出力電圧 V out を変化させる。この動作を図 2 および図 3 ~ 図 6 を用いて説明する。

#### 【 0 0 2 0 】

50

先ず、ゼロクロス信号生成回路 10 の動作を説明する。ゼロクロス信号生成回路 10 は非反転入力端子に供給される電圧が反転入力端子に供給される電圧よりも高いときは出力端子  $v_{out\ z}$  からハイレベルを出力し、これとは逆に、非反転入力端子に供給される電圧が反転入力端子に供給される電圧よりも低いときは、出力端子  $v_{out\ z}$  からローレベルを出力するように動作する。この動作の詳細を図 2 に示す。

#### 【 0 0 2 1 】

図 2 の横軸は電圧  $V_{n\ 1}$  と電圧  $V_{n\ 2}$  の入力電圧差を示し、縦軸は各々の出力電圧を示す。出力電圧  $v_{out\ z}$  は、電圧  $V_{n\ 2}$  が電圧  $V_{n\ 1}$  よりも高いとき、すなわち、 $V_{n\ 2} - V_{n\ 1} > 0$  であるときはハイレベルを出力する。これとは逆に、電圧  $V_{n\ 2}$  が電圧  $V_{n\ 1}$  よりも低いとき、すなわち、 $V_{n\ 2} - V_{n\ 1} < 0$  であるときはローレベルを出力する。従って、ゼロクロス信号生成回路 10 は入力される電圧  $V_{n\ 2}$  と電圧  $V_{n\ 1}$  の差分に応じた出力電圧  $v_{out\ z}$  を出力する。ここで、出力電圧  $v_{out\ z}$  はゼロクロス近傍、すなわち  $V_{n\ 2} - V_{n\ 1} = 0$  近傍のノイズを除去した信号である。このノイズ除去動作の例については後述する。

10

#### 【 0 0 2 2 】

次に、比較回路 20 の動作を説明する。比較回路 20 は、非反転入力端子に供給される電圧が反転入力端子に供給される電圧と電圧  $V_{th\ 1}$  の和よりも高いときは出力端子  $v_{out\ b}$  からハイレベルを出力し、これとは逆に、非反転入力端子に供給される電圧が反転入力端子に供給される電圧と電圧  $V_{th\ 2}$  の和よりも低いときは、出力端子  $v_{out\ b}$  からローレベルを出力するように動作する。電圧  $V_{th\ 1}$  と電圧  $V_{th\ 2}$  のどちらが選択されるかは、出力電圧  $v_{out\ z}$  により決定される。出力電圧  $v_{out\ z}$  がハイレベルのときは電圧  $V_{th\ 1}$  が選択され、出力電圧  $v_{out\ z}$  がローレベルのときは電圧  $V_{th\ 2}$  が選択される。この動作の詳細を図 2 に示す。出力電圧  $v_{out\ b}$  は、電圧  $V_{n\ 2}$  が電圧  $V_{n\ 1}$  と電圧  $V_{th\ 1}$  の和よりも高いとき、すなわち、 $V_{n\ 2} - V_{n\ 1} > V_{th\ 1}$  であるときはハイレベルを出力し、電圧  $V_{n\ 2}$  が電圧  $V_{n\ 1}$  と電圧  $V_{th\ 2}$  の和よりも低いとき、すなわち、 $V_{n\ 2} - V_{n\ 1} < V_{th\ 2}$  であるときはローレベルを出力する。ここで、電圧  $V_{th\ 1}$  は正の値でプラス側の閾値電圧を表し、電圧  $V_{th\ 2}$  は負の値でマイナス側の閾値電圧を表す。出力電圧  $v_{out\ b}$  は、 $V_{n\ 2} - V_{n\ 1}$  が  $V_{th\ 1}$  と  $V_{th\ 2}$  の間であるとき、すなわち、 $V_{th\ 2} < V_{n\ 2} - V_{n\ 1} < V_{th\ 1}$  であるときは選択された閾値電圧に応じてハイレベルまたはローレベルを出力する。

20

#### 【 0 0 2 3 】

次に、電源電圧検出回路 40 の動作を説明する。電源電圧検出回路 40 は、供給される電源電圧に応じて出力電圧  $v_{rel}$  を変化させる。出力電圧  $v_{rel}$  は、供給される電源電圧が低いときはローレベルを出力し、回路動作が正常に行われる十分な電圧が供給された場合にはハイレベルを出力する。

30

#### 【 0 0 2 4 】

次に、論理回路 30 の動作を説明する。論理回路 30 は出力電圧  $v_{out\ z}$  と出力電圧  $v_{out\ b}$  と出力電圧  $v_{rel}$  の論理状態に応じて出力電圧  $v_{out\ t}$  の論理を決定するように動作する。出力電圧  $v_{rel}$  がローレベルからハイレベルに遷移した直後は、論理回路 30 は比較回路 20 の出力電圧  $v_{out\ b}$  にもとづいて決定された電圧を  $v_{out\ t}$  に出力する。その後、すなわち比較回路 20 の出力電圧  $v_{out\ b}$  にもとづいて決定された電圧を  $v_{out\ t}$  に出力した後は、論理回路 30 はゼロクロス信号生成回路 10 の出力電圧  $v_{out\ z}$  にもとづいて決定された電圧を  $v_{out\ t}$  に出力するように動作する。出力電圧  $v_{rel}$  がローレベルからハイレベルに遷移した直後の動作の詳細を図 2 の波形  $v_{out\ t}$  ( a ) に示し、その後の動作の詳細を波形  $v_{out\ t}$  ( b ) に示す。また、この動作の詳細について図 3 ~ 図 6 を用いて説明する。

40

#### 【 0 0 2 5 】

図 3 は、十分に強い正の信号、すなわち  $V_{n\ 2} - V_{n\ 1} > V_{th\ 1}$  であるときに電源が投入された場合のゼロクロス検出回路 1 の動作を示す図である。ここで横軸は時間経過を示し、縦軸は入力電圧差または出力電圧を示す。

50

**【 0 0 2 6 】**

回路に供給される電源電圧  $V_{dd}$  は、時刻  $t_0$ において  $0V$ （ゼロボルト）から上昇を開始し、時刻  $t_1$ で回路が正常に動作するのに十分な電圧に達する。電源電圧検出回路 40 の出力電圧  $V_{rel}$  は、回路が正常に動作するのに十分な電源電圧  $V_{dd}$  に達したことを受けて、時刻  $t_1$ でローレベルからハイレベルに変化する。

**【 0 0 2 7 】**

時刻  $t_1$ より前の時刻においては、回路に供給される電源電圧  $V_{dd}$  が低いために、ゼロクロス信号生成回路 10 および比較回路 20 は正常または正確に動作せず、出力電圧  $V_{outz}$  および  $V_{outb}$  は入力電圧に応じた出力電圧が得られない可能性がある。また出力電圧  $V_{out}$  についても同様に入力電圧に応じた  $V_{out}$  が得られない可能性がある。これを図 3 では斜線で示している。また、電源電圧  $V_{dd}$  が低いときには、出力電圧  $V_{outz}$ 、 $V_{outb}$  および  $V_{out}$  を強制的にローレベルまたはハイレベルにしても良い。出力電圧  $V_{outz}$  および  $V_{outb}$  の出力を強制的にローレベルまたはハイレベルにする動作は、ゼロクロス信号生成回路 10 および比較回路 20 に電源電圧検出回路 40 の出力  $V_{rel}$  を接続することによって実現できる（図示せず）。図 3 では、出力電圧  $V_{rel}$  がローレベルの場合には、出力電圧  $V_{outz}$  を強制的にローレベルにして、出力電圧  $V_{outb}$  および  $V_{out}$  ハイレベルにした場合を示している。

10

**【 0 0 2 8 】**

時刻  $t_1$ より後の時刻においては、電源電圧  $V_{dd}$  は回路が正常に動作するのに十分な電源電圧に達しているため、ゼロクロス信号生成回路 10 および比較回路 20 は正常かつ正確に動作しているとみなすことができる。従って出力電圧  $V_{outz}$  および  $V_{outb}$  についても入力電圧  $V_{n2}$  および  $V_{n1}$  に正しく応じた出力電圧であると見なすことができる。

20

**【 0 0 2 9 】**

時刻  $t_1$ の直後の時刻において、ゼロクロス信号生成回路 10 の出力電圧  $V_{outz}$  は、 $V_{n2} - V_{n1} > 0$  であるからハイレベルを出力する。従って、比較回路 20 の閾値電圧  $V_{th}$  は電圧  $V_{th1}$  が選択される。 $V_{n2} - V_{n1} > V_{th1}$  であるから、比較回路 20 の出力電圧  $V_{outb}$  はハイレベルを出力する。論理回路 30 は出力電圧  $V_{outz}$  および出力電圧  $V_{outb}$  がハイレベルであり、同じレベルであることから、十分に大きい信号が入力されていると判断し、論理回路 30 は比較回路 20 の出力電圧  $V_{outb}$  にもとづいて決定された電圧、すなわちハイレベルを出力電圧  $V_{out}$  に出力する。電圧  $V_{pon}$  は、論理回路 30 の内部信号であり回路図中には図示していない。電圧  $V_{pon}$  は、論理回路 30 が比較回路 20 の出力電圧  $V_{outb}$  にもとづいて決定された電圧を出力する前にハイレベルとなり、論理回路 30 が比較回路 20 の出力電圧  $V_{outb}$  にもとづいて決定された電圧を出力した後にローレベルとなる信号である。一例としては、出力電圧  $V_{rel}$  がハイレベルになった際に電圧  $V_{pon}$  がセットされてハイレベルになり、出力電圧  $V_{outz}$  と  $V_{outb}$  が同じレベルになった際に電圧  $V_{pon}$  がリセットされてローレベルになるように構成される。論理回路 30 は、電圧  $V_{pon}$  がハイレベルのときには出力電圧  $V_{outb}$  にもとづいて決定された電圧を電圧  $V_{out}$  に出力し、電圧  $V_{pon}$  がローレベルのときには出力電圧  $V_{outz}$  にもとづいて決定された電圧を電圧  $V_{out}$  に出力する。本場合においては、上述のとおり時刻  $t_1$ の直後の時刻において、出力電圧  $V_{out}$  には出力電圧  $V_{outb}$  にもとづいた電圧が出力されて、電圧  $V_{pon}$  はハイレベルからローレベルに遷移する。従って、これ以降の時刻では、論理回路 30 はゼロクロス信号生成回路 10 の出力電圧  $V_{outz}$  にもとづいて決定された電圧を  $V_{out}$  に出力するよう動作する。

30

**【 0 0 3 0 】**

図 4 は、弱い正の信号、すなわち  $0 < V_{n2} - V_{n1} < V_{th1}$  であるときに電源が投入された場合のゼロクロス検出回路 1 の動作を示す図である。電源電圧  $V_{dd}$  および出力電圧  $V_{rel}$  の波形については図 3 と同様であり、斜線部についても図 3 と同様である。時刻  $t_1$ までの時刻においての  $V_{outz}$ 、 $V_{outb}$ 、 $V_{pon}$  および  $V_{out}$  の波形に

40

50

ついても図3と同様である。

#### 【0031】

時刻  $t_1$  の直後の時刻において、ゼロクロス信号生成回路10の出力電圧  $V_{outz}$  は、 $V_{n2} - V_{n1} > 0$  であるからハイレベルを出力する。従って、比較回路20の閾値電圧  $V_{th}$  は電圧  $V_{th1}$  が選択される。 $V_{n2} - V_{n1} < V_{th1}$  であるから、比較回路20の出力電圧  $V_{outb}$  はローレベルを出力する。論理回路30は、出力電圧  $V_{outz}$  がハイレベル、出力電圧  $V_{outb}$  がローレベルであり、異なるレベルであることから、小さい信号が入力されていると判断し、論理回路30は出力電圧  $V_{out}$  を変更せず、直前の電圧であるハイレベルを保持する。電圧  $V_{pon}$  についてもハイレベルを保持する。

#### 【0032】

時刻  $t_1$  より後の時刻に、 $V_{n2} - V_{n1}$  は変化を開始し、時刻  $t_2$  で  $V_{n2} - V_{n1} = 0$  となる。すなわちゼロクロスする。時刻  $t_2$  の直後の時刻に、ゼロクロス信号生成回路10の出力電圧  $V_{outz}$  は、 $V_{n2} - V_{n1} < 0$  であるからローレベルを出力する。従って、比較回路20の閾値電圧  $V_{th}$  は電圧  $V_{th2}$  が選択される。 $V_{n2} - V_{n1} > V_{th2}$  であるから、比較回路20の出力電圧  $V_{outb}$  はハイレベルを出力する。論理回路30は、出力電圧  $V_{outz}$  がローレベル、出力電圧  $V_{outb}$  がハイレベルであり、異なるレベルであることから、小さい信号が入力されていると判断し、論理回路30は出力電圧  $V_{out}$  を変更せず、直前の電圧であるハイレベルを保持する。電圧  $V_{pon}$  についてもハイレベルを保持する。

#### 【0033】

時刻  $t_2$  より後の時刻でも  $V_{n2} - V_{n1}$  は変化を続け、時刻  $t_3$  で  $V_{n2} - V_{n1} = V_{th2}$  となる。時刻  $t_3$  の直後の時刻に、 $V_{n2} - V_{n1} < V_{th2}$  となり、比較回路20の出力電圧  $V_{outb}$  はローレベルを出力する。論理回路30は出力電圧  $V_{outz}$  および出力電圧  $V_{outb}$  がローレベルであり、同じレベルであることから、十分に大きい信号が入力されていると判断し、論理回路30は比較回路20の出力電圧  $V_{outb}$  にもとづいて決定された電圧、すなわちローレベルを出力電圧  $V_{out}$  に出力する。電圧  $V_{pon}$  はハイレベルからローレベルに遷移する。これ以降の時刻では、論理回路30はゼロクロス信号生成回路10の出力電圧  $V_{outz}$  にもとづいて決定された電圧を  $V_{out}$  に出力するように動作する。

#### 【0034】

図5は、弱い負の信号、すなわち  $V_{th2} < V_{n2} - V_{n1} < 0$  であるときに電源が投入された場合のゼロクロス検出回路1の動作を示す図である。電源電圧  $V_{dd}$  および出力電圧  $V_{rel}$  の波形については図3と同様であり、斜線部についても図3と同様である。時刻  $t_1$  までの時刻においての  $V_{outz}$ 、 $V_{outb}$ 、 $V_{pon}$  および  $V_{out}$  の波形についても図3と同様である。

#### 【0035】

時刻  $t_1$  の直後の時刻において、ゼロクロス信号生成回路10の出力電圧  $V_{outz}$  は、 $V_{n2} - V_{n1} < 0$  であるからローレベルを出力する。従って、比較回路20の閾値電圧  $V_{th}$  は電圧  $V_{th2}$  が選択される。 $V_{n2} - V_{n1} > V_{th2}$  であるから、比較回路20の出力電圧  $V_{outb}$  はハイレベルを出力する。論理回路30は、出力電圧  $V_{outz}$  がローレベル、出力電圧  $V_{outb}$  がハイレベルであり、異なるレベルであることから、小さい信号が入力されていると判断し、論理回路30は出力電圧  $V_{out}$  を変更せず、直前の電圧であるハイレベルを保持する。電圧  $V_{pon}$  についてもハイレベルを保持する。

#### 【0036】

時刻  $t_1$  より後の時刻に、 $V_{n2} - V_{n1}$  は変化を開始し、時刻  $t_3$  で  $V_{n2} - V_{n1} = V_{th2}$  となる。時刻  $t_3$  の直後の時刻に、 $V_{n2} - V_{n1} < V_{th2}$  となり、比較回路20の出力電圧  $V_{outb}$  はローレベルを出力する。論理回路30は出力電圧  $V_{outz}$  および出力電圧  $V_{outb}$  がローレベルであり、同じレベルであることから、十分に大きい信号が入力されていると判断し、論理回路30は比較回路20の出力電圧  $V_{outb}$  にもとづいて決定された電圧、すなわちローレベルを出力電圧  $V_{out}$  に出力する。電圧  $V$

10

20

30

40

50

$V_{pon}$  はハイレベルからローレベルに遷移する。これ以降の時刻では、論理回路 30 はゼロクロス信号生成回路 10 の出力電圧  $V_{outz}$  にもとづいて決定された電圧を  $V_{out}$  に出力するように動作する。

#### 【0037】

図 6 は、十分に強い負の信号、すなわち  $V_{n2} - V_{n1} < V_{th2}$  であるときには電源が投入された場合のゼロクロス検出回路 1 の動作を示す図である。電源電圧  $V_{dd}$  および出力電圧  $V_{rel}$  の波形については図 3 と同様であり、斜線部についても図 3 と同様である。時刻  $t_1$  までの時刻においての  $V_{outz}$ 、 $V_{outb}$ 、 $V_{pon}$  および  $V_{out}$  の波形についても図 3 と同様である。

#### 【0038】

時刻  $t_1$  の直後の時刻において、ゼロクロス信号生成回路 10 の出力電圧  $V_{outz}$  は、 $V_{n2} - V_{n1} < 0$  であるからローレベルを出力する。従って、比較回路 20 の閾値電圧  $V_{th}$  は電圧  $V_{th2}$  が選択される。 $V_{n2} - V_{n1} < V_{th2}$  であるから、比較回路 20 の出力電圧  $V_{outb}$  はローレベルを出力する。論理回路 30 は、出力電圧  $V_{outz}$  および出力電圧  $V_{outb}$  がローレベルであり、同じレベルであることから、十分に大きい信号が入力されていると判断し、論理回路 30 は比較回路 20 の出力電圧  $V_{outb}$  にもとづいて決定された電圧、すなわちローレベルを出力電圧  $V_{out}$  に出力する。電圧  $V_{pon}$  はハイレベルからローレベルに遷移する。これ以降の時刻では、論理回路 30 はゼロクロス信号生成回路 10 の出力電圧  $V_{outz}$  にもとづいて決定された電圧を  $V_{out}$  に出力するように動作する。

#### 【0039】

次に、ゼロクロス信号生成回路 10 のノイズ除去動作の一例について説明する。

図 7 は、第 1 の実施形態のゼロクロス信号生成回路 10 の一例の回路図である。

#### 【0040】

ゼロクロス信号生成回路 10 は、比較回路 101 と比較回路 102 と論理回路 103 で構成されている。比較回路 101 は反転入力端子と非反転入力端子と出力端子  $out_0$  を有する。比較回路 102 は反転入力端子と非反転入力端子と出力端子  $out_1$  を有する。比較回路 101 の反転入力端子と比較回路 102 の反転入力端子は端子 N1 で共通に接続される。比較回路 101 の非反転入力端子と比較回路 102 の非反転入力端子は端子 N2 で共通に接続される。端子 N1 と端子 N2 には、それぞれ第一入力信号と第二入力信号が供給される。比較回路 101 の出力端子  $out_0$  と比較回路 102 の出力端子  $out_1$  は論理回路 103 に接続される。論理回路 103 は出力端子  $out_0$  と出力端子  $out_1$  を入力とし、出力端子  $out_z$  から論理演算結果を出力する。以降の説明では、出力端子  $out_0$ 、出力端子  $out_1$  の各電圧をそれぞれ出力電圧  $V_{out0}$ 、出力電圧  $V_{out1}$  とする。

#### 【0041】

次に、ゼロクロス信号生成回路 10 の動作を図 8 および図 9 を用いて説明する。

まず、比較回路 101 の動作を説明する。比較回路 101 は、非反転入力端子に供給される電圧が反転入力端子に供給される電圧よりも高いときは出力端子  $out_0$  からハイレベルを出力し、これとは逆に、非反転入力端子に供給される電圧が反転入力端子に供給される電圧よりも低いときは、出力端子  $out_0$  からローレベルを出力する。この動作の詳細を図 8 に示す。ここで横軸は電圧  $V_{n1}$  と  $V_{n2}$  の入力電圧差を示し、縦軸は各々の出力電圧を示す。図 8 に示すように、出力電圧  $V_{out0}$  は、電圧  $V_{n2}$  が電圧  $V_{n1}$  よりも高いとき、すなわち、 $V_{n2} - V_{n1} > 0$  であるときはハイレベルを出力する。これとは逆に、電圧  $V_{n2}$  が電圧  $V_{n1}$  よりも低いとき、すなわち、 $V_{n2} - V_{n1} < 0$  であるときはローレベルを出力する。出力電圧  $V_{out0}$  のハイレベルからローレベルへの遷移は、 $V_{n2} - V_{n1} = 0$  で行われる。また、出力電圧  $V_{out0}$  のローレベルからハイレベルへの遷移は、同様に  $V_{n2} - V_{n1} = 0$  で行われる。

#### 【0042】

また、入力電圧差  $V_{n2} - V_{n1}$  が時間変化した場合の比較回路 101 の動作を図 9 に示す。

10

20

30

40

50

す。ここで横軸は時間経過を示し、縦軸は入力電圧差または出力電圧を示す。入力電圧差  $V_{n2} - V_{n1}$  は時間変化に伴って変化し、様々な値を取りうる。特に、 $V_{n2} - V_{n1} = 0$  となるときをゼロクロスと表現している。入力電圧差  $V_{n2} - V_{n1}$  の時間変化に伴って、出力電圧  $V_{out0}$  は変化する。出力電圧  $V_{out0}$  は、 $V_{n2} - V_{n1} > 0$  のときはハイレベルを出力し、 $V_{n2} - V_{n1} < 0$  のときはローレベルを出力する。 $V_{n2} - V_{n1} = 0$  のとき、すなわち、 $V_{n1} = V_{n2}$  のときに出力電圧  $V_{out0}$  はゼロクロス検出する。

#### 【0043】

次に、比較回路 102 の動作を説明する。比較回路 102 は、非反転入力端子に供給される電圧が反転入力端子に供給される電圧と電圧  $V_{th3}$  の和よりも高いときは出力端子  $o_{ut1}$  からハイレベルを出力し、これとは逆に、非反転入力端子に供給される電圧が反転入力端子に供給される電圧と電圧  $V_{th4}$  の和よりも低いときは、出力端子  $o_{ut1}$  からローレベルを出力するように動作する。この動作の詳細を図 8 に示す。図 8 に示すように、出力電圧  $V_{out1}$  は、電圧  $V_{n2}$  が電圧  $V_{n1}$  と電圧  $V_{th3}$  の和よりも高いとき、すなわち、 $V_{n2} - V_{n1} > V_{th3}$  であるときはハイレベルを出力し、電圧  $V_{n2}$  が電圧  $V_{n1}$  と電圧  $V_{th4}$  の和よりも低いとき、すなわち、 $V_{n2} - V_{n1} < V_{th4}$  であるときはローレベルを出力する。ここで、電圧  $V_{th3}$  は正の値でプラス側のヒステリシス値を表し、電圧  $V_{th4}$  は負の値でマイナス側のヒステリシス値を表す。出力電圧  $V_{out1}$  のハイレベルからローレベルへの遷移は、 $V_{n2} - V_{n1} = V_{th4}$  で行われる。また、出力電圧  $V_{out1}$  のローレベルからハイレベルへの遷移は、 $V_{n2} - V_{n1} = V_{th3}$  で行われる。 $V_{n2} - V_{n1}$  が  $V_{th3}$  と  $V_{th4}$  の間であるときには、直前の状態に応じてハイレベルまたはローレベルを出力する。すなわち、比較回路 102 は、ヒステリシス幅  $|V_{th3}| + |V_{th4}|$  を有する比較回路として動作する。

#### 【0044】

また、入力電圧差  $V_{n2} - V_{n1}$  が時間変化した場合の比較回路 102 の動作を図 9 に示す。入力電圧差  $V_{n2} - V_{n1}$  の時間変化に伴って出力電圧  $V_{out1}$  は変化する。時刻  $t_{11}$  のとき、すなわち  $V_{n2} - V_{n1} > V_{th3}$  のときに出力電圧  $V_{out1}$  はハイレベルを出力し、その後の時間経過後もハイレベルを維持し、 $V_{n2} - V_{n1}$  の減少に伴い、 $V_{n2} - V_{n1} < V_{th4}$  となったときにハイレベルからローレベルの出力に遷移し、その後の時間経過後もローレベルを維持し、 $V_{n2} - V_{n1}$  の増加に伴い、 $V_{n2} - V_{n1} > V_{th3}$  となったときにローレベルからハイレベルに遷移する。

#### 【0045】

次に、論理回路 103 の動作を説明する。論理回路 103 は、出力電圧  $V_{out0}$  と出力電圧  $V_{out1}$  の論理状態に応じて出力電圧  $V_{outz}$  の論理を決定するように動作する。より詳しくは、論理回路 103 は、 $V_{out1}$  がハイレベルであるときには、 $V_{out0}$  のハイレベルからローレベルの遷移によって  $V_{outz}$  をハイレベルからローレベルに遷移させる。 $V_{outz}$  が元々ローレベルであれば  $V_{outz}$  は変化しない。 $V_{out0}$  のローレベルからハイレベルの遷移によって  $V_{outz}$  は変化しない。また、 $V_{out1}$  がローレベルであるときには、 $V_{out0}$  のローレベルからハイレベルの遷移によって  $V_{outz}$  をローレベルからハイレベルに遷移させる。 $V_{outz}$  が元々ハイレベルであれば  $V_{outz}$  は変化しない。 $V_{out0}$  のハイレベルからローレベルの遷移によって  $V_{outz}$  は変化しない。以上の動作について図 9 を用いて説明する。

#### 【0046】

図 9において、時刻  $t_{11}$  のとき、出力電圧  $V_{out0}$  と出力電圧  $V_{out1}$  はハイレベルである。その後、時間が経過して  $V_{n2} - V_{n1}$  が減少し、ゼロクロスしたときに  $V_{out0}$  はハイレベルからローレベルに遷移する。このとき、 $V_{out1}$  はハイレベルであるから、論理回路 103 は、 $V_{out0}$  のハイレベルからローレベルのゼロクロスの検出を  $V_{outz}$  に出力する。その後、時間が経過し、 $V_{n2} - V_{n1} < V_{th4}$  となると、 $V_{out1}$  はハイレベルからローレベルに遷移する。その後、時間が経過して  $V_{n2} - V_{n1}$  が増加し、ゼロクロスしたときに  $V_{out0}$  はローレベルからハイレベルに遷移する

10

20

30

40

50

。このとき、 $V_{out\ 1}$ はローレベルであるから、論理回路103は、 $V_{out\ 0}$ のローレベルからハイレベルのゼロクロスの検出を $V_{out\ z}$ に出力する。その後、時間が経過し、 $V_{n\ 2} - V_{n\ 1} > V_{th\ 3}$ となると、 $V_{out\ 1}$ はローレベルからハイレベルに遷移する。さらにその後、時間が経過し時刻t12のときには、時刻t11と同じ状態になる。

#### 【0047】

時刻t12のとき、出力電圧 $V_{out\ 0}$ と出力電圧 $V_{out\ 1}$ はハイレベルである。その後、時間が経過して $V_{n\ 2} - V_{n\ 1}$ が減少し、ゼロクロスしたときに $V_{out\ 0}$ はハイレベルからローレベルに遷移する。このとき、 $V_{out\ 1}$ はハイレベルであるから、論理回路103は、 $V_{out\ 0}$ のハイレベルからローレベルのゼロクロスの検出を $V_{out\ z}$ に出力する。その後、時間が経過し、ノイズnsによって $V_{n\ 2} - V_{n\ 1}$ は2回ゼロクロスし、出力電圧 $V_{out\ 0}$ は、ローレベルからハイレベルに遷移した後、さらにローレベルに遷移する。このとき、 $V_{out\ 1}$ はハイレベルであるから、論理回路103は $V_{out\ 0}$ のローレベルからハイレベルの遷移を $V_{out\ z}$ に出力しないように動作する。従って、ノイズによるゼロクロス検出は出力端子 $V_{out\ z}$ には現れない。さらに時間が経過し、 $V_{n\ 2} - V_{n\ 1} < V_{th\ 4}$ となると、 $V_{out\ 1}$ はハイレベルからローレベルに遷移する。その後、時間が経過して $V_{n\ 2} - V_{n\ 1}$ が増加し、ゼロクロスしたときに $V_{out\ 0}$ はローレベルからハイレベルに遷移する。このとき、 $V_{out\ 1}$ はローレベルであるから、論理回路103は、 $V_{out\ 0}$ のローレベルからハイレベルのゼロクロスの検出を $V_{out\ z}$ に出力する。その後、時間が経過し、ノイズnsによって $V_{n\ 2} - V_{n\ 1}$ は2回ゼロクロスし、出力電圧 $V_{out\ 0}$ は、ハイレベルからローレベルに遷移した後、さらにハイレベルに遷移する。このとき、 $V_{out\ 1}$ はローレベルであるから、 $V_{out\ 0}$ のハイレベルからローレベルの遷移を $V_{out\ z}$ に出力しないように動作する。従って、ノイズによるゼロクロス検出は出力端子 $V_{out\ z}$ には現れない。その後、時間が経過し、 $V_{n\ 2} - V_{n\ 1} > V_{th\ 3}$ となると、 $V_{out\ 1}$ はローレベルからハイレベルに遷移する。さらにその後、時間が経過し時刻t13のときには、時刻t11および時刻t12と同じ状態になる。

#### 【0048】

以上により、ゼロクロス信号生成回路10の動作を説明し、ゼロクロス検出を行うと共に、ノイズによるゼロクロスの影響を除去することができ、高精度なゼロクロス信号を簡便な回路構成にて得ることが可能であることを示した。

#### 【0049】

ゼロクロス信号生成回路10の動作について、本説明においては、電圧 $V_{th\ 3}$ と電圧 $V_{th\ 4}$ を比較回路102のヒステリシス電圧として説明したが、比較回路102の機能を2つの、比較回路に分割し、一方の比較回路で $V_{n\ 2} - V_{n\ 1}$ が電圧 $V_{th\ 3}$ より大きいか小さいかを判別し、もう一方の比較回路で $V_{n\ 2} - V_{n\ 1}$ が電圧 $V_{th\ 4}$ より大きいか小さいかを判別するようにしてもよい。

#### 【0050】

以上により、本発明の実施形態のゼロクロス検出回路を備えたセンサ装置の動作を説明し、ゼロクロス検出を行うと共に、電源電圧が供給された直後、すなわち動作開始時においては、入力信号の大小をより確実に検出できることを示した。すなわち、本発明のゼロクロス検出回路の動作により、ホール素子2aに印加される磁界のゼロクロス点を検出可能であり、かつ、動作開始時の磁界の大小をより確実に検出可能であることを示した。別の表現をすると、本発明のゼロクロス検出回路を搭載したセンサ装置と磁石との相対的な位置関係を検出する用途において、相対位置の変化によってセンサ装置に印加される磁界がS極からN極に切り替わる点、またはN極からS極に切り替わる点を高精度に検出することが可能であり、かつ、動作開始時の相対位置をより確実に検出可能である。従って本発明のゼロクロス検出回路は、ロータの回転位置を高精度に検出する必要があるブラシレスモータでの使用やエンコーダでの使用に好適である。本実施形態のゼロクロス検出回路を備えたセンサ装置をブラシレスモータで使用すれば、ゼロクロス検知による回転性能の向上だけでなく、強い磁場の印加によって電源投入直後の回転位置検出の確度を高めることができ、回転開始時の動作を確実にすることが可能となる。

### 【0051】

本説明においては、説明のために詳細な条件を記載して説明したが、本発明の趣旨に沿う動作および回路構成であれば、この限りではない。例えば、各電圧のハイレベルとローレベルを明示したが、それぞれハイレベルとローレベルは逆でも良く、またハイレベルとローレベルの組合せは異なっても良い。また、回路動作が正常に行われる十分な電圧に達してから出力電圧  $V_{rel}$  が変化するまでの時間については特に言及せず説明したが、遅延時間を設けても良い。

また、電圧  $V_{th3}$  と電圧  $V_{th4}$  は、それぞれ電圧  $V_{th1}$  と電圧  $V_{th2}$  と等しい電圧でも良い。また、比較回路 20 の閾値  $V_{th}$  を制御する信号をゼロクロス信号生成回路 10 の出力電圧  $V_{outz}$  としたが、この限りではなく、論理回路 30 内で生成する出力電圧  $V_{outz}$  にもとづく電圧により制御しても良い。また、比較回路 20 の閾値  $V_{th}$  を外部から制御するのではなく、比較回路 102 と同様に自らの出力によって閾値を制御する構成としてもよい。さらに、電圧  $V_{pon}$  は出力電圧  $V_{outz}$  と出力電圧  $V_{outb}$  が同じレベルになった際にローレベルになるように構成を説明したが、出力電圧  $V_{out}$  が出力電圧  $V_{outb}$  にもとづいて出力されたことと同義の信号である構成であればこの限りではない。例えば、出力電圧  $V_{out}$  は、出力電圧  $V_{outz}$  と出力電圧  $V_{outb}$  の論理和であっても良い。

### 【0052】

#### <第2の実施形態>

図 10 は、本発明の第 2 の実施形態のゼロクロス検出回路を示すブロック図である。図 10 に示すゼロクロス検出回路 1b と、図 1 に示したゼロクロス検出回路 1 との違いは、ゼロクロス信号生成回路 10 を削除し、ゼロクロス信号生成回路 10 内の比較回路 101 を追加し、論理回路 30 を削除し、論理回路 31 を追加した点である。追加した要素は次のように構成され、接続される。また削除した要素により次の接続および動作が図 1 に示したゼロクロス検出回路 1 と異なる。図 1 および図 7 の場合と同様に、比較回路 101 の反転入力端子は端子 N1 に接続され、非反転入力端子は端子 N2 で共通に接続される。比較回路 101 の出力端子  $out_0$  は、図 1 および図 7 の場合と異なり、論理回路 31 に接続される。論理回路 31 は、論理回路 30 の機能に論理回路 103 の機能を統合した機能を備え、具体的には出力電圧  $V_{out0}$  と出力電圧  $V_{outb}$  から出力信号  $V_{outz}$  を生成する機能を追加で備える。また、論理回路 31 は出力電圧  $V_{outz}$  と出力電圧  $V_{outb}$  と出力電圧  $V_{rel}$  の論理状態に応じて出力電圧  $V_{out}$  の論理を決定するように動作する。出力電圧  $V_{rel}$  がローレベルからハイレベルに遷移した直後は、論理回路 31 は比較回路 20 の出力電圧  $V_{outb}$  にもとづいて決定された電圧を  $V_{out}$  に出力する。その後、すなわち比較回路 20 の出力電圧  $V_{outb}$  にもとづいて決定された電圧を  $V_{out}$  に出力し、出力電圧  $V_{rel}$  がハイレベルからローレベルに遷移した後は、比較回路 20 は出力信号  $V_{outz}$  により図 7 の比較回路 102 と同様の動作をするように制御され、さらに、論理回路 31 は、出力信号  $V_{out0}$  と出力信号  $V_{outb}$  から出力電圧  $V_{outz}$  を生成し、出力電圧  $V_{outz}$  を生成にもとづいて決定された電圧を  $V_{out}$  に出力するように動作する。

### 【0053】

以上のように構成し、動作させることで本実施例のゼロクロス検出回路 1b は第 1 の実施形態のゼロクロス検出回路 1 と同様の出力電圧  $V_{out}$  を得ることができ、比較回路 102 を削除することにより回路規模の縮小を実現できる。

### 【0054】

#### <第3の実施形態>

図 11 は、本発明の実施形態のゼロクロス検出回路を備えた磁気センサ装置の他の例を示すブロック図である。

ホール素子 2b と差動増幅回路 3b の接続の構成は、図 1 の磁気センサ装置のホール素子 2a と差動増幅回路 3a の接続の構成と同様である。またホール素子 2c と差動増幅回路 3c の接続の構成も、図 1 のホール素子 2a と差動増幅回路 3a の接続の構成と同様であ

る。差動増幅回路 3 b および 3 c は差動増幅回路 3 a が差動出力であるのに対して、シングルエンドで出力する。磁電変換素子であるホール素子 2 b の信号は、端子 B b と端子 D b から差動増幅器 3 b に入力され、差動増幅器 3 b はこれを増幅し、差動増幅器 3 b の出力は本発明のゼロクロス検出回路 1 の端子 N 1 に接続される。また、磁電変換素子であるホール素子 2 c の信号は、端子 B c と端子 D c から差動増幅器 3 c に入力され、差動増幅器 3 c はこれを増幅し、差動増幅器 3 c の出力は本発明のゼロクロス検出回路 1 の端子 N 2 に接続される。

#### 【 0 0 5 5 】

ここで、端子 B b、D b、B c、D c の各電圧をそれぞれ V B b、V D b、V B c、V D c とし、ホール素子 2 b および 2 c の信号電圧をそれぞれ V D b - V B b、V D c - V B c とし、差動増幅器 3 b および 3 c の増幅率をともに G とする。すると、端子 N 1 に供給される電圧 V n 1 と端子 N 2 に供給される電圧 V n 2 は次のようになる。

$$V n 1 = G \times ( V D b - V B b ) \cdots ( 2 )$$

$$V n 2 = G \times ( V D c - V B c ) \cdots ( 3 )$$

式(2)と式(3)から次式を得る。

$$V n 2 - V n 1 = G \times \{ ( V D c - V B c ) - ( V D b - V B b ) \} \cdots ( 4 )$$

従って、V n 2 - V n 1 はホール素子 2 b とホール素子 2 c に印加される磁界に応じて、正または負またはゼロの値をとる。すなわち、本発明のゼロクロス検出回路 1 の動作により、ホール素子 2 b とホール素子 2 c に印加される磁界の差のゼロクロス点を検出可能であり、かつ、動作開始時においては入力信号の大小をより確実に検出することが可能になる。別の表現をすると、2つのセンサ素子の信号が等しい場合にはゼロクロス検出信号を出力し、2つのセンサ素子のどちらの信号が大きいかを弁別して出力することが可能になり、かつ、動作開始時においては、どちらの信号が大きいかをより確実に検出することが可能になる。本実施例は、例えば、バイアス磁界を発生する磁石と、鉄などの金属や磁性体で構成された歯車の間に磁気センサ装置を配置し、歯車の回転を磁気センサ装置で検出する用途で好適である。

#### 【 0 0 5 6 】

本説明では、説明の便宜上、差動増幅回路 3 b および 3 c はシングルエンドで出力するとしたが、ノイズ耐性の向上を図るために差動出力としても良い。また、ホール素子が2つの場合を説明したが、2つよりも多くても良い。例えば、2つのホール素子の差分信号 1 と、これとは別の2つのホール素子の差分信号 2 を生成し、差分信号 1 と差分信号 2 のゼロクロスを検出するようにしても良い。

#### 【 0 0 5 7 】

図 1 および図 1 1 に本発明のゼロクロス検出回路を備えたセンサ装置の例を示した。本説明においては、説明のために具体的な例を示したが、必ずしもこの構成やセンサ素子に制限されるものではなく、広範な半導体回路およびセンサ回路において応用可能である。一例としては、磁電変換素子であるホール素子の非理想成分であるオフセット電圧をキャンセルするスピニングカレント回路と組み合わせてもよく、また差動増幅器や比較回路の非理想成分であるオフセット電圧をキャンセルするチョッピング動作またはオートゼロ動作の回路等と組み合わせてもよい。ここで、スピニングカレント回路やチョッピング動作またはオートゼロ動作の回路等と組み合せた場合は、連続時間の信号処理ではなく離散時間の信号処理となるため、ゼロクロス信号生成回路 1 0 、比較回路 2 0 、1 0 1 、1 0 2 のそれぞれの出力を組み合わせ回路によって演算して出力端子 o u t から出力するのは好ましくない。この場合はラッチ回路等の順序回路と組み合わせるのが好適である。また磁電変換素子以外にも、温度センサ素子、加速度センサ素子、圧力センサ素子といったセンサ素子のゼロクロス検出回路としても良い。

#### 【 符号の説明 】

#### 【 0 0 5 8 】

1、1 b ゼロクロス検出回路

1 0 ゼロクロス信号生成回路

10

20

30

40

50

2 0、1 0 1、1 0 2 比較回路

3 0、3 1、1 0 3 論理回路

4 0 電源電圧検出回路

2 a、2 b、2 c ホール素子

3 a、3 b、3 c 差動増幅回路

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5】

【図 6】

10

20

30

【図 7】

【図 8】

40

50

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2017-211365 (JP, A)

特開2014-020796 (JP, A)

特開2014-130088 (JP, A)

特開平07-130082 (JP, A)

特表2002-537547 (JP, A)

米国特許出願公開第2017/0271991 (US, A1)

特開2017-169401 (JP, A)

特開2004-012168 (JP, A)

特開昭64-001155 (JP, A)

米国特許第05327016 (US, A)

特開昭54-161869 (JP, A)

特開昭57-101729 (JP, A)

実開平01-088525 (JP, U)

- (58)調査した分野 (Int.Cl., DB名)

- I P C G 0 1 R 1 9 / 0 0 - 1 9 / 3 2