(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3594346号

(P3594346)

(45) 発行日 平成16年11月24日(2004.11.24)

(24) 登録日 平成16年9月10日(2004.9.10)

(51) Int.C1.<sup>7</sup>

F 1

H01L 21/8249

H01L 27/06 321B

H01L 21/8222

H01L 27/06 321F

H01L 27/06

H01L 27/06 101U

請求項の数 1 (全 13 頁)

(21) 出願番号 特願平6-333222

(22) 出願日 平成6年12月5日(1994.12.5)

(65) 公開番号 特開平7-321240

(43) 公開日 平成7年12月8日(1995.12.8)

審査請求日 平成13年1月22日(2001.1.22)

(31) 優先権主張番号 161960

(32) 優先日 平成5年12月3日(1993.12.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国テキサス州ダラス、ノース

セントラルエクスプレスウェイ 135

OO

(74) 代理人 100066692

弁理士 浅村 晃

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100094673

弁理士 林 銘三

(74) 代理人 100091339

弁理士 清水 邦明

最終頁に続く

(54) 【発明の名称】 Bi CMOSデバイスの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスを作製するための方法であって、

- a . 第1のウエル領域を有する半導体母体の表面を覆って第1の絶縁層を形成すること、

- b . 前記第1のウエル領域の第1の部分へベース領域を打ち込みすること、

- c . 前記第1の絶縁層をエッチして、前記ベース領域の一部を露出させること、

- d . 前記半導体母体の表面を覆って第1のドープされた導電層を形成すること、

- e . 前記第1の導電層を覆ってタングステンシリサイド層を堆積させること、

- f . 前記タングステンシリサイド層および前記第1の導電層をエッチしてエミッター電極を形成し、前記第1の絶縁層の一部を露出させること、および

g . 複数個のPMOSトランジスタを形成して、前記PMOSトランジスタのうちの少なくとも1個が、前記第1のウエル領域中に形成され前記ベース領域に接触する第1のソース／ドレイン領域を有するようにすること、

の工程を有し、

前記複数個のPMOSトランジスタを形成する工程が、

前記エミッター電極によって覆われない前記第1の絶縁層の部分を除去すること、

前記半導体母体と前記タングステンシリサイド層の表面に第2の絶縁層を成長すること、

前記第2の絶縁層の上に、複数のゲート電極を形成し、少なくとも1個のゲート電極を前記第1のウエル領域を覆うように形成すること、

前記半導体母体の表面に複数のソース／ドレイン領域を形成し、前記複数のソース／ドレ 20

イン領域は、前記第1のソース／ドレイン領域を含み、前記第1のソース／ドレイン領域は、前記少なくとも1個のゲート電極と前記エミッター電極の間に形成される前記方法。

【発明の詳細な説明】

【0001】

【産業上の利用分野】

本発明は一般的に半導体処理に関するものであり、更に詳細にはBiCMOSプロセスに関する。

【0002】

【従来の技術】

MOSFET構造とバイポーラートランジスタとを同一の基板上へ集積することは非常に有望なものとなってきた。当業者には良く知られたように、デジタルおよびリニアな機能は、しばしば、バイポーラー技術または金属-酸化物-半導体(MOS)技術のいずれかを用いた集積回路中において実行される。もちろん、バイポーラー集積回路は、特に相補型MOS(CMOS)回路と比べた場合、より大きい電力の消費という犠牲はあるが、MOS回路よりも高速の動作速度とより大きな駆動電流を提供できる。製造技術の進歩によって、同一の集積回路の中にバイポーラートランジスタとCMOSトランジスタの両方を使用することが可能となってきた(一般にBiCMOSデバイスと呼ばれる)。バイポーラートランジスタは、バイポーラートランジスタ用のベースとしてモート領域を、エミッターとしてドープされた多結晶シリコンを、そしてコレクターとしてウエル領域を使用することによって作製されるのが普通である。その後に、付加的なモート領域を用いてPMOSトランジスタのソース／ドレイン領域が形成される。バイポーラートランジスタの電流駆動能力を更に大きなものに拡張することは、より高レベルのバイポーラー集積あるいは融合バイポーラーCMOS集積のために重要である。

【0003】

【発明の概要】

同一のウエル領域中に配置されたバイポーラートランジスタとPMOSトランジスタとを含むBiCMOSデバイスが開示される。バイポーラートランジスタは、多結晶シリコン層とタンゲステンシリサイド層とを含むエミッター電極を含んでいる。本デバイスの作製は、まず、半導体母体の表面上を覆って絶縁層を形成することから始まる。次に、ウエル領域の第1の部分中へベース領域が打ち込まれる。次に、前記第1の絶縁層がエッチされて、前記ベース領域の一部分が露出される。半導体母体の表面を覆ってドープされた導電層が形成され、このドープされた導電層を覆ってタンゲステンシリサイド層が堆積される。次に、このタンゲステンシリサイド層およびドープされた導電層がエッチされて、エミッター電極が形成される。最後に、複数個のPMOSトランジスタが作製され、それらのPMOSトランジスタの少なくとも1個は、前記ウエル領域中に形成され前記ベース領域と接触する第1のソース／ドレイン領域を有するようにされる。

【0004】

本発明の1つの特長は、融合BiCMOSデバイスを作製するための簡略化されたプロセスを提供することである。

【0005】

本発明の別の1つの特長は、p+Si/D打ち込みからエミッターの多結晶シリコンを保護することによって、p+Si/D打ち込みがバイポーラートランジスタの利得を変化させないようにするためのWSi<sub>2</sub>を含む融合されたバイポーラー／PMOS構造を提供することである。

【0006】

本発明の更に別の1つの特長は、高温の酸化物成長工程に耐えるエミッター電極キャップ層を有するBiCMOSデバイスを提供することである。

【0007】

これらおよびその他の特長は、本明細書の説明を図面とともに参照することで当業者には明らかとなるであろう。

10

20

30

30

40

50

## 【0008】

画面において、特に断らない限り、対応する要素には同じ参照符号を用いてある。

## 【0009】

## 【実施例】

本発明の好適実施例として、同一のウエル領域中にバイポーラートランジスタとPMOSトランジスタとを融合させて有するBiCMOS構造を取り上げてここに説明する。

## 【0010】

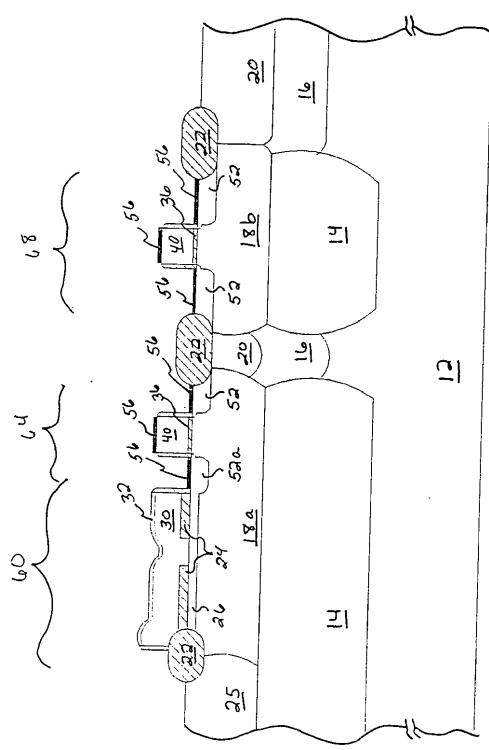

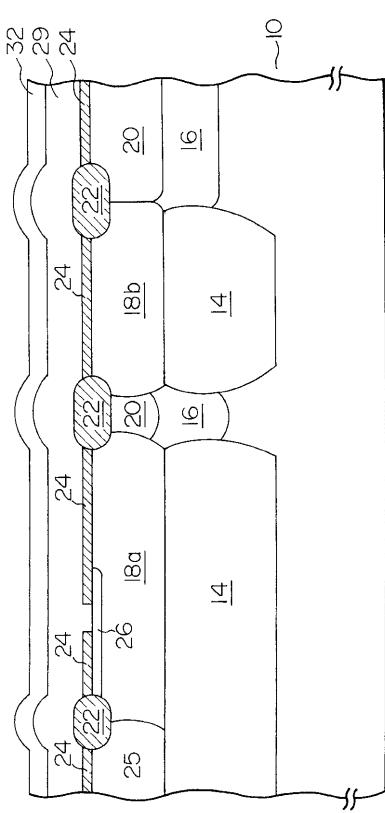

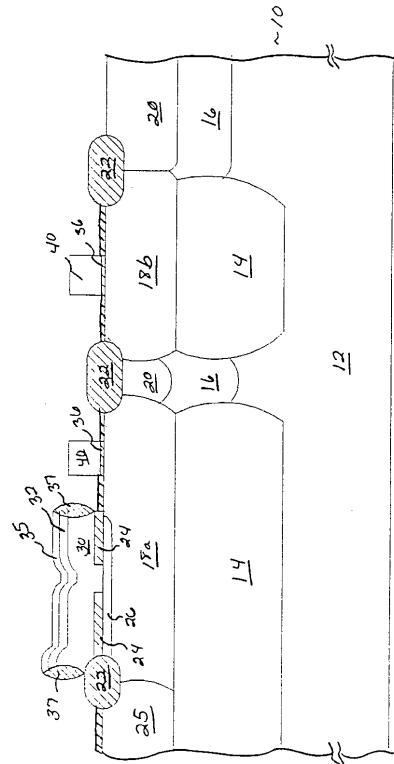

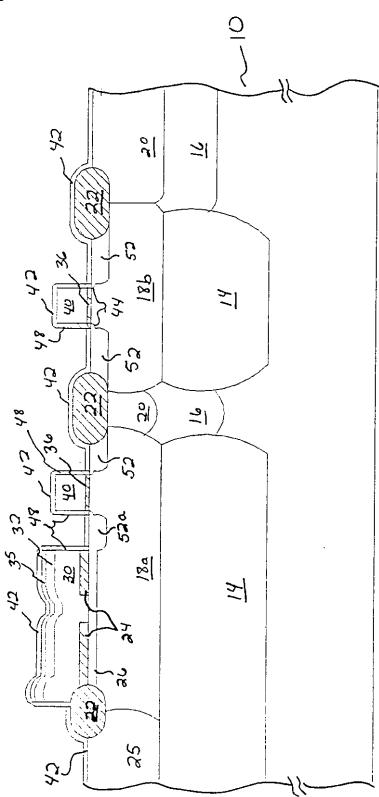

図1はバイポーラートランジスタ60と、pチャンネルトランジスタ64および68を断面図で示している。この構造は、この実施例の場合、p形シリコンである基板12中へ形成される。バイポーラートランジスタ60中の埋め込みn+領域14は、従来の意味のサブコレクターとして働き、n+領域25がそれに対する表面コンタクトとなる。n領域18aは、バイポーラートランジスタ60のコレクター領域であり、またpチャンネルトランジスタ64のウエル領域になっている。n領域18bはpチャンネルトランジスタ68のウエル領域である。真正ベース26はn領域18a-b中に設けられたp形領域である。エミッター電極30はドープされた多結晶シリコン層でよく、それは絶縁層24中の開口部を通って真正ベース領域26へ延びている。タングステンシリサイド層32がエミッター電極30を覆っている。p+領域52aはバイポーラートランジスタ60の外因性(不純物)ベース領域であり、またpチャンネルトランジスタ64のソース/ドレイン領域の1つでもある。p+領域52はpチャンネルトランジスタ64および68の残りのソース/ドレイン領域として働く。ドープされた多結晶シリコンをトランジスタ64および68のゲート40を形成するために使用することができる。ゲート酸化物36がゲート40とn領域18との間に取り付けられる。埋め込み領域16は領域20の下側に位置する。フィールド絶縁領域22は真正ベース領域26をコレクターコンタクト25から分離し、またpチャンネルトランジスタ64と68とを互いに分離する。ゲート40をシリサイド化してTiSi<sub>2</sub>層56を形成することもオプションとして可能である。トランジスタ64および68の下のn+領域14は埋め込みp領域16によって分離され、n領域18a-bはp領域20によって分離されて、2つのトランジスタのn形領域18a-bが異なる電位を有することが許容される。

## 【0011】

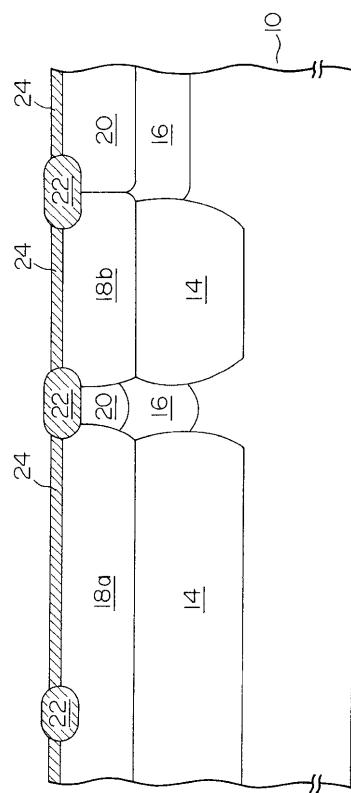

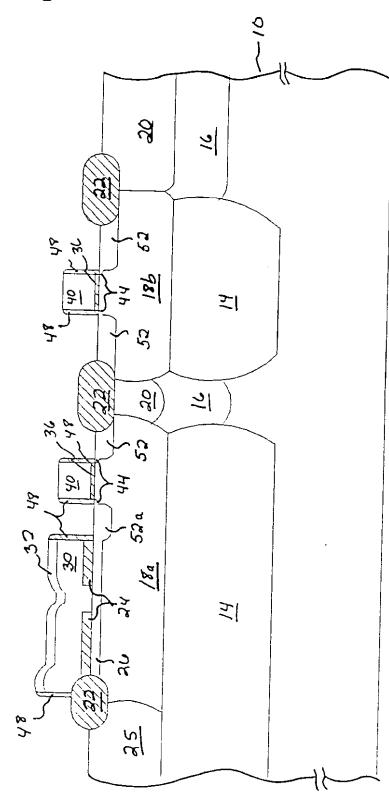

図2は、n+埋め込み層14の上に、p埋め込み層16、n形領域18a-b、p形領域20、フィールド絶縁領域22、および絶縁層24を形成した後の構造10を示している。埋め込み層を形成する方法については、1990年9月18日付けのテキサスインスツルメンツ社に譲渡された米国特許第4,958,213号に述べられている。フィールド絶縁領域22を形成する方法については、1985年9月17日付けのテキサスインスツルメンツ社に譲渡された米国特許第4,541,167号に述べられている。絶縁層24は、アンチKooi(Anti-Kooi)酸化の後に20以下の厚さにまでデグレーズ(deglaze)され、次に300オーダーの厚さに熱酸化して形成したダミーのゲート酸化物でもよい。本発明に従う融合BiCMOSデバイスの作製について、図3に示す構造に至るまでを次に説明する。

## 【0012】

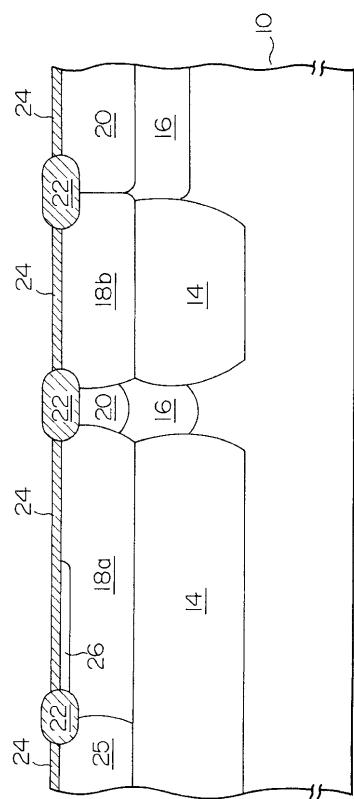

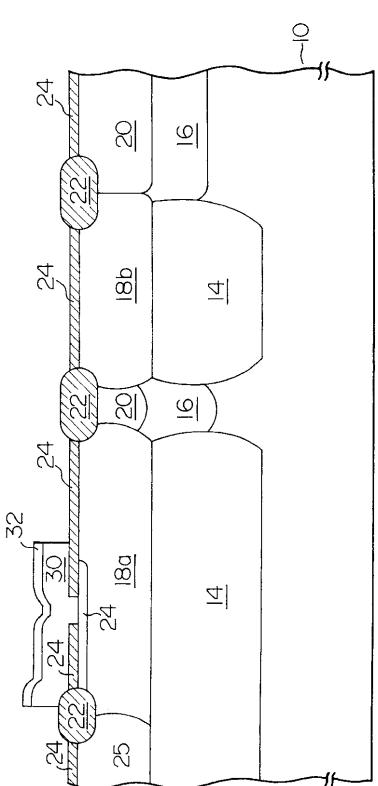

構造10の表面がパターン化され、n形ドーパントを用いた打ち込みが行われて、深いn形領域(コレクターコンタクト25)が形成される。これは、図3に示すように、n領域18を貫通してサブコレクターのn+領域14まで延びている。次に、V<sub>t</sub>調節用の打ち込みが、1つはNMOSトランジスタ(図示されていない)のため、もう1つはPMOSトランジスタ64および68のために実施されよう。更に図3を参照すると、ベース領域26が、パターン化されp形ドーパントの打ち込みがされて(例えば、ホウ素を10keVで7.0E13cm<sup>-2</sup>)、形成される。

## 【0013】

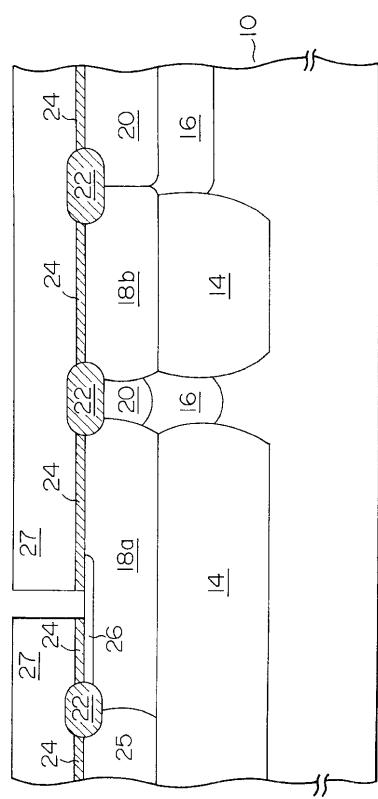

図4を参照すると、マスク層27が用いられてダミーの酸化物層24の一部が露出される。この露出した酸化物を次にエッチすることによって、ベース領域26の一部が露出され

10

20

30

30

40

50

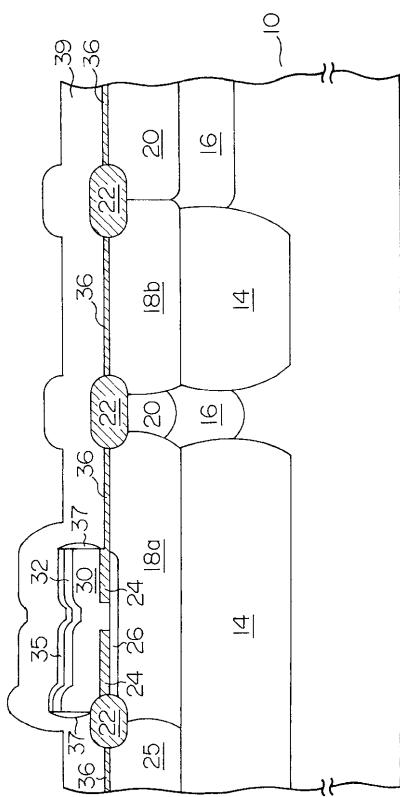

る。マスク層 27 を次に除去して、デグレーズ（例えば、10% の HF で 10 秒間）が実施されて、界面酸化物が最小化される。図 5 を参照すると、多結晶シリコン層 29 等の導電層が 2500 オーダーの厚さに堆積される。次に、イオン打ち込みによって多結晶シリコン層 29 は n 形にドープされる。あるいは、この多結晶シリコンは堆積工程中にその場ドープしてもよい。多結晶シリコン層 29 を覆ってタンゲステンシリサイド WSi<sub>2</sub> 層 32 が堆積される。WSi<sub>2</sub> 層 32 は 500 オーダーあるいはそれ以上の厚さのものでよい。次に、WSi<sub>2</sub> 層 32 がアニールされる。多結晶シリコン層 29 と WSi<sub>2</sub> 層 32 とは次にパターン化されエッチされて、図 6 に示すようにエミッター電極 30 が形成される。WSi<sub>2</sub> 層 32 は以降の処理工程で、エミッター電極 30 の酸化を妨げる。

## 【0014】

図 7 を参照すると、ダミー酸化物層 24 の露出した部分が次にデグレーズによって除去され、ゲート酸化物層 36 等の絶縁層で以て置き換えられる。ゲート酸化物層 36 は、熱酸化によって形成することができ、100 オーダーの厚さを有する。ゲート酸化物層 36 の成長の間に、図 7 に示すように、エミッター電極 30 の縦方向端部には酸化物 37 が成長し、WSi<sub>2</sub> 層 32 の上には二酸化シリコン層 35 が形成される。この熱酸化はエミッターのアニールも兼ねて十分高い温度で行うことができる。好適実施例では、900 オーダーの温度が使用されている。図 7 に示すように、多結晶シリコン層 39 等の第 2 の導電性材料の層が L P C V D 法によって構造 10 の表面を覆って堆積される。多結晶シリコン層 39 は 3500 オーダーの厚さを有する。多結晶シリコン層 39 は、次にイオン打ち込みによってドープすることができる。あるいは、多結晶シリコン層 39 は当業者には良く知られたように、その場ドーピングや（例えば、POCl<sub>3</sub> で以ての）気相でのドーピングのようなその他の手段でドープすることもできる。多結晶シリコン層 39 はパターン化されエッチされて、図 8 に示すようにゲート 40 が形成される。二酸化シリコン層 35 はこの多結晶シリコンゲートエッティングの際のエッチストップとして働く。

## 【0015】

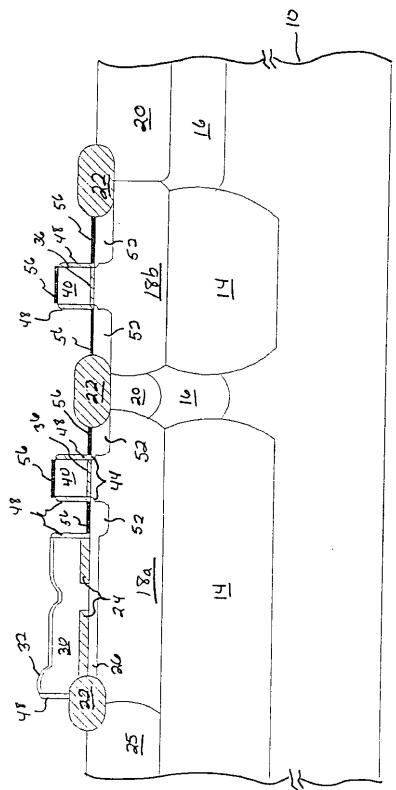

図 9 を参照すると、表面を覆ってテトラエトキシシラン (TEOS) の層 42 が堆積される。次に、従来の方法を用いて、低濃度にドープされたドレイン (LDD) 44 の打ち込みが行われ、側壁スペーサー 48、およびソース / ドレイン領域 52 が形成される。LDD 44 はオプションであり、必ずしも必要でないことを注意しておく。側壁スペーサー 48 は、誘電体層を堆積させ、異方性エッティングによってその誘電体層をエッチすることによって形成することができる。側壁スペーサー 48 はシリコン窒化物を含むことが好ましい。しかし代替えとして、酸化物や使い捨ての多結晶シリコンを使用してもよい。側壁スペーサー 48 を形成した後、ソース / ドレイン領域 52 が打ち込まれアニールされる。ドープされたエミッター電極は既に酸化物層 36 の形成時に “アニール” されているので、ソース / ドレイン領域 52 は低温（850 オーダーの）でアニールされ、短チャネル効果の低減化が図られる。TEOS 層 42 および二酸化シリコン層 35 は、次に図 10 に示すように除去される。

## 【0016】

次に、ゲート 40 と、ソース / ドレイン領域 52 および 52a とをシリサイド化することができる。構造 10 の表面を覆って高融点金属の層（図示されていない）が堆積される。この構造を、窒素を含む雰囲気中で、高速熱アニールを用いてアニールし、あるいは熱炉中でアニールする。これによって高融点金属層は露出シリコンと反応してシリサイドが形成される。図 11 を参照すると、ゲート 40 とソース / ドレイン領域 52 および 52a の上にシリサイド層 56 が形成されている。ほかの場所には、高融点金属の窒化物層および / あるいは未反応金属（図示されていない）の層が形成される。高融点金属窒化物のこの層は次に除去される。

## 【0017】

上述の方法の完了に続いて、図 1 の能動領域へコンタクトを形成するための相互接続金属配線が施される。そのような相互接続を形成するための方法は当業者には良く知られている。次に、個々の回路が基板 12 の部分から分離されて、それぞれに対してワイヤボンデ

10

20

30

40

50

イング、ダイレクトバンブボンディング等の当業者には良く知られた方法で外部接続が施される。個々の回路は次に、デュアルINLINEパッケージ、チップキャリア、あるいはその他の型のパッケージ中へ実装される。そのような実装の例については1985年1月22日付けの、テキサスインスツルメンツ社へ譲渡された米国特許第4,495,376号に述べられている。

【0018】

本発明は例示実施例について説明してきたが、本説明は限定的な意図のものではない。本発明のその他の実施例とともに、例示実施例に対して各種の修正や組み合わせが可能であることは、本説明を参照することによって当業者には明らかであろう。従って、そのような実施例や修正および組み合わせはすべて、本発明の特許請求の範囲に包含されるものと解釈されるべきである。

【0019】

以上の説明の関して更に以下の項を開示する。

(1) 半導体デバイスを作製するための方法であって、

- a . 第1のウエル領域を有する半導体母体の表面を覆って第1の絶縁層を形成すること、

- b . 前記第1のウエル領域の第1の部分へベース領域を打ち込みすること、

- c . 前記第1の絶縁層をエッチして、前記ベース領域の一部を露出させること、

- d . 前記半導体母体の表面を覆って第1のドープされた導電層を形成すること、

- e . 前記第1の導電層を覆ってタングステンシリサイド層を堆積させること、

- f . 前記タングステンシリサイド層および前記第1の導電層をエッチしてエミッター電極を形成し、前記第1の絶縁層の一部を露出させること、および

- g . 複数個のPMOSトランジスタを形成して、前記PMOSトランジスタのうちの少なくとも1個が、前記第1のウエル領域中に形成され前記ベース領域に接触する第1のソース/ドレイン領域を有するようにすること、

の工程を含む方法。

【0020】

(2) 第1項記載の方法であって、前記複数個のPMOSトランジスタを形成する前記工程が、

- a . 前記エミッター電極を覆っていない前記第1の絶縁層の部分を除去すること、

- b . 前記半導体母体の表面と前記タングステンシリサイド層との上に第2の絶縁層を成長させること、

- c . 前記第2の絶縁層の上に複数個のゲート電極を形成することであって、少なくとも1個のゲート電極が前記第1のウエル領域の上に形成されるようにすること、および

- d . 前記半導体母体の前記表面に複数個のソース/ドレイン領域を形成することであって、前記複数個のソース/ドレイン領域が前記第1のソース/ドレイン領域を含み、前記第1のソース/ドレイン領域が、前記少なくとも1個のゲート電極と前記エミッター電極との間に形成されるようにすること、

の工程を含んでいる方法。

【0021】

(3) 第2項記載の方法であって、前記ゲート電極を形成する前記工程が、

- a . 前記半導体母体の表面を覆って第2のドープされた導電層を形成すること、および

- b . 前記第2のドープされた導電層をエッチして前記複数個のゲート電極を形成し、そこにおいて前記エッチングが前記タングステンシリサイド層を覆う前記第2の絶縁層の上で止まるようにすること、

の工程を含んでいる方法。

【0022】

(4) 第2項記載の方法であって、前記第2の絶縁層を850よりも高い温度で成長させる方法。

【0023】

(5) 第2項記載の方法であって、更に、

10

20

30

40

50

- a . 前記ゲート電極を形成する前記工程の後に、各ゲート電極の反対側に、低濃度にドープしたドレインを打ち込みすること、および

- b . 前記ゲート電極の各々および前記エミッター電極に隣接して側壁スペーサーを形成すること、

- の工程を含む方法。

## 【0024】

(6) 第2項記載の方法であって、更に、前記ゲート電極と前記ソース／ドレイン領域とをシリサイド化する工程を含む方法。

## 【0025】

(7) 第6項記載の方法であって、前記ゲート電極と前記ソース／ドレイン領域とをシリサイド化する前記工程が、10

- a . 前記半導体母体の表面を覆って高融点金属の層を堆積させること、

- b . 窒素を含む雰囲気中で前記高融点金属の層をアニールして、前記ゲート電極と前記ソース／ドレイン領域とを覆ってシリサイド層を形成し、その他の場所には高融点金属の窒化物、未反応金属、あるいはそれらの組み合わせを含む未シリサイド化層を形成すること、および

- c . 前記未シリサイド化層をエッチすること、

- の工程を含んでいる方法。

## 【0026】

(8) 第1項記載の方法であって、前記ソース／ドレイン領域を形成する前記工程が、20

- a . 前記ソース／ドレイン領域を打ち込みすること、および

- b . 前記ソース／ドレイン領域を900 オーダーよりも低い温度でアニールすること、

- の工程を含んでいる方法。

## 【0027】

(9) 第1項記載の方法であって、前記第1の絶縁層が300 オーダーの厚さの酸化物を含み、前記第2の絶縁層が100 オーダーの厚さの酸化物を含んでいる方法。

## 【0028】

(10) BiCMOSデバイスを作製する方法であって、

- a . 第1のウエル領域を有する半導体母体の表面に、複数個のフィールド絶縁領域を形成すること、30

- b . 前記半導体母体の前記表面を覆って厚い酸化物層を形成すること、

- c . 前記フィールド絶縁領域の第1の領域に隣接して、前記第1のウエル領域の第1の部分中の前記厚い酸化物層を通してベース領域を打ち込みすること、

- d . 前記厚い酸化物層をエッチして、前記ベース領域を露出させること、

- e . 前記厚い酸化物層および前記ベース領域の前記露出された部分を覆って多結晶シリコンの第1の層を堆積させること、

- f . 前記第1の多結晶シリコン層を覆ってタンゲステンシリサイド層を堆積させること、

- g . 前記タンゲステンシリサイド層および前記第1の多結晶シリコン層をエッチして、前記ベース領域を覆うエミッター電極を形成し、前記厚い酸化物層の一部を露出させること、

- h . 前記厚い酸化物層の前記露出した部分を除去すること、

- i . 前記半導体母体の表面を覆ってゲート酸化物層を成長させること、

- j . 前記ゲート酸化物層を覆って多結晶シリコンの第2の層を堆積させること、

- k . 前記第2の多結晶シリコン層をエッチして複数個のゲート電極を形成することであって、前記ゲート電極のうちの少なくとも1個が前記第1のウエル領域の上に形成されるようすること、

- l . 前記ゲート電極と前記エミッター電極に隣接して側壁スペーサーを形成すること、

- m . 各ゲート電極の反対側の前記半導体母体表面にソース／ドレイン領域を打ち込みすること、および

- n . 前記ソース／ドレイン領域を900 オーダーよりも低い温度でアニールすること、50

の工程を含む方法。

【0029】

(11) 第10項記載の方法であって、更に、前記ゲート電極と前記ソース／ドレイン領域とをシリサイド化する工程を含む方法。

【0030】

(12) 第11項記載の方法であって、前記ゲート電極と前記ソース／ドレイン領域とをシリサイド化する前記工程が、

a. 前記半導体母体の表面を覆って高融点金属の層を堆積させること、

b. 窒素を含む雰囲気中で前記高融点金属の層をアニールして、前記ゲート電極と前記ソース／ドレイン領域とを覆ってシリサイド層を形成し、その他の場所には高融点金属の窒化物、未反応金属、あるいはそれらの組み合わせを含む未シリサイド化層を形成すること、および

c. 前記未シリサイド化層をエッチすること、

の工程を含んでいる方法。

【0031】

(13) BiCMOSデバイスであって、

a. ウエル領域、

b. 前記ウエル領域中に位置する、タングステンシリサイド層と多結晶シリコン層とを含むエミッター電極を有するバイポーラートランジスタ、および

c. 前記ウエル領域中に位置するPMOSトランジスタ、

を含むBiCMOSデバイス。

【0032】

(14) 第13項記載のBiCMOSデバイスであって、前記PMOSトランジスタが前記バイポーラートランジスタのベース領域に接触するソース／ドレイン領域を有しているBiCMOSデバイス。

【0033】

(15) 第13項記載のBiCMOSデバイスであって、前記バイポーラートランジスタが、ベース領域、エミッター電極、および前記エミッター電極と前記ベース領域との間に位置する厚い酸化物領域を含んでいるBiCMOSデバイス。

【0034】

(16) 第15項記載のBiCMOSデバイスであって、前記PMOSトランジスタがゲート酸化物を含み、前記ゲート酸化物が前記厚い酸化物領域よりも薄いものであるBiCMOSデバイス。

【0035】

(17) 第13項記載のBiCMOSデバイスであって、前記PMOSトランジスタがシリサイド化されたゲートを有しているBiCMOSデバイス。

【0036】

(18) 同一のウエル領域18中に形成されたバイポーラートランジスタ60とPMOSトランジスタ64とを有する融合BiCMOSデバイス10。バイポーラートランジスタ60は、エミッター電極30、ベース領域26、およびウエル領域18で形成されるコレクター領域を含む。エミッター電極30は厚い酸化物24によってベース領域26から分離される。タングステンシリサイド層32がエミッター電極30を覆う。PMOSトランジスタ64は、ソース／ドレイン領域52、52a、ゲート電極40、およびゲート酸化物36を含む。PMOSトランジスタ64はオプションとしてLDD領域44を含むことができる。ソース／ドレイン領域52aはベース領域26に接触している。もし必要であれば、エミッター電極30およびゲート電極40をシリサイド化することができる。

【関連出願へのクロスリファレンス】

次の同時譲渡の特許出願をここに参考のために引用する。

10

20

30

40

|                    |                   |                    |

|--------------------|-------------------|--------------------|

| 出願番号               | 出願日               | T I ケース番号          |

| <u>08/106, 458</u> | <u>1993年8月13日</u> | <u>T I - 17015</u> |

【図面の簡単な説明】

【図 1】本発明の好適実施例の断面図。

【図 2】本発明の好適実施例の製造工程を示す図であって、n+埋め込み層14の上に、

絶縁層24を形成した段階の断面図。 10

【図 3】本発明の好適実施例の製造工程を示す図であって、ベース領域26の打ち込みを

実施した段階の断面図。

【図 4】本発明の好適実施例の製造工程を示す図であって、ベース領域26の一部を露出

させた段階の断面図。

【図 5】本発明の好適実施例の製造工程を示す図であって、WSi<sub>2</sub>層の堆積とアニール

の段階の断面図。

【図 6】本発明の好適実施例の製造工程を示す図であって、エミッター電極30形成段階

の断面図。

【図 7】本発明の好適実施例の製造工程を示す図であって、第2の導電層39を形成した

段階の断面図。 20

【図 8】本発明の好適実施例の製造工程を示す図であって、ゲート40を形成した段階の

断面図。

【図 9】本発明の好適実施例の製造工程を示す図であって、側壁スペーサー48を形成し

、ソース／ドレイン領域52の打ち込み、アニールを行った段階の断面図。

【図 10】本発明の好適実施例の製造工程を示す図であって、TEOS層42および二酸化

シリコン層35を除去した段階の断面図。

【図 11】本発明の好適実施例の製造工程を示す図であって、未反応の高融点金属を除去

した段階の断面図。

【符号の説明】

|    |               |    |

|----|---------------|----|

| 10 | 融合 Bi CMOS 構造 | 30 |

| 12 | 基板            |    |

| 14 | 埋め込み n+ 領域    |    |

| 16 | p 領域          |    |

| 18 | n 領域          |    |

| 20 | 領域            |    |

| 22 | フィールド絶縁領域     |    |

| 24 | 絶縁層           |    |

| 25 | n+コレクターコンタクト  |    |

| 26 | 真正ベース領域       |    |

| 27 | マスク層          | 40 |

| 29 | 多結晶シリコン層      |    |

| 30 | エミッター電極       |    |

| 32 | タングステンシリサイド層  |    |

| 35 | 二酸化シリコン層      |    |

| 36 | ゲート酸化物        |    |

| 37 | 酸化物           |    |

| 40 | ゲート           |    |

| 42 | TEOS 層        |    |

| 44 | LDD           |    |

| 48 | 側壁スペーサー       | 50 |

5 2 , 5 2 a ソース / ドレイン ( p + ) 領域

5 6 TiSi<sub>2</sub> 層

6 0 バイポーラートランジスタ

6 4 p チャンネルトランジスタ

6 8 p チャンネルトランジスタ

【 四 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 四 8 】

【 図 9 】

【 図 1 0 】

【 図 1 1 】

---

フロントページの続き

(72)発明者 ロバート ハワード エクルンド

アメリカ合衆国テキサス州プラノ, ジョシュア トリー ドライブ 1121

審査官 安田 雅彦

(56)参考文献 特開平05-029554 (JP, A)

特開平05-006973 (JP, A)

特開平02-026062 (JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 27/06

H01L 21/8222

H01L 21/8249