(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6408245号

(P6408245)

(45) 発行日 平成30年10月17日(2018.10.17)

(24) 登録日 平成30年9月28日(2018.9.28)

|                          |        |        |         |

|--------------------------|--------|--------|---------|

| (51) Int.Cl.             | F 1    |        |         |

| HO 1 L 21/8244 (2006.01) | HO 1 L | 27/11  |         |

| HO 1 L 27/11 (2006.01)   | HO 1 L | 29/78  | 6 1 3 B |

| HO 1 L 29/786 (2006.01)  | HO 1 L | 29/78  | 6 1 8 B |

| HO 1 L 21/8239 (2006.01) | HO 1 L | 27/105 | 4 4 1   |

| HO 1 L 27/105 (2006.01)  | HO 1 L | 27/108 | 6 2 1 Z |

請求項の数 11 (全 47 頁) 最終頁に続く

|              |                               |           |                                                |

|--------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2014-98360 (P2014-98360)    | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成26年5月12日 (2014.5.12)        | (72) 発明者  | 加藤 清<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (65) 公開番号    | 特開2015-167218 (P2015-167218A) | (72) 発明者  | 大貫 達也<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成27年9月24日 (2015.9.24)        |           |                                                |

| 審査請求日        | 平成29年5月8日 (2017.5.8)          | 審査官       | 宮本 博司                                          |

| (31) 優先権主張番号 | 特願2013-104320 (P2013-104320)  |           |                                                |

| (32) 優先日     | 平成25年5月16日 (2013.5.16)        |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                |

| (31) 優先権主張番号 | 特願2013-227346 (P2013-227346)  |           |                                                |

| (32) 優先日     | 平成25年10月31日 (2013.10.31)      |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                |

| (31) 優先権主張番号 | 特願2014-25003 (P2014-25003)    |           |                                                |

| (32) 優先日     | 平成26年2月13日 (2014.2.13)        |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のメモリを有する半導体装置であって、

前記メモリは、第1のデータ保持部を有する揮発性メモリと、第2のデータ保持部を有する不揮発性メモリと、を有し、

前記第2のデータ保持部は、第1のトランジスタ及び第1の容量素子を有し、

前記第1のデータ保持部は、第2のトランジスタを有し、

前記第2のトランジスタ上に前記第1のトランジスタが積層して設けられ、

前記第1のトランジスタのソース及びドレインの一方は、前記第1のデータ保持部と電気的に接続され、

前記第1のトランジスタのソース及びドレインの他方は、前記第1の容量素子の一方の電極と電気的に接続され、

前記第1の容量素子の一方の電極は、前記第1のトランジスタのソースまたはドレインとして機能する電極と同じ層に設けられ、

前記第1の容量素子の他方の電極は、前記第1のトランジスタのゲートとして機能する電極と同じ層に設けられ、

前記複数のメモリがそれぞれ有する前記第1のトランジスタのゲートとして機能する電極は、配線と電気的に接続され、

前記配線は、前記第1の容量素子の他方の電極とは異なる層に設けられ、

前記第1のトランジスタが設けられた層と、前記第2のトランジスタが設けられた層と

の間に、前記第1のトランジスタ及び前記第2のトランジスタを電気的に接続する配線層が設けられ、

前記配線層は、前記第1のトランジスタのゲートとして機能する電極と重なる領域を有する、ことを特徴とする半導体装置。

**【請求項2】**

請求項1において、

前記第2のデータ保持部は、前記第1のトランジスタを非導通状態とし、前記第1のトランジスタのソース及びドレインの他方と、前記第1の容量素子の一方の電極との間に電荷を保持することで、前記第1のデータ保持部に記憶されたデータの保持を行うことを特徴とする半導体装置。

10

**【請求項3】**

請求項1または2において、

前記第1のトランジスタは、半導体層が酸化物半導体であることを特徴とする半導体装置。

**【請求項4】**

請求項1乃至3のいずれか一において、

前記第1のトランジスタは、トップゲート構造のトランジスタであることを特徴とする半導体装置。

**【請求項5】**

請求項1乃至4のいずれか一において、

前記第2のトランジスタは、半導体層がシリコンであることを特徴とする半導体装置。

20

**【請求項6】**

複数のメモリを有する半導体装置であって、

前記メモリは、第1のデータ保持部及び第2のデータ保持部を有する揮発性メモリと、第3のデータ保持部及び第4のデータ保持部を有する不揮発性メモリと、を有し、

前記第3のデータ保持部は、第1のトランジスタ及び第1の容量素子を有し、

前記第4のデータ保持部は、第2のトランジスタ及び第2の容量素子を有し、

前記第1のデータ保持部は、第3のトランジスタを有し、

前記第2のデータ保持部は、第4のトランジスタを有し、

前記第3のトランジスタ上に、前記第1のトランジスタが積層して設けられ、

30

前記第4のトランジスタ上に、前記第2のトランジスタが積層して設けられ、

前記第1のトランジスタのソース及びドレインの一方は、前記第1のデータ保持部と電気的に接続され、

前記第1のトランジスタのソース及びドレインの他方は、第1の容量素子の一方の電極と電気的に接続され、

前記第2のトランジスタのソース及びドレインの一方は、前記第2のデータ保持部と電気的に接続され、

前記第2のトランジスタのソース及びドレインの他方は、第2の容量素子の一方の電極と電気的に接続され、

前記第1の容量素子の一方の電極は、前記第1のトランジスタのソースまたはドレインとして機能する電極と同じ層に設けられ、

40

前記第1の容量素子の他方の電極、及び前記第2の容量素子の他方の電極は、前記第1のトランジスタのゲートとして機能する電極、及び前記第2のトランジスタのゲートとして機能する電極と同じ層に設けられ、

前記第1のトランジスタのゲートとして機能する電極、及び前記第2のトランジスタのゲートとして機能する電極は、配線と電気的に接続され、

前記配線は、前記第1の容量素子の他方の電極、及び前記第2の容量素子の他方の電極とは異なる層に設けられ、

前記第1のトランジスタが設けられた層と前記第3のトランジスタが設けられた層との間には、前記第1のトランジスタ及び前記第3のトランジスタを電気的に接続する第1の

50

配線層が設けられ、

前記第1の配線層は、前記第1のトランジスタのゲートとして機能する電極と重なる領域を有し、

前記第2のトランジスタが設けられた層と前記第4のトランジスタが設けられた層との間には、前記第2のトランジスタ及び前記第4のトランジスタを電気的に接続する第2の配線層が設けられ、

前記第2の配線層は、前記第2のトランジスタのゲートとして機能する電極と重なる領域を有する、ことを特徴とする半導体装置。

**【請求項7】**

請求項6において、

10

前記第1のトランジスタ及び前記第2のトランジスタの半導体層におけるチャネル形成領域は、高電源電位を与える配線に重畠して設けられていることを特徴とする半導体装置。

**【請求項8】**

請求項6または7において、

前記第3のデータ保持部は、前記第1のトランジスタを非導通状態とし、前記第1のトランジスタのソース及びドレインの他方と、前記第1の容量素子の一方の電極との間に電荷を保持することで、前記第1のデータ保持部に記憶されたデータの保持を行い、

前記第4のデータ保持部は、前記第2のトランジスタを非導通状態とし、前記第2のトランジスタのソース及びドレインの他方と、前記第2の容量素子の一方の電極との間に電荷を保持することで、前記第2のデータ保持部に記憶されたデータの保持を行うことを特徴とする半導体装置。

20

**【請求項9】**

請求項6乃至8のいずれか一において、

前記第1のトランジスタ及び前記第2のトランジスタは、半導体層が酸化物半導体であることを特徴とする半導体装置。

**【請求項10】**

請求項6乃至9のいずれか一において、

前記第1のトランジスタ及び前記第2のトランジスタは、トップゲート構造のトランジスタであることを特徴とする半導体装置。

30

**【請求項11】**

請求項6乃至10のいずれか一において、

前記第3のトランジスタ及び前記第4のトランジスタは、半導体層がシリコンであることを特徴とする半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明は、例えば、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法に関する。特に、本発明は、半導体装置に関する。

40

**【背景技術】**

**【0002】**

シリコン（Si）を半導体層に用いたトランジスタと、酸化物半導体（oxide semiconductor：Oxide Semiconductor：OS）を半導体層に用いたトランジスタと、を組み合わせてデータの保持を可能にした半導体装置が注目されている（特許文献1および特許文献2を参照）。

**【0003】**

近年、扱われるデータ量の増大に伴って、より大きな記憶容量を有する半導体装置が求められている。単位面積あたりの記憶容量を増加させるためには、半導体装置を構成するト

50

ランジスタや容量素子の微細化を図ることが有効である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2013-8437号公報

【特許文献2】特開2013-8436号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、半導体装置を構成する素子の微細化をすると、併せて容量素子の面積も減少するため、データを保持するための保持容量が小さくなる。この保持容量の低下により、容量素子に接続されるトランジスタの寄生容量が無視できなくなり、データの保持、および／または退避・復帰が難しくなる。

10

【0006】

そこで、本発明の一態様では、トランジスタのオフ電流が極めて小さいことを利用して容量素子での電荷の保持を行い、データを保持する半導体装置の構成において、素子の微細化を進めてデータの保持に必要な保持容量を確保できる、新規な構成の半導体装置を提供することを課題の一とする。または、本発明の一態様では、半導体装置の製造プロセスや回路を構成する配線や動作が複雑にすることなく、トランジスタのオン電流を大きくできる、新規な構成の半導体装置を提供することを課題の一とする。または、本発明の一態様では、新規な半導体装置などを提供することを課題の一とする。

20

【0007】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、上記以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、上記以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0008】

本発明の一態様は、複数のメモリを有する半導体装置であって、メモリは、第1のデータ保持部を有する揮発性メモリと、第2のデータ保持部を有する不揮発性メモリと、を有し、第2のデータ保持部は、第1のトランジスタ及び第1の容量素子を有し、第1のトランジスタのソースおよびドレインの一方は、第1のデータ保持部に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は、第1の容量素子の一方の電極に電気的に接続され、第1の容量素子の一方の電極は、第1のトランジスタのソースおよびドレインとなる電極と同じ層に設けられた電極であり、第1の容量素子の他方の電極は、第1のトランジスタのゲートとなる電極と同じ層に設けられた電極であり、複数のメモリ間に設けられる、第1のトランジスタのゲートを電気的に接続するための配線は、第1の容量素子の他方の電極とは異なる層に設けられた配線である半導体装置である。

30

【0009】

本発明の一態様において、第2のデータ保持部は、第1のトランジスタを非導通状態とし、第1のトランジスタのソースおよびドレインの他方と、第1の容量素子の一方の電極との間に電荷を保持することで、第1のデータ保持部に記憶されたデータの保持を行うデータ保持部である半導体装置が好ましい。

40

【0010】

本発明の一態様において、第1のトランジスタは、半導体層が酸化物半導体である半導体装置が好ましい。

【0011】

本発明の一態様において、第1のトランジスタは、トップゲート構造のトランジスタである半導体装置が好ましい。

【0012】

50

本発明の一態様において、第1のデータ保持部は、半導体層がシリコンである第2のトランジスタを用いて構成された回路である半導体装置が好ましい。

【0013】

本発明の一態様において、第2のトランジスタ上には、第1のトランジスタが積層して設けられる半導体装置が好ましい。

【0014】

本発明の一態様において、第1のトランジスタが設けられた層と、第2のトランジスタが設けられた層との間には、第1のトランジスタおよび第2のトランジスタを電気的に接続するための配線層が設けられる半導体装置が好ましい。

【0015】

本発明の一態様は、複数のメモリを有する半導体装置であって、メモリは、第1のデータ保持部および第2のデータ保持部を有する揮発性メモリと、第3のデータ保持部および第4のデータ保持部を有する不揮発性メモリと、を有し、第3のデータ保持部は、第1のトランジスタ及び第1の容量素子を有し、第4のデータ保持部は、第2のトランジスタ及び第2の容量素子を有し、第1のトランジスタのソースおよびドレインの一方は、第1のデータ保持部に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は、第1の容量素子の一方の電極に電気的に接続され、第2のトランジスタのソースおよびドレインの一方は、第2のデータ保持部に電気的に接続され、第2のトランジスタのソースおよびドレインの他方は、第2の容量素子の一方の電極に電気的に接続され、第1の容量素子の一方の電極は、第1のトランジスタのソースおよびドレインとなる電極と同じ層に設けられた電極であり、第1の容量素子の他方の電極、及び第2の容量素子の他方の電極は、第1のトランジスタのゲートとなる電極、及び第2のトランジスタのゲートとなる電極と同じ層に設けられた電極であり、第1のトランジスタのゲートと第2のトランジスタのゲートとを電気的に接続するための配線は、第1の容量素子の他方の電極、及び第2の容量素子の他方の電極とは異なる層に設けられた配線である半導体装置である。

10

【0016】

本発明の一態様は複数のメモリを有する半導体装置であって、メモリは、第1のデータ保持部および第2のデータ保持部を有する揮発性メモリと、第3のデータ保持部および第4のデータ保持部を有する不揮発性メモリと、を有し、第3のデータ保持部は、第1のトランジスタ及び第1の容量素子を有し、第4のデータ保持部は、第2のトランジスタ及び第2の容量素子を有し、第1のトランジスタのソースおよびドレインの一方は、第1のデータ保持部に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は、第1の容量素子の一方の電極に電気的に接続され、第2のトランジスタのソースおよびドレインの一方は、第2のデータ保持部に電気的に接続され、第2のトランジスタのソースおよびドレインの他方は、第2の容量素子の一方の電極に電気的に接続され、第1の容量素子の一方の電極は、第1のトランジスタのソースおよびドレインとなる電極と同じ層に設けられた電極であり、第1の容量素子の他方の電極、及び第2の容量素子の他方の電極は、第1のトランジスタのゲートとなる電極、及び第2のトランジスタのゲートとなる電極と同じ層に設けられた電極であり、第1のトランジスタのゲートと第2のトランジスタのゲートとを電気的に接続するための配線は、第1の容量素子の他方の電極、及び第2の容量素子の他方の電極とは異なる層に設けられた配線であり、第1のトランジスタ及び第2のトランジスタの半導体層におけるチャネル形成領域は、高電源電位を与える配線に重畳して設けられること、を特徴とする半導体装置である。

20

【0017】

本発明の一態様において、第3のデータ保持部は、第1のトランジスタを非導通状態とし、第1のトランジスタのソースおよびドレインの他方と、第1の容量素子の一方の電極との間に電荷を保持することで、第1のデータ保持部に記憶されたデータの保持を行うデータ保持部であり、第4のデータ保持部は、第2のトランジスタを非導通状態とし、第2のトランジスタのソースおよびドレインの他方と、第2の容量素子の一方の電極との間に電荷を保持することで、第2のデータ保持部に記憶されたデータの保持を行うデータ保持部

30

40

50

である半導体装置が好ましい。

【0018】

本発明の一態様において、第1のトランジスタおよび第2のトランジスタは、半導体層が酸化物半導体である半導体装置が好ましい。

【0019】

本発明の一態様において、第1のトランジスタおよび第2のトランジスタは、トップゲート構造のトランジスタである半導体装置が好ましい。

【0020】

本発明の一態様において、第1のデータ保持部および第2のデータ保持部は、半導体層がシリコンである第3のトランジスタを用いて構成された回路である半導体装置が好ましい。

10

【0021】

本発明の一態様において、第3のトランジスタ上には、第1のトランジスタおよび第2のトランジスタが積層して設けられる半導体装置が好ましい。

【0022】

本発明の一態様において、第1のトランジスタおよび第2のトランジスタが設けられた層と、第3のトランジスタが設けられた層との間には、第1のトランジスタ、第2のトランジスタおよび第3のトランジスタを電気的に接続するための配線層が設けられることを特徴とする半導体装置が好ましい。

20

【発明の効果】

【0023】

本発明の一態様により、トランジスタのオフ電流が極めて小さいことを利用して容量素子での電荷の保持を行い、データを保持する半導体装置の構成において、素子の微細化を進めてもデータの保持に必要な保持容量を確保できる、新規な構成の半導体装置を提供することができる。または本発明の一態様により、半導体装置の製造プロセスや回路を構成する配線や動作が複雑にすることなく、トランジスタのオン電流を大きくできる、新規な構成の半導体装置を提供することができる。または、本発明の一態様により、新規な半導体装置などを提供することができる。

【0024】

なお、本発明の一態様はこれらの効果に限定されるものではない。例えば、本発明の一態様は、場合によっては、または、状況に応じて、これらの効果以外の効果を有する場合もある。または、例えば、本発明の一態様は、場合によっては、または、状況に応じて、これらの効果を有さない場合もある。

30

【図面の簡単な説明】

【0025】

【図1】メモリセルの回路図および断面の模式図。

【図2】メモリセルの回路図およびタイミングチャート図。

【図3】メモリセルの回路図。

【図4】メモリセルの回路図。

【図5】メモリセルの断面の模式図。

40

【図6】メモリセルの回路図。

【図7】メモリセルの上面図および断面の模式図。

【図8】メモリセルの上面図。

【図9】メモリセルの断面図。

【図10】メモリセルの上面図および断面の模式図。

【図11】メモリセルの上面図。

【図12】メモリセルの断面図。

【図13】半導体装置の作製工程を示すフローチャート図及び斜視模式図。

【図14】半導体装置を用いた電子機器。

【図15】メモリセルの上面図および断面の模式図。

50

- 【図16】メモリセルの上面図。

- 【図17】メモリセルの断面図。

- 【図18】メモリセルの断面図。

- 【図19】メモリセルの回路図およびタイミングチャート図。

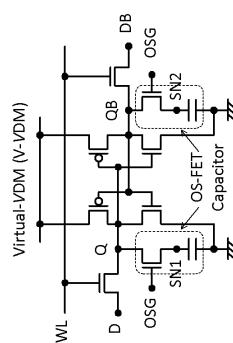

- 【図20】OS-SRAMの回路図。

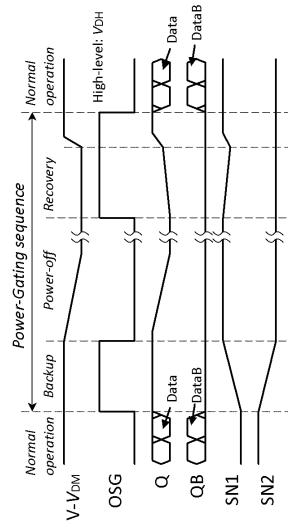

- 【図21】OS-SRAMのPower-Gating sequence。

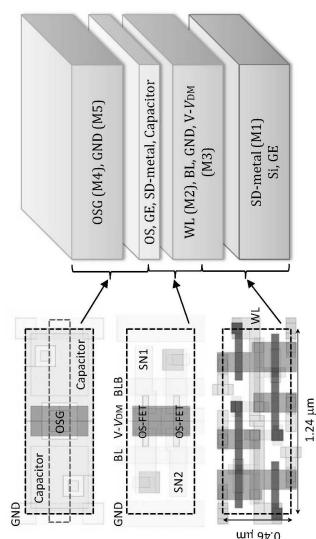

- 【図22】OS-SRAMマスクレイアウトと層構造を示す図。

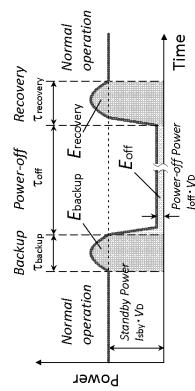

- 【図23】OS-SRAMの消費電力時間変化概略図。

- 【図24】Break-even time見積もりを示す図。

- 【図25】OS-SRAM/standard-SRAMのstatic noise margin比較のための図。 10

- 【図26】試作した32-bit microprocessorのチップ写真。

- 【図27】32-bit microprocessorブロック図。

- 【図28】Cache memory Power-Gating時のオシロスコープ波形。

- 【図29】Power-Gating overhead電力の測定概念図。

- 【図30】Power-Gating overhead電力の測定結果を示す図。

- 【発明を実施するための形態】

- 【0026】

- 以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。 20

- 【0027】

- また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。 30

- 【0028】

- また本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン（ドレイン端子、ドレイン領域又はドレイン電極）とソース（ソース端子、ソース領域又はソース電極）の間にチャネル領域を有しており、ドレインとチャネル領域とソースとを介して電流を流すことができるものである。

- 【0029】

- ここで、ソースとドレインとは、トランジスタの構造又は動作条件等によって変わるため、いざれがソース又はドレインであるかを限定することが困難である。そこで、ソースとして機能する部分、及びドレインとして機能する部分を、ソース又はドレインと呼ばず、ソースとドレインとの一方を第1電極と表記し、ソースとドレインとの他方を第2電極と表記する場合がある。 40

- 【0030】

- なお本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

- 【0031】

- なお本明細書において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間で、何らかの電気的作用を有する対象物が存在するとき、AとBとの電気信号の授受を可能とするものをいう。 50

## 【0032】

なお本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

## 【0033】

なお図面における各回路ブロックの配置は、説明のため位置関係を特定するものであり、異なる回路ブロックで別々の機能を実現するよう図面で示していても、実際の回路ブロックでは、同じ回路ブロック内で別々の機能を実現しうるように設けられている場合もある。また図面における各回路ブロックの機能は、説明のため機能を特定するものであり、一つの回路ブロックとして示していても、実際の回路ブロックでは、一つの回路ブロックで行う処理を複数の回路ブロックで行うよう設けられている場合もある。

10

## 【0034】

なお電圧とは、ある電位と、基準電位（例えばグラウンド電位）との電位差のことを示す場合が多い。よって、電圧、電位、電位差を、各々、電位、電圧、電圧差と言い換えることが可能である。なお電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。

## 【0035】

なお、一般に、電位や電圧は、相対的なものである。したがって、グラウンド電位は、必ずしも、0ボルトであるとは限られない。

20

## 【0036】

また本明細書等において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

## 【0037】

また本明細書等において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

## 【0038】

30

## (実施の形態1)

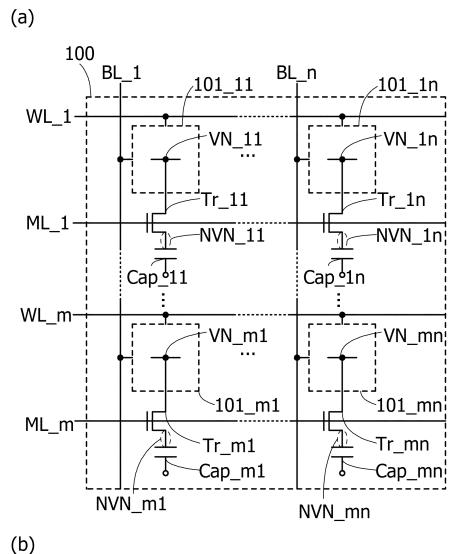

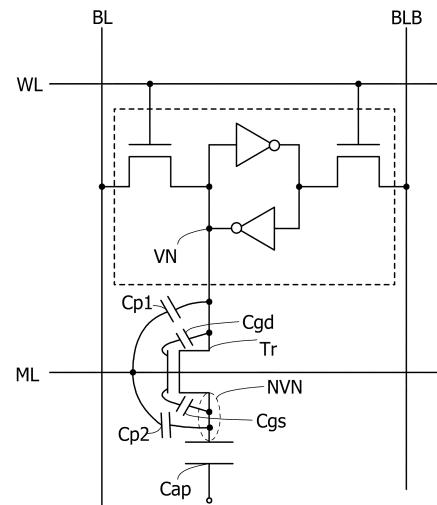

本実施の形態では、開示する発明の一態様に係る半導体装置が有する、メモリセルの回路構成及びその断面の模式図について、図1を参照して説明する。

## 【0039】

なお、半導体装置とは、半導体素子を有する装置のことをいう。なお、半導体装置は、半導体素子を含む回路を駆動させる駆動回路等を含む。なお、半導体装置は、メモリセルの他、別の基板上に配置された駆動回路、電源回路等を含む場合がある。

## 【0040】

図1(a)は、メモリセル100の一例を示す回路図である。

## 【0041】

40

図1(a)に示すメモリセル100では、記憶回路101\_11乃至101\_mn (m、nは自然数)、トランジスタTr\_11乃至Tr\_mn および容量素子Cap\_11乃至Cap\_mnを有する。なお記憶回路101\_mn、トランジスタTr\_mn および容量素子Cap\_mnは、m行n列にあるメモリを構成する回路および素子である。なお記憶回路101\_11乃至101\_mn、トランジスタTr\_11乃至Tr\_mn および容量素子Cap\_11乃至Cap\_mnで構成されるメモリは、マトリクス状に複数設けられている。

## 【0042】

また図1(a)では、ワード線WL\_1乃至WL\_m、ビット線BL\_1乃至BL\_nおよびデータ制御線ML\_1乃至ML\_mを示している。

50

## 【0043】

また図1(a)では、記憶回路101\_11乃至101\_mn内に、データに応じた電位を保持するノードに相当する、揮発性メモリ部VN\_11乃至VN\_mnを示している。また、図1(a)では、トランジスタTr\_11乃至Tr\_mnと容量素子Cap\_11乃至Cap\_mnとの間のノードで、データに応じた電位を保持する、不揮発性メモリ部N VN\_11乃至N VN\_mnを示している。

## 【0044】

なお本明細書において、ノードとは、素子間を電気的に接続するために設けられる配線上のいずれかの箇所のことである。

## 【0045】

本実施の形態で説明する半導体装置では、容量素子Cap\_11乃至Cap\_mnを構成する2つの電極を、トランジスタTr\_11乃至Tr\_mnのゲートとなる電極と同層に設けられた電極、ソースおよびドレインとなる電極と同層に設けられた電極、で構成する。そして、トランジスタTr\_11乃至Tr\_mnのゲートとなる電極を設ける層(ゲート電極層)と、複数のメモリ間のトランジスタTr\_11乃至Tr\_mnのゲートを接続する配線層(メモリセル配線層)と、を別の層に設ける構成とする。

10

## 【0046】

本実施の形態で説明する構成は、ゲート電極層とメモリセル配線層とを別の層に設けることで、トランジスタTr\_11乃至Tr\_mnのゲートに形成される寄生容量を抑制する構成とすることができます。またゲート電極層を、メモリセル配線層とを別の層に設けることで、ゲート電極層と同層に一方の電極が設けられる容量素子Cap\_11乃至Cap\_mnを形成する面積を増加させることができます。

20

## 【0047】

次いで、メモリセル100が有する各回路について説明する。

## 【0048】

記憶回路101\_11乃至101\_mnは、ビット線BL\_1乃至BL\_nに与えられるデータに応じた電位が、ワード線WL\_1乃至WL\_mに与えられるワード信号に従って書き込まれる回路である。一例として記憶回路101\_11乃至101\_mnは、トランジスタTr\_11乃至Tr\_mnが非導通状態のとき、SRAM(Static Random Access Memory)として機能する回路である。具体的に、記憶回路101\_11乃至101\_mnは、2つのトランジスタと2つのインバータ回路で、構成することができる。

30

## 【0049】

揮発性メモリ部VN\_11乃至VN\_mnは、記憶回路101\_11乃至101\_mnに電源供給がされている場合にデータに応じた電位を保持するノードのことをいう。記憶回路101\_11乃至101\_mnがSRAMの場合、2つのインバータ回路の出力信号が出力される、少なくとも一方のノードが揮発性メモリ部VN\_11乃至VN\_mnに相当する。

## 【0050】

なお本明細書において、データを書き込むとは、信号を制御することで配線の電位が、別の配線の電位に従って変化することをいう。たとえば、ワード線WL\_1に与えられるワード信号を制御することで、揮発性メモリ部VN\_11乃至VN\_1nの電位が、ビット線BL\_1乃至BL\_nの電位となることを、記憶回路101\_11乃至101\_1nにデータを書き込む、という。

40

## 【0051】

トランジスタTr\_11乃至Tr\_mnは、不揮発性メモリ部N VN\_11乃至N VN\_mnへのデータの書き込みを制御するスイッチとしての機能を有する。そのためトランジスタTr\_11乃至Tr\_mnは、ゲートに与えられる信号により、導通状態と非導通状態とを切り換えることができる。またトランジスタTr\_11乃至Tr\_mnは、非導通状態を保持することで、書き込んだデータを保持する機能を有する。なおトランジスタT

50

$r_{11}$  乃至  $r_{mn}$  は、第 1 のトランジスタともいう。また、トランジスタ  $r_{11}$  乃至  $r_{mn}$  は、n チャネル型のトランジスタとして、説明を行うものとする。

【0052】

なおトランジスタ  $r_{11}$  乃至  $r_{mn}$  は、非導通状態においてソースとドレインとの間を流れる電流（オフ電流）が低いトランジスタが用いられることが好適である。ここでは、オフ電流が低いとは、室温において、ソースとドレインとの間の電圧を 10 V とし、チャネル幅 1  $\mu$ mあたりの規格化されたオフ電流が 10 zA 以下であることをいう。このようにオフ電流が少ないトランジスタとしては、半導体層に酸化物半導体を有するトランジスタが挙げられる。

【0053】

容量素子  $Cap_{11}$  乃至  $Cap_{mn}$  は、トランジスタ  $r_{11}$  乃至  $r_{mn}$  を導通状態とすることで揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  のデータが書き込まれる容量素子である。また、容量素子  $Cap_{11}$  乃至  $Cap_{mn}$  は、トランジスタ  $r_{11}$  乃至  $r_{mn}$  を非導通状態とすることで、外部からの電源供給がなくても電荷を保持する容量素子である。また、トランジスタ  $r_{11}$  乃至  $r_{mn}$  を導通状態とすることで、容量素子  $Cap_{11}$  乃至  $Cap_{mn}$  で保持されたデータを揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  に書き込む。

10

【0054】

データ制御線  $ML_{11}$  乃至  $ML_{mn}$  は、トランジスタ  $r_{11}$  乃至  $r_{mn}$  の導通状態と非導通状態とを切り替えるための信号が与えられる配線である。データ制御線  $ML_{11}$  乃至  $ML_{mn}$  のいずれか一（例えばデータ制御線  $ML_{11}$ ）に対し、H レベルの信号を与えると、選択したデータ制御線に接続されたトランジスタ  $r_{11}$  乃至  $r_{1n}$  は導通状態となり、L レベルの信号を与えると、選択したデータ制御線に接続されたトランジスタ  $r_{11}$  乃至  $r_{1n}$  は非導通状態となる。

20

【0055】

不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  は、トランジスタ  $r_{11}$  乃至  $r_{mn}$  と容量素子  $Cap_{11}$  乃至  $Cap_{mn}$  の間のノードのことをいう。トランジスタ  $r_{11}$  乃至  $r_{mn}$  が非導通状態の場合、不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  では、容量素子  $Cap_{11}$  乃至  $Cap_{mn}$  に保持された電荷がトランジスタ  $r_{11}$  乃至  $r_{mn}$  を介してほとんどリークしないことをを利用して、電源供給が停止しても揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  のデータを記憶し続けることができる。

30

【0056】

図 1 (a) に示す不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  の構成では、トランジスタ  $r_{11}$  乃至  $r_{mn}$  の非導通状態を保持することで、書き込んだデータを保持している。そのため、不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  での電荷の移動を伴った電位の変動を抑えるスイッチとして、上述したように、オフ電流が少ないトランジスタが用いられることが特に好ましい。

【0057】

トランジスタ  $r_{11}$  乃至  $r_{mn}$  は、オフ電流が少ないトランジスタとして非導通状態を保持することで、不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  を不揮発性のメモリとすることができます。よって、一旦、不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  に書き込まれたデータは、再度、トランジスタ  $r_{11}$  乃至  $r_{mn}$  を導通状態とするまで、不揮発性メモリ部  $VN_{11}$  乃至  $VN_{mn}$  に保持し続けることができる。

40

【0058】

次いで、図 1 (a) に示すメモリセル 100 におけるトランジスタ  $r_{11}$  乃至  $r_{mn}$ 、容量素子  $Cap_{11}$  乃至  $Cap_{mn}$  の断面の模式図を図 1 (b) で説明し、本実施の形態の構成とすることによる作用及び効果について説明する。なお図 1 (b) では、トランジスタ  $r_{11}$  乃至  $r_{mn}$  のいずれか一としてトランジスタ  $r$ 、容量素

50

子 C a p \_ 1 1 乃至 C a p \_ m n のいずれか一として容量素子 C a p を示している。

【 0 0 5 9 】

図 1 ( b ) に示す断面の模式図は、トランジスタ T r および容量素子 C a p の断面の構造を示すものである。なお図 1 ( b ) に示すトランジスタ T r および容量素子 C a p は、図 1 ( a ) で説明した記憶回路 1 0 1 \_ 1 1 乃至 1 0 1 \_ m n を構成するトランジスタおよび該トランジスタ同士を接続するための配線上に設けられる構成となる。

【 0 0 6 0 】

図 1 ( b ) では、トランジスタ T r および容量素子 C a p を説明するための構成として、絶縁層 1 1 1 、半導体層 1 1 2 、ソースおよびドレインの一方となる第 1 電極 1 1 3 、ソースおよびドレインの他方となる第 2 電極 1 1 4 、ゲート絶縁層 1 1 5 、ゲート電極 1 1 6 、ゲート電極 1 1 6 と同じ層に設けられる電極 1 1 7 、層間絶縁層 1 1 8 、および配線層 1 1 9 を示している。

【 0 0 6 1 】

図 1 ( b ) に示すように本実施の形態で説明する半導体装置では、容量素子 C a p を構成する電極をトランジスタ T r のゲート電極 1 1 6 と、ソースおよびドレインの他方となる第 2 電極 1 1 4 と、同層に設けられた電極で構成する。そしてゲート電極 1 1 6 を設ける層と、複数のメモリ間のトランジスタ T r のゲート電極 1 1 6 を接続する配線層 1 1 9 と、を別の層に設ける構成とする。

【 0 0 6 2 】

本実施の形態で説明する構成は、ゲート電極 1 1 6 と配線層 1 1 9 とを別の層に設けることで、トランジスタ T r のゲート電極 1 1 6 における寄生容量を抑制する構成とすることができます。またトランジスタ T r のゲート電極 1 1 6 を設ける層を配線層 1 1 9 と別の層に設けることができるため、ゲート電極 1 1 6 と同層に一方の電極が設けられる容量素子 C a p を形成する面積を増加させることができる。

【 0 0 6 3 】

次いで、図 1 ( b ) の断面の模式図で示した各構成について説明する。

【 0 0 6 4 】

絶縁層 1 1 1 は、一例としては、無機絶縁層を用いればよい。無機絶縁層としては、窒化シリコン膜、酸化窒化シリコン膜、又は窒化酸化シリコン膜等を、単層又は多層で形成することが好ましい。なお絶縁層 1 1 1 より下層には、図 1 ( b ) では省略したが、トランジスタ、ならびに導電層で構成される配線層が設けられる。また絶縁層 1 1 1 は、絶縁層 1 1 1 より下層に設けられた素子と、絶縁層 1 1 1 より上層に設けられた素子とを電気的に接続するための、導電層を有する構成であってもよい。

【 0 0 6 5 】

半導体層 1 1 2 は、トランジスタ T r を非導通状態においてソースとドレインとの間を流れる電流 ( オフ電流 ) が低いトランジスタとするために、酸化物半導体を用いることが好適である。

【 0 0 6 6 】

ソースおよびドレインの一方となる第 1 電極 1 1 3 、並びにソースおよびドレインの他方となる第 2 電極 1 1 4 は、一例としては、アルミニウム、銅、チタン、タンタル、タンゲステン等の金属材料を単層または積層させて用いることができる。

【 0 0 6 7 】

ゲート絶縁層 1 1 5 は、絶縁層 1 1 1 と同様に、無機絶縁層を用いればよい。

【 0 0 6 8 】

ゲート電極 1 1 6 およびゲート電極 1 1 6 と同じ層に設けられる電極 1 1 7 は、第 1 電極 1 1 3 および第 2 電極 1 1 4 と同様に、アルミニウム、銅、チタン、タンタル、タンゲステン等の金属材料を単層または積層させて用いることができる。

【 0 0 6 9 】

層間絶縁層 1 1 8 は、無機絶縁層または有機絶縁層を、単層又は多層で形成することが好ましい。有機絶縁層としては、ポリイミド又はアクリル等を、単層又は多層で形成するこ

10

20

30

40

50

とが好ましい。

【0070】

配線層119は、ゲート電極116および電極117、ならびに第1電極113および第2電極114と同様に、アルミニウム、銅、チタン、タンタル、タングステン等の金属材料を単層または積層させて用いることができる。

【0071】

図1(b)の断面の模式図の構成では、第2電極114と電極117との間にゲート絶縁層115を挟んで形成した容量素子を容量素子Capとしている。ゲート絶縁層115は、層間絶縁層118と比べて、膜厚が小さい。そのため、同じ面積とした際に、より多くの静電容量を確保できる容量素子とすることができます。

10

【0072】

さらに図1(b)の断面の模式図の構成では、複数のメモリ間のトランジスタTrのゲート電極116を接続する配線層119を、ゲート電極116とは別の層に設ける構成とする。そのため、配線層119は、ほかの導電層と離間して設ける構成とすることができる。そのため、配線層119に形成される寄生容量を低減することができ、ゲート電極116と同じ層で複数のメモリ間のトランジスタTrのゲート電極116を接続する場合と比べて、トランジスタTrのゲートに形成される寄生容量を抑制する構成とすることができる。

【0073】

さらに図1(b)の断面の模式図の構成では、ゲート電極116とは別の層で複数のメモリ間のトランジスタTrのゲート電極116を接続する構成としている。この構成の場合、ゲート電極116と同じ層で複数のメモリ間のトランジスタTrのゲート電極116を接続する必要がないため、その分、容量素子Capが占める面積を確保することができる。

20

【0074】

図1(b)の断面の模式図の構成とは逆に、ゲート電極116と同じ層で複数のメモリ間のトランジスタTrのゲート電極116を接続する場合、ゲート電極116と電極117が短絡しないよう、同じ層で離間して設ける必要があり、その分、容量素子Capが占める面積が縮小してしまう。そのため、容量素子Capの静電容量が低下し、トランジスタTrの寄生容量が無視できなくなることにより、データの保持、および／または退避・復帰が難しくなってしまう。

30

【0075】

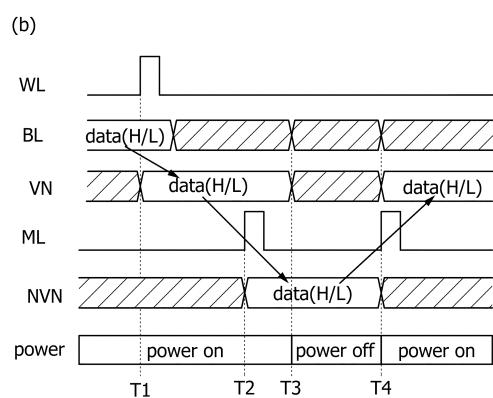

次いでメモリセル100の具体的な回路構成及びその動作について、図2乃至図5を参照して説明する。

【0076】

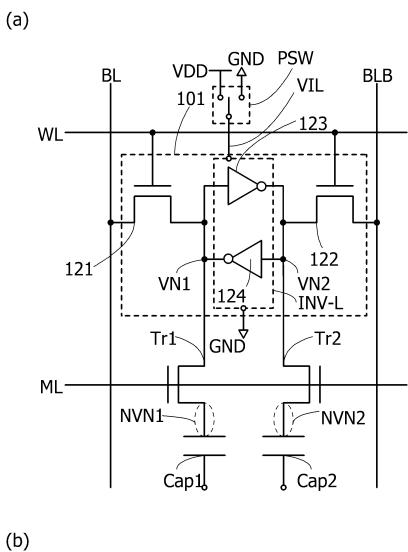

図2(a)は、図1(a)で示したメモリセル100が有する、単位メモリセルの具体的な回路構成を示す図である。

【0077】

図2(a)では、図1(a)と同様に、記憶回路101、トランジスタTrおよび容量素子Capを示している。

40

【0078】

また図2(a)では、ワード線WL、ビット線BL、反転ビット線BLBおよびデータ制御線MLを示している。

【0079】

また図2(a)では、記憶回路101内にSRAMを構成する、トランジスタ121、トランジスタ122、インバータ回路123、およびインバータ回路124を示している。また記憶回路101内には、インバータ回路124の出力信号が出力されるノードを揮発性メモリ部VNとして示している。

【0080】

なおトランジスタ121、およびトランジスタ122、並びにインバータ回路123、お

50

およびインバータ回路124を構成するトランジスタは、チャネルがシリコンで形成されているトランジスタとすることが好ましい。チャネルがシリコンで形成されているトランジスタは、半導体層に酸化物半導体を用いたトランジスタであるトランジスタTrや容量素子Capと積層して設ける際、特に好ましい。

【0081】

また、図2(a)では、図1(a)と同様に、トランジスタTrと容量素子Capとの間のノードで、データに応じた電位を保持する、不揮発性メモリ部N VNを示している。

【0082】

図2(a)に示す単位メモリセルの構成は、図1(a)および図1(b)と同様である。

【0083】

次いで、単位メモリセルの動作について説明する。

【0084】

図2(b)に示すタイミングチャート図では、図2(a)で示したワード線WL、ビット線BL、揮発性メモリ部VN、データ制御線ML、不揮発性メモリ部N VNの電位および電源供給の有無(図中、powerとして表記)を示している。なお図2(b)中、付された平行斜線は、実際には信号が与えられているが、ここでは動作の説明は不要であり、特に説明を省略するために付したものである。

【0085】

まず時刻T1でワード線WLに与えられるワード信号をHレベルにし、ビット線BLに与えられたHレベルまたはLレベルの電位に相当するデータ(図中、data(H/L)と表記)が、揮発性メモリ部VNに書き込まれる。なお反転ビット線BLBにおいても、ビット線BLとは逆の電位に相当するデータが与えられる。

【0086】

次いで時刻T2でデータ制御線MLに与えられる信号をHレベルにし、揮発性メモリ部VNに書き込まれたデータが、不揮発性メモリ部N VNに書き込まれる。なお、時刻T2で行われる、不揮発性メモリ部N VNへのデータの書き込みを、データの退避(またはback upともいう)ともいう。

【0087】

次いで時刻T3で電源供給を停止する。このとき、揮発性メモリ部VNに書き込まれたデータは、失われるものの、不揮発性メモリ部N VNに書き込まれたデータは、オフ電流が極めて小さいトランジスタTrを非導通状態とすることで、保持し続けることができる。

【0088】

次いで時刻T4で電源供給を再開する。そして不揮発性メモリ部N VNに保持されたデータを、揮発性メモリ部VNに再度書き込む処理を行う。この揮発性メモリ部VNへのデータの書き込みは、データ制御線MLに与えられる信号をHレベルにして行われる。なお、時刻T4で行われる、揮発性メモリ部VNへのデータの書き込みを、データの復帰(またはrecoveryともいう)ともいう。

【0089】

なお図2(b)で説明した、データの退避・復帰は、回路図上で模式的に表すと、図3のよう表すことができる。図2(b)、図3で説明した、データの退避・復帰の動作では、いずれも、データ制御線MLにHレベルを与えてトランジスタTrを導通状態としている。

【0090】

トランジスタTrでの、ゲートとソースの間の寄生容量、およびゲートとドレインの間の寄生容量が、容量素子Capの静電容量と比べて無視できない大きさになると、データ制御線MLの電位の変動に伴い、揮発性メモリ部VNおよび不揮発性メモリ部N VNの電位も変動する。揮発性メモリ部VNおよび不揮発性メモリ部N VNにおける電位の変化がデータの退避・復帰の動作時に生じると、正常な動作をすることが難しくなる。

【0091】

逆に言えば、トランジスタTrでの、ゲートとソースの間の寄生容量、およびゲートとド

10

20

30

40

50

レインの間の寄生容量が、容量素子 C a p の静電容量と比べて無視できるほど小さくなれば、データ制御線 M L の電位が変動しても、揮発性メモリ部 V N および不揮発性メモリ部 N V N の電位が変動しないようにすることができる。

【 0 0 9 2 】

本実施の形態の構成では、上述したように、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層を、ゲート電極とは別の層に設ける構成とする。そのため、配線層は、ほかの導電層と離間して設ける構成とすることができます、トランジスタ T r のゲートに形成される寄生容量を抑制する構成とすることができます。寄生容量を抑制することで、データの退避・復帰の動作時における、揮発性メモリ部 V N および不揮発性メモリ部 N V N における電位の変化を小さくし、正常な動作を行うことができる。

10

【 0 0 9 3 】

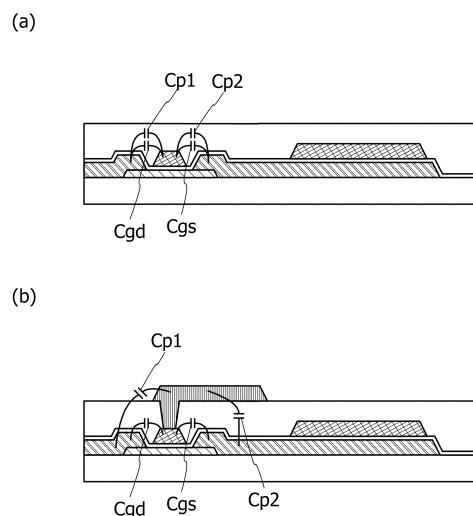

図 4 では、回路図において、トランジスタ T r のゲートとソースの間の寄生容量 C g s 、およびゲートとドレインの間の寄生容量 C g d 、並びに配線層とトランジスタ T r のソースの間の寄生容量 C p 1 、および配線層とトランジスタ T r のドレインの間の寄生容量 C p 2 、を模式的に表した図である。なお図 4 では、ソースおよびドレインの一方をソースとし、ソースおよびドレインの他方をドレインとして説明している。

【 0 0 9 4 】

データ制御線 M L が延設される方向に設けられる配線層を、他の導電層と離間して設けることで、図 4 に示す回路図における、寄生容量 C p 1 、および寄生容量 C p 2 を小さくすることができる。

20

【 0 0 9 5 】

たとえば、図 5 ( a ) に示す断面の模式図にあるように、配線層が、トランジスタのゲート電極と同じ層にある場合、ゲート絶縁層といった他の層より薄い絶縁層を介して他の層と寄生容量 C p 1 、および寄生容量 C p 2 を形成する構成となる。一方、図 5 ( b ) に示す断面の模式図にあるように、配線層が、トランジスタのゲート電極と別の層にある場合、層間絶縁層といった他の層より厚い絶縁層を介して他の層と寄生容量 C p 1 、および寄生容量 C p 2 を形成する構成となる。そのため、図 5 ( b ) の構成では、図 5 ( a ) の構成に比べ、寄生容量を小さくすることができる。

【 0 0 9 6 】

さらに、データ制御線 M L が延設される方向に設けられる配線層を、トランジスタ T r のゲート電極と同層にある容量素子の電極とは別の層に設ける構成とすることで、図 4 に示す回路図における、容量素子 C a p が占める面積を確保することができる。そのため、本実施の形態の構成では、トランジスタの寄生容量を低減する点、容量素子の静電容量の増加する点の、2つの点でデータの退避・復帰の動作時における、揮発性メモリ部 V N および不揮発性メモリ部 N V N における電位の変化を小さくし、正常な動作を行う構成とすることができます。

30

【 0 0 9 7 】

以上説明した、本実施の形態の構成では、トランジスタ T r のゲートに形成される寄生容量を抑制する構成に加えて、ゲート電極と同層で複数のメモリ間のトランジスタ T r のゲート電極を接続しないことで、容量素子が占める面積を確保することができる。そのため、トランジスタおよび容量素子の微細化を進めても、寄生容量の低減、および容量素子を形成するための面積の確保、を図ることができ、揮発性メモリ部 V N および不揮発性メモリ部 N V N の電位の変動を小さくできる。

40

【 0 0 9 8 】

以上、本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

【 0 0 9 9 】

( 実施の形態 2 )

本実施の形態では、開示する発明の一態様に係る半導体装置のメモリセルが有するトランジスタの断面の構造について、回路図、上面図等を参照して説明する。なお本実施の形態

50

では、複数のメモリ間のトランジスタTrのゲート電極を接続する配線層を、ゲート電極とは別の層に設ける構成とすることの利点を説明するため、上面図および断面図において、配線層とゲート電極を同じ層とした構成と、配線層とゲート電極を別の層とした構成と、についてあわせて説明する。

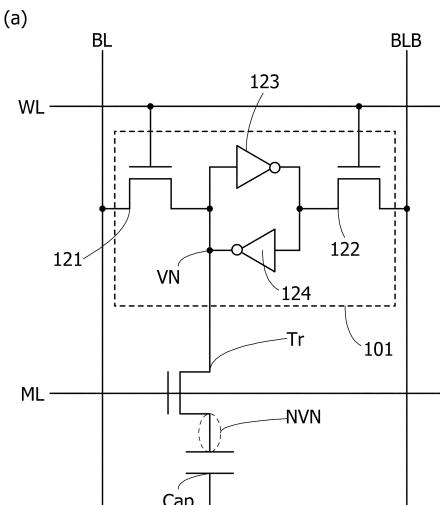

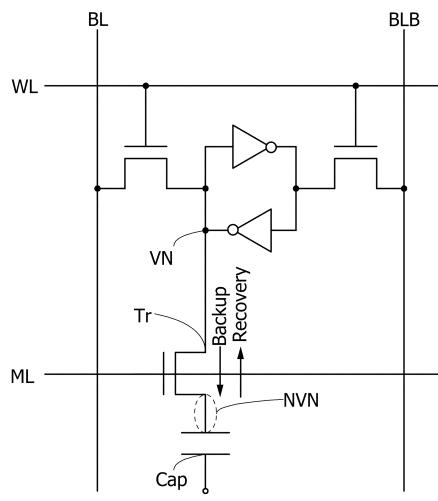

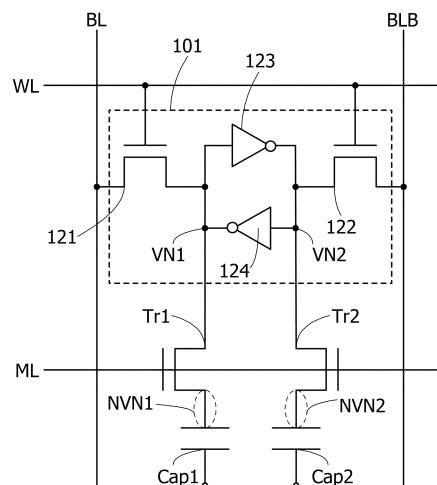

【0100】

まず本実施の形態で一例として説明する、メモリセルの回路構成について図6に示す。図6に示す回路構成は、配線層とゲート電極を同じ層とした構成と、配線層とゲート電極を別の層とした構成とで、共通である。

【0101】

図6では、記憶回路101、トランジスタTr1、トランジスタTr2、容量素子Cap1 10 および容量素子Cap2を示している。

【0102】

また図6では、ワード線WL、ピット線BL、反転ピット線BLB、およびデータ制御線MLを示している。

【0103】

また図6では、図2(a)と同様に、記憶回路101内にSRAMを構成する、トランジスタ121、トランジスタ122、インバータ回路123、およびインバータ回路124を示している。また記憶回路101内には、インバータ回路124の出力信号が出力されるノードを揮発性メモリ部VN1として示している。また記憶回路101内には、インバータ回路123の出力信号が出力されるノードを揮発性メモリ部VN2として示している 20 。

【0104】

また、図6では、トランジスタTr1と容量素子Cap1との間のノードで、データに応じた電位を保持する、不揮発性メモリ部N VN1を示している。また、図6では、トランジスタTr2と容量素子Cap2との間のノードで、データに応じた電位を保持する、不揮発性メモリ部N VN2を示している。

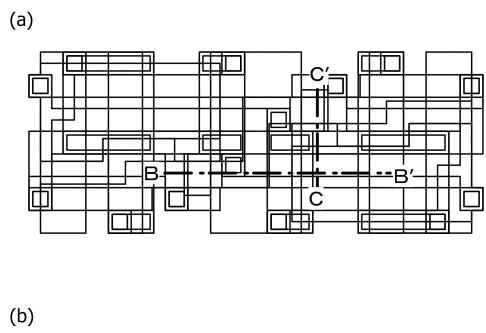

【0105】

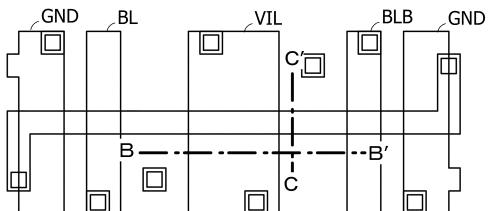

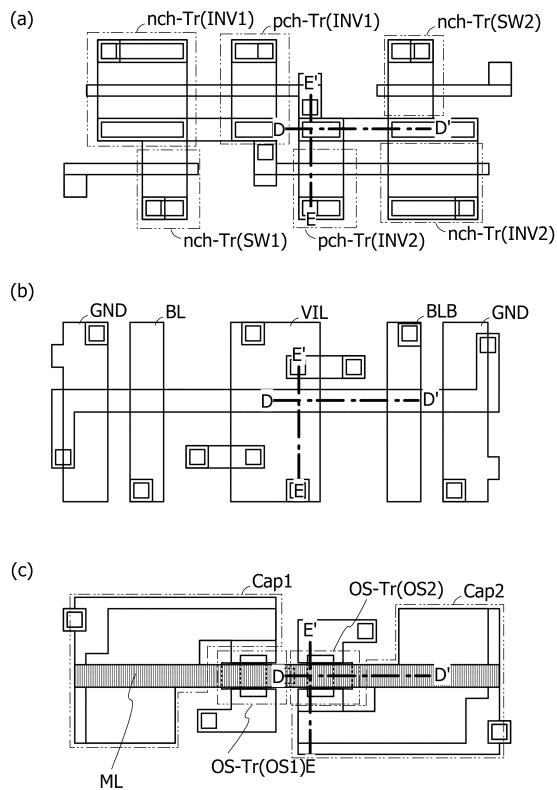

次いで、図7(a)および図8では、配線層とゲート電極を同じ層とした構成について、図6に示した回路構成に対応する上面図を示す。また図9では、図7(a)および図8に示す一点鎖線B-B'および一点鎖線C-C'における断面図を示す。 30

【0106】

まず、図7(a)に示す上面図は、図6に示した回路図における、トランジスタ121、トランジスタ122、インバータ回路123、インバータ回路124、トランジスタTr1、トランジスタTr2、容量素子Cap1および容量素子Cap2の配置を示すものである。

【0107】

図7(a)におけるトランジスタの配置の理解しやすくするために、図7(b)では図7(a)における各素子の層構造についての模式図を示している。図7(b)に示す第1の層301は、半導体層にシリコンを用いたトランジスタが設けられた層(図中、Si\_transistor\_layerと表記)である。図7(b)に示す第2の層302は、電源供給を行うための配線層が設けられた層(図中、wiring\_layerと表記)である。図7(b)に示す第3の層303は、半導体層に酸化物半導体を用いたトランジスタが設けられた層(図中、OS\_transistor\_layerと表記)である。 40

【0108】

図7(b)に示す第1の層301は、半導体層にシリコンを用いたトランジスタ、すなわちトランジスタ121(SW1)、およびトランジスタ122(SW2)、並びにインバータ回路123(INV1)、およびインバータ回路124(INV2)を有する。図7(b)に示す第2の層302は、グラウンド電位を与える配線GND、ピット線BL、高電源電位を与える配線VIL、反転ピット線BLBとなる配線層を有する。図7(b)に示す第3の層303は、半導体層に酸化物半導体を用いたトランジスタ、すなわちトラン 50

ジスタ Tr 1 (OS 1)、およびトランジスタ Tr 2 (OS 2)、並びに容量素子 Cap 1、および容量素子 Cap 2 を有する。

【0109】

図 8 (a) では、図 7 (b) に示す第 1 の層 301 の上面図を示している。図 8 (a) の上面図では、半導体層にシリコンを用いたトランジスタを構成する、半導体層、ゲート電極と同じ層に設けられる配線層、ソース電極およびドレイン電極と同じ層に設けられる配線層、および各層を接続するための開口部についての配置を示している。

【0110】

図 8 (a) に示す上面図では、トランジスタ 121 となる n チャネル型トランジスタ (n ch - Tr (SW1))、トランジスタ 122 となる n チャネル型トランジスタ (n ch - Tr (SW2))、インバータ回路 123 を構成する p チャネル型トランジスタ (p ch - Tr (INV1)) および n チャネル型トランジスタ (n ch - Tr (INV1))、およびインバータ回路 124 を構成する p チャネル型トランジスタ (p ch - Tr (INV2)) および n チャネル型トランジスタ (n ch - Tr (INV2)) の配置を示している。

【0111】

図 8 (b) では、図 7 (b) に示す第 2 の層 302 の上面図を示している。図 8 (b) の上面図では、複数の層に設けられた配線層、および各層を接続するための開口部についての配置を示している。

【0112】

図 8 (b) に示す上面図では、グラウンド電位を与える配線 GND、ピット線 BL、高電源電位を与える配線 VIL、反転ピット線 BLB の配置を示している。

【0113】

図 8 (c) では、図 7 (b) に示す第 3 の層 303 の上面図を示している。図 8 (c) の上面図では、半導体層に酸化物半導体を用いたトランジスタを構成する、半導体層、ゲート電極と同じ層に設けられる配線層、ソース電極およびドレイン電極と同じ層に設けられる配線層、および各層を接続するための開口部についての配置を示している。

【0114】

図 8 (c) に示す上面図では、トランジスタ Tr 1 となる n チャネル型トランジスタ (OS - Tr (OS1))、トランジスタ Tr 2 となる n チャネル型トランジスタ (OS - Tr (OS2))、容量素子 Cap 1、および容量素子 Cap 2、および各層を接続するための開口部の配置を示している。

【0115】

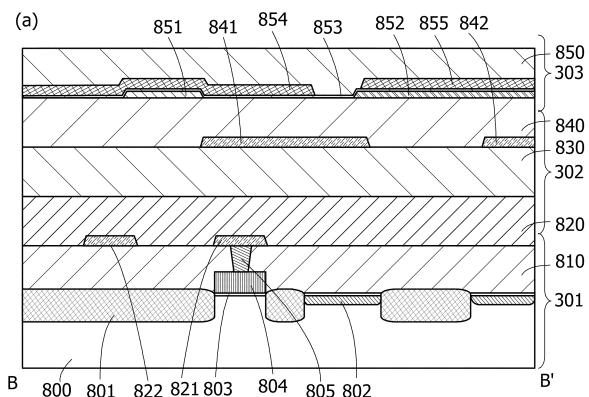

次いで図 9 (a) では、図 7 (a) および図 8 の一点鎖線 B - B' における断面図、図 9 (b) では、図 7 (a) および図 8 の一点鎖線 C - C' における断面図を、例示している。

【0116】

また、本実施の形態では、第 1 の層 301 のトランジスタが、単結晶のシリコン基板に形成され、第 2 の層 302 の配線層が、第 1 の層 301 上に形成され、第 3 の層 303 のトランジスタが、第 2 の層 302 上に形成されている場合を例示している。第 1 の層 301 のトランジスタは、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの薄膜の半導体を半導体層に用いていても良い。

【0117】

図 9 (a) では、半導体基板 800、素子分離用絶縁膜 801、不純物領域 802、ゲート絶縁層 803、ゲート電極 804、配線層 805、層間絶縁層 810、配線層 821、配線層 822、層間絶縁層 820、層間絶縁層 830、層間絶縁層 840、配線層 841、配線層 842、層間絶縁層 850、半導体層 851、導電層 852、ゲート絶縁層 853、導電層 854、および導電層 855 を示している。

【0118】

図 9 (b) では、半導体基板 800、素子分離用絶縁膜 801、ゲート絶縁層 803、ゲ

10

20

30

40

50

ート電極 804、配線層 823、層間絶縁層 810、層間絶縁層 820、層間絶縁層 830、配線層 831、層間絶縁層 840、層間絶縁層 850、半導体層 851、導電層 852、ゲート絶縁層 853、導電層 854、導電層 855 および導電層 856 を示している。

【0119】

半導体基板 800 は、例えば、n 型又は p 型の導電型を有するシリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板、化合物半導体基板 (GaAs 基板、InP 基板、GaN 基板、SiC 基板、GaP 基板、GaInAsP 基板、ZnSe 基板等) 等を用いることができる。

【0120】

第 1 の層 301 のトランジスタは、素子分離用絶縁膜 801 により、他のトランジスタと、電気的に分離されている。素子分離用絶縁膜 801 の形成には、選択酸化法 (LOCOS (Local Oxidation of Silicon) 法) 又はトレンチ分離法等を用いることができる。

【0121】

不純物領域 802 は、p 型を付与する不純物元素、または n 型を付与する不純物元素を、イオンドーピング法またはイオン注入法等を適宜用いて、半導体基板 800 内に添加して形成する。

【0122】

ゲート絶縁層 803 は、熱処理を行い、半導体基板 800 の表面を酸化して酸化シリコン膜を形成した後、選択的にエッチングして、形成する。若しくは、酸化シリコン、酸化窒化シリコン、高誘電率物質 (high-k 材料ともいう) である酸化ハフニウムなどの金属酸化物等を、CVD 法、スパッタリング法等を用いて形成した後、選択的にエッチングして、形成する。

【0123】

ゲート電極 804、配線層 805、配線層 821、配線層 822、配線層 823、配線層 831、配線層 841、配線層 842、導電層 852、導電層 854、導電層 855 および導電層 856 は、アルミニウム、銅、チタン、タンタル、タンゲステン等の金属材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。形成方法は、蒸着法、PE-CVD 法、スパッタリング法、スピノート法などの各種成膜方法を用いることができる。

【0124】

層間絶縁層 810、層間絶縁層 820、層間絶縁層 830、層間絶縁層 840 および層間絶縁層 850 は、無機絶縁層または有機絶縁層を、単層又は多層で形成することが好ましい。無機絶縁層としては、窒化シリコン膜、酸化窒化シリコン膜、又は窒化酸化シリコン膜等を、単層又は多層で形成することが好ましい。有機絶縁層としては、ポリイミド又はアクリル等を、単層又は多層で形成することが好ましい。また、層間絶縁層 810、層間絶縁層 820、層間絶縁層 830、層間絶縁層 840 および層間絶縁層 850 の作製方法に特に限定はないが、例えば、スパッタリング法、MBE 法、PE-CVD 法、パルスレーザ堆積法、ALD (Atomic Layer Deposition) 法等を適宜用いることができる。

【0125】

半導体層 851 は、酸化物半導体を単層または積層して設ければよい。酸化物半導体は、一例として、インジウム、ガリウム、及び亜鉛を含む酸化物であり、In-Ga-Zn 系酸化物 (IGZO とも表記する) を用いることができる。なお、In-Ga-Zn 系酸化物とは、In と Ga と Zn を含む酸化物という意味であり、In と Ga と Zn 以外の金属元素が入っていてもよい。例えば、In-Sn-Ga-Zn 系酸化物、In-Hf-Ga-Zn 系酸化物、In-Al-Ga-Zn 系酸化物を用いることができる。酸化物半導体の形成方法としては、スパッタリング法、ALD 法、蒸着法、塗布法などを用いることができる。

10

20

30

40

50

## 【0126】

ゲート絶縁層853は、無機絶縁層を、単層又は多層で形成することが好ましい。また、ゲート絶縁層853は、半導体層851に酸素を供給する効果があるとより好ましい。

## 【0127】

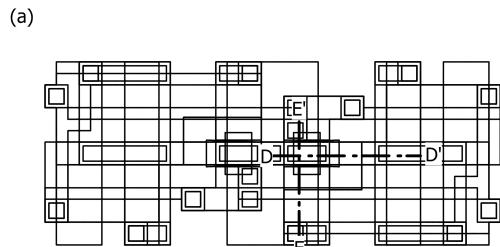

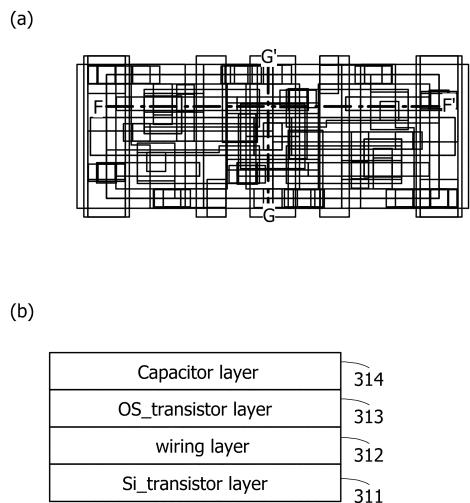

次いで、図10(a)および図11では、配線層とゲート電極を異なる層とした構成について、図6に示した回路構成に対応する上面図を示す。また図12では、図10(a)および図11に示す一点鎖線D-D'および一点鎖線E-E'における断面図を示す。

## 【0128】

まず、図10(a)に示す上面図は、図7(a)と同様にして、図6に示した回路図における、トランジスタ121、トランジスタ122、インバータ回路123、インバータ回路124、トランジスタTr1、トランジスタTr2、容量素子Cap1および容量素子Cap2の配置を示すものである。

10

## 【0129】

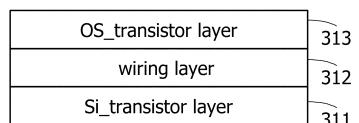

図10(a)におけるトランジスタの配置の理解しやすくするために、図10(b)では図10(a)における各素子の層構造についての模式図を示している。図10(b)に示す第1の層311は、半導体層にシリコンを用いたトランジスタが設けられた層(図中、Si\_transistor\_layerと表記)である。図10(b)に示す第2の層312は、電源供給を行うための配線層が設けられた層(図中、wiring\_layerと表記)である。図10(b)に示す第3の層313は、半導体層に酸化物半導体を用いたトランジスタが設けられた層(図中、OS\_transistor\_layerと表記)である。

20

## 【0130】

図10(b)に示す第1の層311、第2の層312および第3の層313は、図7(b)で説明した第1の層301、第2の層302および第3の層303での説明と同様であり、ここでの説明を省略する。

## 【0131】

図11(a)および図11(b)に示す上面図の説明もまた、図8(a)および図8(b)に併せて示している。図11(a)および図11(b)に示す第1の層311および第2の層312での説明は、図8(a)および図8(b)に示す第1の層301および第2の層302での説明と同様である。

30

## 【0132】

図11(c)では、図10(b)に示す第3の層313の上面図を示している。図11(c)の上面図では、半導体層に酸化物半導体を用いたトランジスタを構成する、半導体層、ゲート電極と同じ層に設けられる配線層、ソース電極およびドレイン電極と同じ層に設けられる配線層、メモリセル間のゲート電極を接続するための配線層、および各層を接続するための開口部についての配置を示している。

## 【0133】

図11(c)に示す上面図では、トランジスタTr1となるnチャネル型トランジスタ(OS-Tr(OS1))、トランジスタTr2となるnチャネル型トランジスタ(OS-Tr(OS2))、容量素子Cap1、および容量素子Cap2、メモリセル間のゲート電極を接続するための配線層(図11(c)中、平行斜線を付した領域ML)、および各層を接続するための開口部の配置を示している。

40

## 【0134】

なお、図11(a)乃至図11(c)に示す上面図のレイアウトが、図8(a)乃至図8(c)に示す上面図のレイアウトと異なる点は、第3の層における領域MLの関するレイアウトに関する点である。具体的には、図11(c)の最上層に、複数のメモリ間のトランジスタTrのゲート電極を接続する配線層(図11(c)中、領域ML)を設け、容量素子Cap1および容量素子Cap2を設けることのできる面積を確保する点で異なる。

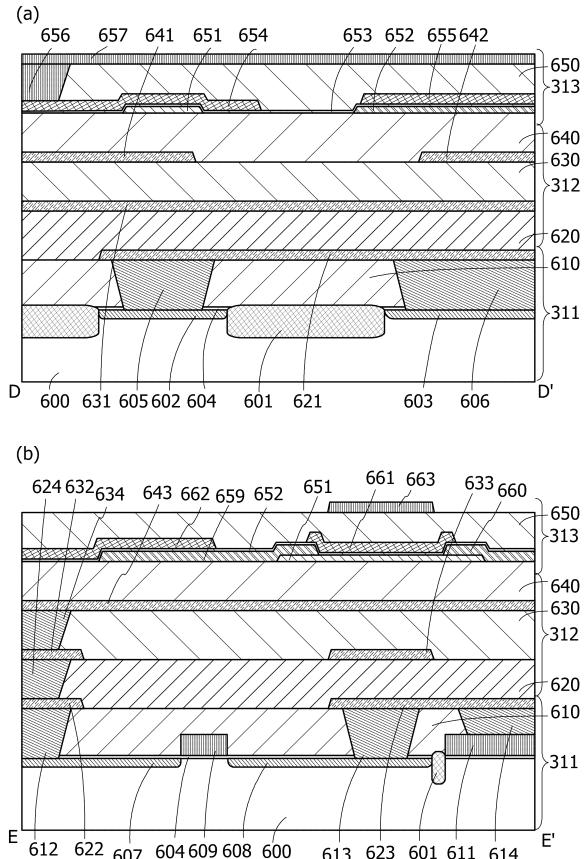

## 【0135】

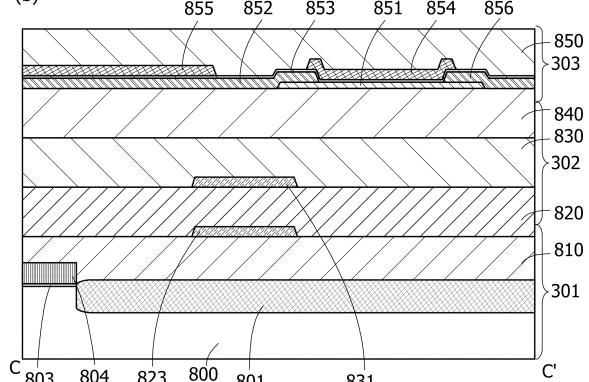

次いで図12(a)では、図10(a)および図11の一点鎖線D-D'における断面図

50

、図12(b)では、図10(a)および図11の一点鎖線E-E'における断面図を、例示している。

【0136】

また、本実施の形態では、第1の層311のトランジスタが、単結晶のシリコン基板に形成され、第2の層312の配線層が、第1の層311上に形成され、第3の層313のトランジスタが、第2の層312上に形成されている場合を例示している。第1の層311のトランジスタは、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの薄膜の半導体を半導体層に用いていても良い。

【0137】

図12(a)では、半導体基板600、素子分離用絶縁膜601、不純物領域602、不純物領域603、ゲート絶縁層604、配線層605、配線層606、層間絶縁層610、層間絶縁層620、配線層621、層間絶縁層630、配線層631、層間絶縁層640、配線層641、配線層642、層間絶縁層650、半導体層651、導電層652、ゲート絶縁層653、導電層654、導電層655、導電層656、導電層657を示している。

【0138】

図12(b)では、半導体基板600、素子分離用絶縁膜601、ゲート絶縁層604、不純物領域607、不純物領域608、ゲート電極609、層間絶縁層610、配線層611、配線層612、配線層613、配線層614、配線層622、配線層623、配線層624、層間絶縁層620、層間絶縁層630、配線層632、配線層633、配線層634、層間絶縁層640、配線層643、層間絶縁層650、半導体層651、導電層659、導電層660、ゲート絶縁層653、ゲート電極661、導電層662、および配線層663を示している。

【0139】

半導体基板600は、例えば、n型又はp型の導電型を有するシリコン基板、ゲルマニウム基板、シリコングルマニウム基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、GaP基板、GaInAsP基板、ZnSe基板等)等を用いることができる。

【0140】

第1の層311のトランジスタは、素子分離用絶縁膜601により、他のトランジスタと、電気的に分離されている。素子分離用絶縁膜601の形成には、選択酸化法(LOCOS(Local Oxidation of Silicon)法)又はトレンチ分離法等を用いることができる。

【0141】

不純物領域602、不純物領域603、不純物領域607および不純物領域608は、p型を付与する不純物元素、またはn型を付与する不純物元素を、イオンドーピング法またはイオン注入法等を適宜用いて、半導体基板600内に添加して形成する。

【0142】

ゲート絶縁層604は、熱処理を行い、半導体基板600の表面を酸化して酸化シリコン膜を形成した後、選択的にエッティングして、形成する。若しくは、酸化シリコン、酸化窒化シリコン、高誘電率物質(high-k材料ともいう)である酸化ハフニウムなどの金属酸化物等を、CVD法、スパッタリング法等を用いて形成した後、選択的にエッティングして、形成する。

【0143】

配線層605、配線層606、配線層621、配線層631、配線層641、配線層642、導電層652、導電層654、導電層655、導電層656、導電層657、ゲート電極609、配線層611、配線層612、配線層613、配線層614、配線層622、配線層623、配線層624、配線層632、配線層633、配線層634、配線層643、導電層660、ゲート電極661、導電層662、および配線層663は、アルミニウム、銅、チタン、タンタル、タンゲステン等の金属材料を用いることが好ましい。ま

10

20

30

40

50

た、リン等の不純物を添加した多結晶シリコンを用いることができる。形成方法は、蒸着法、P E - C V D 法、スパッタリング法、スピンドル法などの各種成膜方法を用いることができる。

【 0 1 4 4 】

層間絶縁層 6 1 0 、層間絶縁層 6 2 0 、層間絶縁層 6 3 0 、層間絶縁層 6 4 0 および層間絶縁層 6 5 0 は、無機絶縁層または有機絶縁層を、単層又は多層で形成することが好ましい。無機絶縁層としては、窒化シリコン膜、酸化窒化シリコン膜、又は窒化酸化シリコン膜等を、単層又は多層で形成することが好ましい。有機絶縁層としては、ポリイミド又はアクリル等を、単層又は多層で形成することが好ましい。また、層間絶縁層 6 1 0 、層間絶縁層 6 2 0 、層間絶縁層 6 3 0 、層間絶縁層 6 4 0 および層間絶縁層 6 5 0 の作製方法に特に限定はないが、例えば、スパッタリング法、M B E 法、P E - C V D 法、パルスレーザ堆積法、A L D 法等を適宜用いることができる。10

【 0 1 4 5 】

半導体層 6 5 1 は、酸化物半導体を単層または積層して設ければよい。

【 0 1 4 6 】

ゲート絶縁層 6 5 3 は、無機絶縁層を、単層又は多層で形成することが好ましい。また、ゲート絶縁層 6 5 3 は、半導体層 6 5 1 に酸素を供給する効果があると好ましい。

【 0 1 4 7 】

本実施の形態の構成である図 1 0 乃至図 1 2 の上面図および断面図の構成では、上記実施の形態 1 でも説明したように、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層を、ゲート電極とは別の層に設ける構成とする。そのため、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層は、ほかの導電層と離間して設ける構成とすることができる。そのため、トランジスタ T r のゲートに形成される寄生容量を抑制する構成とすることができる。20

【 0 1 4 8 】

対照的に図 7 乃至図 9 の上面図および断面図の構成では、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層が、トランジスタのゲート電極と同じ層にあるため、ゲート絶縁層といった他の層より薄い絶縁層を介して他の層と寄生容量を形成する構成となる。

【 0 1 4 9 】

また本実施の形態の構成である図 1 0 乃至図 1 2 の上面図および断面図の構成では、上記実施の形態 1 でも説明したように、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層を、ゲート電極とは別の層に設ける構成とする。そのためトランジスタ T r のゲート電極と同じ層に形成される、容量素子 C a p 1 および容量素子 C a p 2 の電極の面積を、大きくとることができる。そのため、容量素子 C a p 1 および容量素子 C a p 2 の静電容量を大きくすることができる。30

【 0 1 5 0 】

対照的に図 7 乃至図 9 の上面図および断面図の構成では、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層が、トランジスタのゲート電極と同じ層にある。そのため、複数のメモリ間のトランジスタ T r のゲート電極を接続する配線層は、ほかの導電層と離間して設ける構成が必要となり、この配線層と同層に設けられる容量素子 C a p 1 および容量素子 C a p 2 が占める面積も縮小してしまう。そのため、容量素子 C a p 1 および容量素子 C a p 2 の静電容量を大きくすることができない。40

【 0 1 5 1 】

また本実施の形態の構成である図 1 0 乃至図 1 2 の上面図および断面図の構成では、電源供給を行うための配線層が設けられた層を、半導体層にシリコンを用いたトランジスタが設けられた層と、半導体層に酸化物半導体を用いたトランジスタが設けられた層との間に設ける構成としている。そのため、半導体層に酸化物半導体を用いたトランジスタが設けられた層よりも上層に、電源供給を行うための配線層が設けられた層を設ける場合と比べ、容量素子 C a p 1 および容量素子 C a p 2 に設ける開口部の数を最小限にすることがで50

きる。

【0152】

以上説明した本実施の形態の構成では、トランジスタTrのゲートに形成される寄生容量を抑制する構成に加えて、ゲート電極と同層で複数のメモリ間のトランジスタTrのゲート電極を接続しないことで、容量素子が占める面積を確保することができる。そのため、トランジスタおよび容量素子の微細化を進めても、寄生容量の低減、および容量素子を形成するための面積の確保、を図ることができ、揮発性メモリ部VNおよび不揮発性メモリ部NVNの電位の変動を小さくできる。

【0153】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

10

【0154】

(実施の形態3)

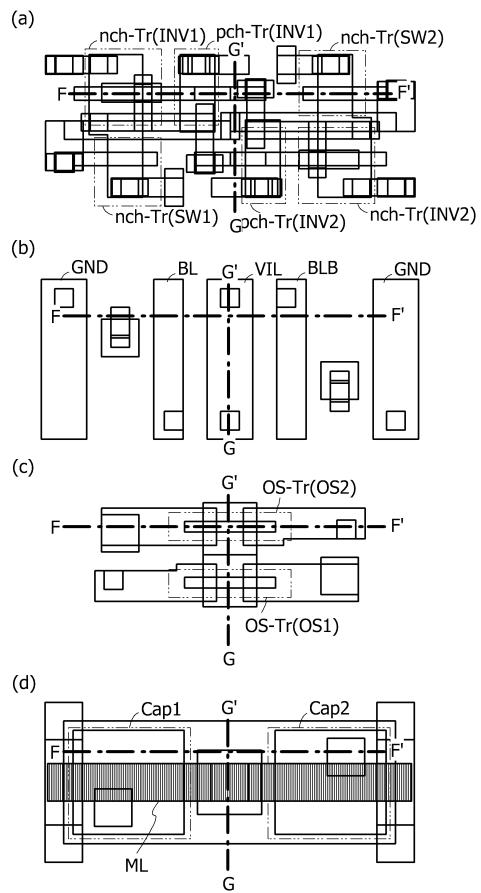

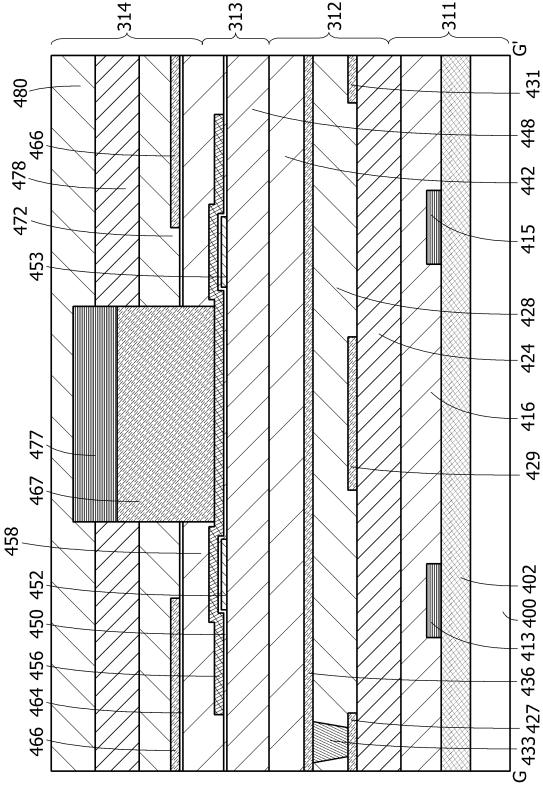

本実施の形態では、上記実施の形態2の図10乃至図12で説明した上面図及び断面図の構成とは異なる構成について、図15乃至図18を参照して説明する。なお図15乃至図17で示す上面図及び断面図に対応する回路図は、図6に示す回路図である。

【0155】

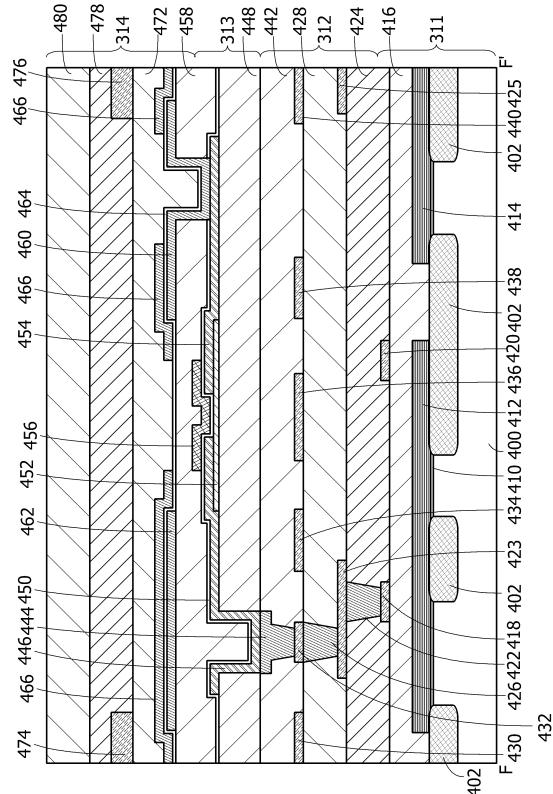

次いで、図15(a)および図16では、配線層とゲート電極を異なる層とし、トランジスタTr1及びトランジスタTr2を、高電源電位を与える配線VILに重畳する構成について、図6に示した回路構成に対応する上面図を示す。また図17では、図15(a)および図16に示す一点鎖線F-F'における断面図、図18では一点鎖線G-G'における断面図を示す。

20

【0156】

まず、図15(a)に示す上面図は、図6に示した回路図における、トランジスタ121、トランジスタ122、インバータ回路123、インバータ回路124、トランジスタTr1、トランジスタTr2、容量素子Cap1および容量素子Cap2の配置を示すものである。

【0157】

図15(a)におけるトランジスタの配置の理解しやすくするために、図15(b)では図15(a)における各素子の層構造についての模式図を示している。図15(b)に示す第1の層311は、半導体層にシリコンを用いたトランジスタが設けられた層(図中、Si\_transistor\_layerと表記)である。図15(b)に示す第2の層312は、電源供給を行うための配線層が設けられた層(図中、wiring\_layerと表記)である。図15(b)に示す第3の層313は、半導体層に酸化物半導体を用いたトランジスタが設けられた層(図中、OS\_transistor\_layerと表記)である。図15(b)に示す第4の層314は、容量素子及び複数のメモリ間のトランジスタTrのゲート電極を接続する配線層が設けられた層(図中、Capacitor\_layerと表記)である。

30

【0158】

図15(b)に示す第1の層311は、半導体層にシリコンを用いたトランジスタ、すなわちトランジスタ121(SW1)、およびトランジスタ122(SW2)、並びにインバータ回路123(INV1)、およびインバータ回路124(INV2)を有する。図15(b)に示す第2の層312は、グラウンド電位を与える配線GND、ビット線BL、高電源電位を与える配線VIL、反転ビット線BLBとなる配線層を有する。図15(b)に示す第3の層313は、半導体層に酸化物半導体を用いたトランジスタ、すなわちトランジスタTr1(OS1)、およびトランジスタTr2(OS2)を有する。図15(b)に示す第4の層314は、容量素子Cap1、容量素子Cap2及び複数のメモリ間のトランジスタTrのゲート電極を接続する配線層を有する。

40

【0159】

図16(a)では、図15(b)に示す第1の層311の上面図を示している。図16(a)の上面図では、半導体層にシリコンを用いたトランジスタを構成する、半導体層、ゲ

50

ート電極と同じ層に設けられる配線層、ソース電極およびドレイン電極と同じ層に設けられる配線層、および各層を接続するための開口部についての配置を示している。

【0160】

図16(a)に示す上面図では、トランジスタ121となるnチャネル型トランジスタ(nch-Tr(SW1))、トランジスタ122となるnチャネル型トランジスタ(nch-Tr(SW2))、インバータ回路123を構成するpチャネル型トランジスタ(pch-Tr(INV1))およびnチャネル型トランジスタ(nch-Tr(INV1))、およびインバータ回路124を構成するpチャネル型トランジスタ(pch-Tr(INV2))およびnチャネル型トランジスタ(nch-Tr(INV2))の配置を示している。

10

【0161】

図16(b)では、図15(b)に示す第2の層312の上面図を示している。図16(b)の上面図では、複数の層に設けられた配線層、および各層を接続するための開口部についての配置を示している。

【0162】

図16(b)に示す上面図では、グラウンド電位を与える配線GND、ピット線BL、高電源電位を与える配線VIL、反転ピット線BLBの配置を示している。

【0163】

図16(c)では、図15(b)に示す第3の層313の上面図を示している。図16(c)の上面図では、半導体層に酸化物半導体を用いたトランジスタを構成する、半導体層、ゲート電極、ソース電極およびドレイン電極と同じ層に設けられる配線層、および各層を接続するための開口部についての配置を示している。

20

【0164】

図16(c)に示す上面図では、トランジスタTr1となるnチャネル型トランジスタ(OS-Tr(OS1))、トランジスタTr2となるnチャネル型トランジスタ(OS-Tr(OS2))、および各層を接続するための開口部の配置を示している。

【0165】

図16(d)では、図15(b)に示す第4の層314の上面図を示している。図16(d)の上面図では、容量素子を構成する導電層、メモリセル間のゲート電極を接続するための配線層、および各層を接続するための開口部についての配置を示している。

30

【0166】

図16(d)に示す上面図では、容量素子Cap1、および容量素子Cap2、およびメモリセル間のゲート電極を接続するための配線層(図16(d)中、平行斜線を付した領域ML)の配置を示している。

【0167】

なお、図16(a)乃至図16(d)に示す上面図のレイアウトが、図11(a)乃至図11(c)に示す上面図のレイアウトと異なる点は、トランジスタTr1及びトランジスタTr2を、高電源電位を与える配線VILに重畠して設ける点にある。また図16(a)乃至図16(d)に示す上面図のレイアウトが、図11(a)乃至図11(c)に示す上面図のレイアウトと異なる点は、複数のメモリ間のトランジスタTrのゲート電極を接続する配線層と同じ第4の層314に、容量素子Cap1および容量素子Cap2を設ける点にある。

40

【0168】

図6に示す回路構成において、データの退避・復帰を行うための速度は、OS-Tr(OS1)及びOS-Tr(OS2)の各トランジスタのオン電流に大きく依存し、オン電流をできるだけ大きくすることがほしい。しかし、微細化に伴って駆動電圧を低下させる必要があり、該トランジスタのオン電流の大きさを保つことが困難になる。なおトランジスタサイズを変更することなく、オン電流を大きくする構成としては、バックゲートとなる電極を新たに追加し、バックゲートに電圧を印加してオン電流を大きくするといった構成でも実現できるが、半導体装置の製造プロセスや回路を構成する配線や動作が複雑にな

50

つてしまう。

【0169】

本実施の形態で示す構成のようにトランジスタTr1及びトランジスタTr2を、高電源電位を与える配線VILに重畠して設けることで、前述のオン電流を大きくすることができる。

【0170】

なお本実施の形態の構成において、電源供給の有無を切り替えるために制御される配線VILの電位は、半導体装置に電源供給を行う場合には高電源電位(VDD)とし、電源供給を行わない場合にはグラウンド電位(配線GNDと等電位)とする。この場合、一例としては、図19(a)の回路構成とすればよい。

10

【0171】

図19(a)の回路構成では、高電源電位を与える配線に、スイッチPSWを接続し、該スイッチPSWの制御によって、配線VILをVDDかGNDに切り替える構成とする。該構成では、スイッチPSWをVDDに切り替えた場合は、メモリセルに電源供給し、スイッチPSWをGNDに切り替えた場合は、メモリセルへの電源供給を停止する。

【0172】

この配線VILの電位の切り替えを、図2(b)に示すタイミングチャート図に併せて図示すると、図19(b)のように表すことができる。図19(b)では、電源供給の有無について表したpowerと、配線VIL及び配線GNDの電位の変化について示している。図19(b)で示すように電源電位を与える配線VILの電位を、半導体装置に電源供給を行う場合には高電源電位とし、トランジスタTr1及びトランジスタTr2のバックゲートとしての機能を配線VILに付与することで、トランジスタTr1及びトランジスタTr2のオン電流を大きくすることができる。一方で、図19(b)で示すように電源電位を与える配線VILの電位を、半導体装置に電源供給を行わない場合にはグラウンド電位とし、トランジスタTr1及びトランジスタTr2のバックゲートとしての機能を配線VILに付与することで、トランジスタTr1及びトランジスタTr2のオフ電流が低いといった特性を阻害することはない。そのため、半導体装置の製造プロセスや回路を構成する配線や動作が複雑にすることなく、微細化が進んだトランジスタTr1及びトランジスタTr2のオン電流の大きさを保つことができる。

20

【0173】

30

次いで図17では、図15(a)および図16の一点鎖線F-F'における断面図、図18では、図15(a)および図16の一点鎖線G-G'における断面図を、例示している。

【0174】

また、本実施の形態では、第1の層311のトランジスタが、単結晶のシリコン基板に形成され、第2の層312の配線層が、第1の層311上に形成され、第3の層313のトランジスタが、第2の層312上に形成され、第4の層314の容量素子及び複数のメモリ間のトランジスタTrのゲート電極を接続する配線層が、第3の層313上に形成されている場合を例示している。第1の層311のトランジスタは、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの薄膜の半導体を半導体層に用いていても良い。

40

【0175】

図17では、半導体基板400、素子分離用絶縁膜402、ゲート絶縁層410、ゲート電極412、ゲート電極414、層間絶縁層416、配線層418、配線層420、導電層422、層間絶縁層424、配線層423、導電層426、層間絶縁層428、配線層430、配線層432、配線層434、配線層436、配線層438、配線層440、導電層444、層間絶縁層442、配線層446、層間絶縁層448、半導体層452、ゲート絶縁層450、配線層454、ゲート電極456、層間絶縁層458、導電層460、導電層462、絶縁層464、導電層466、導電層468、層間絶縁層472、配線層474、配線層476、層間絶縁層478および層間絶縁層480を示している。

50

## 【0176】

図18では、半導体基板400、素子分離用絶縁膜402、ゲート電極413、ゲート電極415、層間絶縁層416、層間絶縁層424、配線層427、配線層429、配線層431、導電層433、層間絶縁層428、配線層436、層間絶縁層442、層間絶縁層448、半導体層452、半導体層453、ゲート絶縁層450、ゲート電極456、層間絶縁層458、絶縁層464、導電層466、層間絶縁層472、層間絶縁層478、導電層467、配線層477および層間絶縁層480を示している。

## 【0177】

半導体基板400は、例えば、n型又はp型の導電型を有するシリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、GaP基板、GaInAsP基板、ZnSe基板等)等を用いることができる。

10

## 【0178】

第1の層311のトランジスタは、素子分離用絶縁膜402により、他のトランジスタと、電気的に分離されている。素子分離用絶縁膜402の形成には、選択酸化法(Local Oxidation of Silicon)法)又はトレンチ分離法等を用いることができる。

## 【0179】

ゲート絶縁層410は、熱処理を行い、半導体基板400の表面を酸化して酸化シリコン膜を形成した後、選択的にエッチングして、形成する。若しくは、酸化シリコン、酸化窒化シリコン、高誘電率物質(high-k材料ともいう)である酸化ハフニウムなどの金属酸化物等を、CVD法、スパッタリング法等を用いて形成した後、選択的にエッチングして、形成する。

20

## 【0180】

ゲート電極412、ゲート電極413、ゲート電極414、ゲート電極415、配線層418、配線層420、導電層422、配線層423、導電層426、配線層430、配線層427、配線層429、配線層431、導電層433、配線層432、配線層434、配線層436、配線層438、配線層440、導電層444、配線層446、配線層454、ゲート電極456、導電層460、導電層462、導電層466、導電層468、配線層474、配線層476、導電層467及び配線層477は、アルミニウム、銅、チタン、タンタル、タンクスチーン等の金属材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。形成方法は、蒸着法、PE-CVD法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。

30

## 【0181】

層間絶縁層416、層間絶縁層424、層間絶縁層428、層間絶縁層442、層間絶縁層448、層間絶縁層458、絶縁層464、層間絶縁層472、層間絶縁層478および層間絶縁層480は、無機絶縁層または有機絶縁層を、単層又は多層で形成することが好ましい。無機絶縁層としては、窒化シリコン膜、酸化窒化シリコン膜、又は窒化酸化シリコン膜等を、単層又は多層で形成することが好ましい。有機絶縁層としては、ポリイミド又はアクリル等を、単層又は多層で形成することが好ましい。また、各絶縁層の作製方法に特に限定はないが、例えば、スパッタリング法、MBE法、PE-CVD法、パルスレーザ堆積法、ALD法等を適宜用いることができる。

40

## 【0182】

半導体層452及び半導体層453は、酸化物半導体を単層または積層して設ければよい。酸化物半導体は、一例として、インジウム、ガリウム、及び亜鉛を含む酸化物であり、In-Ga-Zn系酸化物(IGZOとも表記する)を用いることができる。なお、In-Ga-Zn系酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZn以外の金属元素が入っていてもよい。例えば、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物を用いることができる。酸化物半導体の形成方法としては、スパッタリング法、ALD法、蒸着法、塗布法

50

などを用いることができる。

【0183】

ゲート絶縁層450は、無機絶縁層を、単層又は多層で形成することが好ましい。また、ゲート絶縁層450は、半導体層452及び半導体層453に酸素を供給する効果があるとより好ましい。

【0184】

以上説明した本実施の形態の構成では、半導体装置に電源供給を行う場合にトランジスタTr1及びトランジスタTr2のオン電流を大きくすることができる。一方で、半導体装置に電源供給を行わない場合には、配線VILの電位がグラウンド電位のため、トランジスタTr1及びトランジスタTr2のオフ電流が低いといった特性を阻害することはない。そのため、半導体装置の製造プロセスや回路を構成する配線や動作が複雑にすることなく、微細化が進んだトランジスタTr1及びトランジスタTr2のオン電流の大きさを保つことができる。

【0185】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0186】

(実施の形態4)

本実施の形態では、上記実施の形態で説明したオフ電流の低いトランジスタの半導体層に用いることのできる酸化物半導体について説明する。

【0187】

トランジスタの半導体層中のチャネル形成領域に用いる酸化物半導体としては、少なくともインジウム(Indium)又は亜鉛(Zinc)を含むことが好ましい。特にIndium及びZincを含むことが好ましい。また、それらに加えて、酸素を強く結びつけるスタビライザーを有することが好ましい。スタビライザーとしては、ガリウム(Gallium)、スズ(Silver)、ジルコニウム(Zirconium)、ハフニウム(Hafnium)及びアルミニウム(Aluminum)の少なくともいずれかを有すればよい。

【0188】

また、他のスタビライザーとして、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Europium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplum)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)のいずれか一種又は複数種を有してもよい。

【0189】

トランジスタの半導体層として用いられる酸化物半導体としては、例えば、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-Zr-Zn系酸化物、In-Ti-Zn系酸化物、In-Sc-Zn系酸化物、In-Y-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物等がある。

【0190】

例えば、In:Ga:Zn = 1:1:1、In:Ga:Zn = 3:1:2、あるいはIn:Ga:Zn = 2:1:3の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の

10

20

30

40

50

酸化物を用いるとよい。

【0191】

半導体層を構成する酸化物半導体膜に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタの閾値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜の形成後において、脱水化処理（脱水素化処理）を行い酸化物半導体膜から、水素、又は水分を除去して不純物が極力含まれないように高純度化することが好ましい。

【0192】

なお、酸化物半導体膜への脱水化処理（脱水素化処理）によって、酸化物半導体膜から水素が減少してしまうことがある。よって、酸化物半導体膜への脱水化処理（脱水素化処理）によって増加した水素欠損を補填するため水素を酸化物半導体膜に加える処理を行うことが好ましい。本明細書等において、酸化物半導体膜に水素を供給する場合を、加水素化処理と記す場合がある、又は酸化物半導体膜に含まれる水素を化学量論的組成よりも多くする場合を過水素化処理と記す場合がある。

【0193】

このように、酸化物半導体膜は、脱水化処理（脱水素化処理）により、水素又は水分が除去され、加水素化処理により水素欠損を補填することによって、i型（真性）化又はi型に限りなく近く実質的にi型（真性）である酸化物半導体膜とすることができます。なお、実質的に真性とは、酸化物半導体膜中にドナーに由来するキャリアが極めて少なく（ゼロに近く）、キャリア密度が $1 \times 10^{17} / \text{cm}^3$ 以下、 $1 \times 10^{16} / \text{cm}^3$ 以下、 $1 \times 10^{15} / \text{cm}^3$ 以下、 $1 \times 10^{14} / \text{cm}^3$ 以下、 $1 \times 10^{13} / \text{cm}^3$ 以下であることをいう。

【0194】

また、このように、i型又は実質的にi型である酸化物半導体膜を備えるトランジスタは、極めて優れたオフ電流特性を実現できる。例えば、酸化物半導体膜を用いたトランジスタがオフ状態のときのドレイン電流を、室温（25程度）にて $1 \times 10^{-18} \text{ A}$ 以下、好ましくは $1 \times 10^{-21} \text{ A}$ 以下、更に好ましくは $1 \times 10^{-24} \text{ A}$ 以下、又は85にて $1 \times 10^{-15} \text{ A}$ 以下、好ましくは $1 \times 10^{-18} \text{ A}$ 以下、更に好ましくは $1 \times 10^{-21} \text{ A}$ 以下とすることができます。なお、トランジスタがオフ状態とは、nチャネル型のトランジスタの場合、ゲート電圧が閾値電圧よりも十分小さい状態をいう。具体的には、ゲート電圧が閾値電圧よりも1V以上、2V以上又は3V以上小さければ、トランジスタはオフ状態となる。

【0195】

また、成膜される酸化物半導体は、例えば非単結晶を有してもよい。非単結晶は、例えば、CAAC（C Axis Aligned Crystal）、多結晶、微結晶、非晶質部を有する。

【0196】

酸化物半導体は、例えばCAACを有してもよい。なお、CAACを有する酸化物半導体を、CAAC-OS（C Axis Aligned Crystalline Oxide Semiconductor）と呼ぶ。

【0197】

CAAC-OSは、例えば、透過型電子顕微鏡（TEM：Transmission Electron Microscope）による観察像で、結晶部を確認することができる場合がある。CAAC-OSに含まれる結晶部は、例えば、TEMによる観察像で、一辺 $100 \text{ nm}$ の立方体内に収まる大きさであることが多い。また、CAAC-OSは、TEMによる観察像で、結晶部と結晶部との境界を明確に確認できない場合がある。また、CAAC-OSは、TEMによる観察像で、粒界（グレインバウンダリーともいう。）を明確に確認できない場合がある。CAAC-OSは、例えば、明確な粒界を有さないため、不純物が偏析することが少ない。また、CAAC-OSは、例えば、明確な粒界を有さないため、欠陥準位密度が高くなることが少ない。また、CAAC-OSは、例えば、明

10

20

30

40

50

確な粒界を有さないため、電子移動度の低下が小さい。

【0198】

C A A C - O S は、例えば、複数の結晶部を有し、当該複数の結晶部において c 軸が被形成面の法線ベクトル又は表面の法線ベクトルに平行な方向に揃っている場合がある。また、C A A C - O S は、例えば、X 線回折 ( X R D : X - R a y D i f f r a c t i o n ) 装置を用い、o u t - o f - p l a n e 法による分析を行うと、配向を示す 2 が 3 1 ° 近傍のピークが現れる場合がある。また、C A A C - O S は、例えば、電子線回折パターンで、スポット ( 輝点 ) が観測される場合がある。なお、特に、ビーム径が 10 nm 以下、又は 5 nm 以下の電子線を用いて得られる電子線回折パターンを、極微電子線回折パターンと呼ぶ。また、C A A C - O S は、例えば、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが揃っていない場合がある。C A A C - O S は、例えば、c 軸配向し、a 軸又は / 及び b 軸はマクロに揃っていない場合がある。

10

【0199】

C A A C - O S に含まれる結晶部は、例えば、c 軸が C A A C - O S の被形成面の法線ベクトル又は表面の法線ベクトルに平行な方向になるように揃い、かつ a b 面に垂直な方向から見て金属原子が三角形状又は六角形状に配列し、c 軸に垂直な方向から見て金属原子が層状又は金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、80 ° 以上 100 ° 以下、好ましくは 85 ° 以上 95 ° 以下の範囲も含まれることとする。また、単に平行と記載する場合、-10 ° 以上 10 ° 以下、好ましくは -5 ° 以上 5 ° 以下の範囲も含まれることとする。

20

【0200】

また、C A A C - O S は、例えば、欠陥準位密度を低減することで形成することができる。酸化物半導体において、例えば、酸素欠損は欠陥準位である。酸素欠損は、トラップ準位となることや、水素を捕獲することによってキャリア発生源となることがある。C A A C - O S を形成するためには、例えば、酸化物半導体に酸素欠損を生じさせないことが重要となる。従って、C A A C - O S は、欠陥準位密度の低い酸化物半導体である。又は、C A A C - O S は、酸素欠損の少ない酸化物半導体である。

【0201】

不純物濃度が低く、欠陥準位密度の低い ( 酸素欠損の少ない ) ことを高純度真性又は実質的に高純度真性と呼ぶ。高純度真性又は実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。従って、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、しきい値電圧がマイナスとなる電気特性 ( ノーマリーオンともいう。 ) になることが少ない場合がある。また、高純度真性又は実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。従って、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる場合がある。なお、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性が不安定となる場合がある。

30

【0202】

また、高純度真性又は実質的に高純度真性である C A A C - O S を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

【0203】

酸化物半導体は、例えば多結晶を有してもよい。なお、多結晶を有する酸化物半導体を、多結晶酸化物半導体と呼ぶ。多結晶酸化物半導体は複数の結晶粒を含む。

【0204】

酸化物半導体は、例えば微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。

40

## 【0205】

微結晶酸化物半導体は、例えば、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体に含まれる結晶部は、例えば、1 nm以上100 nm以下、又は1 nm以上10 nm以下の大きさであることが多い。特に、例えば、1 nm以上10 nm以下の微結晶をナノ結晶(nc:nanocrystal)と呼ぶ。ナノ結晶を有する酸化物半導体を、nc-OS(nanocrystalline Oxide Semiconductor)と呼ぶ。また、nc-OSは、例えば、TEMによる観察像では、結晶部と結晶部との境界を明確に確認できない場合がある。また、nc-OSは、例えば、TEMによる観察像では、明確な粒界を有さないため、不純物が偏析することが少ない。また、nc-OSは、例えば、明確な粒界を有さないため、欠陥準位密度が高くなることが少ない。また、nc-OSは、例えば、明確な粒界を有さないため、電子移動度の低下が小さい。10

## 【0206】

nc-OSは、例えば、微小な領域(例えば、1 nm以上10 nm以下の領域)において原子配列に周期性を有する場合がある。また、nc-OSは、例えば、結晶部と結晶部との間で規則性がないため、巨視的には原子配列に周期性が見られない場合、又は長距離秩序が見られない場合がある。従って、nc-OSは、例えば、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。nc-OSは、例えば、XRD装置を用い、結晶部よりも大きいビーム径のX線でout-of-plane法による分析を行うと、配向を示すピークが検出されない場合がある。また、nc-OSは、例えば、結晶部よりも大きいビーム径(例えば、20 nm以上、又は50 nm以上)の電子線を用いる電子線回折パターンでは、ハローパターンが観測される場合がある。また、nc-OSは、例えば、結晶部と同じか結晶部より小さいビーム径(例えば、10 nm以下、又は5 nm以下)の電子線を用いる極微電子線回折パターンでは、スポットが観測される場合がある。また、nc-OSの極微電子線回折パターンは、例えば、円を描くように輝度の高い領域が観測される場合がある。また、nc-OSの極微電子線回折パターンは、例えば、当該領域内に複数のスポットが観測される場合がある。20

## 【0207】

nc-OSは、微小な領域において原子配列に周期性を有する場合があるため、非晶質酸化物半導体よりも欠陥準位密度が低くなる。但し、nc-OSは、結晶部と結晶部との間で規則性がないため、CAC-OSと比べて欠陥準位密度が高くなる。30

## 【0208】

なお、酸化物半導体が、CAC-OS、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、CAC-OSの領域、のいずれか二種以上の領域を有する場合がある。また、混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、CAC-OSの領域、のいずれか二種以上の領域の積層構造を有する場合がある。

## 【0209】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。40

## 【0210】

## (実施の形態5)

本実施の形態では、上述の実施の形態で説明した半導体装置を電子部品に適用する例、及び該電子部品を具備する電子機器に適用する例について、図13、図14を用いて説明する。

## 【0211】

図13(a)では上述の実施の形態で説明した半導体装置を電子部品に適用する例について説明する。なお電子部品は、半導体パッケージ、又はIC用パッケージともいう。この電子部品は、端子取り出し方向や、端子の形状に応じて、複数の規格や名称が存在する。そこで、本実施の形態では、その一例について説明することにする。50

## 【0212】

上記実施の形態2の図10乃至図12、実施の形態3の図15乃至図19に示すようなトランジスタで構成される半導体装置は、組み立て工程（後工程）を経て、プリント基板に脱着可能な部品が複数合わさることで完成する。

## 【0213】

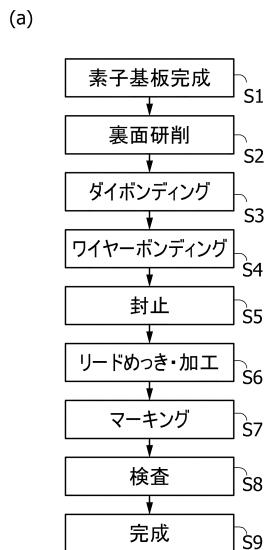

後工程については、図13（a）に示す各工程を経ることで完成させることができる。具体的には、前工程で得られる素子基板が完成（ステップS1）した後、基板の裏面を研削する（ステップS2）。この段階で基板を薄膜化することで、前工程での基板の反り等を低減し、部品としての小型化を図るためである。

## 【0214】

基板の裏面を研削して、基板を複数のチップに分離するダイシング工程を行う。そして、分離したチップを個々にピックアップしてリードフレーム上に搭載し接合する、ダイボンディング工程を行う（ステップS3）。このダイボンディング工程におけるチップとリードフレームとの接着は、樹脂による接着や、テープによる接着等、適宜製品に応じて適した方法を選択する。なお、ダイボンディング工程は、インターポーザ上に搭載し接合してもよい。

## 【0215】

次いでリードフレームのリードとチップ上の電極とを、金属の細線（ワイヤー）で電気的に接続する、ワイヤーボンディングを行う（ステップS4）。金属の細線には、銀線や金線を用いることができる。また、ワイヤーボンディングは、ボールボンディングや、ウェッジボンディングを用いることができる。

## 【0216】

ワイヤーボンディングされたチップは、エポキシ樹脂等で封止される、モールド工程が施される（ステップS5）。モールド工程を行うことで電子部品の内部が樹脂で充填され、機械的な外力により、内蔵される回路部やワイヤーを保護することができ、また水分や埃による特性の劣化を低減することができる。

## 【0217】

次いでリードフレームのリードをメッキ処理する。そしてリードを切断及び成形加工する（ステップS6）。このめっき処理によりリードの錆を防止し、後にプリント基板に実装する際のはんだ付けをより確実に行うことができる。

## 【0218】

次いでパッケージの表面に印字処理（マーキング）を施す（ステップS7）。そして最終的な検査工程（ステップS8）を経て電子部品が完成する（ステップS9）。

## 【0219】

以上説明した電子部品は、上述の実施の形態で説明した半導体装置を含む構成とすることができます。そのため、素子の微細化を進めてもデータの保持に必要な保持容量を確保でき、かつトランジスタの寄生容量を低減することによる正常な動作に必要な保持容量の削減を図ることができる半導体装置を有する電子部品を実現することができる。該電子部品は、データの退避・復帰を行うトランジスタの寄生容量の低減が図られたことで、データの保持に必要な保持容量を確保することを容易にすることができるメモリセルを有する半導体装置を含む。そのため、データの退避・復帰をより確実に行うことのできる電子部品である。

## 【0220】

また、完成した電子部品の斜視模式図を図13（b）に示す。図13（b）では、電子部品の一例として、QFP（Quad Flat Package）の斜視模式図を示している。図13（b）に示す電子部品700は、リード701及び半導体装置703を示している。図13（b）に示す電子部品700は、例えばプリント基板702に実装される。このような電子部品700が複数組み合わされて、それぞれがプリント基板702上で電気的に接続されることで電子部品が実装された基板（実装基板704）が完成する。完成した実装基板704は、電子機器等の内部に設けられる。

10

20

30

40

50

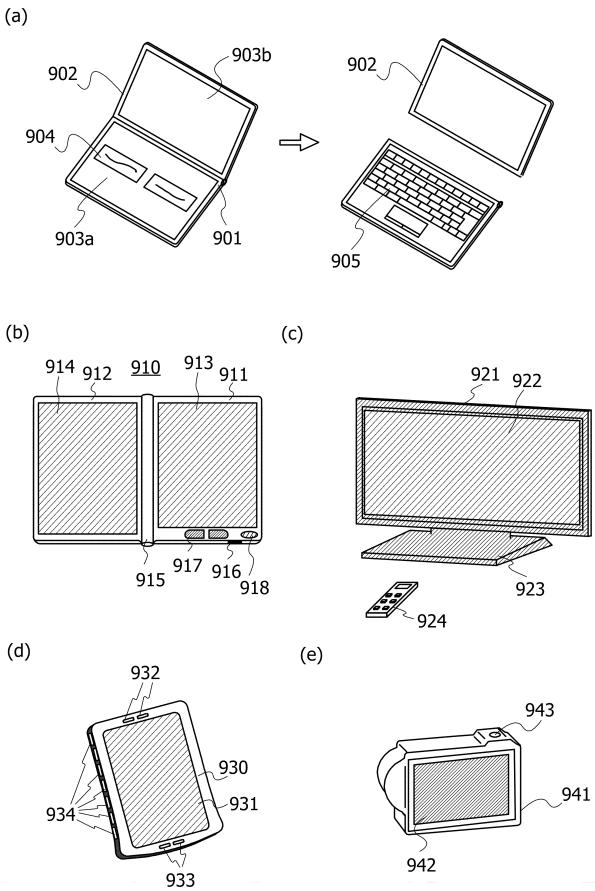

**【 0 2 2 1 】**

次いで、コンピュータ、携帯情報端末（携帯電話、携帯型ゲーム機、音響再生装置なども含む）、電子ペーパー、テレビジョン装置（テレビ、又はテレビジョン受信機ともいう）、デジタルビデオカメラなどの電子機器に、上述の電子部品を適用する場合について説明する。

**【 0 2 2 2 】**

図14（a）は、携帯型の情報端末であり、筐体901、筐体902、第1の表示部903a、第2の表示部903bなどによって構成されている。筐体901と筐体902の少なくとも一部には、先の実施の形態に示す半導体装置を有する実装基板が設けられている。そのため、データの退避・復帰をより確実に行うことのできる携帯型の情報端末が実現される。

10

**【 0 2 2 3 】**

なお、第1の表示部903aはタッチ入力機能を有するパネルとなっており、例えば図14（a）の左図のように、第1の表示部903aに表示される選択ボタン904により「タッチ入力」を行うか、「キーボード入力」を行うかを選択できる。選択ボタンは様々な大きさで表示できるため、幅広い世代の人が使いやすさを実感できる。ここで、例えば「タッチ入力」を選択した場合、図14（a）の右図のように第1の表示部903aにはキーボード905が表示される。これにより、従来の情報端末と同様に、キー入力による素早い文字入力などが可能となる。

**【 0 2 2 4 】**

20

また、図14（a）に示す携帯型の情報端末は、図14（a）の右図のように、第1の表示部903a及び第2の表示部903bのうち、一方を取り外すことができる。第1の表示部903aもタッチ入力機能を有するパネルとし、持ち運びの際、さらなる軽量化を図ることができ、一方の手で筐体902を持ち、他方の手で操作することができるため便利である。

**【 0 2 2 5 】**

図14（a）に示す携帯型の情報端末は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB端子など）、記録媒体挿入部などを備える構成としてもよい。

30

**【 0 2 2 6 】**

また、図14（a）に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

**【 0 2 2 7 】**

更に、図14（a）に示す筐体902にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

**【 0 2 2 8 】**

図14（b）は、電子ペーパーを実装した電子書籍910であり、筐体911と筐体912の2つの筐体で構成されている。筐体911及び筐体912には、それぞれ表示部913及び表示部914が設けられている。筐体911と筐体912は、軸部915により接続されており、該軸部915を軸として開閉動作を行うことができる。また、筐体911は、電源916、操作キー917、スピーカー918などを備えている。筐体911、筐体912の少なくとも一には、先の実施の形態に示す半導体装置を有する実装基板が設けられている。そのため、データの退避・復帰をより確実に行うことのできる電子書籍が実現される。

40

**【 0 2 2 9 】**

図14（c）は、テレビジョン装置であり、筐体921、表示部922、スタンド923などで構成されている。テレビジョン装置920の操作は、筐体921が備えるスイッチ

50

や、リモコン操作機 924 により行うことができる。筐体 921 及びリモコン操作機 924 には、先の実施の形態に示す半導体装置を有する実装基板が搭載されている。そのため、データの退避・復帰をより確実に行うことのできるテレビジョン装置が実現される。

#### 【0230】

図 14 (d) は、スマートフォンであり、本体 930 には、表示部 931 と、スピーカー 932 と、マイク 933 と、操作ボタン 934 等が設けられている。本体 930 内には、先の実施の形態に示す半導体装置を有する実装基板が設けられている。そのためデータの退避・復帰をより確実に行うことのできるスマートフォンが実現される。

#### 【0231】

図 14 (e) は、デジタルカメラであり、本体 941、表示部 942、操作スイッチ 943 などによって構成されている。本体 941 内には、先の実施の形態に示す半導体装置を有する実装基板が設けられている。そのため、データの退避・復帰をより確実に行うことのできるデジタルカメラが実現される。

10

#### 【0232】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置を有する実装基板が搭載されている。このため、データの退避・復帰をより確実に行うことのできる電子機器が実現される。

#### 【実施例 1】

#### 【0233】

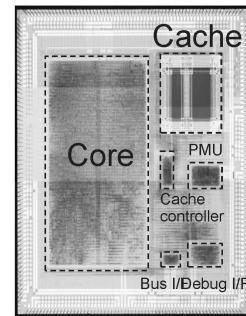

本実施例では、上記実施の形態 3 で説明した半導体装置（以下、OS-SRAM という）の構成のキャッシュメモリを内蔵した 32bit マイクロプロセッサについて試作したので、評価結果に関して説明する。

20

#### 【0234】

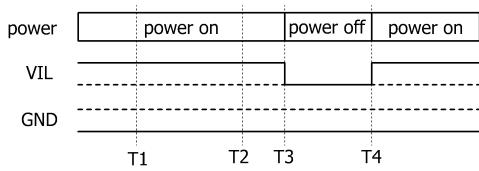

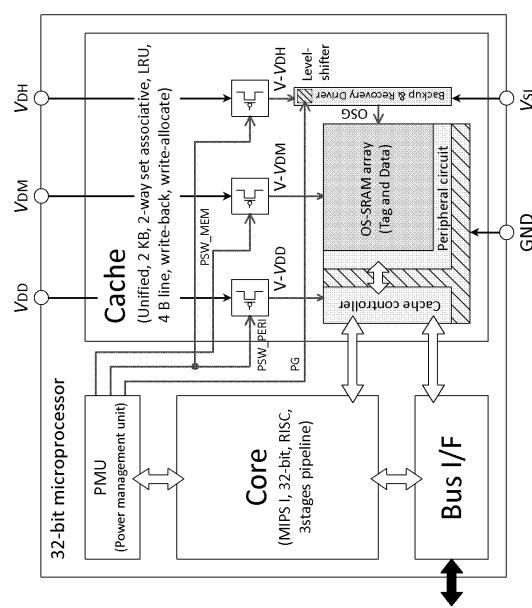

OS-SRAM の回路図と Power - Gating (PG) シーケンスを図 20、図 21 にそれぞれ示す。

#### 【0235】

図 20 に示すように OS-SRAM は標準的な SRAM (6T 型) に、2 つの半導体層に酸化物半導体を用いたトランジスタ（以下、OS-FET という）と 2 つの容量素子（以下、Capacitor という）を追加することで構成される。

#### 【0236】

30

なお図 20 に示す OS-SRAM が有するトランジスタのパラメータは、表 1 の通りである。

#### 【0237】

【表1】

|                                 |                                   |                      |

|---------------------------------|-----------------------------------|----------------------|

| Width/Length of transistor [nm] | Drive Access Load                 | 200/45 130/45 130/45 |

|                                 | OS-FET                            | 40/100               |

| Capacitance of capacitor [fF]   |                                   | 0.94                 |

| Power-supply voltage [V]        | VDM (for Si-FET) VDH (for OS-FET) | 1.1 2.5              |

## 【0238】

図21に示すPGシーケンスによると、双安定部Q<sub>1</sub>，Q<sub>2</sub>に保持されているデータをノードSN1，SN2に退避し、その後Virtual-V<sub>DM</sub> (V-V<sub>DM</sub>)を遮断することで電源供給を停止する。復帰時にはノードSN1，SN2に保持されているデータを双安定部Q<sub>1</sub>，Q<sub>2</sub>に戻すことでPG前の状態から通常動作を再開できる。

## 【0239】

図22にOS-SRAMのレイアウトを示す。データを退避するために追加する部分(2つのOS-FETと2つのCapacitor)は、標準的なSRAMが形成されている層の上に積層することができる。よって、標準的なSRAMからOS-SRAMへの変更によって伴う面積増加は0%とすることができる。OS-SRAMセルの面積は0.46 $\mu\text{m}^2$  (135F<sup>2</sup>)となっている。

## 【0240】

データを退避できるSRAMは、OS-SRAMの他にMRAM(Magnetoresistive RAM), FeRAM(Ferroelectric Random Access Memory)などを用いる手法も提案されている。しかし、いずれも標準的なSRAMからの面積増加があり、面積増加がなくデータを退避できるSRAMにできるのはOS-SRAMだけである。

## 【0241】

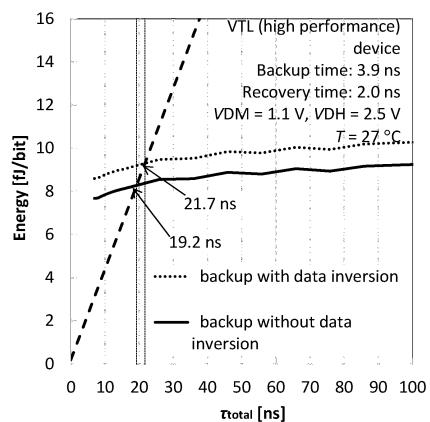

OS-SRAMのPGシーケンスにおける、退避(Backup)時間、復帰(Recovery)時間はそれぞれ3.9ns, 2.0nsで可能であることをシミュレーションにて確認した。ここで、各区間での消費エネルギーについて図23に整理して示す。

## 【0242】

Backup区間：双安定部Q<sub>1</sub>，Q<sub>2</sub>に保持されているデータを退避する際、OS-FETのゲート容量やCapacitorへの充放電によってエネルギーが消費される(E<sub>b</sub><sub>ackup</sub>)。

## 【0243】

Power-off区間：電源遮断を行うことによってスタンバイ電力を削減する。理想的には遮断中のリーク電流I<sub>off</sub>=0であるが、現実には電源遮断を行うパワースイッチにてリーク電流が発生し、この値はパワースイッチ用トランジスタの設計サイズに左右される。本シミュレーションでは設計仕様に左右されない本質的なPG効果を調査するためにパワースイッチのリーク電流をゼロ(I<sub>off</sub>=0)とした。

## 【0244】

20

30

40

50

Recovery区間：backup部（ノードSN1, SN2）から双安定部Q, QBにデータを戻すためにE<sub>recovery</sub>が消費される。E<sub>recovery</sub>にはOS-FETのゲート容量やV<sub>VDM</sub>配線への充電、双安定部Q, QBでの動作開始時における貫通電流がある。

## 【0245】

スタンバイ状態時にはスタンバイ電力（I<sub>sby</sub>’V<sub>D</sub>）が常に消費されるが、PGを行うことによってこのスタンバイ電力をゼロにできる。ある一定区間<sub>total</sub>のスタンバイ電力をPGによって削減する場合、PG適用時の全区間エネルギー（E<sub>backup</sub> + E<sub>off</sub> + E<sub>recovery</sub>）と、スタンバイ電力（I<sub>sby</sub>’V<sub>D</sub>’<sub>total</sub>）の差分E<sub>overhead</sub>は式（1）で表される。

10

## 【0246】

## 【数1】

$$E_{\text{overhead}} = (E_{\text{backup}} + E_{\text{off}} + E_{\text{recovery}}) - (I_{\text{sby}} \times V_{\text{D}} \times \tau_{\text{total}}) \quad (1)$$

## 【0247】

ここで注意すべき点は、「スタンバイ電力ゼロ 低消費電力」ということである。E<sub>overhead</sub> = 0 になる時間（BET：Break-Even Time）よりも短い時間のPGを行った場合、PGを行うことによって逆に消費電力が増加することが式（1）よりわかる。BETは式（2）で表される。

## 【0248】

## 【数2】

$$BET = (E_{\text{backup}} + E_{\text{off}} + E_{\text{recovery}}) / (I_{\text{sby}} \times V_{\text{D}}) \quad (2)$$

## 【0249】

このように、BETよりも短い時間のPGを行うことには低消費電力の効果はなく、いかにBETを短くするかが重要である。OS-SRAMにおいてPGを行った場合のエネルギーを図24に示す。電源遮断を行う時間（off）を振ることでPGとスタンバイ時のエネルギーが等しくなる時間を求めている。シミュレーションの初期条件には、双安定部Q, QBとbackup部のデータが異なる場合と同じ場合の2つを仮定している。この2条件（backup with data inversion, backup without data inversion）でのBETはそれぞれ21.7ns, 19.2nsと見積もられた。

30

## 【0250】

標準的なSRAMからOS-SRAMへ変更したことによる通常動作への影響について調査した。

## 【0251】

待機電力：OS-SRAM, 標準的なSRAMともに419nWである。

## 【0252】

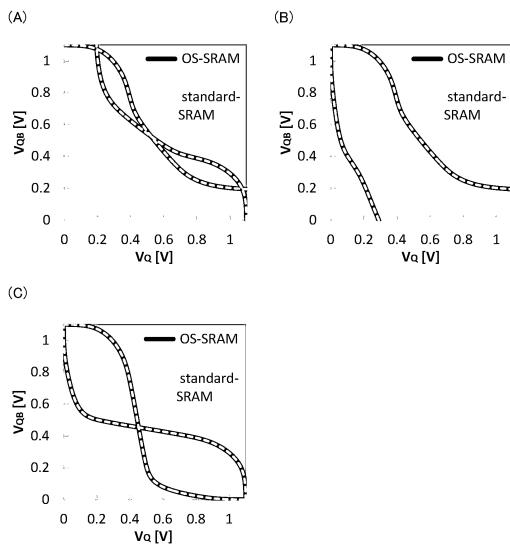

スタティックノイズマージン（SNM）：図25（A）乃至（C）にRead、Write、Hold動作時のSNMを示す。図からわかるように、SNMが重なっており、SNMの劣化は全くない。

40

## 【0253】

遅延時間：双安定部Q, QBの反転遅延はOS-SRAMで17.7ps, 標準的なSRAMで15.2psであった。ワード線の遅延, ビット線の遅延をシミュレーションするために、256行’128列のOS-SRAM arrayおよび標準的なSRAM arrayを仮定した。ワード線の昇圧時間はOS-SRAMで39.4ps, 標準的なSRAMで36.9psであった。読み出し動作時に、ワード線が立ち上がってからビット線の電位が（V<sub>D</sub> - V<sub>BLSENSE</sub>）に放電するまでの時間は、OS-SRAMで131ps, 標準的なSRAMで126psであった（V<sub>BLSENSE</sub> = 0.3V）。

50

## 【0254】

動的消費電力：遅延のシミュレーションと同じテストベンチを使用した。OS-SRAMと標準的なSRAMにおいて、双安定部Q, QBの反転による消費電力：3.73fJ, 3.24fJ, ワード線による消費電力：79.9fJ, 76.6fJ, ビット線による消費電力：3.81pJ, 3.77pJ、であった。

## 【0255】

以上のように、標準的なSRAMからOS-SRAMへ変更したことによる通常動作への影響はほぼ無視できる。これは、通常動作時に使用する双安定部Q, QBとbackup部をOS-FETによって電気的に分離しているためである。

## 【0256】

OS-SRAMの特性について表2にまとめた。

## 【0257】

## 【表2】

|                                    | OS-SRAM                                 | Standard-SRAM |       |

|------------------------------------|-----------------------------------------|---------------|-------|

| Area [ $\mu\text{m}^2$ ]           | 0.5704 (+0%)                            | 0.5704        |       |

| Standby Power [nW/bit]             | 419 (+0%)                               | 419           |       |

| Static Noise Margin                | No degradation                          | -             | 20    |

| Bistable node inversion delay [ps] | 17.7 (+16.1%)                           | 15.2          |       |

| Wordline delay [ps]                | 39.4 (+6.7%)                            | 36.9          |       |

| Bitline delay [ps]                 | 181 (+3.9%)                             | 126           |       |

| VTL (HP)                           | Bistable node inversion energy [fJ/bit] | 3.73 (+15.2%) | 3.24  |

|                                    | Wordline dynamic energy [fJ]            | 79.9 (+4.3%)  | 76.6  |

|                                    | Bitline dynamic energy [pJ]             | 3.81 (+1.1%)  | 3.77  |

| Backup time [ns]                   | 3.9                                     | -             | 30    |

| Recovery time [ns]                 | 2.0                                     | -             |       |

| Energy for PG [fJ/bit]             | 9.09                                    | -             |       |

| BET [ns]                           | 21.7                                    | -             |       |

| VTG (LP)                           | Standby power[nW/bit]                   | 45.7(+0%)     | 45.7  |

|                                    | Energy for PG [fJ/bit]                  | 7.09          | -     |

|                                    | BET [ns]                                | 155           | -     |

| VTH (LSTP)                         | Standby power[nW/bit]                   | 0.589(+0%)    | 0.589 |

|                                    | Energy for PG [fJ/bit]                  | 6.89          | -     |

|                                    | BET [ns]                                | 11700         | -     |

## 【0258】

OS-SRAMを32-bitマイクロプロセッサのキャッシュメモリに適用した。試作した2KBのキャッシュは、CMOS: 350nm, OS: 180nm processes technologyを用い、OS-SRAMのbackup部はW/L = 8/0.0n

m / 180 nm の OS - FET と C = 27.1 fF の Capacitor で構成している。図 26 にチップ写真を示す。また、マイクロプロセッサの仕様を表 3 に示す。

【0259】

【表 3】

| Technology           |              | CMOS: 350 nm               | OS: 180 nm |

|----------------------|--------------|----------------------------|------------|

| Configuration        |              | Unified                    |            |

| Capacity             |              | 2 KB                       | 10         |

| Associativity        |              | 2 way set associative      |            |

| Cache                | Displacement | LRU method                 |            |

|                      | Block size   | 4 B                        |            |

|                      | Write method | write-back, write-allocate |            |

|                      | Hit latency  | 2 clock cycle              |            |

| ISA                  |              | MIPS I (32-bit, RISC)      |            |

| Power-supply voltage | Si: 2.5 V    | OS: 2.5 V / -1 V           | 20         |

| Clock frequency      |              | 15 MHz                     |            |

【0260】

また図 27 にマイクロプロセッサのブロック図を示す。キャッシュのパワードメインは OS - SRAM array 部、駆動回路部 (cache controller 含む)、Backup & Recovery Driver 部 (2.5 V / -1 V 仕様) の 3 つがあり、それぞれの high - level (V - V<sub>DD</sub>, V - V<sub>DM</sub>, V - V<sub>DH</sub>) 側にパワースイッチを設けている。PMU (Power Management Unit) から OS - FET を制御する PG 信号とパワースイッチを制御する PSW\_PERI 信号, PSW\_MEM 信号がキャッシュに入力されることで PG シーケンスが実行される。

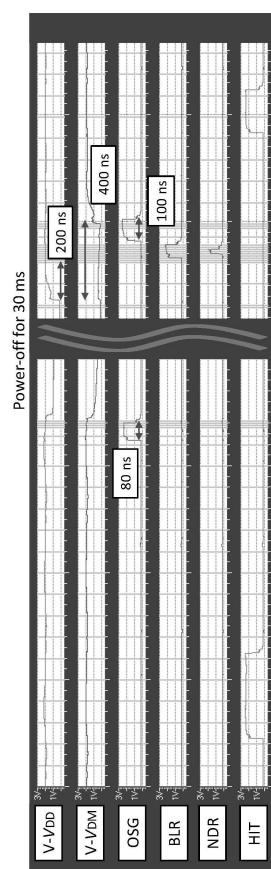

【0261】

図 28 に示す PG 時のオシロスコープ波形から正常な PG 動作を確認できる。図中の BLR 信号と NDR 信号は、復帰動作開始時において SRAM セル中の双安定部 Q, QB を GND 電位にプリチャージするために使用している。測定より 80 ns の退避動作、400 ns の復帰動作 (電源安定化のための 200 ns を含む) を確認した。スタンバイ電力は通常時 922 nW, 電源遮断時 22.5 nW が得られ、PG によって 97.6 % の Standby 電力を削減できることを確認できた。

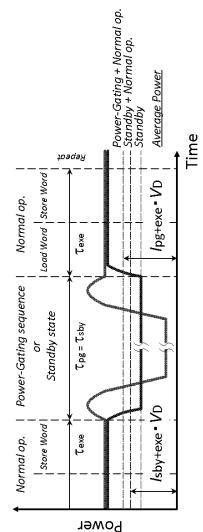

【0262】

図 29 に示す B E T 評価は、通常動作 (Store Word, Load Word) 間に PG 状態を <sub>pg</sub> 插入したときの平均電力 P<sub>pg+exe</sub> と、通常動作間に Standby 状態を <sub>sby</sub> (= <sub>pg</sub>) 插入したときの平均電力 P<sub>sby+exe</sub> の差分をとることでオーバーヘッド電力を測定し (式 3 を参照)、式 (3) におけるオーバーヘッド電力が 0 になる時間を B E T とした。

【0263】

【数 3】

$$P_{\text{overhead}} = P_{\text{pg+exe}} - P_{\text{sby+exe}} \quad (3)$$

10

20

30

40

50

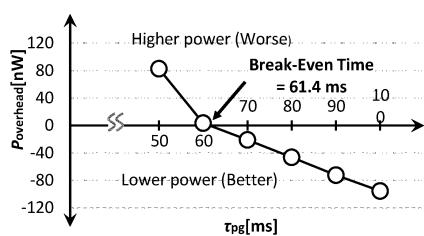

## 【0264】

図30よりBET = 61.4 msが得られた。なお、85において1日以上のデータ保持特性を確認している。

## 【0265】

今回の試作ではCMOS: 350 nm / OS: 180 nmの積層プロセスが実証され、最先端プロセスにおける回路面積を大きくすることなくOS-SRAMを適用できることが実証された。350 nm CMOS processでは、元々リーク電力が大きくなないことから2 KB cacheのBETはms orderに留まっているが、微細化が進みSi-FETのリーク電流が大きくなればなるほどOS-SRAMによるPG技術は効果を発揮する。

10

## 【符号の説明】

## 【0266】

|        |          |    |

|--------|----------|----|

| 100    | メモリセル    | 10 |

| 101    | 記憶回路     |    |

| 101_mn | 記憶回路     |    |

| 101_11 | 記憶回路     |    |

| 111    | 絶縁層      |    |

| 112    | 半導体層     |    |

| 113    | 電極       |    |

| 114    | 電極       | 20 |

| 115    | ゲート絶縁層   |    |

| 116    | ゲート電極    |    |

| 117    | 電極       |    |

| 118    | 層間絶縁層    |    |

| 119    | 配線層      |    |

| 121    | トランジスタ   |    |

| 122    | トランジスタ   |    |

| 123    | インバータ回路  |    |

| 124    | インバータ回路  |    |

| 400    | 半導体基板    | 30 |

| 402    | 素子分離用絶縁膜 |    |

| 410    | ゲート絶縁層   |    |

| 412    | ゲート電極    |    |

| 413    | ゲート電極    |    |

| 414    | ゲート電極    |    |

| 415    | ゲート電極    |    |

| 416    | 層間絶縁層    |    |

| 418    | 配線層      |    |

| 420    | 配線層      |    |

| 422    | 導電層      | 40 |

| 423    | 配線層      |    |

| 424    | 層間絶縁層    |    |

| 426    | 導電層      |    |

| 427    | 配線層      |    |

| 428    | 層間絶縁層    |    |

| 429    | 配線層      |    |

| 430    | 配線層      |    |

| 431    | 配線層      |    |

| 432    | 配線層      |    |

| 433    | 導電層      | 50 |

|       |          |    |

|-------|----------|----|

| 4 3 4 | 配線層      |    |

| 4 3 6 | 配線層      |    |

| 4 3 8 | 配線層      |    |

| 4 4 0 | 配線層      |    |

| 4 4 2 | 層間絶縁層    |    |

| 4 4 4 | 導電層      |    |

| 4 4 6 | 配線層      |    |

| 4 4 8 | 層間絶縁層    |    |

| 4 5 0 | ゲート絶縁層   |    |

| 4 5 2 | 半導体層     | 10 |

| 4 5 3 | 半導体層     |    |

| 4 5 4 | 配線層      |    |

| 4 5 6 | ゲート電極    |    |

| 4 5 8 | 層間絶縁層    |    |

| 4 6 0 | 導電層      |    |

| 4 6 2 | 導電層      |    |

| 4 6 4 | 絶縁層      |    |

| 4 6 6 | 導電層      |    |

| 4 6 7 | 導電層      |    |

| 4 6 8 | 導電層      | 20 |

| 4 7 2 | 層間絶縁層    |    |

| 4 7 4 | 配線層      |    |

| 4 7 6 | 配線層      |    |

| 4 7 7 | 配線層      |    |

| 4 7 8 | 層間絶縁層    |    |

| 4 8 0 | 層間絶縁層    |    |

| 6 0 0 | 半導体基板    |    |

| 6 0 1 | 素子分離用絶縁膜 |    |

| 6 0 2 | 不純物領域    |    |

| 6 0 3 | 不純物領域    | 30 |

| 6 0 4 | ゲート絶縁層   |    |

| 6 0 5 | 配線層      |    |

| 6 0 6 | 配線層      |    |

| 6 0 7 | 不純物領域    |    |

| 6 0 8 | 不純物領域    |    |

| 6 0 9 | ゲート電極    |    |

| 6 1 0 | 層間絶縁層    |    |

| 6 1 1 | 配線層      |    |

| 6 1 2 | 配線層      |    |

| 6 1 3 | 配線層      | 40 |

| 6 1 4 | 配線層      |    |

| 6 2 0 | 層間絶縁層    |    |

| 6 2 1 | 配線層      |    |

| 6 2 2 | 配線層      |    |

| 6 2 3 | 配線層      |    |

| 6 2 4 | 配線層      |    |

| 6 3 0 | 層間絶縁層    |    |

| 6 3 1 | 配線層      |    |

| 6 3 2 | 配線層      |    |

| 6 3 3 | 配線層      | 50 |

|         |          |    |

|---------|----------|----|

| 6 3 4   | 配線層      |    |

| 6 4 0   | 層間絶縁層    |    |

| 6 4 1   | 配線層      |    |

| 6 4 2   | 配線層      |    |

| 6 4 3   | 配線層      |    |

| 6 5 0   | 層間絶縁層    |    |

| 6 5 1   | 半導体層     |    |

| 6 5 2   | 導電層      |    |

| 6 5 3   | ゲート絶縁層   |    |

| 6 5 4   | 導電層      | 10 |

| 6 5 5   | 導電層      |    |

| 6 5 6   | 導電層      |    |

| 6 5 7   | 導電層      |    |

| 6 5 9   | 導電層      |    |

| 6 6 0   | 導電層      |    |

| 6 6 1   | ゲート電極    |    |

| 6 6 2   | 導電層      |    |

| 6 6 3   | 配線層      |    |

| 7 0 0   | 電子部品     |    |

| 7 0 1   | リード      | 20 |

| 7 0 2   | プリント基板   |    |

| 7 0 3   | 半導体装置    |    |

| 7 0 4   | 実装基板     |    |

| 8 0 0   | 半導体基板    |    |

| 8 0 1   | 素子分離用絶縁膜 |    |

| 8 0 2   | 不純物領域    |    |

| 8 0 3   | ゲート絶縁層   |    |

| 8 0 4   | ゲート電極    |    |

| 8 0 5   | 配線層      |    |

| 8 1 0   | 層間絶縁層    | 30 |

| 8 2 0   | 層間絶縁層    |    |

| 8 2 1   | 配線層      |    |

| 8 2 2   | 配線層      |    |

| 8 2 3   | 配線層      |    |

| 8 3 0   | 層間絶縁層    |    |

| 8 3 1   | 配線層      |    |

| 8 4 0   | 層間絶縁層    |    |

| 8 4 1   | 配線層      |    |

| 8 4 2   | 配線層      |    |

| 8 5 0   | 層間絶縁層    | 40 |

| 8 5 1   | 半導体層     |    |

| 8 5 2   | 導電層      |    |

| 8 5 3   | ゲート絶縁層   |    |

| 8 5 4   | 導電層      |    |

| 8 5 5   | 導電層      |    |

| 8 5 6   | 導電層      |    |

| 9 0 1   | 筐体       |    |

| 9 0 2   | 筐体       |    |

| 9 0 3 a | 表示部      |    |

| 9 0 3 b | 表示部      | 50 |

|       |          |    |

|-------|----------|----|

| 9 0 4 | 選択ボタン    |    |

| 9 0 5 | キーボード    |    |

| 9 1 0 | 電子書籍     |    |

| 9 1 1 | 筐体       |    |

| 9 1 2 | 筐体       |    |

| 9 1 3 | 表示部      |    |

| 9 1 4 | 表示部      |    |

| 9 1 5 | 軸部       |    |

| 9 1 6 | 電源       |    |

| 9 1 7 | 操作キー     | 10 |

| 9 1 8 | スピーカー    |    |

| 9 2 0 | テレビジョン装置 |    |

| 9 2 1 | 筐体       |    |

| 9 2 2 | 表示部      |    |

| 9 2 3 | スタンド     |    |

| 9 2 4 | リモコン操作機  |    |

| 9 3 0 | 本体       |    |

| 9 3 1 | 表示部      |    |

| 9 3 2 | スピーカー    |    |

| 9 3 3 | マイク      | 20 |

| 9 3 4 | 操作ボタン    |    |

| 9 4 1 | 本体       |    |

| 9 4 2 | 表示部      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(b)

【図8】

(b)

(c)

【図9】

(b)

【図10】

(b)

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

(b)

【図20】

【図21】

【図22】

【図23】

【図24】

## 【図25】

【 図 2 6 】

【図27】

【 図 2 8 】

【図29】

【図30】

---

フロントページの続き

| (51)Int.Cl.              | F I                   |

|--------------------------|-----------------------|

| H 01 L 21/8242 (2006.01) | H 01 L 27/108 6 7 1 C |

| H 01 L 27/108 (2006.01)  | H 01 L 27/108 6 7 1 Z |

| G 11 C 11/412 (2006.01)  | G 11 C 11/412         |

(56)参考文献 特開2013-008437 (JP, A)

特開2012-256816 (JP, A)

特開2009-278115 (JP, A)

特開2011-142621 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| H 01 L | 21 / 8244 |

| G 11 C | 11 / 412  |

| H 01 L | 21 / 8239 |

| H 01 L | 21 / 8242 |

| H 01 L | 27 / 105  |

| H 01 L | 27 / 108  |

| H 01 L | 27 / 11   |

| H 01 L | 29 / 786  |