(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4492093号

(P4492093)

(45) 発行日 平成22年6月30日(2010.6.30)

(24) 登録日 平成22年4月16日(2010.4.16)

(51) Int.Cl.

H01S 5/323 (2006.01)

F 1

H01S 5/323

請求項の数 8 (全 10 頁)

(21) 出願番号 特願2003-366336 (P2003-366336)

(22) 出願日 平成15年10月27日 (2003.10.27)

(65) 公開番号 特開2005-129857 (P2005-129857A)

(43) 公開日 平成17年5月19日 (2005.5.19)

審査請求日 平成18年6月6日 (2006.6.6)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100122884

弁理士 角田 芳末

(74) 代理人 100113516

弁理士 磯山 弘信

(72) 発明者 矢吹 義文

宮城県白石市白鳥三丁目53番地の2 ソ

ニー白石セミコンダクタ株式会社内

審査官 土屋 知久

最終頁に続く

(54) 【発明の名称】半導体発光装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基体と、

上記基体上に設けられた第1導電型の第1クラッド層と、

上記第1導電型の第1クラッド層上に設けられた活性層と、

上記活性層上に設けられた第2導電型の第2クラッド層とを少なくとも有し、

上記第2クラッド層の上記基体側とは反対側の表面に、互いに対向する一対の第1の凹部と、該一対の第1の凹部の少なくとも一方の第1の凹部の他方の第1の凹部側とは反対側に形成された第2の凹部とが設けられ、該一対の第1の凹部間に主たる電流通路を構成するストライプ状のリッジが画成され、

該第1および第2の凹部は、それぞれ上記活性層に達することができる深さとされ、

上記第1の凹部の領域から上記第2の凹部の領域に渡って、その表面上に形成された第1導電型の電流ブロック層と、

該電流ブロック層上に形成された第2導電型のコンタクト層とを有し、

上記リッジの領域には、上記第1クラッド層、上記活性層及び上記第2クラッド層からなる半導体発光素子が構成され、上記主たる電流通路を通ずる電流により光を発光する発光部が形成され、

上記第2の凹部の領域には、上記第2導電型のコンタクト層、上記第1導電型の電流ブロック層、上記第2導電型のクラッド層、上記活性層及び上記第1導電型の第1クラッド層をこの順で積層してなるサイリスタ構造部が形成され、

10

20

上記サイリスタ構造部のオン電圧に応じて、少なくとも上記第2の凹部の深さが選定され、

上記第1の凹部と上記第2の凹部間に、上記ストライプ状リッジに沿って延在するストライプ状の境界リッジが形成されて成る

半導体発光装置。

【請求項2】

上記活性層が、多重量井戸構造による活性層である

請求項1に記載の半導体発光装置。

【請求項3】

上記サイリスタ構造部のオン電圧が、上記半導体発光素子の動作電圧より高い電圧である

10

請求項1に記載の半導体発光装置。

【請求項4】

上記サイリスタ構造部のオンの後の動作電圧が、上記半導体発光素子の動作電圧より低いか、または同程度である

請求項1に記載の半導体発光装置。

【請求項5】

上記サイリスタ構造部の面積が、上記リッジにおける主たる電流通路の面積より充分大に選定されて成る

請求項1に記載の半導体発光装置。

20

【請求項6】

基体上に、少なくとも、半導体発光素子を構成する第1導電型の第1クラッド層と、活性層と、第2導電型の第2クラッド層とをこの順でエピタキシャル成長する工程と、

上記第2クラッド層の上記基体側とは反対側の表面に、互いに対向する一対の第1の凹部を形成し、該一対の第1の凹部の間に主たる電流通路を構成するストライプ状のリッジが画成する工程と、

その後、またはその前に上記第1の凹部の少なくとも一方の上記リッジ側とは反対側に第2の凹部を形成する工程と、

上記第1および第2の凹部が形成されている表面上に、第1導電型の電流ブロック層と、第2導電型のコンタクト層とをこの順でエピタキシャル成長する工程と、

30

上記リッジ上に上記コンタクト層と上記電流ブロック層に渡る深さの凹部を形成して、さらに該凹部上に肉薄部を形成する工程と、

上記コンタクト層上から第2導電型の不純物を導入して上記肉薄部において、上記リッジの上記第2クラッド層に達するコンタクト部を形成する工程とを有し、

上記リッジの領域には、上記主たる電流通路を通ずる電流により光を発光する発光部が形成され、

上記第2の凹部の領域には、上記第2導電型のコンタクト層、上記第1導電型の電流ブロック層、上記第2導電型のクラッド層、上記活性層及び上記第1導電型の第1クラッド層をこの順で積層してなるサイリスタ構造部が形成され、

少なくとも上記第2の凹部の深さの選定によって上記サイリスタ構造部のオン電圧の設定がなされる

40

半導体発光装置の製造方法。

【請求項7】

上記活性層が、多重量井戸構造による活性層である

請求項6に記載の半導体発光装置の製造方法。

【請求項8】

上記第1の凹部と上記第2の凹部間に、上記ストライプ状リッジに沿って延在するストライプ状の境界リッジが形成されて成る

請求項6に記載の半導体発光装置の製造方法。

【発明の詳細な説明】

50

**【技術分野】****【0001】**

本発明は、例えば半導体レーザ、発光ダイオード等の半導体発光素子を有する半導体発光装置とその製造方法に関し、その半導体発光素子の破壊防止、例えば静電破壊防止を図り、その強度を飛躍的に改善する。

**【背景技術】****【0002】**

例えば半導体レーザ素子を有する半導体発光装置においては静電破壊、すなわち静電許容度が問題となる。

静電破壊は、半導体レーザ自体のショートと、瞬間的発光強度の増加による光出射端面の破壊とがある。 10

そして、一般に低消費電力、高効率等レーザの性能向上を目指した場合、静電許容度は低下する傾向にある。これは、しきいキャリア密度  $J_{th}$  の低下や、微分量子効率の向上によって、同等の静電気が発生した場合の半導体レーザに対するダメージが大きくなると考えられている。

上述した端面破壊については、この端面構造における光の集中を緩和するいわゆる窓構造とすることがなされるが、この破壊を含めて静電破壊を回避して静電許容度を高めるために、通常は、コンデンサや、ダイオード、およびサイリスタなどの保護素子を外部に接続する方法がとられている。

しかしながら、この場合、組立て工数、部品数の増加等によるコストの増加、大型化等の問題がある。 20

**【0003】**

これに対して、半導体発光素子を構成する基板に、保護回路を構成するサイリスタを作り込む構成の提案がなされている（例えば特許文献1参照）。

しかしながら、この構成による半導体発光素子は、複雑な構成とされ、多数の半導体層の積層構造を有し、また、サイリスタのオン電圧等の特性が、半導体発光素子の特性に関与し、その選定の自由度が小さい。

**【0004】**

ところが、例えば半導体発光素子において、その活性層を多重量子井戸構造とする場合、単層構造である場合に比し、そのオン電圧が高くなるなど、特性が変化するものであり、これに応じてサイリスタのオン電圧  $V_{on}$  の設計値を変える必要が生じる。 30

【特許文献1】特開平5-67849号公報、図1。

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

本発明は、目的とする半導体発光素子の構成半導体層数を増加することなく、また特段の製造方法によることなく、半導体発光素子とともにいわゆる静電破壊、不慮の過電流による破壊等を防止するサイリスタを作り込むことができ、しかも、このサイリスタのオン電圧等の特性の選定を、半導体発光素子の特性の設定に殆ど関与しないで、高い自由度をもって選定することができる半導体発光装置とその製造方法を提供するものである。 40

**【課題を解決するための手段】****【0006】**

本発明による半導体発光装置は、基体と、基体上に設けられた第1導電型の第1クラッド層と、第1導電型の第1クラッド層上に設けられた活性層と、活性層上に設けられた第2導電型の第2クラッド層とを少なくとも有し、第2クラッド層の基体側とは反対側の表面に、互いに対向する一対の第1の凹部と、該一対の第1の凹部の少なくとも一方の第1の凹部の他方の第1の凹部側とは反対側に形成された第2の凹部とが設けられ、この一対の第1の凹部間に主たる電流通路を構成するストライプ状のリッジが画成され、この第1および第2の凹部は、それぞれ上記活性層に達することができない深さとされ、第1の凹部の領域から第2の凹部の領域に渡って、その表面上に形成された第1導電型の電流ブロック 50

層と、この電流ブロック層上に形成された第2導電型のコンタクト層とを有し、リッジの領域には、第1クラッド層、活性層及び第2クラッド層からなる半導体発光素子が構成され、主たる電流通路を通ずる電流により光を発光する発光部が形成され、第2の凹部の領域には、上記第2導電型のコンタクト層、第1導電型の電流ブロック層、第2導電型のクラッド層、活性層及び第1導電型の第1クラッド層をこの順で積層してなるサイリスタ構造部が形成され、サイリスタ構造部のオン電圧に応じて、少なくとも第2の凹部の深さが選定され、第1の凹部と第2の凹部間に、ストライプ状リッジに沿って延在するストライプ状の境界リッジが形成されて成ることを特徴とする。

#### 【0007】

また、本発明による半導体発光装置にあって、その活性層が、多重量子井戸(MQW)構造とし得るものである。10

また、サイリスタ構造部のオン電圧は、半導体発光素子の動作電圧より高い電圧とする。

また、サイリスタ構造部のオンの後の動作電圧は、半導体発光素子の動作電圧より低いか、または同程度とする。

また、サイリスタ構造部の面積は、リッジにおける主たる電流通路の面積より充分大に選定される。

#### 【0008】

また、本発明による半導体発光装置の製造方法は、基体上に、少なくとも、半導体発光素子を構成する第1導電型の第1クラッド層と、活性層と、第2導電型の第2クラッド層とをこの順でエピタキシャル成長する工程と、第2クラッド層の基体側とは反対側の表面上に、互いに対向する一対の第1の凹部を形成し、該一対の第1の凹部の間に主たる電流通路を構成するストライプ状のリッジが画成する工程と、その後、またはその前に上記第1の凹部の少なくとも一方のリッジ側とは反対側に第2の凹部を形成する工程と、第1および第2の凹部が形成されている表面上に、第1導電型の電流ブロック層と、第2導電型のコンタクト層とをこの順でエピタキシャル成長する工程と、リッジ上にコンタクト層と電流ブロック層に渡る深さの凹部を形成して、さらに該凹部上に肉薄部を形成する工程と、コンタクト層上から第2導電型の不純物を導入して上記肉薄部において、リッジの上記第2クラッド層に達するコンタクト部を形成する工程とを有し、リッジの領域には、主たる電流通路を通ずる電流により光を発光する発光部が形成され、第2の凹部の領域には、上記第2導電型のコンタクト層、第1導電型の電流ブロック層、第2導電型のクラッド層、活性層及び第1導電型の第1クラッド層をこの順で積層してなるサイリスタ構造部が形成され、少なくとも上記第2の凹部の深さの選定によって上記サイリスタ構造部のオン電圧の設定がなされることを特徴とする。2030

#### 【発明の効果】

#### 【0009】

上述の本発明による半導体発光装置によれば、リッジを形成する第1の凹部の外側に、第2の凹部が形成され、この第2の凹部に渡ってリッジに電流通路を割成するためのブロック層を埋め込み、更にこの上にコンタクト層を形成することによって、半導体発光素子の構成半導体層をもって、第2の凹部において、第1導電型と第2導電型の繰り返しによるサイリスタが構成され、活性層が多重量子井戸構造による場合、この活性層をQと表示すると、P N P Q N構造のサイリスタが構成される。40

そして、このサイリスタと、半導体発光素子とは、電気的に並列構成を有することから、サイリスタのオン電圧を、適当に選定することによって半導体発光素子に異常な電圧が印加された場合に、それ以前において、サイリスタをオンさせて半導体発光素子の破壊を効果的に防止することができるものである。

#### 【0010】

そして、本発明構成によれば、このサイリスタのオン電圧 $V_{on}$ は、第2の凹部の深さによって制御することができるので、特に活性層が多重量子井戸構造による場合におけるように、その構成によって、その破壊電圧が相違してくることから、その保護を行うサイ50

リスタのオン電圧も、これに応じて設計されることが必要であるが、この本発明構造によれば、第2の凹部の選定によって、オン電圧の選定ができることから、半導体発光素子自体の特性に影響を及ぼすことなく、またオン電圧の制御を行うための特段の半導体層を付加する必要も回避される。

#### 【0011】

更に、上述したように、第1および第2の凹部間に、境界リッジが形成された構造とする場合、すなわち第2の凹部をリッジ溝構造とするときは、より発光素子部分の特性がサイリスタ部分によって影響を受けること、例えばサイリスタのオン時の影響を回避することができる。

#### 【0012】

また、このサイリスタ構造部の面積が、リッジ部における主たる電流通路部の面積より充分にできるだけ大に選定することによって、このサイリスタがオンしたときには、このサイリスタにより多くの電流が流れるようにすることができ、より半導体発光素子、例えば半導体レーザの静電破壊強度を高めることができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

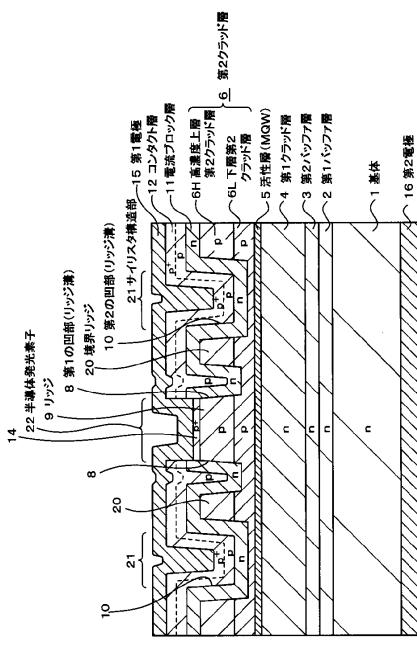

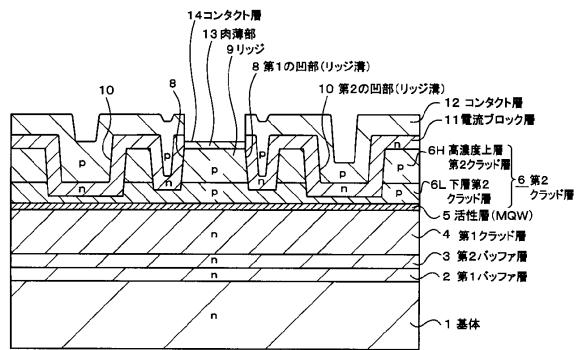

本発明による半導体発光装置の実施する形態例を、図1の概略断面図を参照して説明する。

しかしながら、本発明は、この例に限定されるものではない。

A1GaAs系の例えれば780nm帯の半導体レーザ装置に適用する場合を例示すると、この場合、基体1は、第1導電型の例えればn型のGaAs基板上に、第1導電型のn型のバッファ層、図示の例では、2層の例えればGaAsのバッファ層2およびA1GaAsによる第2のバッファ層3と、第1導電型のn型のA1GaAsによる第1クラッド層4と、GaAsとA1GaAsとの繰り返し積層の多重量子井戸(MQW)構造による活性層5と、それぞれ第2導電型の例えればp型の下層第2クラッド層6Lと、その上に、高濃度の上層第2クラッド層6Hとが積層された第2クラッド層6とを有する。

#### 【0014】

そして、第2クラッド層6側から、主たる電流通路を構成するストライプ状のリッジ9を形成する相対向する対の第1の凹部8を構成する例えればリッジ溝と、この第1の凹部8の少なくとも一方、例えれば両外側に第2の凹部10を構成する例えればリッジ溝とが設けられる。

これら第1および第2の凹部8および10は、それぞれ活性層5に達することができない深さとされ、凹部10の深さは、例えれば高濃度の上層第2クラッド層7を横切る深さに形成される。

このようにして、第1の凹部8と上記第2の凹部10間に、ストライプ状リッジ9に沿って延在するストライプ状の境界リッジ20が形成される。

#### 【0015】

そして、これら第1および第2の凹部8および10内に差し渡って第1導電型のn型の電流ブロック層11と、この電流ブロック層11上に形成された第2導電型のp型のコンタクト層12とが形成される。

この構成によって、活性層5において、主たる電流通路を通ずる電流による発光部が形成されるようになされ、同時に、第2の凹部10において、その上下に配置された第2導電型のp型のコンタクト層12、第1導電型のn型の電流ブロック層11、第2導電型のp型のクラッド層6Hおよび6L、多重量子井戸構造の活性層(MQW)、それぞれ第1導電型のn型の第1のクラッド層4、バッファ層3および2、および基体1との積層によるPNPQNスイッチング素子、すなわちサイリスタ構造部21が形成される。

このサイリスタ構造部21のオン電圧V<sub>on</sub>は、電流ブロック層11の不純物濃度および厚さ、コンタクト層12の不純物濃度等の設定に応じて、第2の凹部10の深さの選定によって選定される。

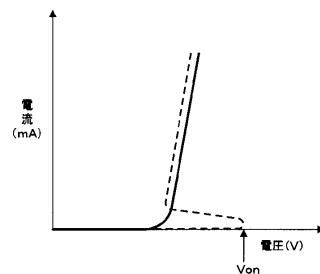

#### 【0016】

この構成による本発明半導体発光装置における、リッジ9における主たる電流通路が形成された本来の半導体発光素子22と、P N P Q N構造部21のそれぞれの電流・電圧特性を、図2において、実線および破線によって示すように、サイリスタのオン電圧V<sub>on</sub>は、半導体発光素子の動作に干渉しない程度で、半導体発光素子のしきい値電圧V<sub>th</sub>またはその動作電圧V<sub>op</sub>に近い値に選定する。

例えば半導体発光素子の動作電圧V<sub>op</sub>が3Vのとき、V<sub>on</sub>は、4V～10V程度となるようにし、サイリスタのオンの後の動作電圧が、半導体発光素子の動作電圧V<sub>op</sub>より低いか、または同程度とすることによって確実に、半導体発光素子に静電破壊が生じないようにする。

さらに、上述したサイリスタ構造部の面積は、リッジ9における主たる電流通路部の面積より充分大に選定される。 10

#### 【0017】

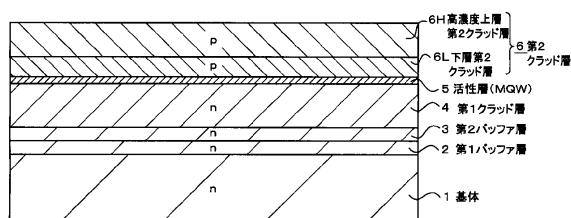

次に、本発明による半導体発光装置の製造方法の1実施形態の例を図3～図6の工程図を参照して説明する。

この例では、図1で説明した構造の発光半導体装置を製造する場合で、先ず、図3に示すように、基体1、例えば第1導電型例えばn型のGaAs基板を用意し、この基体1上に、順次第1の導電型のn型のGaAsによる例えば厚さ5000の第1バッファ層2、同様の第1導電型のn型のAlGaAsによる例えば厚さ5000の第2バッファ層3、第1導電型のn型の例えば厚さ2μmのAl<sub>x</sub>Ga<sub>1-x</sub>Asによる第1クラッド層4、活性層5、第2導電型のp型の例えば厚さ4000のAl<sub>x</sub>Ga<sub>1-x</sub>Asによる第2のクラッド層6、高不純物濃度の第2導電型のp型の例えば厚さ1μmのAl<sub>x</sub>Ga<sub>1-x</sub>Asによる高濃度第2クラッド7を例えばMOCVD(Metal Organic Chemical Vapor Deposition)によってエピタキシャル成長する第1のエピタキシャル成長工程を行う。 20

#### 【0018】

活性層5は、前述したように、例えばAlGa層とAlGaAs層との繰り返し積層による多重量子井戸構造(以下MQWという)によって構成することができる。

また、いわゆるSCH(Separate Confinement Heterostructure)構造とする場合においては、この活性層5を挟んでその上下にガイド層をエピタキシャル成長する。 30

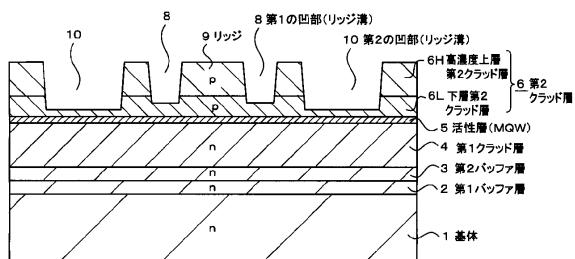

#### 【0019】

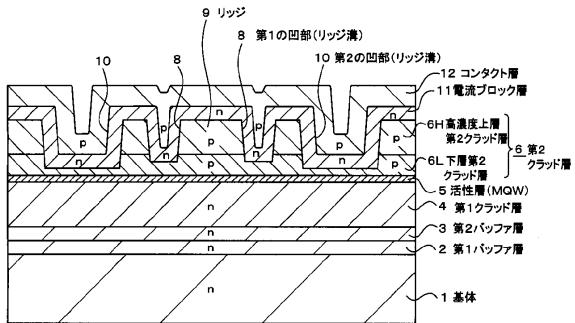

次に、図4に示すように、高濃度上層第2クラッド層6Hを横切って、クラッド6Hに比しては低不純物濃度の下層の第2クラッド層6Lに至る深さの対の第1のリッジ溝8を、フォトリソグラフィによるマスクを用いてRIE(Reactive Ion Etching)等によってパターンエッチングして、これらリッジ溝8間に、主たる電流通路を形成するリッジ9を形成する。

また、リッジ溝8の外側に、例えば対の第2のリッジ溝10を、同様に例えばRIEによって、第1のリッジ溝8に沿って形成する。

#### 【0020】

図5に示すように、高濃度第2クラッド層6H上に、リッジ溝8および10内を含んで例えばMOCVDによって第1導電型のn型の例えばAlGaAsによる例えば厚さ600の電流ブロック層11と、高不純物濃度の第2導電型のp型の例えば厚さ900のGaAsによるコンタクト層12とを順次エピタキシャル成長する第2のエピタキシャル成長工程を行う。 40

#### 【0021】

次に、図6に示すように、リッジ9上のコンタクト層12および電流ブロック層11の積層部を所要の深さに、例えばRIEによるフォトリソグラフィによるパターンエッチングして、リッジ9上に肉薄部13を形成する。

その後、図1に示すように、コンタクト層12上から第2導電型のp型の不純物例えばZnを全面的に例えば500の厚さに拡散して、肉薄部13を高濃度の第2導電型の 50

p型としてコンタクト層14を形成する。

そして、コンタクト層14および12上に例えば全面的に例えばTi/Pt/Auの積層による第1電極15をオーミックに被着形成し、基体1の裏面に例えばAu/Ni/Auの積層による第2電極16をオーミックに被着する。

#### 【0022】

このようにして、図1に示したように、リッジ9において、目的とする半導体レーザすなわち半導体発光素子が形成され、その両脇の第2の凹部10において、サイリスタ構造部21が形成される。

#### 【0023】

上述した本発明製造方法においては、凹部10の形成において、その深さをサイリスタ構造部21で設定されるべき深さ、すなわち、予めそのサイリスタのオン電圧 $V_{on}$ の選定を行う予め設計された深さに形成するものであり、この第2の凹部10の深さの規定は、例えば上述した第1のエピタキシャル成長工程において凹部10の深さ位置、例えばクラッド層6のエピタキシャル成長の過程で、その所定位置に、凹部10を形成するエッチングに対してエッチング速度が充分低い、例えばp型のエッチングストップ層を予め形成しておき、エッチング停止制御を容易にする方法を探ることができる。10

あるいはクラッド層6の不純物濃度、活性層5のMQW構成、および電流ブロック層11の不純物濃度に応じてエッチング時間を制御するなどの方法を探ることができる。

#### 【0024】

尚、本発明による半導体発光装置は、単体半導体発光素子を有する場合に限られるものではなく、複数の半導体発光素子を有する半導体発光装置、あるいは半導体発光素子と共に、他の回路素子を有する集積回路構成とするなど種々の構成によることができる。20

そして、これら半導体発光装置は、多数個同時に基体1に形成して、ペレッタイズによつて同時に多数個の半導体発光装置を得るようにすることは言うまでもない。。

#### 【0025】

上述においては、AlGaAs系の例えば波長780nm帯のCD(Co mpact Disc)用の半導体レーザを有する半導体発光装置を例示したが、例えばDVD(Digital Versatile Disc)用の光源としての例えば波長650nm帯の半導体発光素子、例えばAlGaNP系の半導体レーザによる半導体発光装置に適用することができる。更に、例えば異なる2つ以上の波長例えば上述した波長780nm帯の発光素子と、例えば波長650nm帯の発光素子が共通の基体上に配列形成された構成に適用してサイリスタ構造部を形成することもできるなど、上述した例に限定されるものではなく、本発明を逸脱することなく、種々の変形変更によるものである。30

#### 【図面の簡単な説明】

#### 【0026】

【図1】本発明による半導体発光装置の一例の概略断面図である。

【図2】本発明による半導体発光装置の特性の説明に供する半導体発光素子と、サイリスタ構造部の電流 電圧特性曲線図である。

【図3】本発明による半導体発光装置の製造方法の一例の一工程における要部の概略断面図である。40

【図4】本発明による半導体発光装置の製造方法の一例の一工程における要部の概略断面図である。

【図5】本発明による半導体発光装置の製造方法の一例の一工程における要部の概略断面図である。

【図6】本発明による半導体発光装置の製造方法の一例の一工程における要部の概略断面図である。

#### 【符号の説明】

#### 【0027】

1・・・基体、2・・・第1バッファ層、3・・・第2バッファ層、4・・・第1クラ

50

ツド層、5・・・活性層、6・・・第2クラッド層、6L・・・下層第2クラッド層、6H・・・高濃度上層第2クラッド層、8・・・第1リッジ溝、9・・・リッジ、10・・・第2リッジ溝、11・・・電流ブロック層、12・・・コンタクト層、13・・・肉薄部、14・・・コンタクト層、15・・・第1電極、16・・・第2電極、20・・・境界リッジ、21・・・サイリスタ構造部、22・・・半導体発光素子

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

---

フロントページの続き

(56)参考文献 特開平04-023379(JP,A)

特開平02-283088(JP,A)

特開平11-074624(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50