(12) 发明专利

(10) 授权公告号 CN 109844184 B

(45) 授权公告日 2021.11.30

(21) 申请号 201780049691.6

(22) 申请日 2017.06.13

(65) 同一申请的已公布的文献号

申请公布号 CN 109844184 A

(43) 申请公布日 2019.06.04

(30) 优先权数据

62/350,084 2016.06.14 US

62/350,077 2016.06.14 US

(85) PCT国际申请进入国家阶段日

2019.02.13

(86) PCT国际申请的申请数据

PCT/US2017/037252 2017.06.13

(87) PCT国际申请的公布数据

W02017/218536 EN 2017.12.21

(73) 专利权人 克罗米斯有限公司

地址 美国加利福尼亚州

(72) 发明人 弗拉基米尔·奥德诺博柳多夫

杰姆·巴斯切里 莎丽·法伦斯

(74) 专利代理机构 广州华进联合专利商标代理

有限公司 44224

代理人 景怀宇

(51) Int.CI.

C30B 25/14 (2006.01)

H01L 21/30 (2006.01)

H01L 21/8234 (2006.01)

H01L 29/16 (2006.01)

H01L 29/20 (2006.01)

H01L 29/267 (2006.01)

(56) 对比文件

US 2011117726 A1, 2011.05.19

CN 1809916 A, 2006.07.26

CN 102456721 A, 2012.05.16

CN 1967848 A, 2007.05.23

CN 101621005 A, 2010.01.06

CN 101192533 A, 2008.06.04

CN 102044473 A, 2011.05.04

US 4430149 A, 1984.02.07

US 2010006857 A1, 2010.01.14

US 2012052635 A1, 2012.03.01

US 7732301 B1, 2010.06.08

US 2014021483 A1, 2014.01.23

US 2013234148 A1, 2013.09.12

WO 2016002803 A1, 2016.01.07

审查员 游巧

权利要求书3页 说明书11页 附图10页

(54) 发明名称

用于功率应用和射频应用的工程化衬底结

构

(57) 摘要

一种衬底，所述衬底包括支撑结构，该支撑结构包括：多晶陶瓷芯；第一粘附层，其耦合到多晶陶瓷芯；导电层，其耦合到第一粘附层；第二粘附层，其耦合到导电层；和阻挡层，其耦合到第二粘附层。所述衬底还包括：氧化硅层，其耦合到支撑结构；实质单晶硅层，其耦合到氧化硅层；和外延III-V层，其耦合到实质单晶硅层。

CN 109844184 B

1. 一种衬底, 包括:

支撑结构, 所述支撑结构包括: 多晶陶瓷芯、第一粘附层、导电层、第二粘附层和阻挡层, 其中:

所述第一粘附层形成在所述多晶陶瓷芯上;

所述导电层形成在所述第一粘附层上;

所述第二粘附层形成在所述导电层上; 和

所述阻挡层围绕所述第二粘附层形成;

氧化硅层, 其接合到所述阻挡层;

单晶硅层, 其接合到所述氧化硅层; 和

外延III-V层, 其形成在所述单晶硅层上。

2. 根据权利要求1所述的衬底, 其中所述多晶陶瓷芯包括氮化铝。

3. 根据权利要求2所述的衬底, 其中所述外延III-V层包括外延氮化镓层。

4. 根据权利要求3所述的衬底, 其中所述外延氮化镓层具有 $5\mu\text{m}$ 或更大的厚度。

5. 根据权利要求1所述的衬底, 其中所述单晶硅层包括厚度为 $0.5\mu\text{m}$ 的剥离硅层。

6. 根据权利要求1所述的衬底, 其中所述单晶硅层包括剥离硅层和在所述剥离硅层上生长的外延硅层, 并且所述单晶硅层具有 $0.5\mu\text{m}$ 的厚度。

7. 根据权利要求2所述的衬底, 其中:

所述第一粘附层包括封装所述多晶陶瓷芯的第一原硅酸四乙酯(TEOS)层;

所述导电层包括封装所述第一原硅酸四乙酯(TEOS)层的多晶硅层;

所述第二粘附层包括封装所述多晶硅层的第二TEOS层; 和

所述阻挡层包括封装所述第二TEOS层的氮化硅层。

8. 根据权利要求7所述的衬底, 其中:

所述第一原硅酸四乙酯(TEOS)层具有 $1000\text{\AA}$ 的厚度;

所述多晶硅层具有 $3000\text{\AA}$ 的厚度;

所述第二TEOS层具有 $1000\text{\AA}$ 的厚度; 和

所述氮化硅层具有 $4000\text{\AA}$ 的厚度。

9. 一种制造衬底的方法, 所述方法包括:

形成支撑结构, 所述支撑结构通过以下步骤形成:

提供多晶陶瓷芯;

将所述多晶陶瓷芯封装在第一粘附壳中;

将所述第一粘附壳封装在导电壳中;

将所述导电壳封装在第二粘附壳中; 和

将所述第二粘附壳封装在阻挡壳中;

将键合层接合到所述支撑结构;

将单晶硅层接合到所述键合层;

通过在所述单晶硅层上外延生长来形成外延硅层; 和

通过在所述外延硅层上外延生长来形成外延III-V层。

10. 根据权利要求9所述的方法, 还包括形成从所述外延III-V层通到所述外延硅层的

多个过孔。

11. 根据权利要求9所述的方法,其中所述外延III-V层包括氮化镓。

12. 根据权利要求9所述的方法,其中:

所述第一粘附壳包括第一原硅酸四乙酯(TEOS)壳;

所述导电壳包括多晶硅壳;

所述第二粘附壳包括第二TEOS壳;

所述阻挡壳包括氮化硅壳;和

所述键合层包括氧化硅。

13. 根据权利要求12所述的方法,其中:

所述第一原硅酸四乙酯(TEOS)壳包括单层TEOS;

所述多晶硅壳包括单层多晶硅;

所述第二TEOS壳包括单层TEOS;和

所述氮化硅壳包括单层氮化硅。

14. 一种工程化衬底结构,包括:

支撑结构,所述支撑结构包括:多晶陶瓷芯、第一粘附层、导电层、第二粘附层和阻挡壳,其中:

所述第一粘附层形成在所述多晶陶瓷芯上;

所述导电层形成在所述第一粘附层上;

所述第二粘附层形成在所述导电层上;和

所述阻挡壳围绕所述第二粘附层形成;

键合层,其接合到所述支撑结构;

单晶硅层,其接合到所述键合层;和

外延单晶硅层,其形成在所述单晶硅层上。

15. 根据权利要求14所述的工程化衬底结构,其中:

所述多晶陶瓷芯包括多晶氮化镓;

所述第一粘附层包括原硅酸四乙酯(TEOS);

所述导电层包括多晶硅;

所述第二粘附层包括TEOS;

所述阻挡壳包括氮化硅;和

所述键合层包括氧化硅。

16. 根据权利要求14所述的工程化衬底结构,还包括形成在所述外延单晶硅层上的外延III-V层。

17. 根据权利要求16所述的工程化衬底结构,还包括从所述外延III-V层通到所述外延单晶硅层的多个过孔。

18. 根据权利要求14所述的工程化衬底结构,还包括设置在所述单晶硅层和所述外延单晶硅层之间的一个或多个缓冲层。

19. 根据权利要求14所述的工程化衬底结构,其中所述外延单晶硅层是有应变的。

20. 根据权利要求14所述的工程化衬底结构,其中所述外延单晶硅层的特征在于厚度在 $1\mu\text{m}$ 至 $20\mu\text{m}$ 范围内。

21. 一种衬底，包括：

多晶陶瓷芯；

第一粘附层，其封装所述多晶陶瓷芯；

导电层，其封装第一粘附层；

第二粘附层，其封装所述导电层；

阻挡层，其封装所述第二粘附层；

键合层，其接合到所述阻挡层的；和

单晶硅层，其接合到所述键合层。

22. 根据权利要求21所述的衬底，其中所述多晶陶瓷芯包括多晶氮化铝。

23. 根据权利要求21所述的衬底，其中所述第一粘附层包括原硅酸四乙酯(TEOS)。

24. 根据权利要求21所述的衬底，其中所述第一粘附层具有1000Å的厚度。

25. 根据权利要求21所述的衬底，其中所述导电层包括多晶硅。

26. 根据权利要求21所述的衬底，其中所述导电层具有3000Å的厚度。

27. 根据权利要求21所述的衬底，其中所述第二粘附层包括原硅酸四乙酯(TEOS)。

28. 根据权利要求21所述的衬底，其中所述第二粘附层具有1000Å的厚度。

29. 根据权利要求21所述的衬底，其中所述阻挡层包括氮化硅。

30. 根据权利要求21所述的衬底，其中所述阻挡层具有4000Å的厚度。

31. 根据权利要求21所述的衬底，其中所述单晶硅层包括剥离硅层。

32. 根据权利要求21所述的衬底，其中所述单晶硅层具有0.5μm的厚度。

33. 一种制造衬底的方法，所述方法包括：

提供多晶陶瓷芯；

将所述多晶陶瓷芯封装在第一粘附壳中；

将所述第一粘附壳封装在导电壳中；

将所述导电壳封装在第二粘附壳中；

将所述第二粘附壳封装在阻挡壳中；

将键合层接合到所述阻挡壳；和

将单晶硅层接合到所述键合层。

34. 根据权利要求33所述的方法，其中所述多晶陶瓷芯包括多晶氮化铝。

35. 根据权利要求33所述的方法，其中所述第一粘附壳包括原硅酸四乙酯(TEOS)。

36. 根据权利要求33所述的方法，其中所述导电壳包括多晶硅。

37. 根据权利要求33所述的方法，其中所述第二粘附壳包括原硅酸四乙酯(TEOS)。

38. 根据权利要求33所述的方法，其中所述阻挡壳包括氮化硅。

39. 根据权利要求33所述的方法，其中接合所述单晶硅层包括从绝缘体上硅晶片执行层转移工艺。

40. 根据权利要求39所述的方法，还包括平滑所述单晶硅层。

## 用于功率应用和射频应用的工程化衬底结构

[0001] 相关联申请的交叉引用

[0002] 本申请要求2016年6月14日提交的名称为“用于功率应用和射频应用的工程化衬底结构”的第62/350,084号美国临时专利申请,和2016年6月14日提交的名称为“工程化衬底结构和制造方法”的第62/350,077号美国临时专利申请的优先权。它们的全部内容通过引用而并入本文以用于所有目的。

[0003] 以下两个美国专利申请与本申请同时提交,并且这两个申请的全部公开内容通过引用而并入本文以用于所有目的:

[0004] 2017年6月13日提交的名称为“用于功率和射频应用的工程化衬底结构”的第15/621,335号申请(律师案号No. 098825-1049529-001110US),以及

[0005] 2017年6月13日提交的名称为“工程化衬底结构和制造方法”的第15/621,338号申请(律师案卷号098825-1049532-001610US)。

### 背景技术

[0006] 发光二极管(LED)结构通常是在蓝宝石衬底上外延生长的。目前许多产品使用LED器件,包括照明、计算机监视器和其它显示器件。

[0007] 由于衬底和外延层由不同材料构成,因此蓝宝石衬底上的氮化镓基LED结构的生长是异质外延生长过程。由于异质外延生长过程,外延生长的材料会表现出各种不利影响,包括均匀性的降低和与外延层的电子/光学性质相关联的量度的减小。因此,本领域需要与外延生长过程和衬底结构有关的改进的方法和系统。

### 发明内容

[0008] 本发明通常涉及一种工程化衬底结构。更具体地,本发明涉及适合用于外延生长过程的方法和系统。仅通过示例,本发明已经应用在用于提供适合于外延生长的衬底结构的方法和系统,所述衬底结构的特征是具有实质上与在其上生长的外延层匹配的热膨胀系数(CTE)。该方法和技术可以应用于各种半导体处理操作。

[0009] 根据本发明的实施例,提供了一种衬底。所述衬底包括支撑结构,所述支撑结构包括:多晶陶瓷芯;第一粘附层,其耦合到所述多晶陶瓷芯;导电层,其耦合到所述第一粘附层;第二粘附层,其耦合到所述导电层;和阻挡层,其耦合到所述第二粘附层。所述衬底还包括:氧化硅层,其耦合到所述支撑结构;实质单晶硅层,其耦合到所述氧化硅层;和外延III-V层,其耦合到所述实质单晶硅层。

[0010] 根据本发明的另一个实施例,提供了一种制造衬底的方法。该方法包括通过以下方式形成支撑结构:提供多晶陶瓷芯;将所述多晶陶瓷芯封装在第一粘附壳中;将所述第一粘附壳封装在导电壳中;将所述导电壳封装在第二粘附壳中;和将所述第二粘附壳封装在阻挡壳中。该方法还包括:将键合层接合到所述支撑结构;将实质单晶硅层接合到所述键合层,通过在所述实质单晶硅层上外延生长形成外延硅层;和通过在所述外延硅层上外延生长形成外延III-V层。

[0011] 根据本发明的具体实施例，提供了一种工程化衬底结构。工程化衬底结构包括支撑结构，键合层，其耦合到所述支撑结构，实质单晶硅层，其耦合到所述粘附层；和外延单晶硅层，其耦合到所述实质单晶硅层。所述支撑结构包括：多晶陶瓷芯；第一粘附层，其耦合到所述多晶陶瓷芯；导电层，其耦合到所述第一粘附层；第二粘附层，其耦合到所述导电层；和阻挡壳，其耦合到所述第二粘附层。

[0012] 优于传统技术，通过本发明可实现许多益处。例如，本发明的实施例提供了一种工程化衬底结构，其与适用于光学、电子和光电应用的氮化镓基外延层CTE匹配。用作工程化衬底结构的部件的封装层阻止存在于衬底中心部分中的杂质扩散到达使用工程化衬底的半导体工艺环境。与衬底材料相关联的关键性质（包括热膨胀系数、晶格失配、热稳定性和形貌控制）是独立进行工程化的，用以改善（例如，优化）与氮化镓基外延层和器件层的匹配，以及与不同的设备架构和性能目标的匹配。因为在传统的半导体制造工艺中衬底材料层是集成在一起的，所以简化了工艺集成。结合下文和附图更详细地描述本发明的这些和其它实施例及其许多优点和特征。

[0013] 附图的简要说明

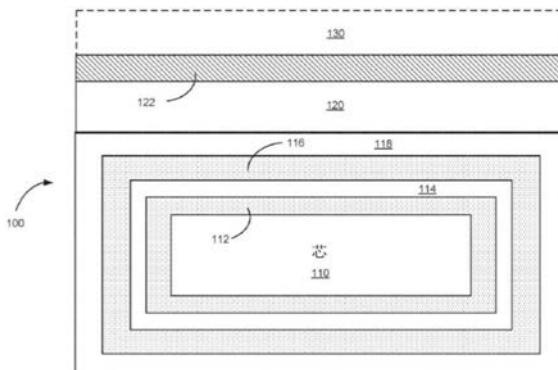

[0014] 图1是示出了根据本发明的实施例的工程化衬底结构的简化示意图。

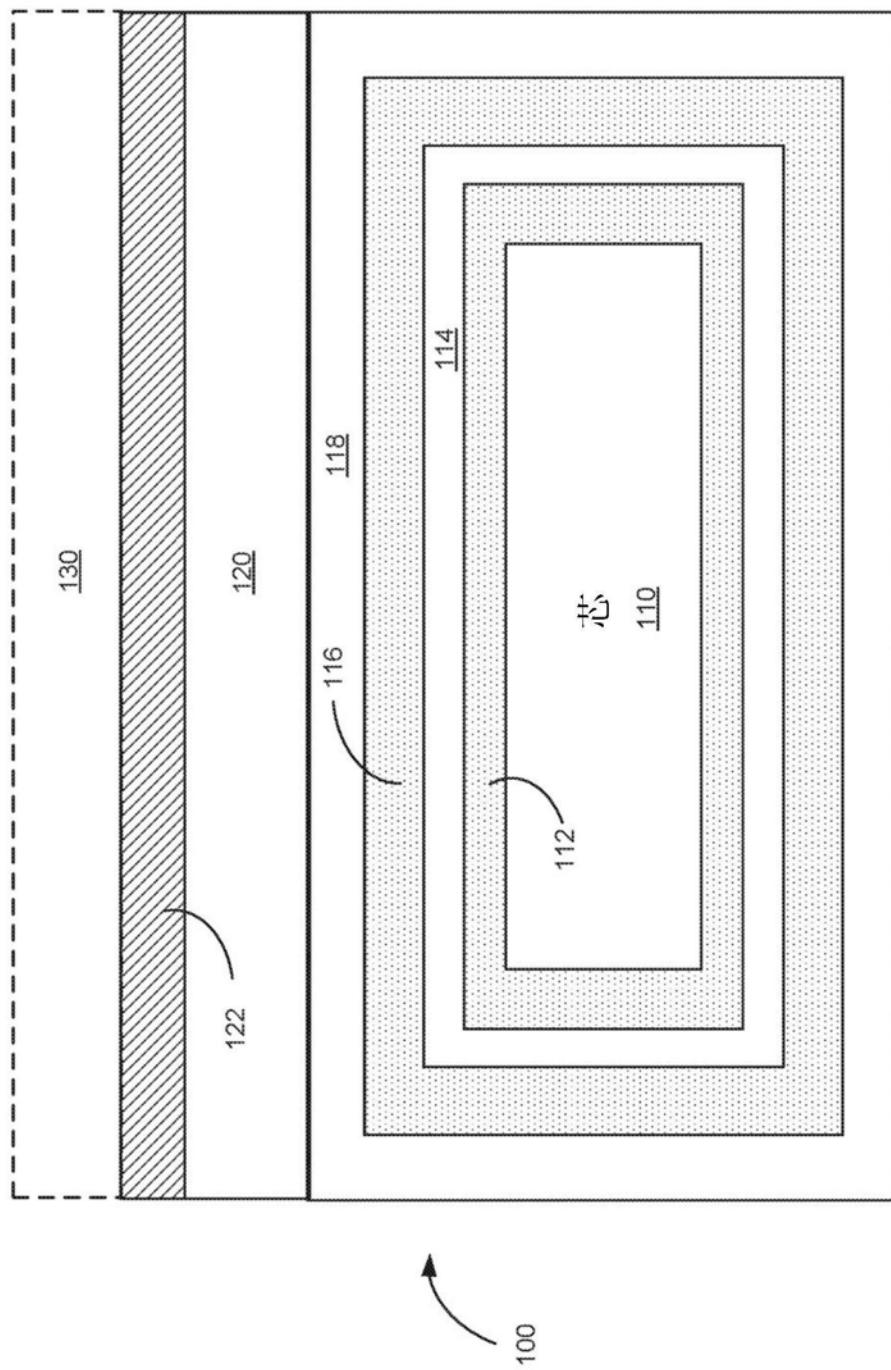

[0015] 图2A是示出了根据本发明实施例的工程化结构的物质浓度作为深度的函数的SIMS分布图。

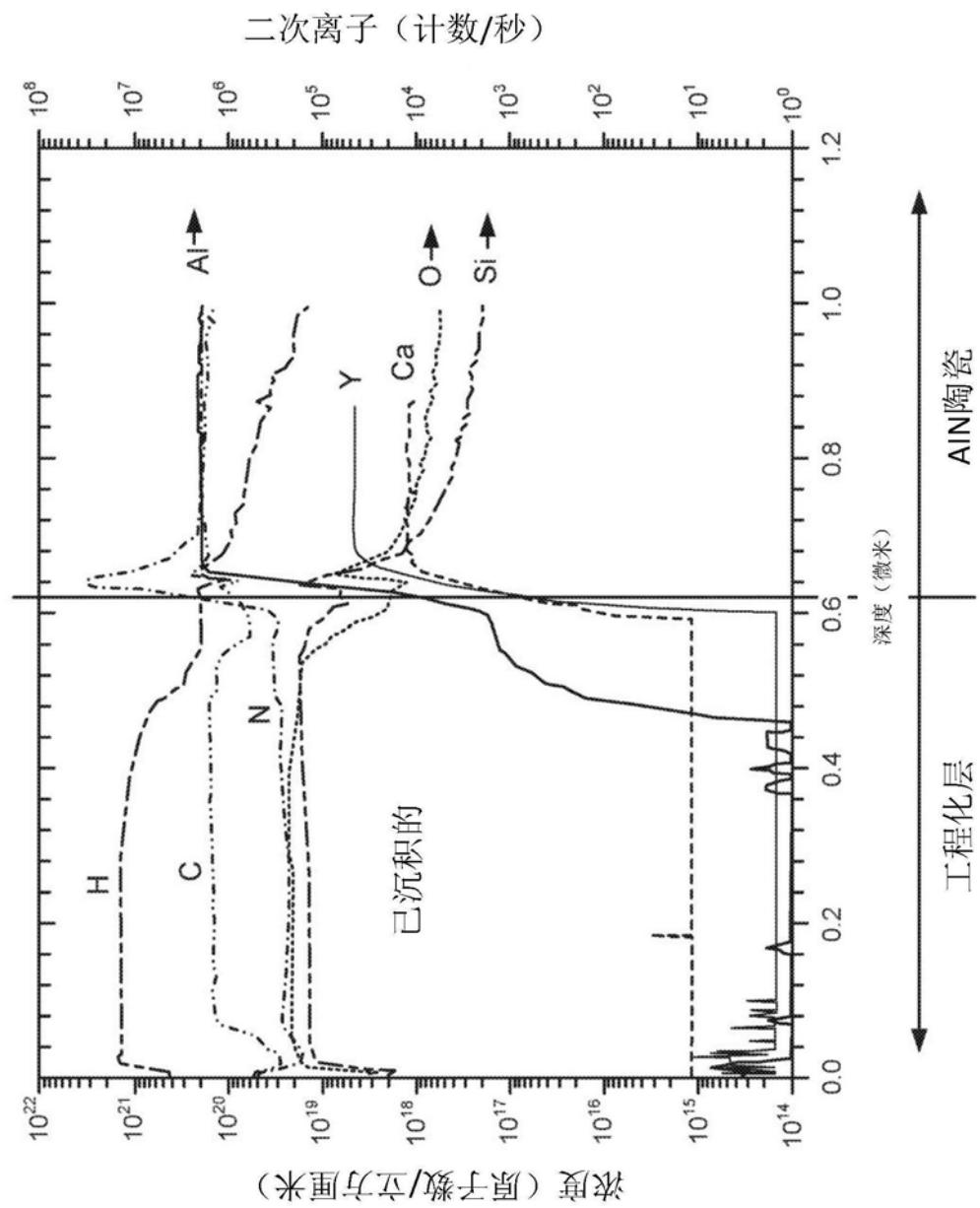

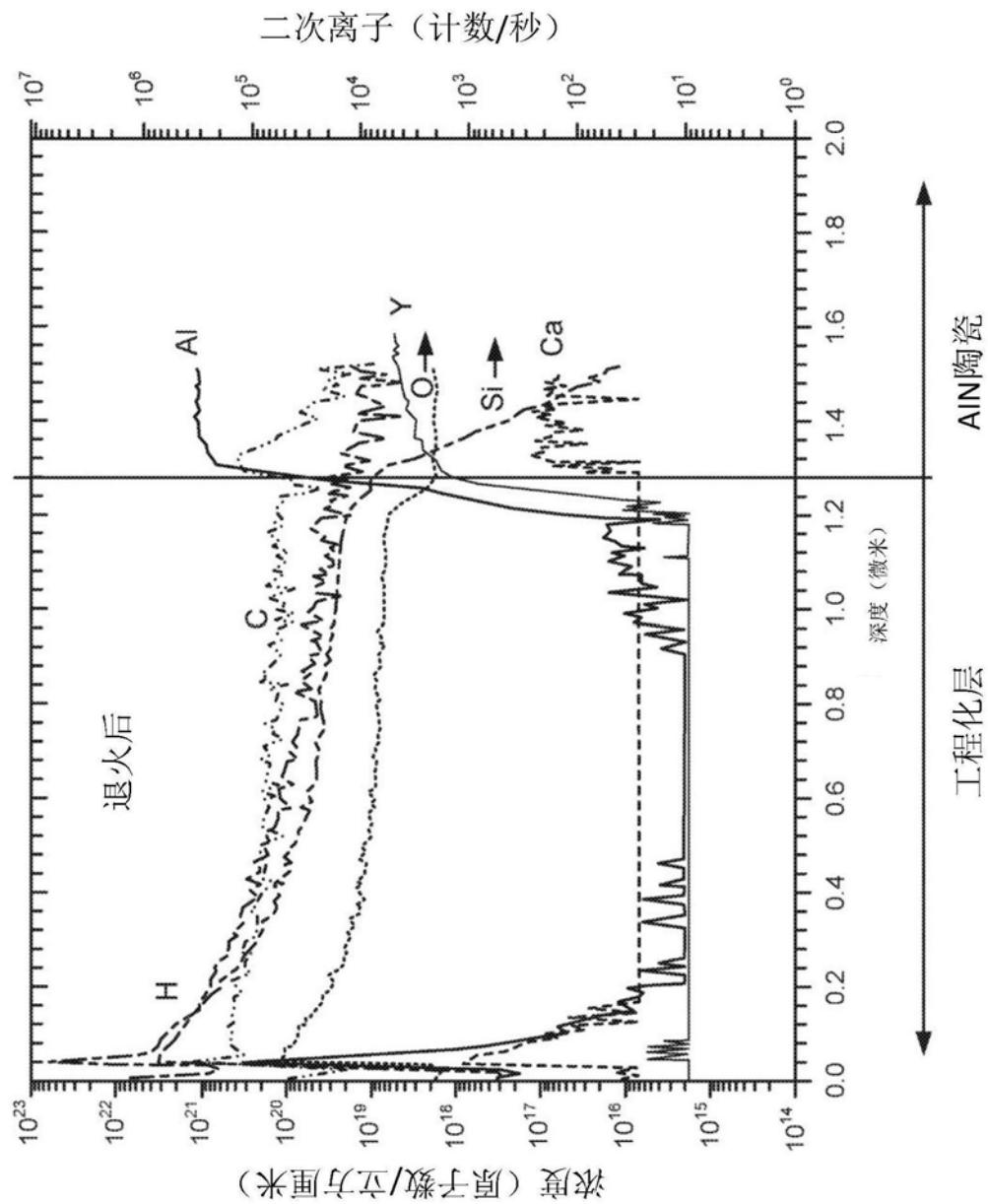

[0016] 图2B是示出了根据本发明实施例的退火后的工程化结构的物质浓度作为深度的函数的SIMS分布图。

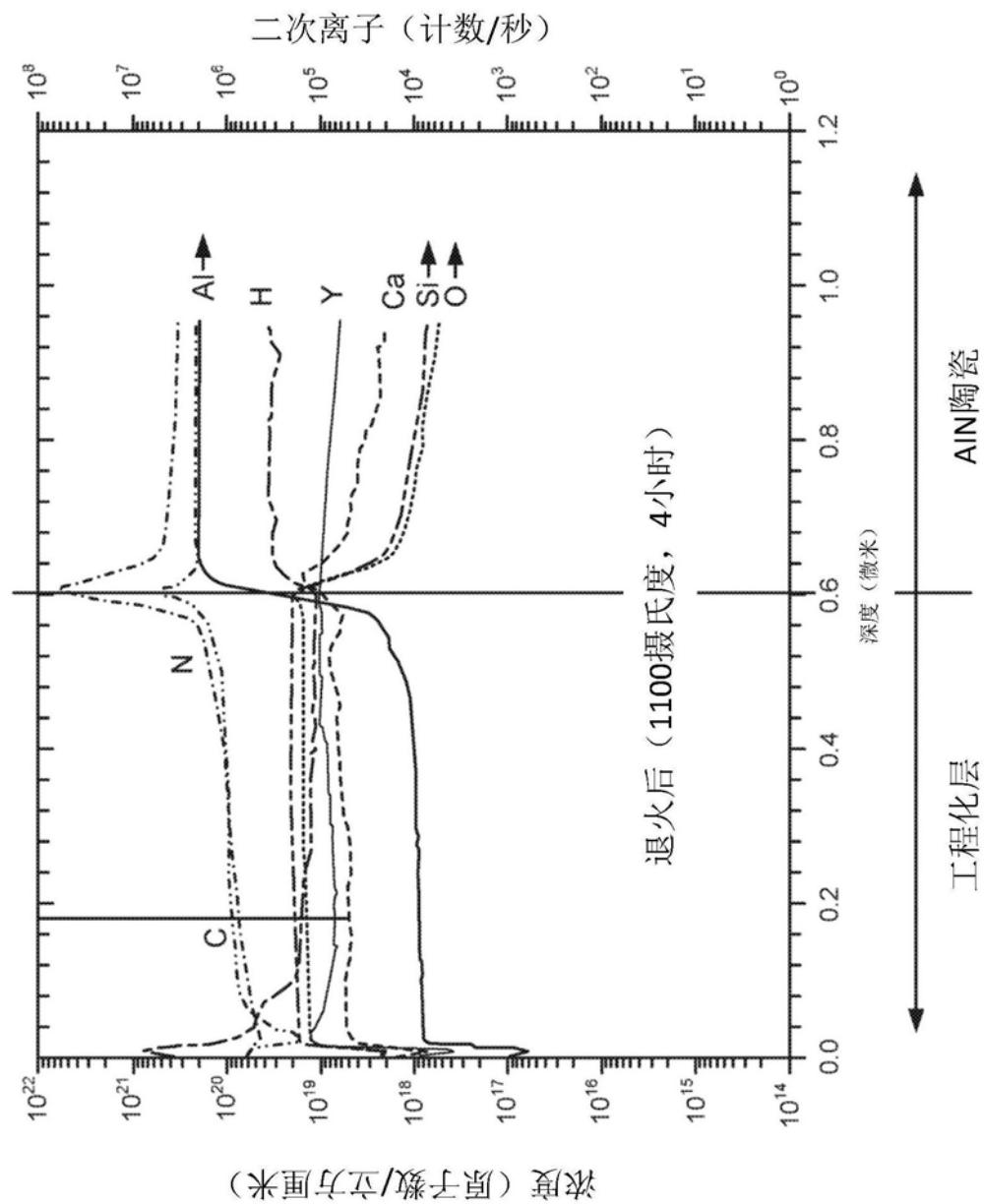

[0017] 图2C是示出根据本发明实施例的退火后的具有氮化硅层的工程化结构的物质浓度作为深度的函数的SIMS分布图。

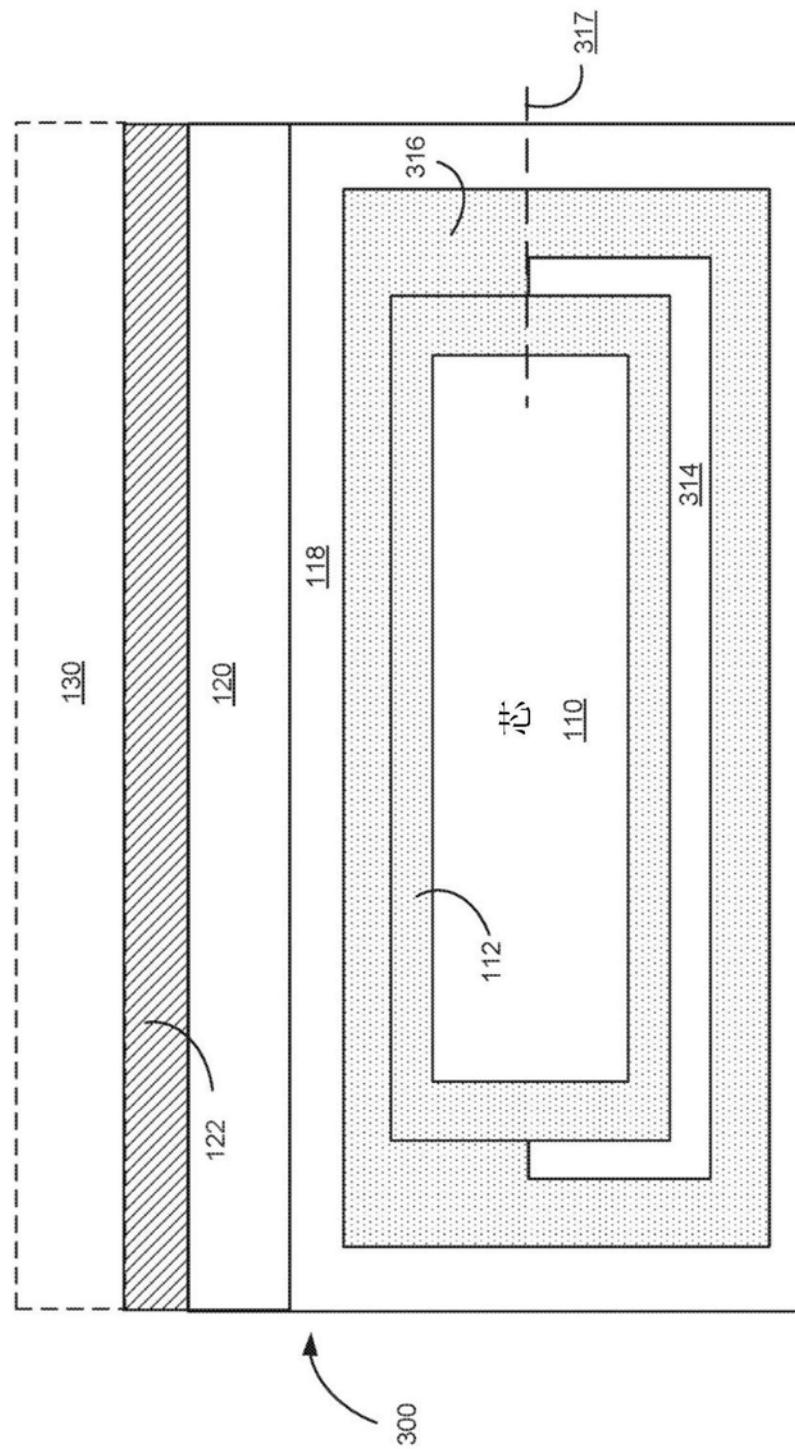

[0018] 图3是示出了根据本发明另一实施例的工程化衬底结构的简化示意图。

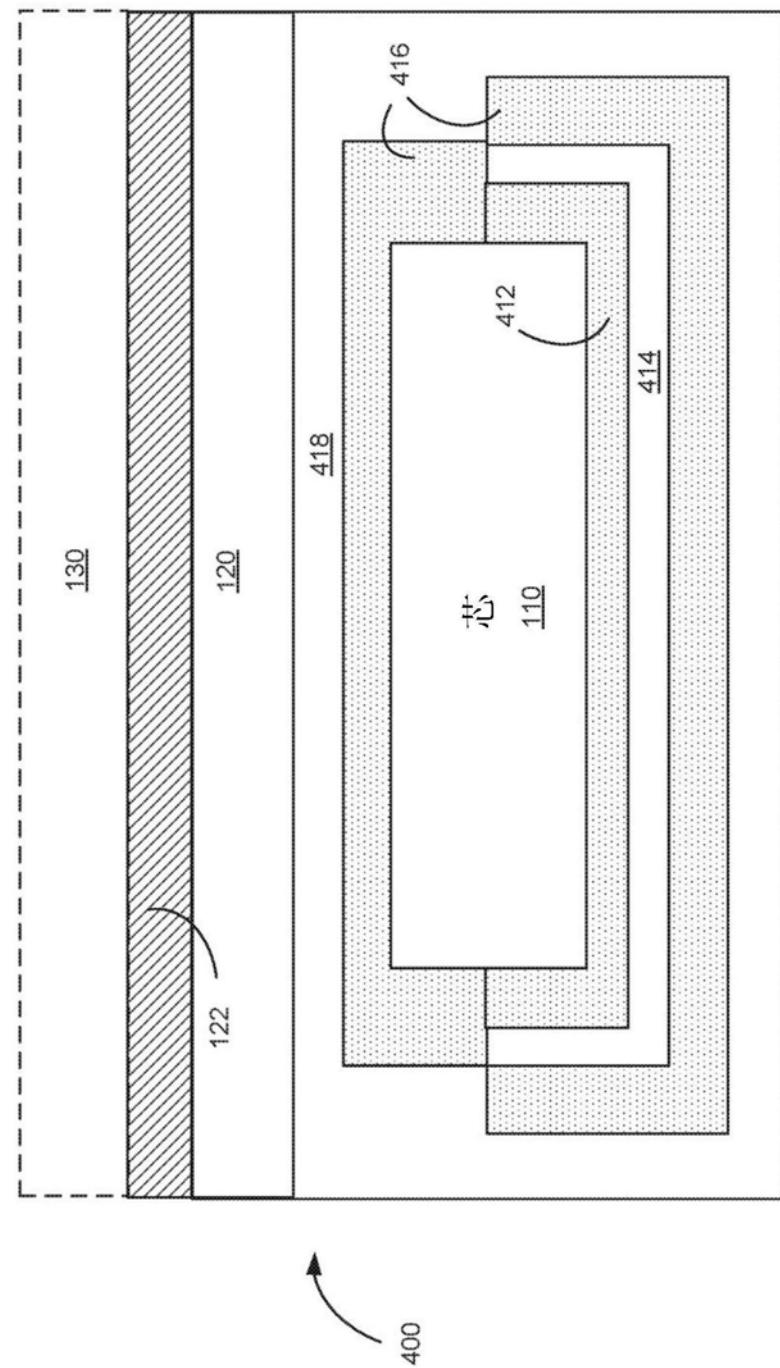

[0019] 图4是示出了根据本发明又一实施例的工程化衬底结构的简化示意图。

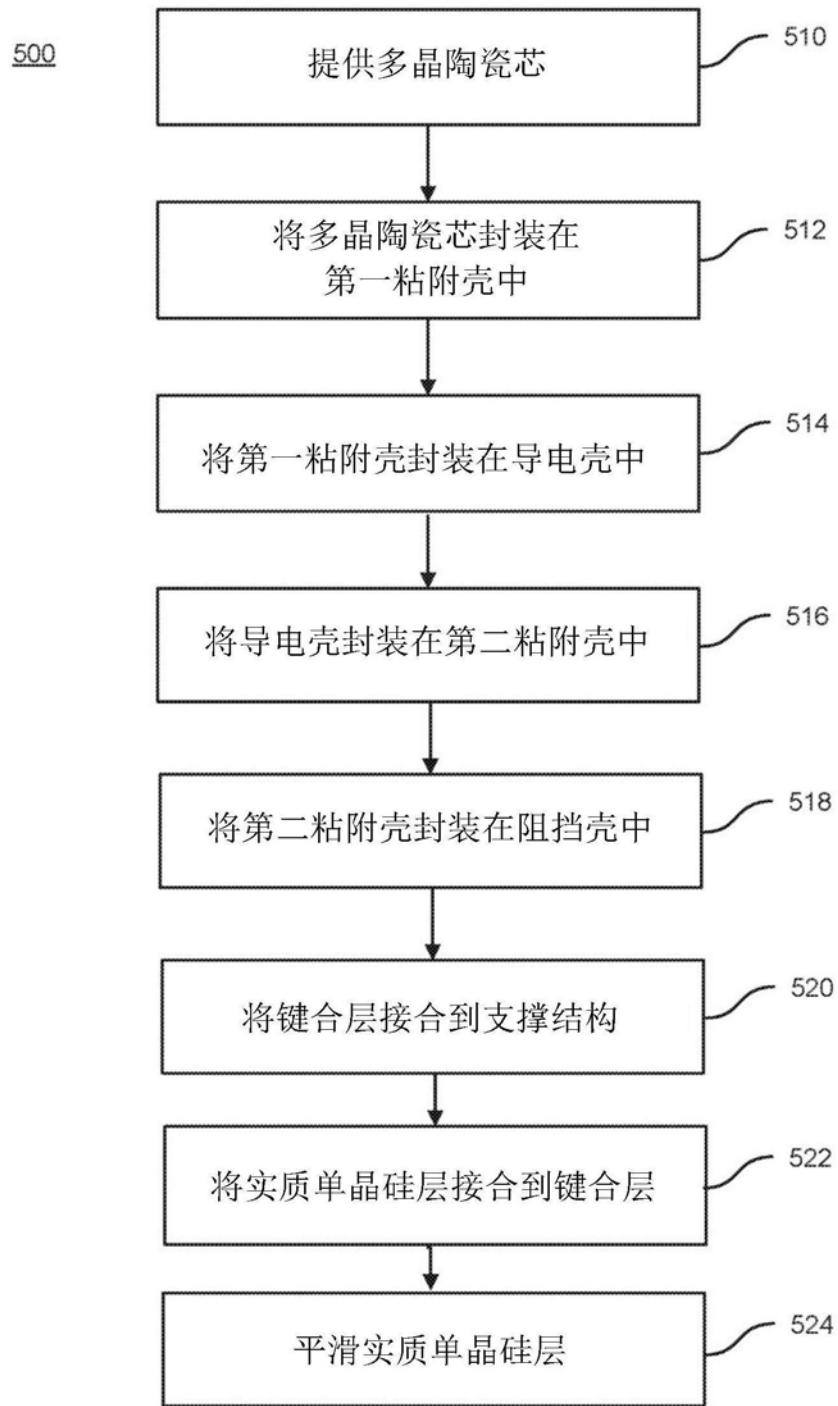

[0020] 图5是示出根据本发明实施例的制造工程化衬底的方法的简化流程图。

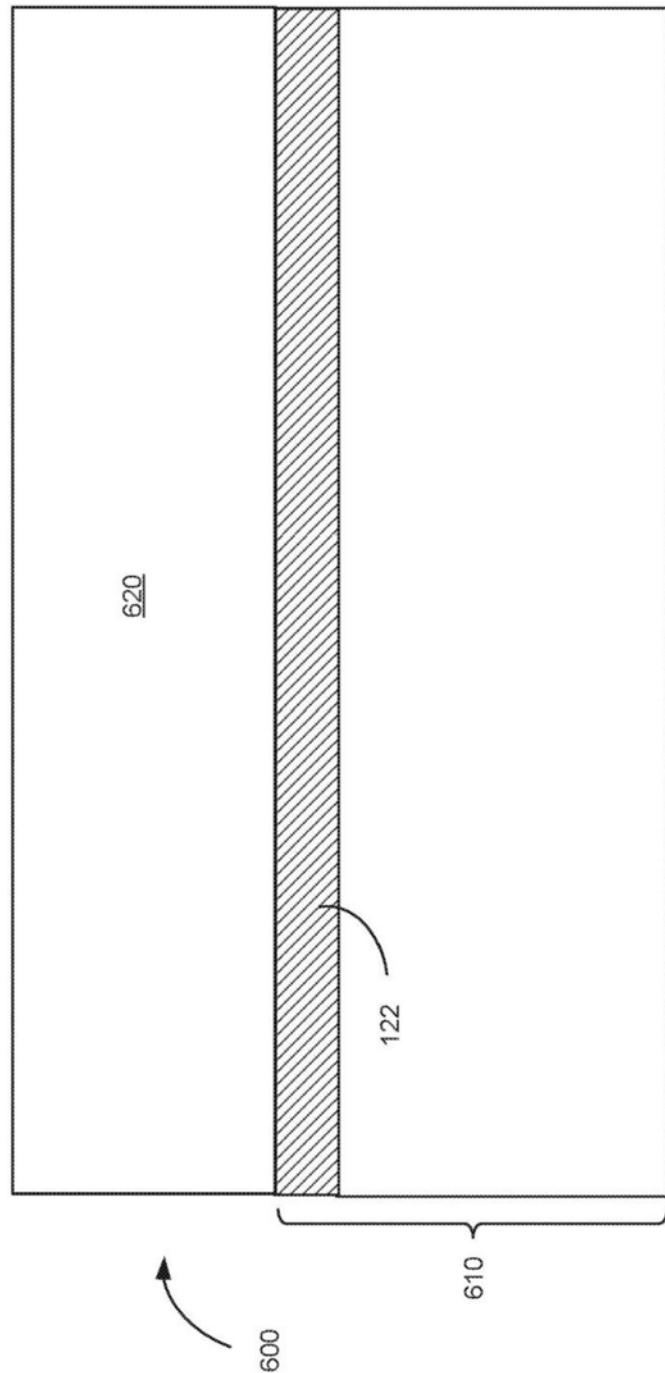

[0021] 图6是示出了根据本发明的实施例的用于RF应用和功率应用的外延/工程化衬底结构的简化示意图。

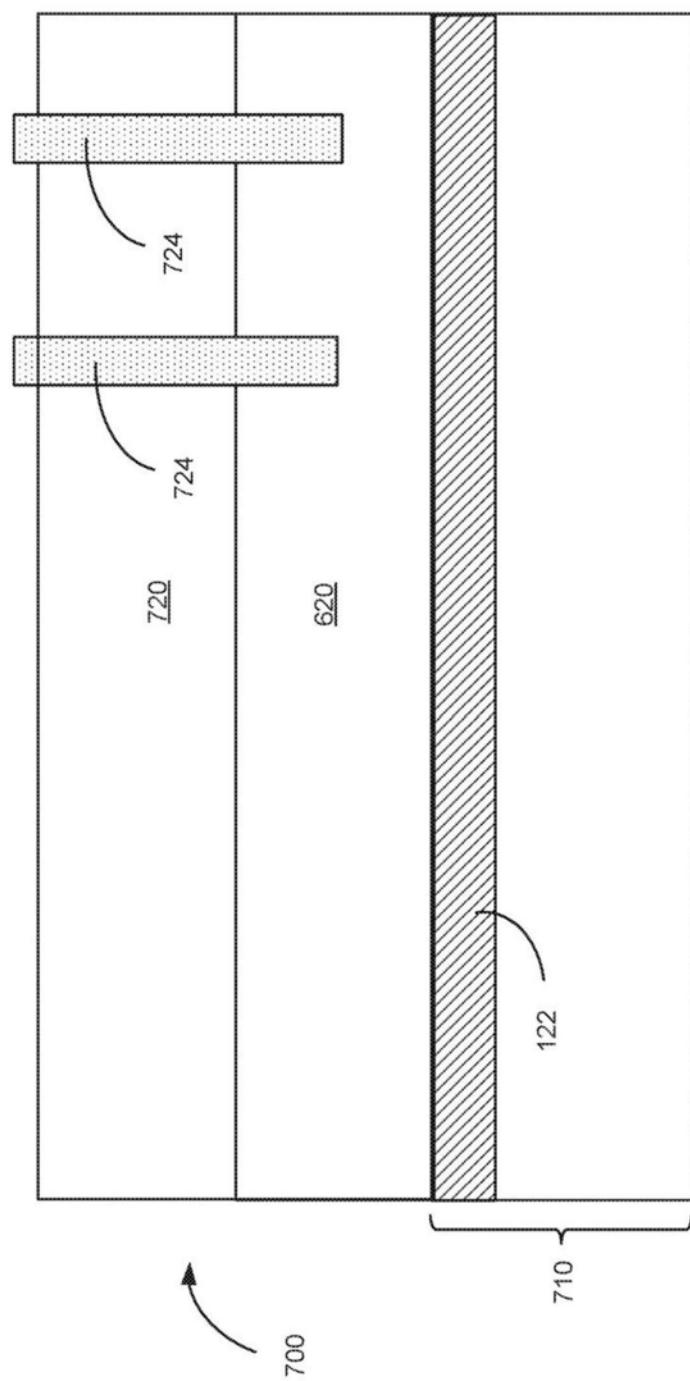

[0022] 图7是示出了根据本发明实施例的工程化衬底结构上的III-V外延层的简化示意图。

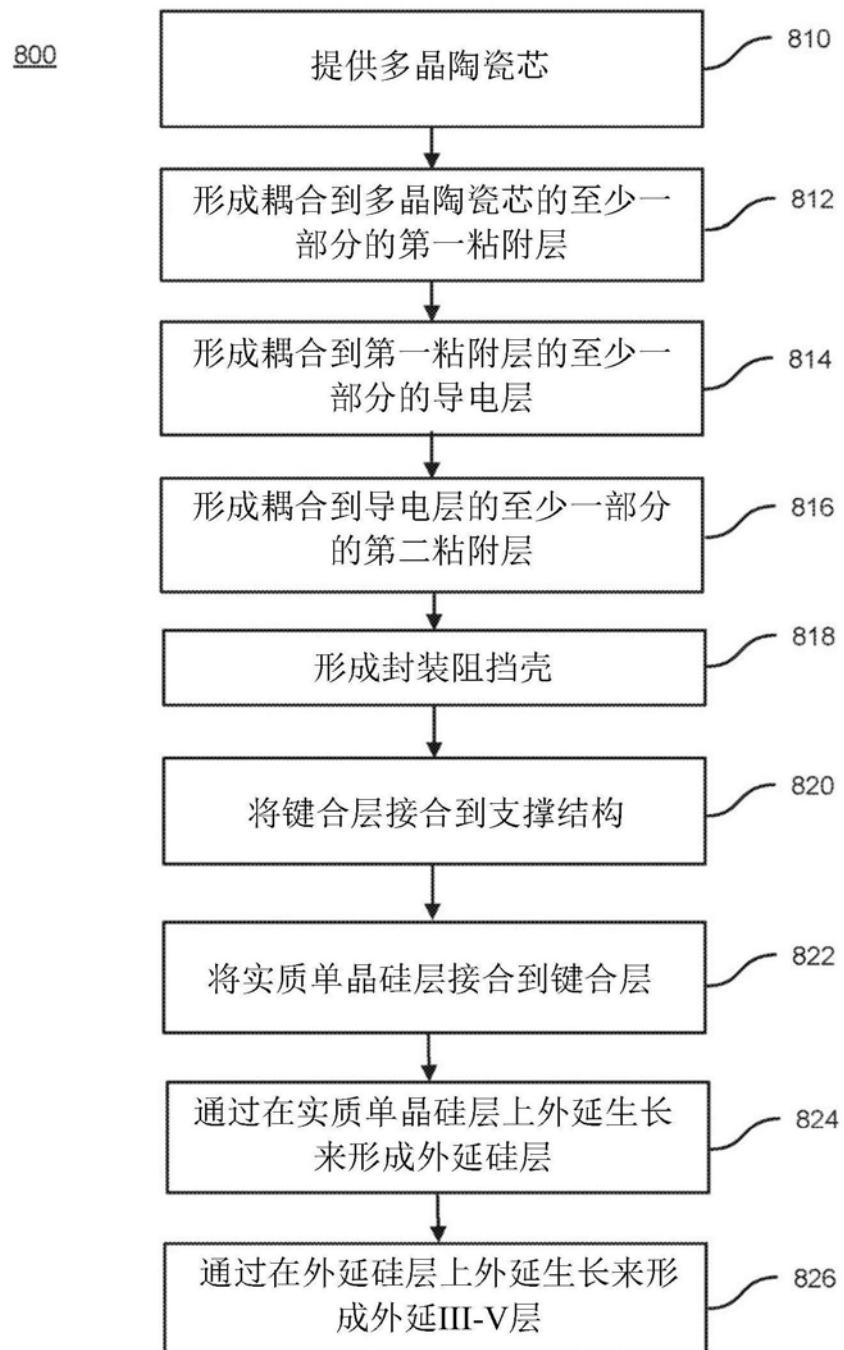

[0023] 图8是示出了根据本发明另一实施例的制造工程化衬底的方法的简化流程图。

[0024] 具体实施方式的详细描述

[0025] 本发明的实施例涉及工程化衬底结构。更具体地，本发明涉及适用于外延生长工艺的方法和系统。仅作为示例，本发明已经应用在用于提供适用于外延生长的衬底结构的方法和系统上，所述衬底结构的特征是具有与在其上生长的外延层实质上匹配的热膨胀系数(CTE)。该方法和技术可以应用于各种半导体工艺操作。

[0026] 图1是示出了根据本发明的实施例的工程化衬底结构的简化示意图。图1中示出的工程化衬底100适用于各种电子和光学应用。工程化衬底包括芯110，其可具有与将生长在工程化衬底100上的外延材料的热膨胀系数(CTE)实质上匹配的CTE。外延材料130被示出为可选的，因为它不需要作为工程化衬底的组成部分，但将通常在工程化衬底上生长。

[0027] 对于包括基于氮化镓(GaN)的材料（包括基于GaN层的外延层）的生长的应用，芯

110 可以是多晶陶瓷材料,例如,多晶氮化铝(AlN),其可以包括诸如氧化钇的粘结材料。可以在芯110中使用其它材料,包括多晶氮化镓(GaN)、多晶氮化铝镓(AlGaN)、多晶碳化硅(SiC)、多晶氧化锌(ZnO)、多晶三氧化镓(Ga<sub>2</sub>O<sub>3</sub>)等。

[0028] 芯的厚度可以为约100μm至1,500μm(例如725μm)的量级。芯110被封装在第一粘附层112中,该第一粘附层112可被称为壳或封装壳。在一个实施例中,第一粘附层112包括厚度为1,000Å量级的原硅酸四乙酯(TEOS)层。在其它实施例中,第一粘附层的厚度变化,例如,从100Å变到2000Å。尽管在一些实施例中TEOS用于粘附层,但是根据本发明的实施例,可以使用在后来沉积的层和下面的层或材料(例如陶瓷,特别是多晶陶瓷)之间提供粘附的其它材料。例如,SiO<sub>2</sub>或其它硅氧化物(Si<sub>x</sub>O<sub>y</sub>)很好地粘附到陶瓷材料,并为随后的沉积(例如导电材料的沉积)提供合适的表面。在一些实施例中,第一粘附层112完全包围芯110以形成完全封装的芯,并且可以使用LPCVD工艺来形成。第一粘附层112提供表面,随后的层粘附在该表面上以形成工程化衬底结构的组成部分。

[0029] 除了使用LPCVD工艺、基于熔炉的工艺等形成封装第一粘附层之外,根据本发明的实施例可以使用其它半导体工艺,包括CVD工艺或类似的沉积工艺。作为示例,可以利用涂覆芯的一部分的沉积工艺,可以翻转芯,并且可以重复沉积工艺以涂覆芯的另外的部分。因此,尽管在一些实施例中利用LPCVD技术来提供完全封装的结构,但是根据具体应用可以使用其它膜形成技术。

[0030] 围绕第一粘附层112形成导电层114。在一个实施例中,导电层114是围绕第一粘附层112形成的多晶硅(polysilicon)(即,多晶硅 polycrystalline silicon)壳,因为多晶硅可以表现出与陶瓷材料的差粘附性。在导电层是多晶硅的实施例中,多晶硅层的厚度可以是500Å-5,000Å(例如,2,500Å)的量级。在一些实施例中,多晶硅层可以形成为壳以完全包围第一粘附层112(例如,TEOS层),从而形成完全封装的第一粘附层,并且其可以使用LPCVD工艺形成。在其它实施例中,如下所述,导电材料可以形成在粘附层的一部分上,例如,衬底结构的下半部分。在一些实施例中,导电材料可以形成为完全封装的层,并且随后在衬底结构的一侧上被移除。

[0031] 在一个实施例中,导电层114可以是掺杂的多晶硅层,以提供高导电材料,例如,掺杂硼以提供p型多晶硅层。在一些实施例中,硼的掺杂处于 $1 \times 10^{19} \text{ cm}^{-3}$ 至 $1 \times 10^{20} \text{ cm}^{-3}$ 的水平,以提供高导电性。不同掺杂剂浓度的其它掺杂剂(例如,掺杂剂浓度范围为 $1 \times 10^{16} \text{ cm}^{-3}$ 至 $5 \times 10^{18} \text{ cm}^{-3}$ 的磷、砷、铋等)可用于提供适用于导电层的n型或p型半导体材料。本领域普通技术人员将认识到许多变化、修改和替代。

[0032] 在将工程化衬底静电吸附到半导体处理工具(例如具有静电吸盘(ESC)的工具)期间,导电层114的存在是有用的。导电层114能够在半导体处理工具中进行处理之后快速去除吸附。因此,本发明的实施例提供的衬底结构可以以传统硅晶片使用的方式进行处理。本领域的普通技术人员将认识到许多变化、修改和替代。

[0033] 围绕导电层114形成第二粘附层116(例如,厚度为1,000Å量级的TEOS层)116。在一些实施例中,第二粘附层116完全包围导电层114以形成完全封装的结构,并且可以使用LPCVD工艺、CVD工艺或任何其它合适的沉积工艺来形成,包括沉积旋涂电介质。

[0034] 围绕第二粘附层116形成阻挡层118,例如氮化硅层。在一个实施例中,阻挡层118

是氮化硅层118，其厚度为2,000Å至5,000Å量级。在一些实施例中，阻挡层118完全包围第二粘附层116，以形成完全封装的结构，并且可以使用LPCVD工艺形成该阻挡层。除了氮化硅层之外，可以使用非晶材料（包括SiCN、SiON、AlN、SiC等）作为阻挡层。在一些实施例中，阻挡层118包括多个子层，该子层被构建以形成阻挡层。因此，术语阻挡层不旨在表示单层或单一材料，而是涵盖以复合方式分层的一种或多种材料。本领域的普通技术人员将认识到许多变化、修改和替代。

[0035] 在一些实施例中，阻挡层118（例如氮化硅层）防止（例如在高温（例如，1000°C）外延生长过程期间）存在于芯110中的元素（例如，氧化钇（yttrium oxide）（即氧化钇（yttria））、氧、金属杂质、其它痕量元素等）扩散和/或放气进入可以存在工程化衬底的半导体处理室的环境中。利用本文所述的封装层，可以在半导体工艺流程和洁净室环境中利用陶瓷材料，该陶瓷材料包括设计用于非洁净室环境的多晶AlN。

[0036] 图2A是示出了根据本发明实施例的工程化结构的物质浓度作为深度的函数的二次离子质谱（SIMS）分布图。工程化结构不包括阻挡层118。参照图2A，存在于陶瓷芯中的几种物质（例如，钇，钙和铝）在工程化层120/122中降至可忽略的浓度。钙、钇和铝的浓度分别下降三个、四个和六个数量级。

[0037] 图2B是示出了根据本发明实施例的退火后的没有阻挡层的工程化结构的物质浓度作为深度的函数的SIMS分布图。如上所讨论的，在半导体工艺操作期间，例如，在基于GaN的层的外延生长期间，由本发明实施例提供的工程化衬底结构可以暴露于高温（～1,100°C）数小时。

[0038] 对于图2B中所示的分布图，工程化衬底结构在1,100°C下退火4小时。如图2B所示，最初在所沉积的样品中以低浓度存在的钙、钇和铝已扩散到工程化层中，达到与其他元素类似的浓度。

[0039] 图2C是示出根据本发明实施例的退火后的具有阻挡层的工程化结构的物质浓度作为深度的函数的SIMS分布图。将扩散阻挡层118（例如，氮化硅层）集成到工程化衬底结构中防止了在扩散阻挡层不存在时发生的退火工艺期间钙、钇和铝扩散到工程化层中。如图2C所示，存在于陶瓷芯中的钙、钇和铝在退火后的工程化层中保持低浓度。因此，阻挡层118（例如，氮化硅层）的使用防止了这些元素扩散通过扩散阻挡层，从而防止了它们释放到工程化衬底周围的环境中。类似地，包含在块状陶瓷材料中的任何其他杂质都将被阻挡层所牵制。

[0040] 通常，用于形成芯110的陶瓷材料在1,800°C的温度下烧制。可以预期的是该过程会驱除陶瓷材料中存在的大量杂质。这些杂质可包括钇（这是由于使用氧化钇作为烧结剂）、钙和其他元素和化合物。随后，在800°C至1,100°C范围内的低得多的温度下进行的外延生长工艺期间，将可以预计的是这些杂质的后续扩散将是微不足道的。然而，与传统预期相反，发明人已经确定即使在远低于陶瓷材料的烧制温度的温度下的外延生长工艺期间，也可能发生元素显着扩散通过工程化衬底的层。因此，本发明的实施例集成了阻挡层118（例如，氮化硅层）以防止背底元素从多晶陶瓷材料（例如，AlN）向外扩散到工程化层120/122和外延层中，例如可选的GaN层130。封装下面的层和材料的氮化硅层提供了所需的阻挡层功能。

[0041] 如图2B所示，最初存在于芯110中的元素，包括扩散到并穿过第一TEOS层、多晶硅

层 114和第二TEOS层的钇。然而,如图2C所示,氮化硅层的存在防止了这些元素扩散穿过氮化硅层,从而防止它们释放到工程化衬底周围的环境中。

[0042] 再次参考图1,在阻挡层118的一部分(例如阻挡层的顶表面)上沉积的键合层120(例如,氧化硅层),并且随后在键合实质单晶层122期间使用该键合层120。在一些实施例中,键合层120的厚度可为约 $1.5\mu\text{m}$ 。

[0043] 实质单晶层122适合在外延生长工艺期间用作生长层,以形成外延材料130。在一些实施例中,外延材料130包括厚度为 $2\mu\text{m}$ 至 $10\mu\text{m}$ 的GaN层,其可以用作光电器件、RF器件和功率器件等中使用的多个层中的一个层。在一个实施例中,实质单晶层122包括利用层转移工艺附接到氧化硅层的实质单晶硅层。

[0044] 图3是示出了根据本发明实施例的工程化衬底结构的简化示意图。图3中所示的工程化衬底300适用于各种电子和光学应用。工程化衬底包括芯110,其可具有与将生长在工程化衬底300上的外延材料130的热膨胀系数(CTE)实质上匹配的CTE。外延材料130被示出为可选的,因为它是不需要作为工程化衬底结构的组成部分,但通常将在工程化衬底结构上生长。

[0045] 对于包括基于氮化镓(GaN)的材料(包括基于GaN层的外延层)的生长的应用,芯110可以是多晶陶瓷材料,例如,多晶氮化铝(AlN)。芯的厚度可以大约为100至 $1,500\mu\text{m}$ 的量级,例如 $725\mu\text{m}$ 。芯110封装在第一粘附层112中,该第一粘附层112可被称为壳或封装壳。在该实施方式中,第一粘附层112完全封装芯,但是如关于图4进一步详细讨论的,这不是本发明所要求的。

[0046] 在一个实施例中,第一粘附层112包括厚度为约 $1000\text{ \AA}$ 量级的原硅酸四乙酯(TEOS)层。在其他实施例中,第一粘附层的厚度变化,例如从 $100\text{ \AA}$ 变到 $2000\text{ \AA}$ 。尽管在一些实施例中TEOS用于粘附层,但是根据本发明的实施例,可以使用在后来沉积的层和下面的层或材料(例如陶瓷,特别是多晶陶瓷)之间提供粘附的其它材料。例如, $\text{SiO}_2$ 或其它硅氧化物( $\text{Si}_{x,y}\text{O}_y$ )很好地粘附到陶瓷材料,并为随后的沉积(例如导电材料的沉积)提供合适的表面。在一些实施例中,第一粘附层112完全包围芯110以形成完全封装的芯,并且可以使用LPCVD工艺。粘附层提供表面,随后的层粘附在该表面上以形成工程化衬底结构的组成部分。

[0047] 除了使用LPCVD工艺、基于熔炉的工艺等形成封装粘附层之外,根据本发明的实施例可以使用其它半导体工艺。作为示例,可以利用涂覆芯的一部分的沉积工艺,例如,CVD、PECVD等,可以翻转芯,并且可以重复沉积工艺以涂覆芯的另外的部分。

[0048] 导电层314形成在第一粘附层112的至少一部分上。在一个实施例中,导电层314包括多晶硅(polysilicon)(即,多晶硅 polycrystalline silicon),其由在芯/粘附层结构的下部(例如,在后侧的下半部分)上的沉积工艺形成。在导电层是多晶硅的实施例中,多晶硅层的厚度可以是几千埃的量级,例如, $3,000\text{ \AA}$ 。在一些实施例中,可以使用LPCVD工艺形成多晶硅层。

[0049] 在一个实施例中,导电层314可以是掺杂的多晶硅层以提供高导电材料,例如,导电层314可以掺杂硼以提供p型多晶硅层。在一些实施例中,硼的掺杂处于为约 $1\times 10^{19}\text{ cm}^{-3}$ 至 $1\times 10^{20}\text{ cm}^{-3}$ 的水平,以提供高导电性。在将工程化衬底静电吸附到半导体处理工具(例

如具有静电吸盘(ESC)的工具)期间,导电层的存在是有用的。导电层314能够在处理之后快速地去除吸附。因此,本发明的实施例提供了可以以传统硅晶片使用的方式进行处理的衬底结构。本领域普通技术人员将认识到许多变化、修改和替代。

[0050] 围绕导电层314(例如,多晶硅层)形成第二粘附层316(例如,第二TEOS层)。第二粘附层316的厚度约为1,000Å量级。在一些实施例中,第二粘附层316可以完全包围导电层314以及第一粘附层112,以形成完全封装的结构,并且可以使用LPCVD工艺来形成。在其他实施例中,第二粘附层316仅部分地围绕导电层314,例如,终止于由平面317示出的位置,平面317可以与导电层314的顶表面齐。在这个示例中,导电层314的顶表面将与阻挡层118的一部分接触。本领域技术人员将认识到许多变化、修改和替代。

[0051] 围绕第二粘附层316形成阻挡层118(例如,氮化硅层)。在一些实施例中,阻挡层118的厚度约为4,000Å至5,000Å量级。在一些实施例中,阻挡层118完全包围第二粘附层316以形成完全封装的结构,并且可以使用LPCVD工艺来形成。

[0052] 在一些实施例中,使用氮化硅阻挡层防止了例如,在高温(例如,1000°C)外延生长工艺期间,存在于芯110中的元素(例如,氧化钇(yttrium oxide)(即氧化钇(yttria))、氧、金属杂质、其他痕量元素等)扩散和/或放气到工程化衬底可以存在的半导体处理室的环境中。利用本文所述的封装层,可以在半导体处理流程和洁净室环境中利用陶瓷材料,该陶瓷材料包括设计用于非洁净室环境的多晶AlN。

[0053] 图4是示出了根据本发明另一实施例的工程化衬底结构的简化示意图。在图4所示的实施例中,第一粘附层412形成在芯110的至少一部分上,但不封装芯110。在这个实施方式中,如下面更全面地描述的,第一粘附层412形成在芯110的下表面(芯110的背面)上,以便增强随后形成的导电层414的粘附性。虽然第一粘附层412仅在图4中的芯110的下表面上示出,但是应当理解的是,粘附层材料在芯的其他部分上的沉积将不会不利地影响工程化衬底结构的性能,并且这种材料可以存在于各种实施例中。本领域普通技术人员将认识到许多变化、修改和替代。

[0054] 导电层414不封装第一粘附层412和芯110,但是基本上与第一粘附层412对齐。尽管导电层414被示出为沿着底部或背面延伸并且向上延伸第一粘附层412的侧面的一部分,本发明不需要沿垂直侧的延伸。因此,实施例可以利用在衬底结构的一侧上的沉积,掩蔽(masking)衬底结构等的一侧。导电层414可以形成在第一粘附层412的一侧的一部分上,例如,底部/背面。导电层414在工程化衬底结构的一侧上提供电传导,这在射频和高功率应用中可以是有利的。如关于图1中的导电层114所讨论的,导电层可以包括掺杂的多晶硅。

[0055] 芯110的一部分、第一粘附层412的部分和导电层414用第二粘附层416覆盖,以便增强阻挡层418与下面的材料的粘合。如上所讨论的,阻挡层418形成封装结构以防止从下面的层扩散。

[0056] 除了基于半导体的导电层之外,在其他实施例中,导电层414是金属层,例如500Å的钛等。

[0057] 再次参考图4,取决于实施方式,可以移除一个或多个层。例如,可以移除第一粘附层412和导电层414,仅留下单个的第二粘附层416和阻挡层418。在另一个实施例中,仅可以移除导电层414。在这个实施例中,第一粘附层412还可以平衡由沉积在阻挡层418的顶部上的键合层120引起的应力和晶片弯曲。在芯110的顶侧上具有绝缘层的衬底结构的构造

(例如,在芯110和键合层120之间仅具有绝缘层)将为功率/射频应用提供益处,其中需要高度绝缘的衬底。

[0058] 在另一个实施例中,阻挡层418可以直接封装芯110,然后是导电层414和随后的粘附层416。在这个实施例中,键合层120可以从顶侧直接沉积在第二粘附层416上。在另一个实施例中,第二粘附层416可以沉积在芯110上,接着是阻挡层418,并且然后是导电层414和另一个第一粘附层412。

[0059] 尽管已经从层的方面讨论了一些实施例,但术语“层”应该被理解为使得层可以包括多个子层,多个子层被构建以形成感兴趣的层。因此,术语“层”不旨在表示由单一材料组成的单层,而是涵盖以复合的方式分层以形成所需结构的一种或多种材料。本领域普通技术人员将认识到许多变化、修改和替代。

[0060] 图5是示出根据本发明实施例的制造工程化衬底的方法的简化流程图。该方法可用于制造与在衬底上生长的一个或多个外延层的CTE匹配的衬底。方法500包括通过以下步骤来形成支撑结构:提供多晶陶瓷芯(510),将多晶陶瓷芯封装在第一粘附层形成的壳(例如,原硅酸四乙酯(TEOS)壳)中(512),并将第一粘附层封装在导电壳(例如,多晶硅壳)中(514)。第一粘附层可以形成为单层TEOS。导电壳可以形成为单层多晶硅。

[0061] 该方法还包括将导电壳封装在第二粘附层(例如,第二TEOS壳)中(516),并将第二粘附层封装在阻挡层壳中(518)。第二粘附层可以形成为单层TEOS。阻挡层壳可以形成为单层氮化硅。

[0062] 一旦通过步骤510-518形成支撑结构,该方法还包括将键合层(例如,氧化硅层)接合到支撑结构上(520),并且将实质单晶层(例如实质单晶硅层)接合到氧化硅层(522)。根据本发明的实施例,可以使用其它实质单晶层,包括SiC、蓝宝石、GaN、AlN、SiGe、Ge、金刚石、 $\text{Ga}_2\text{O}_3$ 、ZnO等。键合层的接合可包括沉积键合材料,然后进行如本文所述的平坦化处理。在如下所述的实施例中,将实质单晶层(例如,实质单晶硅层)接合到键合层利用了层转移工艺,在层转移工艺中该层是从硅晶片转移的单晶硅层。

[0063] 参考图1,可以通过厚(例如,4μm厚)氧化物层的沉积、随后进行化学机械抛光(CMP)处理以将氧化物减薄至约1.5μm的厚度来形成键合层120。厚的初始氧化物用于填充支撑结构上存在的空洞和表面特征,这些空洞和表面特征在制造多晶芯之后可能存在并且在形成图1所示的封装层时继续存在。CMP处理提供无空洞、颗粒或其它特征的实质上平坦的表面,然后可以在晶片转移工艺期间使用该表面来将实质单晶层122(例如,实质单晶硅层)键合到键合层120。应当理解的是,键合层120不必以原子级平坦表面为特征,而应提供实质上平坦的表面,该表面以期望的可靠性支持实质单晶层(例如,实质单晶硅层)的键合。

[0064] 可以使用层转移工艺将实质单晶硅层122接合到键合层120。在一些实施例中,硅晶片(例如,硅(111)晶片)被注入以形成解理面。晶片键合之后,硅衬底可以和解理面下面的单晶硅层的一部分一起被去除,得到图1中所示的剥离的单晶硅层122。实质单晶层122的厚度可以变化以满足各种应用的规格。此外,可以改变实质单晶层122的晶体取向以满足应用的规格。另外,可以改变实质单晶层122中的掺杂水平和分布,以满足特定应用的规格。

[0065] 图5中所示的方法还可以包括平滑实质单晶层(524)。在一些实施例中,可以进一步修改实质单晶层122的厚度和表面粗糙度以用于高质量外延生长。不同的器件应用可以具有关于实质单晶层122的厚度和表面平滑度的略微不同的规格。解理过程在注入的离子

分布的峰值处使实质单晶层122与体单晶硅晶片分层。在解理之后，在将实质单晶层122用作其它材料(例如氮化镓)的外延生长的生长表面之前，可以在几个方面调节或修改实质单晶层122。

[0066] 第一，转移的实质单晶层122可含有少量的残余氢浓度，并且可能具有来自注入物的一些晶体损伤。因此，移除转移的实质单晶层122的其中晶格被损坏的薄的部分可以是有益的。在一些实施例中，可以将注入物的深度调节为大于实质单晶层122的所需最终厚度。附加厚度允许移除转移的实质单晶层的被损坏的薄的部分，留下具有所需最终厚度的未损坏的部分。

[0067] 第二，可能希望调节实质单晶层122的总厚度。通常，可能希望使实质单晶层122足够厚以为一个或多个外延层的随后生长提供高质量的晶格模板，但又足够薄以具有高顺应性 (compliant)。当实质单晶层122相对较薄时，使得其物理性质是少受约束的，且与其周围的材料非常相似，具有少的生成晶体缺陷的倾向时，实质单晶层122可以被称为是“顺应的”。实质单晶层122的顺应性可以与实质单晶层122的厚度成反比关系。较高的顺应性可以导致在模板上生长的外延层中的较低缺陷密度并且能够实现较厚的外延层生长。在一些实施例中，可以通过在剥离硅层上外延生长硅来增加实质单晶层122的厚度。

[0068] 第三，改善实质单晶层122的平滑度可能是有益的。该层的平滑度可能与总的氢剂量、任何共注入物质的存在以及用于形成氨基解理面的退火条件有关。如下所讨论的，通过热氧化和氧化物剥离可以减轻由层转移(即，切割步骤)导致的初始粗糙度。

[0069] 在一些实施例中，通过对剥离硅层的顶部进行热氧化、然后用氢氟(HF)酸进行氧化物层剥离，来实现受损层的移除并调节实质单晶层122的最终厚度。例如，可以对初始厚度为 $0.5\mu\text{m}$ 的剥离硅层进行热氧化，以产生约 $420\text{nm}$ 厚的二氧化硅层。在移除生长的热氧化物之后，转移层中的其余的硅厚度可能为约 $53\text{nm}$ 。在热氧化期间，注入的氢可以向表面迁移。因此，随后的氧化物层剥离可以去除一些损坏。而且，热氧化通常在 $1000^\circ\text{C}$ 或更高的温度下进行。升高的温度也可以修复晶格损伤。

[0070] 热氧化期间在实质单晶层的顶部上形成的氧化硅层可以使用HF酸蚀刻来剥离。通过调节HF溶液的温度和浓度以及氧化硅的化学计量和密度，可以调节HF酸在氧化硅和硅( $\text{SiO}_2$ : Si)之间的蚀刻选择性。蚀刻选择性是指一种材料相对于另一种材料的蚀刻速率。对于( $\text{SiO}_2$ : Si)，HF溶液的选择性的范围可以为约 $10:1$ 至约 $100:1$ 。高蚀刻选择性可以将表面粗糙度从初始表面粗糙度以相似的因子降低。然而，所得到的实质单晶层122的表面粗糙度仍可能大于所需的表面粗糙度。例如，体Si(111)表面可以具有小于 $0.1\text{nm}$ 的均方根(RMS)表面粗糙度，其通过在额外处理之前由 $2\mu\text{m} \times 2\mu\text{m}$ 原子力显微镜(AFM)扫描来确定。在一些实施例中，在Si(111)上外延生长的氮化镓材料的期望表面粗糙度在 $30\mu\text{m} \times 30\mu\text{m}$ 的AFM扫描区域中可以是例如小于 $1\text{nm}$ 、小于 $0.5\text{nm}$ 或小于 $0.2\text{nm}$ 。

[0071] 如果在热氧化和氧化物层剥离之后实质单晶层122的表面粗糙度超过期望的表面粗糙度，则可以执行额外的表面平滑。具有几种平滑硅表面的方法。这些方法可包括氢退火、激光微调、等离子平滑和触摸抛光(例如，化学机械抛光或CMP)。这些方法可能涉及高纵横比表面峰的择优侵蚀。因此，可以比低纵横比特征更快地移除表面上的高纵横比特征，从而产生更平滑的表面。

[0072] 应该理解的是，图5中所示的具体步骤提供了根据本发明的实施例的制造工程化

衬底的特定方法。根据可替代实施例，还可以执行其它步骤顺序。例如，本发明的可替代实施例可以以不同的顺序执行以上概述的步骤。此外，图5中所示的单独的步骤可以包括多个子步骤，这些子步骤可以适合于单独步骤的各种顺序执行。此外，根据特定应用，可以添加或移除附加步骤。本领域的普通技术人员将认识到许多变化、修改和替代。

[0073] 图6是示出了根据本发明的实施例的用于RF和功率应用的外延/工程化衬底结构的简化示意图。在一些LED应用中，工程化衬底结构提供了能够生长高质量的GaN层的生长衬底，并且工程化衬底结构随后被移除。然而，对于RF和功率器件应用，工程化衬底结构形成成品器件的部分，并且因此，工程化衬底结构或工程化衬底结构的组成部分的电学、热学和其他性质对于特定应用是重要的。

[0074] 参考图1，单晶硅层122通常是使用注入和剥离技术从硅施主晶片分离的剥离层。典型的注入物是氢和硼。对于功率和RF器件应用，工程化衬底结构中的层和材料的电特性是重要的。例如，一些器件架构利用电阻大于 $10^3$ 欧姆·厘米 (Ohm·cm) 的高绝缘硅层来减少或消除通过衬底和界面层的泄漏。其他应用利用包括预定厚度(例如， $1\mu\text{m}$ )的导电硅层的设计，以便将器件的源极连接到其他元件。因此，在这些应用中，需要控制单晶硅层的尺寸和性质。在层转移期间使用注入和剥离技术的设计中，硅层中存在残留的注入原子，例如氢或硼，从而改变电性质。另外，使用例如可能影响注入分布的导电性以及半导体的半高宽(FWHM) 的注入剂量的调整、表面粗糙度和解理面位置精度的调整，和使用能影响层厚度的注入深度的调整，可能难以控制薄硅层的厚度、导电性和其他性质。

[0075] 根据本发明的实施例，利用工程化衬底结构上的硅外延来实现适合于特定器件设计的单晶硅层的所需特性。

[0076] 参考图6，外延/工程化衬底结构600包括工程化衬底结构610和在其上形成的外延单晶硅层620。工程化衬底结构610可以与图1,3和4中所示的工程化衬底结构相似。通常，在层转移之后，实质单晶硅层122约为 $0.5\mu\text{m}$ 量级。在一些工艺中，可利用表面调节工艺将单晶硅层122的厚度减小至约 $0.3\mu\text{m}$ 。为了将单晶硅层的厚度增加到约 $1\mu\text{m}$ 以用于实现可靠的欧姆接触，例如，使用外延工艺在由层转移工艺形成的实质单晶硅层122上生长外延单晶硅层620。可以使用各种外延生长工艺来生长外延单晶硅层620，包括CVD, ALD, MBE等。外延单晶硅层620的厚度可以在约 $0.1\mu\text{m}$ 至约 $20\mu\text{m}$ 的范围内，例如在 $0.1\mu\text{m}$ 至 $10\mu\text{m}$ 之间。

[0077] 图7是示出了根据本发明实施例的工程化衬底结构上的III-V外延层的简化示意图。图7中所示的结构可以被称为如下所述的双外延结构。如图7所示，包括外延单晶硅层620的工程化衬底结构710具有在其上形成的III-V外延层720。在一个实施例中，III-V外延层包括氮化镓(GaN)。

[0078] 根据所期望的功能，III-V外延层720的期望厚度可以显著变化。在一些实施例中，III-V外延层720的厚度可以在 $0.5\mu\text{m}$ 至 $100\mu\text{m}$ 之间变化，例如，厚度大于 $5\mu\text{m}$ 。在III-V外延层720上制造的器件的所得击穿电压可以根据III-V外延层720的厚度而变化。一些实施例提供至少 $100\text{V}$ 、 $300\text{V}$ 、 $600\text{V}$ 、 $1.2\text{kV}$ 、 $1.7\text{kV}$ 、 $3.3\text{kV}$ 、 $5.5\text{kV}$ 、 $13\text{kV}$ 或 $20\text{kV}$ 的击穿电压。

[0079] 为了在III-V外延层720(其可包括多个子层)的各部分之间提供导电性，形成一组过孔(vias)724，在这个示例中，过孔724通过III-V外延层720的顶表面进入外延单晶硅层620。过孔724衬有绝缘层(未示出)，使得它们与III-V外延层720绝缘。作为示例，这些过孔可以用于通过过孔提供欧姆接触将二极管或晶体管的电极连接到下面的硅层，从而释放

器件中积累的电荷。

[0080] 如果III-V外延层生长在单晶硅层122上，则难以通过过孔实现这种欧姆接触，因为在单晶硅层122中终止过孔蚀刻将是困难的：例如，蚀刻通过5μm的GaN并在整个晶片上可靠地终止0.3μm硅层中的蚀刻。利用本发明的实施例可以提供厚度为多个微米的单晶硅层，这是使用注入和剥离工艺难以实现的，因为实现大的注入深度需要高的注入能量。进而，厚硅层使得能够实现例如示出的过孔等应用，其使得能够实现多种多样的器件设计。

[0081] 除了通过在单晶硅层122上外延生长外延单晶硅层620来增加硅“层”的厚度之外，还可以对单晶硅层122的原本性质进行其他调整，包括电导率、结晶度等的修改。例如，如果在III-V层或其他材料的额外外延生长之前需要10μm量级的硅层，则根据本发明的实施例可以生长这种厚层。

[0082] 因为注入工艺会影响单晶硅层122的性质，例如，残留的硼/氢原子会影响硅的电性能，本发明的实施例在外延单晶硅层620的外延生长之前去除了一部分单晶硅层122。例如，可以减薄单晶硅层122以形成厚度为0.1μm或更小的层，去除大部分或全部残留的硼/氢原子。然后使用外延单晶硅层620的后续生长来提供具有电和/或其他基本上与使用层转移工艺形成的层的相应性质无关的性质的单晶材料。

[0083] 除了增加耦合到工程化衬底结构的单晶硅材料的厚度之外，电性质（包括外延单晶硅层620的导电性）可以与单晶硅层122的电性质不同。外延单晶硅层620在生长期间的掺杂可以通过掺杂硼产生p型硅并且通过掺杂磷产生n型硅。未掺杂的硅可以生长以提供在具有绝缘区域的器件中使用的高电阻率硅。特别地，绝缘层可用于RF器件中。

[0084] 外延单晶硅层620的晶格常数可以在生长期间调整，以与单晶硅层122的晶格常数不同，以产生应变外延材料。除了硅之外，还可以外延生长其他元素以提供包括应变层（其中包括硅锗等）的层。例如，缓冲层可以在单晶硅层122上、在外延单晶硅层620上或在层之间生长，以增强随后的外延生长。这些缓冲层可包括应变III-V层、硅锗应变层等。另外，缓冲层和其他外延层可以以摩尔分数、掺杂剂、极性等分级。本领域普通技术人员将认识到许多变化、修改和替代。

[0085] 在一些实施例中，存在于单晶硅层122或外延单晶硅层620中的应变可在随后的外延层（包括III-V外延层）的生长期间被释放。

[0086] 图8是示出了根据本发明另一实施例的制造工程化衬底的方法的简化流程图。该方法包括通过提供多晶陶瓷芯（810）、形成耦合到多晶陶瓷芯的至少一部分的第一粘附层（812）来形成支撑结构。第一粘附层可包括原硅酸四乙酯（TEOS）层。该方法还包括形成耦合到第一粘附层的导电层（814）。导电层可以是多晶硅层。第一粘附层可以形成为单层TEOS。导电层可以形成为单层多晶硅。

[0087] 该方法还包括形成耦合到导电层的至少一部分的第二粘附层（816），并形成阻挡壳（818）。第二粘附层可以形成为单层TEOS。阻挡壳可以被形成为单层氮化硅或一系列形成阻挡壳的子层。

[0088] 一旦通过步骤810-818形成支撑结构，该方法还包括将键合层（例如，氧化硅层）接合到支撑结构（820），和将实质单晶硅层或实质单晶层接合到氧化硅层（822）。键合层的接合可以包括键合材料的沉积，然后进行如本文所述的平坦化工艺。

[0089] 可以使用层转移工艺将实质单晶硅层122接合到键合层120。在一些实施例中，硅

晶片被注入(例如,硅(111)晶片)以形成解理面。晶片键合之后,硅衬底可以和解理面下面的单晶硅层的一部分一起被去除,得到图1中所示的剥离的单晶硅层122。实质单晶硅层122的厚度可以变化以满足各种应用的规格。另外,可以改变实质单晶层122的晶体取向以满足应用的规格。另外,可以改变实质单晶层122中的掺杂水平和分布以满足特定应用的规格。在一些实施例中,可以如上所述平滑实质单晶硅层122。

[0090] 图8中所示的方法还可以包括通过在实质单晶硅层上外延生长来形成外延硅层(824),以及通过在外延硅层上外延生长来形成外延III-V层(826)。在一些实施例中,外延III-V层可以包括氮化镓(GaN)。

[0091] 应当理解的是,图8中所示的具体步骤提供了根据本发明另一实施例的制造工程化衬底的特定方法。根据可替代实施例,还可以执行其它步骤顺序。例如,本发明的可替代实施例可以以不同的顺序执行以上概述的步骤。此外,图8中所示的单独步骤可以包括多个子步骤,这些子步骤可以适合于单独步骤的各种顺序执行。此外,根据特定应用,可以添加或移除附加步骤。本领域的普通技术人员将认识到许多变化、修改和替代。

[0092] 还应理解,本文描述的示例和实施例仅用于说明目的,并且对于本领域技术人员而言,本领域技术人员可以对其进行各种修改或改变,并且各种修改或改变包括在本申请的精神和范围内和所附权利要求的范围内。

图1

图2A

图2B

图2C

图3

图4

图5

图6

图7

图8