| DOMANDA DI INVENZIONE NUMERO | 102021000024365 |

|------------------------------|-----------------|

| Data Deposito                | 22/09/2021      |

| Data Pubblicazione           | 22/03/2023      |

# Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| G       | 11     | С           | 16     | 28          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| G       | 11     | С           | 16     | 24          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| G       | 11     | С           | 7      | 06          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| G       | 11     | С           | 7      | 12          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| G       | 11     | С           | 16     | 32          |

# Titolo

PROCEDIMENTO PER ACCEDERE A CELLE DI MEMORIA, CORRISPONDENTI CIRCUITO E DISPOSITIVO DI MEMORIZZAZIONE DATI DESCRIZIONE dell'invenzione industriale dal titolo:

"Procedimento per accedere a celle di memoria, corrispondenti circuito e dispositivo di memorizzazione dati"

di: STMicroelectronics S.r.l., nazionalità italiana, via C. Olivetti, 2 - 20864 Agrate Brianza (MB) (ITALIA)

Inventori designati: Gianbattista LO GIUDICE, Antonino CONTE.

Depositata il: 22 settembre 2021

\*\*\*\*

## TESTO DELLA DESCRIZIONE

### Campo tecnico

La descrizione è relativa a tecniche per l'accesso a dati memorizzati in dispositivi di memorizzazione dati.

Una o più forme di attuazione possono essere applicate, per esempio, in circuiti integrati.

## Sfondo

Un dispositivo di memorizzazione dati come ad esempio un blocco di circuito di memoria in un dispositivo a semiconduttore ("chip" o "die") comprende un ("schiera") di celle di memoria. Per esempio, le celle di memoria nell'array possono essere disposte in righe (attualmente denominate wordline o WL) (attualmente denominate bitline o BL) nel chip semiconduttore in modo che una cella dell'array si trovi all'intersezione di una particolare wordline e bitline. Questo può essere utilizzato come un rispettivo indirizzo di memoria.

Un tempo di accesso per la lettura di una cella di

memoria è un'importante Figura di merito nella valutazione delle prestazioni dei blocchi di circuiti di memoria.

Accedere ad una cella di memoria in un blocco di circuito di memoria per leggerne il suo contenuto sfrutta i circuiti di un amplificatore di rilevamento ("sense amplifier"). Per esempio, due bitline complementari della array di celle di memoria possono essere accoppiate a un amplificatore di rilevamento a margine dell'array. Gli elementi di dati nelle celle di memoria vengono letti (o scritti) dalle stesse bitline che corrono lungo la parte superiore delle righe e delle colonne. Un amplificatore di rilevamento può sfruttare le pre-cariche delle bitline per eseguire il rilevamento della differenza di corrente.

Gli amplificatori di rilevamento sono elementi importanti nelle memorie CMOS. Le loro prestazioni influenzano in modo significativo sia il tempo di accesso alla memoria che la dissipazione di potenza complessiva.

Progettare un amplificatore di rilevamento è un processo complesso che considera la possibilità di aumentare la velocità, migliorare la capacità e mantenere una bassa dissipazione di potenza nelle memorie CMOS.

Per esempio, le prestazioni dell'amplificatore di rilevamento sono influenzate se la capacità di memoria viene aumentata e la tensione di alimentazione viene ridotta.

Per esempio:

aumentare il numero di celle di memoria per bitline aumenta la capacità parassita della bitline,

diminuire l'area della cella di memoria per potere integrare più celle di memoria in un singolo chip riduce la corrente che pilota una bitline pesantemente caricata,

diminuire la tensione di alimentazione si traduce in

margini di rumore ridotti che a loro volta influiscono sull'affidabilità dell'amplificatore di rilevamento.

Le capacità di pre-carica occupano una notevole quantità del tempo di lettura; questo può crescere con la dimensione delle celle nell'array di memoria e produce un picco di consumo di corrente.

Per esempio, per generare un'uscita indicativa dello stato della cella di memoria che viene letta durante un'operazione di lettura, la capacità parassita della bitline viene portata ai livelli di tensione operativa dell'amplificatore di rilevamento.

In tale contesto, con bitline pesantemente caricate da capacità parassite (in particolare in array di memoria ad alta densità), il punto di funzionamento del circuito di pre-carica può essere difficile da controllare.

Le soluzioni convenzionali che utilizzano alimentatori attivi (per esempio, regolatori di tensione) soffrono della presenza di picchi di corrente. Questi picchi possono influenzare il livello regolato di alimentazione fornito dal dispositivo di alimentazione, per esempio iniettando rumore causato da picchi di corrente elevati.

Le soluzioni convenzionali per la pre-carica rapida della bitline soffrono di vari inconvenienti come:

è coinvolta una circuiteria complessa, in particolare nel caso di array di memoria di dimensioni considerevoli,

una pre-carica più breve ha il costo di un picco di consumo di corrente più elevato, e

i circuiti con anelli di retroazione hanno una larghezza di banda limitata.

#### Scopo e sintesi

Uno scopo di una o più forme di attuazione è quello di contribuire a superare gli inconvenienti discussi in precedenza.

Secondo una o più forme di attuazione, tale scopo può essere raggiunto con un procedimento che presenta le caratteristiche esposte nelle rivendicazioni che seguono.

Una o più forme di attuazione si riferiscono a un circuito corrispondente.

Una o più forme di attuazione si riferiscono a un dispositivo di memorizzazione dati corrispondente (per esempio, un'unità di memoria non volatile).

Le rivendicazioni sono una parte integrante dell'insegnamento tecnico qui fornito con riferimento alle forme di attuazione.

Una o più forme di attuazione facilitano l'esecuzione di una fase di pre-carica rapida della bitline, in particolare nel caso di array di memoria di dimensioni considerevoli.

Una o più forme di attuazione facilitano il livellamento dei picchi di consumo di corrente durante la pre-carica rapida.

Una o più forme di attuazione facilitano la riduzione dei picchi di consumo di corrente.

Una o più forme di attuazione sfruttano la condivisione della carica tra una capacità di accumulo di polarizzazione e le capacità nella bitline; ciò facilita la riduzione dell'utilizzo della circuiteria di alimentazione.

Una o più forme di attuazione facilitano il ripristino lento della carica dei condensatori di bitline tra le fasi di pre-carica e le fasi di lettura.

Una o più forme di attuazione facilitano una

implementazione semplice con un dimensionamento ridotto della linea di alimentazione.

# Breve descrizione delle diverse viste dei disegni

Una o più forme di attuazione verranno ora descritte, solo a titolo di esempio non limitante, con riferimento alle figure allegate, in cui:

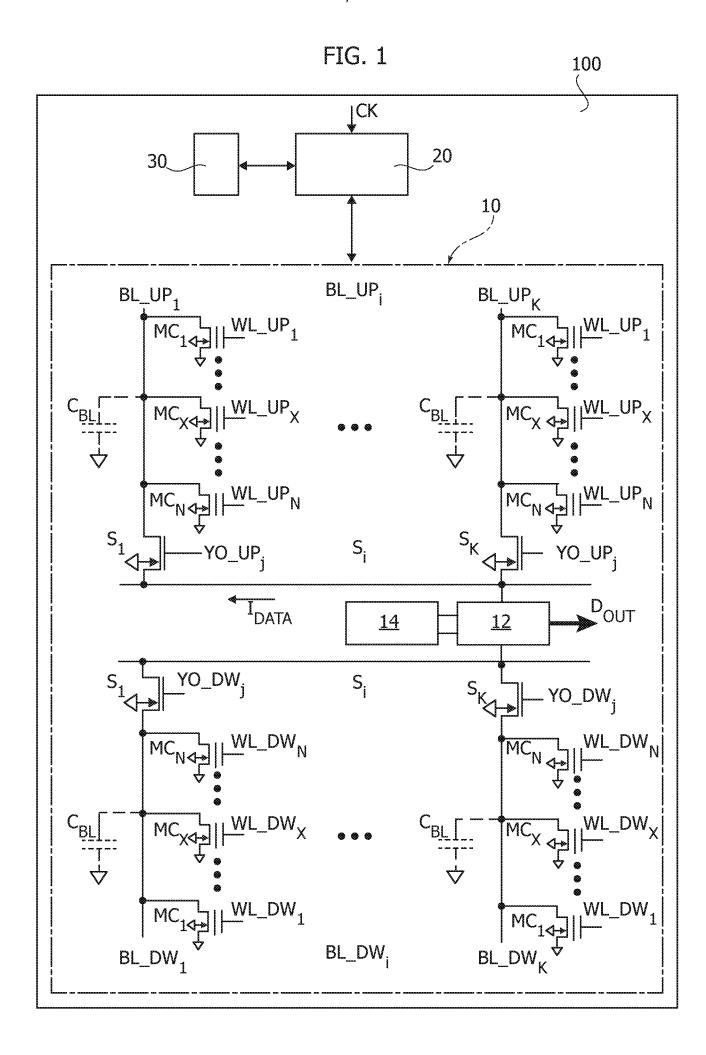

la Figura 1 è un diagramma esemplificativo dei principi alla base del funzionamento degli amplificatori di rilevamento,

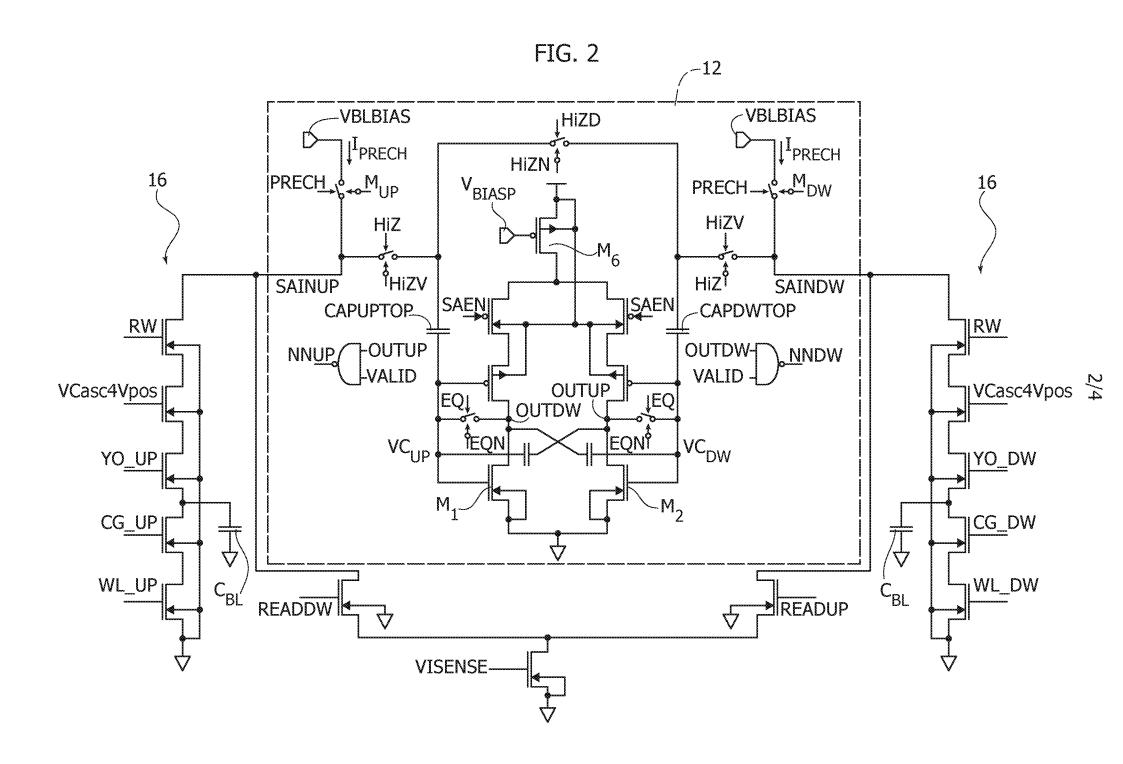

la Figura 2 è un diagramma esemplificativo di un amplificatore di rilevamento,

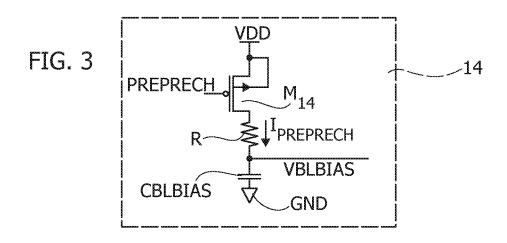

la Figura 3 è un diagramma circuitale esemplificativo di un circuito di pre-carica in un amplificatore di rilevamento,

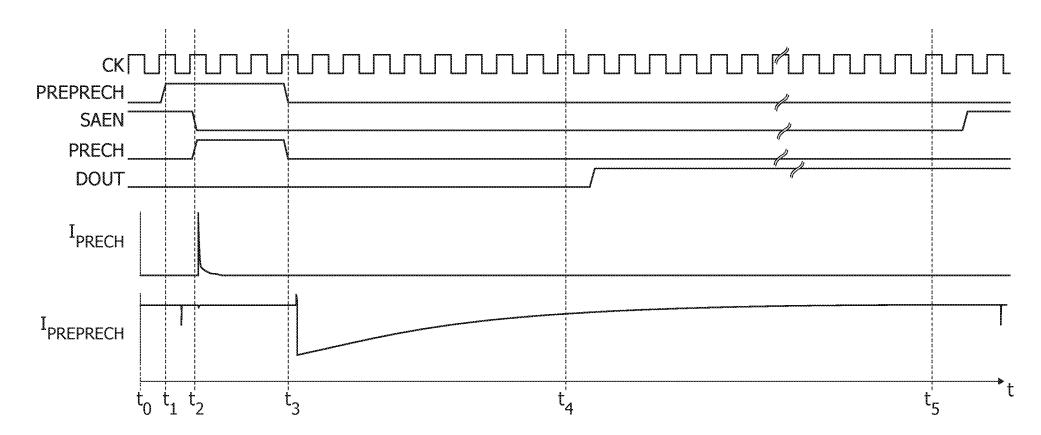

la Figura 4 è un diagramma temporale esemplificativo di possibili comportamenti temporali di segnali che possono essere presenti in una o più forme di attuazione, e

le Figure 5 e 6 sono schemi circuitali di forme di attuazione alternative.

# Descrizione dettagliata delle forme di attuazione esemplificative

Nella descrizione che segue, sono illustrati uno o più dettagli specifici allo scopo di fornire una comprensione approfondita di esempi di forme di attuazione secondo questa descrizione. Le forme di attuazione possono essere ottenute senza uno o più degli specifici dettagli, o con altri procedimenti, componenti, materiali, ecc. In altri casi, strutture, materiali o operazioni note non sono illustrate o descritte in dettaglio in modo che vari aspetti delle forme

di attuazione non saranno offuscati.

Il riferimento a "una forma di attuazione" o "una sola forma di attuazione" nel quadro della presente descrizione è inteso a indicare che una particolare configurazione, struttura, o caratteristica descritta in relazione alla forma di attuazione è compresa in almeno una forma di attuazione. Quindi, frasi come "in una forma di attuazione", "in una sola forma di attuazione" che possono essere presenti in uno o più punti della presente descrizione non si riferiscono necessariamente a una stessa e unica forma di attuazione.

Inoltre, particolari funzionalità, strutture, o caratteristiche possono essere combinate in qualsiasi modo adequato in una o più forme di attuazione.

I disegni sono in forma semplificata e non sono in una scala precisa.

In tutte le figure qui allegate, parti o elementi simili sono indicati con riferimenti/numeri simili e una descrizione corrispondente non verrà ripetuta per brevità.

I riferimenti qui utilizzati sono forniti solo per comodità e quindi non definiscono l'estensione di protezione o la portata delle forme di attuazione.

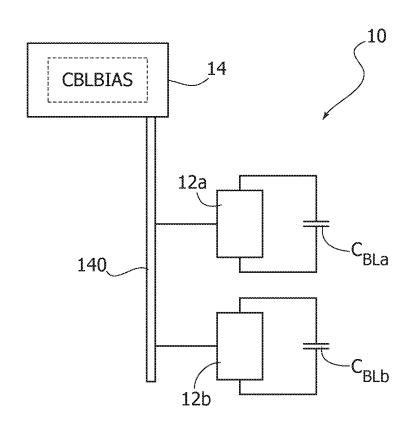

La Figura 1 è una rappresentazione esemplificativa di un blocco di circuito di memoria 10 che comprende un array di celle di memoria  $MC_1,...,MC_x,...,MC_N$  (per esempio, basate su MOSFET).

Ogni cella di memoria presenta un percorso corrente tra un primo nodo e un secondo nodo.

I primi nodi delle celle di memoria  $MC_1,...,MC_x,...,MC_N$  sono configurati per essere accoppiati selettivamente (per esempio, tramite un primo insieme di interruttori  $S_1$ ,  $S_i$ ,  $S_K$ )

a un rispettivo primo insieme di rami di bitline BL\_UP1, BL UP1, BL UP $_{\text{K}}$ .

I secondi nodi delle celle di memoria  $MC_1,...,MC_x,...,MC_N$  sono configurati per essere accoppiati selettivamente (per esempio, tramite un secondo insieme di rispettivi interruttori  $S_1$ ,  $S_i$ ,  $S_K$ ) a un secondo insieme di rami di bitline BL  $DW_1$ , BL  $DW_1$ , BL  $DW_K$ .

Ogni cella di memoria (si veda, per esempio, la cella a gate mobile MC<sub>1</sub>) è configurata per memorizzare dati in cui è possibile accedere (o leggere) o modificare (o scrivere) accoppiando selettivamente il primo e il secondo nodo ai rispettivi rami di bitline BL\_UP<sub>1</sub>, BL\_DW<sub>1</sub> nel primo e nel secondo insieme di rami di bitline BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub></sub>

Come illustrata nella Figura 1, la circuiteria di amplificatore di rilevamento 12 è accoppiata all'array di celle di memoria  $MC_1$ ,  $MC_x$ ,  $MC_N$  tramite il primo e il secondo insieme di rami di bitline  $BL_UP_1$ ,  $BL_UP_i$ ,  $BL_UP_K$ ,  $BL_DW_1$ , BL

Come illustrata nella Figura 1, la circuiteria di precarica 14 è accoppiata alle bitline BL tramite la circuiteria di amplificatore di rilevamento 12 (per esempio, tramite un bypass in esso); il circuito di pre-carica 14 è configurato per caricare il primo e/o il secondo array di bitline BL\_UP1, BL\_UP1, BL\_UP1, BL\_UP1, BL\_DW1, BL\_DW1, BL\_DW1, BL\_DW2 caricandovi una certa carica elettrica, per esempio prima che venga eseguita un'operazione di lettura su una cella di memoria selezionata (per esempio, MC1).

Come esemplificato nella Figura 1, la cella di memoria selezionata in lettura (per esempio,  $MC_1$ ) viene selezionata tramite l'attivazione di almeno un rispettivo interruttore (per esempio,  $S_1$ ) accoppiato con essa.

Per esempio, in risposta all'attivazione di interruttori come  $S_1$ , per esempio, la cella di memoria  $MC_1$  selezionata per essere letta produce una corrente  $I_{DATA}$  che rimuove parte della carica dQ immagazzinata sul primo insieme pre-caricato di bitline BL  $UP_1$ , BL  $UP_1$  BL  $UP_K$ .

Per semplicità, gli array sono qui discussi facendo riferimento a un array lineare di celle di memoria  $MC_1,...,MC_x,...,MC_N$ .

Sarà d'altronde apprezzato che questa rappresentazione è puramente esemplificativa e in nessun modo limitativa: le forme di attuazione si applicano mutatis mutandis teoricamente a qualsiasi altra disposizione di array di celle di memoria  $MC_1,...,MC_x,...,MC_N$ , per esempio, array planari.

La rappresentazione della Figura 1 mostra che ammassare un numero crescente di celle  $MC_1,...,MC_x,...,MC_N$  in circuiti di memoria come il circuito 10 porta a un accesso sempre più condiviso alle bitline nel primo insieme di bitline e nel secondo insieme di bitline.

Queste linee presentano una capacità parassita  $C_{BL}$  che può essere relativamente grande (per esempio, fino ad alcuni picoFarad, con 1 picoFarad = 1pF =  $10^{-12}$  Farad) se confrontata, per esempio, con la capacità di altri componenti nella memoria 10.

Come esemplificato nella Figura 1, in presenza di una capacità di bitline  $C_{BL}$  crescente, un'oscillazione di tensione di bitline  $dV_{BL}$  causata dalla rimozione di una carica dQ dal ramo di bitline BL (per esempio,  $dV_{BL} = dQ/C_{BL}$ )

può essere relativamente piccola.

La circuiteria di amplificatore di rilevamento 12 come esemplificata nella Figura 1 è configurata per tradurre una tale variazione di tensione  $dV_{BL}$  in un segnale logico amplificato  $D_{OUT}$  che può essere ulteriormente elaborato (per esempio, tramite logica digitale 20).

Come esemplificato nella Figura 1, il blocco di circuito di memoria 10 può essere incorporato in un dispositivo elettronico 100, ad esempio un dispositivo microcontrollore 100 con la memoria 10 che funge da memoria non volatile (in breve, NVM, "Non-Volatile Memory") per la memorizzazione di codice, per esempio.

Come esemplificato nella Figura 1, il dispositivo elettronico 100 comprende un'unità di elaborazione 20, ad esempio un microprocessore. L'unità di elaborazione 20 è configurata per essere accoppiata alla memoria 10 per fornire segnali di controllo per pilotare (in modo sincronizzato sulla base di un segnale di clock CK, per esempio) la circuiteria di amplificatore di rilevamento 12 per leggere/scrivere dati memorizzati nelle celle di memoria  $MC_1, ..., MC_x, ..., MC_N$ , come discusso nel seguito.

Come esemplificata nella Figura 1, l'unità di elaborazione 20 è inoltre configurata per ricevere segnali di lettura e segnali di programma scritti nelle celle di memoria  $MC_1,...,MC_x,...,MC_N$  della memoria 10.

Come esemplificata nella Figura 1, un'unità di interfaccia di ingresso/uscita (in breve, I/O) 30, è accoppiata all'unità di elaborazione 20 ed è configurata in modo da innescare la comunicazione del dispositivo elettronico 100 con il mondo esterno, per esempio con sistemi periferici esterni.

Come esemplificato nella Figura 2, un circuito amplificatore di rilevamento con latch come indicato nel documento US 10573382 B2 (assegnato allo stesso assegnatario della presente domanda) è adatto per l'impiego come circuiteria di amplificatore di rilevamento 12 in una o più forme di attuazione.

Come esemplificato nella Figura 2, la circuiteria di amplificatore di rilevamento 12 è accoppiata alla capacità equivalente  $C_{BL}$  delle bitline tramite decodificatori 16 configurati per selezionare una determinata cella di memoria (per esempio,  $MC_1$ ) nell'array di celle di memoria  $MC_1$ , ...,  $MC_N$ . La selezione di celle di memoria (per esempio,  $M_1$ ) tramite i decodificatori 16 può avvenire in un modo di per sé noto agli esperti nel settore, di modo che non verrà fornita una discussione dettagliata per motivi di brevità.

Inoltre, una o più forme di attuazione sono discusse nel seguito principalmente per quanto riguarda il circuito di amplificatore di rilevamento con latch 12 della Figura 2. Resta peraltro inteso che una tale architettura circuitale è puramente esemplificativa e in nessun modo limitativa.

Vari tipi di amplificatori di rilevamento possono essere utilizzati nelle forme di attuazione, in quanto questi sono configurati per funzionare eventualmente con bitline BL polarizzate a una tensione desiderata VBIAS\_SUPPLY durante una fase di rilevamento in modo discontinuo (cioè non durante un'intera fase di rilevamento, ma anche durante porzioni di una fase di rilevamento).

Un amplificatore di rilevamento come esemplificato nella Figura 2 presenta una struttura differenziale che comprende:

una prima porzione di circuito i cui nodi sono indicati

dal suffisso "UP" e sono configurati per essere accoppiati al primo insieme di rami di bitline  $BL\_UP_1$ ,  $BL\_UP_i$ ,  $BL\_UP_K$  e

una seconda porzione di circuito i cui nodi sono indicati dal suffisso "DW" e sono configurati per essere accoppiati al secondo insieme di rami di bitline  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ .

Come esemplificato nella Figura 2, l'amplificatore di rilevamento 12 comprende almeno un nodo di alimentazione di tensione VBLBIAS configurato per ricevere un livello di alimentazione (per esempio, tensione) dal circuito di precarica 14, nonché nodi di dati SAINUP, SAINDW comprendenti un primo nodo dati SAINUP e un secondo nodo dati SAINDW.

Come esemplificato nella Figura 2, il primo nodo dati SAINUP è configurato per essere accoppiato a un primo ramo (per esempio, BL\_UP1) del primo insieme di rami di bitline BL\_UP1, BL\_UP1, BL\_UP $_{\rm K}$  e il secondo nodo dati SAINDW è configurato per essere accoppiato a un primo ramo (per esempio, BL\_UP1) del primo insieme di rami di bitline BL\_UP1, BL\_UP1, BL\_UP1, BL\_UP1,

Come esemplificato nella Figura 2, uno dei nodi dati (per esempio, SAINUP) è configurato per rilevare la variazione di tensione (per esempio,  $dV_{BL}$ ) nel rispettivo ramo di bitline (per esempio, primo  $BL_UP_1$ ) a causa della lettura della cella di memoria (per esempio,  $MC_1$ ), mentre l'altro nodo dati (per esempio, SAINDW) è configurato per rilevare un segnale (di tensione) di riferimento VISENSE, l'amplificatore di rilevamento 12 configurato per eseguire un confronto tra la variazione di tensione rilevata (per esempio,  $dV_{BL}$ ) e il segnale di riferimento VISENSE.

Come esemplificato nella Figura 2, un insieme di interruttori  $M_{\text{UP}}$ ,  $M_{\text{DW}}$  è interposto nel nodo di alimentazione

VBLBIAS.

Come illustrato, tale insieme di interruttori  $M_{\text{UP}}\text{, }M_{\text{DW}}$  comprende:

- i) un primo transistore di commutazione  $M_{UP}$  che presenta un percorso di corrente attraverso di esso tra un primo nodo accoppiato al nodo di alimentazione VBLBIAS e il primo nodo dati SAINUP dell'amplificatore di rilevamento 12; il primo transistore di commutazione  $M_{UP}$  presenta un nodo di controllo PRECH configurato per accoppiare selettivamente la capacità di bitline  $C_{BL}$  al nodo di alimentazione VBLBIAS, tramite il primo nodo dati SAINUP, sulla base di un primo segnale di controllo PRECH (fornito dall'unità processore 20, per esempio) ricevuto al nodo di controllo PRECH, e

- ii) un secondo transistore di commutazione  $M_{DW}$  che presenta un percorso di corrente attraverso di esso tra un rispettivo primo nodo accoppiato al nodo di alimentazione VBLBIAS e il secondo nodo dati SAINDW dell'amplificatore di rilevamento 12; il secondo transistore di commutazione  $M_{DW}$  presenta un nodo di controllo PRECH configurato per accoppiare selettivamente la capacità di bitline  $C_{BL}$  al nodo di alimentazione VBLBIAS, tramite il secondo nodo dati SAINDW, sulla base di un primo segnale di controllo PRECH (fornito dall'unità processore 20, per esempio) ricevuto al nodo di controllo PRECH.

Per esempio, durante il funzionamento di una disposizione come esemplificata nella Figura 2:

il primo interruttore  $M_{UP}$  e il secondo interruttore  $M_{DW}$  sono configurati per essere pilotati in un primo stato (per esempio, chiuso o conduttivo) sulla base del primo segnale di controllo PRECH avente un primo segnale (per esempio, "1" o "alto"), in modo che i rispettivi percorsi di flusso di

corrente siano resi conduttivi e abbiano una corrente  $I_{\text{PRECH}}$  che scorre attraverso di essi durante il primo stato, e

il primo interruttore  $M_{UP}$  e il secondo interruttore  $M_{DW}$  sono configurati per essere pilotati in un secondo stato (per esempio, aperto o non conduttivo) sulla base del primo segnale di controllo PRECH avente un secondo segnale (per esempio, "1" o "alto"), in modo che i rispettivi percorsi di flusso di corrente siano resi non conduttivi durante il secondo stato.

Come esemplificato nella Figura 2, quando il primo e il secondo interruttore  $M_{UP}$ ,  $M_{DW}$  sono nel primo stato, chiuso o conduttivo, l'alimentazione è accoppiata ai rami di bitline  $BL_UP$ ,  $BL_DW$  delle bitline BL, in modo che la capacità di bitline  $C_{BL}$  possa essere caricata durante la fase di precarica, come discussa nel seguito.

Come esemplificato nella Figura 2 (e in un modo di per sé noto agli esperti nel settore) l'amplificatore di rilevamento 12 può essere configurato per eseguire una elaborazione di amplificazione di rilevamento dei segnali ricevuti al primo e al secondo nodo dati sulla base di un segnale di "abilitazione" SAEN asserito con un primo valore (per esempio, "0" o "basso").

Un circuito di pre-carica 12 come esemplificato nella Figura 3 comprende un primo interruttore M14, per esempio, un transistore MOSFET a canale p, che presenta un nodo di controllo PREPRECH e un percorso di corrente attraverso di esso tra un nodo di alimentazione VDD (per esempio, a un livello di tensione di polarizzazione VDD fornito tramite una circuiteria di alimentazione non visibile nella Figura, per esempio) e un secondo nodo VBLBIAS: il percorso di corrente comprende una resistenza R (per esempio, un

resistore esterno o la resistenza interna del transistore M14), il transistore M14 configurato per fornire selettivamente un flusso di corrente attraverso la resistenza R sulla base di un secondo segnale di controllo PREPRECH (fornito dal microprocessore, per esempio) ricevuto al rispettivo nodo di controllo.

Un circuito di pre-carica 12 come esemplificato nella Figura 3 comprende inoltre una capacità di accumulo CBLBIAS accoppiata al secondo nodo VBLBIAS del transistore M14 e configurata per essere caricata alternativamente tramite la corrente che scorre nel transistore M14 o scaricata quando accoppiata alla capacità di bitline  $C_{\rm BL}$ , come discussa nel seguito.

Per esempio, durante il funzionamento di una disposizione come esemplificata nella Figura 3:

il transistore M14 è configurato per essere pilotato in un primo stato (per esempio, chiuso o conduttivo) sulla base del primo segnale di controllo PREPRECH avente un primo segnale (per esempio, "0" o "basso"), il percorso di flusso di corrente attraverso di esso configurato per essere reso conduttivo e avente una corrente IPREPRECH che scorre attraverso di esso durante il primo stato,

il transistore M14 è configurato per essere pilotato in un secondo stato (per esempio, aperto o non conduttivo) sulla base del primo segnale di controllo PREPRECH avente un secondo segnale (per esempio, "1" o "alto"), il percorso di flusso di corrente attraverso di esso configurato per essere reso non conduttivo durante il secondo stato.

Come esemplificato nelle figure 2 e 3, il nodo di alimentazione di bitline VBLBIAS dell'amplificatore di rilevamento 12 è configurato per essere accoppiato al nodo

di alimentazione di tensione VBLBIAS interposto tra la capacità di accumulo  $C_{BL}$  e il transistore M14.

Per esempio, la capacità di accumulo CBLBIAS è configurata per immagazzinare una carica adeguata a precaricare le capacità di bitline  $C_{BL}$  (o almeno una frazione di essa, come discusso nel seguito con riferimento alla Figura 6) quando accoppiata a essa.

È stato osservato che il circuito di pre-carica 14 facilita la pre-carica della capacità di bitline  $C_{BL}$  senza produrre picchi di corrente che influenzano il circuito di alimentazione. Ciò è dovuto alla condivisione di carica tra la capacità di accumulo di polarizzazione reattiva CBLBIAS e la capacità di bitline CBL, in modo che nessuna circuiteria di alimentazione sia accoppiata direttamente alle bitline  $C_{BL}$  durante una fase di pre-carica, come discusso nel seguito.

La Figura 4 illustra un possibile diagramma temporale del primo PRECH e secondo PREPRECH segnale di controllo, nonché il segnale di abilitazione SAEN e un segnale di uscita  $D_{OUT}$  della circuiteria di amplificatore di rilevamento 12 in una o più forme di attuazione del procedimento di precaricamento della capacità di bitline  $C_{BL}$  secondo la presente divulgazione.

La Figura 4 illustra inoltre diagrammi temporali esemplificativi del comportamento della corrente  $I_{PRECH}$  che scorre nel primo e nel secondo transistore  $M_{UP}$ ,  $M_{DW}$  quando resi conduttivi e la corrente IPREPRECH che scorre nel percorso di flusso di corrente del transistore M14 quando reso conduttivo.

Come esemplificato nella Figura 4:

in una fase iniziale (per esempio, nell'istante di tempo

iniziale to), il segnale di abilitazione SAEN viene asserito con un valore (per esempio, "alto") che disabilita il rilevamento dei segnali di dati SAINUP, SAINDW; allo stesso tempo, il secondo segnale di controllo PREPRECH viene asserito a un primo stato (per esempio, "0" o "basso"); di consequenza, il percorso di flusso di corrente transistore di pre-carica M14 è reso conduttivo e la capacità di accumulo CBLBIAS è accoppiata all'alimentazione VDD e (per esempio, lentamente) caricata; durante la carica della capacità di accumulo CBLBIAS, il primo segnale di controllo PRECH è anche nel secondo stato (per esempio, "0" o "basso"), in modo che i percorsi di flusso di corrente del primo  $M_{\text{UP}}$  e del secondo  $M_{\text{DW}}$ transistore di commutazione nell'amplificatore di rilevamento 12 siano conduttivi e il nodo di alimentazione di tensione VBLBIAS del circuito di pre-carica 14 sia disaccoppiato dalla capacità di bitline CBL;

in un primo istante di tempo t<sub>1</sub>, il secondo segnale di controllo PREPRECH viene asserito nel secondo stato (per esempio, "alto") in modo che l'alimentazione VDD sia disaccoppiata dalla capacità di accumulo CBLBIAS; allo stesso tempo, il primo segnale di controllo PRECH rimane nel secondo stato in modo che gli interruttori Mup, MDW rimangano aperti e la tensione nel nodo di polarizzazione VBLBIAS diventi la tensione ai capi della capacità di accumulo caricata CBLBIAS;

in un secondo istante di tempo  $t_2$ , il segnale di abilitazione SAEIN viene asserito al primo valore (per esempio, "basso") in modo che il rilevamento ai nodi dati SAINUP, SAINDW dell'amplificatore di rilevamento 12 sia attivato; allo stesso tempo, il secondo segnale di controllo

rimane asserito nel secondo stato (per esempio, "alto") in modo che il secondo transistore M14 rimanga non conduttivo e la linea di alimentazione VDD sia isolata dalla capacità di accumulo CBLBIAS; allo stesso tempo, il primo segnale di controllo PRECH viene asserito nel primo stato (per esempio, "alto") in modo che i percorsi di corrente dei transistori  $M_{\rm UP}$ ,  $M_{\rm DW}$  siano resi conduttivi e una corrente  $I_{\rm PRECH}$  fluisca in essi; di conseguenza, la capacità CBLBIAS viene accoppiata alla/alle capacità di bitline  $C_{\rm BL}$  che vengono rapidamente caricate (per esempio, in un intervallo di tempo di circa 2ns, con 1 ns = 1 nanosecondo =  $10^{-9}$  secondi) come risultato del fatto che la carica accumulata nella capacità di accumulo CBLBIAS è condivisa con le capacità di bitline  $C_{\rm BL}$  durante la fase di pre-carica PRECH.

Come esemplificato nella Figura 4, si può osservare un picco nel segnale  $I_{\text{PRECH}}$  (immediatamente) dopo il secondo istante  $t_2$ . Si noti che questo picco di corrente è adeguatamente gestito dal componente reattivo CBLBIAS mentre è disaccoppiato (per esempio, grazie a PREPRECH nello stato "alto") da qualsiasi circuiteria di alimentazione VDD, in modo che non influenzi o danneggi la linea di alimentazione VDD fornendo al contempo una pre-carica rapida ed efficace delle bitline  $C_{\text{BL}}$ .

Come esemplificato nella Figura 4, per esempio:

in un terzo istante di tempo t<sub>3</sub>, la fase di pre-carica termina in risposta all'asserimento del primo segnale di controllo PRECH nel rispettivo secondo stato (per esempio, "basso") e al secondo segnale di controllo PREPRECH che viene anch'esso commutato e asserito nel rispettivo primo stato (per esempio, "basso"); ciò comporta rendere non conduttivo il percorso di flusso di corrente del primo e secondo

transistore  $M_{\text{UP}}$ ,  $M_{\text{DW}}$  dell'amplificatore di rilevamento 12 e rendere conduttivo il percorso di flusso di corrente del rispettivo transistore del circuito di pre-carica M14.

Come esemplificato nella Figura 4, (appena) dopo il terzo istante  $t_3$ , una corrente non nulla  $I_{\text{PREPRECH}}$  inizia a scorrere nella resistenza R del circuito di pre-carica M14 per reintegrare la carica precedentemente immagazzinata nella capacità di accumulo CBLBIAS, consumata per pre-caricare la capacità di bitline  $C_{\text{BL}}$  nella precedente fase di pre-carica da  $t_2$  a  $t_3$ .

Nell'esempio della Figura 4, per esempio:

in un quarto istante di tempo  $t_4$ , un segnale di uscita  $D_{OUT}$  è asserito come risultato dell'elaborazione dell'amplificatore di rilevamento 12 eseguita sui segnali di dati rilevati SAINUP, SAINDW, in un modo di per sé noto,

in un quinto istante di tempo  $t_5$ , la capacità di accumulo CBLBIAS ha quasi completato il ripristino della carica, per esempio allo stesso livello che essa aveva all'istante di tempo iniziale  $t_0$ , in modo che possa avvenire una nuova fase di pre-carica come discussa in precedenza rispetto all'intervallo di tempo da  $t_0$  a  $t_3$ .

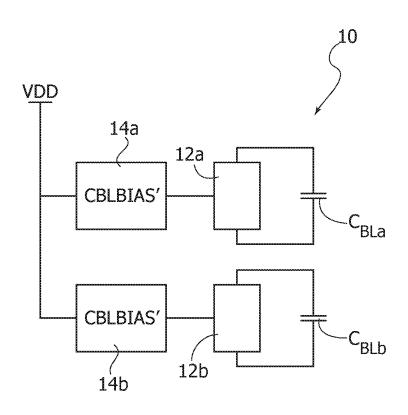

Come esemplificato nelle figure 5 e 6, un blocco di circuito di memoria 10 comprende una pluralità di array di celle di memoria accoppiate a bitline comuni che presentano rispettive capacità di bitline  $C_{BLa}$ ,  $C_{BLb}$  e ciascuna accoppiata a un rispettivo amplificatore di rilevamento 12a, 12b.

Per esempio, l'amplificatore di rilevamento 12 esemplificato nella Figura 2 è configurato per leggere wordline con K=79 bit, ciascuna selezionata asserendo al livello "alto" un solo segnale di segnale di controllo (per esempio YO UP; e YO DW; per selezionare K bitline e il WL UPx

per selezionare le K celle di bit di tali K bitline nella riga  $\mathbf{x}$ ) e un bit di riferimento VISENSE, in un modo di per sé noto.

Di conseguenza, durante la fase di pre-carica t2-t3 come esemplificata nella Figura 4, viene caricato un totale di 79 UP e 79 DW capacità di bitline equivalenti  $C_{\rm BL}$ .

In un caso esemplificativo in cui il circuito di precarica 14 come esemplificato nella Figura 3 è accoppiato al circuito di amplificatore di rilevamento esemplificato nella Figura 2, il livello di tensione di alimentazione nel secondo nodo VBLBIAS può essere calcolato come:

$$VBLBIAS=VDD \times \frac{CBLBIAS}{CBLBIAS + 2 \times 79 \times CBL}$$

dove CBL è la capacità equivalente della bitline BL.

Come esemplificato nella Figura 5, un singolo circuito di pre-carica 14 comprendente una capacità di accumulo CBLBIAS può essere accoppiato a ciascun amplificatore di rilevamento nella pluralità di amplificatori di rilevamento 12a, 12b per fornire a essi la tensione di polarizzazione VBLBIAS.

Nell'esempio considerato, una metallizzazione dedicata 140 può essere progettata al fine di sostenere i valori di picco di corrente (per esempio, circa 500 mA) nell'accoppiamento di questa capacità di accumulo relativamente grande CBLBIAS alle capacità di bitline  $C_{BLa}$ ,  $C_{BLb}$ .

In un caso alternativo come esemplificato nella Figura 6, la memoria 10 comprende una pluralità di circuiti di precarica 14a, 14b e una pluralità di circuiti amplificatori di rilevamento 12a, 12b, in cui ogni bitline (per esempio, C<sub>BLa</sub>) presenta un rispettivo amplificatore di rilevamento (per

esempio, 12a) e un rispettivo circuito di pre-carica (per esempio, 14a) accoppiato a essa, il rispettivo circuito di pre-carica presentando una capacità di accumulo configurata per fornire una frazione del valore totale di capacità di accumulo utilizzato per caricare tutte le capacità di bitline  $C_{BLa}$ ,  $C_{BLb}$ .

In un caso esemplificativo in cui la pluralità di bitline  $C_{BLa}$ ,  $C_{BLb}$  presenta una capacità equivalente totale circa il doppio di settantanove volte una singola capacità di bitline  $C_{BL}$  ( $2\times79\times CBL$ ) e ogni circuito amplificatore di rilevamento 12a, 12b comprende un amplificatore di rilevamento 12 come esemplificato in Figura 2, ogni circuito di pre-carica della pluralità di circuiti di pre-carica 12a, 12b può essere dotato di una capacità di accumulo CBLBIAS' che è una frazione della singola capacità di accumulo CBLBIAS utilizzata nella disposizione esemplificata nella Figura 5, per esempio CBLBIAS'=CBLBIAS/79.

Come esemplificata nella Figura 6, questa disposizione può ridurre un valore di picco di corrente (per esempio, da 500 mA a 6,3 mA) e rendere più gestibile con mezzi di connessione elettrica relativamente semplici fornire correnti adatte a caricare le capacità di bitline  $C_{\rm BLa}$ ,  $C_{\rm BLb}$  tramite i rispettivi circuiti di pre-carica 12a, 12b.

Si comprenderà d'altronde che le varie singole opzioni di implementazione esemplificate in tutte le figure che accompagnano questa descrizione non sono necessariamente destinate ad essere adottate nelle stesse combinazioni esemplificate nelle figure. Una o più forme di attuazione possono quindi adottare queste opzioni (d'altronde non imperative) singolarmente e/o in combinazioni diverse rispetto alla combinazione esemplificata nelle figure

allegate.

Senza pregiudizio per i principi sottostanti, i dettagli e le forme di attuazione possono variare, anche in modo significativo, rispetto a quanto è stato descritto in precedenza solo a titolo di esempio, senza allontanarsi dall'estensione di protezione. L'estensione di protezione è determinata dalle rivendicazioni allegate.

# RIVENDICAZIONI

### 1. Procedimento, comprendente:

accedere (12; 12a, 12b) a celle di memoria in un array di celle di memoria (MC1, MCx, MCN) che immagazzinano rispettivi segnali di dati ( $I_{DATA}$ ), in cui celle di memoria (MC1) nell'array di celle di memoria (MC1, MCx, MCN) presentano un primo nodo selettivamente accoppiabile (S1) a rispettivi rami di bitline in un primo insieme di rami di bitline (BL\_UP1, BL\_UPi, BL\_UPK) e un secondo nodo (S1) selettivamente accoppiabile a rispettivi rami di bitline in un secondo insieme di rami di bitline (BL\_DW1, BL\_DW1, BL\_DW1,

in cui il primo insieme di rami di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>i</sub>, BL\_UP<sub>k</sub>) e il secondo insieme di rami di bitline (BL\_DW<sub>1</sub>, BL\_DW<sub>k</sub>) forniscono almeno una capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) configurata per immagazzinare un livello di carica di polarizzazione in risposta all'essere caricata,

in cui il procedimento comprende:

fornire una capacità di accesso (CBLBIAS) riferita a massa (GND) e applicare (M14, PRECH,  $t_0$ ) a essa un livello di tensione di polarizzazione (VDD), in cui un corrispondente livello di carica di polarizzazione è caricato sulla capacità di accesso (CBLBIAS),

interrompere (M14, PREPRECH,  $t_1$ ) l'applicazione di detto livello di tensione di polarizzazione (VDD) alla capacità di accesso (CBLBIAS),

accoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_2$ ) la capacità di accesso (CBLBIAS; CBLBIAS') al primo insieme di bitline (BL\_UP<sub>1</sub>, BL UP<sub>1</sub>, BL UP<sub>K</sub>) e al secondo insieme di bitline (BL DW<sub>1</sub>,

BL  $UP_i$ , BL  $UP_K$ ),

caricare  $(t_2,\ t_3)$  la almeno una capacità di bitline  $(C_{BL};$   $C_{BLa},\ C_{BLb})$  a detto livello di carica di polarizzazione,

disaccoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_3$ ) la capacità di accesso (CBLBIAS; CBLBIAS') dalla almeno una capacità di bitline ( $C_{BL}$ ;  $C_{BL}a$ ,  $C_{BL}b$ ),

selezionare (16) almeno una cella di memoria ( $MC_1$ ) nell'array di celle di memoria ( $MC_1$ ,  $MC_X$ ,  $MC_N$ ) e accoppiare (PRECH, SAEN,  $S_1$ ) il primo nodo della cella di memoria selezionata ( $MC_1$ ) al rispettivo ramo di bitline ( $BL_UP_1$ ) nel primo insieme di rami di bitline ( $BL_UP_1$ ,  $BL_UP_i$ ,  $BL_UP_K$ ) e il secondo nodo della cella di memoria selezionata ( $MC_1$ ) alla rispettiva bitline ( $BL_DW_1$ ) nel secondo insieme di rami di bitline ( $BL_DW_1$ ,  $BL_DW_K$ ) e

rilevare (12; 12a, 12b) una variazione del livello di carica immagazzinata nella capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) rispetto a detto livello di carica di polarizzazione, in cui detta variazione del livello di carica è indicativa del segnale di dati ( $I_{DATA}$ ) memorizzato nella cella di memoria selezionata ( $MC_1$ ).

- 2. Procedimento secondo la rivendicazione 1, in cui l'array di celle di memoria ( $MC_1$ ,  $MC_i$ ,  $MC_N$ ) è un array planare comprendente una pluralità di rami di bitline ( $BL_UP_1$ ,  $BL_UP_i$ ,  $BL_UP_K$ ,  $BL_DW_1$ ,  $BL_DW_i$ ,  $BL_DW_K$ ) che forniscono rispettive capacità di bitline ( $C_{BLa}$ ,  $C_{BLb}$ ) configurate per immagazzinare su di esse rispettivi livelli di polarizzazione di carica.

- 3. Procedimento secondo la rivendicazione 2, comprendente:

accoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_2$ ) la capacità di accesso caricata (CBLBIAS) alla pluralità di rami di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>K</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>K</sub>) rendendo selettivamente conduttivo (PRECH) almeno un percorso di flusso di corrente (120) tra un primo nodo di capacità (VBLBIAS) e la pluralità di rami di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>K</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>K</sub>),

caricare  $(t_2, t_3)$  la pluralità di capacità di bitline  $(C_{BL}; C_{BLa}, C_{BLb})$  ai rispettivi livelli di carica di polarizzazione tramite una corrente di polarizzazione  $(I_{PRECH})$  che scorre attraverso detto almeno un percorso di flusso di corrente (120),

disaccoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_3$ ) la capacità di accesso (CBLBIAS) dalla pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_2$ ,  $BL_UP_3$ ,  $BL_DW_3$ ,  $BL_DW_3$ ,  $BL_DW_3$ ) rendendo selettivamente non conduttivo (PRECH) l'almeno un percorso di flusso di corrente (120) tra detto primo nodo di condensatore (VBLBIAS) e le capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) della pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_3$ ,  $BL_UP_3$ ,  $BL_UP_3$ ,  $BL_DW_3$ ,  $BL_DW_3$ ,  $BL_DW_3$ ).

4. Procedimento secondo la rivendicazione 2, in cui il procedimento comprende:

fornire una pluralità di condensatori (CBLBIAS') ciascuno avente una capacità pari a una rispettiva frazione di detta capacità di accesso (CBLBIAS) riferita a massa (GND), e

applicare (14a, 14b,  $t_0$ ) un livello di tensione di polarizzazione (VDD) alla pluralità dei condensatori (CBLBIAS'), caricando una rispettiva carica sulla pluralità di condensatori (CBLBIAS'),

interrompere (14a, 14b, t<sub>1</sub>) l'applicazione di detto

livello di tensione di polarizzazione (VDD) alla pluralità di condensatori (CBLBIAS'),

accoppiare (12a, 12b t<sub>2</sub>) la capacità caricata (CBLBIAS) alla pluralità di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>i</sub>, BL\_UP<sub>K</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>K</sub>) rendendo selettivamente conduttiva (PRECH) una pluralità di percorsi di flusso di corrente tra la pluralità di condensatori (CBLBIAS') e la pluralità di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>i</sub>, BL\_UP<sub>K</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>i</sub>, BL\_DW<sub>K</sub>) e caricare (t<sub>2</sub>, t<sub>3</sub>) la pluralità di capacità di bitline (CBLa, CBLb) ai rispettivi livelli di carica di polarizzazione tramite correnti che scorrono attraverso detta pluralità di percorsi di flusso di corrente, in cui dette correnti sono una frazione di detta corrente di polarizzazione (IPRECH), e

disaccoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_3$ ) la pluralità di capacità (CBLBIAS') dalla pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_2$ ) rendendo selettivamente non conduttiva (PRECH) la pluralità di percorsi di flusso di corrente tra la pluralità di condensatori (CBLBIAS') e la pluralità di bitline ( $BL_UP_1$ ,  $BL_DW_1$ ,  $BL_DW_2$ ,  $BL_DW_3$ ).

# 5. Procedimento secondo la rivendicazione 3 o la rivendicazione 4, comprendente inoltre:

selezionare (16) una pluralità di celle di memoria ( $MC_1$ ,  $MC_N$ ) nell'array di celle di memoria ( $MC_1$ ,  $MC_1$ ,  $MC_1$ ,  $MC_N$ ) e accoppiare (PRECH, SAEN,  $S_1$ ) un primo e un secondo nodo della pluralità selezionata di celle di memoria a rispettive bitline in detta pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_K$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ), e

rilevare (12a, 12b) una pluralità di variazioni dei livelli di carica immagazzinati nelle rispettive capacità di

bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) di detta pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_2$ ) rispetto a detti rispettivi livelli di carica di polarizzazione, in cui detta pluralità di variazioni dei livelli di carica sono indicativi di segnali di dati ( $I_{DATA}$ ) memorizzati nella pluralità selezionata di celle di memoria ( $MC_1$ ,  $MC_N$ ).

## 6. Circuito (12, 14), comprendente:

una circuiteria di amplificatore di rilevamento (12; 12a, 12b) configurata per accedere (12; 12a, 12b) a celle di memoria in un array di celle di memoria ( $MC_1$ ,  $MC_x$ ,  $MC_N$ ) che memorizzano rispettivi segnali di dati (IDATA), in cui le celle di memoria (MC1) nell'array di celle di memoria (MC1, presentano un primo nodo selettivamente  $MC_N$ ) accoppiabile (S1) a rispettivi rami di bitline in un primo insieme di rami di bitline (BL UP1, BL UP1, BL UPK) e un secondo nodo (S1) selettivamente accoppiabile a rispettivi rami di bitline in un secondo insieme di rami di bitline (BL  $DW_1$ , BL  $DW_i$ , BL  $DW_K$ ), in cui il primo insieme di rami di bitline (BL UP1, BL UP1, BL UPK) e il secondo insieme di rami di bitline (BL DW<sub>1</sub>, BL DW<sub>i</sub>, BL DW<sub>K</sub>) forniscono almeno una capacità di bitline (CBL; CBLa, CBLb) configurata per immagazzinare un livello di carica di polarizzazione in risposta all'essere caricata,

in cui la circuiteria di amplificatore di rilevamento (12, 12a, 12b) è inoltre configurata per:

selezionare (16) almeno una cella di memoria ( $MC_1$ ) nella array di celle di memoria ( $MC_1$ ,  $MC_x$ ,  $MC_N$ ) e accoppiare (PRECH, SAEN,  $S_1$ ) il primo nodo della cella di memoria selezionata ( $MC_1$ ) al rispettivo ramo di bitline ( $BL_UP_1$ ) nel primo insieme di rami di bitline ( $BL_UP_1$ ,  $BL_UP_K$ ) e il

secondo nodo della cella di memoria selezionata (MC1) alla rispettiva bitline (BL\_DW1) nel secondo insieme di rami di bitline (BL DW1, BL DW1, BL DWK) e

rilevare (12; 12a, 12b) una variazione del livello di carica immagazzinata nella capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) rispetto a detto livello di carica di polarizzazione, in cui detta variazione del livello di carica è indicativa del segnale di dati ( $I_{DATA}$ ) memorizzato nella cella di memoria selezionata ( $MC_1$ ).

il circuito comprendendo inoltre:

una circuiteria di pre-carica (14; 14a, 14b) comprendente una capacità (CBLBIAS) riferita a massa (GND) e una circuiteria di alimentazione (VDD) configurata per fornire un livello di tensione di polarizzazione (VDD), la capacità (CBLBIAS) presentando un nodo (VBLBIAS) selettivamente accoppiabile (M14) alla circuiteria di alimentazione (VDD),

una circuiteria di controllo (20) accoppiata alla circuiteria di pre-carica (14, 14a, 14b) e configurata per pilotare la circuiteria di pre-carica (14, 14a, 14b) per:

accoppiare la circuiteria di alimentazione (VDD) alla capacità (CBLBIAS) e applicare (M14, PRECH,  $t_0$ ) a essa un livello di tensione di polarizzazione (VDD), in cui un corrispondente livello di carica di polarizzazione viene caricato sulla capacità di accesso (CBLBIAS),

interrompere (M14, PREPRECH,  $t_1$ ) l'applicazione di detto livello di tensione di polarizzazione (VDD) alla capacità di accesso (CBLBIAS),

la circuiteria di controllo accoppiata inoltre alla circuiteria di amplificatore di rilevamento (12, 12a, 12b) e configurata inoltre per pilotare la circuiteria di

amplificatore di rilevamento (12, 12a, 12b) per:

accoppiare (MuP, MDW, PRECH,  $t_2$ ) la capacità di accesso (CBLBIAS; CBLBIAS') al primo insieme di bitline (BL\_UP1, BL\_UP1, BL\_UP1, BL\_UPK) e al secondo insieme di bitline (BL\_DW1, BL\_UP1, BL\_UPK),

caricare  $(t_2,\ t_3)$  la almeno una capacità di bitline  $(C_{BL};$   $C_{BLa},\ C_{BLb})$  a detto livello di carica di polarizzazione,

disaccoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_3$ ) la capacità di accesso (CBLBIAS; CBLBIAS') dalla almeno una capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ).

- 7. Circuito secondo la rivendicazione 6, in cui l'array di celle di memoria ( $MC_1$ ,  $MC_i$ ,  $MC_N$ ) è un array planare comprendente una pluralità di rami di bitline ( $BL_UP_1$ ,  $BL_UP_i$ ,  $BL_UP_K$ ,  $BL_DW_1$ ,  $BL_DW_i$ ,  $BL_DW_K$ ) che forniscono rispettive capacità di bitline ( $C_{BLa}$ ,  $C_{BLb}$ ) configurate per immagazzinare rispettivi livelli di carica di polarizzazione su di esse.

- 8. Procedimento secondo la rivendicazione 7, in cui la circuiteria di pre-carica (12a, 12b) comprende una pluralità di condensatori (CBLBIAS') ciascuno avente una capacità riferita a massa (GND) pari a una rispettiva frazione di detta capacità di accesso (CBLBIAS), e

in cui il circuito di controllo è configurato per pilotare la circuiteria di pre-carica (12a, 12b) per:

accoppiare la circuiteria di alimentazione (VDD) alla pluralità di condensatori (CBLBIAS') e applicare (M14, PRECH,  $t_0$ ) a essa il livello di tensione di polarizzazione (VDD), caricando i condensatori nella pluralità di condensatori (CBLBIAS') con una rispettiva frazione di

carica su di essi,

interrompere (14a, 14b, PREPRECH, t1) l'applicazione di detto livello di tensione di polarizzazione (VDD) alla pluralità di condensatori (CBLBIAS'),

in cui il circuito di controllo è configurato per pilotare la circuiteria di amplificatore di rilevamento (12a, 12b) per:

accoppiare (14a, 14b,  $t_2$ ) condensatori nella pluralità dei condensatori (CBLBIAS') a bitline nella pluralità di bitline (BL\_UP1, BL\_UP1, BL\_UPK, BL\_DW1, BL\_DW1, BL\_DWK) rendendo selettivamente conduttiva (PRECH) una pluralità di percorsi di flusso di corrente tra la pluralità di condensatori (CBLBIAS') e la pluralità di bitline (BL\_UP1, BL\_UP1, BL\_UPK, BL\_DW1, BL\_DW1, BL\_DWK) e caricare ( $t_2$ ,  $t_3$ ) la pluralità di capacità di bitline ( $C_{BLa}$ ,  $C_{BLb}$ ) a rispettivi livelli di carica di polarizzazione tramite correnti che scorrono attraverso detta pluralità di percorsi di flusso di corrente, in cui dette correnti sono una frazione di detta corrente di polarizzazione ( $I_{PRECH}$ ),

disaccoppiare ( $M_{UP}$ ,  $M_{DW}$ , PRECH,  $t_3$ ) la pluralità di condensatori (CBLBIAS') dalla pluralità di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>K</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>K</sub>) rendendo selettivamente non conduttiva (PRECH) la pluralità di percorsi di flusso di corrente tra la pluralità di condensatori (CBLBIAS') e la pluralità di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_UP<sub>1</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>1</sub>, BL\_DW<sub>K</sub>).

9. Circuito secondo la rivendicazione 7 o la rivendicazione 8, in cui la circuiteria di controllo (20) è inoltre configurata per pilotare la circuiteria di amplificatore di rilevamento (12, 12a, 12b) per:

selezionare (16) una pluralità di celle di memoria ( $MC_1$ ,  $MC_N$ ) nell'array di celle di memoria ( $MC_1$ ,  $MC_1$ ,  $MC_1$ ,  $MC_N$ ) e accoppiare (PRECH, SAEN,  $S_1$ ) un primo e un secondo nodo della pluralità selezionata di celle di memoria ( $MC_1$ ,  $MC_N$ ) alle rispettive bitline ( $BL_UP_1$ ,  $BL_UP_N$ ,  $BL_DW_1$ ,  $BL_DW_N$ ) in detta pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_2$ ,  $BL_UP_3$ ,  $BL_UP_4$ ,  $BL_UP_5$ ,  $BL_UP_6$ ,  $BL_$

rilevare (12a, 12b) una pluralità di variazioni dei livelli di carica immagazzinata nelle rispettive capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) di detta pluralità di bitline ( $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_UP_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ,  $BL_DW_1$ ) rispetto a detti rispettivi livelli di carica di polarizzazione, in cui detta pluralità di variazioni dei livelli di carica è indicativa di segnali di dati ( $I_{DATA}$ ) memorizzati nella pluralità selezionata di celle di memoria ( $MC_1$ ,  $MC_N$ ).

10. Dispositivo di memorizzazione dati non volatile (10), comprendente:

un array di celle di memoria (MC1, MC1, MCN) comprendente celle di memoria configurate per memorizzare rispettivi segnali di dati ( $I_{DATA}$ ),

almeno una bitline (BL) comprendente un primo insieme di rami di bitline (BL\_UP<sub>1</sub>, BL\_UP<sub>i</sub>, BL\_UP<sub>K</sub>) e un secondo insieme di rami di bitline (BL\_DW<sub>1</sub>, BL\_DW<sub>i</sub>, BL\_DW<sub>K</sub>) che forniscono almeno una capacità di bitline ( $C_{BL}$ ;  $C_{BLa}$ ,  $C_{BLb}$ ) configurata per immagazzinare un livello di carica di polarizzazione su di essa in risposta all'essere caricata,

in cui le celle di memoria  $(MC_1)$  nell'array di celle di memoria  $(MC_1, MC_x, MC_N)$  presentano un primo nodo selettivamente accoppiabile  $(S_1)$  a rispettivi rami di bitline nel primo insieme di rami di bitline  $(BL_UP_1, BL_UP_i, BL_UP_K)$

e presentano un secondo nodo selettivamente accoppiabile a rispettivi rami di bitline nel secondo insieme di rami di bitline (BL  $DW_1$ , BL  $DW_K$ ),

il circuito (12, 14) secondo una qualsiasi delle rivendicazioni 6 a 9, in cui detta circuiteria di amplificatore di rilevamento (12, 12a, 12b) è configurata per accedere a quelle selezionate di dette celle di memoria nell'array di celle di memoria ( $MC_1$ ,  $MC_1$ ,  $MC_N$ ).

FIG. 4

FIG. 5

FIG. 6