**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

**(51) Int. Cl.<sup>6</sup>**

**G11B 20/10**

**(45) 공고일자** 2003년08월21일

**(11) 등록번호** 10-0385248

**(24) 등록일자** 2003년05월13일

|             |                                                                                                                                                                   |             |                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|

| (21) 출원번호   | 10-1995-0705652                                                                                                                                                   | (65) 공개번호   | 특 1996-0703261 |

| (22) 출원일자   | 1995년 12월 08일                                                                                                                                                     | (43) 공개일자   | 1996년 06월 19일  |

| 번역문제출일자     | 1995년 12월 08일                                                                                                                                                     |             |                |

| (86) 국제출원번호 | PCT/IB1995/00165                                                                                                                                                  | (87) 국제공개번호 | WO 1995/27977  |

| (86) 국제출원일자 | 1995년 03월 13일                                                                                                                                                     | (87) 국제공개일자 | 1995년 10월 19일  |

| (81) 지정국    | 국내특허 : 오스트레일리아 브라질 일본 대한민국 폴란드 싱가포르 EA<br>유라시아특허 : 러시아<br>EP 유럽특허 : 오스트리아 벨기에 스위스 리히텐슈타인 사이프러스 독<br>일 덴마크 스페인 핀란드 프랑스 영국 그리스 아일랜드 이탈리아<br>룩셈부르크 모나코 네덜란드 포르투칼 스웨덴 |             |                |

(30) 우선권주장

225193 1994년04월08일 미국(US)

253535 1994년06월03일 미국(US)

(73) 특허권자

코닌클리케 필립스 일렉트로닉스 엔.브이.

네델란드왕국, 아인드호펜, 그로네보드스베그 1

(72) 발명자

로날드 빌헬름 요한 요제프 자에이스

네델란드, 베아 아인드호펜 5621, 그로네보드세베그 1

임란 샤

미국, 뉴욕 10562, 오시닝, 허드슨 뷰 힐 30

타카시 사토

일본국 도쿄도 114 기타구 맘유죠 1-15-10

(74) 대리인

이병호

**신사관 : 한충희**

**(54) 기록캐리어상에MPEG정보를기록하고기록캐리어로부터MPEG정보를재생하는방법**

**영세서**

**<1> 관련 출원**

본 출원은 공동 양도된 출원의 연속 출원으로서, W. J. Van Gestal, R. W. J. J. Saeijs 및 I. A. Shah에 의해 발명의 명칭이 "기록 캐리어 상에 MPEG 정보를 기록하고 기록 캐리어로부터 MPEG 정보를 재생하는 방법"이고 1994년 4월 8일자 출원된 일련 번호 제08/225.193호이다.

**<3> 발명의 배경**

본 발명은 기록 캐리어 상의 트랙에 정보 신호를 기록하는 기록 장치에 관한 것으로서, 상기 장치는,

<5> - 정보 신호를 수신하는 입력 단자와,

<6> - 상기 기록 캐리어 상의 트랙에 기록을 위해 적당한 채널 신호를 얻기 위해 정보 신호를 채널 인코딩하는 채널 인코딩 수단과,

<7> - 트랙에 채널 신호를 기록하는 기록 수단으로서, 상기 채널 신호는 순차 또는 연속 신호 블록을 구비하고, 각각의 신호 블록은 동기화 신호를 구비한 제1 블록 섹션과, 다수의 채널 바이트 구비한 제2 블록 섹션을 포함하고, 기록 장치에 따라 얻어진 기록 캐리어에 기록하여, 그 기록 캐리어의 정보 신호를 재생하는 재생장치에 기록 수단을 포함한다.

<8> 서두에 주어진 기록 장치는 본 출원의 끝 부분에서 알 수 있는 참고문헌의 리스트 문서(1)의 EP A 492,704에 공지되어 있다.

<9> 상지 공지된 장치는 디지털 VCR(VDCR)과 같은 나선 주사형 기록 장치이고, 연속 트랙 내의 오디오 신호 기록 섹터 및 비디오 신호 기록 섹터 각각의 디지털 오디오 신호 및 디지털 비디오 신호를 구비하는 정보를 기록하는데, 여기서, 트랙을 기록할 때, 트랙 내의 비디오 신호 기록 섹터는 우선 처리되고, 이어서 오디오 신호 기록 섹터에 의해 처리된다.

<10> 그러나 섹터가 트랙에서 나타나는 순서는 역 순서로 될 수 있다. 또한, 다른 섹터는 한 트랙의 시작부에 위치한 클럭 런-인 영역(clock run-in area)과 같은 한 트랙 내에 포함될 수 있어, 트랙으로부터 판독되는 신호에 따라 내부 시스템 클럭을 잠금(locking-in)시킬 수 있고, 프리앰프 및 포스트앰프 영역은 여러 섹터 사이에 위치하여 에디트 갭(edit gap)으로서 기능을 한다. 참조 문헌은, 참조 문헌중 리

스트 내에서 참조되어 이미 출원된 유럽 특허 출원 제93.202.950호에 대하여 이루어진 참조문헌(2)와, 참조문헌 중 리스트 내에 참조된 제93.201.263호의 참조문헌(3)이다.

<11> 종래 기술의 참조 문헌은 자기 테이프와 같은 길이 방향의 자기 기록 캐리어 상에 디지털 비디오 및 디지털 오디오를 기록하고 이 자기 기록 캐리어로부터 디지털 비디오 및 디지털 오디오를 재생할 수 있게 하는 신규한 디지털 비디오 카세트(DVC) 레코더 표준 방식을 실현하기 위한 제안에 관한 것이다. 그 신규한 디지털 비디오 기록기 장치 표준 방식은 소위 DVC 형태의 새로운 디지털 비디오 기록 장치 재생 장치로 유도된다.

## 본 발명의 개요

<13> 본 발명은 서두에 정의된 공지된 형태의 포맷으로 정보 신호의 다른 형태를 기록할 수 있는 기록 장치를 제공하는 것이다. 본 발명에 따른 기록 장치에 있어서, 정보 신호는 MPEG 포맷에 따른 MPEG 정보 신호이고, 그 MPEG 정보 신호는 시계열 혹은 순차 전송 패킷을 구비하며; 채널 인코딩 수단은 채널 신호의 y 신호 블록그룹의 제2 블록 섹션 내의 MPEG 정보 신호의 x 전송 패킷 내에 포함된 각각의 시간 정보를 기억하기 위해 채택되고; y 신호 블록 그룹의 최소한 제1 신호 블록의 제2 블록 섹션은 y 신호 블록 그룹의 제1 신호 블록이 되는 것으로 신호 클럭을 식별하는 식별 정보를 기억하는 제3 블록 섹션을 포함하며, x 및 y는  $x \geq 1$  및  $y \geq 1$ 과 같은 정수인 상기 기록 장치에 있어서, 정보인 것을 특징으로 하는 보다 특히, 신호는 MPEG 포맷에 따른 MPEG 정보 신호이고, 그 MPEG 정보 신호는 순차 전송 패킷을 구비하며; 채널 인코딩 수단은 채널 신호의 y 신호 블록 그룹의 제2 블록 섹션 내의 MPEG 정보 신호의 x 전송 패킷 내에 포함된 각각의 시간 정보를 기억하기 위해 채택되고; 신호 블록의 제2 블록 섹션은 신호 블록의 순서 번호에 관련된 순서 번호를 기억하는 제3 블록 섹션을 포함하며; x 및 y는  $x \geq 1$  및  $y \geq 1$ 과 같은 정수인 것을 특징으로 한다.

<14> 본 발명은 다음 인식을 기초로 한다. 참조 문헌 리스트의 문서(4)인 1994년 2월 22일자 Grand Alliance HDTV 시스템 명세 중, 특히 챕터(V 및 VI)에는 MPEG 정보 신호를 전송하는 전송 시스템의 설명이 있고, 그 정보 신호는 케이블 네트워크를 통해 전송 및 방송을 위해, 상응하는 데이터 디지털 정보 신호 및 데이터 압축된 디지털 정보 신호를 포함한다.

<15> 그 MPEG 정보 신호는 시간상 가변 길이 또는 동일 길이 중 하나를 갖는 전송 포맷 형태로 되어 있다. 그러나 두 경우에 있어서, 전송 패킷은 199 바이트 정보를 포함하고, 그 제1 바이트는 동기 바이트이다.

<16> 테이프로서 자기 기록 캐리어와 같은 기록 캐리어로부터 재생에 따른 기록형태인 MPEG 정보 신호의 전송은 공지된 테이프 포맷을 통해 그와 같은 종류의 전송을 실현하기 위해 취해지는 특정 측정을 필요로 한다. 보다 특히, 본 발명은 공지된 테이프 포맷의 신호 블록 내에 전송 패킷을 기억하는 것에 관한 것이다.

<17> 일반적으로, 다수의 y개의 신호 블록 내에 MPEG 정보 신호의 다수의 x개의 전송 패킷 내에 포함된 정보를 기억할 때, 약간의 점유되지 않은 공간은 부가 정보 기억을 위해 y개의 신호 블록 내에 이용될 수 있도록 유지되고, 그 부가 정보는 기록 캐리어 상에 MPEG 정보를 기록하고 기록 캐리어로부터 MPEG 정보를 재생하는 특정한 응용에 관한 것이다. DVC 포맷의 특정 예에 있어서, 5개의 신호 블록의 제2 블록 섹션이다. 지금, 11 바이트( $= 5 \times 77 - 2 \times 187$ )는 5개의 신호 블록 내에 이용 가능하게 유지된다. 그들 11 바이트는 제3 블록 섹션을 얻기 위해 여러 방법으로 5개의 신호 블록 중 제2 블록 섹션을 통해 분할될 수 있다. 그와 같은 방법 중 하나는 모든 제2 블록 섹션 중 첫 번째 2개의 바이트는 제3 블록 섹션으로 이용될 수 있고, 최종 바이트는 5개의 신호 블록에 기억되는 2개의 전송 패킷의 정보 사이의 경계를 나타내는 제3 블록 섹션으로 고려될 수 있다.

<18> 상기 실시예에 있어서, y 신호 블록 그룹의 제1 신호 블록이 되는 신호 블록을 식별하는 식별 정보는 y 신호 블록 그룹 내의 제1 신호 블록의 제3 블록 섹션에 기억될 수 있다.

<19> 또한, 신호 블록의 순차에 관련된 순차 번호 정보(순차 번호)는 제3 블록 섹션에 기억될 수 있다. 그 순차 번호는 연속 카운터로 식별될 수도 있다. 이러한 제시된 측정은 여러 장점을 얻는다.

<20> 신호 블록 그룹 내의 제1 신호 블록으로 한 신호 블록을 식별하는 식별 정보를 이용하는 장점은 그룹의 시작부가 검출될 수 있고, 재생 동안 데이터의 판독을 간단히 할 수 있다는 점이다.

<21> 순차 번호를 이용하는 한 장점은, 신호 블록을 재생할 때, 순차 번호의 검색에 따라, 한 신호 블록이 재생의 예러로 인한 오류가 존재하는지의 여부를 결정할 수 있어, 예러 보정 또는 은폐를 실행시킬 수 있다는 점이다. 다른 장점은 기록에 따라 신호 블록 내에 기억될 수 있는 정보를 서플 처리할 수 있다는 점이다. 순차번호의 검색에 따라, 원래의 데이터 스트림을 얻기 위하여 검색된 순차 번호에 응답하여 상응하는 디셔플 처리를 실현할 수 있다.

<22> 또한, 신호 블록의 제3 블록 섹션 내에 포함된 순차 번호를 갖는다는 것은, 그들 신호 블록 내에 기억된 MPEG 데이터 스트림의 전송 재킷이 기록 및 순차 재생 단계 동안 발생할 수 있는 예러에 대해 보다 높게 보호할 필요성이 있는 경우에 신호 블록을 반복시킬 수 있다.

<23> 또한, 서두에 설명된 기록 장치에 있어서, 정보 신호는 MPEG 포맷에 따른 MPEG 정보 신호이고, 그 MPEG 정보 신호는 순차 전송 패킷을 구비하며; 채널 인코딩 수단은 채널 신호의 상기 신호 블록 중 y개의 제1 신호 블록의 제1 그룹의 제2 블록 섹션 내의 MPEG 정보 신호의 x개의 전송 패킷 내에 포함된 각각의 시간 정보를 기억하기 위해 채택되어, 정상 플레이 재생 모드 동안 y개의 제1 신호 블록 중 상기 제1 그룹 내에 기억된 비디오 정보를 이용하여 정상 플레이 모드를 가능하게 하고; 상기 채널 인코딩 수단은 MPEG 정보로부터 트릭 모드 비디오 신호를 검색하고, 채널 신호의 상기 신호 블록 중 z개의 제2 신호 블록 중 제2 그룹의 제2 블록 섹션 내의 상기 트릭 모드 비디오 신호에 더 채택되어, 상기 제2 신호 블록 내에 기억된 비디오 정보를 사용하여 트릭 플레이 모드를 실행하며; 제1 및 제2 신호 블록 중 제1 및 제2 그룹의 각각 내에 최소한 하나의 신호 블록의 제2 블록 섹션은 그룹이 제1 신호 블록 또는 제2 신호 블록을 구비하는지의 여부를 식별하는 식별 정보를 기억하는 제3 블록 섹션을 각각 포함하며; x, y 및 z는 x

$\geq 1$ ,  $y > 1$  및  $z > 1$ 과 같은 정수인 것을 특징으로 한다. 보다 특히, 신호는 MPEG 포맷에 따른 MPEG 정보 신호이고, 그 MPEG 정보 신호는 순차 또는 연속 전송 패킷을 구비하며; 채널 인코딩 수단은 채널 신호의  $y$ 개의 신호 블록 그룹의 제2 블록 섹션 내의 MPEG 정보 신호의  $x$ 개의 전송 패킷 내에 포함된 각각의 시간 정보를 기억하기 위해 채택되고; 전송 패킷의 시작부를 포함하는  $y$ 개의 신호 블록 그룹의 최소한 그들 신호 블록의 제2 블록 섹션은 신호 블록의 제2 블록 섹션에 기억된 그 시작부를 갖는 전송 포맷에 상응하는 전송 패킷 순서 번호에 관련된 순차 번호 정보를 기억하는 제3 블록 섹션을 포함하며,  $x$  및  $y$ 는  $x \geq 1$  및  $y > 1$ 과 같은 정수인 것을 특징으로 한다. 이는 제1 신호 블록을 사용하는 정상 플레이 모드에서 재생 장치의 재생과, 제1 신호 블록 또는 제2 신호 블록 각각을 포함하는 그룹을 나타내는 정보의 검출에 응답하여, 제2 신호 블록을 사용하는 트릭 플레이 모드에서 재생을 가능하게 한다.

<24> 또한, 서두에 설명된 기록 장치에 있어서, 제1 및 제2 신호 블록 그룹의 각각 제1 및 제2 그룹 내의 모든 신호 블록의 제2 블록 섹션은 제1 신호 블록 또는 제2 신호 블록을 그룹이 포함하는지의 여부를 표시하는 식별 정보를 각각 포함하는 것을 특징으로 한다. 보다 특히,  $y$  신호 블록 그룹의 제2 블록 섹션은 상기 신호 블록 내에 기억된 전송 패킷 정보에 상응하는 전송 패킷 순차 번호와 관련된 순차 번호 정보를 기억하는 제3 블록 섹션을 각각 포함한다.

<25> 패킷 순차 번호를 기억하는 것은, MPEG 데이터 스트림이 일정한 비트 또는 전송 속도를 가지고 수신된다면 그 장점을 가지며, MPEG 데이터 스트림 내에 인터리브된 다수의 상이한 비디오 프로그램을 포함한다. 일반적으로, 그와 같은 데이터 스트림은 기록 캐리어 상에 전체 데이터 스트림을 기록하기 위해 너무 큰 비트 전송 속도를 갖는다. 전형적으로, MPEG 비트 전송 속도는 45Mbps지만, 전형적인 기록 캐리어는 25Mbps 비트 전송 속도로 기록한다.

<26> 지금, 그 기록 장치는 한 비디오 프로그램을 검색하는 프로그램 센터와, 기록을 위한 MPEG 정보 신호를 얻기 위해 MPEG 데이터 스트림으로부터 상응하는 오디오 신호를 포함한다. 단지 하나의 비디오 프로그램에 상응하는 정보가 MPEG 전송 패킷 내에 포함될 때, 그와 같은 프로그램 선택기는 상기 단지 하나의 프로그램에 상응하는 정보를 포함하는 MPEG 데이터 스트림으로부터 단지 그들 전송 패킷을 선택한다. 상기 의미는 수신된 원래의 MPEG 데이터 스트림의 약간의 패킷은 삭제된다는 것이다. 그러나 재생에 따라, 지금 단지 하나의 비디오 프로그램을 포함하는 MPEG 신호에 따른 MPEG 비디오 신호는 재형성되거나, 재작성된다. 그와 같은 재형성된 데이터 스트림은 동일한 위치에서 기록에 따라 선택되었던 전송 패킷을 가져야 하고, 하나 또는 다른 방법에 있어서, 기록에 따라 삭제된 패킷에 상응하는 더미 패킷은 재생된 데이터 스트림에 삽입되어야 한다. 기록함에 따라, 각각의 수신된 전송 패킷에 순차 번호가 부가되는데, 즉, 여러 패킷에 대해 삭제될 것이다. 선택 및 기억된 패킷의 순차 번호는 전송 패킷이 기억된 신호 블록의 제3 블록 섹션에 기억된다. 재생에 따라, 번호의 순차는 순차 번호가 다음 고차 번호가 될 필요성이 없는지를 검색한다. 상기 상태에서, 하나 또는 다수의 더미 패킷은 원래의 MPEG 데이터 스트림의 사본(replica)을 재형성하기 위해 삽입되어야 한다.

<27> 서두에 설명된 기록 장치에 있어서, 정보 신호는 MPEG 포맷에 따른 MPEG 정보 신호이고, 그 MPEG 정보 신호는 순차 전송 패킷을 구비하며; 기록 장치는 전송 패킷의 수신량을 검출하여, 수신된 각각의 전송 패킷의 타이밍 정보를 발생하기 위한 검출 수단은 포함하고, 한 전송 패킷에 대한 타이밍 정보는 상기 전송 패킷의 상기 수신량에 상응하고, 채널 인코딩 수단은 채널 신호의  $y$ 개의 신호 블록 그룹의 제2 블록 섹션 내에 MPEG 정보 신호의  $x$ 개의 전송 패킷 내에 포함된 각각의 시간정보를 기억하기 위해 채택되고; 전송 패킷의 시작부를 포함하는  $y$ 개의 신호 블록 그룹의 최소한 그들 신호 블록의 제2 블록 섹션은 신호 블록의 제2 블록 섹션에 기억된 그 시작부를 갖는 상기 전송 포맷의 시간 정보를 기억하는 제3 블록 섹션을 포함하며;  $x$  및  $y$ 는  $x \geq 1$  및  $y > 1$ 과 같은 정수인 것을 더 특징으로 한다. 보다 특히,  $y$ 개의 신호 블록 그룹의 제2 블록 섹션은 상기 신호 블록의 제2 블록 섹션내에 기억된 정보를 갖는 전송 패킷에 상응하는 타이밍 정보를 기억하는 제3 블록 섹션을 각각 포함한다. 전송 패킷에 상응하는 타이밍 정보를 기억하는 것은, 기록장치에 전송 패킷의 수신 시간을 검출하는 검출 수단이 제공될 필요가 있다. 상기 수단은 MPEG 데이터 스트림이 가변 비트 전송 속도를 가지고, MPEG 데이터 스트림에서 인터리브된 상이한 다수의 비디오 프로그램을 포함할 때 유리하게 된다. 상기 기술한 것처럼, 일반적으로, 그러한 데이터 스트림은 기록 캐리어 상에 전체 데이터 스트림을 기억하기 위해 너무 큰 비트 전송 속도를 갖는다.

<28> 지금, 상기 기록 장치는 기록을 위한 MPEG 정보 신호를 얻기 위해 MPEG 데이터 스트림으로부터 상응하는 오디오 신호에 따른 하나의 비디오 프로그램을 검색하는 프로그램 선택기를 포함한다.

<29> 오직 하나의 비디오 프로그램에 상응하는 정보가 MPEG 전송 패킷에 포함될 때, 그러한 프로그램 선택기는 오로지 하나의 비디오 프로그램에 상응하는 정보를 포함하는 MPEG 데이터 스트림으로부터 오로지 그들 전송 패킷을 선택한다. 전송 패킷에 상응하는 타이밍 정보를 검출 및 기억시켜, 재생 장치는 타이밍 정보를 검색할 수 있고, 상기 타이밍 정보를 이용하여 MPEG 정보 신호를 재작성할 수 있다.

<30> 상기 기술한 수단은 기록 장치에서 한가지로 또는 서로 조합으로 적용될 수 있음을 주목한다. 과거적으로, 기록 캐리어는 기록 캐리어 상의 트랙에 기억된 신호 블록을 가지고 얻어지고, 동기 신호를 포함하고, 다수의 채널 바이트를 포함하는 제1 블록 섹션을 가지고 얻어질 수 있으며, MPEG 정보 신호의  $x$  개의 전송 패킷은 채널 신호의  $y$ 개의 신호 블록 그룹의 제2 블록 섹션에 기억된다. 또한, 본 발명에 따라,

<31> -  $y$ 개의 신호 블록 그룹의 최소한 제1 신호 블록의 제2 블록 섹션은  $y$ 개의 신호 블록 그룹의 제1 신호 블록이 되는 신호 블록을 식별하는 식별 정보를 기억하는 제3 블록 섹션을 포함하거나,

<32> - 상기 식별 정보는 순차 번호 정보이고,  $y$ 개의 신호 블록 그룹의 제2 블록 섹션은 상기 블록의 순차 번호에 관한 순차 번호 정보를 기억하는 제3 블록 섹션을 모두 포함하거나,

<33> - 신호 블록의 제2 블록 섹션은 신호 블록이 '정상 플레이' 데이터 또는 '트릭 모드' 데이터를 포함하는 여부를 나타내는 식별 정보를 기억하는 제3 블록 섹션을 각각 포함하거나,

<34> - 전송 패킷의 시작부를 포함하는  $y$ 개의 신호 블록의 그룹 내에 최소한 그들 신호 블록의 제2 블록 섹션은 신호 블록의 제2 블록 섹션에 기억된 그 시작부를 갖는 전송 패킷에 상응하는 전송 패킷 순차

번호에 관련된 식별 정보를 기억하는 제3 블록 섹션을 포함하거나,

<35> - 전송 패킷의 시작부를 포함하는 y개의 신호 블록의 그룹 내에 최소한 그들 신호 블록의 제2 블록 섹션은 신호 블록의 제2 블록 섹션에 기억된 그 시작부를 갖는 상기 전송 패킷에 타이밍 정보를 기억하는 제3 블록 섹션을 포함하거나,

<36> - 제3 블록 섹션은 상기 나열된 수단 중 하나 또는 다수의 조합의 결과로 얻은 정보를 포함한다.

<37> 기록 캐리어 상에 기록된 MPEG 정보 신호의 재생을 가능하게 하기 위하여, 기록 장치의 각각의 특정 실시예에 재생 장치가 채택될 필요성이 있음을 알 수 있다. 그와 같은 재생 장치는 재생 장치에 관련한 특허청구 범위의 요체이다.

<38> 또한, 본 발명은, 임의 임계 시간 정보의 변화 없이 비동기 채널을 통해 타이밍 임계 데이터를 전송하는 방법을 포함하는데, 다시 말해, 타이밍 임계 데이터에 대한 비동기 채널 전송시키는 전송 방법을 포함한다. 넓게 설명하면, 상기는 채널을 통해 전송하기 이전에 타이밍 정보에 따른 데이터를 형성시키는 하나 또는 그 이상의 전송 유닛을 태그(tag)하고, 그 후, 채널의 다른 단부에서 적당한 데이터 타이밍을 재작성하기 위해 태그된 정보를 이용하여 성취된다. 예를 들어, 상기 데이터는 MPG 정보 신호와, DVCR의 채널이 될 수 있다. 그러나 본 발명은 상기 출원에 제한을 두지 않고, 컴퓨터 네트워크, 전화기 네트워크 또는 디지털 인터페이스와 같은 비동기 채널에 적용될 수 있다.

### 도면의 간단한 설명

<39> 본 발명의 상기 및 다른 관점은 첨부된 도면과 이후에 설명하는 실시예를 참조하면 명백히 알 수 있다.

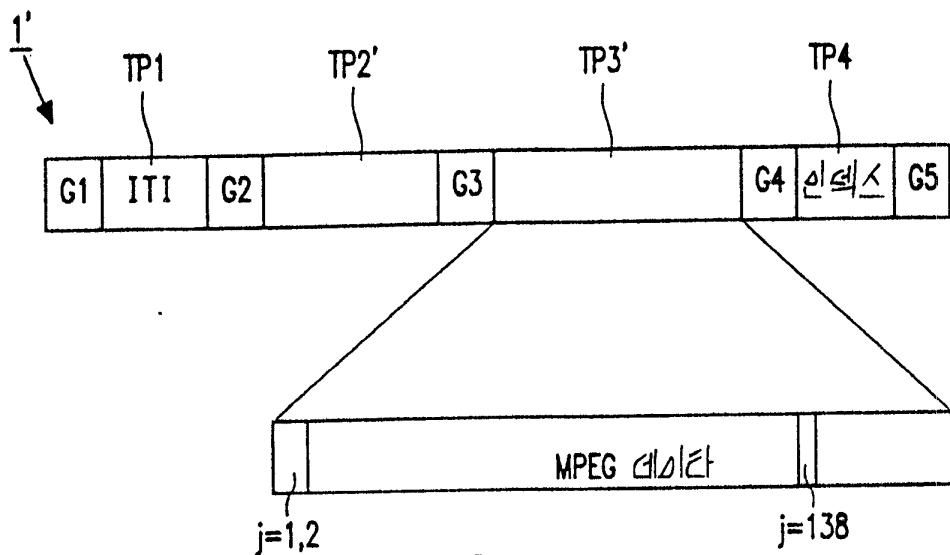

<40> 제1도는 DVC형 기록 캐리어의 트랙 포맷을 도시한 도면이고,

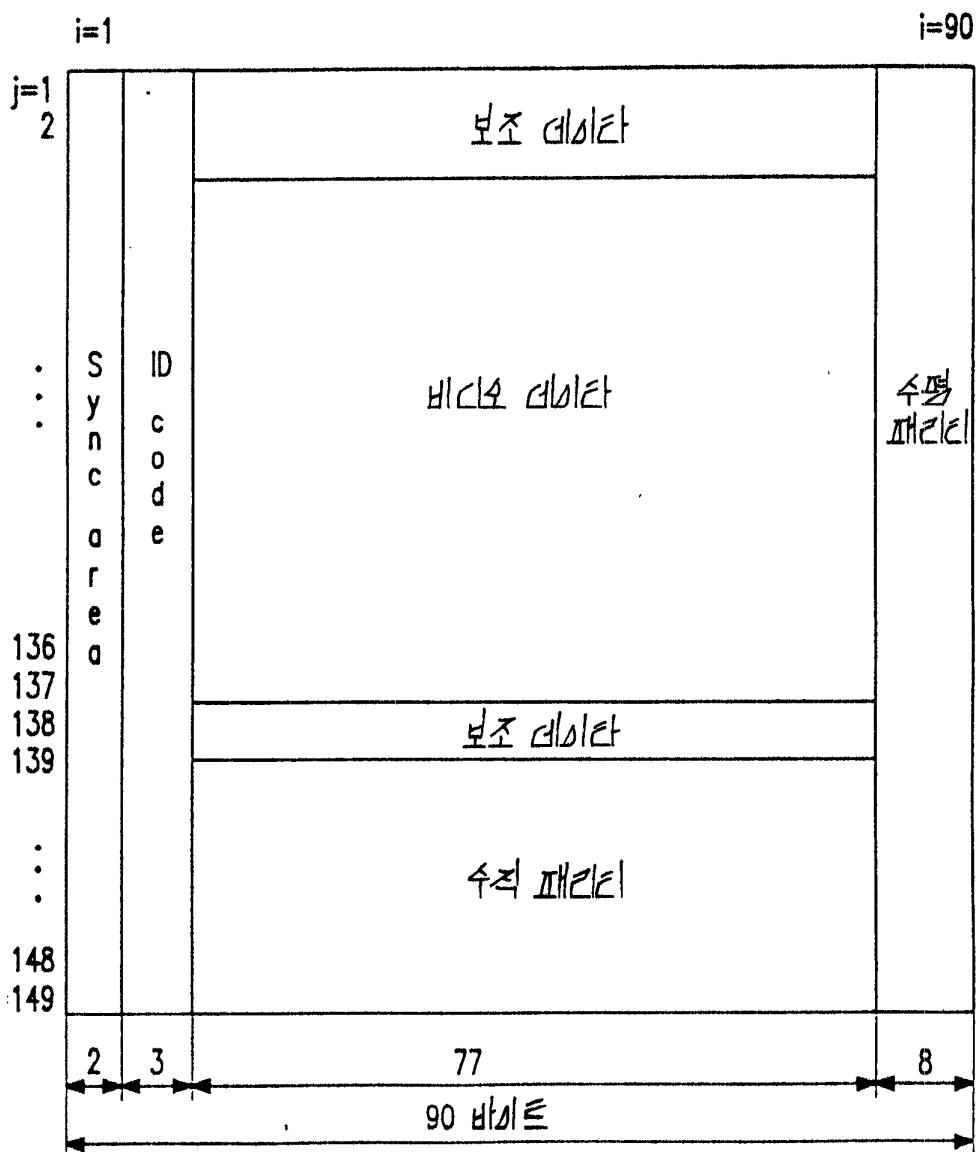

<41> 제2도는 제1도의 트랙 내의 비디오 신호 레코딩 섹터의 내용을 개략적으로 도시한 도면이고,

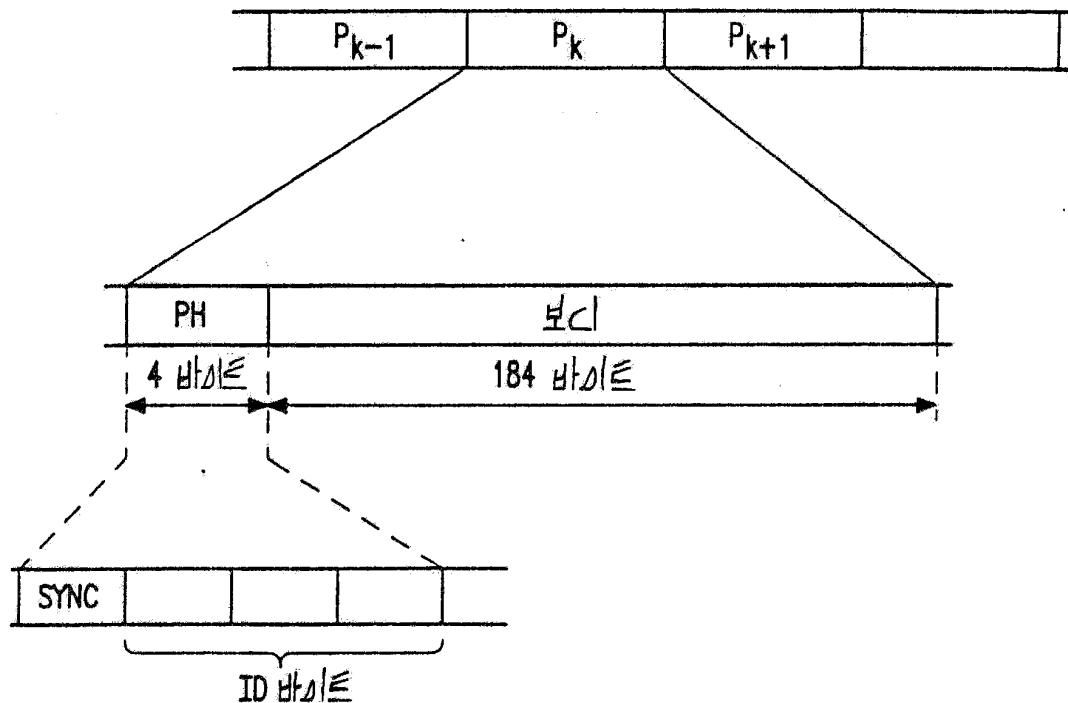

<42> 제3도는 일련의 MPEG 데이터 스트림과 일련의 MPEG 데이터 스트림에 포함된 전송 패킷의 포맷을 개략적으로 도시한 도면이고,

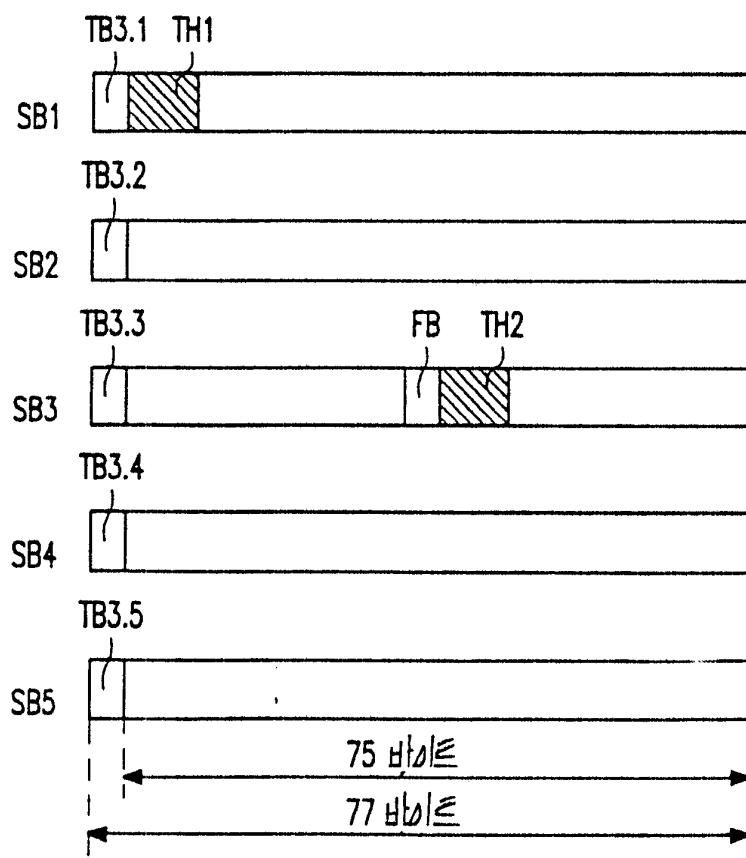

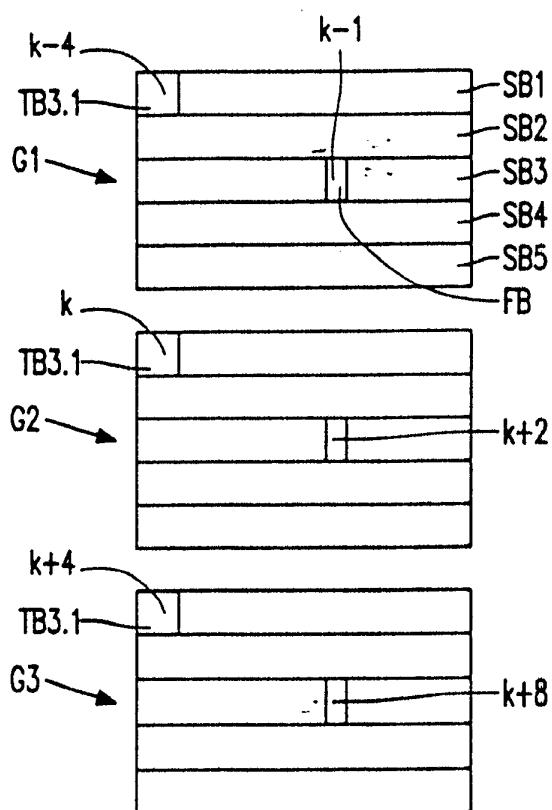

<43> 제4도는 5개의 신호 블록 내의 2개의 전송 패킷의 기억부의 예를 도시한 도면이고,

<44> 제5도는 내부에 기록된 MPEG 정보를 가질 때 트랙의 내용을 도시한 도면이고,

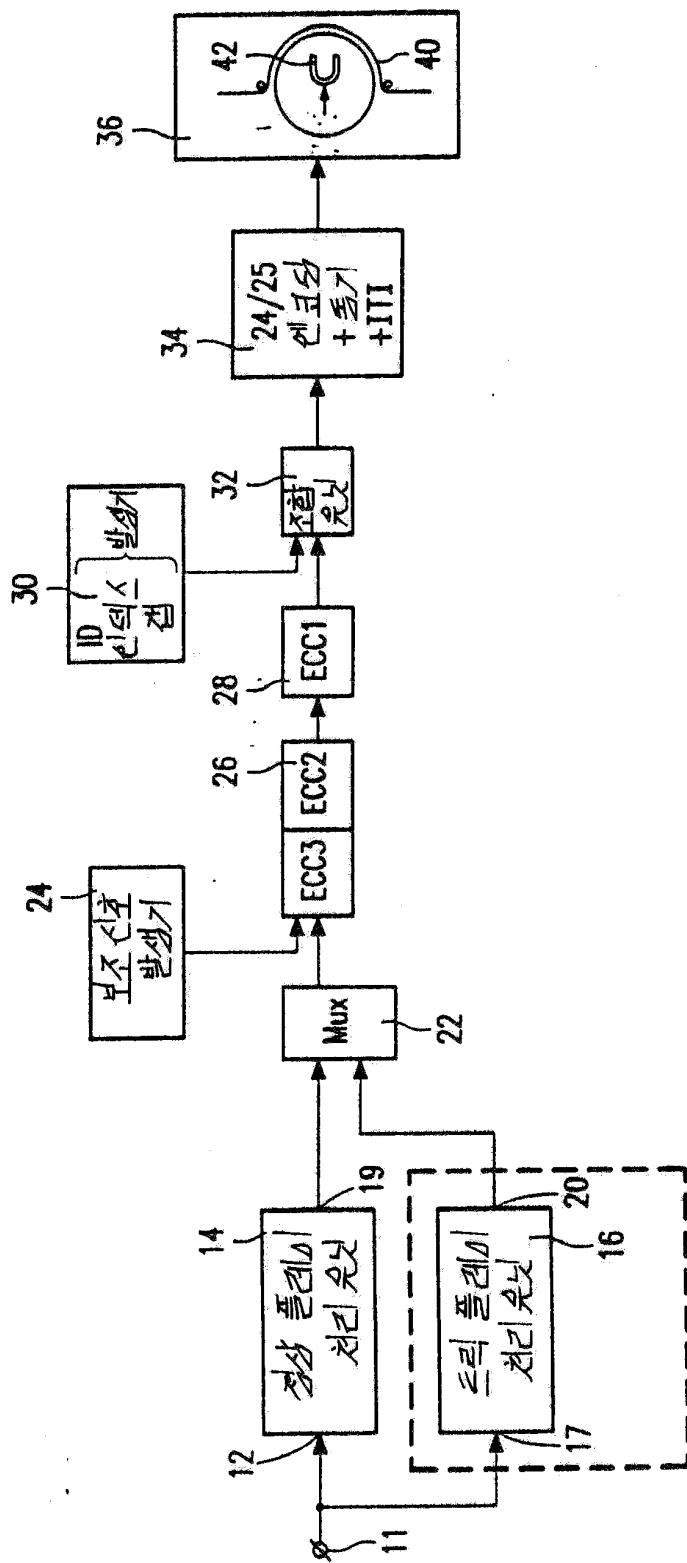

<45> 제6도는 기록 장치의 한 실시예를 도시한 도면이고,

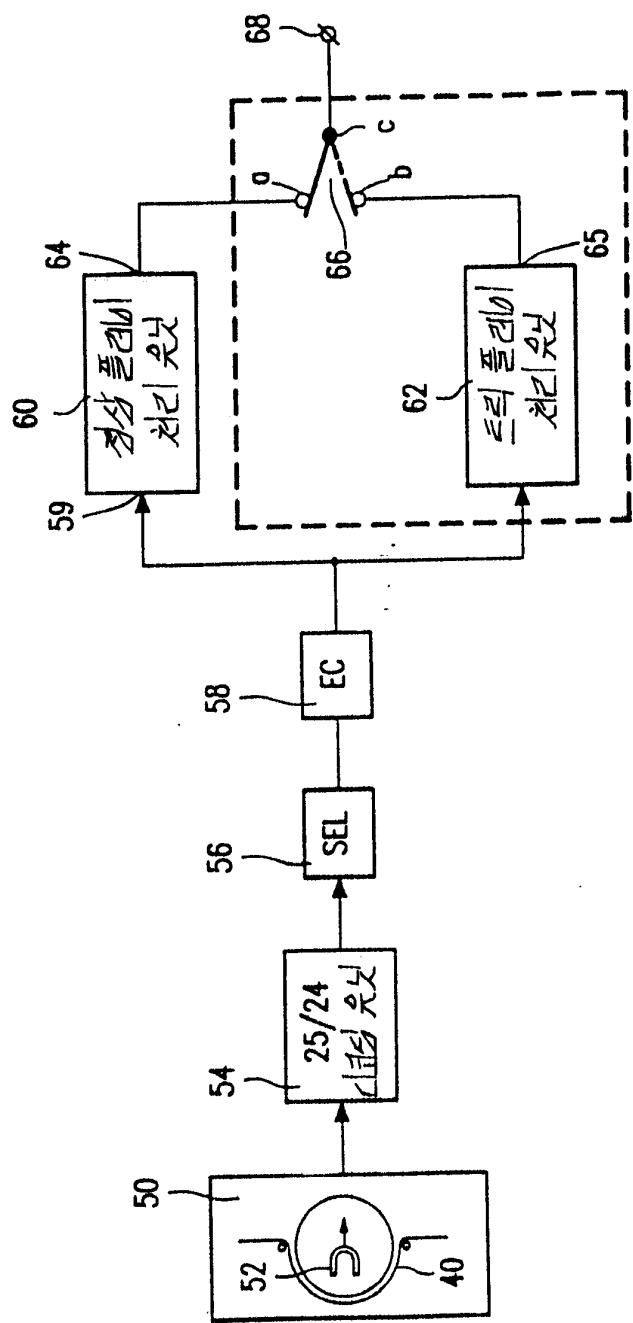

<46> 제7도는 재생 장치의 한 실시예를 도시한 도면이고,

<47> 제8a도는 일정한 비트 전송 속도 및 패킷 전송 속도를 갖는 원래의 시리얼 MPEG 데이터 스트림의 예를 도시한 도면이고, 제8b도는 기록되는 MPEG 데이터 스트림을 도시한 도면이고, 제8c도는 원래의 시리얼 MPEG 데이터 스트림의 재형성된 사본을 도시한 도면이고,

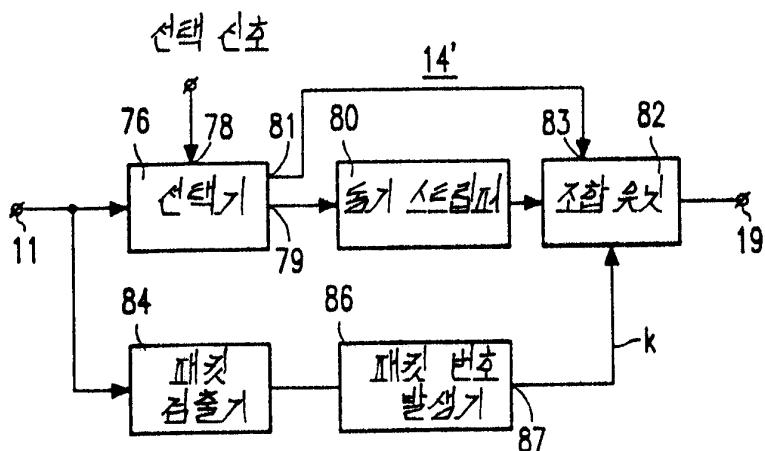

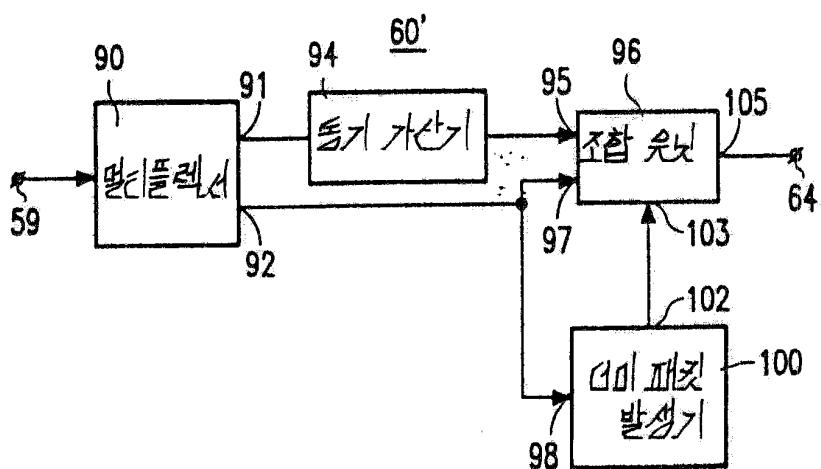

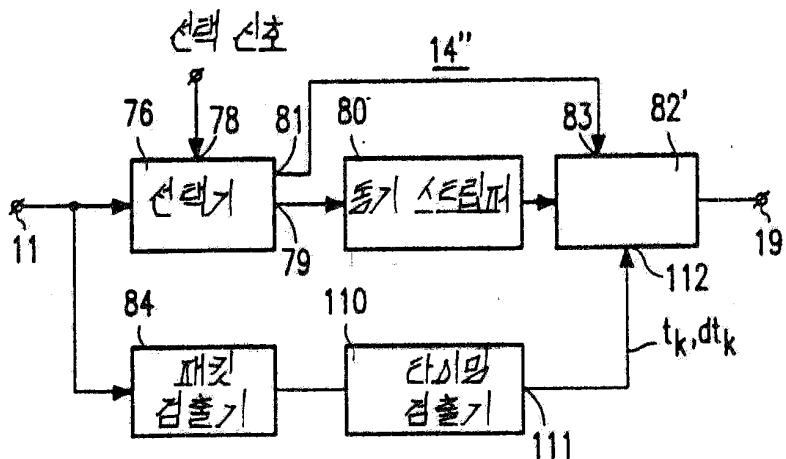

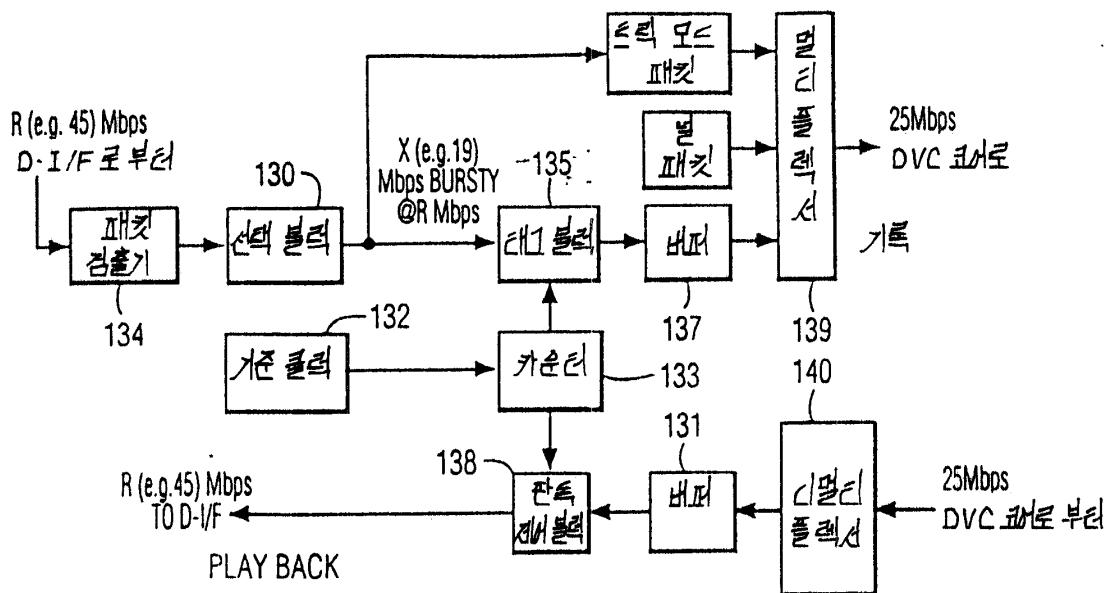

<48> 제 9도는 제6도의 기록 장치 내의 '정상 플레이' 처리 유닛의 한 실시예를 도시한 도면이고,

<49> 제10도는 5개의 신호 블록 각각의 3개의 그룹 순서의 한 예를 도시한 도면이고,

<50> 제11도는 5개의 신호 블록 각각의 3개의 그룹 순서의 다른 예를 도시한 도면이고,

<51> 제12도는 제7도의 재생 장치 내의 '정상 플레이' 처리 유닛의 한 예를 도시한 도면이고,

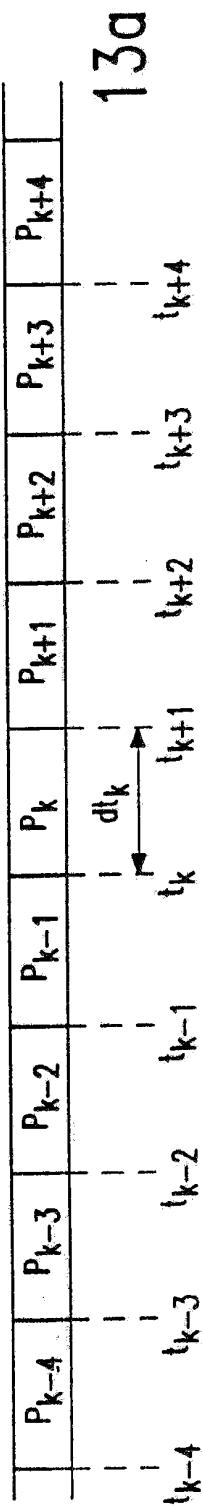

<52> 제13a도는 가변 비트 전송 속도 및 패킷 전송 속도를 가진 원래의 시리얼 MPEG 데이터 스트림의 한 예를 도시한 도면이고, 제13b도는 기록되는 MPEG 데이터 스트림을 도시한 도면이고, 제13c도는 원래의 시리얼 MPEG 데이터 스트림의 재형성된 사본을 도시한 도면이고,

<53> 제14도는 제6도의 기록 장치 내의 '정상 플레이' 처리 유닛의 다른 실시예를 도시한 도면이고,

<54> 제15도는 제7도의 재생 장치 내의 '정상 플레이' 처리 유닛의 다른 실시예를 도시한 도면이고,

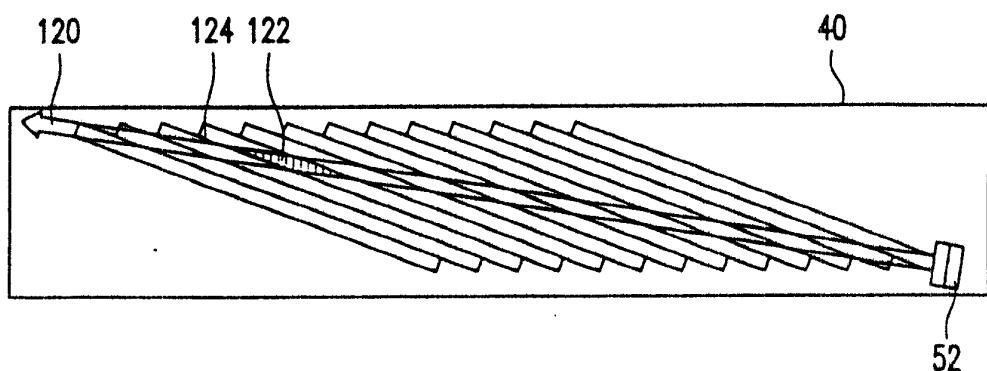

<55> 제16도는 트릭 플레이 모드 동안 기록 캐리어를 주사하는 판독 헤드와 기록 캐리어를 도시한 도면이고,

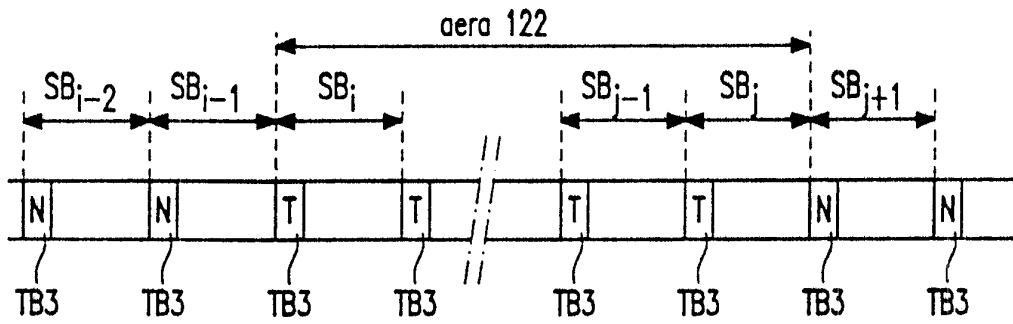

<56> 제17도는 트릭 플레이 영역을 형성하는 트랙 내의 신호 블록 순차를 도시한 도면이고,

<57> 제18도는 기록 및 재생 시스템을 조합하는 본 발명의 다른 실시예를 도시한 도면이고,

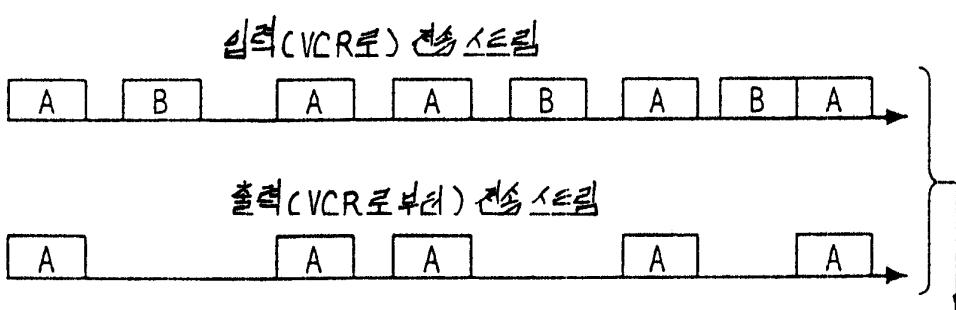

<58> 제19도는 제18도의 장치로부터 입력 및 출력 데이터 스트림의 예를 도시한 도면이고,

<59> 제20도는 제18도와 같은 장치로부터 입력 및 출력 데이터 스트림의 다른 예를 도시한 도면이고,

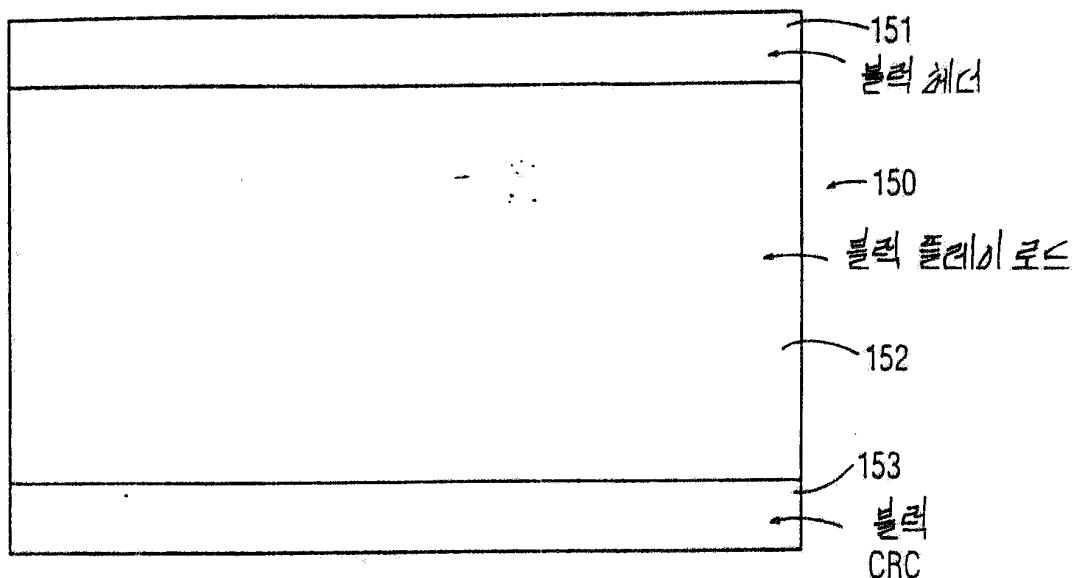

<60> 제21도는 비동기 채널을 통해 전송을 위해 본 발명의 데이터 블록의 한 형태를 도시한 도면이고,

<61> 제22도는 제21도의 데이터 블록의 블록 페이로드를 보다 상세히 설명하는 도면이고,

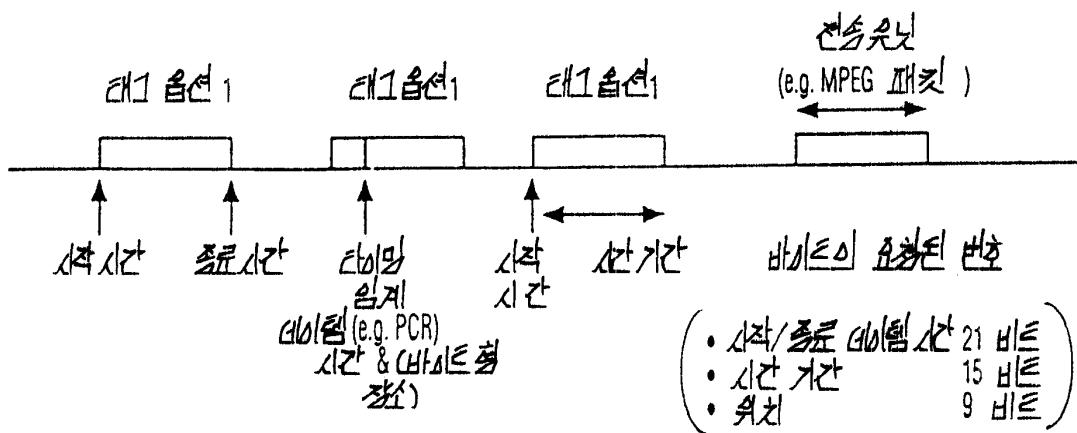

<62> 제23도는 본 발명에 따른 여러 태그 옵션을 도시한 도면이다.

### 발명의 상세한 설명

<63> 제1도는 DVC형 나선 주사 비디오 기록 장치에 의해 자기 기록 캐리어상의 트랙에 기록되는 신호의 포맷을 도시한다. 제1도의 트랙(1)의 좌측 단부는 트랙의 시작부이고, 우측 단부는 트랙의 종료부이다. 그 트랙은 다수의 트랙부를 포함한다. G1로 표시된 트랙부는 프리앰플 트랙부이다.

- <64> 프리앰블 트랙부(G1)의 한 예는 참고 문헌(1)에 독점적으로 기술되어 있다.

- <65> 트랙부(G1) 다음에 따른 톤 기록부(TP1)는 ITI(타이밍 정보 삽입)에 의해 표시되고 트랙킹 톤, 동기화 정보 및 식별(또는 타이밍) 정보를 포함한다. ITI 트랙의 다른 내용 설명은 참고문헌(3)에서 알 수 있다.

- <66> 트랙부(TP1) 다음에는 에디트 캡(G2)이 있다. 그 에디트 캡(G2) 다음에는 트랙부(TP2)가 있는데, 오디오 신호 기록 섹터이며, 디지털 오디오 정보를 포함한다. 그 에디트 캡(G3) 다음에는 비디오 신호 기록 섹터인 트랙부(TP3)가 있으며, 디지털 비디오 정보를 포함한다. 그 에디트 캡(G2) 다음에는 INDEX로 표시된 트랙부(TP4)가 있으며, 절대치 또는 상대치의 시간 정보와 내용 테이블(TOC)과 같은 다른 항목 중 서브 코드 정보를 포함한다. 상기 트랙은 트랙부(G5)에 의해 종결된다.

- <67> 상기는 부분(TP1, TP2 및 TP3)이 트랙에서 발생할 수 있는 순차가 상이하게 될 수 있음을 의미한다.

- <68> 비디오 신호 기록 섹터(TP3)의 내용은 제2도에 설명되어 있다. 사실상, 제2도는  $j=1$  내지  $j=149$ 로 표시되어 내부에 기억된 정보의 바이트를 갖는 다수의 149개의 수평 라인을 개략적으로 도시한다. 그 149개의 라인은 비디오 신호 기록 섹터(TP3)에 순차적으로 기억될 수 있는데, 사실상 149개의 신호 블록(또는, 동기 블록)이 된다.  $i=1$  내지  $i=90$ 으로 표시된 정보의 90 바이트는 각각의 신호 블록에 기억된다.

- <69> 각각의 신호 블록의 첫 번째 2 바이트( $i=1$  및  $i=2$ )는 보다 긴 2 바이트의 동기 패턴을 형성한다. 각각의 신호 블록 내의 다음 3개의 바이트는 비디오 신호 기록부(TP3) 내의 신호 블록의 순차 번호를 나타내는 다른 항목 정보를 포함하는 ID 코드를 형성한다. 신호 블록의 최종 8바이트는 수평 패리티 정보를 형성한다. 수직 패리티 정보는 최종 11개의 신호 블록을 포함하는 기억 장소( $i=6$  내지  $i=82$ )에 기억된다.

- <70> 비디오 신호 정보의 바이트는 포함된 순차 번호( $j=3$  내지  $j=137$ )를 갖는 신호 블록이 포함된 기억 장소( $i=6$  내지  $i=82$ )에 기억된다. 보조 데이터의 바이트는 순차 번호( $j=1, 2$  및 138)를 갖는 신호 블록이 포함된 기억 장소( $i=6$  내지  $i=82$ )에 기억된다.

- <71> 그 신호 블록은 신호 블록이  $j=149$ 를 지정할 때까지,  $y=1$ 로 표시된 신호 블록으로 시작하여 다음에  $j=2$ 로 표시된 신호 블록이 따르는 비디오 신호부(TP3)에 순차로 기억된다.

- <72>  $j=1, 2$  및 138로 표시된 신호 블록에 기억하는 보조 데이터는 텔레텍스트 데이터 또는 제어 데이터가 될 수 있다.

- <73> 상기 보조 데이터는 메모리 내의 상이한 위치에 기억될 수 있다는 점을 지정할 수 있음을 주시한다. 문서(1)에 대해 이루어진 참조 문헌, 제13도에서는 데이터가 111에 의해 표시된 메모리부에 기억된다.

- <74> 제3도는 본 발명에 따른 기록 장치에 인가되는 MPEG 데이터를 개략적으로 도시한다. 그 MPEG 데이터 스트림은 ...,  $P_k-1, P_k, P_k+1, \dots$ 에 의해 표시된 순차 전송 패킷을 포함한다. 그 패킷은 긴 4 바이트의 패킷 헤더부(PH) 및 긴 184 바이트의 바디부(body portion)를 각각 포함한다. 그 전송 패킷은 일정한 비트 전송 속도를 갖는 데이터 스트림에 전송될 수 있다.

- <75> 상기는 패킷이 균일하게 길고, 동시에 나타나면, 고정된 패킷 전송 속도로 수신됨을 의미한다. 또한, 상기 전송 재킷은 가변 비트 전송 속도를 갖는 데이터 스트림 내에 전송될 수도 있다. 상기 상태에 있어서, 그 패킷은 반드시 동일한 길이가 되고, 동시에 보여지며, 가변 패킷 전송 속도로 수신될 필요는 없다. 패킷 헤더(PH)의 제1 바이트는 동기 바이트이다. 동기 바이트는 모든 전송 패킷에 대해 동일하게 된다. 그 헤더의 다른 3 바이트는 패킷 식별자와 같은 ID 정보를 포함한다. ID 정보 내용의 다른 설명에 대해서는, 참고문헌의 리스트, 특히 챕터(V), 27페이지의 패러그래프(5, 1)의 문서(4)에 나타나 있다.

- <76> 전송 패킷의 바디부는 MPEG 포맷에 따라 전송되어야 하는 비디오 및 오디오 정보를 기억하기 위한 각각 184 바이트를 포함한다. 하나의 전송 패킷의 바디부는 임의 비디오 신호에 상응하는 오디오 정보나 비디오 정보를 기억할 수 있다. 또한, 다수의 비디오 프로그램이 MPEG 데이터 스트림을 통해 전송되는 경우에, 바디부는 전송된 그와 같은 비디오 프로그램중 하나에 상응하는 비디오 신호를 기억한다.

- <77> 지금, 본 발명의 한 관점은 비디오 신호와, MPEG 데이터 스트림을 통해 전송되는 그들 비디오 프로그램 중 한 프로그램에 상응하는 예측될 수 있는 오디오 신호에 상응하는 신호를 제1도 및 제2도에 설명된 트랙 포맷을 갖는 기록 캐리어 상에 기록하는 것이다. 전송 패킷에 기억된 정보는 신호 블록에 기억되어야 하는데, 특히, 한 트랙의 비디오 신호 기록부(TP3) 내에  $j=137$ 로 표시된 135개의 신호 블록에 기억되어야 한다. 그들 신호 블록 내에,  $i=1$  및  $i=2$ 로 표시된 2개의 동기 바이트,  $i=3, 4$  및 5로 표시된 3개의 ID 바이트 형태의 ID 정보, 뿐만 아니라,  $i=83$  내지 90으로 표시된 8 수평 패리티 바이트는 정확한 기록 및 재생에 필요하다. 결과적으로,  $j=3$  내지 137로 표시된 신호 블록 내에  $i=6$  내지 82에 의해 표시된 단지 77 바이트만이 MPEG 정보의 전송 패킷의 기억에 이용된다. 77 바이트( $i=6$  내지  $i=82$ )에 의해 형성된 신호 블록의 부분은 신호 블록의 제2 블록 섹션이 되는 것으로 정의된다.

- <78> 기록 및 재생 동안 동기화가 각각의 신호 블록 내의 동기 워드에 의해 보장될 때, 기록 캐리어를 통해 전송 패킷의 동기 바이트를 전송시킬 필요가 없다. 그래서  $j=3$  내지 135로 표시된 신호 블록의 제2 블록 섹션 내의 전송 패킷에 포함된 정보를 기억시키기 전에, 모든 전송 패킷의 동기 바이트는 폐기된다. 결과적으로, 단지 187 바이트의 정보가 각각의 전송 패킷에 대한 신호 블록에 기억되어야 한다.

- <79> 단순한 계산은 두 개의 전송 패킷이 5개의 신호 블록에 기억될 수 있고, 11 바이트가 다른 정보의 기억에 이용 가능하게 남아 있게 하는 것이다. 제4도는 제4도에 SB1 내지 SB5로 표시된 5개의 신호 블록 그룹의 제2 블록 섹션에 두 개의 전송 패킷이 어떻게 기억될 수 있는가의 예를 나타낸다. 제4도는 신호 블록 내에 포함된 77 바이트의 길이의 제2 블록 섹션 내용만을 나타낸다. 제4도에 도시된 것처럼, 11 바이트는 5개의 신호 블록 그룹 전체를 통해 분할되어, 각각의 제2 블록 섹션은 5개의 신호 블록(SB1 내지 SB5) 각각의 제2 블록 섹션의 시작부에서 긴 2 바이트의 제3 블록 섹션(TB 3.1 내지 TB 3.5)과, 제3

신호 블록(SB3)에 이용가능하고, FB에 의해 표시된 1 바이트 형태로 제3 블록 섹션을 포함한다. 제1 전송 패킷의 187 바이트는 TH1에 의해 표시된 제1 전송 패킷의 패킷 헤더의 3개의 ID 바이트가 제3 블록 섹션(TB 3.1) 이후에 바로 신호 블록 내에 우선 기억되고, 다음에, 제1 전송 패킷 내의 처음 72 바이트가 신호 블록(SB1)에 제2 블록 섹션 내에 기억되는 제1 패킷의 바디 내의 다음 75 바이트는 제3 블록 섹션(TB 3.1) 이후에, 신호 블록(SB2)의 제2 블록 섹션에 기억되고, 제1 전송 패킷의 바디 내의 최종 37 바이트는, 제3 블록 섹션(TB 3.3) 이후에, 신호 블록(SB3)의 제2 블록 섹션 내에 기억된다.

<80> 다음은 5개의 신호 블록 그룹에 기억된 제1 및 제2 전송 패킷의 정보 사이의 경계를 나타내는 바이트(FB)이다.

<81> 제2 전송 패킷의 187 바이트는, TH2로 표시된 제2 전송 패킷의 패킷 헤더의 3개의 ID 바이트가 바이트(FB) 바로 이후에, 신호 블록(SB3)에 우선 기억되는 신호 블록(SB3, SB4 및 SB5)에 기억된다. 다음은, 제2 전송 패킷의 바디 내의 우선 34 제1 바이트가 신호 블록(SB3)의 제2 블록 섹션 내에 기억된다.

<82> 제2 전송 패킷의 바디 내의 다음 75 바이트는 제3 블록 섹션(TB 3.4) 이후에, 신호 블록(SB4)의 제2 블록 섹션에 기억되고, 제2 전송 패킷의 바디의 최종 75 바이트는 제3 블록 섹션(TB 3.5) 이후에, 신호 블록(SB5)의 제2 블록 섹션에 기억된다.

<83> 상기 5 개 신호 블록 전체를 통하여 11개의 이용 가능한 바이트의 다른 전개가 있을 수 있음을 알 수 있다. 한 예로서, 11 바이트는 두 개의 제3 블록 섹션, 예를 들어 6 바이트를 가지고 제1 신호 블록(SB1)의 시작부에 위치하는 하나의 제3 블록 섹션과, 제3 신호 블록 내에 위치되고 5개의 신호 블록 내에 기억된 2개의 전송 패킷 사이의 경계를 나타내는 5 바이트 긴 다른 제3 블록 섹션으로 분할될 수 있다. 다른 예는 신호 블록(SB1 내지 SB3)의 시작부에 위치한 제3 블록 섹션과, 신호 블록(SB1) 내의 제3 블록 섹션이 예를 들어 4 바이트를 가질 수 있고, 예로 3 바이트의 신호 블록(SB3) 내의 첫 번째 제3 블록 섹션 및 상기 경계를 나타내는 신호 블록(SB3) 내의 제3 블록 섹션이 예를 들어 4 바이트 길게 되는 다른 제3 블록 섹션을 가질 수 있다.

<84> 상기 제3 블록 섹션(TB 3.1 내지 TB 3.5)은 부가 정보의 기억을 위해 이용될 수 있다. 제1 실시 예에서와 같이, 제3 블록 섹션(TB 3.1)은 5개의 신호 블록 그룹내에 제1 신호 블록으로 신호 블록(SB1)을 식별하는 표시(indication)를 포함할 수 있다. 상기는 '0' 또는 '1'과 같은 임의 패리티의 비트 값을 제3 블록 섹션(TB 3.1) 내의 한 지정 비트 위치 내에 기억시켜 실현될 수 있다. 제3 블록 섹션(TB 3.2 내지 TB 3.5) 내의 동일한 비트 위치에 있어서, 반대 극성의 비트 값이 기억되어야 한다. 다른 실시예에 있어서, 순차 번호 정보, 즉, 1 내지 5 까지 실행하는 순차 번호는, 제3 블록 섹션(TB 3.1)이 순차 번호('1')를 갖고, 블록 섹션(TB 3.5)이 그들에 기억된 순차 번호를 갖는 5개의 신호 블록 그룹의 제3 블록 섹션(TB 3.1 내지 TB 5) 각각에 기억될 수 있다. 제3 블록 섹션(TB 3.1 내지 TB 3.5) 내의 3개의 지정 비트 위치는 기억된 순차 번호에 필요하게 된다. 그러나 그 순차 번호는, 예를 들어 한 트랙 내, 또는 한 트랙 이상의 트랙 내에 신호 블록의 보다 큰 순차를 식별하기 위해 그룹 경계 양단을 실행할 수 있다.

<85> 다른 실시예에 있어서, 5개의 신호 블록 그룹의 제3 블록 섹션(TB 3.1 내지 TB 3.5) 내의 한 특정 비트 위치는, 신호 블록 내에 포함된 비디오 데이터가 소위 '정상 플레이' 데이터인지를 식별하기 위하여 '0' 또는 '1'과 같은 한 극성의 비트값을 기억시키거나, 신호 블록 내에 포함된 비디오 데이터가 소위 '트릭 플레이' 비디오 데이터인지를 식별하기 위하여, 반대 극성의 비트 값을 기억시키는데 이용될 수 있다. '정상 플레이' 비디오 데이터 및 '트릭 플레이' 비디오 데이터의 이용은 이후에 설명한다.

<86> 다시, 다른 실시예에 있어서, 순차 번호는 수신되는 MPEG 데이터 스트림 내의 전송 패킷에 응답하여 발생된다. 이전에 설명한 것처럼, 그와 같은 MPEG 데이터 스트림은 한 비디오 프로그램 이상을 포함할 수 있다. MPEG 데이터 스트림의 비트 전송 속도가 기록될 수 있는 신호의 비트 전송 속도 보다 통상 크게 될 때, 단지 한 비디오 프로그램이 기록을 위해 시리얼 MPEG 데이터 스트림으로부터 선택될 수 있다. 한 비디오 프로그램의 선택은 상기 비디오 프로그램과 관계하고, 다른 패킷을 삭제하는 정보를 포함하는 MPEG 데이터 스트림 이외의 전송 패킷의 선택을 의미한다.

<87> 결과적으로, 기록될 전송 패킷의 시리얼 어레이에는, 삭제된 전송 패킷의 그들 순차 번호가 존재하지 않을 때, 다음 보다 큰 번호를 필요치 않는 순차 번호를 갖는다. 제3 블록 섹션 내의 순차 번호를 기억할 때, 그들 순차 번호는 재생에 따라 검색될 수 있다. 수신된 순차적 순차 번호를 검사하여, 기록 장치에 적용된 원래의 MPEG 데이터 스트림이 재생된 두 개의 전송 패킷 사이의 삭제된 전송 패킷이 포함되는지를 설정할 수 있다.

<88> 그렇다면, 원래의 MPEG 데이터 스트림의 사본은 재생된 두 개의 전송 패킷 사이의 하나 이상의 더미 패킷을 삽입하여 재형성될 수 있다.

<89> 관련된 실시예에 있어서, 타이밍 정보는, 그와 같은 데이터 스트림이 가변비트 전송 속도를 갖는 데이터 스트림인 경우에, 원래의 MPEG 데이터 스트림의 사본을 재형성하기 위하여, 상기 설명된 것과 동일한 이유로, 제3 블록 섹션 내에 기억된다.

<90> 또한, 상기 설명한 부가의 정보의 조합은 5개의 신호 블록 그룹 내에 그와 같은 정보를 기억할 수 있는 11 바이트 내에 포함될 수 있음이 명백하다.

<91> 한 예로서, 5개의 신호 블록 그룹 내에 신호 블록의 순차 번호를 표시하기 위해 제3 블록 섹션에 3 비트 워드가 필요함을 명백하게 된다. 특히, 3 비트 워드('000', '001', '010', '011' 및 '100')는 순차를 식별하기 위해 이용된다. 상기는 3 비트 워드 '101', '110' 및 '111'는 다른 식별에 이용가능하게 유지된다. 한 예로서, 3 비트 워드('101' 및 '110')는 '정상 플레이' 데이터 또는 '트릭 모드' 데이터를 식별하는데 이용된다.

<92> 제5도는 MPEG 정보가 트랙부(TP3)로 표시된 제1도의 트랙부(TP3)의 신호 블록의 제2 블록부에 기록되었을 때, 트랙의 트랙 정보를 도시한다. 제5도는 보조 데이터를 포함하는 트랙부(TR3') 내의 제1 두 신호 블록(j=1, 2)과, MPEG 정보 및 상기 기술한 부가 정보를 포함하는 다음의 135개의 신호 블록(j=3 내지 j=137)을 도시한다. 다음 한 신호 블록(j=138)은 또한 보조 데이터를 포함하고, 뒤따르는 11개의 신호

블록은 패리티 정보를 포함한다. 135개의 신호 블록 내의 MPEG 정보 및 부가 정보의 기억은 상기 정보에 따라 실행되는 부가 에러 인코딩 단계를 필요하고, 그 결과 부가 패리티 정보는 한 트랙 내에 기억되어야 한다.

<93> 비디오 정보 및 상응하는 오디오 정보를 포함하는 MPEG 정보는 트랙부(TP3')내의 신호 135개의 블록에 기억되고, 제1도의 트랙부(TP2)에 오디오 정보를 기억시킬 필요가 없다. 제5도에 TP2'에 의해 표시된 상기 부분은 부가 에러 인코딩 단계로부터 얻어진 패리티 정보를 기억하는데 이용될 수 있다.

<94> 제6도는 기록 장치의 한 실시예를 개략적으로 도시한다.

<95> 상기 기록 장치는 트랙 중 트랙부(TP3')의 신호 블록 내의 데이터 스트림에 포함된 전송 패킷을 기록하기 위해 MPEG 시리얼 데이터 스트림을 수신하기 위한 입력 단자(11)를 포함한다. 그 입력 단자(11)는 '정상 플레이' 처리 유닛(14)의 입력(12)에 결합된다.

<96> 선택적으로, '트랙 플레이' 처리 유닛(16)은 입력 단자(11)에도 결합된 입력을 갖는다. '정상 플레이' 처리 유닛(14) 및 '트랙 플레이' 처리 유닛(16)(존재한다면)의 출력(19 및 20)은 멀티플렉서(22)의 상응하는 입력에 결합된다. '트랙 플레이'의 부재중에는, 멀티플렉서(22)가 존재하지 않음을 알 수 있다.

<97> 보조 신호 발생기(24)는 j=1, 2 및 138로 표시된 신호 블록에 기억하는 보조신호 정보를 공급하기 위해 존재한다(제2도 참조). 멀티플렉서(22) 및 발생기(24)의 출력은 ECC3으로 표시된 제1 에러 보정 인코딩 단계와, ECC2로 표시된 제2 에러 보정 인코딩을 실행할 수 있다. 다음에는 ECC1으로 표시된 제3 에러 교정 인코딩 단계는 에러 교정 엔코더 유닛(28)에서 실행된다.

<98> 상기 기록 장치는, 제2도에 도시된 것처럼, 신호 블록의 바이트(i=3, 4 및 5)의 ID 정보를 부가하고, 제5도에 도시된 것처럼, 트랙부(TP4)에 기억하기 위한 인덱스 정보를 부가하여, 제5도에 도시된 것처럼, 캡(G1 내지 G5)을 실현하기 위한 캡 정보를 부가하기 위한 발생기(30)를 더 포함한다.

<99> 조합 유닛(32)에서 신호의 조합 이후에, 조합된 신호는 인입되는 비트 스트림의 24 비트 워드가 25 비트 워드로 매번 변환되고, 동기 워드가 신호 블록 내에서 제1 두 개의 바이트(i=1, 2)를 얻기 위해 부가되며, 트랙부(TP1) 내에 기억시키기 위해 III 정보가 부가되는 인코딩을 실행하는 유닛(34)에 인가된다.

<100> 인코딩 유닛(34)에서 실행되는 24-25 인코딩은 본 기술에 관련하여 이미 공지되어 있다. 참조 문헌은 참조 문헌중의 리스트의 문서(5)인, 미국 특허 제 5,142,421호에 관하여 것이다. 상기 문서는 또한 데이터 스트림에 동기 워드를 부가하는 방법을 기술하고 있다.

<101> 인코딩 유닛(34)의 출력은, 인코딩 유닛(34)에 따라 얻어진 데이터 스트림이 최소한 하나의 기록 헤드(42)에 의해 기록 캐리어 상의 슬랜트 트랙에 기록되는 기록 유닛(36)의 입력에 결합된다.

<102> ECC3으로 표시된 제1 에러 교정 인코딩 단계는 기록 캐리어 상에 기록될 DPEG 정보의 부가 에러 보호를 실현하기 위해 필요하고, 그 결과로서, 이전에 설명한 것처럼, 패리티 정보가 트랙부(TP2')에 기억된다. ECC2로 표시된 제2 교정 인코딩 단계에서는 제2도 및 제5도에 도시된 것처럼, 트랙부(TP3')의 11 신호 블록(j=139 내지 149)에 기억되는 수직 패리티 정보를 얻는다. ECC1로 표시된 제3 에러 교정 인코딩 단계에서는 제2도 및 제5도에 도시된 것처럼, 트랙부(TP3') 내의 신호 블록의 최종 8 바이트에 기억되는 수평 패리티 정보를 결과로 얻는다.

<103> 제6도의 기록 장치의 '정상 플레이' 처리 유닛(14) 및 '트랙 플레이' 처리 유닛(16)의 다른 설명 이전에, 우선, 재생 장치를 개략적으로 설명한다. 상기는, 처리 유닛(14 및 16)에 적용된 임의 수단을 더 설명할 때, 직접적인 관계가 재생동안 그들 수단의 장점 및 중요성이 주어질 수 있다.

<104> 제7도는 제6도의 기록 장치에 따라 얻어진 기록 캐리어(40)로부터 정보를 재생 장치의 실시예를 개략적으로 도시한다. 그 재생 장치는 기록 캐리어(40)상의 슬랜트 트랙으로부터 정보를 판독하는 최소한 하나의 판독 헤드(52)를 갖는 판독 유닛(50)을 포함한다. 판독 유닛(50)의 출력은 인입 데이터 스트림 내의 25 비트 워드를 24 비트 워드로 변환하기 위하여, 판독된 신호에 따라 25-24 디코딩을 실행하는 디코딩 유닛(54)의 입력에 결합된다. 다음, 선택기 유닛(56)에서 원래의 MPEG 데이터 스트림의 사본을 재작성하는데 필요치 않은 모든 정보를 선택한 이후에, 에러 보정은 에러 보정 유닛(58)에서 실행된다. 그 실행된 에러 보정은 3 단계로 실행됨을 알 수 있다. ECC1에 기초한 한 에러 보정 단계는 제2도에 도시된 것처럼 수평 패리티를 사용하고, ECC2를 기초한 제2 에러 보정은 수직 패리티를 이용하며, ECC3를 기초한 제3 에러 보정은 제5도에 도시된 것처럼, 트랙부(TP2')에 저장된 패리티를 이용한다.

<105> 에러 교정 유닛(58)의 출력 단자는 '정상 플레이' 처리 유닛(60)의 입력에 결합된다. 선택적으로, '트랙 플레이' 처리 유닛(62)은 에러 교정 유닛(58)의 출력에도 결합된 입력을 가지고 제공된다. '정상 플레이' 처리 유닛(60) 및 '트랙 플레이' 처리 유닛(62)(만일 존재한다면)의 출력(64 및 65)은 스위치(66)의 상응하는 단자(a 및 b)에 결합되고, 그 c 단자는 출력단자(68)에 결합된다. '트랙 플레이' 처리 유닛(62)의 부재에 있어서는, 스위치(66)도 부재가 됨을 알 수 있다. 재생 장치가 '정상 플레이' 재생 모드로 스위칭된다면, 상기 의미는 기록 캐리어가 정속으로 전송되고, '정상 플레이' 처리 유닛(60)이 인에이블되면, 스위치(66)가 위치(a-c)로 스위치 됨을 의미한다.

<106> 재생 장치가 '트랙 플레이' 재생 모드 또한, 소위 '미래 모드'(feature mode)로 스위칭된다면, 상기는 기록 캐리어가 정속 이외의 다른 속도에서 전송되고, '트랙 플레이' 처리 유닛(62)이 인에이블되며, 스위치(66)가 위치(b-c)로 스위칭됨을 의미한다.

<107> 다음 설명은 제7도의 처리 유닛(60 및 62)과 조합으로, 제6도의 처리 유닛(14 및 16)이 된다.

<108> 기록 장치는 사용자에 의해 장치에 공급되는 선택 신호에 응답하여, 입력 단자(11)에 인가되는 시리얼 MPEG 데이터 스트림으로부터 하나의 비디오 프로그램 및 그에 상응하는 오디오 신호를 선택할 수 있다고 가정한다. 이미 설명한 것처럼, 시리얼 MPEG 스트림 내의 그들 전송 패킷만이 선택된 비디오 프로그램에 관련된 정보를 포함하여 선택되어야 한다. 제8a도는 Pk로 표시된 전송 패킷을 포함하는 시간 함수

로서 시리얼 MPEG 데이터 스트림을 나타낸다. MPEG 데이터 스트림의 전송 패킷이 패킷 번호를 포함하지 않는 것을 주목한다. 그러므로, 제8a도 내의 패킷에 주어진 패킷 번호(k)는 이후에 설명될 제9도의 패킷 번호 발생기(86)에 의해 발생되는 번호이다.

<109> 비디오 프로그램 선택 수단에 관련된 정보를 포함하는 제8a도의 패킷(Pk)의 그들 패킷만을 선택하는 것은, 예를 들어, 패킷(Pk-4, Pk-1, Pk, Pk+2, Pk+4, Pk+8)이 선택되고, 중간 패킷이 폐기된다. 결과적으로, 데이터 스트림은 시간 함수로서 데이터 스트림을 도시한 제8b도에 도시한 것처럼, 기록 캐리어 상에 기록을 위한 기록 장치 내에 포함된다.

<110> 결과적으로 제8a도 제8b도의 시간 스케일 내의 타이밍으로부터 이끌어낼 수 없고, 제8a도 및 제8b도의 시간 스케일 사이의 관련된 장소로부터 이끌어 낼 수 없다. 상기에 대한 이유는, 이전에 설명한 것처럼, 원래의 MPEG 데이터 스트림(제8a도)의 비트 전송 속도는 기록 캐리어 상에 기록되는 선택된 전송 패킷의 비트 전송속도와 상이(보다 큼)하게 된다.

<111> 제8b도에 도시된 데이터 스트림을 기록하기 위한 '정상 플레이' 처리 유닛(14)의 실시예는 제9도에 개략적으로 도시되어 있다. 제9도에 14'로 표시된 실시예는 유닛(14')의 입력(11)에 결합된 입력을 갖는 선택기 유닛(76)을 포함한다.

<112> 상기 선택기 유닛(76)은 사용자에 의해 공급되는 선택 신호를 수신하기 위한 다른 입력(78)을 갖는다. 선택기 유닛(78)의 출력(79)은 출력이 신호 조합 유닛(82)에 결합된 동기 스트립퍼(80)의 입력에 결합된다. 또한, 선택기(76)의 출력(81)은 조합 유닛(82)에 제어 신호를 공급하기 위해, 조합 유닛(82)의 제어 입력에 결합된다.

<113> 상기 입력(11)은, 패킷 번호 발생기(86)의 입력에 결합된 출력을 갖는 패킷 검출기(84)의 입력에 더 결합된다. 발생기(86)의 출력은 조합 유닛(82)의 제2 입력에 결합된다.

<114> 상기 선택기(76)는 입력(78)을 통해 수신된 선택 신호에 응답하여 입력(11)에 인가된 시리얼 MPEG 데이터 스트림으로부터 전송 패킷(Pk-4, Pk-1, Pk, Pk+2, Pk+4, Pk+8)을 선택한다.

<115> 그 선택된 패킷은, 제3도에 도시된 것처럼, 패킷 헤더에 제1 동기 바이트가 이전에 주어진 설명에 따라, 패킷으로부터 삭제되는 동기 스트립퍼(80)에 인가된다. 그 패킷 검출기(84)는 입력(11)에 인가된 원래의 시리얼 MPEG 데이터 스트림내의 각각의 패킷의 수신을 검출하고, 검출된 각각의 패킷에 대한 클럭 임펄스를 발생한다. 발생기(86)는 발생기(86)에 인가되는 클럭 임펄스의 영향 하에 카운트-업하는 카운터를 포함한다. 결과적으로, 다음 고차 카운트 번호는 수신된 각각의 클럭 임펄스에 대한 출력에 인가된다. 따라서, 발생기(86)의 출력(87)에는 카운트 번호(... k-4, k-3, k-2, k-1, k, k+1, k+2, k+3, k+8...)를 나타낸다. 조합 유닛(82)의 제어 입력(83)에 인가되는 제어 신호의 영향 하에서, 제어 유닛은 선택기(76)에 의해 선택되는 패킷(Pk-4, Pk-1, Pk, Pk+2, Pk+4, Pk+8) 뿐만 아니라 신호블록에 기억시키기 위한 패킷 번호 발생기(86)에 의해 공급된 카운트 번호 스트림 외부의 카운트 번호(k-4, k-1, k, k+2, k+4, k+8)를 조합한다.

<116> 제10도는 어떻게 전송 패킷 및 상응하는 패킷 번호가 5개의 신호 블록 그룹에 기억될 수 있는가를 나타내는 실시예를 도시한다. 제10도는 정보가 기억되는 G1, G2 및 G3으로 표시된 5개의 신호 블록의 3개의 연속 그룹을 도시한다. 그룹(G1)의 제1 신호 블록(SB1)의 제3 블록 섹션(TB 3.1)에 있어서, 그 패킷 번호(k-4)가 기억되고, 패킷(Pk-4)에서 구성된 정보가 후에 그룹(G1)의 신호 블록(SB1, SB2 및 SB3)에 기억된다. 그룹(G1)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록 섹션에 있어서, 패킷 번호(k-1)가 기억되고, 패킷(Pk-1)으로 구성된 정보는 이후에 그룹(G1)의 신호 블록(SB3, SB4 및 SB5)에 기억된다. 그룹(G2)의 제1 신호 블록(SB1)의 제3 블록 섹션(TB 3.1)에 있어서, 패킷 번호(k)는 기억되고, 패킷(Pk)으로 구성된 정보는 이후에 그룹(G2)의 신호 블록(SB1, SB2 및 SB3)에 기억된다. 그룹(G2)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록 섹션에 있어서, 패킷 번호(k+2)가 기억되고, 패킷(Pk+2)으로 구성된 정보가 후에 그룹(G2)의 신호 블록(SB3, SB4 및 SB5)에 기억된다. 그룹(G3)의 제1 신호 블록(SB1)의 제3 블록 섹션(TB 3.1)에 있어서, 패킷 번호(k+4)는 기억되고, 패킷(Pk+4)으로 구성된 정보는 후에 그룹(G3)의 신호 블록(SB3, SB4 및 SB5)에 기억된다. 그룹(G3)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록 섹션에 있어서, 패킷 번호(k+8)는 기억되고, 패킷(Pk+8)으로 구성된 정보는 후에 그룹(G3)의 신호 블록(SB3, SB4 및 SB5)에 기억된다. 패킷 번호의 다수의 비트가 8과 같거나 이보다 작게 되는 동안, 패킷 번호는 1 바이트 긴 제3 블록 섹션(FB)에 고정된다.

<117> 제3 블록 섹션 내에 패킷 번호를 기억시키는 다른 실시예는 제11도에 나타나 있다. 그룹(G1)의 신호 블록(SB1, SB2 및 SB3) 각각의 제3 블록 섹션(TB 3.1, TB 3.2 및 TB 3.3)에 있어서, 패킷 번호(k-4)는 기억되고, 패킷(Pk-4)으로 구성된 정보는 제4도를 참조하여 이전에 설명한 것처럼, 그룹(G2)의 신호 블록(SB1, SB2 및 SB3)에 기억된다. 그룹(G1)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록뿐만 아니라, 그룹(G1)의 신호 블록(SB4 및 SB5)의 제3 블록 섹션(TB 3.4 및 TB 3.5)에 있어서, 패킷 번호(k-1)는 기억되고, 패킷(Pk-1)으로 구성된 정보는 제4도를 참조하여 이전에 설명한 것처럼, 그룹(G1)의 신호 블록(SB3, SB4 및 SB5)에 기억된다. 그룹(G2)의 신호 블록(SB1, SB2 및 SB3) 각각의 제3 블록 섹션(TB 3.1, TB 3.2 및 TB 3.3)에 있어서, 패킷 번호(k)는 기억되고, 패킷(Pk)으로 구성된 정보는 그룹(G2)에 신호 블록(SB1, SB2 및 SB3)에 기억된다. 그룹(G2)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록뿐만 아니라, 그룹(G2)의 신호 블록(SB4 및 SB5)의 제3 블록 섹션(TB 3.4 및 TB 3.5)에 있어서, 패킷 번호(k-2)는 기억되고, 패킷(Pk-2)으로 구성된 정보는 그룹(G2)의 신호 블록(SB3, SB4 및 SB5)에 기억된다. 그룹(G3)의 신호 블록(SB1, SB2 및 SB3) 각각의 제3 블록 섹션(TB 3.1, TB 3.2 및 TB 3.3)에 있어서, 패킷 번호(k+4)는 기억되고, 패킷(Pk+4)으로 구성된 정보는 그룹(G3)의 신호 블록(SB1, SB2 및 SB3)에 기억된다.

<118> 그룹(G3)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록뿐만 아니라, 그룹(G3)의 신호 블록(SB4 및 SB5)의 제3 블록 섹션(TB 3.4 및 TB 3.5)에 있어서, 패킷 번호(k-8)는 기억되고, 패킷(Pk-8)으로 구성된 정보는 그룹(G3)의 신호 블록(SB3, SB4 및 SB5)에 기억된다.

<119> 그룹(G1) 내의 신호 블록(SB3)의 제3 블록 섹션(TB 3.3)에 패킷 번호(k-4)를 기억시키는 대신에, 상기 제3 블록 섹션 내에 패킷 번호(k-1)가 기억될 수 있다. 그룹(G2) 내의 신호 블록(SB3)의 제3 블록

섹션(TB 3.3)에 패킷 번호(k)를 기억시키는 대신에, 상기 제3 블록 섹션 내에 패킷 번호(k+2)가 기억될 수 있다. 그룹(G3) 내의 신호 블록(SB3)의 제3 블록 섹션(TB 3.3)에 패킷 번호(k+4)를 기억시키는 대신에, 상기 제3 블록 섹션 내에 패킷 번호(k+8)가 기억될 수 있다.

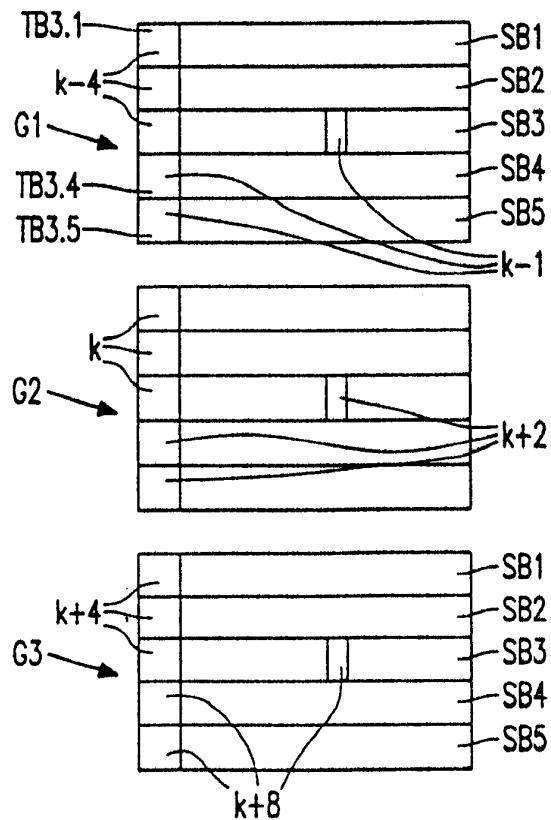

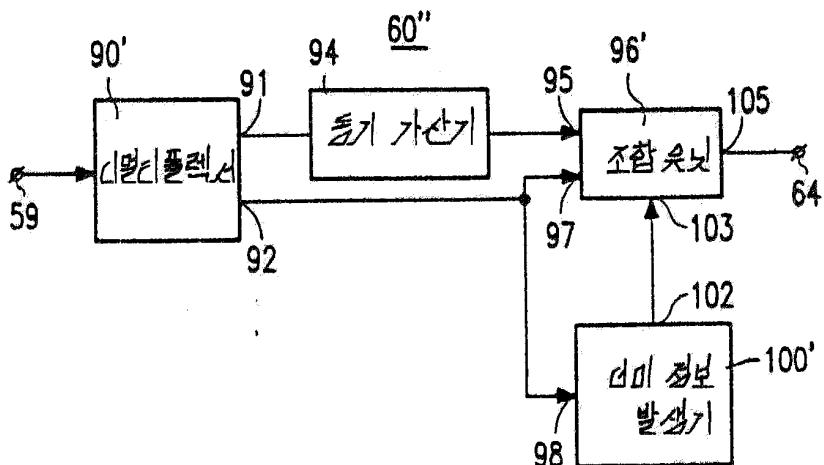

<120> 제12도는 상기 기술한 방법으로, 신호 블록 내에 또한 기억된 패킷 번호 정보를 이용하여, 제8b 도에 도시된 것 같은 데이터 스트림으로부터 제8a도의 원래의 MPEG 데이터 스트림의 사본을 재생하기 위해, 제7도의 재생 장치의 '정상 플레이' 처리 유닛(60)의 실시예를 개략적으로 도시한다. MPEG 데이터 스트림의 재생된 사본은 제8c도에 도시되어 있다.

<121> 60'으로 표시된 제12의 '정상 플레이' 처리 유닛의 실시예는 제10도 또는 제11도의 그룹(G1, G2 및 G3)과 같은, 신호 블록의 순차 그룹을 수신하고, 출력(91)에 공급되는 패킷을 검색하여 신호 블록 내의 제3 블록 섹션으로부터 패킷 번호(... k-4, k-1, k, k+2, k+4, k+8 ...)의 어레이를 검색하고, 출력(92)에 패킷 번호의 상기 어레이를 공급하기 위한 처리 유닛(60')의 입력(59)에 결합된 입력을 갖는 디멀티플렉서(90)를 포함한다. 검색된 패킷은 1 바이트 긴 패킷 동기 신호가 모든 패킷 내의 제1 바이트로서 재삽입된다. 그로 인해 얻어진 패킷은 조합 유닛(96)이 입력에 공급된다. 디멀티플렉서(90)의 출력(92)은 조합 유닛(96) 및 더미 패킷 발생기(100)의 입력(97 및 98) 각각에 결합된다. 더미 패킷 발생기(100)의 출력(102)은 조합 유닛(103)의 입력(103)에 결합된다. 조합 유닛(96)의 출력(105)은 '정상 플레이' 처리 유닛(60')의 출력(64)에 결합된다.

<122> 패킷(Pk-4) 및 패킷 번호(k-4)가 5개의 신호 블록의 제1 블록(G1)으로부터 검색되고, 조합 유닛(96) 및 더미 패킷 발생기(100)에 인가된다고 가정한다. 상기 결과는 조합 유닛(96)에 의해 출력에 패킷(Pk-4)이 공급된다. 다음, 패킷(Pk-1) 및 패킷 번호(k-1)는 그룹(G1)으로부터 검색되어, 조합 유닛(96) 및 더미 패킷 발생기(100)에 인가된다. 상기는 비교기 및/또는 감산기(도시하지 않음)에 의해 패킷 번호(k-1)가 이전에 수신된 패킷 번호(k-4)의 다음 보다 높은 패킷 번호가 되지 않고, 두 개의 패킷 번호가 누락된다. 결과적으로, 더미 패킷(100)은 데이터 스트림 내에 다른 패킷과 같은 동일한 길이인 2 배의 더미 패킷을 발생하고, 조합 유닛(96)은 제8c도에 도시된 것처럼, 패킷(Pk-4) 이후에 바로, 시리얼 데이터 스트림내에 그들 두 더미 패킷을 삽입한다. 다음, 조합 유닛(96)은 패킷(Pk-1)을 시리얼 데이터 스트림에 삽입한다.

<123> 여기서, 더미 패킷 발생기를 설명하는 발생기(100)에 대한 설명은 필요 없음을 주목한다. 또한, 그 발생기는, 시간 길이가 한 패킷의 시간 길이 배와 같거나 패킷의 시간 길이와 같게 되는 시간의 임의 길이의 더미 정보를 발생하는 더미 정보 발생기가 될 수도 있다.

<124> 패킷(Pk)은 디멀티플렉서(90)에 의해 검색되는 다음 패킷이고, 동기 신호가 조합 유닛(96)의 입력(95)에 부가된 이후에, 그 패킷은 공급된다. 패킷 번호(k)가 패킷 번호(k-1)에 대해 다음 보다 높은 패킷 번호일 때, 더미 패킷은 발생되지 않고, 그 패킷(Pk)은 출력(105)에 공급된다.

<125> 다음은 패킷(Pk+2)이 검색된다. 패킷 번호(k+2)를 검색된 이전의 패킷 번호(k)와 비교한 이후에, 한 더미 패킷이 시리얼 데이터 스트림에 삽입되어야 함이 나타난다. 다음, 패킷(Pk+2)은 제8c도에 도시된 것처럼, 데이터 스트림에 부가된다.

<126> 상기 진행은 제8c도의 MPEG 데이터 스트림의 재생된 사본을 얻기 위해 다른 패킷에 대해 계속된다. 제8a도 및 제8c도를 비교할 때, 제8c도는 제8a도의 MPEG 데이터 스트림과 같은 비트 전송 속도 및 패킷 전송 속도를 갖는 MPEG 시리얼 데이터 스트림을 나타낸다.

<127> 상기 데이터 스트림은, 제8c도의 MPEG 데이터 스트림으로부터, 재생동안 기록 장치에 의해 선택된 비디오 프로그램을 디코딩할 수 있다.

<128> 제13a도는 시간 함수로서 MPEG 시리얼 데이터 스트림을 도시하고, 그 데이터 스트림은 가변 길이를 갖는 패킷(Pk)을 포함하고, 그 데이터 스트림의 비트 전송 속도도 변화될 수 있다. MPEG 데이터 스트림의 전송 패킷이 패킷 번호를 구비하지 않음을 주목한다. 그러므로, 제13a도의 패킷에 주어진 패킷 번호(k)는 식별 목적을 위해 상기 설명에만 부가된다. 제14도는 제13a도에 도시된 것처럼 시리얼 데이터 스트림에 포함된 한 비디오 프로그램을 기록하기 위한 '정상 플레이' 처리 유닛(14)의 실시예를 개략적으로 도시한다. 제14도에 14"로 표시된 실시예는 제9도의 실시예를 갖는 큰 재구성을 도시한다. 상기 실시예(14")는 제9도의 실시예와 다른데, 즉, 패킷 번호 발생기(86) 대신에 검출기(84)의 출력에 결합된 입력과, 조합 유닛(82)의 입력(112)에 결합된 출력(111)을 갖는 타이밍 검출기(110)가 존재한다.

<129> 하나의 비디오 프로그램에 관련된 정보를 포함하는 제13a도의 시리얼 데이터 스트림 내의 패킷(Pk)의 그들 패킷(Pk) 만을 선택하는 것은 다시 선택되는데, 예를 들어, 패킷(Pk-4, Pk-1, Pk, Pk+2, Pk+4, Pk+8)이 선택되고, 중간 패킷이 무시된다. 제13b도는 제10도 및 제11도를 참조하여 이미 설명한 것처럼, 신호 블록의 그룹 내에 기억되는 선택된 패킷의 데이터 스트림을 도시한다. 여기서, 또한, 제13a도 및 제13b도의 시간 축 사이의 시간 관계가 없음을 주목한다. 또한, 제13a도의 데이터 스트림 내의 패킷이 동일치 못한 길이를 갖는다 해도, 그들 모두는 188 바이트 정보를 포함한다.

<130> 따라서 제13b도에 선택 및 표시된 패킷은 동일한 길이를 갖는 패킷으로 도시되어 있다.

<131> 제14도의 실시예는 제13a도의 데이터 스트림을 수신하고, 그 수신으로부터 패킷(Pk-4, Pk-1, Pk, Pk+2, Pk+4, Pk+8)을 선택한다. 패킷 검출기(84)는 입력(11)에 인가된 원래의 시리얼 MPEG 데이터 스트림 내의 각각의 패킷의 수신을 검출하고, 검출된 각각의 패킷에 클럭 임펄스를 발생한다.

<132> 수신된 각각의 클럭 임펄스에 응답하여, 타이밍 검출기(110)는 패킷(Pk)의 발생의 시간 순간(tk)를 제13a도에 도시된 것처럼 검출한다. 따라서, 검출기(110)의 출력에서는 시간 순간(... tk-4, tk-3, tk-2, tk-1, tk, ...) 등)이 나타난다. 또한, 시간 검출기(110)는 두 개의 연속 시간 순간 사이의 시간 간격(dt\_k)의 길이를 검출하는데, 여기서, dt\_k 는 시간 간격(tk-1-tk)과 같다. 그들 시간 간격 수치(dt\_k)는 출력(1111)에도 인가된다. 조합 유닛(82')의 제어 입력(83)에 인가되는 제어 신호와 영향 하에, 제어 유닛은 선택기(76)에 의해 선택된 패킷(Pk-4, Pk-1, Pk, Pk+2, Pk+4, Pk+8) 뿐만 아니라 신호 블록에 기억시키기 위해 타이밍 검출기(110)에 의해 공급된 정보 스트림의 외부에 상응하는 시간 간격(tk-4, dt\_k-4,

$tk-1, dtk-1, tk, dtk, tk+2, dtk+2, tk+4, tk+8, dtk+8$ 을 조합한다.

<133> 신호 블록 내의 전송 패킷의 기억은 제10도 및 제11도를 참조하여 상기 기술한 동일한 방법으로 실행된다. 제3 블록 섹션 내의 타이밍 정보의 기억은 다음과 같이 될 수 있다.

<134> 제10도의 그룹(G1)의 제1 신호 블록(SB1)의 제3 블록 섹션(TB 3.1)에 있어서, 타이밍 정보( $tk-4$  및  $dtk-4$ )는 기억 된다. 그룹(G1)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록 섹션에 있어서, 타이밍 정보( $tk-1$  및  $dtk-1$ )는 기억된다.

<135> 그룹(G2)의 제1 신호 블록의 제3 블록 섹션(TB 3.1)에 있어서, 타이밍 정보( $tk+2$  및  $dtk+2$ )는 기억된다. 그룹(G3)의 제1 신호 블록(SB1)의 제3 블록 섹션(TB 3.1)에 있어서, 타이밍 정보( $tk+4$  및  $dtk+4$ )는 기억된다. 그룹(G3)의 제3 신호 블록(SB3)의 FB로 표시된 제3 블록 섹션에 있어서, 타이밍 정보( $tk+8$  및  $dtk+8$ )가 기억된다.

<136> 상기는 그룹 내의 제1 신호 블록(SB1) 내의 제3 블록 섹션(TB 3.1) 및/또는 그룹 내의 제3 신호 블록(SB3) 내의 제3 블록 섹션(FB)는 타이밍 정보를 기억하기 위해 너무 작게 되도록 될 수 있다. 상기 경우에, 타이밍 정보는 어느 경우에도 기억될 수 있거나, 제3 블록 섹션(TB 3.1 및 FB) 내의 일부 및 아래에 설명된 것처럼, 어느 경우의 일부에 기억될 수 있다.

<137> 제11도의 실시예에 따라, 타이밍 정보( $tk-4$  및  $dtk-4$ )는 그룹(G1)의 신호 블록(SB1, SB2 및 SB3)의 제3 블록 섹션(TB 3.1, TB 3.2 및 TB 3.3) 내에 기억된다. 타이밍 정보의 기억은 제3 블록 섹션(TB 3.1, TB 3.2 및 TB 3.3)의 전체 기억 용량내에서 한번 실행될 수 있거나, 최소한 한번 반복될 수 있다. 예를 들어, 타이밍 정보( $tk-4$  및  $dtk-4$ )는 제3 블록 섹션(TB 3.1, TB 3.2 및 TB 3.3)의 각각에 기억된다. 그 타이밍 정보( $tk-4$  및  $dtk-1$ )는 그룹(G1)의 신호 블록(SB3, SB4 및 SB5) 각각의 제3 블록 섹션(FB, TB 3.4 및 TB 3.5)에 기억될 수 있다. 타이밍 정보의 기억은 제3 블록 섹션(FB, TB 3.4 및 TB 3.5)의 전체 기억 용량에서 한번 실행될 수 있거나, 최소한 한 번 반복될 수 있다. 예를 들어, 타이밍 정보( $tk-4$  및  $dtk-4$ )는 제3 블록 섹션(TB 3.4 및 TB 3.5)의 각각에 기억된다. 상기는 제3 블록 섹션(TB 3.3)의 패킷(Pk-1)에 대해 타이밍 정보를 기억시킬 수 있다. 또한, 제3 블록 섹션(TB 3.4 및 TB 3.5)에서 타이밍 정보를 기억할 수 있고, 블록 섹션(FB)에 기억시킬 수 없다.

<138> 패킷(Pk)에 대한 타이밍 정보는 패킷(Pk-4)에 대한 타이밍 정보가 그룹(G1)의 제3 블록 섹션 내에 기억되는 방식으로 그룹(G2)의 제3 블록에 기억될 수 있다. 패킷(Pk+2)에 대한 타이밍 정보는 패킷(Pk-1)에 대한 타이밍 정보가 그룹(G1)의 제3 블록 섹션 내에 기억되는 방식으로 그룹(G2)의 제3 블록 섹션에 기억시킬 수 있다.

<139> 패킷(Pk+4k)에 대한 타이밍 정보는 패킷(Pk-4)에 대한 타이밍 정보가 그룹(G1)의 제3 블록 섹션에 기억되는 방식으로 그룹(G3)의 제3 블록 섹션에 기억될 수 있다. 패킷(Pk+8)에 대한 타이밍 정보는 패킷(Pk-1)에 대한 타이밍 정보가 그룹(G1)의 제3 블록 섹션에 기억된 방식으로 그룹(G3)의 제3 블록 섹션에 기억될 수 있다.

<140> 제15도는, 상기 기술한 방식으로, 신호 블록에 기억된 타이밍 정보를 이용하여, 제13b도에 도시된 데이터 스트림으로부터 제13a도의 원래 MPEG 데이터 스트림의 사본을 재생하기 위해, 60"으로 표시된 제7도의 재생 장치의 '정상 플레이' 처리 유닛의 실시예를 개략적으로 도시한다. MPEG 데이터 스트림의 재생된 사본은 제13c도에 도시되어 있다. 제12도의 실시예(60")는 제12도의 처리 유닛과 함께 보다 큰 구성을 나타낸다. 디멀티플렉서(90')는 신호 블록의 연속 그룹으로부터 패킷을 검색하고, 그 패킷을 출력(91)에 공급하도록 채택된다. 그 디멀티플렉서(90')는 신호 블록 내의 제3 블록 섹션으로부터 타이밍 정보( $tk$  및  $dtk$ )를 검색하고, 상기 타이밍 정보를 출력(92)에 공급하기 위해 채택된다. 동기 바이트는 동기 가산기(94) 내의 각각의 패킷에 부가된다. 따라서 얻어진 패킷은 조합 유닛(96')의 입력(95)에 공급된다. 디멀티플렉서(90)의 출력(92)은 조합 유닛(96') 및 발생기(100')에 타이밍 정보를 공급하기 위해 조합 유닛(96') 및 더미 정보 발생기(100')의 입력(97 및 98) 각각에 결합된다.

<141> 패킷(Pk-4)과 상응하는 타이밍 정보는 5 신호 블록의 제1 그룹(G1)으로부터 검색되고, 조합 유닛(96') 및 더미 패킷 발생기(100')에 인가된다고 가정한다. 상기는 타이밍 정보에 응답하여, 조합 유닛(96')에 의해 출력(105)에 패킷(Pk-4)이 공급된다. 패킷(Pk-4)의 길이는  $dtk-4$ 와 같게 되고, 패킷은  $tk-4$ 에 상응하는 시간상수로 출력(105)에 인가된다.

<142> 다음에, 패킷(Pk-1) 및 패킷(Pk-1)에 상응하는 타이밍 정보는 그룹(G1)으로부터 검색되고, 조합 유닛(96') 및 더미 패킷 발생기(100')에 인가된다. 상기는, 비교기 및/또는 감산기(도시하지 않음)에 의해, 시간 순간( $tk-1$ )은  $tk-4 + dtk-4$ 와 같지 않게 설정된다. 결과적으로, 최소한 하나의 패킷 다음의 패킷(Pk-4)은 기록동안 무시된다. 결과적으로, 더미 정보 발생기(100')는, 제13c도에 도시된 것처럼, 시간 순간( $tk-4 + dtk-4$ ) 및 시간 상수( $tk-1$ )에서, 패킷(Pk-4)의 단부 사이의 캡을 채우기 위해 더미 정보의 블록을 발생한다.

<143> 다음, 조합 유닛(96')은 길이( $dtk-1$ )를 갖는 패킷(Pk-1)을 시리얼 데이터 스트림에 삽입한다.

<144> 패킷(Pk)은 디멀티플렉서(90)에 의해 검색된 다음 패킷이고, 그 패킷은 조합 유닛(96')의 입력(95)에 동기 바이트의 부가 이후에 공급된다. 패킷(Pk)에 상응하는 타이밍 정보는 조합 유닛(96) 및 더미 정보 발생기(100')의 입력(97 및 98)에 공급된다.  $tk$  가  $tk-1 + dtk-1$ 일 때, 더미 정보가 발생할 필요가 없고, 패킷(Pk)은 출력(105)에 공급된다.

<145> 다음, 패킷(Pk+2)은 검색된다.  $tk+2$ 와  $tk+dtk$ 를 비교한 이후에, 상기는 발생기(100')에 의해 발생된 더미 정보가 채워질 수 있는 필요성이 있는 캡을 설정한다. 다음, 길이  $dtk+2$ 를 갖는 패킷(Pk+2)은 제13c도에 도시된 것처럼, 데이터 스트림에 부가된다. 상기 공정은, 제13c도의 MPEG 데이터 스트림의 재발생된 사본을 얻기 위해 다른 패킷에 대해 계속된다. 제13a도와 제13c도를 비교할 때, 제13c도는 제13a도의 MPEG 데이터 스트림과 같은 동일한(가변) 비트 전송 속도 및 패킷 전송 속도를 갖는 MPEG 시리얼 데이터 스트림을 나타냄을 알 수 있다. 상기 데이터 스트림은 가변 비트 전송 속도 및 패킷 전송 속도를 갖는 제13c도의 MPEG 데이터 스트림으로부터, 기록동안 기록 장치에 의해 선택된 비디오 프로그램을 디코딩

할 수 있다.

<146> 지금, 다른 정보는 상기 기술한 타이밍 정보 및 패킷 번호 정보와 함께 또는 따로 신호 블록의 그룹 내의 자유 공간에 삽입될 수 있음을 설명한다.

<147> 그와 같은 다른 정보의 한 예는 신호 블록 그룹 내의 제1 신호 블록이 되는 y(=5) 신호 블록의 그룹 내의 신호를 식별하는 정보이다. 그 정보는 제10도 및 제11도의 그룹(G1, G2 및 G3) 내의 신호 블록(SB1)의 제3 블록 섹션(TB 3.1) 내에 기억될 수 있다.

<148> 그 다른 정보의 다른 예는 제11도의 상태와 같은 신호 블록의 제3 블록 섹션내의 신호 블록 번호의 포함이다. 신호 블록 번호 지정은 그룹 내에서 실행될 수 있기 때문에, 제11도의 실시예에서 번호(1 내지 5)는 각각의 그룹 내의 신호 블록(SB1 내지 SB5)의 제3 블록 섹션(TB 3.1 내지 TB 3.5)에 기억된다. 신호 블록 번호 지정은 신호 블록의 한 그룹보다 큰 그룹에 속하는 신호 블록의 보다 큰 번호가 실현될 수 있다. 한 트랙 내의 신호 블록의 모든 것은 신호 블록의 제3 블록 섹션내에 기억된 유일한 신호 블록 번호를 가짐을 알 수 있다. 지금, 한 트랙 내의 모든 신호 블록은 그들 유일한 신호 블록 번호에 의해 식별될 수 있다.

<149> 상기 기술한 것 같은 신호 블록을 번호 지정하는 신호 블록은 다수의 장점을 갖는다. 신호 블록을 번호 지정은 유일한 블록 번호에 의해 식별된 신호 블록의 그룹 내에 셔플링이 실행되는 동안, 원래의 순서와 다른 순서로 신호 블록을 셔플링할 수 있다. 재생 동안 신호 블록 번호를 검출하여, 디셔플링은 신호 블록의 원래의 순서를 얻기 위해 셔플링된 신호 블록을 실행될 수 있다.

<150> 신호 블록 내에 포함된 정보의 기록 및 순차 재생이 전송 에러에 대하여 보다 높은 보호를 필요로 하기 때문에 실행될 수 있는 다른 측정은 반복될 수 있다. 반복된 신호 블록은 동일한 신호 블록 번호를 가질 수 있기 때문에, 재생에 따라 식별될 수 있다.

<151> 또한, 신호 블록 번호의 검출에 따라, 신호 블록이 손실되는지를 검출할 수 있는데, 그 이유는 순차 기록 및 재생 단계 동안 전송 에러가 발생할 수 있기 때문이다. 신호 블록 번호의 순차로 신호 블록 번호를 누락할 때, 누락된 신호 블록 번호를 갖는 신호 블록이 손실되는지를 결정할 수 있다. 그와 같은 검출에 따라, 누락된 신호 블록을 교정 및 취소하기 위해 에러 보정 또는 취소가 실행될 수 있다.

<152> 다음은, 제6도의 기록 장치 및 제7도의 재생 장치 각각의 '트릭 플레이' 처리 유닛(16 및 62)의 기능을 설명한다.

<153> 재생 장치에 따른 트릭 모드(또는 특징 모드) 재생을 실행하기 위해, 기록 캐리어(40)는 정상 전송 속도와 다른 속도로 전송 된다. 제16도는 기록되는 슬랜트 트랙의 수를 갖는 기록 캐리어(40)를 도시한다. 또한, 제16도는 참고 번호(120)에 의해 표시된 경로를 도시하는데, 그 경로를 통해 판독 헤드(54)는 상기 트랙 모드에서 기록 캐리어를 주사한다. 일반적으로, 트랙 내의 정보는 우수 번호의 트랙이 하나의 수평각을 갖고, 기수 번호의 트랙이 다른 수평각을 갖게 되도록, 상이한 수평각 갭을 갖는 최소한 두 헤드에 의해 기록된다. 상기는 경로(120)를 따라 기록 캐리어를 주사할 때, 두 개의 수평각 중 한 각도를 갖는 헤드(52)는 단지 기수 번호 또는 단지 기수 번호의 트랙으로부터 정보를 판독할 수 있다.

<154> 트릭 플레이동안 비디오 정보의 재생을 가능하게 하기 위하여, 특히, 비디오 정보가 감소된 데이터 형태로 기록되는 경우에 있어서, 트릭 플레이 모드에서 있을 수 있는 기록 캐리어에 대한 여러 전송 속도를 헤드에 의해 그들 위치가 주사되도록 트랙 내의 특정 위치에 특정 트릭 플레이 정보를 부가시킬 필요가 있다. 상기 트릭 플레이 정보는 상기 기술한 방법으로 트랙 내에 기록된 정상 플레이 비디오 정보에 부가하여 기록되는 특정 비디오 정보이다. 결과적으로, 트랙 내의 약간의 신호 블록은 상기 트랙 플레이 정보를 포함하는데, 상기는 트랙 플레이 모드에서 헤드(52)에 의해 주사 및 판독되어야 한다.

<155> 여기서, MPEG 데이터 스트림 내의 비디오 데이터가 관련되는 동안, MPEG 데이터는 데이터가 감소된 비디오 정보를 포함함을 주시한다. 그와 같은 감소된 비디오 정보를 실현하기 위해, 한 화상에 상응하는 정보는 소위 I-프레임을 얻기 위해 인트라 인코딩된다. 보다 높은 데이터 감소는 제1 화상에 대한 I-프레임 및 제2 화상에 대한 P-프레임을 얻는 최소한 두 개의 순차 화상에 인터 프레임 인코딩을 실행하여 얻어질 수 있다.

<156> 두 개의 화상을 재작성을 위해, 인트라 프레임 인코딩에 대해 반전된 인트라 프레임 인코딩은 제1 화상을 재생하기 위해 I-프레임 정보 상에서 실행되어야 하고, 인터 프레임 인코딩에 반전된 인터 프레임 디코딩은 제2 화상을 재생하기 위해 I-프레임 정보 및 P-프레임 정보 모두를 이용하여 실행되어야 한다.

<157> 트릭 모드에 있어서, 단지 I-프레임 정보는 I-프레임 정보뿐만 아니라 상응하는 P-프레임 정보를 검색할 때 인터 프레임 디코딩을 실현하기 위하여 비디오 신호를 재생하는데 이용될 수 있다. 따라서 '트릭 플레이' 정보를 얻기 위하여, 시리얼 MPEG 데이터 스트림에 포함된 I-프레임이 기억된 정보만이 '트릭 플레이' 데이터로서 추출 및 이용된다.

<158> 상기는 제16도의 트랙(124) 내의 해칭된 영역(122)에 의해 표시된 위치와 같은 트랙 내의 특정 장소에서, 삽입된 다수의 신호 블록은 '트릭 플레이' 정보를 포함하는 것을 의미한다. 제17도는 트랙(124) 내의 신호 블록의 순서를 나타낸다. 제16도의 해칭된 영역(122)은 제17도에 주어진 순서에 포함된 신호 블록(SBi 내지 SBj)의 순서에 의해 형성된다. 트랙의 트랙 플레이 영역(122) 내에 포함된 신호 블록(SBi 내지 SBj)은 신호 블록이 트랙 모드 정보를 포함하는 표시를 포함한다. 상기 표시 정보는 포함된 신호 블록(SBi 내지 SBj)의 제3 블록 섹션(TB3)내의 'T'에 의해 표시된다. 트릭 플레이 영역(122) 이전에 트릭 내에 기억된 신호 블록뿐만 아니라 트랙 플레이 영역(122) 이후에 트랙 내에 기억된 신호 블록은 신호 블록 내에 기억된 정보가 정상 플레이 정보인 것을 나타내는 정보를 포함한다. 상기 표시 정보는 신호 블록(SBi-2, SBi-1, SBj+1) 내의 제3 블록 섹션의 'N'으로 표시된다.

<159> 따라서 제16도의 '트릭 플레이'는 입력(17)에 인가된 MPEG 데이터 스트림으로부터 트릭 플레이 정보를 유도하고, 트랙 내의 특정 위치에 트릭 플레이 정보를 기억하는 것을 특히 의미 하는 그들 신호

블록 내의 트릭 플레이 정보를 기억하며, 신호 블록이 트릭 모드 정보가 그들 신호 블록의 제3 블록 섹션에 기억되는 신호 블록을 나타내는 표시 정보를 삽입할 수 있다. 또한, '정상 플레이' 처리 유닛(14)은 유닛(14)에 의해 발생된 신호 블록이 그들 신호 블록의 제3 블록 섹션에서, 정상 플레이 정보를 나타내는 표시 정보를 기억시킬 수 있다.

<160> 재생 장치가 트릭 모드로 전환될 때, '트릭 플레이' 처리 유닛(62)은 그들 제3 블록 섹션에 기억된 'T' 식별자를 갖는 그들 신호 블록을 검출하여, 트릭 모드동안 재검토 옵션을 실현하기 위해 다른 처리를 위해 그들 신호 블록으로부터 정보를 검색할 수 있다.

<161> 상기 기술한 실시예에는 MPEG 이송 스트림을 수신하고, 비동기적으로 DVCR 상에 기록하며, 재생동안 원래의 MPEG 전송 스트림을 재작성하기 위한 장치를 설명한다. 상기는 비동기 채널(DVCR)을 통해 타이밍 임계값(MPEG 데이터 스트림)을 전송하는 방법으로 넓게 볼 수 있다.

<162> MPEG 데이터 스트림과 함께, 비동기 채널을 통해 타이밍 임계 데이터의 전송에 필요로 될 수 있는 여러 다른 응용이 있을 수 있다. 여기서, 비동기는 채널의 물리적 데이터 속도가 전송 속도와 상이함을 의미하고, 데이터의 비트와 같은 타이밍은 채널 전송을 통해 유지되지 못함을 의미한다.

<163> 타이밍 임계 데이터의 예로서 MPEG 전송 스트림에 있어서, 예를 들어, 프로그램 클럭 참조(PCR) 인 전송 스트림의 타이밍 전송을 나타내는 데이터의 관련된 도착 시간은 그에 따라 PCR 값 변경 없이 전송을 통해 특정 허용 오차 이상으로 변화할 수 없다. 반면에, 상기는 디코더의 위상 고정 루프(PLL) 회로는 데이터 클럭을 재생하는데 실패하고, 그 버퍼는 언더/오버플로우 될 수 있다.

<164> 동기 채널이 컴퓨터 네트워크, 전화기 네트워크 또는 디지털 인터페이스, 예를 들어 P1394에 전송될 임의 데이터 변경 없이 비동기화 채널을 통해 타이밍 임계 데이터가 어떻게 전송되는지의 문제가 존재한다.

<165> MPEG 출원에 관련된 상기 설명에서처럼, 기본 장치는 전송 이전에 타이밍 정보와 각각의 전송 유닛, 예를 들어 MPEG 전송 패킷을 태그하고, 채널의 다른 단부에서 적당한 데이터 타이밍을 재작성하기 위한 태그된 정보를 사용한다.

<166> 1. 전송 유닛의 사이즈와 전송 속도 모두가 공지되고 일정하다면, 채널의 전송기 측면은 각각의 전송 유닛에서 1로 증가된 순차 번호와 각각의 전송 유닛을 태그한다. 상기 태그는, 한 예로서, 각각의 전송 유닛의 전면에 고정된 비트 번호를 삽입시켜 행해진다. 태그에 대한 다수의 비트는 표현된 다수의 순서가, 예를 들어 채널 에러로 인한 최대 연속 누락 전송 유닛으로 카피하기에 충분히 크게 되도록 선택된다. 그 카운터는 각각의 전송 세션의 시작부에서 제1 수신된 전송 유닛의 순차 번호로 로드되고, 수신기가 전송 유닛 또는 더미 유닛을 전송할 때 매번 1로 증가된다. 수신된 전송 유닛의 순차 번호가 카운터 값과 일치한다면, 수신된 전송 유닛은 전송되고, 반면에, 더미 유닛의 필요한 수는 카운터 값이 순차 번호와 일치할 때까지 전송된다. 상기 수신기는 태그된 정보를 스트림하고, 이미 공지되고 일정한 속도로 전송 유닛 또는 더미 유닛을 전송한다.

<167> 2. 전송 유닛의 사이즈가 공지되고 일정하지만, 전송 속도가 공지되어 있지 않다면, 채널의 전송 기 측은, 예를 들어, 전송 유닛의 시작 시간 및 종료 시간을 결정하는데 충분한 2배의 정보와 각각의 전송 유닛을 태그한다. 예를 들어, 전송 유닛의 시작 시간 및 시간 간격의 쌍 또는 시작 시간 및 종료 시간 자체의 쌍을 이용할 수 있다. 채널의 수신기측은 각각의 전송 유닛의 시작 시간을 체크하면서 태그된 전송으로부터 전송 속도를 재작성하여야 한다. 상기 경우에 더미 유닛을 삽입시킬 필요가 없다.

<168> 3. 특정 데이터의 타이밍만이 중요하게 된다면, 전체의 전송 스트림의 특성을 유지할 필요가 없는데, 예를 들어, 특정 데이터의 타이밍만이 유지되어야 하고, 전송 유닛의 시간 충돌이 발생하지 않을 만큼 높은 수신기에 의해 작성된 전송 속도가 제공되는 태그된 정보로부터 전송 속도를 재형성할 필요가 없다. 채널의 전송족은 각각의 전송 유닛을 타이밍 임계 데이터 위치와 예측된 도착 시간과 태그한다. 그 장소는 공지되고 일정하게 된다면, 위치 정보는 생략될 수 있다.

<169> 각각의 유닛 내의 하나의 타이밍 임계 데이터보다 더 많다면, 다수의 예비 정보 쌍은 그에 따라 부가될 수 있다. 채널의 수신기측은 출력 전송 속도, 위치 및 타이밍 임계 데이터의 예측된 도착 시간으로부터 각각의 전송 유닛의 시작 시간을 결정한다.

<170> 상기 경우에 더미 유닛을 삽입시킬 필요가 없다.

<171> 제18도는 디지털 인터페이스(D-I/F)로부터 전송 패킷의 연속 형태로 전송 유닛을 서브 분할한 MPEG 데이터 스트림의 전송 비율을 R 이 나타내는 MPEG 출원에 다시 인가된 기본 시스템의 다른 형태인 블록도를 나타낸다.

<172> 선택 블록(130)은 제 9도의 선택기(76)에 상응한다.

<173> 상기 실시예는 위치(2)에 상응하고, 그로인해, 입력된 데이터 스트림의 타이밍 정보를 결정하기 위한 기준 클럭(132) 및 카운터(133)를 포함하고, 로컬 카운터에 관하여, "도착 타이밍(TOA) 스템프 및 "도착 기간"(DOA) 모두와 블록(135)을 통해 각각의 전송 패킷을 태그한다. 상기 태그 비트는 이전에 설명된 것처럼, 2 내지 5 동기 블록 매핑으로부터 이용 가능한 예비 비트를 사용하여 상응하는 전송 패킷(TPs)과 함께 테이프에 버퍼(137)를 통해 기록된다.

<174> 재생에 따라, 각각의 기록 패킷은 판독 제어 블록(138)의 제어 하에 "도착 시간" 및 "도착 기간" 스템프 정보에 따라 정확한 시간 및 속도로 판독된다. TOA 스템프는 VCR 이 버퍼(131)로부터 특정 TP를 판독하여 D-I/F에 출력을 시작할 때의 시간을 나타낸다. 그 DOA 스템프는 TP 가 판독되어야 하는 비율을 나타내는데, 예를 들어, TP 의 188 바이트는 TP 가 패킷의 DOA 동안 판독되어야 하고, 그로인해 그 속도는 쉽게 계산될 수 있다. MUX 블록(139)는 정상 방법으로 이용되어, 원하는 널(null) 패킷 및 트릭 모드와 태그된 패킷을 인터리브되고, DE-MUX 블록(140)은 재생이 따라 부가된 패킷은 스트립하기 위해 작동한다. 상기 장치는 정확한 시간 및 정확한 속도로 정밀하게 원하는 모든 패킷을 재생한다. 그러나 출력 스트림은 누락된 패킷을 채우지 못하므로, 겹을 갖는다. 상기 주된 이유는 입력 스트림이 전송 패킷 길이의

정수가 아닌 캡을 가질 수 있기 때문이다. 예를 들어, Grand Alliance 스트림은 긴 20 바이트만큼 작은 캡을 갖도록 기대된다. 그들은 VCR에 의해 채워지지 못할 수 있다. 또한, 상기 장치에 있어서, 기록되지 않은 PID 패킷은 출력 전송 스트림에서 캡으로 나타난다.

<175> 제19도는 전송 스트림 결과의 예를 나타낸다.

<176> 상부도에 있어서, 예를 들어, 입력 전송 스트림은 두 개의 프로그램 스트림을 갖는데, 프로그램(A) 및 프로그램(B)이다. 우리는 단지 프로그램(A)을 기록한다. 재생에 따라, 프로그램(A)에 속하는 모든 패킷은 그들 원래의 시간 및 속도로 정밀하게 재생되지만, 기록되지 않은 프로그램(B)에 채워지지 않는다.

<177> 따라서 하부도에 도시된 출력 스트림은 입력 스트림보다 더 많은 버스티를 갖는다. 입력 스트림이 유효 MPEG 신호였다면, 그 출력 스트림은 유효하게 될 수 있다.

<178> 입력 데이터 스트림(R) 내의 타이밍 정보는 본 발명에 중요하지 않은 다수의 상이한 방법으로 결정될 수 있다.

<179> 예를 들어, 한 간단한 방법은 각각 들어오는 TP의 시작 및 종료를 검출할 수 있는 공지된 패킷 검출기 회로(134)에 입력 데이터 스트림을 접속시키는 것이다. 그 후, 패킷 검출기 회로의 출력은 소정의 타이밍 정보를 나타내는 카운터(133)의 카운터 값을 검출하는데 이용될 수 있다. 기준 클럭(132)은 태그된 정보의 일관된 해석에 대한 기록 및 재생 공정에 대해 동일한 주파수가 되어야 하고, 적당한 단계는 기록 및 재생 동안 일치된 선정된 방법 내의 카운터(133)를 초기화하기 위해 취해진다.

<180> 기록된 타이머 정보는 판독 제어 블록(138) 내의 전송 스트림으로부터 스트립되고, 기억된(TPs) 가 출력될 때를 결정하기 위해 이용된다.

<181> 인입 전송 스트림의 전송 속도가 일정하고 공지된 상태(1)에 있어서, 이전 방법에 따른 변화는 재생에 따른 상기 스트림을 재작성하는데 이용될 수 있다. 본 실시예의 메인 특성은 단지 로컬 카운터(제 18도의 기준 클럭 및 카운터 대신에)를 필요로 하고, 각각의 전송 패킷의 도착에서 증가하고, 2 내지 5 매핑으로부터 이용가능한 예비 비트를 사용하여, '도착 순서'(SOA)와 각각의 전송 패킷을 태그한다. 재생에 따라, SOA 태그 내의 "불연속"이 매번 검출되고, TP 가 기록되지 않는 결과가 발생됨을 인지한다. 상기 "누락"패킷은 널 패킷과 대치된다. 모든 TP는 공지되고 일정한 전송 속도로 출력된다.

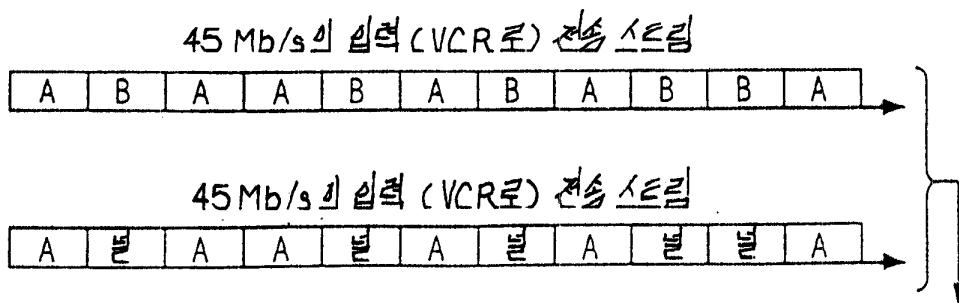

<182> 제20도는 임계 타이밍 정보의 보수를 도시한 입출력 스트림을 설명하는 타이밍도이다.

<183> 제18도의 블록도에 있어서, 데이터의 흐름만이 화살표로 도시되어 있다. 본 기술에 숙련된 사람들은 도면에는 도시하지 않았지만 명령 및 제어 신호에 여러 블록이 상호 접속됨을 알 수 있다.

<184> 이전에 지적한 것처럼, 본 발명은 임계 타이밍 데이터를 보존하는 다른 데이터 포맷 및 다른 방법에 응용될 수 있다.

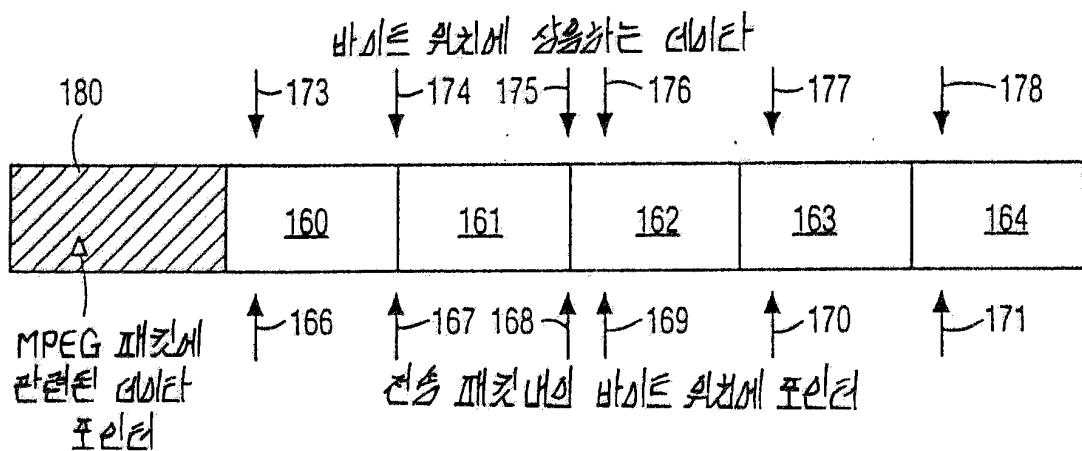

<185> 제21도는 각각의 데이터 블록(150)이 블록 헤더의 형태로 프리앰블(151), 데이터 스트림을 실행하기 위한 블록 페이로드(152)와, 블록(CRC)의 형태로 포스트앰블(153)을 포함하는 약간의 채널의 블록 데이터 전송 유닛을 나타낸다. 제22도는 MPEG 출원에서 블록 페이로드의 포맷팅의 한예를 도시한다. 본 예에 있어서, 블록 페이로드(152)는 5개의 188 바이트 MPEG 전송 패킷(160...164)을 전달한다. 전송 패킷의 바이트 위치에 6개의 지시자(166...171)가 있다. 각각의 바이트 지시자(166...171)와 관련된 데이터(173...178)는 타이밍 정보이다. 모든 지시자와 타이밍 정보를 나타내는 관련된 데이터는 한 예를 들어, 5 전송 패킷과 함께 기억되는 예비 24 바이트가 필요하다. 그들은 페이로드 태그 또는 헤더(180)에 기억된다. 예를 들어, 각각의 위치 지시자 x 6개의 지시자(166...171) = 60 바이트에 대한 10비트; 각각의 타이밍 데이터 지시자 x 6개의 지시자(173...178) = 126 바이트에 대한 21 비트; 전체의 186 바이트 또는 약 24 바이트를 가정한다.

<186> 알 수 있듯이, 바이트 위치 지시자는 특정 패킷의 시작 및 종료에 대해 모든 지적을 필요치 않는다. 상기 예에 있어서, 단지 바이트 위치 지시자(167 및 168)는 제2 전송 패킷(161)의 시작 및 종료 위치에 대해 지시하는 것이 바람직하다. 그 오프셋 위치는 PCR 위치인데, 데이터 스트림의 인코딩 소스에 장치 내의 클럭을 고정하기 위한 데이터 동기 펄스와 같은 타이머 회복에 전형적으로 이용되고, 전송 패킷의 시작부 이후에 12 번째 바이트에 전형적으로 위치된다. 바이트 위치 지시자의 선택에 의해, 단지 6개의 지시자(166...171)는 2개의 지시자를 갖는 1 패킷과 단지 1개의 지시자를 갖는 나머지 4개의 패킷인 5 개의 패킷 160...164 순서의 타이밍 정보를 식별하는데 필요하다. 상기 경우에 관련된 데이터(173...178)는 6개의 지시자에 의해 지적된 시간 순간이다. 그 관련된 데이터는 또한 패킷 번호를 포함할 수 있다. 비트 전송 속도가 공지되고 일정하게 되는 경우에, 데이터는 패킷 번호 하나만 있을 수 있다. 결과적인 전체 플레이 로드는 5개의 패킷(160...164) 플러스 플레이 로드 헤더 또는 연속 5TP에 대한 타이밍 정보를 포함하는 태그(180)이다.

<187> 헤더(180) 내에 포함된 것은 정보 유닛과 관련된 두 개의 필드임을 알 수 있다. 예를 들어, 지시자에 의해 지적된 바이트 위치를 포함하고, 바이트 위치에 대한 타이밍 정보를 포함하는 제2 필드를 포함한다.

<188> 제21도 및 제22도에 설명된 장치의 구현을 위해, 제18도에 설명된 동일한 장치는 블록 헤더, 플레이 로드 태그를 계산 및 부가하는 것과, 전송 패킷 및 CRC 블록을 기록이전에 부가하는 것을 포함하는 블록 포맷팅을 제공하기 위해 버퍼단(137) 이전에 위치한 블록 포맷터단과 이용될 수 있다.

<189> 본 발명과 이용 가능한 여러 태그 선택은 제23도에 요약되어 있다. 태그 선택(1)은 패킷 시작 및 종료 시간을 포함하고; 태그 선택(2)은 패킷 시작 시간 및 패킷 기간을 포함하고; 태그 선택(3)은 위치가 공지된 PCR과 같은 타이밍 임계 데이터를 포함하며, 따라서, 다른 선택과 비교된 정보의 지시자 또는 항목은 최소한 2개의 정보 항목을 필요로 한다.

<190> 본 명세서의 "타이밍 정보" 표현은 제23도의 정보뿐만 아니라, 패킷 순차 번호를 포함하기 위해

방송 센스에 이용되고, 일반적으로, 타이밍을 위한 모든 정보는 외부 관찰자를 통해 볼 수 있는 것을 의미하고, 채널은 타이밍을 실행하지도, 또는 변경하지도 못한다.

<191> 본 발명은 실시간 데이터, 소위 MPEG 정보 신호에 의해 전송되거나 방송오디는 데이터는 비-실시간 메디아(DVCR)에 기록되는 상태에서 설명되었다. 다른 중요한 실시예는 P1394 D-I/F로서 공지된 것이고, 원래 데이터 스트리밍의 타이밍을 회복하는데 비동기 전송이 필수적으로 포함된다.

<192> P1394 인터페이스 프로토콜에 있어서, 제21도에 도시된 것과 같은 데이터 블록은 예를 들어, 컴퓨터 또는 소비자 전자 장치 사이의 데이터 전송을 위해 이용된다. 데이터가 MPEG 전송 패킷일 때, 제21도 및 제22도에 관하여 상기 주어진 설명이 이용될 수 있다. 이 경우에, 채널은 P1394 인터페이스의 비동기 특성으로 MPEG 데이터 스트리밍을 기억하지 못하고, MPEG 패킷의 정확한 타이밍은 본 명세서에 기재된 발명을 사용없이 손실된다.

### 참조 문헌

<194> (1) 유럽 특허출원 제492,704호(PHN 13.546)

<195> (2) 유럽 특허출원 제93.202.950호(PHN 14.241)

<196> (3) 유럽 특허출원 제93.201.263호(PHN 14.449)

<197> (4) Grand Alliance HDTV System Specification, Draft document, February 22, 1994.

<198> (5) 미국 특허 명세서 제5,142,421호(PHN 13.537)

## (57) 청구의 범위

### 청구항 1

비동기 채널을 통해 타이밍 임계(timing-critical) 데이터를 전송하는 방법으로서,

(i) 임계적으로 시간 조정된 연속적인 전송 유닛들의 스트리밍으로 재분할된 상기 타이밍 임계 데이터를 제공하는 단계를 포함하는 상기 타이밍 임계 데이터 전송 방법에 있어서,

(ii) 상기 타이밍 임계 데이터로부터 상기 전송 유닛들에 대한 타이밍 정보의 적어도 한 개의 항목을 포함하는 스트리밍 재작성 정보를 판정하는 단계로서, 상기 스트리밍 재작성 정보로부터 상기 타이밍 임계 데이터가 재작성될 수 있는, 상기 스트리밍 재작성 정보 판정 단계와,

(iii) 상기 전송 유닛들 중 적어도 일부의 전송 유닛들에 타이밍 정보의 상기 적어도 한 개의 항목을 태그하는 단계와,

(iv) 상기 전송 유닛들을 타이밍 정보의 상기 태그된 항목들과 함께 상기 비동기 채널 상으로 전송하는 단계를 더 포함하는 특징으로 하는 타이밍 임계 데이터 전송 방법.

### 청구항 2

제1항에 있어서, 상기 타이밍 임계 데이터는 MPEG 데이터 스트리밍이고, 상기 전송 유닛들은 전송 패킷들인, 타이밍 임계 데이터 전송 방법.

### 청구항 3

제2항에 있어서, 상기 채널은 디지털 VCR인, 타이밍 임계 데이터 전송 방법.

### 청구항 4

제2항에 있어서, 상기 채널은 비동기인, 타이밍 임계 데이터 전송 방법.

### 청구항 5

제1항에 있어서, 한 개의 전송 유닛에 대한 타이밍 정보는 연관된 타이밍 정보 및 상기 전송 유닛의 바이트 위치에 대한 오직 한 개의 지시자를 포함하는, 타이밍 임계 데이터 전송 방법.

### 청구항 6

제1항에 있어서, 복수의 전송 유닛들에 대한 타이밍 정보는 상기 복수의 전송 유닛들 중 일부의 전송 유닛들의 바이트 위치들에 대한 두 개의 지시자들과, 연관된 타이밍 정보와 함께 상기 복수의 전송 유닛들 중 나머지 전송 유닛의 바이트 위치에 대한 한 개의 지시자를 포함하는, 타이밍 임계 데이터 전송 방법.

### 청구항 7

제6항에 있어서, 상기 복수의 전송 유닛들에 대한 타이밍 정보는 상기 복수의 전송 유닛들과 연관된 데이터 유닛 내에 저장되는, 타이밍 임계 데이터 전송 방법.

### 청구항 8

제6항에 있어서, 상기 두 개의 지시자들은 상기 한 개의 전송 유닛의 각기 개시 및 종료 시간들을 지시하는, 타이밍 임계 데이터 전송 방법.

### 청구항 9

제8항에 있어서, 상기 한 개의 지시자는 상기 전송 유닛 내의 바이트 위치가 되는, 타이밍 임계

데이터 전송 방법.

#### 청구항 10

제9항에 있어서, 상기 한 개의 지시자와 연관된 데이터는 상기 전송 유닛들 중 일부의 전송 유닛의 시간 순간이 되는, 타이밍 임계 데이터 전송 방법.

#### 청구항 11

제10항에 있어서, 상기 복수의 전송 유닛들은 MPEG 정보 신호의 전송 패킷들인, 타이밍 임계 데이터 전송 방법.

#### 청구항 12

제11항에 있어서, 상기 한 개의 지시자는 PCR을 지시하는, 타이밍 임계 데이터 전송 방법.

#### 청구항 13

제11항에 있어서, 상기 복수의 전송 유닛들은 5개인, 타이밍 임계 데이터 전송 방법.

#### 청구항 14

제1항에 있어서, 상기 타이밍 임계 데이터는 블록 헤더와, 상기 타이밍 정보와 함께 복수의 전송 유닛들을 포함하는 블록 페이로드와, 예러 검사 블록을 순서대로 포함하는 데이터 블록으로서 포맷되는, 타이밍 임계 데이터 전송 방법.

#### 청구항 15

제14항에 있어서, 상기 블록 페이로드는 복수의 전송 패킷들과, 상기 복수의 전송 패킷들에 대한 타이밍 정보를 포함하는 한 개의 태크 패킷을 포함하는, 타이밍 임계 데이터 전송 방법.

#### 청구항 16

비동기 채널을 통해 타이밍 임계 데이터를 전송하는 장치로서, (i) 임계적으로 시간 조정된 연속적인 전송 유닛들의 스트림으로 재분할된 상기 타이밍 임계 데이터를 제공하는 수단을 포함하는 상기 타이밍 임계 데이터 전송 장치에 있어서,

(ii) 상기 타이밍 임계 데이터로부터 상기 전송 유닛들에 대한 타이밍 정보의 적어도 한 개의 항목을 포함하는 스트림 재작성 정보를 판정하는 수단으로서, 상기 재작성 정보로부터 상기 타이밍 임계 데이터가 재작성될 수 있는, 상기 스트림 재작성 정보 판정 수단과,

(iii) 상기 전송 유닛들 중 적어도 일부의 전송 유닛들에 타이밍 정보의 상기 적어도 한 개의 항목을 태그하는 수단과,

(iv) 상기 비동기 채널 상으로 타이밍 정보의 상기 태그된 항목과 함께 상기 전송 유닛들을 전송하는 수단을 더 포함하는 것을 특징으로 하는 타이밍 임계 데이터 전송 장치.

#### 청구항 17

비동기 채널로부터 타이밍 임계 데이터를 수신하는 방법에 있어서,

(i) 상기 채널로부터, 태그된 스트림 재작성 정보와 함께 제공된 전송 유닛들을 수신하는 단계로서, 상기 스트림 재작성 정보는 타이밍 정보의 항목을 포함하는, 상기 전송 유닛 수신 단계와,

(ii) 전송 유닛들로부터 타이밍 정보의 태그된 항목들을 검색하는 단계와,

(iii) 타이밍 정보의 상기 항목들에 응답하여 상기 타이밍 임계 데이터를 재작성하는 단계를 포함하는 것을 특징으로 하는 타이밍 임계 데이터 수신 방법.

#### 청구항 18

비동기 채널로부터 타이밍 임계 데이터를 수신하는 장치에 있어서,

(i) 태그된 스트림 재작성 정보와 함께 제공된 전송 유닛들을 수신하는 수신수단으로서, 상기 스트림 재작성 정보는 상기 채널로부터의 타이밍 정보의 항목을 포함하는, 상기 전송 유닛 수신 수단과,

(ii) 전송 유닛들로부터의 타이밍 정보의 태그된 항목들을 검색하는 검색 수단과,

(iii) 타이밍 정보의 상기 항목들에 응답하여 상기 타이밍 임계 데이터를 재작성하는 수단을 포함하는 타이밍 임계 데이터 수신 장치.

#### 청구항 19

기록 캐리어 상에 기록된 타이밍 임계 데이터를 가진 상기 기록 캐리어로서, 상기 타이밍 임계 데이터는 임계적으로 시간 조정된 연속적인 전송 유닛들의 스트림으로 재분할되고, 상기 전송 유닛들 중 적어도 일부의 전송 유닛들에는 상기 전송 유닛들에 대한 타이밍 정보의 적어도 한 개의 항목을 포함하는 스트림 재작성 정보가 태그되며, 상기 타이밍 임계 데이터는 상기 기록 캐리어로부터의 재생시 상기 스트림 재작성 정보로부터 재작성될 수 있는, 기록 캐리어.

#### 요약

전송되는 임의의 데이터를 변화시키지 않고 비동기 채널을 통해 타이밍 임계 데이터를 전송시키

는 방법이다. 그 타이밍 임계 데이터는 MPEG 전송 스트림이 될 수 있다. 상기 비동기 채널은, 컴퓨터 또는 전화기 네트워크, 디지털 VCR과 같은 디지털 기억 매디아 또는, 디지털 인터페이스가 될 수 있다. 상기 방법은 채널에 입력되기 이전에, 데이터 스트림의 각각의 전송 유닛을 타이밍 정보와 태그하는 단계와, 적당한 데이터 타이밍을 재작성하기 위하여 채널의 출력 단부에서 타이밍 정보를 사용하는 단계를 포함한다. 여러 설계안을 다수의 전송 유닛 또는 각각의 전송 유닛과 태그하는 타이밍 정보를 패킹하는 것에 대해 기술되어 있다.

### 도면

#### 도면1

#### 도면2

도면3

도면4

도면5

도면6

도면7

도면8

|           |           |           |           |       |           |           |           |           |

|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|

| $p_{k-4}$ | $p_{k-3}$ | $p_{k-2}$ | $p_{k-1}$ | $p_k$ | $p_{k+1}$ | $p_{k+2}$ | $p_{k+3}$ | $p_{k+4}$ |

|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|

8a

|           |           |       |           |           |           |

|-----------|-----------|-------|-----------|-----------|-----------|

| $p_{k-4}$ | $p_{k-1}$ | $p_k$ | $p_{k+2}$ | $p_{k+4}$ | $p_{k+8}$ |

|-----------|-----------|-------|-----------|-----------|-----------|

8b

|           |           |           |           |       |           |           |           |           |

|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|

| $p_{k-4}$ | $\square$ | $\square$ | $p_{k-1}$ | $p_k$ | $\square$ | $p_{k+2}$ | $\square$ | $p_{k+4}$ |

|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|

8c

도면9

도면10

도면11

도면12

도면13

| $p_{k-4}$ | $p_{k-3}$ | $p_{k-2}$ | $p_{k-1}$ | $p_k$ | $p_{k+1}$ | $p_{k+2}$ | $p_{k+3}$ | $p_{k+4}$ |

|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|

| $t_{k-4}$ | $t_{k-3}$ | $t_{k-2}$ | $t_{k-1}$ | $t_k$ | $t_{k+1}$ | $t_{k+2}$ | $t_{k+3}$ | $t_{k+4}$ |

13a

| $p_{k-4}$ | $p_{k-3}$ | $p_{k-2}$ | $p_{k-1}$ | $p_k$ | $p_{k+1}$ | $p_{k+2}$ | $p_{k+3}$ | $p_{k+4}$ | $p_{k+8}$ |

|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|-----------|

|           |           |           |           |       |           |           |           |           |           |

13b

13c

## 도면 14

도면 15

도면 16

도면17

도면18

도면19

도면20

도면21

도면22

도면23