(12) 发明专利

(10) 授权公告号 CN 109416552 B

(45) 授权公告日 2020.11.27

(21) 申请号 201780000309.2

(72) 发明人 李经珊 陈科 詹昶

(22) 申请日 2017.04.13

(74) 专利代理机构 上海晨皓知识产权代理事务所(普通合伙) 31260

(65) 同一申请的已公布的文献号

代理人 成丽杰

申请公布号 CN 109416552 A

(51) Int.CI.

G05F 1/56 (2006.01)

(43) 申请公布日 2019.03.01

(56) 对比文件

CN 106537276 A, 2017.03.22

(85) PCT国际申请进入国家阶段日

CN 2750356 Y, 2006.01.04

2017.05.09

CN 102830742 A, 2012.12.19

(86) PCT国际申请的申请数据

JP 2012185595 A, 2012.09.27

PCT/CN2017/080422 2017.04.13

审查员 杨欢欢

(87) PCT国际申请的公布数据

W02018/188018 ZH 2018.10.18

(73) 专利权人 深圳市汇顶科技股份有限公司

权利要求书1页 说明书5页 附图3页

地址 518045 广东省深圳市福田保税区腾飞工业大厦B座13层

(54) 发明名称

低压差线性稳压器

(57) 摘要

一种低压差线性稳压器，包括：运算放大器(A1)、源极跟随器(M2)、功率调整管(M4)、共栅放大器(M3)、上拉管(M5)以及尾电流源(M1)；源极跟随器(M2)的源极连接于功率调整管(M4)的漏极与运算放大器(A1)的反相输入端，源极跟随器(M2)的漏极与运算放大器(A1)的输出端，源极跟随器(M2)的栅极连接于运算放大器(A1)的输出端；共栅放大器(M3)的漏极连接于上拉管(M5)的漏极与功率调整管(M4)的栅极，共栅放大器(M3)的源极通过尾电流源(M1)接地；功率调整管(M4)的源极与上拉管(M5)的源极均连接至电压源；其中，运算放大器(A1)的正相输入端用于输入参考电压，源极跟随器(M2)的源极用于输出稳压电压。采用所述低压差线性稳压器，能得到得到高精度的输出电压，且输出电压具有较高的自由度。

1. 一种低压差线性稳压器,包括:运算放大器、源极跟随器、功率调整管、共栅放大器、上拉管以及尾电流源;

所述源极跟随器的源极连接于所述功率调整管的漏极与所述运算放大器的反相输入端,所述源极跟随器的漏极通过所述尾电流源接地,所述源极跟随器的栅极连接于所述运算放大器的输出端;

所述共栅放大器的漏极连接于所述上拉管的漏极与所述功率调整管的栅极,所述共栅放大器的源极通过所述尾电流源接地;

所述功率调整管的源极与所述上拉管的源极均连接至电压源;

其中,所述运算放大器的正相输入端用于输入参考电压,所述源极跟随器的源极用于输出稳压电压;

所述低压差线性稳压器还包括第一共源共栅放大器与第二共源共栅放大器;

所述第一共源共栅放大器连接于所述源极跟随器的漏极与所述尾电流源之间,所述第二共源共栅放大器连接于所述共栅放大器的漏极与所述上拉管的漏极之间。

2. 如权利要求1所述的低压差线性稳压器,其中,所述低压差线性稳压器还包括外接电容;

所述外接电容的一端连接于所述源极跟随器的源极,另一端接地;

所述外接电容的电容值的范围为0到1uF。

3. 如权利要求1所述的低压差线性稳压器,其中,所述第一共源共栅放大器为NMOS管,所述第二共源共栅放大器为PMOS管。

4. 如权利要求1所述的低压差线性稳压器,其中,所述尾电流源为NMOS管。

5. 如权利要求1至4中任一项所述的低压差线性稳压器,其中,所述源极跟随器、功率调整管及所述上拉管均为PMOS管,所述共栅放大器为NMOS管。

## 低压差线性稳压器

### 技术领域

[0001] 本申请涉及电路设计技术领域,特别涉及一种低压差线性稳压器。

### 背景技术

[0002] 低压差线性稳压器 (low dropout regulator, 缩写为LDO) 可以提供与电源及环境温度无关的输出电压, 具有一定的负载能力, 已经广泛地应用于各种功率芯片中。相对于传统的线性稳压器, LDO允许输入端和输出端之间的电压差较小; 例如, LDO的输入端电压可以仅比输出端电压高1.7V, 或者更小。

[0003] 发明人发现现有技术中至少存在以下问题: 现有的一种常规低功耗电压跟随翻转 (flipped voltage follower, 缩写为FVF) 结构LDO电路, 其输出电压受工艺和温度影响较大, 且LDO电路输出端的负载电容在较大范围内变化时, 会降低LDO电路的环路稳定性。另外, 若采用一种常规低功耗LDO电路, 虽然能够解决负载电容变化较大时带来的稳定性问题, 但是LDO电路无法输出与电源电压比较接近的电压, LDO电路的输出电压受到限制。

### 发明内容

[0004] 本发明部分实施例的目的在于提供一种低压差线性稳压器, 可以通过调整参考电压获得不同的高精度的输出电压, 同时输出电压具有较高的自由度; 减小了低压差线性稳压器的输出阻抗, 使得输出节点对应的极点处于较高的频率。

[0005] 本发明的一个实施例提供了一种低压差线性稳压器, 包括: 运算放大器、源极跟随器、功率调整管、共栅放大器、上拉管以及尾电流源; 源极跟随器的源极连接于功率调整管的漏极与运算放大器的反相输入端, 源极跟随器的漏极通过尾电流源接地, 源极跟随器的栅极连接于运算放大器的输出端; 共栅放大器的漏极连接于上拉管的漏极与功率调整管的栅极, 共栅放大器的源极通过尾电流源接地; 功率调整管的源极与上拉管的源极均连接至电压源; 其中, 运算放大器的正相输入端用于输入参考电压, 源极跟随器的源极用于输出稳压电压。

[0006] 本申请相对于现有技术而言, 运算放大器和源极跟随器构成单位增益负反馈电路, 低压差线性稳压器的输出电压等于参考电压, 不受源极跟随器的阈值电压影响, 不仅提高了输出电压的精度, 而且, 由于能够通过调整参考电压获得不同的输出电压 (即输出电压不受限), 使得输出电压具有较高的自由度; 同时, 引入运算放大器后, 低压差线性稳压器的输出阻抗进一步减小了, 使得输出节点对应的极点处于较高的频率, 能够避免外接负载电容在较大范围内变化时对环路稳定性造成影响。

[0007] 另外, 低压差线性稳压器还包括外接电容; 外接电容的一端连接于源极跟随器的源极, 另一端接地; 外接电容的电容值范围为0到1uF。本实施例中, 于低压差线性稳压器中设置外接电容, 以提高瞬态响应性能, 满足负载的大电流要求, 同时不影响低压差线性稳压器的稳定性。

[0008] 另外, 低压差线性稳压器还包括第一共源共栅放大器与第二共源共栅放大器; 第

一共源共栅放大器连接于源极跟随器的漏极与尾电流源之间,第二共源共栅放大器连接于共栅放大器的漏极与上拉管的漏极之间。本实施例能够提高环路增益,以提高低压差线性稳压器线性调整和负载调整性能。

[0009] 另外,第一共源共栅放大器为NMOS管,第二共源共栅放大器为PMOS管。本实施例提供了第一共源共栅放大器与第二共源共栅放大器的具体实现方式。

[0010] 另外,尾电流源为NMOS管。本实施例提供了尾电流源的具体实现方式。

[0011] 另外,源极跟随器、功率调整管及上拉管均为PMOS管,共栅放大器为NMOS管。本实施例提供了源极跟随器、功率调整管、上拉管以及共栅放大器的具体实现方式,可以提高环路环路增益,从而提高低压差线性稳压器线性调整和负载调整性能。

## 附图说明

[0012] 一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,附图中具有相同参考数字标号的元件表示为类似的元件,除非有特别申明,附图中的图不构成比例限制。

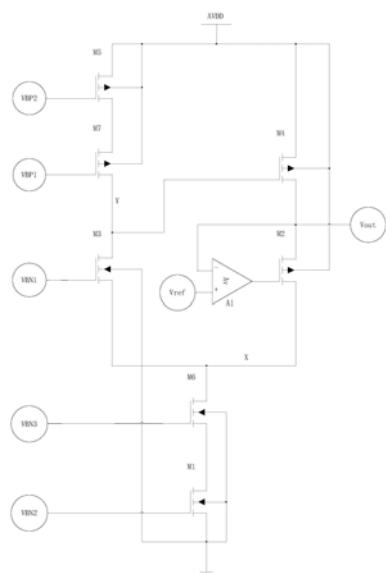

[0013] 图1是根据本申请第一实施例的低压差线性稳压器的电路图;

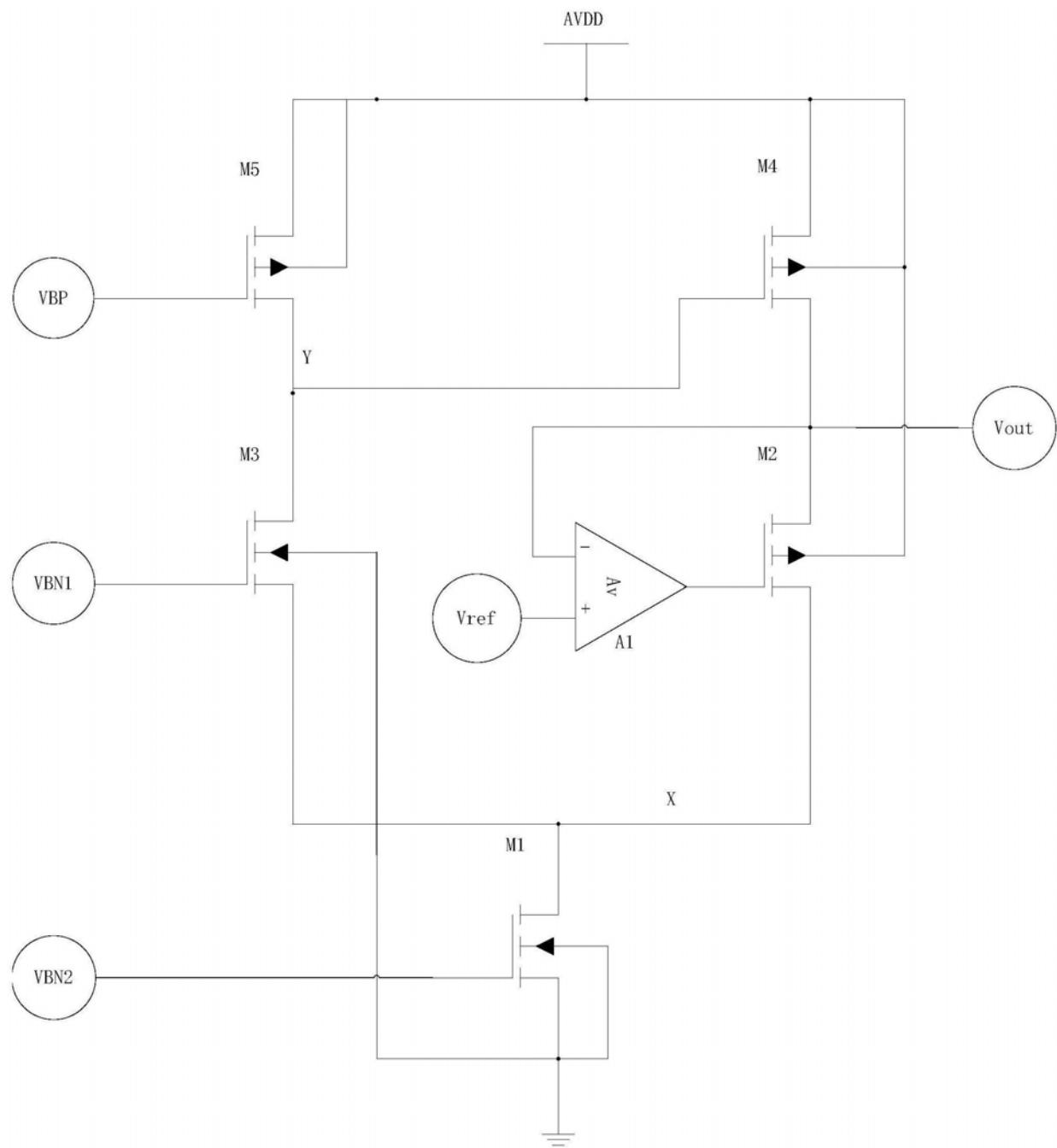

[0014] 图2是根据本申请第二实施例的低压差线性稳压器的电路图;

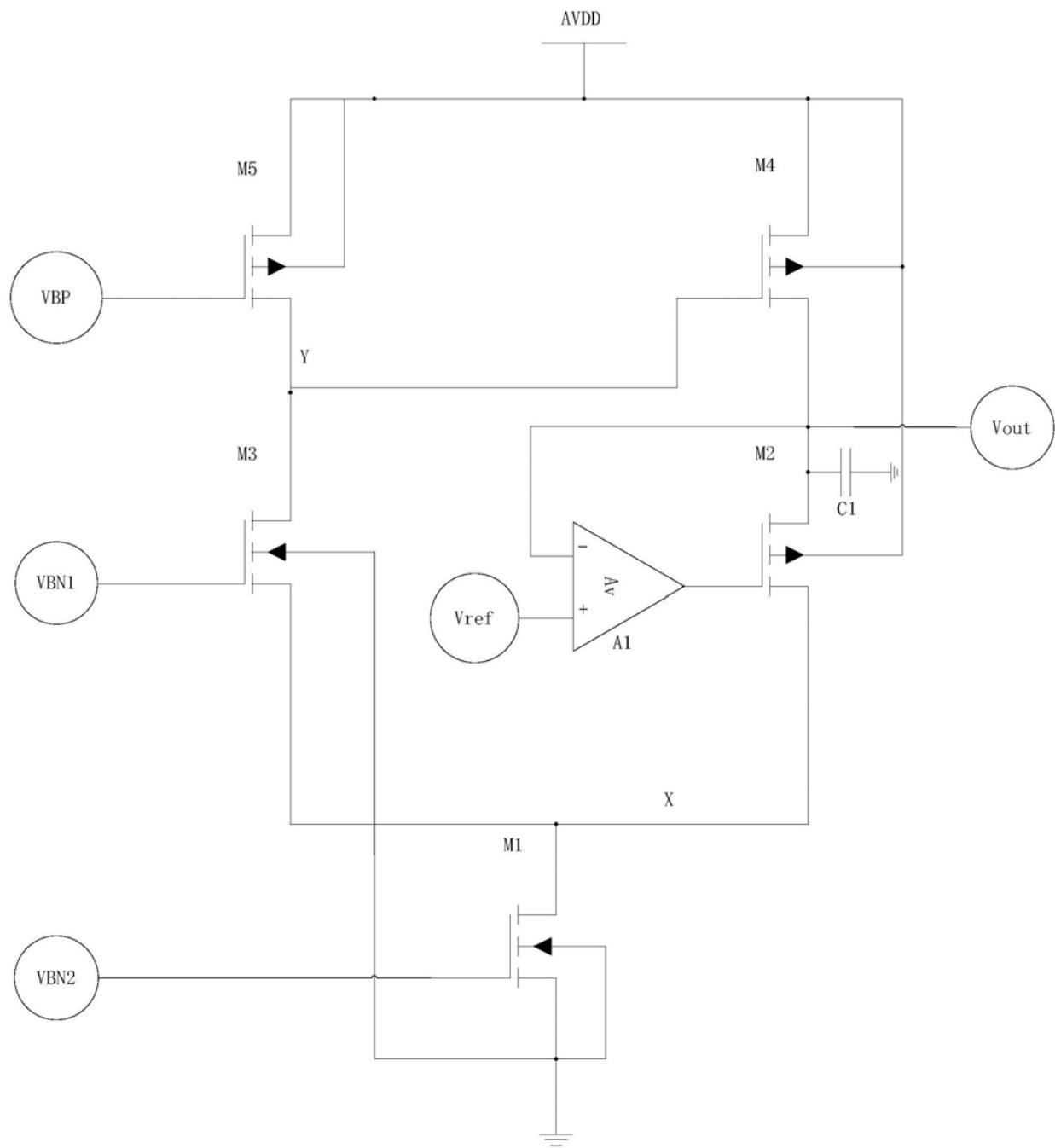

[0015] 图3是根据本申请第三实施例的低压差线性稳压器的电路图。

## 具体实施方式

[0016] 为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明部分实施例进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0017] 本申请第一实施例涉及一种低压差线性稳压器,应用于提供与电源及环境温度无关的输出电压,具有一定的负载能力,可以外接电容。本实施例中,请参考图1,低压差线性稳压器包括运算放大器A1、源极跟随器M2、功率调整管M4、共栅放大器M3、上拉管M5以及尾电流源M1;其中,VBP为上拉管M5的偏置电压,VBN1为共栅放大器M3的偏置电压,VBN2为尾电流源M1的偏置电压;其中,偏置电压VBP、VBN1以及VBN2分别使得上拉管M5、共栅放大器M3以及尾电流源M1工作在饱和区。

[0018] 本实施例中,源极跟随器M2的源极连接于功率调整管M4的漏极与运算放大器A1的反相输入端,源极跟随器M2的漏极通过尾电流源接地,源极跟随器M2的栅极连接于运算放大器A1的输出端;共栅放大器M3的漏极连接于上拉管M5的漏极与功率调整管M4的栅极,共栅放大器M3的源极通过尾电流源M1接地;功率调整管M4的源极与上拉管M5的源极均连接至电压源。

[0019] 其中,运算放大器A1的正相输入端用于输入参考电压,源极跟随器M2的源极用于输出稳压电压。

[0020] 本实施例中,尾电流源M1可以为NMOS管,然不限于此,也可以为半导体三极管。

[0021] 本实施例中,源极跟随器M2、功率调整管M4及上拉管M5均为PMOS管,共栅放大器M3为NMOS管。

[0022] 本实施例中,源极跟随器M2、共栅放大器M3和功率调整管M4构成负反馈环路,运算

放大器A1与源极跟随器M2构成单位增益负反馈环路;上拉管M5是为了保证共栅放大器M3具有一定的增益。

[0023] 本实施例的低压差线性稳压器的工作原理如下:

[0024] LDO电路的输出电压表达式:  $V_{out} = V_{ref}$  (1)

[0025] 其中,  $V_{out}$  为输出电压,  $V_{ref}$  为参考电压。

[0026] 由上式(1)可知, 输出电压  $V_{out}$  只与参考电压  $V_{ref}$  有关, 只要  $V_{ref}$  具有零温度系数, 则  $V_{out}$  同样也是零温度系数。

[0027] 断开源极跟随器M2、共栅放大器M3和功率调整管M4构成的负反馈环路, LDO电路的零极点分布情况如下:

[0028] LDO电路输出端所对应的极点为:  $P_{out} \approx \frac{1}{r_{out}C_L} \approx \frac{A_v g_{M2}}{C_L}$  (2)

[0029] 其中,  $r_{out} \approx \frac{1}{A_v g_{M2}}$ ,  $r_{out}$  为LDO电路的输出阻抗,  $A_v$  为运算放大器A1的电压增益,  $g_{M2}$  为源极跟随器M2的跨导,  $C_L$  为负载电容。

[0030] X节点所对应的极点为:  $P_X \approx \frac{1}{r_X C_X} \approx \frac{g_{M3}}{C_X}$  (3)

[0031] 其中,  $r_X \approx \frac{1}{g_{M3}}$ ,  $C_X$  为X节点的寄生电容,  $g_{M3}$  为共栅放大器M3的跨导。

[0032] Y节点所对应的极点为:  $P_Y \approx \frac{1}{r_Y C_Y} \approx \frac{1}{r_{o5} C_Y}$  (4)

[0033] 其中,  $r_Y \approx r_{o5}$ ,  $r_{o5}$  为上拉管M5的输出阻抗,  $C_Y$  主要由功率调整管M4的栅端寄生电容构成。

[0034] 运算放大器A1输出节点对应的极点频率为:  $P_1 \approx \frac{1}{r_{oA1} C_{A1}}$  (5)

[0035] 其中,  $r_{oA1}$  为运算放大器A1的输出阻抗,  $C_{A1}$  为运算放大器输出节点处的寄生电容。

[0036] 由上式(2)至(5)可知, 主极点为  $P_Y$ , 次主极点为  $P_1$ , 而非主极点  $P_X$  和  $P_{out}$  离  $P_Y$  和  $P_X$  较远, 由于LDO电路的输出阻抗减小了很多,  $P_{out}$  也会处于较高频率处, 因此, LDO电路能够保证很好的稳定性。

[0037] 现有的FVF结构LDO电路中, 不包括运算放大器A1, 使得LDO电路的输出电压变为:

[0038]  $V_{out} = V_{ref} + V_{th}$

[0039] 其中,  $V_{out}$  为输出电压,  $V_{ref}$  为参考电压,  $V_{th}$  为M2管的阈值电压。

[0040] 此时, LDO电路输出电压  $V_{out}$  不仅跟参考电压  $V_{ref}$  有关, 还与M2管的阈值电压  $V_{th}$  有关, 由于  $V_{th}$  受工艺的影响较大, 且具有一定的温度系数, 所以LDO电路输出电压  $V_{out}$  受工艺和温度的影响也比较大。若要实现  $V_{ref}$  和  $V_{th}$  温度补偿,  $V_{ref}$  必须具有正温度系数, 此时LDO电路输出电压  $V_{out}$  只能实现在某个电压值具有零温度系数, 因此LDO电路的输出电压受到限制。

[0041] 另外, 由于没有运算放大器A1, 主极点仍为  $P_Y$ , 当LDO电路输出负载电容在较大范围内变化, 次主极点会在  $P_X$  和  $P_{out}$  之间变化, 或者两者位置相近, 从而降低了LDO电路的环路稳定性。

[0042] 本实施例相对于现有技术而言,运算放大器和源极跟随器构成单位增益负反馈电路,低压差线性稳压器的输出电压等于参考电压,不受源极跟随器的阈值电压影响,不仅提高了输出电压的精度,而且,由于能够通过调整参考电压获得不同的输出电压(即输出电压不受限),使得输出电压具有较高的自由度;同时,引入运算放大器后,低压差线性稳压器的输出阻抗进一步减小了,使得输出节点对应的极点处于较高的频率,能够避免外接负载电容在较大范围内变化时对环路稳定性造成影响。

[0043] 本申请第二实施例涉及一种低压差线性稳压器,本实施例是在第一实施例基础上的改进,主要改进之处在于:本实施例中,请参考图2,低压差线性稳压器还包括外接电容C1。

[0044] 外接电容C1的一端连接于源极跟随器M2的源极,另一端接地。

[0045] 本实施例中,为了提高LDO电路的瞬态响应性能,外接电容C1一般为大电容,即外接电容C1的电容值的范围为0到1uF;由于LDO电路的输出阻抗减小了很多,LDO电路输出端所对应的极点p<sub>out</sub>也处于较高频率,此时不会对LDO电路的环路稳定性造成影响;因此,LDO电路外接电容C1为大电容时,同样可以保证LDO电路具有很好的稳定性。

[0046] 本实施例相对于第一实施例而言,于低压差线性稳压器中设置外接电容,以提高瞬态响应性能,满足负载的大电流要求,同时不影响低压差线性稳压器的稳定性。

[0047] 本申请第三实施例涉及一种低压差线性稳压器,本实施例是在第一实施例基础上的改进,主要改进之处在于:本实施例中,请参考图3,低压差线性稳压器还包括第一共源共栅放大器M6与第二共源共栅放大器M7;其中,VBN3为第一共源共栅放大器M6的偏置电压,VBP1为第二共源共栅放大器M7的偏置电压,VBP2为上拉管M5的偏置电压;其中,偏置电压VBN3、VBP1以及VBP2分别使得第一共源共栅放大器M6、第二共源共栅放大器M7以及上拉管M5工作在饱和区。

[0048] 本实施例中,第一共源共栅放大器M5连接于源极跟随器M2的漏极与尾电流源M1之间,第二共源共栅放大器M6连接于共栅放大器M3的漏极与上拉管M5的漏极之间。

[0049] 其中,第一共源共栅放大器M6为NMOS管,所述第二共源共栅放大器M7为PMOS管。

[0050] 本实施例的低压差线性稳压器的工作原理与第一实施例大致相同,主要不同之处在于:

[0051] 在第一实施例中,源极跟随器M2、共栅放大器M3和功率调整管M4构成的负反馈环路增益为:  $Loop\ Gain \approx g_{M4}r_{out}g_{M2}r_Xg_{M3}r_Y \approx \frac{g_{M4}r_{05}}{A_V} \quad (6)$

[0052] 其中,  $g_{M4}$  为功率调整管M4的跨导,由上式(6)可知,LDO电路的环路增益较小。

[0053] 本实施例中,源极跟随器M2、共栅放大器M3和功率调整管M4构成的负反馈环路增益为:  $Loop\ Gain \approx g_{M4}r_{out}g_{M2}r_Xg_{M3}r_Y \approx \frac{g_{M4}g_{M3}g_{M2}r_o^3}{A_V} \quad (7)$

[0054] 其中,  $r_X = r_o$ ,  $r_Y = (g_{M2}r_o)^2$ , 可以假设  $r_{05} = r_{07} = r_o$ ; 由于  $r_X$  和  $r_Y$  都增大为原来的  $g_{M2}r_o$  倍, 根据式(6)和(7)可知, 本实施例中环路增益便增大为第一实施例中环路增益的  $(g_{M2}r_o)$  2 倍。

[0055] 本实施例相对于第一实施例而言,能够提高环路增益,以提高低压差线性稳压器线性调整和负载调整性能。需要说明的是,本实施例也可以作为在第二实施例基础上的改

进,能够达到同样的技术效果。

[0056] 本领域的普通技术人员可以理解,上述各实施例是实现本发明的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本发明的精神和范围。

图1

图2

图3