(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-524431

(P2006-524431A)

(43) 公表日 平成18年10月26日(2006.10.26)

| (51) Int.CI.                  | F 1        |      | テーマコード (参考) |

|-------------------------------|------------|------|-------------|

| <b>H01L 27/092 (2006.01)</b>  | H01L 27/08 | 321D | 4M1O4       |

| <b>H01L 21/8238 (2006.01)</b> | H01L 21/28 | A    | 5FO48       |

| <b>H01L 21/28 (2006.01)</b>   | H01L 21/28 | E    |             |

審査請求 未請求 予備審査請求 未請求 (全 14 頁)

|               |                              |          |                                                                                                                                                          |

|---------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2006-508066 (P2006-508066) | (71) 出願人 | 304038747<br>ナショナル ユニバーシティー オブ シンガポール<br>NATIONAL UNIVERSITY OF SINGAPORE<br>シンガポール 119260、ケント・リッジ・クレッセント 10<br>10 Kent Ridge Crescent, Singapore 119260 |

| (86) (22) 出願日 | 平成16年4月19日 (2004.4.19)       |          |                                                                                                                                                          |

| (85) 翻訳文提出日   | 平成17年12月20日 (2005.12.20)     |          |                                                                                                                                                          |

| (86) 國際出願番号   | PCT/SG2004/000100            |          |                                                                                                                                                          |

| (87) 國際公開番号   | W02004/095572                |          |                                                                                                                                                          |

| (87) 國際公開日    | 平成16年11月4日 (2004.11.4)       |          |                                                                                                                                                          |

| (31) 優先権主張番号  | 60/464,936                   |          |                                                                                                                                                          |

| (32) 優先日      | 平成15年4月22日 (2003.4.22)       |          |                                                                                                                                                          |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                                                          |

最終頁に続く

(54) 【発明の名称】デュアルメタルゲート電極を有するCMOSデバイスの製造方法

## (57) 【要約】

金属エッチング工程においてゲート誘電体(26)が露出することを防止するために、処理の間、メタルゲート(30)とゲート誘電体(26)との間の超薄窒化アルミニウム( $\text{AlN}_x$ )バッファ層(28)を使用する、デュアルメタルゲートCMOS構造を構築する方法。不必要なゲートメタルをエッチング除去した後、CMOS構造は熱処理される。熱処理の間に、メタルゲート(30)との反応を通じてバッファ層(28)は完全に消費され、新らしいメタル合金(38, 40)が形成される。その結果、実効酸化膜厚は最小限しか増加しない。バッファ層(28)およびゲートメタル(30)は、元のゲートメタルの仕事関数が熱処理工程の結果変化するため、メタル/誘電体界面の仕事関数の決定に重要な役割を果たす。

**【特許請求の範囲】****【請求項 1】**

C M O S デバイスを製造する方法であって、

( a ) N M O S F E T を形成するための p ウェル領域と、 P M O S F E T を形成するための n ウェル領域とに区分され得る半導体基板上に、ゲート誘電体を形成する工程と、

( b ) ゲート誘電体上にバッファ層物質を形成する工程と、

( c ) バッファ層上に第 1 メタルを堆積する工程と、

( d ) 第 1 エッチャントにより第 1 メタルを選択的にエッチングし、前記 p ウェル領域および n ウェル領域のうち一方にバッファ層を露出させる工程と、

( e ) 露出したバッファ層と残った第 1 メタルの両方の上に第 2 メタルを堆積する工程と、

( f ) 選択された領域において前記第 1 メタル、前記第 2 メタル、および前記バッファ層を除去し、前記 C M O S デバイスの P M O S ゲート電極および N M O S ゲート電極を形成する工程と、

( g ) 前記第 1 メタル、前記第 2 メタル、および前記バッファ層が残った部分を熱処理し、前記第 1 メタルおよび前記第 2 メタルと反応させることにより前記バッファ層の前記部分を消費させて、それぞれ第 1 および第 2 の仕事関数を有する第 1 および第 2 の導電性合金を形成する工程と、

を含む方法。

**【請求項 2】**

前記バッファ層物質は、前記第 1 エッチャントから前記ゲート誘電体を保護するための前記第 1 エッチャントに対する耐性を有するように選択される請求項 1 に記載の方法。

**【請求項 3】**

前記窒素に対する前記アルミニウムの組成比が、前記メタル合金の所望の仕事関数が得られるように選択される請求項 2 に記載の方法。

**【請求項 4】**

前記バッファ層物質は、アルミニウムおよび窒素を含有する化合物である請求項 1 または 2 に記載の方法。

**【請求項 5】**

前記バッファ層は、 2 0 n m 未満のバッファ層厚を有する請求項 1 ~ 4 のいずれかに記載の方法。

**【請求項 6】**

前記第 1 エッチャントは、硫酸と過酸化水素との混合物を含有する湿式化学溶液である請求項 1 ~ 5 のいずれかに記載の方法。

**【請求項 7】**

前記第 1 エッチャントは、フッ化水素酸と過酸化水素との混合物を含有する湿式化学溶液である請求項 1 ~ 5 のいずれかに記載の方法。

**【請求項 8】**

前記熱処理は、 4 0 0 °C を超える温度で行われる請求項 1 ~ 7 のいずれかに記載の方法。

**【請求項 9】**

第 1 メタルおよび第 2 メタルは、チタン ( T i ) 、ハフニウム ( H f ) 、およびタンタル ( T a ) からなる群より選択される請求項 1 ~ 8 のいずれかに記載の方法。

**【請求項 10】**

前記第 1 メタルはハフニウムであり、前記第 2 メタルはタンタルである請求項 1 ~ 9 のいずれかに記載の方法。

**【請求項 11】**

前記バッファ層の形成は、物理気相蒸着 ( P V D ) 、化学気相蒸着 ( C V D ) 、および原子層蒸着 ( A L D ) からなる群より選択される工程を含む請求項 1 ~ 1 0 のいずれかに記載の方法。

10

20

30

40

50

**【請求項 1 2】**

第1メタルおよび第2メタルは、1.34eV未満の電気陰性度を有する請求項1～1のいずれかに記載の方法。

**【請求項 1 3】**

メタルゲート電極の仕事関数を決定する方法であつて、

(a) ゲート誘電体上にバッファ層物質を堆積し、

(b) 前記バッファ層物質の上に金属を堆積し、

(c) 前記バッファ層および前記金属を熱処理して、前記バッファ物質および前記金属を反応させて所望の仕事関数を有する合金を形成することを含む工程により、所望のメタルゲート電極の仕事関数を決定することを含む方法。

10

**【請求項 1 4】**

前記バッファ層物質は、アルミニウムおよび窒素を含有する請求項13に記載の方法。

**【請求項 1 5】**

前記窒素および前記アルミニウムの組成比は、所望の前記仕事関数が得られるように選択される請求項14に記載の方法。

**【請求項 1 6】**

メタルゲートと、隣接するメタルゲート誘電体との間の接触部が、AlN<sub>x</sub>および電気陰性度が1.4未満の金属から形成された合金を含有する、CMOSに適用されるメタルゲート。

**【請求項 1 7】**

前記金属はHfであり、

前記合金は、NMOSに適切な約4.4eVの仕事関数を有する請求項16に記載のメタルゲート。

**【請求項 1 8】**

前記金属はTaであり、

前記合金は、PMOSに適切な約4.9eVの仕事関数を有する請求項16に記載のメタルゲート。

**【発明の詳細な説明】****【技術分野】****【0001】**

30

本発明は、概してCMOSデバイスの製造方法に関し、さらに詳しくは、メタルゲートとゲート誘電体との間の消費可能な薄いバッファ層を用いたデュアルメタルゲート電極を有するCMOSデバイスの製造方法に関する。

**【背景技術】****【0002】**

CMOSデバイスを構築する際に、ゲート電極としてドープ多結晶シリコンが一般的に使用されている。多結晶シリコンは、2つのCMOSゲートにおいて所望の仕事関数を得るためにドープできるので都合が良い。

**【0003】**

しかし、CMOSデバイスがより小さい寸法に縮小されるに従って問題が生じる。高抵抗率化、反転電荷密度および相互コンダクタンスの減少、およびドープ多結晶シリコングート電極における望ましくない空乏が生じ得るので、ゲート酸化膜の厚さにおいて有害な増加を生じる結果になる。また、多結晶シリコンからゲート酸化膜の内部へ拡散によってホウ素が侵入するという問題もある。

**【0004】**

実効ゲート酸化膜厚(EO T)が1.0nm未満に減少するに従って、多結晶シリコングート内における空乏層に接続される容量がEO T縮小の重要な制限要因になる。よって、メタルゲート、特にデュアルメタルゲートには50nmかそれよりも小さいゲート長が要求されるということが課題とされてきた。

**【0005】**

40

50

デュアルメタルゲートでは、N M O S メタルとP M O S メタルがデュアルゲートとして使用される。しかし、現在のデュアルメタルゲートには、工程の集積化において、特に、リソグラフィーによるマスキングをして、ウェハ部分に堆積したデュアルメタルゲートの第1メタルをゲート誘電体へエッチング損傷を生じさせずに除去する過程において、解決されていない問題がある。

#### 【0006】

デュアルメタルゲート電極を製造するための通常の方法では、ゲート誘電体の上部に第1メタルを堆積する。第1メタルはその後、リソグラフィーによるマスキングおよびウェル領域の一方からの選択エッチングにより除去される。このウェル領域は、nウェル領域またはpウェル領域のいずれであってもよい。その後、第2メタルが、露出した誘電体の上部と共に第1メタルの上部に堆積される。10

#### 【0007】

不都合なことに、エッチング用化学溶液は、ゲート誘電体部分も侵食して除去し得る。これは、適当な金属がうまく同定されたとしても、デュアルメタルゲート技術を製造に使用するに際して実際的な障害となる。

#### 【0008】

デュアルメタルゲート電極を製造するための別の方法は、イオン注入技術を伴う。この場合、ゲート誘電体の上部に金属が堆積され、ウェル領域の一方はフォトレジストで被覆される。その後、メタル電極の一方でイオン注入が適用され、当該メタルの仕事関数を変化させる。その結果、メタル電極において2つの異なる仕事関数が得られる。20

#### 【0009】

しかし、イオン注入はゲート誘電体を損傷し、結果としてゲート誘電体の性能を劣化させる。

#### 【発明の開示】

#### 【0010】

簡略に言うと、本発明の好ましい態様は、通常は20nm未満の厚さをもつ超薄窒化アルミニウム(A1N<sub>x</sub>)バッファ層を用いたデュアルメタルゲートCMOS構造を構築する方法を包含する。

#### 【0011】

この層は、メタルゲートのエッチング工程の間ゲート誘電体を保護するための過程において、メタルゲートとゲート誘電体との間にあたる。デュアルメタルゲートが形成された後、CMOS構造は熱処理温度におかれ。熱処理の間に、バッファ層はメタルゲートとの反応を通じて完全に消費され、最適な仕事関数をもつ新しい合金が形成される。熱処理工程は、実効膜厚に最小限の増加しか生じさせない。30

#### 【発明を実施するための最良の形態】

#### 【0012】

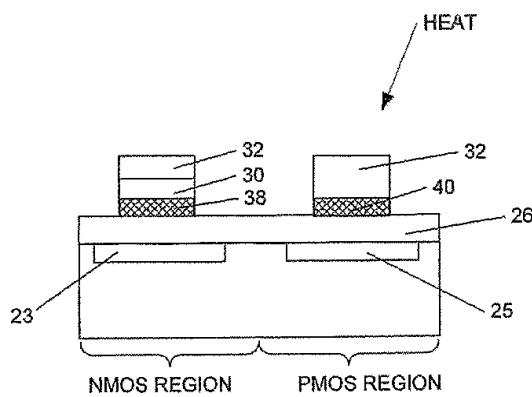

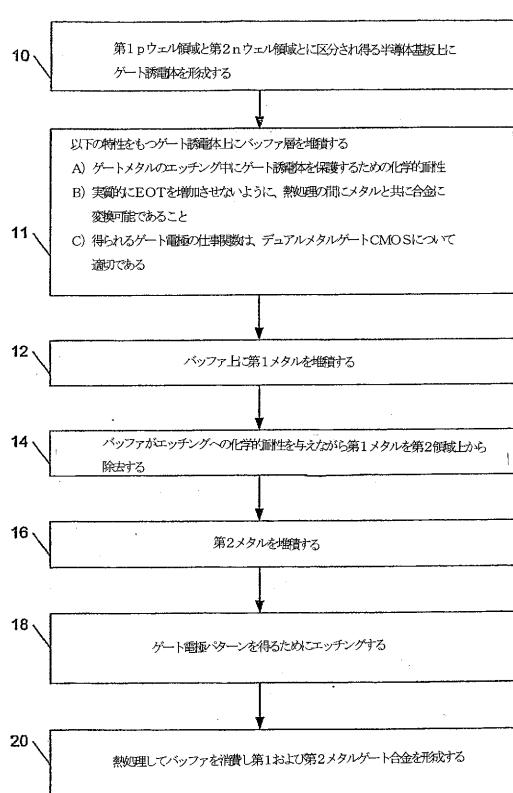

本発明の方法を図1のフローチャートに示す。この工程/方法では、CMOSデバイスのデュアルメタルゲート電極を製造する。この方法によれば、各メタルゲート電極に、その最適な仕事関数、すなわちN M O S では4.4V、P M O S では4.9Vを与えることができる。40

#### 【0013】

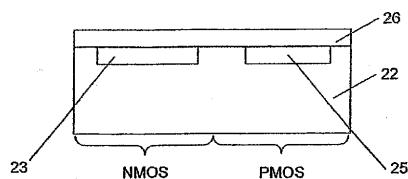

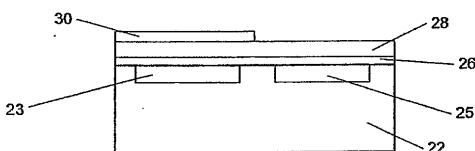

当該工程は、CMOS内へのN M O S F E T およびP M O S F E T デバイスの形成に用いられるpウェル領域およびnウェル領域を有する基板22上に、ゲート誘電体26を形成することから始まる(ブロック10)。ある好ましい態様では、ゲート誘電体は、熱酸化SiO<sub>2</sub>である。

#### 【0014】

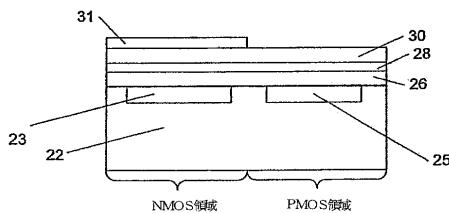

その後、CMOSのpおよびnウェル構造におけるゲート誘電体26上にバッファ層28を堆積する(ブロック11)。

バッファ層を堆積させる方法としては、物理気相蒸着(P V D)、化学気相蒸着(C V D)、原子層蒸着(A L D)、およびスパッタリングが挙げられる。

10

20

30

40

50

## 【0015】

バッファ層物質は、次の3つの基準に適合するように選択される。

(a) バッファ上に堆積されたゲートメタルのエッチング中に使用されるエッチャントへの露出から下にあるゲート誘電体を保護するために化学的耐性がなければならない。

(b) 热処理工程の間にゲートメタルとの反応によってデュアルメタル合金を形成して、消費されたバッファ層が最終的な実効酸化膜厚を増加しないようにするため、热処理の間に消費可能でなければならない。

(c) バッファ層物質は、热処理後に得られたデュアルメタルゲートの仕事関数が、デュアルメタルゲートCMOSについて最適となるように選択されなければならない。

## 【0016】

これらの基準は、全て図1のブロック11に含まれている。

好みのバッファ物質は、非化学量論的な窒化アルミニウム( $\text{AlN}_x$ )である。ここで、“x”は $0.98 \sim 1.02$ の範囲にある。好みのバッファ層の厚さは $1.5\text{ nm}$ 未満である。厚さが $1.5\text{ nm}$ よりも大きいと、热処理の間にゲートメタルと完全に合金化せず、よって好みしくない。

## 【0017】

ある1つの態様では、ゲートメタルは $100\text{ nm}$ の厚さをもち、ゲート誘電体は $3.5\text{ nm}$ の厚さをもち、 $\text{AlN}_x$ (ここで“x”は $1.0$ に近い)は約 $1.0\text{ nm}$ の初期厚さをもつ。要求される基準に適合する他の物質も本発明の精神に包含される。

## 【0018】

$\text{AlN}_x$ のような絶縁体が、 $\text{Hf}$ のような金属と合金化して、CMOSへの適用のための最適な仕事関数をもつメタル合金を形成することは、大いに異常であり、かつ予期し得ないことである。

## 【0019】

$\text{AlN}_x$ バッファは、化学エッチングに対して非常に高い化学的耐性を有する。さらに、 $1.34$ 未満の電気陰性度をもつ、 $\text{Ti}$ ( $1.32$ )、 $\text{Hf}$ ( $1.23$ )、および $\text{Ta}$ ( $1.33$ )のようなゲートメタルと反応して、これらの金属の仕事関数を高める合金を形成することができる。例えば、 $\text{Hf-AlN}_x$ 合金は、NMOSに最適な $4.4\text{ eV}$ の仕事関数をもち、 $\text{Ta-AlN}_x$ 合金は、PMOSに最適な $4.9\text{ eV}$ の仕事関数をもつ。

## 【0020】

図1に戻ると、バッファ層を堆積した後、バッファ層の上には、特に第1および第2ウェルを被覆する、第1メタルが堆積される(ブロック12)。第1メタルはその後、第2ウェル上から除去される(ブロック14)。好みの第1メタルは、 $\text{Hf}$ である。

## 【0021】

マスクされていないゲートメタルを除去する好みの方法は、先行技術において知られている、硫酸および過酸化水素、またはフッ化水素酸と過酸化水素と脱イオン水との混合物等の溶液中における、湿式化学エッチングである。

## 【0022】

その後、第1メタル上および露出したバッファ上に、第2メタルが堆積される(ブロック16)。好みの第2メタルは $\text{Ta}$ である。2つの異なるメタルが堆積された後、ゲート電極パターンを得るために、RIEのようなドライエッチ工程を用いたエッチングが行われる(ブロック18)。

## 【0023】

残った第1メタルおよび第2メタルと、その下にあるバッファ層とを含むこのCMOS構造には、その後熱処理が施される。热処理の温度と時間は、ゲートメタルと反応し、それによりバッファ物質およびゲート物質から構成されるメタル合金を形成することによってバッファ層の消費が起こるように選択される(ブロック20)。热処理温度は、 $400 \sim 700$ の範囲であり、好みの温度は $420$ である。

## 【0024】

10

20

30

40

50

本発明に係る方法の工程において、バッファ物質の選択と組み合わせてゲートメタルを選択することによって、メタルゲート電極の仕事関数を制御、すなわち決定できる。

得られるゲートメタルの仕事関数を決定するために、アルミニウムと窒素との特定の組成比を選択できる。すなわち、仕事関数は、熱処理温度および時間と同様に、窒素に対するアルミニウムの組成比に依存する。

#### 【0025】

熱処理は、炉内において400～500で30分間、または、RTAツール内において500～700で1時間行われる。

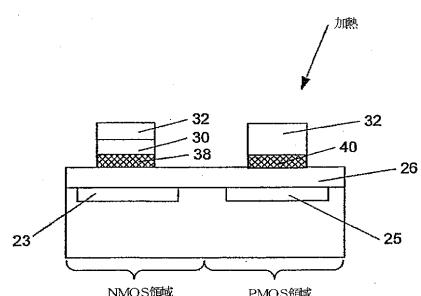

図2A～図2Gを参照しながら、本発明の工程／方法をさらに明確に説明する。図2Aは、従来技術における基板22（好ましくはSi）、ゲート誘電体26を図示し、NMOSpウェル23およびPMOSnウェル25を符号で示している。当業者であれば、図2Aおよびその変形の構築の仕方を理解するであろう。それらの全ては、図1を参照して記述され、以下に詳細に記述されたゲート構造および構築方法と組み合わせて、本発明に包含される。

#### 【0026】

本発明によれば、図2Bに示すように、バッファ層28がゲート誘電体26上に堆積される。バッファ層28は、ゲート誘電体／ゲート酸化物26が金属エッチング工程に曝されることを防止し、また、金属／誘電体界面における仕事関数を決定する。

#### 【0027】

熱処理の間に、バッファ層はゲートメタルとの反応によって完全に消費され、新しい合金が形成される。この工程は、ゲート誘電体領域における実効酸化膜厚の変化が最小限であるという更なる利点を有する。

#### 【0028】

バッファ層物質は、図1のブロック11を参照して論じた要求に適合するように選択される。本発明の好ましい態様は、バッファ物質としてAlNxを含む。ここで“x”は0.98～1.02の範囲内における約1.0である。

#### 【0029】

上記において論じたバッファ物質に対する要求の1つは、熱処理工程の間に、ゲートメタルと共にメタル合金へ変換されなければならないということである。AlNxは、熱処理工程において、Ti(1.32)、Hf(1.23)、およびTa(1.33)のような1.34未満の電気陰性度をもつ金属と反応した際に、メタル合金に変換され、仕事関数が変更された合金を形成することができる。これらの金属とAlNxとの合金は、金属そのものよりも実質的に高い仕事関数を有する。

#### 【0030】

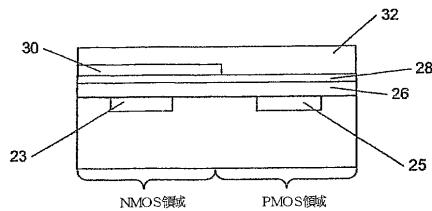

図2Bは、前記工程／方法における次の工程を示し、該工程では、第1ゲートメタル30がバッファ層28上に堆積される。当該例におけるメタル30はNMOSメタルである。第1ゲートメタルは、Ta(Hfではない)のようなPMOS金属であってもよい。第1メタル30がNMOSメタルであるとすると、NMOSメタルはその後、PMOSFET領域上から除去されなければならない。あるいは、第1メタルがPMOSメタルであるならば、それはNMOSFET領域から除去されなければならないであろう。

#### 【0031】

この例においては、図示したように、NMOSFET領域上の第1メタル30(NMOSメタル)上に、フォトトレジスト31が配置され、該メタルは、PMOSFET領域上からエッチング除去され、結果として図2Cに示す構造になる。

#### 【0032】

NMOSメタルをPMOSFET領域から除去すると共に、図2Dに示すようにPMOSメタルが堆積され、NMOSメタル30およびPMOSFET領域を被覆する。これを図2Dに平坦化して示す。

#### 【0033】

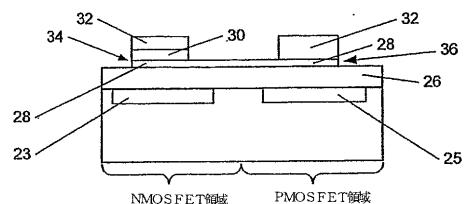

次の工程では、図2Eにおいてそれぞれ34, 36として符号で示したNMOSおよび

10

20

30

40

50

P M O S ゲート領域以外において、P M O S F E T およびN M O S F E T メタルの両方と、バッファ層とを除去する。当業者であれば、この除去を達成するための各種の方法を知っているであろう。

#### 【0034】

図示した方法では、図2Eに示すように2つのゲート領域上に単にレジスト38を配置し、残りの露出したメタルをエッチングする。第2メタルのエッチングは、第1メタルのエッチングとは異なっている。第1メタルは、選択的にエッチングされる一方、第2メタルのエッチングは、ゲート電極パターンを定義するのみである。

#### 【0035】

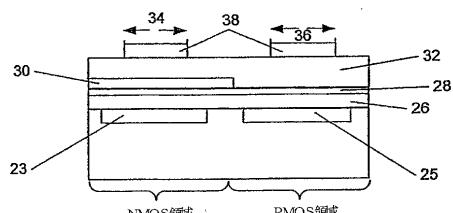

図2Fに示すように、エッチング後にバッファ層28は残存する。しかしながら、図2Gに示すように、バッファ層は熱処理工程において消費され、堆積したメタルと合金38,40を形成することに注目されたい。

10

#### 【0036】

本発明は、上述したような目的で新規なバッファ層28を使用する、図2Fに示すような構造を得るための他の方法も包含する。

次の工程では、バッファ層を、それぞれN M O S F E T およびP M O S F E T ゲートのためのメタル層30および32と合金化するために図2Fの構造を熱処理して、バッファ層を消費し、図2Gにおいて符号38および40で示したように、メタル合金を形成する。バッファ層28は、熱処理／合金化工程において効率的に消費される。

#### 【0037】

各種膜のエッチング速度を図3に表す。H P Mは、H F、H<sub>2</sub>O<sub>2</sub>およびH<sub>2</sub>Oの混合物であり、S P MはH<sub>2</sub>S O<sub>4</sub>およびH<sub>2</sub>O<sub>2</sub>の混合物である。図示したように、H P Mは、H fまたはS i O<sub>2</sub>に比べてA l N<sub>x</sub>に対して非常に遅いエッチング速度をもつ。S P Mは、S i O<sub>2</sub>に対するエッチング速度が0でありH fに対して非常に速いエッチング速度であることと比較すると、A l N<sub>x</sub>に対するエッチング速度が0である。

20

#### 【0038】

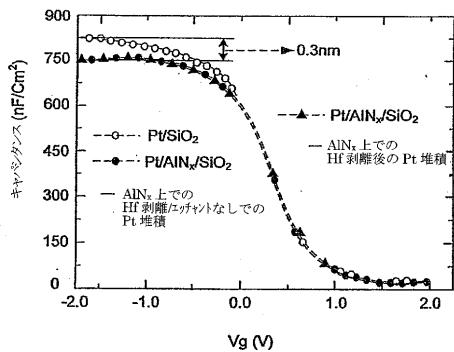

図4は、曲線“- - -”を含み、これは、S i O<sub>2</sub>ゲート誘電体上に直接堆積したP t ゲートメタルを有しバッファ層がないゲート構造のゲート電圧に対するゲート容量を表す。

。

#### 【0039】

曲線“- - -”は、420で熱処理した後の、S i O<sub>2</sub>ゲート誘電体上のバッファ層の上にP t ゲートメタルを有するゲート構造のゲート電圧に対するゲート容量を表す。曲線“- - -”の構造は、例えばH fメタルを除去するためのエッチャントには露出されておらず、それゆえ比較のための参照として挙げる。

30

#### 【0040】

上記曲線は、-2Vでの容量が、P t / S i O<sub>2</sub>で約820nF/cm<sup>2</sup>であり、P t / A l N<sub>x</sub> / S i O<sub>2</sub>(熱処理後)で約750nF/cm<sup>2</sup>であった。これは、A l N<sub>x</sub>とS i O<sub>2</sub>の誘電係数が等しいと仮定すると、実効酸化膜厚において0.3nmの差に相当する。

。

#### 【0041】

曲線“- - -”は、熱処理後のP t / A l N<sub>x</sub> / S i O<sub>2</sub>構造のゲート電圧に対するゲート容量を表す。しかし、その構築工程において、P t層の堆積に先立ってA l N<sub>x</sub>上へ湿式化学エッチングが施された。これは、第1メタル30の一部を除去するために使用される湿式エッチングへの耐性におけるA l N<sub>x</sub>層の効能を試験するためになされた。

40

#### 【0042】

上記曲線は、曲線“- - -”と曲線“- - -”との間で大きな差を示さず、これは、A l N<sub>x</sub>が湿式化学H f剥離工程に耐えるために、エッチングマスクとして有効であったことを示している。

#### 【0043】

さらなる試験／評価として、T a / A l N<sub>x</sub> / S i O<sub>2</sub> / S i ゲート層が形成され、熱処

50

理前および、420<sup>10</sup>での熱処理後の、結合したAlN<sub>x</sub>/SiO<sub>2</sub>層の厚さを示す高分解能透過電子顕微鏡(HRTEM)像を得た。熱処理前における厚さは4.24nmであり、熱処理後の厚さは3.50nmであった。熱処理前後における0.74nmの厚さの差は、TEM画像に示されるように、消費されたAlNを示した。これにより、AlNの消費が確認された。0.74nmの値は、1.5nm未満であることは注目されるべきである。

#### 【0044】

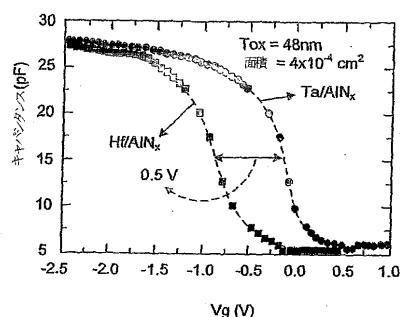

図5は、2つの構造についてのゲート電圧に対するゲート容量の曲線を示す。その一方はハフニウム(Hf)ゲートメタルを使用し、他方はタンタル(Ta)ゲートメタルを使用している。該曲線は、420<sup>10</sup>での熱処理後のものであり、曲線における最大差は0.5Vを示す。

#### 【0045】

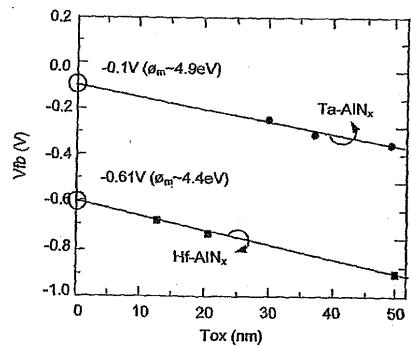

図6は、熱処理後における2つの異なるゲート構造についてのゲート酸化膜厚(T<sub>ox</sub>)に対するゲート順方向バイアス電圧(V<sub>fb</sub>)のプロットである。両方とも、本発明の工程におけるAlN<sub>x</sub>バッファ層を使用している。評価された仕事関数は、Taをゲートメタルとした場合には4.9V、Hf(ハフニウム)をゲートメタルとした場合には4.4eVであり、=0.5Vを示した。

#### 【0046】

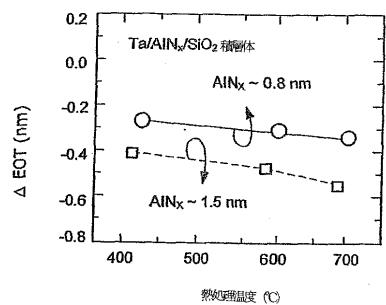

図7は、様々な熱処理温度および2つの異なる構造についての、熱処理工程の結果得られた実効酸化膜厚の変化のプロットである。その一方は、AlN<sub>x</sub>の厚さが約0.8nm<sup>20</sup>であり、他方はAlN<sub>x</sub>の厚さが約1.5nmである。

#### 【0047】

グラフは、熱処理工程の結果として実効酸化膜厚がやや減少し、厚い構造の方がより減少することを示している。最大変化は、Ta/AlN<sub>x</sub>/SiO<sub>2</sub>積層体において1.5nmのAlN<sub>x</sub>層を使用した700<sup>30</sup>での熱処理に相当する約0.5nmであった。

#### 【0048】

以上に、特定の態様によって本発明を記述したが、その変更および修正も疑いなく当業者に明らかになるであろうことが予期される。それゆえ、次の請求項は、そのような全ての変更および修正を、発明の真の精神および範囲の内に入るように包含するものとして解釈されることを意図している。

#### 【図面の簡単な説明】

#### 【0049】

【図1】図1は、本発明の方法を説明するためのフローチャートである。

【図2-A】図2-Aは、ゲート誘電体上へのバッファ層の堆積を示す。

【図2-B】図2-Bは、バッファ層上への第1メタルの堆積および、バッファ層の一部から第1メタルを除去するための準備を示す。

【図2-C】図2-Cは、第1メタルにおける不要な部分を除去した構造を示す。

【図2-D】図2-Dは、第2メタルの堆積を示す。

【図2-E】図2-Eは、第1および第2メタル、およびバッファ層の選択エッチングのための準備を示す。

【図2-F】図2-Fは、図2-Eを参照して言及したように、メタルが除去されたCMOS構造を示す。

【図2-G】図2-Gは、熱処理およびその結果として生じるバッファ層への効果を示す。

【図3】図3は、各種膜のエッティング速度を示す表である。

【図4】図4は、熱処理後における各種白金(Pt)ゲートのゲート電圧に対するキャパシタンスのグラフである。

【図5】図5は、熱処理後におけるHf-AlN<sub>x</sub>/SiO<sub>2</sub>およびTa-AlN<sub>x</sub>/SiO<sub>2</sub>ゲートのゲート電圧に対するキャパシタンスのグラフである。

【図6】図6は、Hf-AlN<sub>x</sub>/SiO<sub>2</sub>およびTa-AlN<sub>x</sub>/SiO<sub>2</sub>ゲートメタルに

10

20

30

40

50

おける熱処理後の酸化領域の厚さに対する順方向ゲート電圧のグラフである。

【図7】図7は、AlN<sub>x</sub>バッファ層の2つの異なる厚さにおける、熱処理温度の関数としての、結果として生じた実効ゲート酸化膜厚の変化のグラフである。

【符号の説明】

【0050】

- |     |           |

|-----|-----------|

| 2 2 | 基板        |

| 2 3 | pウェル      |

| 2 5 | nウェル      |

| 2 6 | ゲート誘電体    |

| 2 8 | バッファ層     |

| 3 0 | 第1ゲートメタル  |

| 3 1 | フォトレジスト   |

| 3 2 | 第2ゲートメタル  |

| 3 4 | NMOSゲート領域 |

| 3 6 | PMOSゲート領域 |

| 3 8 | 合金        |

| 4 0 | 合金        |

10

【図1】

FIG. 1

【図2-A】

FIG. 2A

【図2-B】

FIG. 2B

【図2-C】

FIG. 2C

【図 2 - D】

【図 2 - F】

【図 2 - E】

【図 2 - G】

【図 3】

(単位: nm/min)

|     | Hf   | AlN <sub>x</sub> | SiO <sub>2</sub> |

|-----|------|------------------|------------------|

| HPM | 82   | <0.1             | 6.0              |

| SPM | >100 | 0                | 0                |

FIG. 3

【図 4】

FIG. 4

【図 5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/SG2004/000100

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                      |                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|

| A. CLASSIFICATION OF SUBJECT MATTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      |                       |

| Int. Cl. 7: H01L 21/8238, 29/78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                      |                       |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |                       |

| B. FIELDS SEARCHED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                      |                       |

| Minimum documentation searched (classification system followed by classification symbols)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |                       |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |                       |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>DWPI, JAPIO IPC H01L with keywords: gate; work function, electron affin; anneal, rta, heat, thermal, temperature; buffer, barrier, shield, protect, dual (2w) gate; aluminium nitride, aln, alnx; titanium hafnium, tantalum, ti, hf, ta; electronegativ; aluminium; nitrogen                                                                                                                                                                                                          |                                                                                                      |                       |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |                       |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages                   | Relevant to claim No. |

| P, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US 2003/0180994 A1 (POLISHCHUK et al.) 25 September 2003<br>Whole document                           | 1-18                  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EP 1298722 A2 (TEXAS INSTRUMENTS INCORPORATED) 2 April 2003<br>Whole document                        | 1-18                  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2002/0086507 A1 (PARK et al.) 4 July 2002<br>Whole document                                       | 1-18                  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Patent Abstracts of Japan, JP 61-140176 A (SEMICONDUCTOR ENERGY LAB CO LTD) 27 June 1986<br>Abstract | 1-18                  |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C <input checked="" type="checkbox"/> See patent family annex                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                      |                       |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                      |                       |

| Date of the actual completion of the international search<br>28 May 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date of mailing of the international search report<br>~ 3 JUN 2004                                   |                       |

| Name and mailing address of the ISA/AU<br>AUSTRALIAN PATENT OFFICE<br>PO BOX 200, WODEN ACT 2606, AUSTRALIA<br>E-mail address: pct@ipaaustralia.gov.au<br>Facsimile No. (02) 6285 3929                                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer<br><b>MICHAEL HALL</b><br>Telephone No : (02) 6283 2474                           |                       |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

PCT/SG2004/000100

This Annex lists the known "A" publication level patent family members relating to the patent documents cited in the above-mentioned international search report. The Australian Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

| Patent Document Cited in<br>Search Report |            |      | Patent Family Member |    |            |               |

|-------------------------------------------|------------|------|----------------------|----|------------|---------------|

| US                                        | 2003180994 | NONE |                      |    |            |               |

| EP                                        | 1298722    | JP   | 2003179155           | US | 2003062577 |               |

| US                                        | 2002086507 | CN   | 1363949              | JP | 2002237469 | KR 2002056260 |

| JP                                        | 61140176   | NONE |                      |    |            |               |

Due to data integration issues this family listing may not include 10 digit Australian applications filed since May 2001.

END OF ANNEX

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,M,D,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(71)出願人 503231882

エージェンシー フォー サイエンス , テクノロジー アンド リサーチ

シンガポール国シンガポール、セントロス、ナンバー 07 - 01、ビオポリス、ウェイ、20

(74)代理人 100081994

弁理士 鈴木 俊一郎

(72)発明者 パク , チャン ソ

シンガポール 138686, #04-04 ドーバー パークビュー , 32 ドーバー ライズ

(72)発明者 チョ , ピュン ジン

シンガポール 129792, #04-07 ケント ベイル , 111 クレメンティ ロード

(72)発明者 ナラヤナン , バラスプラマニアン

シンガポール 117685, 11 サイエンス パーク ロード , インスティチュート オブ

マイクロエレクトロニクス 内

F ターム(参考) 4M104 AA01 BB02 BB13 BB14 BB17 BB38 CC05 GG09 GG10 GG14

HH20

5F048 AA01 AA07 AC03 BA01 BB04 BB09 BB10 BB12 BB13 BB15

BE03