# (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

テーマコード (参考)

特表2005-530422 (P2005-530422A)

(43) 公表日 平成17年10月6日 (2005.10.6)

(51) Int.C1.<sup>7</sup>

HO4N 7/32

HO3M 7/36

F I HO4N 7/137 HO3M 7/36

Z

5CO59 5JO64

# 審查請求 未請求 予備審查請求 未請求 (全 40 頁)

| (21) 出願番号     | 特願2004-514353 (P2004-514353) | (71 |

|---------------|------------------------------|-----|

| (86) (22) 出願日 | 平成15年6月18日 (2003.6.18)       |     |

| (85) 翻訳文提出日   | 平成17年2月17日 (2005.2.17)       |     |

| (86) 国際出願番号   | PCT/US2003/019401            |     |

| (87) 国際公開番号   | W02003/107681                |     |

| (87) 国際公開日    | 平成15年12月24日 (2003.12.24)     |     |

| (31) 優先権主張番号  | 60/390, 101                  |     |

| (32) 優先日      | 平成14年6月18日 (2002.6.18)       | (74 |

| (33) 優先権主張国   | 米国 (US)                      |     |

| (31) 優先権主張番号  | 10/371, 793                  | (74 |

| (32) 優先日      | 平成15年2月21日 (2003.2.21)       |     |

| (33) 優先権主張国   | 米国(US)                       | (74 |

|               |                              |     |

|               |                              | (74 |

|               |                              |     |

弁理士 鈴江 武彦 74)代理人 100091351 弁理士 河野 哲

4) 代理人 100088683 弁理士 中村 誠

74)代理人 100108855 弁理士 蔵田 昌俊

最終頁に続く

(54) 【発明の名称】ビデオをエンコーディングする技法とデコーディングする技法

## (57)【要約】

【課題】ビデオをエンコーディングおよびデコーディングする技法。

【解決手段】ビデオシーケンスをエンコーディングするのに必要な処理サイクルとメモリ転送との数を減少させることが可能なビデオエンコーディング技法を開示する。ビデオエンコーディング技法は、動き推定ルーチンのための検索スペースに対応するカラム中にビデオブロックを記憶する候補メモリを利用する。メモリ制御ユニットは、絶対差分和(SAD)技法や二乗差分和(SSD)技法を用いて、候補メモリをアドレス指定し、複数の画素を並行に検索し、同時に、エンコーディングされるビデオブロック中の画素と比較する。差分プロセッサはこの並行計算を実行する。次いでエンコーディングされるビデオブロックに対して、候補メモリを、検索スペース全体を再ロードすることによってではなくビデオブロックの新しいカラムをロードすることによってインクリメンタルに更新する。

#### 【特許請求の範囲】

## 【請求項1】

第1の検索スペースを定義するために画素値の集合をメモリ中にロードし、ここで前記第 1の検索スペースは、動き推定ルーチンの第1の逐次代入中にエンコーディングされる第 1のビデオブロックと比較される候補ビデオブロックの第1の複数のカラムを定義し、

前記第1のビデオブロックを前記第1の検索スペース中の前記候補ビデオブロックと比較するために前記第1の逐次代入を実行し、そして

第2の検索スペースを定義するためにカラムの部分集合を再ロードし、ここで前記第2の検索スペースは、前記動き推定ルーチンの第2の逐次代入中にエンコーディングされる第2のビデオブロックと比較される候補ビデオブロックの第2の複数のカラムを定義することを、

を含む方法。

#### 【請求項2】

前記第2のビデオブロックを前記第2の検索スペース中の前記候補ビデオブロックと比較するために前記第2の逐次代入を実行することを更に含む請求項1に記載の方法。

#### 【請求項3】

第3の検索スペースを定義するためにカラムの別の部分集合を再ロードし、ここで前記第3の検索スペースは、動き推定ルーチンの第3の逐次代入中にエンコーディングされる第3のビデオブロックと比較される候補ビデオブロックの第3の複数のカラムを定義し、

前記第3のビデオブロックを前記第3の検索スペース中の前記候補ビデオブロックと比較するために前記第3の逐次代入を実行すること、

を更に含む請求項2に記載の方法。

## 【請求項4】

第4の検索スペースを定義するためにカラムの別の部分集合を再ロードし、ここで前記第4の検索スペースは、動き推定ルーチンの第4の逐次代入中にエンコーディングされる第4のビデオブロックと比較される候補ビデオブロックの第4の複数のカラムを定義し、

前記第4のビデオブロックを前記第4の検索スペース中の前記候補ビデオブロックと比較するために前記第4の逐次代入を実行すること、

を更に含む請求項3に記載の方法。

## 【請求項5】

前記第1の逐次代入を実行することは、エンコーディングされる前記第1のビデオブロックの画素値と、前記第1の検索スペース中の前記候補ビデオブロックの内の1つの候補ビデオブロックの画素値との間で、複数の差分計算を並行に実行することを含む、請求項1に記載の方法。

## 【請求項6】

エンコーディングされるマクロブロックの画素と検索スペース内の候補マクロブロックの画素との間で差分計算を実行し、

前記計算に基づいてマイクロブロックの差分値の集合を発生し、ここで前記マイクロブロック差分値は、それぞれ、エンコーディングされる前記マクロブロックを形成する複数のマイクロブロックの各々と、前記候補マクロブロックを形成するマイクロブロックとの間の差を示し、

前記計算に基づいてマクロブロックの差分値を発生し、ここで前記マクロブロック差分値は、エンコーディングされる前記マクロブロックと前記候補マクロブロックとの間の差を示す

ことを含む方法。

## 【請求項7】

前記差分計算を実行することは、複数の差分計算を並行に実行することを含む、請求項 6 に記載の方法。

## 【請求項8】

前記並行に実行される複数の差分計算は、前記マイクロブロックの内の1つのマイクロブ

20

10

30

40

30

40

50

ロックのローに対応する、請求項7に記載の方法。

## 【請求項9】

動き推定ルーチンに従ってビデオフレームをエンコーディングするエンコーダであって、前記エンコーダは、画素値の集合をメモリ中にロードして、第1の検索スペースを定義し、前記第1の検索スペースは、前記動き推定ルーチンの第1の逐次代入中にエンコーディングされる第1のビデオブロックと比較される候補ビデオブロックから成る第1の複数のカラムを定義するものであり、また、前記第1の逐次代入を実行して、前記第1のビデオブロックを前記第1の検索スペース中の前記候補ビデオブロックと比較し、また、カラムの部分集合を再ロードして、第2の検索スペースを定義し、前記第2の検索スペースは、前記動き推定ルーチンの第2の逐次代入中にエンコーディングされる第2のビデオブロックと比較される候補ビデオブロックから成る第2の複数のカラムを定義するように構成されている、前記エンコーダと、

前記エンコーディングされたビデオフレームを送信する送信機と、 を含むデバイス。

## 【請求項10】

前記エンコーダは、エンコーディングされる前記第2のビデオブロックを前記第2の検索スペース中の前記候補ビデオブロックと比較するために前記第2の逐次代入を実行するように更に構成されている、請求項9に記載のデバイス。

#### 【請求項11】

前記エンコーダは、カラムの別の部分集合を再ロードして、第3の検索スペースを定義し、前記第3の検索スペースは、動き推定ルーチンの第3の逐次代入中にエンコーディングされる第3のビデオブロックと比較される候補ビデオブロックの第3の複数のカラムを定義するものであり、また、前記第3の逐次代入を実行して、前記第3のビデオブロックを前記第3の検索スペース中の前記候補ビデオブロックと比較するように更に構成されている、請求項10に記載のデバイス。

## 【請求項12】

前記エンコーダは、カラムの別の部分集合を再ロードして、第4の検索スペースを定義し、前記第4の検索スペースは、動き推定ルーチンの第4の逐次代入中にエンコーディングされる第4のビデオブロックと比較される候補ビデオブロックの第4の複数のカラムを定義するものであり、また、前記第4の逐次代入を実行して、前記第4のビデオブロックを前記第4の検索スペース中の前記候補ビデオブロックと比較するように更に構成されている、請求項11に記載のデバイス。

#### 【請求項13】

前記エンコーダは、エンコーディングされる前記第1のビデオブロックの画素値と、前記第1の検索スペース中の前記候補ビデオブロックの内の1つの候補ビデオブロックの画素値との間で複数の差分計算を並行に実行するように構成されている、請求項9に記載のデバイス。

## 【請求項14】

前記デバイスは、ディジタルテレビ、無線通信デバイス、携帯情報端末、ラップトップコンピュータ、デスクトップコンピュータ、ディジタルカメラ、ディジタル記録デバイス、ビデオ機能を有するセルラー無線電話及びビデオ機能を有する衛星無線電話からなるグループから選択される、請求項9に記載のデバイス。

## 【請求項15】

ビデオフレームをリアルタイムでキャプチャするビデオキャプチャデバイスを更に備え、前記エンコーダはビデオフレームをリアルタイムでエンコーディングし、前記送信機はエンコーディングされたビデオフレームをリアルタイムで送信するように構成されている、請求項9に記載のデバイス。

## 【請求項16】

ビデオフレームをエンコーディングするエンコーダであって、前記エンコーダは、エンコーディングされるマクロブロックの画素と検索スペース内の候補マクロブロックの画素と

の間で差分計算を実行し、また、前記差分計算に基づいてマイクロブロックの差分値の集合を発生し、前記マイクロブロック差分値は、それぞれ、エンコーディングされる前記マクロブロックを形成する複数のマイクロブロックの各々と、前記候補マクロブロックを形成するマイクロブロックとの間の差を示すものであり、また、前記計算に基づいてマクロブロックの差分値を発生し、前記マクロブロック差分値は、エンコーディングされる前記マクロブロックと前記候補マクロブロックとの間の差を示すように構成されている、エンコーダと、

エンコーディングされたビデオフレームを送信する送信機と、 を含むデバイス。

# 【請求項17】

前記エンコーダは、複数の差分計算を並行に実行するように構成されている、請求項 1 6 に記載のデバイス。

## 【請求項18】

前記並行に実行される複数の差分計算は、前記マイクロブロックの内の 1 つのマイクロブロックのローに対応する、請求項 1 6 に記載のデバイス。

#### 【請求項19】

ビデオフレームをリアルタイムでキャプチャするビデオキャプチャデバイスを更に備え、前記エンコーダはビデオフレームをリアルタイムでエンコーディングし、前記送信機はエンコーディングされたビデオフレームをリアルタイムで送信するように構成されており、前記ビデオフレームは、Moving Picture Experts Group4 (MPEG-4)基準に従ってエンコーディングされる、請求項16に記載のデバイス。

#### 【請求項20】

前記デバイスはバッテリ式無線デバイスである、請求項16に記載のデバイス。

#### 【請求項21】

## メモリと、

画素値の集合を前記メモリ中にロードして、第1の検索スペースを定義するメモリ制御ユニットであって、前記第1の検索スペースは、動き推定ルーチンの第1の逐次代入中にエンコーディングされる第1のビデオブロックと比較される候補ビデオブロックの第1の複数のカラムを定義するものであって、また前記メモリ制御ユニットは、カラムの部分集合を再ロードして、第2の検索スペースを定義し、前記第2の検索スペースは、前記動き推定ルーチンの第2の逐次代入中にエンコーディングされる第2のビデオブロックと比較される候補ビデオブロックの第2の複数のカラムを定義するものである、前記メモリ制御ユニットと、

前記第1の逐次代入を実行して、前記第1のビデオブロックを前記第1の検索スペース中の前記候補ビデオブロックと比較し、また、前記第2の逐次代入を実行して、前記第2のビデオブロックを前記第2の検索スペース中の前記候補ビデオブロックと比較するプロセッサと、

を含む装置。

# 【請求項22】

前記メモリ制御ユニットは、カラムの別の部分集合を再ロードして、第3の検索スペースを定義し、前記第3の検索スペースは、前記動き推定ルーチンの第3の逐次代入中にエンコーディングされる第3のビデオブロックと比較される候補ビデオブロックの第3の複数のカラムを定義するものであり、

前記プロセッサは、前記第3の逐次代入を実行して、前記第3のビデオブロックを前記 第3の検索スペース中の前記候補ビデオブロックと比較する、

請求項21に記載の装置。

#### 【請求項23】

前記メモリ制御ユニットは、カラムの別の部分集合を再ロードして、第4の検索スペースを定義し、前記第4の検索スペースは、前記動き推定ルーチンの第4の逐次代入中にエンコーディングされる第4のビデオブロックと比較される候補ビデオブロックの第4の複数

10

20

30

40

のカラムを定義するものであって、

前記プロセッサは、前記第4の逐次代入を実行して、前記第4のビデオブロックを前記 第4の検索スペース中の前記候補ビデオブロックと比較する、

請求項22に記載の装置。

## 【請求項24】

前記プロセッサは、エンコーディングされる前記ビデオブロックの内の1つと、前記検索スペースの内の1つの中の前記候補ビデオブロックの内の1つとの間で複数の差分計算を並行に実行するように構成されている、請求項21に記載の装置。

## 【請求項25】

コンピュータ読み取り可能命令を記憶するメモリと、

前記命令を実行して、

エンコーディングされるマクロブロックの画素と検索スペース内の候補マクロブロックの画素との間で差分計算を実行し、

前記計算に基づいてマイクロブロックの差分値の集合を発生し、前記マイクロブロックの差分値は、それぞれ、エンコーディングされる前記マクロブロックを形成する複数のマイクロブロックの各々と、前記候補マクロブロックを形成するマイクロブロックとの間の差を示し、

前記計算に基づいてマクロブロックの差分値を発生し、前記マクロブロックの差分値は、エンコーディングされる前記マクロブロックと前記候補マクロブロックとの間の差を示す、

プロセッサと、

を含む装置。

## 【請求項26】

前記プロセッサは、複数の差分計算を並行に実行するように構成されている、請求項25 に記載の装置。

## 【請求項27】

前記並行に実行される複数の差分計算は、前記マイクロブロックの内の 1 つのマイクロブロックのローに対応する、請求項 2 6 に記載の装置。

# 【請求項28】

Moving Picture Experts Group (MPEG)基準に従って ビデオブロックをエンコーディングする装置であって、前記装置は、

画素値の集合をメモリ中にロードして、第1の検索スペースを定義し、前記第1の検索スペースは、動き推定ルーチンの第1の逐次代入中にエンコーディングされる第1のビデオブロックと比較される候補ビデオブロックの第1の複数のカラムを定義し、

前記第1の逐次代入を実行して、前記第1のビデオブロックを前記第1の検索スペース中の前記候補ビデオブロックと比較し、

カラムの部分集合を再ロードして、第2の検索スペースを定義し、前記第2の検索スペースは、前記動き推定ルーチンの第2の逐次代入中にエンコーディングされる第2のビデオブロックと比較される候補ビデオブロックの第2の複数のカラムを定義する、

ように構成されている、前記装置。

# 【請求項29】

前記装置は、前記第2の逐次代入を実行して、前記第2のビデオブロックを前記第2の検索スペース中の前記候補ビデオブロックと比較するように構成されている、請求項28に記載の装置。

## 【請求項30】

# 前記装置は、

カラムの別の部分集合を再ロードして、第3の検索スペースを定義し、前記第3の検索スペースは、動き推定ルーチンの第3の逐次代入中にエンコーディングされる第3のビデオブロックと比較される候補ビデオブロックの第3の複数のカラムを定義し、

前記第3の逐次代入を実行して、前記第3のビデオブロックを前記第3の検索スペース

10

20

40

50

中の前記候補ビデオブロックと比較する、

ように更に構成されている、

請求項29に記載の装置。

### 【請求項31】

前記装置は、

カラムの別の部分集合を再ロードして、第4の検索スペースを定義し、前記第4の検索スペースは、動き推定ルーチンの第4の逐次代入中にエンコーディングされる第4のビデオブロックと比較される候補ビデオブロックの第4の複数のカラムを定義し、

前記第4の逐次代入を実行して、前記第4のビデオブロックを前記第4の検索スペース中の前記候補ビデオブロックと比較する、

ように更に構成されている、

請求項30に記載の装置。

#### 【請求項32】

前記装置は、エンコーディングされる前記第1のビデオブロックの画素値と、前記第1の検索スペース中の前記候補ビデオブロックの内の1つの候補ビデオブロックの画素値との間で、複数の差分計算を並行に実行するように構成されている、請求項28に記載の装置

### 【請求項33】

Moving Picture Experts Group(MPEG)基準に従ってビデオブロックをエンコーディングする装置であって、前記装置は、

エンコーディングされるマクロブロックの画素と検索スペース内の候補マクロブロックの画素との間で差分計算を実行し、

前記計算に基づいてマイクロブロックの差分値の集合を発生し、前記マイクロブロック差分値は、それぞれ、エンコーディングされる前記マクロブロックを形成する複数のマイクロブロックの各々と、前記候補マクロブロックを形成するマイクロブロックとの間の差を示し、

前記計算に基づいてマクロブロックの差分値の集合を発生し、前記マクロブロック差分値は、エンコーディングされる前記マクロブロックと前記候補マクロブロックとの間の差を示す、

ように構成される、前記装置。

# 【請求項34】

前記装置は、複数の差分計算を並行に実行するように構成されている、請求項33に記載の装置。

## 【請求項35】

前記並行に実行される複数の差分計算は、前記マイクロブロックの内の 1 つのマイクロブロックのローに対応する、請求項 3 4 に記載の装置。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本出願は、本出願の譲受人に譲渡され、2002年6月18日に提出された「ビデオ動き推定システムにおける消費電力を減少させる方法」という題名の米国仮出願第60/390,101号の利益を主張するものであり、本明細書においてこれは参照して全体としてここに組み込まれる。

# [0002]

## (関連出願)

本出願は、上記と同じ日付に提出された、「ビデオをエンコーディングする技法とデコーディングする技法」という題名の同時係属出願第10/371,768号(事件整理番号第020127号)に関連する。本出願は、更に、2002年5月3日に提出された「ビデオをエンコーディングする技法」という題名の同時係属出願第10/139,772号(事件整理番号第020086号)に関連する。これらの出願はどちらも本出願と同一

10

20

30

40

20

30

50

(7)

の譲受人に譲渡される。

## [0003]

本開示はディジタルビデオ処理に関し、より詳しくは、ビデオシーケンスのエンコーディングに関する。

## 【背景技術】

## [0004]

ディジタルビデオの機能は、ディジタルテレビ、ディジタル直接衛星放送システム、無線通信デバイス、携帯情報端末(PDA)、ラップトップコンピュータ、デスクトップコンピュータ、ディジタルカメラ、ディジタル記録デバイス、携帯式もしくは衛星式無線電話等を含む広い範囲のデバイスに組み込むことが可能である。ディジタルビデオデバイスは、フルモーションビデオシーケンスの作成、修正、送信、記憶、記録、再生という点で、従来のアナログビデオシステムよりかなりの改善をもたらすことが可能である。

## [0005]

ディジタルビデオシーケンスをエンコーディングする多くの様々なビデオエンコーディング基準が確立されている。例えば、MPEG(Moving Picture Experts Group)によって、MPEG-1、MPEG-2及びMPEG-4を含む多くの基準が開発されてきた。他の基準には、ITU H.263や、カリフォルニア州クパーティノ(Cupertino California)のアップルコンピュータ社(Apple Computer)によって開発されたQuickTime(商標)技術や、ワシントン州レッドモンド(Redmond,Washington)のマイクロソフト社(Microsoft Corporation)によって開発されたWindows(商標)用のVideoや、インテル社(Intel Corporation)によって開発されたIndeo(商標)や、ワシントン州シアトル(Seatle,Washington)のリアルネットワーク社(RealNetworks,Inc.)からのRealVideo(商標)や、スーパーマック社(SuperMac,Inc.)によって開発されたCinepak(商標)がある。

## [0006]

多くのビデオエンコーディング基準で、データを圧縮してエンコーディングすることによって送信レートが増加している。圧縮することによって、送信する必要があるデータの全体量を減少させて、ビデオフレームの送信を効果的にすることが可能である。例えば、MPEG基準は、圧縮なしで達成され得るよりも狭い帯域幅でビデオと画像の送信を容易化するように設計されているグラフィックスとビデオを圧縮する技法を利用している。

#### [0007]

例えば、MPEG基準は、一時的相関またはフレーム間相関と呼ばれる連続するビデオフレーム間の類似性を利用して、フレーム間圧縮をするビデオエンコーディング技法をサポートしている。このフレーム間圧縮技法は、ビデオフレームの画素ベース表示を動き表示に変換することによってフレーム全体にわたるデータ冗長度を利用するものである。更に、ビデオエンコーディング技法は、空間相関またはフレーム内相関と呼ばれるフレーム内での類似性を利用して、ビデオフレームを更に圧縮するものである。フレーム内圧縮は、一般的には、離散コサイン変換(DCT)式エンコーディングなどの静止画像を圧縮するテクスチャエンコーディングに基づいている。

#### [00008]

圧縮をサポートするために、ディジタルビデオデバイスは、一般的に、ディジタルビデオシーケンスを圧縮するエンコーダと、このディジタルビデオシーケンスを解凍するデコーダとを含んでいる。多くの場合、これらエンコーダとデコーダは、ビデオ画像のシーケンスを定義するフレーム内の画素のブロック上で動作する統合エンコーダ / デコーダ(CODEC)を形成する。例えば、MPEG-4基準では、エンコーダは、一般的に、送信されるビデオフレームを、16×16の画素配列を備えるマクロブロックに分割する。

# [0009]

ビデオフレーム中の各マクロブロックに対して、エンコーダは、直前のビデオフレーム

30

40

50

(または後続のフレーム)のマクロブロックを検索して、最も類似したマクロブロックを特定し、また、送信用のマクロブロック間の差を、前のフレームからのどのマクロブロックがエンコーディングに用いられたかを示す動きベクトルと共に、エンコーディングする。 デコーダは、この動きベクトルとエンコーディングされた差を受信して、動き補償を実行して、ビデオシーケンスを発生する。

#### [0010]

このビデオエンコーディングプロセスは、特に動き推定技法を用いる場合には計算集約的である。例えば、エンコーディングされるビデオブロックを前に送信されたフレームのビデオブロックと比較するプロセスでは、多量の計算が必要となる。改良型のエンコーディング技法は、特に、計算リソースがより限られ、また、消費電力が関心事とされる無線デバイスや他の携帯式ビデオデバイスで使用するのが非常に望ましい。同時に、改良型の圧縮は、ビデオシーケンスを効果的に送信するために必要とされる帯域幅が減少する目的には望ましいものである。これらの要因の1つ以上を改善することによって、特に、無線帯域幅の設定や限られた大域幅の設定の場合には、ビデオシーケンスのリアルタイムエンコーディングが容易化されたり改善されたりする。

#### 【発明の開示】

【発明が解決しようとする課題】

## [0011]

本開示は、ビデオシーケンスをエンコーディングするために必要な処理サイクルの数と、メモリ転送の回数とを減少させることが可能なビデオエンコーディング技法を説明する。このように、ここに開示するビデオエンコーディング技法によって、ビデオエンコーディング速度が増し、消費電力が減少する。更に、この技法は、エンコーディングされるマクロブロックと関連する差分値を定義する計算と、エンコーディングされるマクロブロックを形成する様々なマイクロブロックと関連する差分値を定義する計算とで同じ計算の集合を用いる。

## 【課題を解決するための手段】

## [0012]

本明細書に記載するビデオエンコーディング技法では、カラム方向の動き推定ルーチンのための検索スペースを記憶する候補メモリを用いる。メモリ制御ユニットは、候補メモリをアドレス指定して、複数の画素を並行して検索して、例えば、絶対差分和(SAD)技法や二乗差分和(SSD)技法を用いて、エンコーディングされるビデオブロックの画素と同時に比較することが可能である。差分プロセッサは、これらの計算を並行して実行する。平行な計算の各集合は、マクロブロックを形成するマイクロブロックの内の1つのローに対応している。更に、エンコーディングされる後続のビデオブロックに対しては、候補メモリは、検索スペース全体を再ロードするのではなく新しいビデオブロックのカラムをロードすることによって、インクリメンタルに更新することが可能である。

# [0013]

本明細書に記載するこれらの技法及び他の技法は、ディジタルビデオデバイス中で、ハードウエアとして、ソフトウエアとして、ファームウエアとしてまたはこれらの組み合わせで実施される。ソフトウエアとして実施する場合、上記の技法は、実行すると、本明細書に記載するエンコーディング技法の内の1つ以上を実行するプログラムコードを備えるコンピュータ読み取り可能媒体を志向する。様々な実施形態の更なる詳細は、添付図面と以下の説明に記載されている。他の特徴、目的及び利点は、この説明及び図面と特許請求の範囲とから明らかであろう。

## 【発明を実施するための最良の形態】

# [0014]

一般に、本開示は、ディジタルビデオデータのエンコーディングを改善するために用いることが可能なビデオエンコーディング技法を志向する。このビデオエンコーディング技法は、ビデオシーケンスをエンコーディングするために必要な処理サイクルの数とメモリ転送の回数とを減少させ、これで、ビデオエンコーディング速度を増加させ、消費電力を

減少させる。例えば、このビデオエンコーディング技法によれば、一般的にビデオエンコーディングプロセスの最も計算集約的な態様である動き推定プロセスでは特に、計算効率が増加する。更に、このビデオエンコーディング技法は、MPEG-4デコーディング基準などのデコーディング基準と互換性がある。

#### [ 0 0 1 5 ]

このビデオエンコーディング技法は、ディジタル放送システム、携帯情報端末(PDA)、ラップトップコンピュータ、デスクトップコンピュータ、ディジタルカメラ、ディジタル記録デバイス、携帯電話等などの様々なディジタルビデオデバイス中で実施される。このビデオエンコーディング技法によって、MPEG-4などの基準に従ってビデオをエンコーディングする効率が改善され、また、計算リソースがより制限され消費電力が関心事とされる携帯電話などの無線通信デバイス内でのビデオのエンコーディングの実施をより容易なものとする。

## [0016]

このビデオエンコーディング技法は、カラム方向に検索スペースのビデオブロックを記憶する候補メモリを用いる。メモリ制御ユニットは、候補メモリをアドレス指定して、複の画素を並行して検索して、例えば、絶対差分和(SAD)技法や二乗差分和(SSD)技法を用いて、エンコーディングされるビデオブロックの画素と同時に比較するのとま行して、エンコーディングされるビデオブロックと比較されてハースの候補ビデオブロックと関連する差分値(ときとして、エンコーディングされる後続の候補ビデオブロックと関連するを受して、エンコーディングされる後続の形態で検索結果を発生することが可能である。更に、エンコーディングされる後続のドガロックに対しては、候補メモリは、検索スペース全体を再ロードするので新されることが可能である。このようなカラムの更新によって、消費電力とシステムバスの使用とが減少し、また、新しい検索スペースをロードするのに要する時間が減少する。

## [0017]

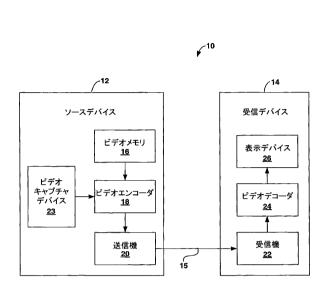

図 1 は、ソースデバイス 1 2 が、エンコーディングされたビデオデータのシーケンスを 受 信 デ バ イ ス 1 4 に 通 信 リ ン ク 1 5 を 介 し て 送 信 す る 例 示 の シ ス テ ム 1 0 を 示 す ブ ロ ッ ク 図である。ソースデバイス12と受信デバイス14は双方共、ディジタルビデオデバイス である。特に、ソースデバイス12は、様々なビデオ圧縮基準の内のどれか1つ、例えば 、Moving Picture Experts Groupによって開発されたMP EG-4を用いてビデオデータをエンコーディングして送信する。他の基準には、MPE G-1、MPEG-2またはMoving Picture Experts Grou pによって開発された他のMPEG基準、ITU H.263及び類似の基準、Moti on JPEG2000、カリフォルニア州クパーティノ(Cupertino Cal ifornia)のアップルコンピュータ社(Apple Computer)によって 開発されたQuickTime(商標)技術や、ワシントン州レッドモンド(Redom ond, Washington)のマイクロソフト社(Microsoft Corpo ration)によって開発されたWindows(商標)のVideoや、インテル社 (Intel Corporation)によって開発されたIndeo(商標)や、ス ーパーマック社(SuperMac,INC.)によって開発されたCinepak(商 標)がある。

## [0018]

通信リンク15は、無線リンク、物理送信ライン、ローカルエリアネットワークや、ワイドエリアネットワークや、インターネットなどのグローバルネットワークなどのパケットベースネットワーク、公衆交換電話網(PSTN)等を備える。従って、通信リンク15は、ソースデバイス12から受信デバイス14にビデオデータを送信するための、任意の適当な通信媒体または、場合によっては様々なネットワークとリンクとの集合物を表している。

# [0019]

40

20

30

40

50

ソースデバイス12は、ビデオデータをエンコーディングして送信することが可能な任意のディジタルビデオデバイスである。例えば、ソースデバイス12は、ディングするビデオメモリ16と、このシーケンスをエンコーディングするビデオエンコーダ18と、エンコーディングされたシーケンスを、通信リンク15を介してソースデバイス14に送信する送信機20とを含むことができる。ビデオエンコーダ18は、例えば、1つ以上のプログラム可能ソフトウエアモジュールを実行してビデオエンコーディング技法を制御するディジタル信号プロセッサ(DSP)を含むことができる。関連のメモリと論理回路とが備えられ、これで、DSPがビデオエンコーディング技法を制御するのをサポートする。以下に説明するように、ビデオエンコーダ18は、処理サイクル、メモリ転送及び消費電力を減少させるように構成される。更に、ビデオエンコーダ18は、集合を成す計算を実行して、マクロブロックの差分値と、このマクロブロックを形成するマイクロブロックの様々な差分値とを発生するように構成することが可能である。

[0020]

更に、ソースデバイス12は、ビデオシーケンスをキャプチャして、そのキャプチャしたシーケンスをメモリ16中に記憶するビデオカメラなどのビデオキャプチャデバイス23を含むことができる。特に、ビデオキャプチャデバイス23は、電荷結合素子(CCD)、電荷注入デバイス、光ダイオードの配列、相補型金属酸化物半導体(CMOS)デバイスまたは、ビデオ画像もしくはディジタルビデオシーケンスをキャプチャすることが可能な他の任意の感光性デバイスを含む。

[0021]

更に別の例として、ビデオキャプチャデバイス 2 3 は、例えば、テレビ、ビデオカセットレコーダ、カムコーダ等からのアナログビデオデータをディジタルビデオデータに変換するビデオコンバータである。一部の実施形態では、ソースデバイス 1 2 は、リアルタイムビデオシーケンスを、通信リンク 1 5 を介して送信するように構成される。その場合、受信デバイス 1 4 は、リアルタイムビデオシーケンスを受信して、そのビデオシーケンスをユーザに対して表示する。代替例では、ソースデバイス 1 2 は、受信デバイス 1 4 にビデオデータファイルとして、すなわち、リアルタイムではなく送られたビデオシーケンスをキャプチャしてエンコーディングする。このように、ソースデバイス 1 2 と受信デバイス 1 4 は、ビデオクリップの再生や、ビデオメールや、ビデオ会議などのアプリケーションを、例えば、モバイル無線ネットワーク上でサポートする。

[ 0 0 2 2 ]

受信デバイス14は、ビデオデータを受信してデコーディングすることが可能であればどのようなディジタルビデオデバイスの形態をとってもよい。例えば、受信デバイス14は、エンコーディングされたディジタルビデオシーケンスを送信機20から、例えば、中間リンクや、ルータや、他のネットワーク装置等を介して受信する受信機22を含むことができる。受信デバイス14はまた、このシーケンスをデコーディングするビデオデコーダ24と、このシーケンスをユーザに対して表示する表示デバイス26とを含むことができる。一部の実施形態では、受信デバイス14は、組み込み式表示デバイス14を含まなくてもよい。それどころか、受信デバイス14は、受信したビデオデータをデコーディングして、個々の表示デバイス、例えば、テレビやモニターを駆動する受信機として働く。

[0023]

ソースデバイス12と受信デバイス14との例示のデバイスは、コンピュータネットワーク上にあるサーバと、ワークステーションもしくは他のデスクトップ型計算デバイスと、ラップトップコンピュータもしくは携帯情報端末(PDA)等の携帯型計算デバイスとを含む。他の例には、ディジタルテレビ、ディジタルカメラ、ディジタルビデオカメラもしくは他のディジタル記録デバイスなどのディジタルテレビ放送の衛星デバイス及び受信デバイス、ビデオ機能を有する携帯電話などのディジタルビデオ電話、他の無線ビデオデバイス等がある。

[0024]

場合によっては、ソースデバイス12と受信デバイス14はその各々が、ディジタルビ

30

40

50

デオデータをエンコーディングしたりデコーディングしたりするエンコーダ / デコーダ(CODEC)(図示せず)を含む。その場合、ソースデバイス12と受信デバイス14は双方共が、送信機及び受信機並びにメモリ及びディスプレイを含む。以下に概括するエンコーディング技法の内の多くは、ディジタルビデオデバイスがエンコーダを含むような状況下で説明される。しかしながら、エンコーダはCODECの一部を形成することが理解されよう。その場合、CODECはDSP、マイクロプロセッサ、特定用途向け集積回路(ASIC)、個々のハードウエアコンポーネントまたはそれらの様々な組み合わせで実現される。

## [0025]

#### [0026]

時として、解像度は、マクロブロックではなくてマイクロブロックの動き推定を計算することによって改善することが可能である。その上、以下に更に詳述するように、マクロブロックの差分値の計算と並行してより小さいマイクロックの、差分測定基準とも呼ばれる、差分値の計算を可能とするように記憶またはアドレス指定される。すなわち、マクロブロックの差分測定基準の計算は、このマクロブロックを形成する1連の計算とみなされる。従って、マクロブロックの差分測定基準の4つから成る1連の計算とみなされる。従って、マクロブロックと、このマイクロブロックを形成するマイクロブロックの差分測定基準は、同じ計算から発生することが可能である。特に、このような技法は、更なるSAD計算やSSD計算を追加することなく容易化される。それどころか、アドレス指定方式と計算方式とは、同じ計算が、エンコーダによって、マイクロブロックの差分値の計算とマクロブロックの差分値の計算であると解釈することが可能となるように設計することが可能である。

# [0027]

マイクロブロックまたはマクロブロック中の各々の画素は、色や強度などの画素の視覚特徴、例えば、クロミナンスや輝度を定義するnビットの値、例えば、8ビットで表される。しかしながら、動き推定は、通常は、輝度成分にだけ基づいて実行されるが、それは、人間の視覚は色より輝度の変化に対してより敏感であるからである。従って、動き推定という目的のためには、nビット値全体が、所与の画素の定量化輝度であってよい。しかしながら、本開示の原理は、画素のフォーマットに限られることなく、より簡単な少ビット画素フォーマットまたはより複雑な大ビット画素フォーマットでの適用にまで拡大される。

# [0028]

ビデオフレーム中の各ビデオブロックに対して、ソースデバイス12のビデオエンコーダ18は、メモリ16に記憶されているビデオブロックを検索して、すでに送信されている先行するビデオフレーム(または後続のビデオフレーム)を求め、これで、類似のビデオブロックを特定し、また、ビデオブロック間の差を、エンコーディングに用いられた前

30

40

50

のフレーム(または後続のフレーム)からビデオブロックを特定する動きベクトルと共にエンコーディングする。このようにして、各フレームを独立した画像としてエンコーディングする代わりに、ビデオエンコーダ18は、隣り合ったフレーム同士間の差をエンコーディングする。動き推定の実行には、エンコーディングされる現行のフレーム中にマイクロブロックまたはマクロブロックと最も良好に適合する、前のまたは後続のフレーム中のマイクロブロックまたはマクロブロックの識別動作が伴う。

[0029]

動きベクトルは、ビデオブロックの左上の角と関連する画素位置を定義することができるが、他の動きベクトルのフォーマットを用いることも可能である。いずれの場合も、動きベクトルを用いてビデオブロックをエンコーディングすることによって、ビデオデータストリムの送信に必要とされる帯域幅をかなり減少させることが可能である。場合によっては、ソースデバイス12は、エンコーディングプロセス中に様々な比較や計算を終了させて、計算回数を減少させて電力を節約することが可能なプログラム可能閾値をサポートする。

[0030]

受信デバイス14の受信機22は、動きベクトルという形態のエンコーディング済みビデオデータと、エンコーディング済みの差とを受信する。デコーダ24は、動き補償技法を実行して、ビデオシーケンスを発生して、表示デバイス26でユーザに表示するようにする。受信デバイス14のデコーダ24もまた、エンコーダ/デコーダ(CODEC)として実現される。その場合、ソースデバイス12と受信デバイス14は双方共、ディジタルビデオシーケンスをエンコーディングし、送信し、受信し、デコーディングすることが可能である。

[0031]

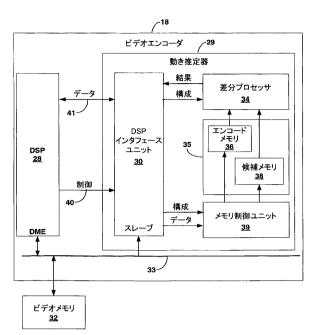

図2は、ここに記載する技法に従ってディジタルビデオシーケンスをエンコーディングするビデオエンコーダ18を示すブロック図である。図2は例示の実現例を表しており、本開示を制限するものと考えるべきではない。図2に示すように、ビデオエンコーダ18は、ディジタル信号プロセッサ(DSP)28と動き推定器29とを含むことができる。DSP28は、動き推定器29の動作を制御し、また、ビデオエンコーディングコントローラとして働く。代替例では、ビデオエンコーディングコントローラは、プロセッサや、ハードウエアコンポーネントや、ファームウエアや、特定用途向け集積回路(ASIC)や、フィールドプログラム可能ゲートアレイ(FPGA)等で実現することが可能である

[0032]

図2の例では、DSP28は、1つ以上のプログラム可能ソフトウエアモジュールを実行して、ビデオエンコーディング技法を制御する。動き推定器29は、DSPインタフェース30及びビデオメモリ32は、バス33を介して通信する。ビデオメモリ32は、ビデオエンコーダ18にとのの外部コンポーネントまたはビデオエンコーダ18の一部として組み込まれているものとみなされる。DSPインタフェース30は、動き推定ルーチンと関連する計算を実行する差分プロセッサ34はSAD計算またはSSD計算を実行して、例えば、所与のビデオフレームに対してエンコーディングされるブロックまたはマクロブロックの動きベクトルを計算する。エンコーディングアルゴリズムの制御をDSP28に分け与え、また、動き推定器29のハードウエア内での計算の計算集約的な動き推定を分離することによって、リアルタイムエンコーディングをサポートする能力を高めることが可能である。

[ 0 0 3 3 ]

差分プロセッサメモリ35は、図2で更に示すように、エンコードメモリ36と候補メモリ38とを含んでいる。エンコードメモリ36は、エンコーディングされる現行のマクロブロックを動き推定ルーチンを用いて記憶する。現行のマクロブロックは、エンコーディングされるビデオフレーム中の複数のマクロブロックの配列の内の1つに対応している

30

40

50

。候補メモリ38は、検索スペースを形成する別のフレームからのマクロブロックの配列を記憶する。差分プロセッサ34は、候補メモリ38中のマクロブロックをエンコードメモリ36中の現行のマクロブロックと比較して、動きベクトルとして使用するのに最もよく適合するものを特定する。例えば、48×48画素の検索スペースを用いるとする。その場合、検索スペースは、9個のマクロブロック、すなわち、各々が16×16配列の画素を含む3つのマクロブロックのカラム3つを含む。他のマクロブロックも、48×48画素配列の検索スペース内で定義して、この検索スペースを定義する9個のマクロブロックの内の2つ以上のマクロブロックからの画素を含むようにすることが可能である。

メモリ制御ユニット39は、候補メモリ38とエンコードメモリ36とのアドレス指定を制御して、動き推定ルーチンの検索プロセスを駆動する。特に、メモリ制御ユニット39は、バス33を介してのビデオメモリ32から候補メモリ38への画素データのロード動作を制御して、検索スペースを形成する。この目的のため、メモリ制御ユニット39年を展補メモリ38中に、DSP28からの干渉なしでロードすると、DSP28とDSP28をにインタフェースユニット30との間のバスのアクティビティを減少させ、ビデオデータを移った。差分プロセッサ34は、各マクロブロックのSAD結果またはSSD結果を決定して、当会によく適合する結果をDSPインタフェース30に送り返す。一方、DSP28に出力して、バス33を介してビデオメモリ32中に記憶させるようにする。

[0035]

[ 0 0 3 4 ]

動作中、DSP28はDSPインタフェースユニット30を制御して、制御チャネル40を介して検索プロセスを駆動する。一般に、制御チャネル40は、メモリロードコマンドのために用いられるが、このコマンドは、候補メモリ38中にロードされる検索スペースの画素指標を含む。各画素指標は、左上角または候補マクロブロックのアドレスを発生が、他の形態を用いても良い。更に、DSP28は、差分プロセッサ34によって発生れた検索結果を、データチャネル41を介して受信する。データチャネル41はまた、ハードウエアの構成とモードの切り替えに用いられる。DSP28とビデオメモリ32に用いられる。DSP28とビデオメモリ32に対して遂行される。この場合、DSPインタフェースユニット30と、差分プロセッサ34と、エンコードメモリ36と、候補メモリ38と、メモリ制御ユニット39とは、アータをビデオメモリ32からフェッチして、それをエンコードメモリ36と候補メモリ38との中にロードするために用いられる。

[0036]

図2の例では、DSPインタフェースユニット30は、ビデオメモリ32からのエンコードメモリ36と候補メモリ38とに対する、バス33とメモリ制御ユニット39とを介してのメモリ転送のためのスレーブとして働く。最初は、DSPインタフェースユニット30は、検索スペース全体を候補メモリ38中にロードしてよい。その後で、DSPインタフェースユニット30は、インクリメンタルに候補メモリ38を更新して、例えば、新しいカラムを検索スペースに対して、エンコーディングされる所与のフレーム中の次のブロックとして追加する。DSPインタフェースユニット30は、ビデオデータの転送とメモリ制御ユニット39の構成とのためのデータと構成チャネルとを有することができる。更に、DSPインタフェースユニット30は、差分プロセッサ34によって実行される検索プロセスを制御するための構成チャネルと、検索結果を受信するための結果チャネルとを有する。

[0037]

図 2 の例では、ビデオエンコーダ 1 8 は、圧縮されたディジタルビデオシーケンスをホストソースデバイス 1 2 に提供して、受信デバイス 1 4 に送信されるようにする。ビデオ

30

40

50

エンコーダ18は、このビデオシーケンスをエンコーディングして、それを送信に先立って、エンコーディングされたこのディジタルビデオシーケンスをビデオメモリ32内でバッファする。ビデオメモリ32と差分プロセッサメモリ35とは、同期式ダイナミックランダムアクセスメモリ(SDRAM)、FLASHメモリ、電気的に消去可能なプログラム可能読み出し専用メモリ(EEPROM)等の形態をとる。エンコードメモリ36と候補メモリとは、一般的には、ビデオエンコーダ18のローカルメモリであり、「仮想の」メモリに分離される共通メモリデバイスを備える。

## [0038]

図 2 に示すコンポーネントに加えて、一部の実施形態では、ビデオエンコーダ 1 8 は、離散コサイン変換(DCT)エンコーディングなどの静止像の圧縮のために一般的に用いられる、フレーム内またはフレーム間圧縮を実行するテクスチャエンコーダなどの他のコンポーネントを含むことができる。例えば、テクスチャエンコーディングは、処理機能が効果的な動き推定をするにはあまりに限られているとみなされるシナリオで、動き推定に加えてまたは、場合によっては動き推定の代わりに実行される。DSP28は、任意の時点で処理機能に基づいて動き推定器(29)とテクスチャエンコーダ(図示せず)とを選択的に発動することによってエンコーディングルーチンを出力する。

## [0039]

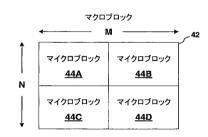

図3に、ビデオフレームでビデオメモリ32内に記憶することが可能なマクロブロック42という形態のビデオブロックの例を示す。MPEG基準と他のビデオエンコーディング中にマクロブロックという形態でビデオブロックを利用する。上述したように、MPEG-4に適合するシステムでは、「マクロブロック」という用語は、ビデオフレームの部分集合を形成する16×16の画素値の集合の数のビットを用いて各画素を定義して、所望の撮像品質を達成するようにしてもよい。マクロブロックは、より少ない数の8×8の画素マイクロブロック44Aから44Dを備えることができる。しかしながら、一般に、本明細書に記載するエンコーディング技法は、16バイト×16バイトのマクロブロック、8バイト×8バイトのミクロブロックのブロックまたは、所望しだいでは別のサイズのビデオブロックなどの定義された任意のサイズのブロックを用いて動作する。

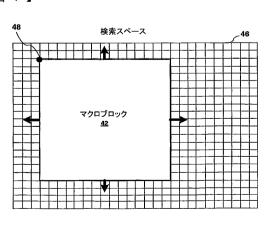

## [0040]

図4に、候補メモリ38内に記憶することが可能な検索スペース46の一部分の例を示す。検索スペース46は、前に送信されたビデオフレーム(または後続のフレームシーケンスのビデオフレーム)に対応する画素の集合体である。検索スペースは、前のもしくは後続のビデオフレームの全体または、所望しだいではこれらビデオフレームの部分集合を備えることができる。検索スペースは、図示するように矩形形状であるか、または、広い範囲の様々な形状とサイズの内のいずれかを取る。

# [0041]

ビデオエンコーディング中、エンコーディングされる現行のマクロブロックは、検索スペース46中のビデオブロックと比較され、適切に適合するものを特定し、これで、検索スペース中での現行のマクロブロックとこの類似のマクロブロック間の差が、この類似のビデオブロックを特定する動きベクトルとともに送信することが可能となるようにする。上述したように、検索スペース46内で定義されたマクロブロック48は候補メモリ38中に記憶することが可能であり、エンコーディングされる現行のマクロブロックはエンコードメモリ36に記憶することが可能である。

#### [0042]

動き推定ビデオエンコーディング中、差分プロセッサ34は、エンコーディングされる 現行のマクロブロックを前のまたは後続のフレームのマクロブロックと、SAD技法また はSSD技法などの比較技法を用いて比較することが可能である。図4に示すように、検 索スペース46内のマクロブロック48は、それぞれのマクロブロックの左上の画素アド レス48によって特定することが可能である。他の比較技法を用いてもよい。特に、本開

30

40

50

示の原理に従って、SAD計算またはSSD計算を、複数の画素に対して並行に実行することが可能である。その上、画素毎の比較のアドレス指定と計算の順序は、エンコーディングされる各マクロブロックの差分値と、このマクロブロックを形成するマイクロブロックの差分値とを発生するような仕方で実行することが可能である。

#### [0043]

本開示では、「タスク」という用語は、検索スペース内の現行のビデオブロックと別のビデオブロックと比較するために用いられる計算の共通集合のことである。すなわち、タスクとは、検索スペース中の現行のビデオブロックと別のビデオブロックとの1つの比較のことである。例えば、タスクには、検索スペース中の現行のビデオブロックの多くの画素を候補ビデオブロックの画素と比較するために多くの計算を実行する動作が伴う。本明細書に記載するように、これらのタスク計算の様々な部分集合を並行に実行して、エンコーディングプロセスをスピードアップする。64回の計算をマイクロブロックタスクとみなし(マイクロブロックは8×8の画素配列で定義されるものと仮定する)、256回の計算をマクロブロックタスクとみなす(マクロブロックは16×16の画素配列で定義されるものと仮定する)。各タスク中、これらの計算を累積して、タスクの現行の差分値(時として、差分測定基準と呼ばれる)を定義する。

#### [0044]

本開示では、「逐次代入」という用語は、ビデオエンコーディング中に実行されるタスクの共通集合のことである。エンコーディングされる現行のビデオブロックと関連する1連のタスク全体が逐次代入である。すなわち、逐次代入は、検索スペース中で現行のビデオブロックを前のビデオブロック(または後続のビデオブロック)の集合と比較する比較の集合である。個別の比較はその各々が、多くの比較を伴うタスクである。従って、検索スペースは、逐次代入中に現行のビデオブロックと比較されるビデオブロックの集合を定義する。逐次代入の比較は各々がタスクと呼ばれ、従って、各々のタスク、すなわち、各々の比較には多くの計算が伴う。

## [0045]

場合によっては、逐次代入は、検索スペース上に第1の検索を定義することと、前記検索スペース中で第1の適合を特定することと、前記第1の適合に基づいて前記検索スペースの部分集合上に第2の検索を定義することと、前記部分集合中で第2の適合を特定することとを含む。例えば、逐次代入の後半の検索には、検索スペース内で少しシフトして、最良の適合を的確に示す動作が含まれる。最低の差分値を生じるマクロブロックを特定する画素位置がダイアモンド形状の検索パラメータの中心に置かれるまで検索が継続される、ダイアモンド検索技法などの他の検索技法を用いることも可能である。更に、最低の差分値を生じるマクロブロックを特定する画素位置が半径(R)で定義される検索パラメータの中心に置かれる、円検索技法などの他の技法も用いられる。半径(R)の円は、ダイアモンド検索パラメータより大きく、より包含的な検索パラメータを定義することが可能である。

## [0046]

ダイアモンド検索技法または円検索技法を逐次代入中に用いると、初期化技法も用いられて、ダイアモンド形状検索パラメータまたは円形に定義された検索パラメータの中心にある最低の差分値を生じるマクロブロックを特定するプロセスをスピードアップさせる。例えば、空間冗長性という現象を利用する初期化技法が用いられることができる。空間冗長性は、一般的に、所与のビデオブロックのビデオの動きは、その所与のビデオブロックに空間的に非常に近接している別のビデオブロックのビデオの動きに類似している可能性が高いことを予測するものである。この初期化技法は、この現象をより容易に利用して、これを用いるとビデオエンコーディングを効果的なものとすることが可能なビデオブロックを含む確率が非常に高い検索スペース内の位置での動き推定を初期化することが可能である。

## [0047]

より具体的には、この初期化技法は、エンコーディングされるビデオブロックに空間的

20

30

40

50

に非常に近接しているビデオブロックについて計算された動きベクトルを利用して、動き推定ルーチンを初期化することが可能な検索スペース内の位置、すなわち、この動き推定ルーチンが始動する検索スペース内の画素位置を特定する。例えば、平均画素位置、中央画素位置または、重み付け関数を用いて計算された画素位置は、エンコーディングされる現行のビデオブロックに空間的に非常に近接しているビデオブロックに対して前に決定された動きベクトルに基づいて計算される。他の線形または非線形の関数を用いることも可能である。いずれの場合も、このように動き推定ルーチンを初期化することによって、エンコーディングされているビデオブロックにとって容認可能な適合である検索スペース内のビデオブロックを突き止めるのに必要とされる逐次代入におけるタスクの数を減少させて、ダイアモンド検索シナリオまたは円検索シナリオでのビデオエンコーディングを加速する。

[0048]

差分値を発生するために用いられる計算には、SAD技法や、SSD技法や、必要に応じて他の比較技法が実施される。SAD技法には、現行のマクロブロックが比較されている相手の以前のマクロブロックの画素値でエンコーディングされる、現行のマクロブロックの画素値同士間の絶対差分の計算を実行するタスクが伴う。このような絶対差分計算の結果が合計され、すなわち、累積されて、現行のマクロブロックと、この現行のビデオブロックが比較されている相手の以前のマクロブロックとの間の差を示す、差分値を定義する。8×8画素の像ブロックの場合、64の差が計算されて合計され、16×16画素マクロブロックの場合、256の差が計算されて合計され、16×10をアドレス指定して、特定の順序で計算を実行することによって、256の差が計算されるが、これはまた、4つの互いに分離した集合で合計され、これで、各マイクロブロックの差分値を定義することが可能である。

[0049]

差分値が低いということは、一般に、現行のマクロブロックと比較されているマクロブロックは、より高い差分値、すなわち、より大きい歪みを生じる候補マクロブロックよりも動き推定エンコーディングで用いられるのにより良好な適合であり、従って、より良好な候補であることを示すものである。場合によっては、累積された差分値が所定の閾値を超えると、計算が終了する。その場合、追加の計算は不要であるが、それは、現行のビデオブロックと比較されているマクロブロックは、動き推定エンコーディングで効果的に用いられるものとは容認されないからである。

[0050]

SSD技法にも、現行のマクロブロックが比較されている相手の以前のマクロブロックの画素値でエンコーディングされる現行のマクロブロックの画素値同士間の差分の計算を実行するタスクが伴う。しかしながら、SSD技法においては、絶対差分の計算の結果は二乗され、次に、この二乗された値は合計され、すなわち、累積されて、現行のマクロブロックとこのマクロブロックが比較されている相手の以前のマクロブロックとの間の差を示す差分値を定義する。代替例では、平均二乗誤差(MSE)や、正規化相互相関関数(NCCF)や、他の適切な比較アルゴリズムなどの他の比較技法が実行される。

[0051]

場合によっては、例えば、所与のタスクが以前のタスクより良好な適合を生じないと判定されたら、または、所与のタスクが容認可能な適合を生じると識別されたら早期に様々なタスクや逐次代入を終了させる。例えば、所与のタスクに対する追加の計算が不要となったときを識別する技法を用いることが可能である。より具体的には、第2のタスクの計算の部分集合が合計で、以前に計算された第1のタスクと関連する差分値より大きい差分値を生じる場合、一般的に、第2のタスクに対する追加の計算は不必要であることが分かるが、その理由は、第2のタスクが完了すると、その結果、第1のタスクより低い差分値が得られるからである。その場合、第2のタスクがエンコーディングの性能を犠牲にすることなく終了させることが可能であり、また、第3のタスクの実行をより迅速に開始する

20

30

40

50

ことが可能である。

## [0052]

終了技法もまた、逐次代入レベルで、またはタスクレベルと逐次代入レベルの双方で実行される。一実施形態では、逐次代入閾値が、容認可能な、すなわち、ビデオエンコーディングを効果的に実行するに適切な値を定義する。その場合、逐次代入閾値によって容認可能であるとみなされるような仕方でエンコーディングされる現行のビデオブロックに適合する検索スペース中の候補ビデオブロックを識別するタスクを実行すると、その逐次代入を終了させることが可能であり、また、エンコーディングする次のビデオブロックを検索スペースと比較することが可能である。その場合、多くの不必要なタスクの実行を回避することが可能である。

[0053]

本明細書における技法の多くは、エンコーディングされるビデオブロックを以前のビデオフレームの以前のビデオブロックと比較する状況で説明される。しかしながら、エンコーディングされるビデオブロックを後続のビデオフレームの候補ビデオブロックと比較する際にも同じ技法が用いられることが理解されよう。場合によっては、双方向性の動き推定を用いるが、ここで、エンコーディングされるビデオブロックは、1つ以上の以前のビデオフレームの様々な候補ビデオブロックと、後続のビデオフレームの様々なビデオブロックと比較される。端的に言えば、本明細書に記載する多くの技法が、エンコーディングされるビデオブロックが、以前のビデオフレームの候補ビデオブロックなどの別のビデオブロックと比較されているときには、いつでも用いられる。すなわち、検索スペースに、互いに異なった様々な候補をロードする。

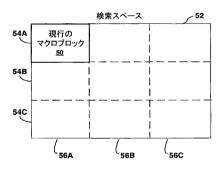

[0054]

図5は、候補マクロブロックの配列として配置された例示の検索スペース52内でエンコーディングされる、現行のマクロブロック50の概念図である。特に、図5に示すように、検索スペース52は、エンコーディングされるマクロブロック50と比較するための、候補マクロブロックの3つのロー54Aから54Cと、3つのカラム56Aから56Cを含んでいる。従って、図5の例では、検索スペース52は、16×16画素マクロブロックを9個備え、48×48の画素からなるエリアを形成している。エンコーディングされる現行のマクロブロック50は、検索スペース52中のマクロブロックと、差分プロセッサ34を用いて比較される。

[0055]

ビデオメモリ32と候補メモリ38及び関連する処理オーバヘッド間のメモリ転送を減少させるために、一旦検索スペース52が初期にロードされたら、検索スペースに対する後続の更新が、必要に応じて、カラム毎に実行される。例えば、所与のフレームの後続のマクロブロックをエンコーディングするのに、メモリ制御ユニット39は、検索スペース52全体を再ロードするのではなく、単に、検索スペース52の左側のカラム56A内の候補マクロブロックを置き換えるだけである。

[0056]

カラム毎の更新を実行し、また、動き推定計算を複数の画素に対して並行にそして同時に実行させるため、メモリ制御ユニット39は、ビデオメモリ32と、エンコードメモリ36と、候補メモリ38とに保持されているメモリアドレスの変換のためのアドレスマッピング方式を実行するように構成されている。エンコードメモリ36と候補メモリ38とに対するデータの更新は、ビデオメモリ32との間で、ビデオメモリに直接にアクセスするバス33を介して発生する。バス33を介してこの転送を初期化、制御するために、DSP28はDMEポートを介してバスマスターとして働く。

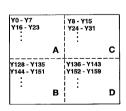

[0057]

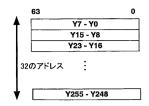

図6Aは、マクロブロックの画素指標を示す図である。図6Aに示すように、マクロブロック画素指標は、4つのマイクロブロック(A、B、C、D)に分割される。このマクロブロック画素指標は16×16構成となっているが、マイクロブロックA、B、C、D

30

40

50

は各々が8×8構成となっている。マクロブロック画素指標全体が、左上画素Y0から右下画素Y255(図示せず)に延長している。この画素指標は、DSP28によって維持されて、検索スペース内でマクロブロックを追跡する。メモリ制御ユニット39は、DSP28によって提供された画素指標を、ビデオメモリ32、エンコードメモリ36または候補メモリ38中の物理的メモリのアドレスに適切に変換する働きをする。例えば、メモリ制御ユニット39は、この変換されたアドレスを候補メモリ38に供給して、検索スペースを更新したり、エンコードメモリ36に供給して、SADエンジン34によってSADを計算させたりする。

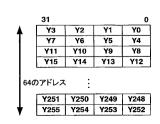

[0058]

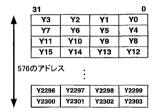

図6Bは、ビデオメモリ32内でのビデオデータの配置を示す図である。特に、図6Bは、DSP28によって保持されるマクロブロック画素指標とビデオメモリ32内のマクロブロック画素データの物理的配置との間の差を示す。図6Bに示すように、ビデオメモリ32は、4つの画素から成るローに配置されている64個のアドレスのところにマクロブロック画素データを記憶して、マクロブロック毎に64のローを生成する。画素当たり8ビットの割合で、各ローは、32ビットのデータを含む。従って、DSP28からの画素指標に応答してビデオメモリ32にアクセスするためには、メモリ制御ユニット39は、この画素指標をビデオメモリ中の物理アドレスに変換する必要がある。

[0059]

図6Cは、エンコードメモリ34内でのビデオデータの配置を示す図である。図6Cに示すように、エンコードメモリ36に記憶されているマクロブロック画素データは、本開に8画素の割合で32個のローに、すなわち、ロー毎に64ビットで配置される。本開示によれば、エンコードメモリ36中のメモリ配置によって、複数の画素に対してる。 一時のから、図6Cの例は、8画素のAD計算を一度にそでででででででででででででででででででである。エンコードメモリ36のを配置によって、マイクロブロックを8回素分のにである。エンコードメモリ36の幅は64ビットである。図6Aから6Cは、共に、である。エンコードメモリ36の幅は64ビットである。図6Aから6Cは、共に、である。エンコードメモリ36の幅は64ビットである。図6Aから6Cは、共に、である。エンコードメモリ36の幅は64ビットである。図6Aから6Cは、共に、どのにしてビデオメモリを差分プロセッサメモリ35中の物理的エンコードメモリ36にしてビデオメモリを表分プロセッサメモリ35中の物理のエンコードメモリ36に

[0060]

図7Aは、DSP28によって保持される検索スペースの画素指標を示す図である。検索スペース内の画素指標は、DSP28によって、検索タスク、例えば、差分プロセッサ34によって発生される結果(差分値)を生じさせるために用いられる計算の集合を指定するのに用いられる。図7Aの検索スペース画素指標は、3マクロブロック×3マクロブロックの検索スペースに対応し、従って、2304画素(3×3×16×16)を含む。図7Aに更に示すように、検索スペース画素指標は、各々が48画素を含む48のローを含む。

[0061]

図7Bは、ビデオメモリ32内での検索スペースの配置を示す図である。図7Bに示すように、検索スペース画素の物理的配置には、図6Bのマクロブロックメモリ配置の場合のようにロー当たり4画素を含んでいる。更に、画素は576個のローに配置されている。1画素当たり8ビットで、4画素から成る各ローは32ビットを含む。

[0062]

図7 C は、候補メモリ3 8 内での検索スペースの配置を示す図である。とりわけ、エンコードメモリ3 6 のように、候補メモリ3 8 は、8 画素から成るローに配置されている。探索スペース全体を記憶するために、候補メモリ3 8 は 2 8 8 のローを含む。すなわち、候補メモリ3 8 は、2 8 8 の 8 バンク x 8 ビットのメモリとして配置される。各ローの幅は6 4 ビットである。エンコードメモリ3 6 はマクロブロックしか記憶せず、また、候補

30

40

50

メモリ38は3マクロブロック幅の検索スペースを記憶して、合計で9個のマイクロブロックを含むが、メモリ36と38はその各々が8画素幅の出力を有する。このようにして、エンコードメモリ36と候補メモリ38とは、エンコーディングされる各マクロブロックを容易に比較できるように、すなわち、8画素の絶対差分値を並列にそして一度に計算しやすくするように配置されている。更に、エンコードメモリ36と候補メモリ38とは、マクロブロック差分値の計算中にマクロブロックの差分値の計算をするように配置されている。

# [0063]

また、複数の画素に対して並列にAD計算をすることを可能とすることに加えて、候補メモリ38は、検索スペース内のどの画素からでもマクロブロックのアドレス指定をすることができるように配置されている。その上、以下に説明するように、候補メモリ38の構造によって、カラムのインクリメンタルな更新、すなわち、エンコーディングされる新しいマクロブロック毎に検索スペース全体を再ロードするのではなく、1カラム分のマクロブロックを一度にロードすることが可能となる。このようなロード技法によって、冗長なメモリ負荷を回避し、バス33の使用を軽減することによって電力を減少させることが可能である。また、メモリ制御ユニット39を装備して、検索スペース画素指標をビデオメモリ32内の物理的メモリアドレスに変換し、次に、ビデオメモリからのメモリアドレスを候補メモリ38中の対応する物理的メモリアドレスに変換する。

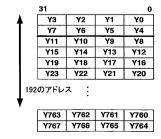

# [0064]

図8Aは、マクロブロックのカラム画素指標を示す図である。エンコーディングされる、隣り合った2つのマクロブロックの場合、適応可能な検索スペース間の差はこれらマクロブロックの内の1つだけである。その結果、たった1つのマクロブロックのカラムを更新する必要があるだけである。候補メモリ38は、この態様を利用して、ビデオメモリ32と候補メモリとの間の転送に必要とされるデータ帯域幅を減少させるように配置されている。図8Aに示すように、DSP28によって保持されるマクロブロックカラム画素指標は、16画素から成るローに配置されて、検索スペース中で1つのカラム、すなわち、48のローの長さにわたって延長する。このように、図8Aに示すマクロブロック画素指標の1/3に対応する。

## [0065]

マクロブロックカラム画素指標のビデオメモリ32中の物理的メモリ配置もまた、検索スペース画素指標全体のメモリ配置とは異なる。図8Bは、ビデオメモリ32内でのマクロブロックのカラムの配置を示す図である。マクロブロックカラムの場合、ビデオメモリ32は、それぞれが4画素から成るローを192個提供する。従って、ビデオメモリ32は、マクロブロックのカラムを32ビット幅で配置する。一旦検索スペースが、最初のマクロブロックのために候補メモリ38中にロードされると、エンコーディングされる後続の隣接したマクロブロックに対する検索を、単に新しいカラムをロードするだけで実行することが可能である。

# [0066]

カラムの更新中、メモリ制御ユニット39は、前の左側のマクロブロックカラムを新しいマクロブロックカラムと交換する。次に、この新たにロードされたマクロブロックカラムは、現行の右側のマクロブロックカラムとして指定され、前の右側のマクロブロックカラムは新しい中央マクロブロックカラムとして指定される。

#### [0067]

従って、検索スペースは、より大きいビデオフレーム内の右にシフトして前にあった左側のマクロブロックカラムが消えて、これで、新しい右側のマクロブロックカラムのための場所を空けたものとみなすことが可能である。このカラム更新動作に続いて、候補メモリ38中の検索スペースは、エンコードメモリ36中の次のマクロブロックを考慮するのに適している。

30

40

50

[0068]

DSP28によって提供される画素指標をメモリ制御ユニット39内のビデオメモリ32と候補メモリ38中の物理アドレスに変換することによって、DSPは、カラムシフト動作を追跡する必要がないことになる。その結果、DSP28は、単に、新しい右側のマクロブロックカラムの画素指標を提供する必要があるだけである。

[0069]

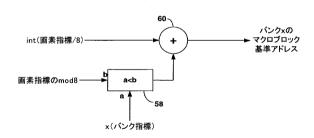

図9は、画素指標を候補メモリ38中のメモリバンクの基準アドレスに変換するのに用いられる、メモリ制御ユニット39の一部を形成する例示の回路を示すブロック図である。図9に示すように、メモリ制御ユニット39は、エンコードメモリ36の更新、候補メモリ38の更新もしくは完全ロードまたは、差分プロセッサ34がエンコードメモリと候補メモリとの内容に対する並行AD計算を実行する検索タスクなどの現行の逐次代入を追跡する。以下に説明するように、メモリ制御ユニット39はまた、検索中にブロック境界を追跡し、候補メモリ38中でのマクロブロックカラムシフトを管理し、画素からアドレスへの変換を実行する。

[0070]

一般に、検索するために、メモリ制御ユニット39は、対応する画素の開始バンク、すなわち、候補メモリ38中の8画素から成るロー内の位置を次式に従って決定する。

開始画素のバンク = mod 8 (画素指標) (1)

更に、メモリ制御ユニット39は、次式に従って開始画素のローを決定する。

[0071]

開始画素のI - = i n t ( 画素指標 / 8 ) (2)

このように、mod関数(1)によれば、開始バンクは、画素指標を8で除算した残余である。整数分割関数(2)によれば、開始ローは画素指標で除算し得る最大の整数である。

式(1)と式(2)とを上記のように仮定すると、それぞれのバンク×の開始アドレス 、すなわち、「基準」アドレスは次式で表すことが可能である。

[0072]

である。

バンク×の基準アドレス = x > = 開始画素のバンクであれば、開始画素のローであり、

x < 開始画素のバンクであれば、開始画素のロー+ 1 (3)

図9に示すように、メモリ制御ユニット39内の比較器58は、画素指標(画素指標のmod8)によって示されるローをバンク指標と比較して、画素指標がバンク指標未満であれば1という出力を発生し、画素指標がバンク指標以上であれば0という出力を発生する。次に、メモリ制御ユニット39内の加算器60は、比較器58の出力である1か0を、画素指標(int(画素指標/8))で示されるバンクに加算して、バンク×の基準アドレスを生成する。

[0073]

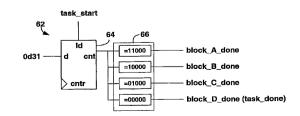

図10は、図3に示すように、マクロブロックを形成する1連のマイクロブロック(A、B、C、D)に対する検索の追跡動作進行状況のビデオブロックカウンタ回路62を示すブロック図である。一旦それぞれのバンクの基準アドレスが決定されたら、メモリ制御ユニット39は、ブロック境界に基づいてアドレス発生カウンタのインクリメンタルな更新と再ロードを追跡する。図10の例では、ブロックカウンタ回路62は、最初に31という値をロードされて32というカウント値を出力する5ビットカウンタ64を含む。初期化(task\_start)されると、カウンタ64はクロックサイクル毎に1つずつ

カウントアップする。しかしながら、カウントダウンするカウンタを用いてもよい。

#### [ 0 0 7 4 ]

カウント値が0b11000に達すると、判断論理66は、差分プロセッサ34によって実行される検索が、マイクロブロックAのAD計算を完了したことを示す。同様に、カウント値が0b100100、0b0100、0b0000となると、それは、マイクロブロックB、C、Dがそれぞれ完了したことを示す。カウント値が0b0000に達すると、所与のマクロブロックの検索が完了(task\_done)したことになる。このようにして、ブロックカウンタ回路62は、差分プロセッサ34で取り扱われている現行のマクロブロックの差分値の計算の進行状況を探索する。更に、ブロックカウンタ回路62は、各マイクロブロックと関連する差分値がいつ計算されたかを判定することが可能である。

#### [0075]

マイクロブロックの境界を越えるたびに、判断論理66は、差分プロセッサ34に個々のマイクロブロックの結果をラッチするように命令するblock\_done信号を発生する。従って、ビデオエンコーダ18は、各々の個別のマイクロブロックの差分値結果と、マクロブロックの差分値結果とを発生する。その上、これらの差分結果は、それぞれ同じ計算を用いて発生される。すなわち、4つの別個の計算の部分集合で、マイクロブロックの各差分値を発生し、これら計算の全てを合計して、マクロブロックの差分値を発生する。

## [0076]

上述したように、終了技法を追加して、様々なタスクや逐次代入を終了させて、ある種のシナリオにおける計算を回避する。1つの実現例では、タスクを終了させるかどうかは、並行AD計算の各集合が実行された後で判断することが可能である。すなわち、マイクロブロックのローをラッチする毎に、タスクの閾値を超えたかどうかを判定する良いタイミングが与えられることになる。超えていれば、その特定のタスクに対する追加の計算を終了することが可能であるが、それは、その検索では最低の差分値が得られないことが分かるからである。特に、タスク閾値を超えていれば、候補マクロブロックの部分集合の差分値は、検索スペースのより早い時期の候補マクロブロックに対して計算された差分値をすでに超えている。

# [0077]

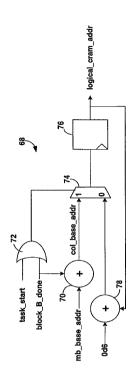

図11は、候補メモリ38中のメモリバンクの物理アドレスマッピング回路68を示すブロック図である。候補メモリ38内の物理アドレスを発生するには、画素指標で発生された基準アドレスを累算器にロードしてから、図9に示すアドレス変換に至るまでの動作が伴う。クロックサイクル毎に、アドレスは48画素だけインクリメントされて、マクロブロック中の次のラインの画素に至り、これが6個のロー(48画素/8バンク)に変換される。ブロックBが完了すると、累算器は、ブロックCとブロックDの計算のために基準アドレス+1を再ロードする。

## [0078]

図 1 1 に示すように、マッピング回路 6 8 は、ブロック B の計算が実行されたら( b 1 o c k \_ b \_ d o n e ) 1 を基準アドレスに加算して( m b \_ b a s e \_ a d d r )、これで、候補メモリ 3 8 内のカラム基準アドレス( c o 1 \_ b a s e \_ a d d r )を生成する、加算器 7 0 を含むことができる。 O R ゲート 7 2 は、ブロック B が実行されたかまたは検索タスクが開始されたら( t a s k \_ s t a r t )、高い論理出力をマルチプレクサ 7 4 に渡す。

#### [0079]

ORゲート72からの高い論理出力に応答して、マルチプレクサ74は、カラム基準アドレスを累算器76に出力する。ORゲート72からの低い論理出力に応答して、マルチプレクサは加算器78の出力を累算器76に渡す。加算器78は、累算器76からの現在の候補メモリアドレス(logical\_cram\_addr)を6という値に加算する。検索タスクの開始もプロックBの完了もない場合、マルチプレクサ74と累算器78は

10

20

30

40

30

40

50

、現在の候補メモリアドレスを 6 個のロー分だけ、すなわち、 8 個のバンクにわたって 4 8 画素分だけ進める。このようにして、ブロック B が完了したり新しい探索タスクが開始されたりすると、メモリ制御ユニット 3 9 は、候補メモリ 3 8 中の 8 バンクから成る各ローを循環して、差分プロセッサ 3 4 に対してマイクロブロックローを一度に 1 つ提示する。従って、計算をロー毎に、マイクロブロックの各差分値が発生されるまで、また、計算をマイクロブロック毎に、マクロブロックの差分値が計算されるまで、実行する。次に、このプロセスは、探索スペースの次のマクロブロックに対してロー毎に、そして、マクロブロック毎に、次から次へと継続される。

[0800]

図12は、候補メモリ中のマクロブロックカラム更新の物理アドレスのマッピング回路80を示すブロック図である。図11に示すアドレスマッピング回路68は、マクロブロックカラム更新が発生するとマクロブロックカラムシフトを取り扱わない。それどころか、マッピング回路68は、完全に再ロードされた検索スペース中のマクロブロックカラムに適応可能である。カラム更新機能を適応すると、図12のアドレスマッピング回路80は、別のレベルのアドレスマッピングを提供する。

[0081]

物理的候補メモリ38では、マクロブロックカラム中の各ローが2つのローのデータに対してマッピングされる。例えば、リセットされると、アドレス0とアドレス1(addr0/1)は、左のマクロブロックカラムの第1のローを表す。特に、アドレス0は、左のマクロブロックカラムの画素指標ロー中の1番目の8画素に対応する候補メモリ38中の8バンクのローを表す。アドレス1は、左のマクロブロックカラムの画素指標ロー中の2番目の8画素に対応する候補メモリ38中の8バンクのローを表す。

[0082]

次に、アドレス 2 とアドレス 3 ( a d d r 2 / 3 )は中央のマクロブロックカラムの第 1 のローを表し、アドレス 4 とアドレス 5 ( a d d r 4 / 5 )は右のマクロブロックカラムの第 1 のローを表す。従って、図 7 C に示すように、候補メモリ 3 8 の 8 バンクから成るローは、各ロー全体(例えば、第 1 のローの Y 0 から Y 4 7 )が左のマクロブロックカラム、中央のマクロブロックカラム及び右のマクロブロックカラムに及ぶ画素データを順次記憶する。

[0083]

1 つのマクロブロックカラムの更新の後で、 a d d r 0 / 1 (以前は左側のマクロブロックカラムを表していた)を用いて右側のマクロブロックカラムを表し、 a d d r 2 / 3 (以前は中央のマクロブロックカラムを表していた)は左側のマクロブロックカラムを表し、a d d r 4 / 5 (以前は右側マクロブロックカラムを表していた)は中央のマクロブロックカラムを表す。

[0084]

このようにして、左右のマクロブロックカラムが同じデータを以前のそれぞれ中央と右側のマクロブロックカラムとして記憶し、これで、新しいデータを再ロードする必要はない。しかしながら、アドレス(addr2/3とaddr4/5)はこの時点で、左側と中央のマクロブロックカラムにマッピングされる。しかしながら、以前の左側のマクロブロックカラムに再マッピングされて、ビデオメモリ32からの新しいデータが再ロードされる。

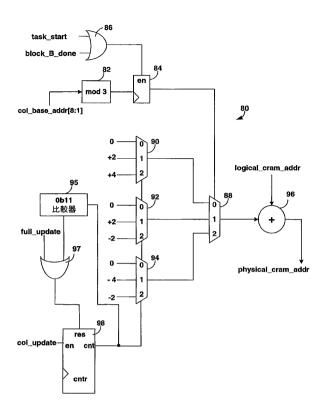

[ 0 0 8 5 ]

カラム更新モードの場合のアドレスマッピングを実行するために、図12のマッピング回路80は、2つの条件を判定する。候補メモリカラム基準アドレス(col\_base\_addr mod3)のmod3出力とマクロブロックカラムシフトステータス、すなわち完全更新が要求されているかかある。

[0086]

図 1 2 に示すように、マッピング回路 8 0 は、現在の基準カラムアドレスを 2 で除算したもの(cram\_addr(8:1))のmod3出力を生成し、このmod3出力を

30

40

50

一時記憶デバイス 8 4 に (フリップフロップと呼ばれる場合がある) に印加するmod3 演算子 8 2 を含んでいる。このmod3出力は、カラム基準アドレスに対して常に0、1 または 2 である。例えば、第 1 のカラムのカラム基準アドレス (Y 0 ) は 0 を生じ、第 2 のカラムのカラム基準アドレス (Y 1 6 ) は 1 を生じ、第 3 のカラムのカラム基準アドレス ス (Y 3 2 ) は 2 を生じる。

## [0087]

新しい検索タスクを開始( t a s k  $\_$  s t a r t ) するか、またはブロック B の計算が実行される( b 1 o c k  $\_$  b  $\_$  d o n e ) と、 O R ゲート 8 6 はフリップフロップ 8 4 をイネーブルして、 m o d 3 演算子 8 2 からの m o d 3 出力を出力してマルチプレクサ 8 8 に印加させるようにする。この m o d 3 出力は、カラム基準アドレスが現在常駐しているカラム、すなわち、第 1 のカラム( 0 )、第 2 のカラム( 1 )または第 3 のカラム( 2 )を示す。

### [0088]

それに応答して、マルチプレクサ88は、マルチプレクサ90、92、94の出力の内の1つを加算器96に回す。マルチプレクサ90、92、94の出力が、2ビットカウンタ98の出力によって判定される。カウンタ98は、fu11\_update信号が受信されるとこれに応答して0という値でリセットされて、候補メモリ38中の検索スペース全体が再ロードされることを示す。イネーブル入力にco1\_update信号が印加されるとそれに応答して、カウンタ98は1つカウントアップする(または、他の実現例の場合、カウントダウンする)。

## [0089]

col\_update信号は、候補メモリ38中の検索スペースは、1つの新しいカラムをロードすることによってインクリメンタルに更新されることを示す。カウンタ98は、カラムが更新される毎にまたはカラムが2回更新される毎にインクリメントされ、3回目のカラム更新の後で0という値に戻る。例えば、カウンタ98は、0 1 2 0 1 2 0 1 2 0 1 5 0 1 2 0 1 6 0 0 x 1 1 になるとリセットされ、このリセット動作はイネーブル状態とは無関係に発生する。

# [0090]

いずれの場合でも、カウンタ98のカウント出力は、カラムシフトがインクリメンタルなカラム更新ルーチンの経過中に何回実行されたかを追跡するものである。カウンタ98のカウント出力は、マルチプレクサ90、92、94に対する論理入力となり、アドレスマッピングの判定が容易となる。マルチプレクサ90、92、94は、検索スペースのそれぞれ左、中央、右のカラムに対応している。カウント出力が0であれば、マルチプレクサ90、92、94の出力値はそれぞれ+2、+2、-4である。カウント出力が2であれば、マルチプレクサ90、92、94の出力値はそれぞれ0、-4、+2である。更に、カウント出力は0b11比較器95に提供され、この比較器は信号をORゲート97に出力する。従って、カウンタ98のリセットは、どちらもORゲート97への入力であるfu11\_update信号または比較器95からの信号のどちらかに応答して発生し得る。

#### [0091]

マルチプレクサ90、92、94のこの動作は、前の中央のカラムが左側のカラムにシフトすることと、前の右側のカラムが中央のカラムにシフトすること、すなわち、どちらの場合も左側に2つのロー分だけ(+2)シフトすることを反映している。マクロプロックカラム中の各ローは、候補メモリ38中の2つのローで表される(図7Cを参照)ことを思い出されたい。この動作はまた、前の左側のカラムが右側のカラムにシフトする、すなわち、左側に4つのロー分だけ(-4)シフトすることを反映している。3回カラムが更新された後では、アドレスが再度物理的メモリに適合し、従って、マルチプレクサ90、92、94の出力値は、それぞれ0、0、0に戻る。

20

30

40

50

## [0092]

マルチプレクサ90、92、94の出力は、シーケンス中の次のシフトを反映する。二回目のシフトの後では、オリジナルの中央カラムはすでに左側のカラムにシフトしており、現在では、右側のカラムにシフトしており、オリジナルの右側のカラムは現在では、左側のカラムにシフトしており、オリジナルの左側のカラムは現在では、中央のカラムにシフトしている。この場合、現在の左側のカラムは、+4ローだけ右側カラム中のそのオリジナルの位置から隔たっており、現在の右側のカラムは、-2ローだけ中央のカラム中のそのオリジナルの位置から隔たっている。

#### [0093]

フリップフロップ84の出力が0であれば、第1のカラムマルチプレクサ90の出力はマルチプレクサ88を通過する。フリップフロップ84の出力が1または2であれば、それぞれ第2または第3のカラムマルチプレクサ92、94の出力はマルチプレクサ88を通過する。いずれの場合も、マルチプレクサ88の出力は加算器96に印加され、この加算器は出力を候補メモリの論理アドレスに加算する(1ogica1\_cram\_addr)。

## [0094]

このようにして、加算器96は、カラム更新シフトのステータスと釣り合った分量だけ候補メモリの論理アドレスをシフトして、適当なマクロブロックの候補メモリの物理アドレスを得る。この論理アドレスはシフト動作の結果として右側のカラムに対応しているが、物理アドレスは実際には中央のカラムに対応して、マッピング回路80は、必要なアドレス変換を実行する。次に、メモリ制御ユニット39は、差分プロセッサ34に対して、候補メモリ38中の正しくアドレス指定されたデータをエンコードメモリ36中の対応するデータと比較させる、例えば、8個の出力バンクにわたって並行AD計算を実行する。

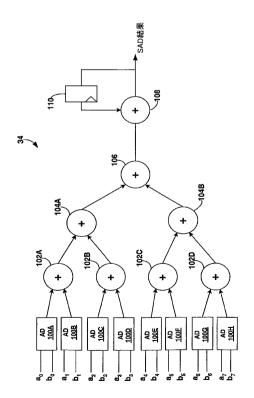

## [0095]

図13は、差分プロセッサ34をより詳細に示すブロック図である。特に、図13は、8個のバンク出力を同時に生成するエンコードメモリ36と候補メモリ38との配置によって提供される並行計算機能を示している。図13に示すように、差分プロセッサは、複数の絶対差分(AD)計算チャネル100Aから100H(まとめて100)を含むことができる。各AD計算チャネル100は、エンコーディングされるマクロブロックに対するエンコードメモリ36からのそれぞれのバンク出力(a0からa7)を受信する。

# [0096]

絶対差分の比較と計算のため、各AD計算チャネル100もまた、候補メモリ38から対応するバンク出力(b0からb7)を受信する。このADの結果は、カスケード式にと備されている8ビット加算器102Aから102Dの集合と、9ビット加算器104A は104Bの対と、10ビット加算器106とによって合計される。大きいビット値算器106を表せば、大きい加算器108はそれ自身の出力を、カリップ110を介して、加算器106の出力を合計して、絶対差分の和(SAD)という結果を生成する。8個の入力(a0からa7)の各集合は、8画素から成るローのマイクロブロックBのの入力(a0からa7)の各集合は、8回素から成るローのマイクロブロックBののの入がに、マイクロブロックAのロー毎に(図6A)、次に、マイクロブロックBのロー毎に(次に、マイクロブロックトカーを差分プロセッサに提供する。累積値は、各マイクロブロックに対する差分測定基準に対応する累積値の合計を再びラッチすることが可能である。

# [0097]

その上、それぞれラッチする毎に、タスクを終了させるべきであるかどうかの判定を下すことが可能である。すなわち、マイクロブロックのローをラッチする毎に、タスクの閾値を超えたかどうかを判定する良いタイミングが提供される。超えていた場合、その特定のタスクに対する追加の計算を終了させることが可能であるが、それは、その検索では最

30

40

50

低差分値が与えられないことが分かるからである。

## [0098]

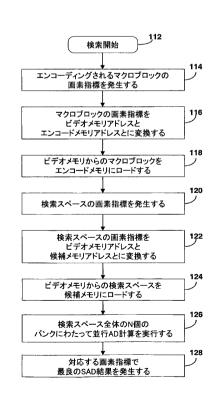

図14は、本明細書に記載するようなビデオエンコーディング技法を示すフローチャートである。図14に示すように、検索が開始されると、すなわち、タスクが開始すると(112)、DSP28は、エンコーディングされるマクロブロックの画素指標を発生する(114)。メモリ制御ユニット39は、このマクロブロック画素指標をビデオメモリアドレスとエンコードメモリアドレスとに変換し(116)、マクロブロックがビデオメモリ32からエンコードメモリ36に対してバス33とメモリ制御ユニットを介してロードされる(118)。DSP28はまた、検索スペースの画素指標を発生する(120)。検索スペース画素指標がビデオメモリアドレスと候補メモリアドレスに変換されると(122)、メモリ制御ユニット39は、候補メモリ38に検索スペースマクロブロックをロードする(124)。

#### [0099]

差分プロセッサ34は、候補メモリ38の複数バンク出力とエンコードメモリ36との間で並行AD計算を実行して(126)、エンコーディングされるマクロブロックを検索スペース内のマクロブロックと比較する。この並行AD計算に基づいて、差分プロセッサ34は、検索スペース全体で最良のSAD結果を発生する(128)(または、場合によっては、完全な検索スペースを考慮することなく容認可能な結果を発生する)。どちらの場合も、結果は、エンコーディングされるマクロブロックの画素指標と関連している。上述したように、差分プロセッサ34はまた、追加のSAD計算を必要とすることなくマクロブロックを形成する各マイクロブロックに対するSAD結果を発生する。マクロブロックを形成する各マイクロブロックに対するSAD結果を発生する。マクロブロックを判定することが可能であり、特定されたら、動きベクトルを記憶して、MPEG-4 圧縮基準に従ってエンコーディングされるマクロブロックを特定することが可能である

## [0100]

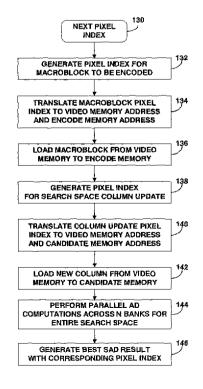

図15は、検索スペースをインクリメンタルにロードするためにカラム更新を用いるビデオエンコーディング技法を示すフローチャートである。別の探索スペースを駆動するために次の画素指標(130、132)をDSP28によって発生したら、メモリ制御ユニット39は、マクロブロック画素指標をビデオメモリアドレスとエンコードメモリアドレスとに変換する(134)。次に、関連するマクロブロックをビデオメモリ32からエンコードメモリ36にロードする(136)。しかしながら、この場合、検索スペースは、検索スペース全体を再ロードするのではなく新しいカラムを追加することによってインクリメンタルに更新される。

## [0101]

従って、DSP28は、検索スペースカラムが更新される毎に画素指標を発生し(138)、次に、これがメモリ制御ユニット39によって変換されて、関連するビデオメモリアドレスと候補メモリアドレスとを生成する(140)。新しいマクロブロックカラムをビデオメモリ32から候補メモリ38にロードすると(142)、差分プロセッサ34は、候補メモリ38とエンコードメモリ36との8個の出力バンクにわたる並行AD計算を実行して(144)、多くの並行AD計算の後で最良のSAD結果(または容認可能なSAD結果)を発生する(146)。

## [0102]

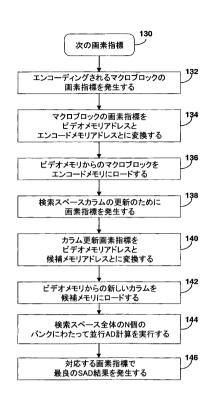

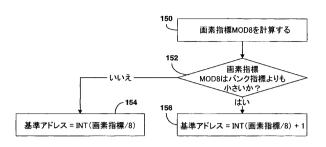

図16は、候補メモリ中のメモリバンクに対する基準アドレスのマッピングを示すフローチャートである。図16に示すプロセスは、図9の回路の動作に対応しているが、この回路の他の変更例を用いてもよい。画素指標から基準アドレスを得るために、メモリ制御ユニット39は、画素指標に対するmod8演算の結果を計算する(150)。この結果が現行のバンク指標以上であれば(152)、基準アドレスは、画素指標を8で除算した整数の商に等しい(154)。その結果が現行のバンク指標未満であれば(152)、基準アドレスは、画素指標を8で除算して1を加算した整数の商に等しい(156)。

## [0103]

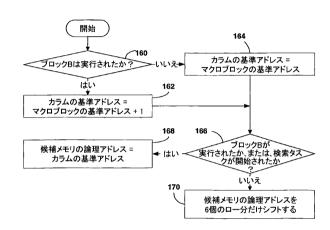

図17は、候補メモリ中のメモリバンクに対する物理アドレスのマッピングを示すフローチャートである。図17に示すプロセスは図11の回路68の動作に対応するが、この回路の他の変更例を用いてもよい。マクロブロック内のブロックBのAD計算が完了したら(160)、候補メモリ38中のカラム基準アドレスは、マクロブロック基準アドレスに1を加算した値に等しい(162)。ブロックBが実行されていなければ(160)、候補メモリ38中のカラム基準アドレスはマクロブロック基準アドレスに等しい(164)。次に、ブロックBが実行されるかまたは新しい検索タスクが開始されたら(166)、候補メモリ38の論理メモリアドレスはカラム基準アドレスに等しい(168)。ブロックBが実行されず、新しい探索も開始されていない場合(166)、候補メモリの論理アドレスは6個のロー分だけシフトされる(170)。

[ 0 1 0 4 ]

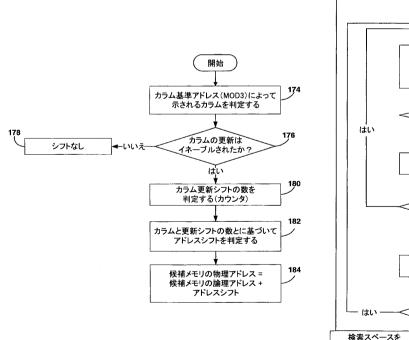

図18は、候補メモリ中でのマクロブロックカラムの更新のための物理アドレスのマッピングを示すフローチャートである。図18に示すプロセスは、図12の回路80の動作に対応しているが、この回路の別の変更例を用いてもよい。図18に示すように、カラム基準アドレスが示すカラムを決定するために、メモリ制御ユニット39はmod3演算をカラム基準アドレスに対して適用する(174)。カラム更新機能がイネーブルされなければ(176)、候補メモリの論理アドレスはシフトされない(178)。これは、図12のマルチプレクサ90、92、94からの出力(0、0、0)に対応するが、これは、カウンタ98からの0というカウンタ出力に、従って、マルチプレクサ88からの0の出力に対応している。

[ 0 1 0 5 ]

カラム更新がイネーブルされると(176)、メモリ制御ユニット39は、発生したカラム更新シフトの数をカウンタ98の出力を参照して判定する(180)。特定されたカラムとカラム更新シフトの数に基づいて、メモリ制御ユニット39は、候補メモリの論理アドレスをシフトすべき分量を決定して、正確な候補メモリの物理アドレスを生成する(182)。次に、メモリ制御ユニット39は、アドレスシフトを適用することによって、この候補メモリの論理アドレスを候補メモリの物理アドレスに変換する(184)。

[0106]

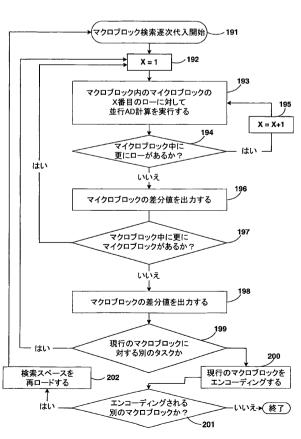

図19は、マクロブロックと、このマクロブロックを形成する多くのマクロブロックの差分値を、同じ計算量で発生する様子を示すフローチャートである。図示するように、動き推定器29がマクロブロック検索逐次代入を開始すると(191)、差分プロセッサ34は、マイクロブロックのロー毎に並行絶対差分(AD)計算を実行する。例えば、値Xを初期化することが可能であり(192)、また、差分プロセッサ34は、エンコーディングされているマクロブロック内の第1のマイクロブロックのX番目のローに並行AD計算を実行することが可能である(193)。マイクロブロック中にまだローがあるかぎり(194ではい)、値Xはインクリメントされ(195)、並行AD計算がマイクロブロックの次のローに対して実行される。

[0107]

ビデオブロックカウンタ回路62は、マイクロブロック中にまだローがあるかどうか判定することが可能である(194)。例として、ビデオブロックカウンタ回路62は、差分プロセッサ34の一部として組み込むことが可能であったり、DSPインタフェースユニット30の一部を形成したりする。AD計算が第1のマイクロブロックの全てのローに対して実行されたと判定されたら、差分プロセッサ34は、第1のマイクロブロックの差分値を出力する(196)。このプロセスは、マイクロブロックがなくなるまでマクロブロックの全てのマイクロブロックに対して継続することが可能である(197)。タスク終了技法がまたプロセスのこの段階で用いられて、例えば、累積された全体の差分値が、現行の逐次代入に対してすでに計算された最低の差分値に対応する閾値などのタスク閾値を超えたら、タスクを終了させる。

[0108]

50

10

20

30

20

30

40

50

差分プロセッサ34は、マクロブロックの現行の差分値を累積することが可能であり、また、各マイクロブロックの計算が実行されるにつれて各マイクロブロックの差分値を出力することができる。第1のマイクロブロックの差分値は、その時点までの差分値の累積値である。第2のマイクロブロックの差分値は、その時点までの累積合計値から第1のマイクロブロックの差分値を減算した値に対応する。第3のマイクロブロックの差分値は、その時点までの累積合計値から第1と第2のマイクロブロックの差分値を減算した値に対応する、・・・、という具合である。

# [0109]

ビデオブロックカウンタ回路62はまた、最後のマイクロブロックの計算が累積されたか(197ではい)判定する。その時点で、差分プロセッサ34は、その時点までのAD計算の累積合計値であるマクロブロックの差分値を出力する(198)。DSP28は、又は場合によってはDSPインタフェースユニット30は、エンコーディングされる現行のマクロブロックに対して実行すべき別のタスクがあるかどうか、マイクロブロック中に更にローがあるかどうか判定することが可能である(194)。また、タスクとは、エンコーディングされる現行のビデオブロックを検索スペース中のビデオブロックと比較するために用いられる計算の集合のことであり、逐次代入とは、検索スペースの互いに異なった様々なビデオブロックとエンコーディングされる現行のビデオブロックとの比較に対応するタスクの集合のことである。

## [0110]

逐次代入は、検索スペースのビデオブロックの所定の集合をエンコーディングされるビデオブロックと比較するのと同じほど簡単であるか、または、それよりはるかに複雑で、検索スペース内の位置を突き止める初期化技法、ネスティングされた検索及び / または、可能な限り迅速な最良の適合を突き止める定義されたり再定義されたりした検索パラメータを含む。いずれの場合も、動き推定器 2 9 が逐次代入の全てのタスクを実行したら(199でいいえ)、ビデオエンコーダ 1 8 は、現行のマクロブロックをエンコーディングする(200)。ビデオエンコーダが、検索スペースの様々な候補マクロブロックの差分値が発生され、また、この候補を形成するマイクロブロックの差分値もまた発生されたときに、エンコーディングプロセスに様々なオプションがあれば有利である。

# [0111]

最良の候補マイクロブロックに対応する4つの別個の動きベクトルを用いてマクロブロックをエンコーディングすれば、圧縮動作が改善される。しかしながら、マクロブロック動きベクトルを認識するだけのデコーダに対する準拠性が維持されるなどの、他の理由によって、最良の候補マクロブロックに対応する単一の動きベクトルを用いることが望まれる。エンコーディングされる現行のマクロブロックと動きベクトルによって定義されるビデオブロックとの間の差を定義するマトリックスに対して離散コサイン変換(DCT)エンコーディングを実行するなどして、テクスチャエンコーディングもまた追加されることができる。

## [0112]

現行のマクロブロックがエンコーディングされたら、ビデオエンコーダ18は、現行のビデオフレームに対してエンコーディングされる別のマクロブロックが存在するかどうかりでなわち、実行すべき別の逐次代入が存在するかどうか判定する(201)。存在しないれば、所与のビデオフレームに対するエンコーディングプロセスは完了した(201でいいえ)ことになり、そのフレームに対するエンコーディング済みビデオブロックがあれば、現行のビデオフレームに対して送信することが可能である(図1)。しかしながら、境索スペースを再ロードすることが可能であり(202)、また、次の逐次代入が開始である(191)。その上、検索スペースを再ロードするプロセス(202)では、ボーリ制御ユニットが候補メモリ38のカラムの部分集合を再ロードして、本明細書に概括したようなアドレス指定方式によって候補メモリを追跡する、上記に概括したよカラム更新技法が利用される。本明細書に概括するようなこのような技法や他の技法は、様々

な従来のエンコーディングプロセスを改善するために単独で用いられようと他と組み合わ せて用いられようと、MPEG-4などの基準にしたがったビデオエンコーディング技法 の効率を改善し、また、計算リソースがより限られ、また、消費電力が関心事となる携帯 電 話 な ど の 無 線 通 信 デ バ イ ス 内 で の ビ デ オ エ ン コ ー デ ィ ン グ の 実 施 を よ り 容 易 な も の と す る。

[0113]

様々な多くの実施形態を説明した。上記の技法は、メモリ転送、計算サイクル及び消費 電力を軽減することによってビデオエンコーディング動作を改善し、これで、エンコーデ ィングプロセスを高速化し、場合によっては、バッテリ式のビデオデバイスの寿命を延長 することが可能である。更に、これらの技法は、追加のAD計算を必要とすることなく、 マ ク ロ ブ ロ ッ ク と マ イ ク ロ ブ ロ ッ ク の 差 分 値 を 発 生 す る こ と に よ っ て エ ン コ ー デ ィ ン グ プ ロセスのオプションを提供する。このような方法によって、場合によってはこれ以外の方 法によって、これらの技法は、MPEG-4などの基準や他のビデオエンコーディング基 準によるビデオエンコーディング動作を改善することが可能である。

[ 0 1 1 4 ]

これらの技法は、ハードウエア、ソフトウエア、ファームウエアまたはこれらの任意の 組み合わせで実現される。ソフトウエアで実現する場合、上記の技法は、MPEG-4基 準に準拠したビデオシーケンスをエンコーディングするデバイス中で実行されると、上記 の方法を1つ以上実行するプログラムコードを備えるコンピュータ読み取り可能媒体を志 向する。その場合、このコンピュータ読み取り可能媒体は、同期式ダイナミックランダム アクセスメモリ(SDRAM)などのランダムアクセスメモリ(RAM)や、読み出し専 用メモリ(ROM)、不揮発性ランダムアクセスメモリ(NVRAM)、電気的に消去可 能なプログラム可能読み出し専用メモリ(EEPROM)、フラッシュメモリ等を備える

[0115]

上記のプログラムコードは、コンピュータ読み取り可能な命令という形態でメモリに記 憶される。その場合、DSPなどのプロセッサは、メモリに記憶されている命令を実行し て、本明細書に記載する1つ以上の技法を実行する。これらの技法は、動き推定器などの 様 々 な ハ ー ド ウ エ ア コ ン ポ ー ネ ン ト を 発 動 し て 、 エ ン コ ー デ ィ ン グ プ ロ セ ス を ス ピ ー ド ア ップするDSPによって実行される場合もある。ビデオエンコーダが、マイクロプロセッ サ、 1 つ以上の特定用途向け集積回路 ( A S I C ) 、 1 つ以上のフィールドプログラム可 能 ゲ ー ト ア レ イ ( F P G A ) ま た は 他 の 任 意 の ハ ー ド ウ エ ア ・ ソ フ ト ウ エ ア の 組 み 合 わ せ として実現される場合もある。上記の実施形態や他の実施形態は、特許請求の範囲内にあ る。

【図面の簡単な説明】

[0116]

【 図 1 】ディジタルビデオソースデバイスが、エンコーディングされたビデオデータのシ ー ケン ス を デ ィ ジ タ ル ビ デ オ 受 信 デ バ イ ス に 送 信 す る 例 示 の シ ス テ ム 例 を 示 す ブ ロ ッ ク 図 である。

【 図 2 】 ディジタルビデオシーケンスをエンコーディングするビデオエンコーダを示すブ ロック図である。

【 図 3 】 ビ デ オ デ ー タ の 例 示 の マ ク ロ ブ ロ ッ ク の 概 念 図 で あ る 。

【 図 4 】 例 示 の 検 索 スペース の 概 念 図 で あ る。

【 図 5 】 マクロブロックの配列として配置された検索スペース上で概念的にエンコーディ ングされるマクロブロックの概念図である。

【図6A】マクロブロックの画素指標を示す図である。

【図6B】ビデオメモリ内でのビデオデータの配置を示す図である。

【図6C】エンコードメモリ内でのビデオデータの配置を示す図である。

【 図 7 A 】 検 索 ス ペ ー ス の 画 素 指 標 を 示 す 図 で あ る 。

【図7B】ビデオメモリ内での検索スペースの配置を示す図である。

20

30

40

20

30

- 【図7C】候補メモリ内での検索スペースの配置を示す図である。

- 【図8A】マクロブロックのカラム画素指標を示す図である。

- 【図8B】ビデオメモリ内でのマクロブロックのカラムの配置を示す図である。

- 【 図 9 】 画 素 指 標 を 候 補 メ モ リ 中 の メ モ リ バ ン ク の 基 準 ア ド レ ス に 変 換 す る 様 子 を 示 す ブ ロック図である。

- 【 図 1 0 】 マクロブロックを形成する 1 連のブロックに対する検索の追跡動作進行状況の ブロックカウンタを示すブロック図である。

- 【図11】候補メモリ中のメモリバンクの物理アドレスのマッピングを示すブロック図で ある。

- 【図12】候補メモリ中のマクロブロックカラム更新の物理アドレスのマッピングを示す ブロック図である。

- 【図13】差分プロセッサを示すブロック図である。

1 1 0 ... フリップフロップ、 2 0 0 0 ... J P E G

- 【図14】ビデオエンコーディング技法を示すフローチャートである。

- 【図15】検索スペースにインクリメンタルにロードするためにカラム更新を用いるビデ オエンコーディング技法を示すフローチャートである。

- 【 図 1 6 】 候 補 メ モ リ 中 の メ モ リ バ ン ク に 対 す る 基 準 ア ド レ ス の マ ッ ピ ン グ を 示 す フ ロ ー チャートである。

- 【図17】候補メモリ中のメモリバンクに対する物理アドレスのマッピングを示すフロー チャートである。

- 【図18】候補メモリ中でのマクロブロックの更新のための物理アドレスのマッピングを 示すフローチャートである。

- 【図19】マクロブロックと、このマクロブロックを形成する多くのマクロブロックの差 分値を同じ計算量で発生する様子を示すフローチャートである。

## 【符号の説明】

[0117]

10…システム、 12…ソースデバイス、 14…受信デバイス、 15…通信リン ク、 16... ビデオメモリ、 18... ビデオエンコーダ、 20... 送信機、 22... 受信 23…ビデオキャプチャデバイス、 24…ビデオデコーダ、 26…表示デバイ 機、 ス、 28…ディジタル信号プロセッサ、 29…動き推定器、 30…DSPインタフ ェースユニット、 32…ビデオメモリ、 33…バス、 34…差分プロセッサ、 3 5 ... 差分プロセッサメモリ、 3 6 ... エンコードメモリ、 3 8 ... 候補メモリ、 3 9 ... メモリ制御ユニット、 40…制御チャネル、 41…データチャネル、 42…マクロ ブロック、 44A…画素マイクロブロック、 46…検索スペース、 48…マクロブ 50…マクロブロック、 52…検索スペース、 54A…ロー、 56A… ロック、 カラム、 5 8 … 比較器、 6 0 … 加算器、 6 2 … ビデオブロックカウンタ回路、 6 4 ... ビットカウンタ、 6 6 ... 判断論理、 6 8 ... アドレスマッピング回路、 7 0 ... 加 算器、 72…0Rゲート、 74…マルチプレクサ、 76…累算器、 78…加算器 80…アドレスマッピング回路、 82…演算子、 84…一時記憶デバイス(フリ ップフロップ)、 86…ORゲート、 88…マルチプレクサ、 90.92…マルチ プレクサ、 90…第1のカラムマルチプレクサ、 92.94…第3のカラムマルチプ 9 5 ... 比較器、 9 6 ... 加算器、 9 7 ... O R ゲート、 9 8 ... ビットカウン タ、 100A…絶対差分計算チャネル、 100…AD計算チャネル、 102A…ビ ット加算器、 104A…ビット加算器、 1 0 6 ... ビット加算器、 1 0 8 ... 加算器、

【図1】 【図2】

【図3】

【図5】

【図4】

【図 6 A】

【図6B】

# 【図6C】

# 【図7A】

# 【図7B】

# 【図7C】

# 【図8A】

# 【図8B】

# 【図9】

# 【図10】

【図11】

【図12】

【図13】

【図14】

## 【図15】

## 【図16】

# 【図17】

## 【図18】

## 【図19】

# 【国際調査報告】

|                                                                                                              | INTERNATIONAL SEARCH REPOR                                                                                                                                                                                                                                                                                                                                                                                                                     | Т                                                                                                                                                                                                                                                    | in attonal Application No<br>PČT/US 03/19401                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A. CLASSI<br>IPC 7                                                                                           | FICATION OF SUBJECT MATTER H04N7/26 H04N7/50                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                              | o International Patent Classification (IPC) or to both national classifica<br>SEARCHED                                                                                                                                                                                                                                                                                                                                                         | ation and IPC                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Minimum do<br>IPC 7                                                                                          | cumentation searched (classification system followed by classification $H04N$                                                                                                                                                                                                                                                                                                                                                                  | on symbols)                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Documentat                                                                                                   | ion searched other than minimum documentation to the extent that st                                                                                                                                                                                                                                                                                                                                                                            | uch documents are incl                                                                                                                                                                                                                               | uded in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                              | ata base consulted during the international search (name of data bas<br>ternal, WPI Data, COMPENDEX, INSPEC,                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                      | , search terms used)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| с. росим                                                                                                     | ENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Category *                                                                                                   | Citation of document, with indication, where appropriate, of the rela                                                                                                                                                                                                                                                                                                                                                                          | evant passages                                                                                                                                                                                                                                       | Relevant to claim No.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| X                                                                                                            | US 6 122 442 A (PURCELL STEPHEN C<br>19 September 2000 (2000-09-19)<br>column 5, line 6 -column 5, line<br>column 23, line 15 -column 25, li<br>column 34, line 55 -column 36, li<br>column 37, line 53 -column 41, li<br>figures 10A-10D,16D-16E,18D-18F2                                                                                                                                                                                     | 61<br>ne 36<br>ne 27<br>ne 30                                                                                                                                                                                                                        | 1-35                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                | / <sup>'</sup>                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ì                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| X Furti                                                                                                      | ner documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                         | χ Patent family                                                                                                                                                                                                                                      | members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| "A" docume consid "E" earlier of filing d "L" docume which i citation "O" docume other i "P" docume later in | ont defining the general state of the art which is not ered to be of particular relevance occument but published on or after the international ate of the published on the published on the published on the published on the published to establish the publication date of another or or other special reason (as specified) and the published prior to the international filips of the published prior to the international filips date but | or priority date an cited to understar invention "X" document of partic cannot be conside involve an inventi "Y" document of partic cannot be conside document is comments, such comin the art.  "&" document member "&" document member in the art. | olished after the international filing date do not in conflict with the application but do the principle or theory underlying the subar relevance; the claimed invention ered novel or cannot be considered to ve step when the document is taken alone ular relevance; the claimed invention ered to invalve an inventive step when the bined with one or more other such docuplination being obvious to a person skilled or of the same patent family |

|                                                                                                              | May 2004                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                      | 4. Mai 2004                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Name and n                                                                                                   | nailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL – 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                  | Authorized officer                                                                                                                                                                                                                                   | j, G                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Form PCT/ISA/210 (second sheet) (January 2004)

Inexpational Application No PCT/US 03/19401

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1/05 03/19401                     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|            | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                         | Industrial St. 12                 |

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                 | Relevant to daim No.              |

| х          | HANG H-M ET AL: "MOTION ESTIMATION FOR VIDEO CODING STANDARDS" JOURNAL OF VLSI SIGNAL PROCESSING SYSTEMS FOR SIGNAL, IMAGE, AND VIDEO TECHNOLOGY, KLUWER ACADEMIC PUBLISHERS, DORDRECHT, NL, vol. 17, no. 2/3, 1 November 1997 (1997-11-01), pages 113-136, XP000724575 ISSN: 0922-5773 abstract page 128, right-hand column, paragraph 2 -page 131, left-hand column, paragraph 1                                                                                 | 1-5,<br>9-15,<br>21-24,<br>28-32  |

| X          | YOSHINO T ET AL: "A 54MHz Motion Estimation Engine for Real-Time MPEG Video Encoding" DIGEST OF TECHNICAL PAPERS OF THE INTERNATIONAL CONFERENCE ON CONSUMERELECTRONICS (ICCE), 21 - 23 June 1994, pages 76-77, XPO10218282                                                                                                                                                                                                                                        | 1,5,9,<br>13-15,<br>28,32         |

| A          | New York page 76, left-hand column, paragraph 3 -right-hand column, last paragraph; figures 1-3                                                                                                                                                                                                                                                                                                                                                                    | 2-4,<br>10-12,<br>21-24,<br>29-31 |

|            | KUHN P M ET AL: "A flexible VLSI architecture for variable block size segment matching with luminance correction"  APPLICATION-SPECIFIC SYSTEMS, ARCHITECTURES AND PROCESSORS, 1997. PROCEEDINGS., IEEE INTERNATIONAL CONFERENCE ON ZURICH, SWITZERLAND 14-16 JULY 1997, LOS ALAMITOS, CA, USA, IEEE COMPUT. SOC, US, 14 July 1997 (1997-07-14), pages 479-488, XP010236717 ISBN: 0-8186-7959-X abstract page 484, paragraph 1 -page 486, paragraph 1; figures 5-8 | 6-8,<br>16-20,<br>25-27,<br>33-35 |

|            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |

Form PCT/ISA/210 (continuation of second sheet) (January 2004)

In atlanat Application No PCT/US 03/19401

| C (Continu | etion) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                   | <u> </u>                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Category ° | Citation of document, with indication, where appropriate, of the retevant passages                                                                                                                                                                                                                                                                                                                                           | Relevant to claim No.             |

| X          | JAEHUN LEE ET AL: "A new VLSI architecture of a hierarchical motion estimator for low bit-rate video coding" IMAGE PROCESSING, ICIP 99, PROCEEDINGS. INTERNATIONAL CONFERENCE 24-28 OCT. 1999, PISCATAWAY, NJ, USA, IEEE, US, 24 October 1999 (1999-10-24), pages 774-778, XP010369030 Kobe, Japan ISBN: 0-7803-5467-2 abstract page 775, left-hand column, last paragraph -page 777, left-hand column, line 27; figures 4-7 | 6-8,<br>16-20,<br>23-27,<br>33-35 |

| X          | T. WIEGAND: "WORKING DRAFT NUMBER 2, REVISION 0 (W0-2)" DOCUMENT JVT-B118R1, 29 January 2002 (2002-01-29), pages 1-99, XP001086631                                                                                                                                                                                                                                                                                           | 6,16,19,<br>20,25,33              |

| Α .        | Geneva, Switzerland page 70, line 1 -page 73, line 11                                                                                                                                                                                                                                                                                                                                                                        | 7,8,17,<br>18,26,<br>27,34,35     |

| A          | LEHTORANTA O ET AL: "Real-time H.263 encoding of QCIF-images on TMS320C6201 fixed point DSP" ISCAS 2000 - IEEE INTERNATIONAL SYMPOSIUM ON CIRCUITS AND SYSTEMS, vol. 1, 28 - 31 May 2000, pages I583-I586, XPD10503265 Geneva, Switzerland abstract page 585, left-hand column, paragraph 3 -page 586, left-hand column, paragraph 1; figure 2.2                                                                             | 1-5,<br>9-15,<br>21-24,<br>28-32  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |

emational application No. PCT/US 03/19401

| Box I Observations where certain claims were found unsearchable (Continuation of Item 1 of first sheet)                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|