(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4005663号

(P4005663)

(45) 発行日 平成19年11月7日(2007.11.7)

(24) 登録日 平成19年8月31日(2007.8.31)

(51) Int.C1.

F 1

H01L 21/8242 (2006.01)

H01L 27/10 27/10 681G

H01L 27/108 (2006.01)

G11C 11/34 362B

G11C 11/4097 (2006.01)

請求項の数 13 (全 24 頁)

(21) 出願番号

特願平9-119639

(22) 出願日

平成9年5月9日(1997.5.9)

(65) 公開番号

特開平10-313101

(43) 公開日

平成10年11月24日(1998.11.24)

審査請求日

平成16年4月2日(2004.4.2)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100070437

弁理士 河井 将次

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタ及び第2のトランジスタを含む第1のカラムゲートと、

前記第1のトランジスタとの第1の共通ノードを有する第3のトランジスタと、前記第2のトランジスタとの第2の共通ノードを有する第4のトランジスタと、前記第1の共通ノード及び前記第2の共通ノードを有する第5のトランジスタとを含む第1のイコライズ回路と、

第6のトランジスタ及び第7のトランジスタを含む第2のカラムゲートと、

前記第6のトランジスタとの第3の共通ノードを有する第8のトランジスタと、前記第7のトランジスタとの第4の共通ノードを有する第9のトランジスタと、前記第3の共通ノード及び前記第4の共通ノードを有する第10のトランジスタとを含む第2のイコライズ回路と

により単位素子領域を構成し、

前記第3のトランジスタと前記第8のトランジスタとが共通ノードを有し、且つ前記第4のトランジスタと前記第9のトランジスタとが共通ノードを有することを特徴とする半導体記憶装置。

## 【請求項 2】

第1のトランジスタ及び第2のトランジスタを含む第1のカラムゲートと、

前記第1のトランジスタとの第1の共通ノードを有する第3のトランジスタと、前記第2のトランジスタとの第2の共通ノードを有する第4のトランジスタと、前記第1の共通

10

20

ノード及び前記第2の共通ノードを有する第5のトランジスタとを含む第1のイコライズ回路と、

第6のトランジスタ及び第7のトランジスタを含む第2のカラムゲートと、

前記第6のトランジスタとの第3の共通ノードを有する第8のトランジスタと、前記第7のトランジスタとの第4の共通ノードを有する第9のトランジスタと、前記第3の共通ノード及び前記第4の共通ノードを有する第10のトランジスタとを含む第2のイコライズ回路と

を有し、

前記第1のトランジスタは、第1の拡散領域と、前記第1の共通ノードとなる第2の拡散領域と、これら第1の拡散領域及び第2の拡散領域の間に設けられた第1のゲート電極とを含み、10

前記第2のトランジスタは、第3の拡散領域と、前記第2の共通ノードとなる第4の拡散領域と、これら第3の拡散領域及び第4の拡散領域の間に設けられた第2のゲート電極とを含み、

前記第3のトランジスタは、前記第2の拡散領域と、第5の拡散領域と、これら第2の拡散領域及び第5の拡散領域の間に設けられた第3のゲート電極とを含み、

前記第4のトランジスタは、前記第4の拡散領域と、第6の拡散領域と、これら第4の拡散領域及び第6の拡散領域の間に設けられた第4のゲート電極とを含み、

前記第5のトランジスタは、前記第2の拡散領域と、前記第4の拡散領域と、これら第2の拡散領域及び第4の拡散領域の間に設けられた第5のゲート電極とを含み、20

前記第6のトランジスタは、第7の拡散領域と、前記第3の共通ノードとなる第8の拡散領域と、これら第7の拡散領域及び第8の拡散領域の間に設けられた第6のゲート電極とを含み、

前記第7のトランジスタは、第9の拡散領域と、前記第4の共通ノードとなる第10の拡散領域と、これら第9の拡散領域及び第10の拡散領域の間に設けられた第7のゲート電極とを含み、

前記第8のトランジスタは、前記第5の拡散領域と、前記第8の拡散領域と、これら第5の拡散領域及び第8の拡散領域の間に設けられた第8のゲート電極とを含み、

前記第9のトランジスタは、前記第6の拡散領域と、前記第10の拡散領域と、これら第6の拡散領域及び第10の拡散領域の間に設けられた第9のゲート電極とを含み、30

前記第10のトランジスタは、前記第8の拡散領域と、前記第10の拡散領域と、これら第8の拡散領域及び第10の拡散領域の間に設けられた第10のゲート電極とを含むことを特徴とする半導体記憶装置。

#### 【請求項3】

前記第1の拡散領域は第1のデータ線に接続され、前記第2の拡散領域は第1のビット線に接続され、前記第3の拡散領域は第2のデータ線に接続され、前記第4の拡散領域は第2のビット線に接続され、前記第5の拡散領域及び前記第6の拡散領域はイコライズ回路電源線に接続され、前記第7の拡散領域は第3のデータ線に接続され、前記第8の拡散領域は第3のビット線に接続され、前記第9の拡散領域は第4のデータ線に接続され、前記第10の拡散領域は第4のビット線に接続され、40

前記第1、第2、第6及び第7のゲート電極はカラムゲート選択線に接続され、前記第3、第4、第5、第8、第9及び第10のゲート電極はイコライズ回路制御線に接続されていることを特徴とする請求項2に記載の半導体記憶装置。

#### 【請求項4】

前記イコライズ回路電源線の電位はビット線のプリチャージ電位であることを特徴とする請求項3に記載の半導体記憶装置。

#### 【請求項5】

第1のトランジスタ及び第2のトランジスタを含む第1のカラムゲートと、前記第1のトランジスタとの第1の共通ノードを有する第3のトランジスタと、前記第2のトランジスタとの第2の共通ノードを有する第4のトランジスタと、前記第1の共通ノード及び前50

記第2の共通ノードを有する第5のトランジスタとを含む第1のイコライズ回路と、第6のトランジスタ及び第7のトランジスタを含む第2のカラムゲートと、前記第6のトランジスタとの第3の共通ノードを有する第8のトランジスタと、前記第7のトランジスタとの第4の共通ノードを有する第9のトランジスタと、前記第3の共通ノード及び前記第4の共通ノードを有する第10のトランジスタとを含む第2のイコライズ回路により単位素子領域を構成し、

互いに隣り合った前記単位素子領域間に前記第3、第4、第5、第8、第9及び第10のトランジスタの各ゲート電極に接続されるイコライズ回路制御線のパターンを形成したことを特徴とする半導体記憶装置。

**【請求項6】**

第1のトランジスタ及び第2のトランジスタを含む第1のカラムゲートと、前記第1のトランジスタとの第1の共通ノードを有する第3のトランジスタと、前記第2のトランジスタとの第2の共通ノードを有する第4のトランジスタと、前記第1の共通ノード及び前記第2の共通ノードを有する第5のトランジスタとを含む第1のイコライズ回路と、第6のトランジスタ及び第7のトランジスタを含む第2のカラムゲートと、前記第6のトランジスタとの第3の共通ノードを有する第8のトランジスタと、前記第7のトランジスタとの第4の共通ノードを有する第9のトランジスタと、前記第3の共通ノード及び前記第4の共通ノードを有する第10のトランジスタとを含む第2のイコライズ回路により単位素子領域を構成し、

互いに隣り合った前記単位素子領域の一方に含まれる第1のトランジスタと他方に含まれる第6のトランジスタとが共通ノードを有し、且つ互いに隣り合った前記単位素子領域の一方に含まれる第2のトランジスタと他方に含まれる第7のトランジスタとが共通ノードを有することを特徴とする半導体記憶装置。

**【請求項7】**

半導体基板と、

前記半導体基板に形成された素子領域と、

前記半導体基板の上方に形成された第1及び第2のデータ線と、

前記素子領域上に形成された二つの拡散層と第1のゲート電極とを有する第1のトランジスタを備え、前記第1のトランジスタの前記拡散層の一方が前記第1のデータ線に接続された第1の選択ゲートと、

前記素子領域上に形成された二つの拡散層と第2のゲート電極とを有する第2のトランジスタを備え、前記第2のトランジスタの前記拡散層の一方が前記第2のデータ線に接続された第2の選択ゲートと、

第3、第4及び第5のトランジスタを備えたイコライザとを備え、

前記第3のトランジスタは前記素子領域上に形成された二つの拡散層と第3のゲート電極とを有し、前記第3のトランジスタの前記拡散層の一方と前記第1のトランジスタの前記拡散層の他方とが共通化され、前記第3のトランジスタの前記拡散層の他方が電位供給線に接続されており、前記第4のトランジスタは前記素子領域上に形成された二つの拡散層と第4のゲート電極とを有し、前記第4のトランジスタの前記拡散層の一方と前記第2のトランジスタの前記拡散層の他方とが共通化され、前記第4のトランジスタの前記拡散層の他方が前記電位供給線に接続されており、前記第5のトランジスタは前記素子領域上に形成された二つの拡散層と第5のゲート電極とを有し、前記第5のトランジスタの前記拡散層の一方と前記第1のトランジスタの前記拡散層の他方とが共通化され、前記第5のトランジスタの前記拡散層の他方が前記電位供給線に接続されており、前記第5のトランジスタの前記拡散層の他方と前記第2のトランジスタの前記拡散層の他方とが共通化されており、

前記第1のゲート電極と第2のゲート電極とが同一の配線層で構成され、前記第3のゲート電極と第4のゲート電極と第5のゲート電極とが同一の配線層で構成されていることを特徴とする半導体記憶装置。

**【請求項8】**

半導体基板と、

10

20

30

40

50

第1の方向に平行に配置され、それぞれがメモリセルに対してデータ入出力を行う第1及び第2のビット線と、

プリチャージ電位供給線に接続された第1の拡散層と、

前記第1のビット線に接続された第2の拡散層と、

前記第2のビット線に接続された第3の拡散層と、

前記プリチャージ電位供給線に接続された第4の拡散層と、

第1、第2及び第3の部分を有し、第1の部分が前記半導体基板の上方であって且つ前記第1及び第2の拡散層に隣接して設けられ、第2の部分が前記半導体基板の上方であって且つ前記第2及び第3の拡散層に隣接して設けられ、第3の部分が前記半導体基板の上方であって且つ前記第3及び第4の拡散層に隣接して設けられた第1のゲート電極と、

第1のデータ線に接続された第5の拡散層と、

第2のデータ線に接続された第6の拡散層と、

第4及び第5の部分を有し、第4の部分が前記半導体基板の上方であって且つ前記第2及び第5の拡散層に隣接して設けられ、第5の部分が前記半導体基板の上方であって且つ前記第3及び第6の拡散層に隣接して設けられた第2のゲート電極と、

を備えたことを特徴とする半導体記憶装置。

【請求項9】

半導体基板と、

第1の方向に平行に配置され、それぞれがメモリセルに対してデータ入出力を行う第1から第8のビット線と、

前記第1の方向に対して垂直な第2の方向に平行に配置された第1から第8のデータ線と、

前記半導体基板に形成され、第1から第10の拡散層を有し、第1及び第2の拡散層がプリチャージ電位供給線に接続され、第3から第6の拡散層がそれぞれ前記第1から第4のビット線に接続され、第7から第10の拡散層がそれぞれ前記第1から第4のデータ線に接続された第1の素子領域と、

前記半導体基板に形成され、前記第1の素子領域に隣接して設けられ、第11から第20の拡散層を有し、第11及び第12の拡散層が前記プリチャージ電位供給線に接続され、第13から第16の拡散層がそれぞれ前記第5から第8のビット線に接続され、第17から第20の拡散層がそれぞれ前記第5から第8のデータ線に接続された第2の素子領域と、

前記第1及び第2の素子領域の上方に形成され、第1から第12の部分を有し、第1の部分が前記第1及び第3の拡散層に隣接して設けられ、第2の部分が前記第3及び第4の拡散層に隣接して設けられ、第3の部分が前記第2及び第4の拡散層に隣接して設けられ、第4の部分が前記第1及び第5の拡散層に隣接して設けられ、第5の部分が前記第5及び第6の拡散層に隣接して設けられ、第6の部分が前記第2及び第6の拡散層に隣接して設けられ、第7の部分が前記第11及び第13の拡散層に隣接して設けられ、第8の部分が前記第13及び第14の拡散層に隣接して設けられ、第9の部分が前記第12及び第14の拡散層に隣接して設けられ、第10の部分が前記第11及び第15の拡散層に隣接して設けられ、第11の部分が前記第15及び第16の拡散層に隣接して設けられ、第12の部分が前記第12及び第16の拡散層に隣接して設けられた第1のゲートと、

前記第1及び第2の素子領域の上方に形成され、第1から第4の部分を有し、第1の部分が前記第3及び第7の拡散層に隣接して設けられ、第2の部分が前記第4及び第8の拡散層に隣接して設けられ、第3の部分が前記第13及び第17の拡散層に隣接して設けられ、第4の部分が前記第14及び第18の拡散層に隣接して設けられた第2のゲートと、

前記第1及び第2の素子領域の上方に形成され、第1から第4の部分を有し、第1の部分が前記第5及び第9の拡散層に隣接して設けられ、第2の部分が前記第6及び第10の拡散層に隣接して設けられ、第3の部分が前記第15及び第19の拡散層に隣接して設けられ、第4の部分が前記第16及び第20の拡散層に隣接して設けられた第3のゲートと、

前記第1の素子領域と第2の素子領域の間に設けられ、前記第1から第3のゲートにそれぞれ接続された第1から第3のコンタクトと、

前記第2及び第12の拡散層にそれぞれ接続された第4及び第5のコンタクトとを備え、

前記第1から第5のコンタクトが実質的に一つの線上に配置されていることを特徴とする半導体記憶装置。

**【請求項10】**

半導体基板と、

第1の方向に平行に配置され、それぞれがメモリセルに対してデータ入出力を行う第1から第8のビット線と、

前記第1の方向に対して垂直な第2の方向に平行に配置された第1から第8のデータ線と、

前記半導体基板に形成され、第1から第10の拡散層を有し、第1及び第2の拡散層がプリチャージ電位供給線に接続され、第3から第6の拡散層がそれぞれ前記第1から第4のビット線に接続され、第7から第10の拡散層がそれぞれ前記第1から第4のデータ線に接続された第1の素子領域と、

前記半導体基板に形成され、第11から第20の拡散層を有し、第11及び第12の拡散層が前記プリチャージ電位供給線に接続され、第13から第16の拡散層がそれぞれ前記第5から第8のビット線に接続され、第17から第20の拡散層がそれぞれ前記第5から第8のデータ線に接続され、前記第11の拡散層が前記第2の拡散層に対向するように前記第1の素子領域に隣接して設けられた第2の素子領域と、

前記第1及び第2の素子領域の上方に形成され、第1から第12の部分を有し、第1の部分が前記第1及び第3の拡散層に隣接して設けられ、第2の部分が前記第3及び第4の拡散層に隣接して設けられ、第3の部分が前記第2及び第4の拡散層に隣接して設けられ、第4の部分が前記第1及び第5の拡散層に隣接して設けられ、第5の部分が前記第5及び第6の拡散層に隣接して設けられ、第6の部分が前記第2及び第6の拡散層に隣接して設けられ、第7の部分が前記第11及び第13の拡散層に隣接して設けられ、第8の部分が前記第13及び第14の拡散層に隣接して設けられ、第9の部分が前記第12及び第14の拡散層に隣接して設けられ、第10の部分が前記第11及び第15の拡散層に隣接して設けられ、第11の部分が前記第15及び第16の拡散層に隣接して設けられ、第12の部分が前記第12及び第16の拡散層に隣接して設けられた第1のゲートと、

前記第1の素子領域の上方に形成され、第1から第4の部分を有し、第1の部分が前記第3及び第7の拡散層に隣接して設けられ、第2の部分が前記第4及び第8の拡散層に隣接して設けられ、第3の部分が前記第5及び第9の拡散層に隣接して設けられ、第4の部分が前記第6及び第10の拡散層に隣接して設けられた第2のゲートと、

前記第2の素子領域の上方に形成され、第1から第4の部分を有し、第1の部分が前記第13及び第17の拡散層に隣接して設けられ、第2の部分が前記第14及び第18の拡散層に隣接して設けられ、第3の部分が前記第15及び第19の拡散層に隣接して設けられ、第4の部分が前記第16及び第20の拡散層に隣接して設けられた第3のゲートとを備え、

前記プリチャージ電位供給線が、前記第2の方向に平行に配置され、且つ実質的に前記第11の拡散層の上方に設けられていることを特徴とする半導体記憶装置。

**【請求項11】**

半導体基板と、

第1の方向に平行に配置され、それぞれがメモリセルに対してデータ入出力を行う第1から第8のビット線と、

前記第1の方向に対して垂直な第2の方向に平行に配置された第1から第8のデータ線と、

前記半導体基板に形成され、第1から第10の拡散層を有し、第1及び第2の拡散層がプリチャージ電位供給線に接続され、第3から第6の拡散層がそれぞれ前記第1から第4

10

20

30

40

50

のビット線に接続され、第7から第10の拡散層がそれぞれ前記第1から第4のデータ線に接続された第1の素子領域と、

前記半導体基板に形成され、第11から第20の拡散層を有し、第11及び第12の拡散層が前記プリチャージ電位供給線に接続され、第13から第16の拡散層がそれぞれ前記第5から第8のビット線に接続され、第17から第20の拡散層がそれぞれ前記第5から第8のデータ線に接続され、前記第11の拡散層が前記第2の拡散層に対向するよう前記第1の素子領域に隣接して設けられた第2の素子領域と、

前記第1及び第2の素子領域の上方に形成され、第1から第12の部分を有し、第1の部分が前記第1及び第3の拡散層に隣接して設けられ、第2の部分が前記第3及び第4の拡散層に隣接して設けられ、第3の部分が前記第2及び第4の拡散層に隣接して設けられ、第4の部分が前記第1及び第5の拡散層に隣接して設けられ、第5の部分が前記第5及び第6の拡散層に隣接して設けられ、第6の部分が前記第2及び第6の拡散層に隣接して設けられ、第7の部分が前記第11及び第13の拡散層に隣接して設けられ、第8の部分が前記第13及び第14の拡散層に隣接して設けられ、第9の部分が前記第12及び第14の拡散層に隣接して設けられ、第10の部分が前記第11及び第15の拡散層に隣接して設けられ、第11の部分が前記第15及び第16の拡散層に隣接して設けられ、第12の部分が前記第12及び第16の拡散層に隣接して設けられた第1のゲートと、

前記第1の素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第3及び第7の拡散層に隣接して設けられ、第2の部分が前記第4及び第8の拡散層に隣接して設けられた第2のゲートと、

前記第1の素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第5及び第9の拡散層に隣接して設けられ、第2の部分が前記第6及び第10の拡散層に隣接して設けられた第3のゲートと、

前記第2の素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第13及び第17の拡散層に隣接して設けられ、第2の部分が前記第14及び第18の拡散層に隣接して設けられた第4のゲートと、

前記第2の素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第15及び第19の拡散層に隣接して設けられ、第2の部分が前記第16及び第20の拡散層に隣接して設けられた第5のゲートと、

前記第1から第8のビット線の上方であって前記第2の方向に設けられ、前記第2及び第3のゲートに接続された第1の配線と、

前記第1から第8のビット線の上方であって前記第2の方向に設けられ、前記第4及び第5のゲートに接続された第2の配線とを備え、

前記プリチャージ電位供給線が、前記第2の方向に平行に配置され、且つ実質的に前記第11の拡散層の上方に設けられていることを特徴とする半導体記憶装置。

#### 【請求項12】

半導体基板と、

第1の方向に平行に配置され、それぞれがメモリセルに対してデータ入出力を行う第1から第8のビット線と、

前記第1の方向に対して垂直な第2の方向に平行に配置された第1から第8のデータ線と、

前記半導体基板に形成され、第1から第19の拡散層を有し、第1、第2及び第11の拡散層がプリチャージ電位供給線に接続され、第3から第6及び第12から第15の拡散層がそれぞれ前記第1から第8のビット線に接続され、第7から第10及び第16から第19の拡散層がそれぞれ前記第1から第8のデータ線に接続された素子領域と、

前記素子領域の上方に形成され、第1から第6の部分を有し、第1の部分が前記第1及び第3の拡散層に隣接して設けられ、第2の部分が前記第3及び第4の拡散層に隣接して設けられ、第3の部分が前記第2及び第4の拡散層に隣接して設けられ、第4の部分が前記第1及び第5の拡散層に隣接して設けられ、第5の部分が前記第5及び第6の拡散層に隣接して設けられ、第6の部分が前記第2及び第6の拡散層に隣接して設けられた第1の

10

20

30

40

50

ゲートと、

前記素子領域の上方に形成され、第1から第6の部分を有し、第1の部分が前記第2及び第12の拡散層に隣接して設けられ、第2の部分が前記第12及び第13の拡散層に隣接して設けられ、第3の部分が前記第11及び第13の拡散層に隣接して設けられ、第4の部分が前記第2及び第14の拡散層に隣接して設けられ、第5の部分が前記第14及び第15の拡散層に隣接して設けられ、第6の部分が前記第11及び第15の拡散層に隣接して設けられた第2のゲートと、

前記第1から第8のビット線の上方であって前記第2の方向に設けられ、前記第1及び第2のゲートに接続されたビット線イコライザ制御線と、

前記素子領域の上方に形成され、第1から第4の部分を有し、第1の部分が前記第3及び第7の拡散層に隣接して設けられ、第2の部分が前記第4及び第8の拡散層に隣接して設けられ、第3の部分が前記第5及び第9の拡散層に隣接して設けられ、第4の部分が前記第6及び第10の拡散層に隣接して設けられた第3のゲートと、

前記素子領域の上方に形成され、第1から第4の部分を有し、第1の部分が前記第12及び第16の拡散層に隣接して設けられ、第2の部分が前記第13及び第17の拡散層に隣接して設けられ、第3の部分が前記第14及び第18の拡散層に隣接して設けられ、第4の部分が前記第15及び第19の拡散層に隣接して設けられた第4のゲートと、

を備えたことを特徴とする半導体記憶装置。

### 【請求項13】

半導体基板と、

第1の方向に平行に配置され、それぞれがメモリセルに対してデータ入出力を行う第1から第8のビット線と、

前記第1の方向に対して垂直な第2の方向に平行に配置された第1から第8のデータ線と、

前記半導体基板に形成され、第1から第19の拡散層を有し、第1、第2及び第11の拡散層がプリチャージ電位供給線に接続され、第3から第6及び第12から第15の拡散層がそれぞれ前記第1から第8のビット線に接続され、第7から第10及び第16から第19の拡散層がそれぞれ前記第1から第8のデータ線に接続された素子領域と、

前記素子領域の上方に形成され、第1から第6の部分を有し、第1の部分が前記第1及び第3の拡散層に隣接して設けられ、第2の部分が前記第3及び第4の拡散層に隣接して設けられ、第3の部分が前記第2及び第4の拡散層に隣接して設けられ、第4の部分が前記第1及び第5の拡散層に隣接して設けられ、第5の部分が前記第5及び第6の拡散層に隣接して設けられ、第6の部分が前記第2及び第6の拡散層に隣接して設けられた第1のゲートと、

前記素子領域の上方に形成され、第1から第6の部分を有し、第1の部分が前記第2及び第12の拡散層に隣接して設けられ、第2の部分が前記第12及び第13の拡散層に隣接して設けられ、第3の部分が前記第11及び第13の拡散層に隣接して設けられ、第4の部分が前記第2及び第14の拡散層に隣接して設けられ、第5の部分が前記第14及び第15の拡散層に隣接して設けられ、第6の部分が前記第11及び第15の拡散層に隣接して設けられた第2のゲートと、

前記第1から第8のビット線の上方であって前記第2の方向に設けられ、前記第1及び第2のゲートに接続されたビット線イコライザ制御線と、

前記素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第3及び第7の拡散層に隣接して設けられ、第2の部分が前記第4及び第8の拡散層に隣接して設けられた第3のゲートと、

前記素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第5及び第9の拡散層に隣接して設けられ、第2の部分が前記第6及び第10の拡散層に隣接して設けられた第4のゲートと、

前記素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第12及び第16の拡散層に隣接して設けられ、第2の部分が前記第13及び第17の拡散層に

10

20

30

40

50

隣接して設けられた第5のゲートと、

前記素子領域の上方に形成され、第1及び第2の部分を有し、第1の部分が前記第14及び第18の拡散層に隣接して設けられ、第2の部分が前記第15及び第19の拡散層に隣接して設けられた第6のゲートと、

前記第1から第8のビット線の上方であって前記第2の方向に設けられ、前記第3及び第4のゲートに接続された第1の配線と、

前記第1から第8のビット線の上方であって前記第2の方向に設けられ、前記第5及び第6のゲートに接続された第1の配線と、

を備えたことを特徴とする半導体記憶装置。

【発明の詳細な説明】

10

【0001】

【発明の属する技術分野】

本発明は、半導体記憶装置、特にDRAMのセンスアンプ部の改良に係るものである。

【0002】

【従来の技術】

近年のマイクロプロセッサの動作速度の向上に伴い、半導体メモリにも高速化が求められている。また、半導体メモリの大容量化や携帯機器の普及により、低消費電力化も求められている。高速化、低消費電力化を実現する上で、ビット線容量を低減することは効果的であり、従来から種々の手法が考案されている。

【0003】

20

ビット線の容量を構成する主な要素としては、ビット線と他の配線（隣接ビット線を含む）との容量、ビット線と拡散層とのコンタクト部分（以下、ビット線コンタクトという）における拡散容量があげられる。ビット線コンタクトは、メモリセルトランジスタの拡散層部分へのコンタクトと、センスアンプ部を構成するトランジスターゲート、ビット線イコライザ、カラムゲート、センスアンプでのコンタクトとに大別できる。従来、センスアンプ部を構成するこれらの各回路はそれぞれ独立した素子パターンで構成されていたため、これら各回路毎にビット線コンタクトを配置する必要があった。

【0004】

【発明が解決しようとする課題】

このように、従来はセンスアンプ部を構成する各回路毎にビット線コンタクトを設けていたので、ビット線容量を低減することが困難であり、高速化や低消費電力化をはかることが困難であった。

30

【0005】

本発明の目的は、センスアンプ部におけるビット線コンタクトの数を削減することによってビット線容量を低減し、低消費電力かつ高速動作が可能な半導体記憶装置を提供することにある。

【0006】

【課題を解決するための手段】

本発明における半導体記憶装置は、カラムゲートと、このカラムゲートの素子パターンと融合された素子パターンを有するイコライズ回路とを有することを特徴とする。

40

【0007】

このように、カラムゲートの素子パターンとイコライズ回路の素子パターンとを融合させることにより、従来カラムゲートとイコライズ回路のそれぞれに必要であったビット線から拡散層へのコンタクトを共有することができ、センスアンプ部におけるビット線コンタクトの数を削減することができる。したがって、センスアンプ部におけるビット線容量を低減することができ、センス動作の高速化及びセンス動作時における低消費電力化をはかることができる。また、従来と比べてイコライズ回路におけるプリチャージ電位供給用トランジスタのゲート幅を大きくすることが可能となり、イコライズ動作の高速化をはかることが可能となる。また、隣接するビット線間の間隔を従来よりも緩和することができるため、ビット線の配線余裕の向上をはかることができ、製造歩留りの向上をはかるこ

50

とができる。さらに、カラムゲートの素子パターンとイコライズ回路の素子パターンとが融合しているので、従来のようにカラムゲートの素子パターンとイコライズ回路の素子パターンとを別々に設けた場合に比べて、センスアンプ部の面積を減少させることが可能となる。

#### 【0008】

以下、本発明の理解を容易にするため、図面に付した符号を参照して本発明の構成を記載する。

#### 【0009】

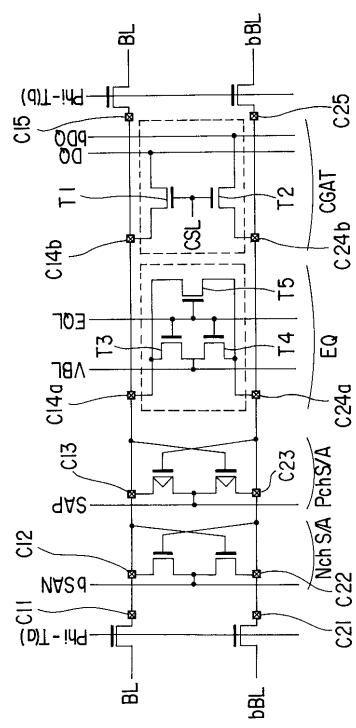

主として回路的な構成に着目すると、本発明における半導体記憶装置は、ゲートがカラムゲート選択線 C S L に接続されソース又はドレインの一方が第 1 のデータ線 D Q に他方が第 1 のビット線 B L に接続された第 1 のトランジスタ T 1 と、ゲートがカラムゲート選択線 C S L に接続されソース又はドレインの一方が第 2 のデータ線 b D Q に他方が第 2 のビット線 b B L に接続された第 2 のトランジスタ T 2 とを含むカラムゲート C G A T と、；ゲートがイコライズ回路制御線 E Q L に接続されソース又はドレインの一方が第 1 のビット線 B L に他方がイコライズ回路電源線 V B L に接続された第 3 のトランジスタ T 3 と、ゲートがイコライズ回路制御線 E Q L に接続されソース又はドレインの一方が第 2 のビット線 b B L に他方がイコライズ回路電源線 V B L に接続された第 4 のトランジスタ T 4 と、ゲートがイコライズ回路制御線 E Q L に接続されソース又はドレインの一方が第 1 のビット線 B L に他方が第 2 のビット線 b B L に接続された第 5 のトランジスタ T 5 とを含むイコライズ回路 E Q を有し、；前記第 1 のトランジスタ T 1 のソース又はドレインの他方、前記第 3 のトランジスタ T 3 のソース又はドレインの一方及び前記第 5 のトランジスタ T 5 のソース又はドレインの一方が共通のコンタクト C 1 4 を介して前記第 1 のビット線 B L に接続され、前記第 2 のトランジスタ T 2 のソース又はドレインの他方、前記第 4 のトランジスタ T 4 のソース又はドレインの一方及び前記第 5 のトランジスタ T 5 のソース又はドレインの他方が共通のコンタクト C 2 4 を介して前記第 2 のビット線 b B L に接続されていることを特徴とする。

10

#### 【0010】

また、主としてトランジスタの配置等に着目すると、本発明における半導体記憶装置は、第 1 のトランジスタ T 1 及び第 2 のトランジスタ T 2 を含む第 1 のカラムゲート C G A T と、前記第 1 のトランジスタ T 1 との第 1 の共通ノード N 1 を有する第 3 のトランジスタ T 3 と、前記第 2 のトランジスタ T 2 との第 2 の共通ノード N 2 を有する第 4 のトランジスタ T 4 と、前記第 1 の共通ノード N 1 及び前記第 2 の共通ノード N 2 を有する第 5 のトランジスタ T 5 とを含む第 1 のイコライズ回路 E Q と、；第 6 のトランジスタ T 6 及び第 7 のトランジスタ T 7 を含む第 2 のカラムゲート C G A T と、；前記第 6 のトランジスタ T 6 との第 3 の共通ノード N 3 を有する第 8 のトランジスタ T 8 と、前記第 7 のトランジスタ T 7 との第 4 の共通ノード N 4 を有する第 9 のトランジスタ T 9 と、前記第 3 の共通ノード N 3 及び前記第 4 の共通ノード N 4 を有する第 10 のトランジスタ T 10 とを含む第 2 のイコライズ回路 E Q を有することを特徴とする。

20

#### 【0011】

また、主として全体のパターン配置に着目すると、本発明における半導体記憶装置は、第 1 のトランジスタ T 1 及び第 2 のトランジスタ T 2 を含む第 1 のカラムゲート C G A T と、前記第 1 のトランジスタ T 1 との第 1 の共通ノード N 1 を有する第 3 のトランジスタ T 3 と、前記第 2 のトランジスタ T 2 との第 2 の共通ノード N 2 を有する第 4 のトランジスタ T 4 と、前記第 1 の共通ノード N 1 及び前記第 2 の共通ノード N 2 を有する第 5 のトランジスタ T 5 とを含む第 1 のイコライズ回路 E Q と、第 6 のトランジスタ T 6 及び第 7 のトランジスタ T 7 を含む第 2 のカラムゲート C G A T と、前記第 6 のトランジスタ T 6 との第 3 の共通ノード N 3 を有する第 8 のトランジスタ T 8 と、前記第 7 のトランジスタ T 7 との第 4 の共通ノード N 4 を有する第 9 のトランジスタ T 9 と、前記第 3 の共通ノード N 3 及び前記第 4 の共通ノード N 4 を有する第 10 のトランジスタ T 10 とを含む第 2 のイコライズ回路 E Q により単位素子領域を構成し、；互いに隣り合った前記単位素子領域

40

50

域間に前記第3、第4、第5、第8、第9及び第10のトランジスタの各ゲート電極に接続されるイコライズ回路制御線EQ-Lのパターンを形成したことを特徴とする。

#### 【0012】

##### 【発明の実施の形態】

以下、図面を参照して、本発明の実施形態を説明する。

#### 【0013】

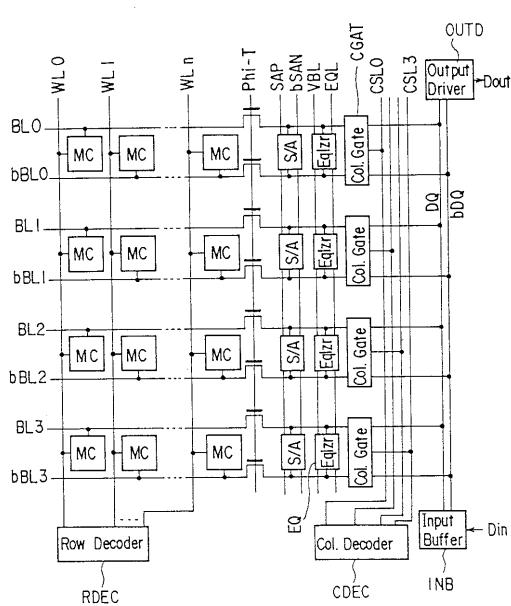

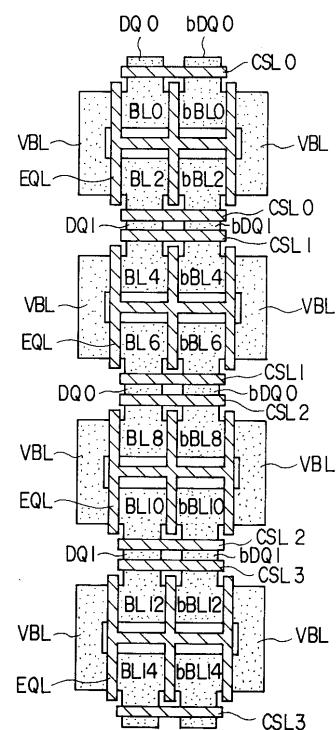

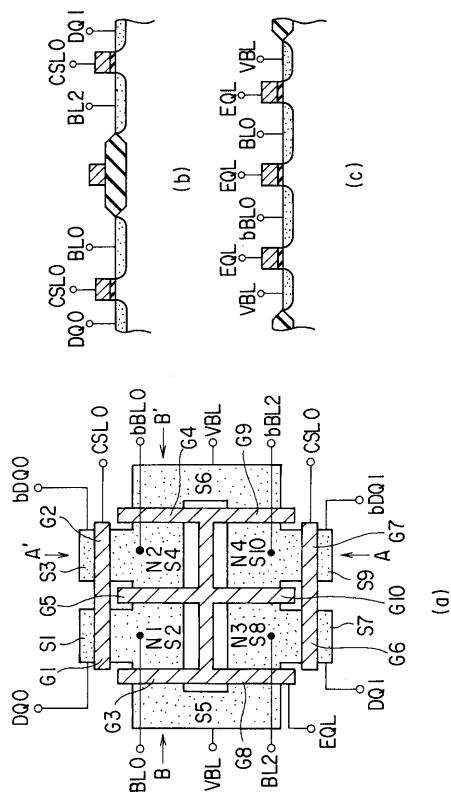

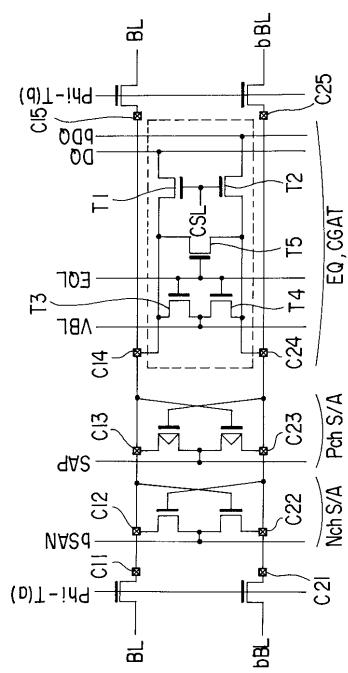

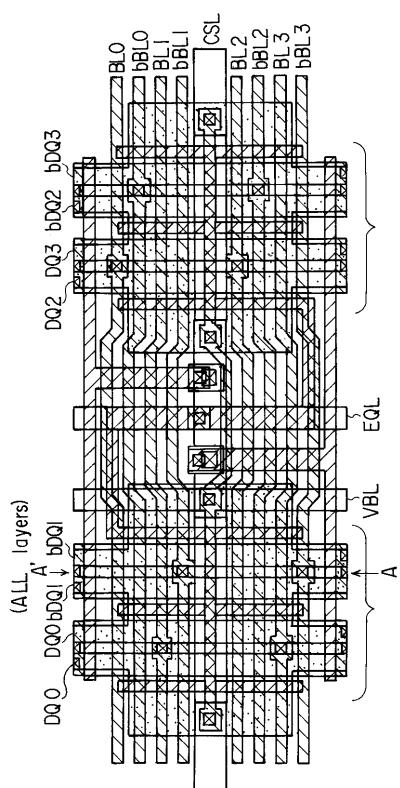

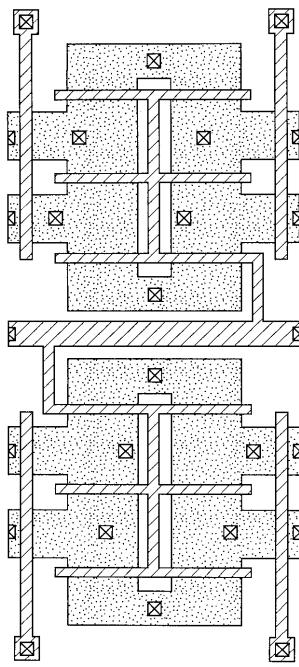

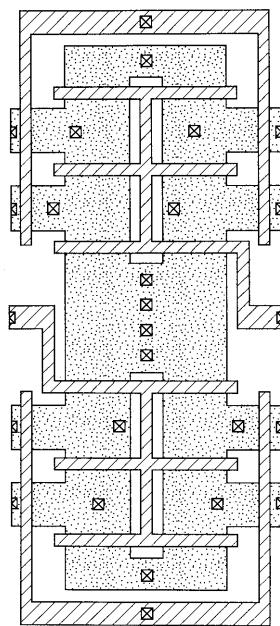

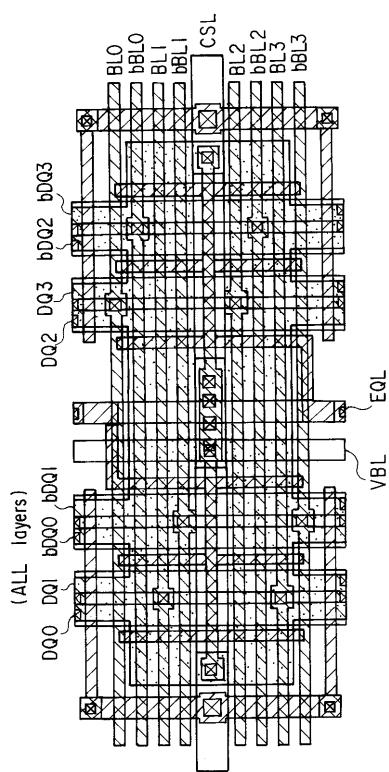

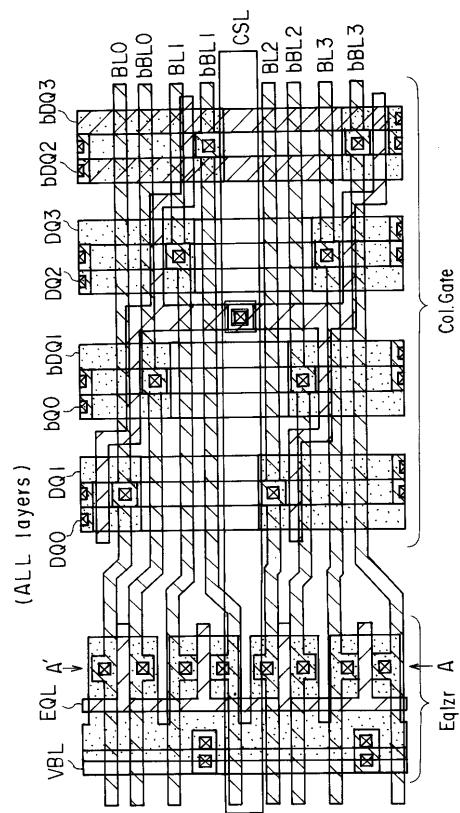

まず、図1～図4を参照して、実施形態の基本的な構成について説明する。図1は本実施形態におけるDRAMの概略構成を示した図、図2はDRAMのセンスアンプ部に含まれるカラムゲート及びビット線イコライザのパターン構成を示した図、図3(a)は図2のパターンの一部を示した図、図3(b)及び(c)は図3(a)のそれぞれA-A'及びB-B'における断面構成を示した図、図4はセンスアンプ部の構成を等価回路として示した図である。10

#### 【0014】

図1において、MCはメモリセル、S/Aはセンスアンプ、EQはビット線イコライザ、CGATはカラムゲート、OUTDは出力ドライバ、INBはインプットバッファ、RD/DECはロウデコーダ、CDECはカラムデコーダ、BL0～BL3はビット線、bBL0～bBL3はそれぞれBL0～BL3と対をなすビット線、WL0～WLnはワード線、Ph/Tはトランスマルチゲート制御線、SAP及びbSANはセンスアンプ駆動線、VBLはプリチャージ電位供給線(イコライズ回路電源線)、EQ-Lはビット線イコライザ制御線、CSL0～CSL3はカラムゲート選択線、DQはデータ線、bDQはDQと対をなすデータ線、Dinは入力端子、Doutは出力端子をそれぞれ示している。なお、その他の各図においても、上記と同一或いは対応する構成要素には上記と同一の符号を付している。20

#### 【0015】

図3において、G1～G10はゲート電極、S1～S10はソース又はドレイン等を構成する拡散領域、N1～N4は共通ノードをそれぞれ示している。ゲート電極G1、G2、G6及びG7にはカラムゲート選択線CSL0が接続され、ゲート電極G3、G4、G5、G8、G9及びG10にはビット線イコライザ制御線EQ-Lが接続されている。また、拡散領域S1、S3、S7及びS9にはそれぞれデータ線DQ0、bDQ0、DQ1及びbDQ1が接続され、拡散領域S2、S4、S8及びS10にはそれぞれビット線BL0、bBL0、BL2及びbBL2が接続され、拡散領域S5及びS6にはプリチャージ電位供給線(イコライズ回路電源線)VBLが接続されている。なお、図2の構成要素については、図3から容易に類推できるため、説明は省略する。30

#### 【0016】

図4において、T1及びT2はカラムゲートCGATを構成するMOSトランジスタ、T3、T4及びT5はビット線イコライザEQを構成するMOSトランジスタをそれぞれ示している。また、C11～C15はビット線BLとセンスアンプ部に含まれる各トランジスタの拡散領域とのコンタクトを、C21～C25はビット線bBLとセンスアンプ部に含まれる各トランジスタの拡散領域とのコンタクトを、それぞれ示している。40

#### 【0017】

本実施形態では、図2及び図3において特徴的に示されるように、カラムゲートの素子パターンとイコライズ回路の素子パターンとが融合された素子パターンとして形成されている。図3に示した例でいえば、ゲートG1を有するトランジスタ(カラムゲートを構成するトランジスタ)、ゲートG3を有するトランジスタ(ビット線イコライザを構成するトランジスタ)及びゲートG5を有するトランジスタ(ビット線イコライザを構成するトランジスタ)は共通ノードN1となる拡散層S2を共有している。同様に、共通ノードN2、N3及びN4もそれぞれカラムゲートを構成する一つのトランジスタとビット線イコライザを構成する二つのトランジスタによって共有されている。そして、各共通ノードN1、N2、N3及びN4(拡散領域S2、S4、S8及びS10)には、ビット線コンタクトを介してそれぞれビット線BL0、bBL0、ビット線BL1及びbBL1が接続され50

ている。

**【0018】**

このように、カラムゲートを構成するトランジスタとビット線イコライザを構成するトランジスタとで拡散領域を共有することにより、従来カラムゲートとビット線イコライザそれぞれに設けられていたビット線コンタクトをカラムゲートとビット線イコライザとで共有することができる。したがって、カラムゲート及びビット線イコライザに関していえば、ビット線コンタクトの数を従来に比べて半減させることができる。

**【0019】**

図4はこの様子を回路的に示したものであるが、同図に示されるように、カラムゲートC G A Tとビット線イコライザE Qとでビット線コンタクト（ビット線B Lに対してはC 1 4、ビット線b B Lに対してはC 2 4）を共有することになる。図30は、従来のセンスアンプ部の構成を示した等価回路図であるが、従来はカラムゲートC G A Tとビット線イコライザE Qとを別々に設けていたため、カラムゲートC G A T及びビット線イコライザE Qそれぞれに対して別々のビット線コンタクト（ビット線B Lに対してはC 1 4 a及びC 1 4 b、ビット線b B Lに対してはC 2 4 a及びC 2 4 b）が必要となる。また、センスアンプ部全体でみても、本実施形態では従来構成に比べてビット線コンタクトの数が5/6に低減されている。

**【0020】**

このように、本発明では、カラムゲートを構成するトランジスタとビット線イコライザを構成するトランジスタとで拡散領域を共有することにより、カラムゲートとビット線イコライザとでビット線コンタクトを共通化することができるため、センスアンプ部におけるビット線コンタクトの数を削減することができる。したがって、センスアンプ部におけるビット線容量を低減させることができ、センス動作の高速化及びセンス動作における低消費電力化をはかることが可能となる。

**【0021】**

また、従来はビット線イコライザのV B Lとビット線B L、b B Lとを接続するトランジスタT 3、T 4のゲート幅をそのレイアウト上大きくとれないため、トランジスタのドライバビリティを十分確保することが困難であった。本実施形態では、トランジスタT 3、T 4のゲート幅をビット線イコライザのビット線対どおりを接続するトランジスタT 5のゲート幅と同程度に広くすることができるため、トランジスタT 3、T 4のドライバビリティを十分確保することができる。したがって、イコライザ動作の高速化をはかることができる。

**【0022】**

次に、上記の基本的な実施形態で示した構成に基づいて得られる具体的なレイアウトパターン例について説明する。

**【0023】**

なお、以下の各レイアウトパターン例において、“layer # n”は第n番目のレイヤ（“layer # 0”は最下層のレイヤ（第0番目のレイヤ）、“layer # 4”は最上層のレイヤ（第4番目のレイヤ））を表したものであり、“cont - xy”は“layer # y”から“layer # x”へのコンタクトを表したものである。

**【0024】**

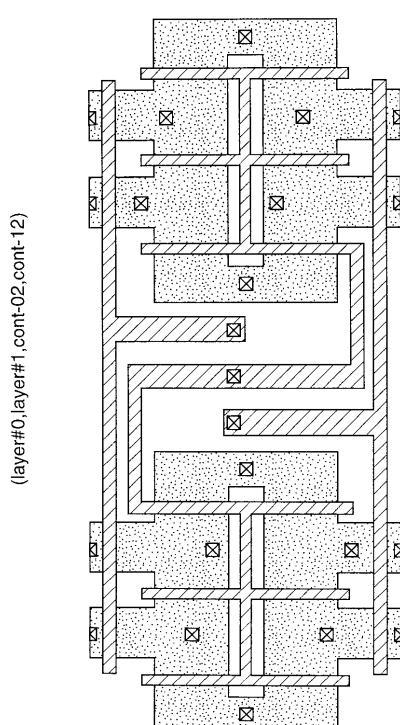

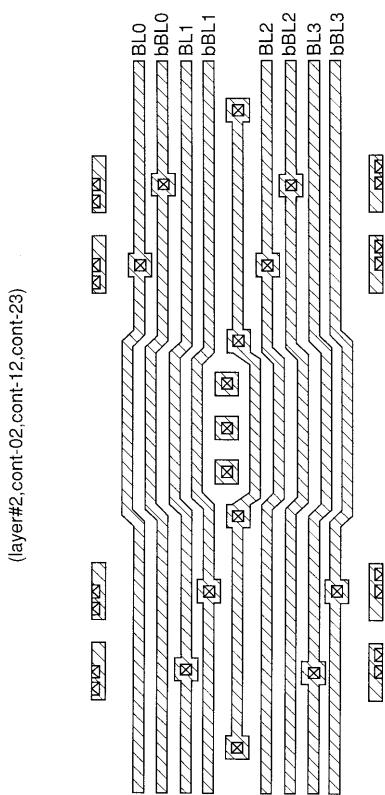

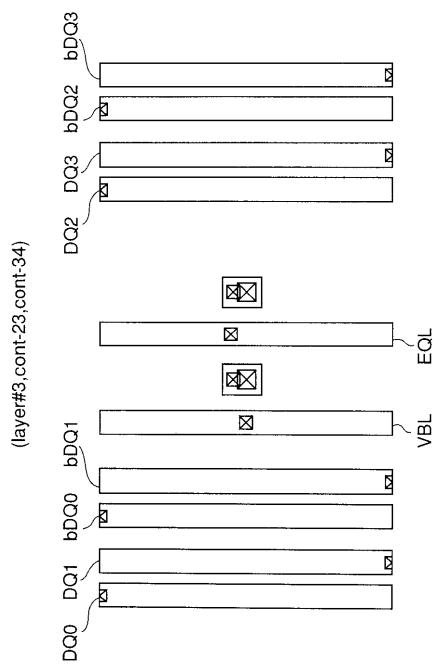

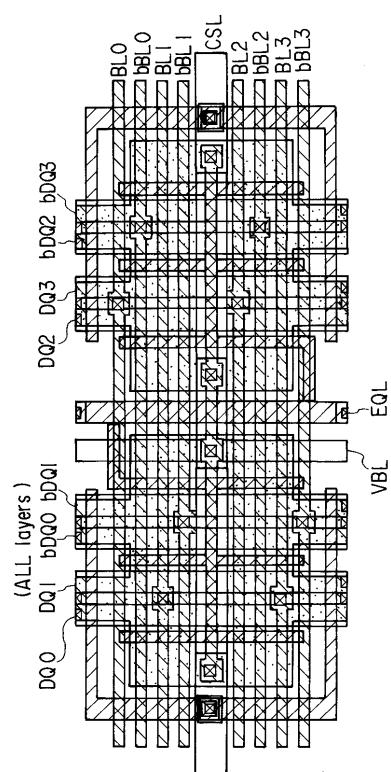

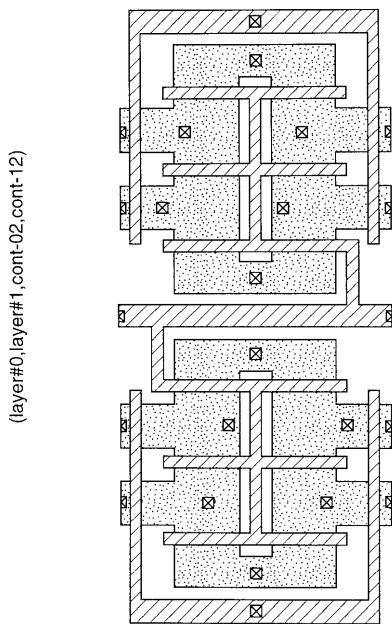

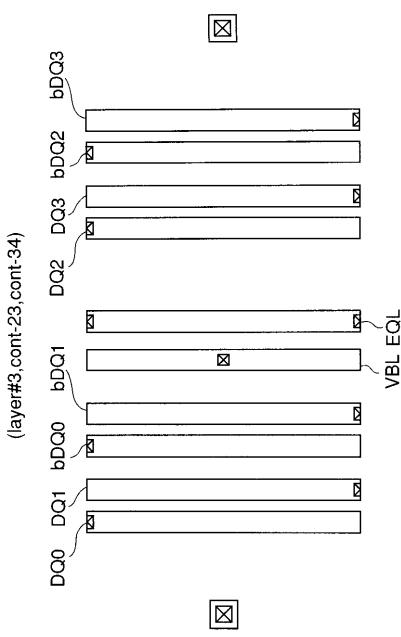

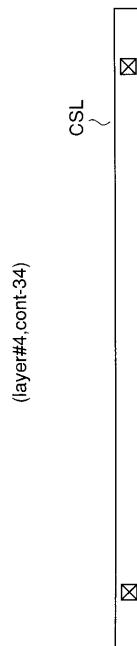

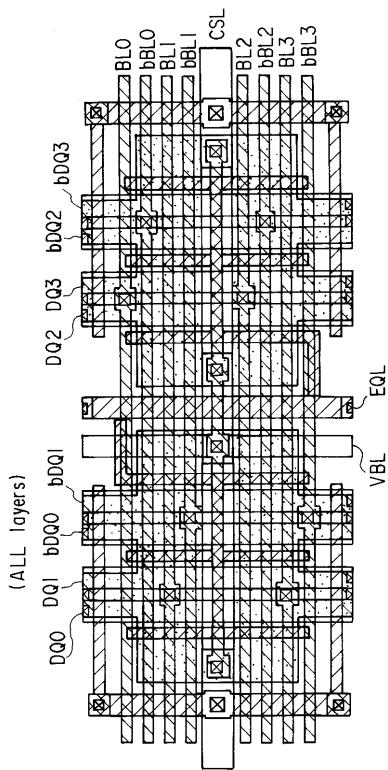

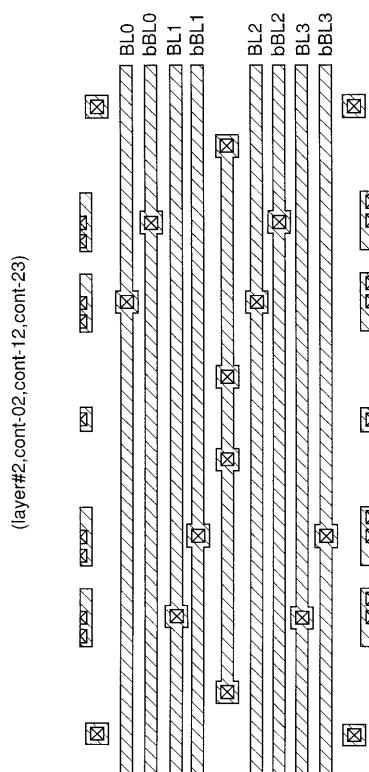

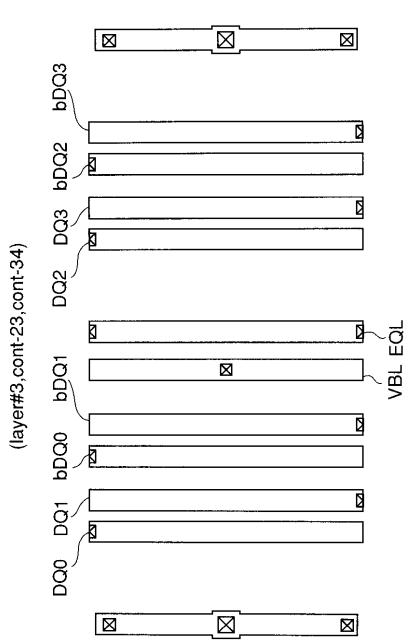

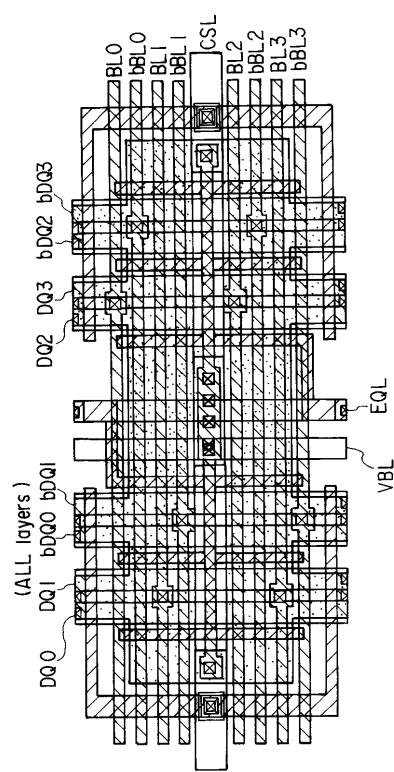

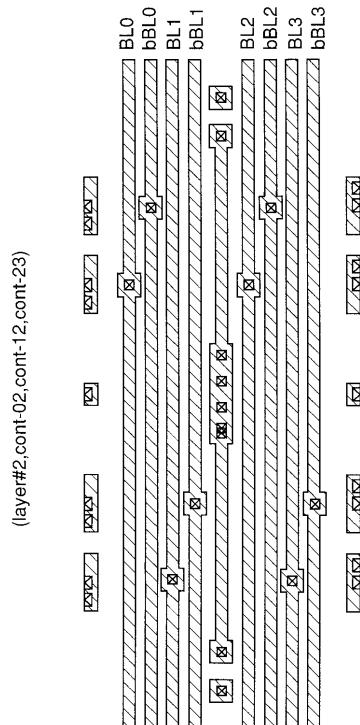

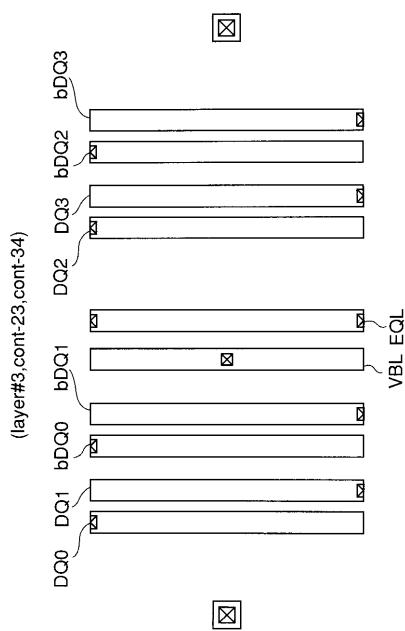

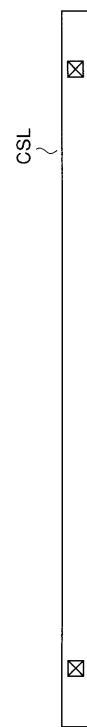

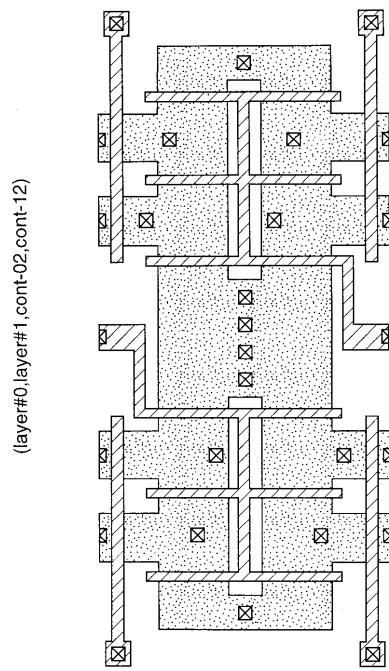

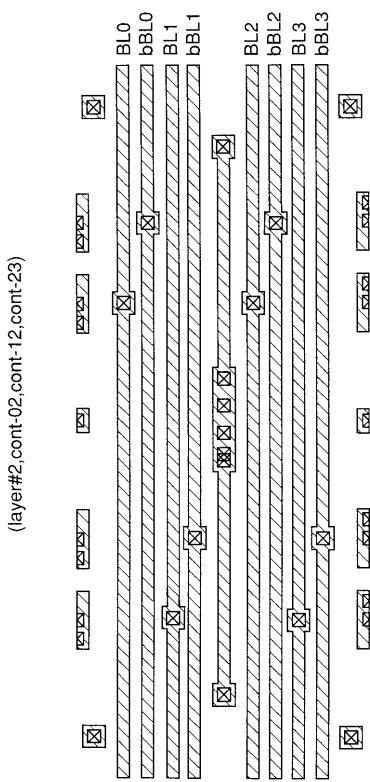

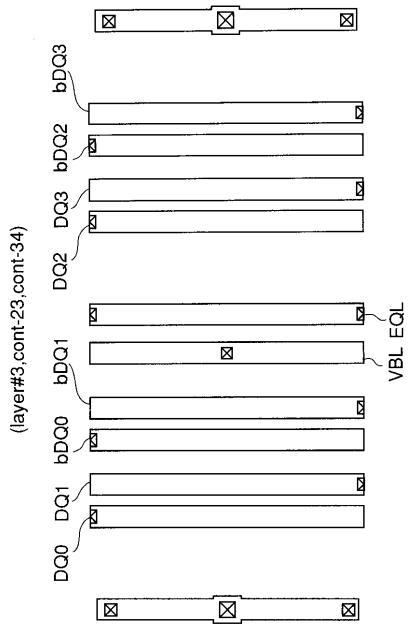

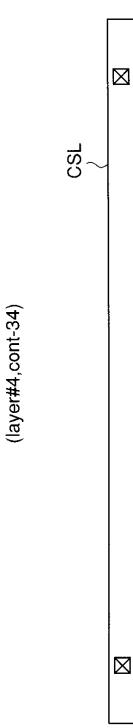

まず、第1のレイアウトパターン例について、図5～図9を参照して説明する。図5はレイアウトパターンの全レイヤ及び全コンタクトを示したものであり、図6は「layer # 0、layer # 1、cont - 02、cont - 12」を、図7は「layer # 2、cont - 02、cont - 12、cont - 23」を、図8は「layer # 3、cont - 23、cont - 34」を、図9は「layer # 4、cont - 34」を、それぞれ示したものである。

**【0025】**

本レイアウトパターン例（他のレイアウトパターン例も同様）では、1本のカラム選択線C S Lが活性化されたときに、4組のビット線対からの情報が4組のD Q線に出力される

10

20

30

40

50

場合を示している。本レイアウトパターン例（他のレイアウトパターン例も同様）では、図5の左右の領域（図5において“{”で示した領域）に、それぞれ図3に示したパターンと同様のパターンが形成されている（図6に示されたパターンも参照）。なお、D Q線の方向に図5に示されたパターンと同様に形成されるパターンでは、隣接するパターン間の境界線（図面上においてD Q線等を切断している線）を境に線対称のパターンが形成される（他のレイアウトパターン例も同様）。

#### 【0026】

ここで、ビット線の配線間余裕について考える。従来のレイアウトパターン例として図3 1に示すようなものを想定した場合、最もビット線の配線間余裕がきびしいのは図3 1のA - A'の部分である。一方、図5において最もビット線の配線間余裕がきびしいのは図5のA - A'の部分である。ここで、ビット線の最小線幅をL、ビット線間の最小間隔をS、ビット線コンタクト部分の最小幅をCとし、ビット線コンタクトとトランジスタのチャネルとの間の距離はビット線とビット線コンタクトとの合わせ余裕に等しいと仮定する。

#### 【0027】

図3 1に示した従来例では、4つのイコライザを配置した場合にビット線の配置に必要な幅は、「 $8C + 8S$ 」と表される。これに対して、図5に示した例では、「 $3C + 17S$ 」と表される。例えば、 $C = 0.5 \mu m$ 、 $L = 0.25 \mu m$ 、 $S = 0.25 \mu m$ と仮定すると、4つのイコライザを配置した場合にビット線の配置に必要な幅は、図3 1に示した従来例では $6 \mu m$ であるのに対し、図5に示した例では $5.75 \mu m$ となる。

#### 【0028】

このように、本発明では、隣接するビット線間の間隔を従来よりも緩和することが可能となり、ビット線の配線余裕の向上をはかることができる。

#### 【0029】

また、図3 1に示した従来例では、カラムゲート及びビット線イコライザのパターンが別々の領域に形成されている。これに対して、本発明では、図5に示すように、カラムゲート及びビット線イコライザのパターンが融合して形成されているため、センスアンプ部の面積を低減することが可能となる。

#### 【0030】

また、本例では、ビット線イコライザ制御線EQ Lが、図5において左右に設けた二つの素子領域の間に形成されている（その他のレイアウトパターン例も同様）。したがって、各トランジスタまでのゲート配線を短くすることができ、高速化をはかることができる。

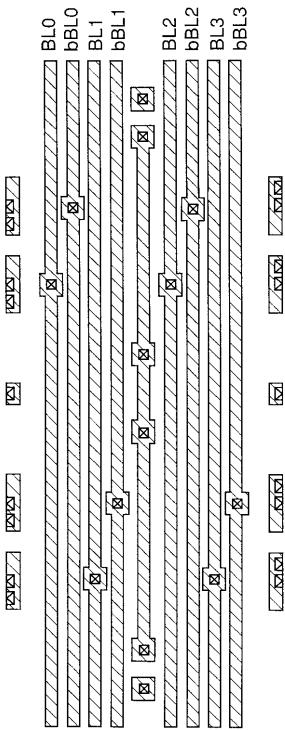

#### 【0031】

つぎに、第2のレイアウトパターン例について、図10～図14を参照して説明する。図10はレイアウトパターンの全レイヤ及び全コンタクトを示したものであり、図11は「layer #0、layer #1、cont - 02、cont - 12」を、図12は「layer #2、cont - 02、cont - 12、cont - 23」を、図13は「layer #3、cont - 23、cont - 34」を、図14は「layer #4、cont - 34」を、それぞれ示したものである。

#### 【0032】

本例では、カラムゲートへの配線をカラムゲート及びビット線イコライザの両側に配置するとともに、ビット線イコライザ制御線EQ Lを中央に複数カラムを貫通するように配置している。これにより、カラムゲート及びビット線イコライザの中央部でのビット線配線が単純になる。

#### 【0033】

つぎに、第3のレイアウトパターン例について、図15～図19を参照して説明する。図15はレイアウトパターンの全レイヤ及び全コンタクトを示したものであり、図16は「layer #0、layer #1、cont - 02、cont - 12」を、図17は「layer #2、cont - 02、cont - 12、cont - 23」を、図18は「layer #3、cont - 23、cont - 34」を、図19は「layer #4、cont - 34」を、それぞれ示したものである。

10

20

30

40

50

t - 3 4」を、それぞれ示したものである。

#### 【0034】

本例でも、第2のレイアウトパターン例と同様、カラムゲートへの配線をカラムゲート及びビット線イコライザの両側に配置するとともに、ビット線イコライザ制御線EQLを中央に複数カラムを貫通するように配置している。第2のレイアウトパターン例と異なる点は、カラムゲート及びビット線イコライザの両側において、ビット線よりも上層側の配線を用いてカラムゲートへの配線を形成し、カラムゲート及びビット線イコライザのビット線方向の占有領域を削減していることである。

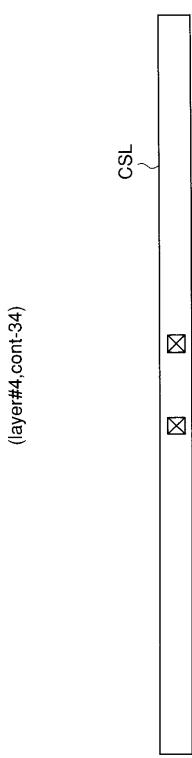

#### 【0035】

つぎに、第4のレイアウトパターン例について、図20～図24を参照して説明する。図20はレイアウトパターンの全レイヤ及び全コンタクトを示したものであり、図21は「layer#0、layer#1、cont-02、cont-12」を、図22は「layer#2、cont-02、cont-12、cont-23」を、図23は「layer#3、cont-23、cont-34」を、図24は「layer#4、cont-34」を、それぞれ示したものである。

10

#### 【0036】

本例では、カラムゲートへの配線をカラムゲート及びビット線イコライザの両側に配置するとともに、第1～第3のレイアウトパターン例では左右に分離して配置されていたカラムゲート及びビット線イコライザを、拡散層で接続している。これにより、プリチャージ電位供給線VBLのコンタクトを多くとることができ。また、カラムゲート及びビット線イコライザのビット線方向の占有領域を削減することができる。

20

#### 【0037】

つぎに、第5のレイアウトパターン例について、図25～図29を参照して説明する。図25はレイアウトパターンの全レイヤ及び全コンタクトを示したものであり、図26は「layer#0、layer#1、cont-02、cont-12」を、図27は「layer#2、cont-02、cont-12、cont-23」を、図28は「layer#3、cont-23、cont-34」を、図29は「layer#4、cont-34」を、それぞれ示したものである。

#### 【0038】

本例では、第4のレイアウトパターン例において、カラムゲート及びビット線イコライザの両側において、ビット線よりも上層側の配線を用いてカラムゲートへの配線を形成し、カラムゲート及びビット線イコライザのビット線方向の占有領域を削減している。

30

#### 【0039】

以上、本発明の実施形態について詳述したが、本発明はこれに限定されるものではなく、その趣旨を逸脱しない範囲内で種々変形して実施可能である。

#### 【0040】

#### 【発明の効果】

本発明では、カラムゲートの素子パターンとイコライズ回路の素子パターンとを融合させることにより、カラムゲートとイコライズ回路とでビット線コンタクトを共通化することができるため、センスアンプ部におけるビット線コンタクトの数を削減することができる。したがって、センスアンプ部におけるビット線容量を低減することができ、センス動作の高速化及びセンス動作における低消費電力化をはかることができる。また、カラムゲートの素子パターンとイコライズ回路の素子パターンとを融合させることにより、イコライズ動作の高速化、ビット線の配線余裕の向上、センスアンプ部の面積の減少等をはかることも可能となる。

40

#### 【図面の簡単な説明】

【図1】本発明の実施形態におけるDRAMの概略構成を示した図。

【図2】本発明の実施形態におけるDRAMのセンスアンプ部に含まれるカラムゲート及びビット線イコライザのパターン構成を示した図。

【図3】図3(a)は図2のパターンの一部を示した図、図3(b)及び(c)は図3(

50

a ) のそれぞれ A - A ' 及び B - B ' における断面構成を示した図。

【図 4】本発明の実施形態におけるセンスアンプ部の構成を等価回路として示した図。

【図 5】本発明の実施形態における第 1 のレイアウトパターン例を示した図。

【図 6】本発明の実施形態における第 1 のレイアウトパターン例について、最下層のレイヤ及び第 1 番目のレイヤ等を示した図。

【図 7】本発明の実施形態における第 1 のレイアウトパターン例について、第 2 番目のレイヤ等を示した図。

【図 8】本発明の実施形態における第 1 のレイアウトパターン例について、第 3 番目のレイヤ等を示した図。

【図 9】本発明の実施形態における第 1 のレイアウトパターン例について、第 4 番目のレイヤ等を示した図。 10

【図 10】本発明の実施形態における第 2 のレイアウトパターン例を示した図。

【図 11】本発明の実施形態における第 2 のレイアウトパターン例について、最下層のレイヤ及び第 1 番目のレイヤ等を示した図。

【図 12】本発明の実施形態における第 2 のレイアウトパターン例について、第 2 番目のレイヤ等を示した図。

【図 13】本発明の実施形態における第 2 のレイアウトパターン例について、第 3 番目のレイヤ等を示した図。

【図 14】本発明の実施形態における第 2 のレイアウトパターン例について、第 4 番目のレイヤ等を示した図。 20

【図 15】本発明の実施形態における第 3 レイアウトパターン例を示した図。

【図 16】本発明の実施形態における第 3 のレイアウトパターン例について、最下層のレイヤ及び第 1 番目のレイヤ等を示した図。

【図 17】本発明の実施形態における第 3 のレイアウトパターン例について、第 2 番目のレイヤ等を示した図。

【図 18】本発明の実形態における第 3 のレイアウトパターン例について、第 3 番目のレイヤ等を示した図。

【図 19】本発明の実施形態における第 3 のレイアウトパターン例について、第 4 番目のレイヤ等を示した図。

【図 20】本発明の実施形態における第 4 レイアウトパターン例を示した図。 30

【図 21】本発明の実施形態における第 4 のレイアウトパターン例について、最下層のレイヤ及び第 1 番目のレイヤ等を示した図。

【図 22】本発明の実施形態における第 4 のレイアウトパターン例について、第 2 番目のレイヤ等を示した図。

【図 23】本発明の実形態における第 4 のレイアウトパターン例について、第 3 番目のレイヤ等を示した図。

【図 24】本発明の実施形態における第 4 のレイアウトパターン例について、第 4 番目のレイヤ等を示した図。

【図 25】本発明の実施形態における第 5 レイアウトパターン例を示した図。

【図 26】本発明の実施形態における第 5 のレイアウトパターン例について、最下層のレイヤ及び第 1 番目のレイヤ等を示した図。 40

【図 27】本発明の実施形態における第 5 のレイアウトパターン例について、第 2 番目のレイヤ等を示した図。

【図 28】本発明の実形態における第 5 のレイアウトパターン例について、第 3 番目のレイヤ等を示した図。

【図 29】本発明の実施形態における第 5 のレイアウトパターン例について、第 4 番目のレイヤ等を示した図。

【図 30】従来技術に係るセンスアンプ部の構成例を示した等価回路図。

【図 31】従来技術に係るレイアウトパターン例を示した図。

【符号の説明】

E Q ... ピット線イコライザ (イコライズ回路)

C G A T ... カラムゲート

T 1 ~ T 5 ... 第 1 ~ 第 5 のトランジスタ

N 1 ~ N 4 ... 第 1 ~ 第 4 の共通ノード

G 1 ~ G 1 0 ... 第 1 ~ 第 1 0 のゲート電極

S 1 ~ S 1 0 ... 第 1 ~ 第 1 0 の拡散領域

C 1 1 ~ C 1 5、C 2 1 ~ C 2 5 ... コンタクト

D Q 0 ... 第 1 のデータ線

b D Q 0 ... 第 2 のデータ線

D Q 1 ... 第 3 のデータ線

b D Q 1 ... 第 4 のデータ線

B L 0 ... 第 1 のビット線

b B L 0 ... 第 2 のビット線

B L 2 ... 第 3 のビット線

b B L 2 ... 第 4 のビット線

V B L ... プリチャージ電位供給線 (イコライズ回路電源線)

E Q L ... ピット線イコライザ制御線 (イコライズ回路制御線)

C S L 0 ~ C S L 3 ... カラムゲート選択線

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

(layer#0,layer#1,cont-02,cont-12)

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

---

フロントページの続き

(72)発明者 稲場 恒夫

神奈川県川崎市幸区堀川町580番1号 株式会社東芝半導体システム技術センター内

(72)発明者 土田 賢二

神奈川県川崎市幸区堀川町580番1号 株式会社東芝半導体システム技術センター内

(72)発明者 白武 慎一郎

神奈川県川崎市幸区堀川町580番1号 株式会社東芝半導体システム技術センター内

審査官 瀧内 健夫

(56)参考文献 特開平03-035490(JP,A)

特開平06-131876(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8242

H01L 27/108