(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-342988

(P2004-342988A)

(43) 公開日 平成16年12月2日(2004.12.2)

(51) Int.Cl.<sup>7</sup>

H01L 23/12

H01L 21/60

F 1

H01L 23/12

H01L 21/60

H01L 23/12

501B

311Q

N

テーマコード(参考)

5FO44

審査請求 未請求 請求項の数 9 O L (全 11 頁)

(21) 出願番号

特願2003-140558 (P2003-140558)

(22) 出願日

平成15年5月19日 (2003.5.19)

(71) 出願人 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 井上 明宣

長野県長野市大字栗田字舍利田711番地

新光電気工業株式会社内

(72) 発明者 加治木 篤典

長野県長野市大字栗田字舍利田711番地

新光電気工業株式会社内

(72) 発明者 山西 学雄

長野県長野市大字栗田字舍利田711番地

新光電気工業株式会社内

最終頁に続く

(54) 【発明の名称】半導体パッケージの製造方法、及び半導体装置の製造方法

## (57) 【要約】

【課題】歩留まりを向上させることができ可能な半導体パッケージの製造方法及び半導体装置の製造方法を提供すること。

本発明の実施の形態に係る半導体パッケージの

製造方法を工程順に示す断面図(その2)

【解決手段】第1パッド7aを有する一層目金属配線層(第1導体パターン)7をポリイミドフィルム(絶縁性基材)1上に形成する工程と、第2パッド8aを有する四層目金属配線層(第2導体パターン)8をポリイミドフィルム1の他方の面上に形成する工程と、第1パッド7aの全側面が露出する大きさの開口9aを備えた第1ソルダーレジスト層9をポリイミドフォルム1上に形成する工程と、第1パッド7a上に第1はんだバンプ12を介して半導体素子11を接続する工程と、ポリイミドフィルム1と半導体素子11との間を絶縁性接着剤13で充填する工程と、第2はんだバンプ14を加熱することにより第2パッド8a上に接合する工程と、を有することを特徴とする半導体パッケージの製造方法による。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

第1パッドを有する第1導体パターンを絶縁性基材の一方の面上に形成する工程と、

第2パッドを有する第2導体パターンを前記絶縁性基材の他方の面上に形成する工程と、

前記第1パッドの全ての側面が露出する大きさの開口を備えたソルダーレジスト層を前記

絶縁性基材の一方の面上に形成する工程と、

前記第1パッド上に第1はんだバンプを介して半導体素子を電気的に接続する工程と、

前記絶縁性基材の一方の面と前記半導体素子との間を絶縁性接着剤で充填する工程と、

前記絶縁性接着材を充填した後、前記第2パッドの上に第2はんだバンプを載せ、該第2

はんだバンプを加熱して溶融することにより前記第2パッド上に接合する工程と、

10 を有することを特徴とする半導体パッケージの製造方法。

**【請求項 2】**

前記第2はんだバンプの加熱温度は、前記第1はんだバンプの融点以上であることを特徴

とする請求項1に記載の半導体パッケージの製造方法。

**【請求項 3】**

前記第1はんだバンプ及び前記第2はんだバンプを共晶はんだで構成することを特徴とする

請求項1に記載の半導体パッケージの製造方法。

**【請求項 4】**

前記第2はんだバンプを前記第2パッド上に接合した後、前記第1はんだバンプの融点以上

の熱履歴が該第1はんだバンプに加わることを特徴とする請求項1に記載の半導体パッ

ケージの製造方法。 20

**【請求項 5】**

前記絶縁性基材の一方の面上に一層以上の配線層を形成し、前記配線層の最上層として前

記第1導体パターンを形成することを特徴とする請求項1に記載の半導体パッケージの製

造方法。

**【請求項 6】**

前記絶縁性基材の他方の面上に一層以上の配線層を形成し、前記配線層の最下層として前

記第2導体パターンを形成することを特徴とする請求項1に記載の半導体パッケージの製

造方法。

**【請求項 7】**

請求項1に記載の半導体パッケージが備える前記第2はんだバンプを加熱して溶融すること

により、実装基板の端子上に前記第2はんだバンプを電気的に接続することを特徴とする

半導体装置の製造方法。 30

**【請求項 8】**

前記第2はんだバンプの加熱温度は、前記第1はんだバンプの融点以上であることを特徴

とする請求項7に記載の半導体装置の製造方法。

**【請求項 9】**

前記第2はんだバンプを前記端子上に接続した後、加熱されて溶融したはんだを介して電子

部品を前記実装基板上に電気的に接続する工程を行うことを特徴とする請求項7に記載

の半導体装置の製造方法。 40

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、半導体パッケージの製造方法及び半導体装置の製造方法に関し、より詳細には

、半導体パッケージと半導体装置の歩留まりを向上させるのに有用な技術に関する。

**【0002】****【従来の技術】**

近年の電子機器の小型化に伴い、その電子機器に搭載される半導体パッケージを小型化したり、電子機器内のマザーボード上に半導体パッケージを高密度に実装することが求められ

ている。そのような要求を満足する半導体パッケージとして、内部構造の工夫によつて

50

外形寸法を半導体素子の寸法に抑えた C S P ( C h i p S i z e P a c k a g e ) がある。

【 0 0 0 3 】

その C S P には様々なタイプがあるが、中でも B G A ( B a l l G r i d A r r a y ) と呼ばれるタイプの半導体パッケージは、マザーボード上に高密度に実装することができ、電子機器の小型化に大きく寄与する。

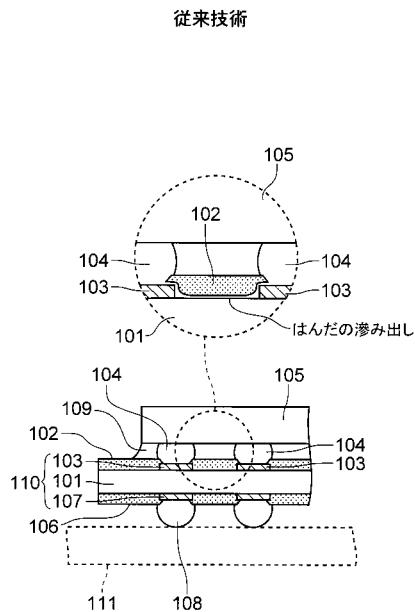

【 0 0 0 4 】

図 1 はその B G A タイプの半導体パッケージの拡大断面図である。このパッケージは、絶縁性基材 1 0 1 の両面に導電性の第 1 パッド 1 0 3 と第 2 パッド 1 0 7 とを形成してなるインターポーザ 1 1 0 を有し、半導体素子 1 0 5 が第 1 パッド 1 0 3 上に第 1 はんだバンプ 1 0 4 を介して電気的に接続される。そして、インターポーザ 1 1 0 の実装面側にある第 2 パッド 1 0 7 上には、この半導体パッケージの外部接続端子として機能する第 2 はんだバンプ 1 0 8 が接合されており、この第 2 はんだバンプ 1 0 8 を介して上記の B G A が実装基板 1 1 1 上に電気的に接続される。

【 0 0 0 5 】

第 1 バンプ 1 0 4 は、それをリフローすることによって第 1 パッド 1 0 3 上に電気的に接続されるが、そのリフローの際、第 1 パッド 1 0 3 と同じ面内にある導体パターンにはんだが付着するのを防止するため、第 1 パッド 1 0 3 以外の部分の絶縁性基材 1 0 1 上には、第 1 ソルダーレジスト層 1 0 2 が形成される。同様の理由により、第 2 パッド 1 0 7 が形成される側の絶縁性基材 1 0 1 上に第 2 ソルダーレジスト層 1 0 6 が形成される。

【 0 0 0 6 】

この B G A タイプの半導体パッケージでは、第 1 はんだバンプ 1 0 4 の個数が少ないと、半導体素子 1 0 5 とインターポーザ 1 1 0 との接合強度が弱くなり、半導体素子 1 0 5 とインターポーザ 1 1 0 との間に導通不良が発生し易くなる。そこで、通常は、半導体素子 1 0 5 とインターポーザ 1 1 0 との間にアンダーフィル樹脂と呼ばれる絶縁性の接着剤 1 0 9 を流し込み、半導体素子 1 0 5 とインターポーザ 1 1 0 との接合強度を補強する。

【 0 0 0 7 】

なお、本発明に関連する技術として、特許文献 1 ~ 3 には、上記のようにはんだバンプを介して半導体素子をインターポーザや実装基板に電気的に接続する技術が開示される。

【 0 0 0 8 】

【 特許文献 1 】

特開平 1 1 - 8 7 8 9 9 号公報

【 特許文献 2 】

特開平 1 1 - 1 5 0 2 0 6 号公報

【 特許文献 3 】

特開平 1 1 - 2 9 7 8 8 9 号公報

【 0 0 0 9 】

【 発明が解決しようとする課題 】

ところで、第 2 はんだバンプ 1 0 8 は、それをリフローすることによって第 2 パッド 1 0 7 上に接合されるが、このリフローによって、第 1 はんだバンプ 1 0 4 も加熱されて溶融されることになる。

【 0 0 1 0 】

この際、溶融した第 1 はんだバンプ 1 0 4 は、熱膨張によってその体積が増えるのに対し、第 1 はんだバンプ 1 0 4 の周囲を囲う接着剤 1 0 9 は固化したままなので、膨張したはんだバンプ 1 0 4 は、密着強度の弱い第 1 パッド 1 0 3 とソルダーレジスト 1 0 2 との界面に滲みだすことになる。

【 0 0 1 1 】

こうなると、点線円内に示すように、滲みだしたはんだによって隣接する第 1 はんだバンプ 1 0 4 同士がショートしてしまうので、半導体パッケージの歩留まりが低下してしまう。

10

20

30

40

50

**【 0 0 1 2 】**

本発明は係る従来例の問題点に鑑みて創作されたものであり、歩留まりを向上させることができ可能な半導体パッケージの製造方法、及び半導体装置の製造方法を提供することを目的とする。

**【 0 0 1 3 】****【課題を解決するための手段】**

本発明の一観点によれば、第1パッドを有する第1導体パターンを絶縁性基材の一方の面上に形成する工程と、第2パッドを有する第2導体パターンを前記絶縁性基材の他方の面上に形成する工程と、前記第1パッドの全ての側面が露出する大きさの開口を備えたソルダーレジスト層を前記絶縁性基材の一方の面上に形成する工程と、前記第1パッド上に第1はんだバンプを介して半導体素子を電気的に接続する工程と、前記絶縁性基材の一方の面と前記半導体素子との間を絶縁性接着剤で充填する工程と、前記絶縁性接着材を充填した後、前記第2パッドの上に第2はんだバンプを載せ、該第2はんだバンプを加熱して溶融することにより前記第2パッド上に接合する工程と、を有することを特徴とする半導体パッケージの製造方法が提供される。10

**【 0 0 1 4 】**

本発明によれば、第1パッドの全ての側面が露出する大きさにソルダーレジスト層の開口を形成するので、第1パッドとソルダーレジスト層とが重ならず、それらの界面が存在しない。従って、第2はんだバンプを加熱して溶融させる際に第1はんだバンプが溶融しても、溶融した第1はんだバンプが第1パッドとソルダーレジスト層との界面に滲み出さないので、滲み出したはんだによって隣接する第1はんだバンプ同士が電気的にショートする危険性を低減することができ、ひいては半導体パッケージの歩留まりを向上させることができる。20

**【 0 0 1 5 】**

よって、この本発明は、第2はんだバンプの加熱温度が第1はんだバンプの融点以上に設定され、第2はんだバンプの加熱時に第1はんだバンプが確実に溶融してしまう場合に特に有用である。

**【 0 0 1 6 】**

更に、第2はんだバンプが加熱される場合の他に、第1はんだバンプの融点以上の熱履歴が該第1はんだバンプに加わる場合にも、上記と同様の利点を得ることができる。30

**【 0 0 1 7 】**

また、本発明の別の観点によれば、上記した半導体パッケージが備える前記第2はんだバンプを加熱して溶融することにより、実装基板の端子上に前記第2はんだバンプを電気的に接続することを特徴とする半導体装置の製造方法が提供される。

**【 0 0 1 8 】**

本発明によれば、第2はんだバンプを加熱して溶融する際、半導体パッケージの第1はんだバンプが溶融しても、上記した理由により、隣接する第1はんだバンプ同士が電気的にショートするのを防止することができる。

**【 0 0 1 9 】**

このような利点は、第2はんだバンプを上記端子上に接続した後、加熱されて溶融したはんだを介して電子部品を実装基板上に電気的に接続する工程においても得ることができる。40

**【 0 0 2 0 】****【発明の実施の形態】**

以下に本発明の実施形態を図面に基づいて説明する。

**【 0 0 2 1 】**

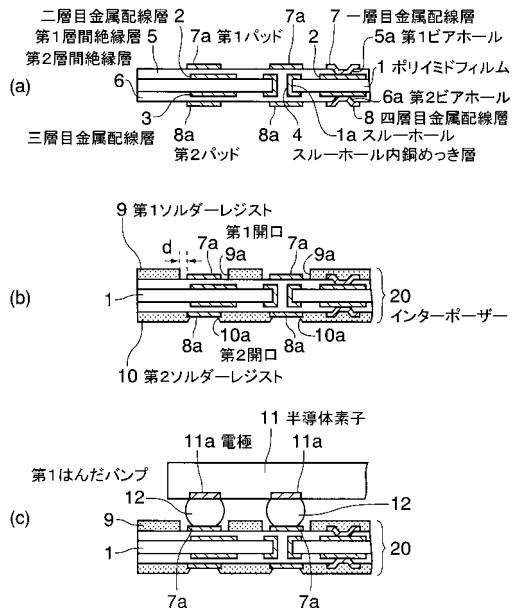

図2～図3は、本発明の実施の形態に係る半導体パッケージの製造方法を工程順に示す断面図である。

**【 0 0 2 2 】**

最初に、図2(a)に示す断面構造を得るまでの工程について説明する。50

## 【0023】

まず、両面に銅箔が貼り付けられた可撓性のポリイミドフィルム（絶縁性基材）1に対し、レーザや機械ドリル等を用いてスルーホール1aを形成する。続いて、このスルーホール1aの内面と銅箔の表面とに無電解銅めっき層を形成し、更にこの無電解銅めっき層上に電解銅めっき層を成長させることにより、銅箔とこれらの銅めっき層よりなる厚さ約35μmの銅層をポリイミドフィルム1上に形成する。その後に、この銅層をパターニングし、これによりポリイミドフィルム1の両面に残った銅層を二層目金属配線層2、三層目金属配線層3とする。各金属配線層2、3は、スルーホール1a内に形成された上記の電解銅めっき層と無電解銅めっき層よりなるスルーホール内銅めっき層4によって電気的に接続されることになる。

10

## 【0024】

続いて、ポリイミドフィルム1の両面にカーテンコート法により感光性ポリイミド樹脂を厚さ30μmに塗布した後、それを露光、現像し、更に加熱して硬化する。これにより、二層目金属配線層2に至る深さの第1ビアホール5aを備えた第1層間絶縁層5が二層目金属配線層2上に形成されると共に、三層目金属配線層3に至る深さの第2ビアホール6aを備えた第2層間絶縁層6が三層目金属配線層3上に形成される。

## 【0025】

なお、感光性ポリイミド樹脂に代えて、非感光性ポリイミド樹脂やエポキシ樹脂等により各絶縁層5、6を構成してもよい。その場合、各ビアホール5a、6aは、各絶縁層5、6にレーザを照射し、レーザが照射された部分の樹脂を蒸散させることにより形成される。

20

## 【0026】

その後、各絶縁層5、6の表面に無電解銅めっき層を形成し、更にこの無電解銅めっき層を給電層にして電解銅めっき層を成長させ、これら無電解銅めっき層と電解銅めっき層とで構成される厚さ約13μmの銅層を各絶縁層5、6上に形成する。その後に、第1層間絶縁層5の上の銅層をパターニングして一層目金属配線（第1導体パターン）7とすると共に、第2層間絶縁層6の上の銅層をパターニングして四層目金属配線（第2導体パターン）8とする。

## 【0027】

その一層目金属配線7は、第1ビアホール5aを介して二層目金属配線2と電気的に接続されると共に、後述する半導体素子のはんだバンプが接合される第1パッド7aを有する。その第1パッド7aの平面形状は円形であり、その直径は約100μm程度である。

30

## 【0028】

また、四層目金属配線8は、第2ビアホール6aを介して三層目金属配線3と電気的に接続されると共に、パッケージの外部接続端子として機能するはんだバンプが後で接合される第2パッド8aを有する。第1パッド7aと同様に、この第2パッド8aの平面形状は円形であり、その直径は約400μm程度である。

## 【0029】

次に、図2(b)に示す断面構造を得るまでの工程について説明する。

## 【0030】

まず、感光性の樹脂よりなるソルダーレジストを第1層間絶縁層5の上に塗布し、それを露光・現像することにより厚さ約23μm程度の第1ソルダーレジスト層9とする。その第1ソルダーレジスト層9は、第1パッド7aの全ての側面が露出する大きさの円形の第1開口9aを有し、その第1開口9aと第1パッド7aのそれぞれの側面の間隔dは約50μm程度である。また、この第1開口9aの直径は、特に限定されないが、約200μm程度である。

40

## 【0031】

その後、第1ソルダーレジスト層9を形成したのと同様の方法を用いることにより、第2層間絶縁層8の上に第2ソルダーレジスト層10を厚さ33μmに形成する。その第2ソルダーレジスト層10には、第2パッド8aが露出する大きさの第2開口10aが形成さ

50

れる。

【0032】

以上により、ソルダーレジスト層9、10が両面に形成されたインターポーザ20の基本構造が完成する。

【0033】

次に、図2(c)に示す断面構造を得るまでの工程について説明する。

【0034】

まず、共晶はんだボールを半導体素子11の電極端子11a上に搭載し、これをリフローすることにより第1はんだバンプ12とする。そして、この第1はんだバンプ12が冷えて固化した後、第1はんだバンプ12を第1パッド7a上に当接させ、この状態で第1はんだバンプ12をその融点(約183)以上の温度でリフローする。

10

【0035】

これにより、第1はんだバンプ12が溶融して第1パッド7a上に濡れ拡がり、はんだが冷却して固化した後は、この第1はんだバンプ12を介して半導体素子11と第1パッド7aとが電気的に接続される。そのような接続構造は、フリップチップ接続とも呼ばれる。

。

【0036】

また、第1はんだバンプ12の配列方法は特に限定されないが、本実施形態では、半導体素子11の電極形成面にグリッド状に50数個配列する。

【0037】

ところで、このように第1はんだバンプ12が50数個と少ないと、半導体素子11とインターポーザ20との接合強度が全体として低下し、半導体素子11が第1パッド7aから剥がれ易くなってしまう。

【0038】

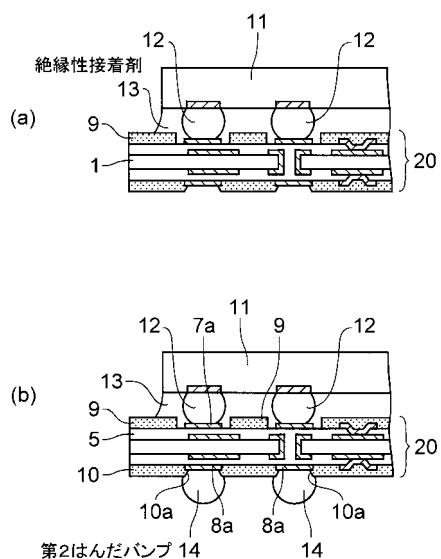

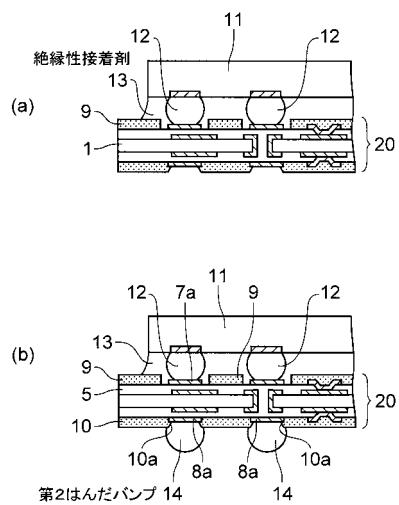

そこで、本実施形態では、この接合強度の不足を補うため、図3(a)に示すように、半導体素子11と第1ソルダーレジスト層9との間にエポキシ系のアンダーフィル樹脂を絶縁性接着材13として充填する。その絶縁性接着材13は、充填前には液状であるが、充填後には約150に加熱されて固化する。

【0039】

この絶縁性接着材13により、半導体素子11がインターポーザ20から剥がれ難くなり

30、半導体素子11と第1パッド7aとの接続不良を防止することができる。

【0040】

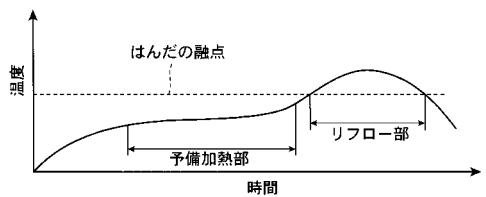

次いで、図3(b)に示すように、第1はんだバンプ12と同じ組成の共晶はんだよりなる第2はんだバンプ14を第2パッド8a上に載せ、熱風法や遠赤外線法によりその第2はんだバンプ14をリフローして第2パッド8a上に接合する。このリフローの温度プロファイルは、図5に示すように、共晶はんだの融点(約183)未満、例えば120

~140の温度に第2はんだバンプ14を50秒~70秒間加熱する予備加熱部と、それに引き続き行われるリフロー部とを有する。そして、リフロー部においては、共晶はんだの融点以上、例えば最低温度225でピーク温度が245の温度に第2はんだバンプ14を約40秒~60秒間加熱する。

40

【0041】

なお、リフロー前の第2はんだバンプ14のことをはんだボールと言う場合もある。

【0042】

このようなリフローによって溶融した第2はんだバンプ14は、冷却して固化することにより、第2パッド8a上に接合されることになる。

【0043】

以上により、本実施形態に係るBGAタイプの半導体パッケージの基本構造が完成する。

【0044】

上記した実施形態によれば、図3(b)の工程において第2はんだバンプ14をリフローする際、第2はんだバンプ14と同じ材料よりなる第1はんだバンプ12も溶融し、固化

50

した絶縁性接着材 13 内で熱膨張しようとするが、第 1 ソルダーレジスト 9 を第 1 電極パッド 7a に重ならないように形成したので、第 1 ソルダーレジスト 9 と第 1 電極パッド 7a との密着強度の弱い界面が存在せず、溶融した第 1 はんだバンプ 12 がその界面に沿って滲み出すことが無い。

【 0 0 4 5 】

これにより、滲み出したはんだによって隣接するはんだバンプ 12 同士が電気的にショートする危険性が低減されるので、半導体パッケージの歩留まりを向上させることができる。

【 0 0 4 6 】

なお、第 1 層間絶縁層 5 は、第 1 電極パッド 7a と比較して第 1 ソルダーレジスト層 9 との密着性が良いので、溶融したはんだが第 1 層間絶縁層 5 と第 1 ソルダーレジスト層 9 との界面から滲み出すことは殆ど無い。 10

【 0 0 4 7 】

また、上記では、第 2 はんだバンプ 14 のリフロー時ににおける第 1 はんだバンプ 12 の滲み出しを考えたが、第 1 はんだバンプ 12 が溶融するような温度の熱履歴がこの半導体パッケージに加わる場合でも上記と同様の利点を得ることができる。

【 0 0 4 8 】

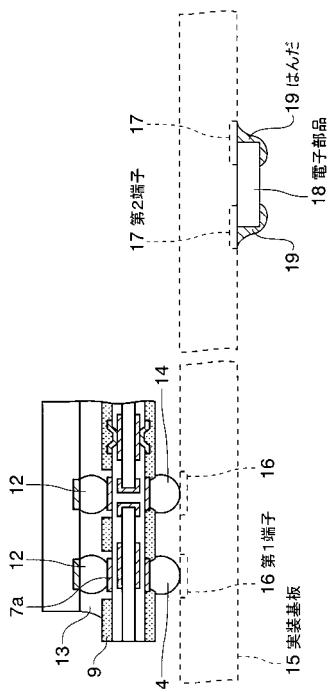

そのような熱履歴としては、図 4 の断面図に示すように、上記の半導体パッケージを実装基板 15 上に実装して半導体装置を作製する際に行われる種々のリフロー工程が挙げられる。 20

【 0 0 4 9 】

例えば、上記の実装を行うには、半導体パッケージの第 2 はんだバンプ 14 が実装基板 15 の第 1 端子 16 上に当接した状態で全体をリフロー雰囲気に置くが、このリフローにより、第 2 はんだバンプ 14 だけでなく、第 1 はんだバンプ 12 も溶融する。このように溶融しても、上記した理由によって、隣接する第 1 はんだバンプ 12 同士が電気的にショートするのを防ぐことができる。 30

【 0 0 5 0 】

更に、この実装が終了後、別の半導体パッケージやチップコンデンサ等の電子部品 18 をはんだ 19 によって実装基板 15 の第 2 端子 17 に電気的に接続する場合も、はんだ 19 を溶融するための熱が半導体パッケージに加わるが、この場合でも上記と同様の利点を得ることができる。

【 0 0 5 1 】

この電子部品 18 は、実装基板 15 の一方の面のみに実装してもよいし、両面に実装してもよい。特に、両面に実装する場合は、片面ずつ計 2 回のリフロー工程が行われ、各リフロー工程を行う度に第 1 はんだバンプ 12 が溶融するので、第 1 はんだバンプ 12 同士のショートの抑止効果が顕著に現れる。

【 0 0 5 2 】

以上、本発明の実施の形態について詳細に説明したが、本発明は上記実施形態に限定されない。

【 0 0 5 3 】

例えば、上記では可撓性のあるポリイミドフィルム 1 を使用したが、これに代えて、ガラス・エポキシ基板のようなリジッドな基板を使用してもよい。 40

【 0 0 5 4 】

また、上記では、全部で 4 層の配線層をインターポーザ 20 に形成したが、配線の積層数はこれに限定されず、配線層を 5 層以上形成してもよい。その場合は、最上層の配線層に上記の第 1 パッド 7a を形成し、最下層の配線層に上記の第 2 パッド 8a を形成すればよい。

【 0 0 5 5 】

更に、半導体素子 11 に代えて、半導体素子上に半導体素子の電極と接続した再配線層を形成し、該再配線層のパッドにはんだバンプを形成した CSP をインターポーザ 20 に搭 50

載する場合でも、上記した本発明を適用することができる。

【0056】

【発明の効果】

以上説明したように、本発明によれば、第1パッドの全ての側面が露出する大きさにソルダーレジスト層の開口を形成するので、溶融した第1はんだバンプが第1パッドとソルダーレジスト層との界面に滲み出さず、隣接する第1はんだバンプが電気的にショートする危険性を低減することができ、ひいては半導体パッケージや半導体装置の歩留まりを向上させることができる。

【図面の簡単な説明】

【図1】図1は、従来例に係る半導体パッケージの断面図である。

10

【図2】図2は、本発明の実施の形態に係る半導体パッケージの製造方法を工程順に示す断面図(その1)である。

【図3】図3は、本発明の実施の形態に係る半導体パッケージの製造方法を工程順に示す断面図(その2)である。

【図4】図4は、本発明の実施の形態に係る半導体装置の製造方法について示す断面図である。

【図5】図5は、本発明の実施の形態におけるリフローの温度プロファイルを示すグラフである。

【符号の説明】

1 … ポリイミドフィルム、 2 … 二層目金属配線層、 3 … 三層目金属配線層、 4 … スルーホール内銅めっき層、 5 … 第1層間絶縁層、 5 a … 第1ビアホール、 6 … 第2層間絶縁層、 6 a … 第2ビアホール、 7 … 一層目金属配線層、 7 a、 103 … 第1パッド、 8 … 四層目金属配線層、 8 a、 107 … 第2パッド、 9、 102 … 第1ソルダーレジスト層、 9 a … 第1開口、 10、 106 … 第2ソルダーレジスト層、 10 a … 第2開口、 11、 105 … 半導体素子、 11 a … 電極、 12、 104 … 第1はんだバンプ、 13、 109 … 絶縁性接着剤、 14、 108 … 第2はんだバンプ、 15、 111 … 実装基板、 16 … 第1端子、 17 … 第2端子、 18 … 電子部品、 101 … 絶縁性基材、 110 … インターポーザ。

20

【図1】

【図2】

本発明の実施の形態に係る半導体パッケージの

製造方法を工程順に示す断面図(その1)

【図3】

本発明の実施の形態に係る半導体パッケージの

製造方法を工程順に示す断面図(その2)

【図4】

本発明の実施の形態に係る半導体装置の製造方法について示す断面図

## 【図5】

本発明の実施の形態におけるリフローの温度プロファイルを示すグラフ

---

フロントページの続き

(72)発明者 坪田 崇

長野県長野市大字栗田字舎利田 711番地 新光電気工業株式会社内

(72)発明者 高津 浩幸

長野県長野市大字栗田字舎利田 711番地 新光電気工業株式会社内

F ターム(参考) 5F044 KK18 LL01 LL05 QQ03