(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5084169号

(P5084169)

(45) 発行日 平成24年11月28日(2012.11.28)

(24) 登録日 平成24年9月14日(2012.9.14)

(51) Int.Cl.

F 1

|                    |                  |             |      |

|--------------------|------------------|-------------|------|

| <b>HO1L 21/336</b> | <b>(2006.01)</b> | HO1L 29/78  | 617V |

| <b>HO1L 29/786</b> | <b>(2006.01)</b> | HO1L 29/78  | 626C |

| <b>HO1L 21/316</b> | <b>(2006.01)</b> | HO1L 29/78  | 619A |

| <b>HO1L 21/318</b> | <b>(2006.01)</b> | HO1L 29/78  | 618C |

|                    |                  | HO1L 21/316 | A    |

請求項の数 13 (全 47 頁) 最終頁に続く

(21) 出願番号

特願2006-122941 (P2006-122941)

(22) 出願日

平成18年4月27日 (2006.4.27)

(65) 公開番号

特開2006-332634 (P2006-332634A)

(43) 公開日

平成18年12月7日 (2006.12.7)

審査請求日

平成21年1月21日 (2009.1.21)

(31) 優先権主張番号

特願2005-133680 (P2005-133680)

(32) 優先日

平成17年4月28日 (2005.4.28)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 磯部 敦生

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 村上 智史

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 高野 圭恵

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が0.5eV以上1.5eV以下の条件下でプラズマ処理を行うことにより、前記半導体膜の表面に酸化膜を形成し、前記酸化膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が0.5eV以上1.5eV以下の条件下でプラズマ処理を行うことにより、前記酸化膜の表面を窒化し、

前記表面が窒化された酸化膜を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

基板上に第1の絶縁膜を形成し、

前記第1の絶縁膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が0.5eV以上1.5eV以下の条件下でプラズマ処理を行うことにより、前記第1の絶縁膜の表面を酸化または窒化し、

前記表面が酸化または窒化された第1の絶縁膜上に半導体膜を形成し、

前記半導体膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が0.5eV以上1.5eV以下の条件下でプラズマ処理を行うことによ

10

20

り、前記半導体膜の表面に酸化膜を形成し、

前記酸化膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより

、前記酸化膜の表面を窒化し、

前記表面が窒化された酸化膜を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

#### 【請求項3】

基板上に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより

10

、前記半導体膜の表面に酸化膜を形成し、

前記酸化膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより

10

、前記酸化膜の表面を窒化し、

前記表面が窒化された酸化膜を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより、前記第2の絶縁膜の表面を酸化または窒化し、

10

前記表面が酸化または窒化された第2の絶縁膜上にゲート電極を形成することを特徴とする半導体装置の作製方法。

#### 【請求項4】

基板上に第1の絶縁膜を形成し、

前記第1の絶縁膜上に半導体膜を形成し、

前記半導体膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより

10

、前記半導体膜の表面に酸化膜を形成し、

前記酸化膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより

10

、前記酸化膜の表面を窒化し、

前記表面が窒化された酸化膜を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜上にゲート電極を形成し、

前記ゲート電極を覆って第3の絶縁膜を形成し、

前記第3の絶縁膜に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより、前記第3の絶縁膜の表面を酸化または窒化し、

30

前記表面が酸化または窒化された第3の絶縁膜上に導電膜を形成することを特徴とする半導体装置の作製方法。

#### 【請求項5】

請求項4において、

40

前記第3の絶縁膜として、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、またはシロキサン樹脂を形成することを特徴とする半導体装置の作製方法。

#### 【請求項6】

請求項1乃至5のいずれか一において、

前記半導体膜の端部がテーパー形状であることを特徴とする半導体装置の作製方法。

#### 【請求項7】

請求項1乃至6のいずれか一において、

前記基板に対し、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより、

50

前記基板の表面を酸化または窒化することを特徴とする半導体装置の作製方法。

**【請求項 8】**

請求項 1 乃至 7 のいずれか一において、

前記第 1 の絶縁膜として、酸化珪素 (SiO<sub>x</sub>)、窒化珪素 (SiN<sub>x</sub>)、酸化窒化珪素 (SiO<sub>x</sub>N<sub>y</sub>) ( $x > y$ )、または窒化酸化珪素 (SiN<sub>x</sub>O<sub>y</sub>) ( $x > y$ ) を形成することを特徴とする半導体装置の作製方法。

**【請求項 9】**

請求項 1 乃至 8 のいずれか一において、

前記第 2 の絶縁膜として、酸化珪素 (SiO<sub>x</sub>)、窒化珪素 (SiN<sub>x</sub>)、酸化窒化珪素 (SiO<sub>x</sub>N<sub>y</sub>) ( $x > y$ )、または窒化酸化珪素 (SiN<sub>x</sub>O<sub>y</sub>) ( $x > y$ ) を形成することを特徴とする半導体装置の作製方法。 10

**【請求項 10】**

請求項 1 乃至 9 のいずれか一において、

前記プラズマ処理を行う際にマイクロ波を用いることを特徴とする半導体装置の作製方法。

**【請求項 11】**

請求項 1 乃至 10 のいずれか一において、

前記プラズマ処理による酸化を、酸素と希ガスとを含む雰囲気下または酸素と水素と希ガスとを含む雰囲気下で行うことを行なうことを特徴とする半導体装置の作製方法。

**【請求項 12】**

請求項 1 乃至 10 のいずれか一において、

前記プラズマ処理による窒化を、窒素と希ガスとを含む雰囲気下またはNH<sub>3</sub>と希ガスとを含む雰囲気下で行うことを行なうことを特徴とする半導体装置の作製方法。 20

**【請求項 13】**

請求項 1 乃至 12 のいずれか一において、

前記基板として、ガラス基板またはプラスチック基板を用いることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

30

本発明は、導電膜、絶縁膜または半導体膜等を積層させて形成させる場合において、当該絶縁膜または半導体膜にプラズマ処理を行い表面の改質を行うことによって、良質の膜を有する半導体装置および当該半導体装置の作製方法に関する。

**【背景技術】**

**【0002】**

40

近年、ガラス等の絶縁表面を有する基板上に形成された半導体薄膜（厚さ数nm～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタは、ICや電気光学装置のような半導体装置に広く応用され、半導体装置の小型化または高性能化の要求に伴い、より微細な構造を有する薄膜トランジスタの開発が求められている。より微細で高性能な薄膜トランジスタを作製するためには、ゲート電極やソースおよびドレイン配線等の導電膜だけでなく、ゲート絶縁膜を初めとする絶縁膜を薄く設ける必要がある。通常、薄膜トランジスタのゲート絶縁膜等の絶縁膜は、CVD法等を用いて形成されている（例えば、特許文献1）。

**【0003】**

**【特許文献1】特開2001-135824号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

しかしながら、CVD法やスパッタ法により数nmの膜厚で形成した絶縁膜は、膜の内部に欠陥を有し、膜質が十分でないため、例えばCVD法で形成した絶縁膜をゲート絶縁

50

膜として用いる場合、リーク電流の発生や半導体膜とゲート電極間のショート等の恐れがある。また、熱酸化法によって、例えば、半導体膜の表面を酸化させることによって緻密な絶縁膜を形成することができるが、薄膜トランジスタの作製においては、コストの面からガラス等の耐熱性の低い基板を用いるため、熱酸化法を利用することは困難である。

#### 【0005】

本発明は上記問題を鑑み、導電膜、絶縁膜または半導体膜等を積層させて形成させる場合において、CVD法やスパッタ法等で形成した膜に比べて、緻密で欠陥が少ない良質な膜を形成する半導体装置の作製方法および半導体装置の提供を課題とする。

#### 【課題を解決するための手段】

#### 【0006】

本発明の半導体装置の作製方法は、基板上に第1の絶縁膜を形成し、第1の絶縁膜上に半導体膜を形成し、当該半導体膜に高周波を用いて電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより半導体膜を酸化または窒化し、半導体膜を覆って第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極を形成し、ゲート電極を覆って第3の絶縁膜を形成し、第3の絶縁膜上に導電膜を形成することを特徴としている。

#### 【0007】

また、本発明では上記構成において、基板、第1の絶縁膜、第2の絶縁膜または第3の絶縁膜にプラズマ処理を行い酸化または窒化を行うことも可能である。

#### 【0008】

本発明において、プラズマ処理により半導体膜または絶縁膜を酸化するとは、高周波を用いたプラズマ励起により活性化された酸素ラジカルや酸素イオン等の酸素種を当該半導体膜または絶縁膜に直接作用させて酸化または窒化を行うことをいう。また、プラズマ処理により半導体膜または絶縁膜を窒化するとは、高周波を用いたプラズマ励起により活性化された窒素ラジカルや窒素イオン等の窒素種を当該半導体膜または絶縁膜に直接作用させて酸化または窒化を行うことをいう。

#### 【0009】

本発明の他の半導体装置の作製方法は、基板上に第1の絶縁膜を形成し、第1の絶縁膜上に端部がテーパー形状を有する半導体膜を形成し、半導体膜の端部に選択的に高周波を用いて電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下の条件下でプラズマ処理を行うことにより半導体膜の端部を選択的に酸化または窒化し、半導体膜を覆って第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極を形成し、ゲート電極を覆って第3の絶縁膜を形成し、第3の絶縁膜上に導電膜を形成することを特徴としている。

#### 【0010】

本発明の半導体装置は、絶縁表面上に設けられた半導体膜と、半導体膜の上方にゲート絶縁膜を介して設けられたゲート電極と、ゲート電極を覆って設けられた絶縁膜と、絶縁膜上に設けられた導電膜とを有し、半導体膜の端部が酸化または窒化されていることを特徴としている。また、半導体膜の端部をテーパー形状に設けることも可能である。

#### 【発明の効果】

#### 【0011】

プラズマ処理により半導体膜または絶縁膜を酸化または窒化して、当該半導体膜または絶縁膜の表面を改質することによって、緻密な表面を有する絶縁膜を得ることができるために、特性の高い半導体素子を有する半導体装置を作製することができる。

#### 【発明を実施するための最良の形態】

#### 【0012】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々なに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の

10

20

30

40

50

構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

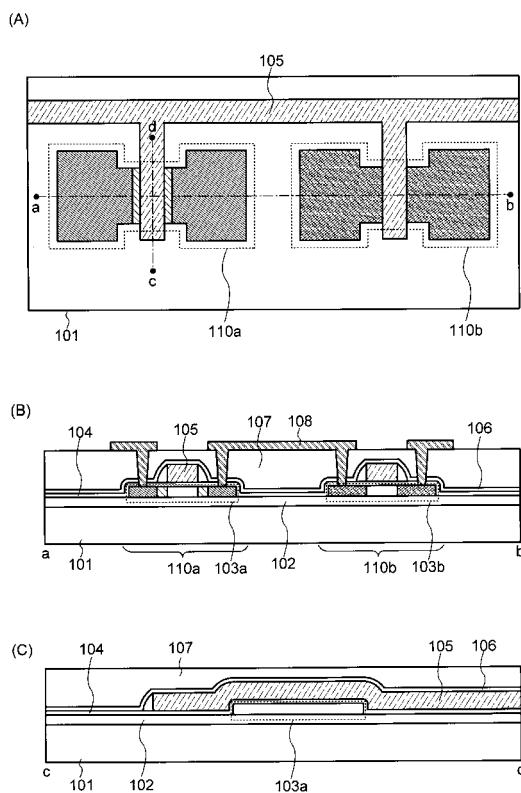

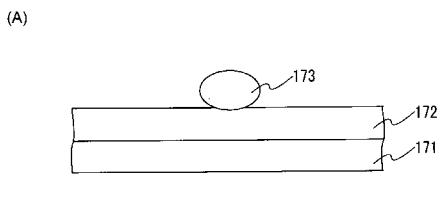

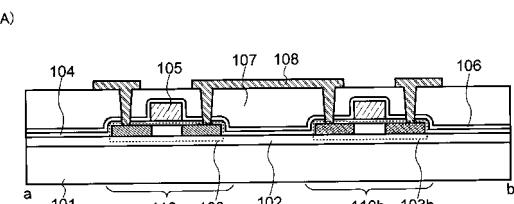

**【0013】**

本発明の半導体装置の一例を図1に示す。なお、図1において、図1(B)は図1(A)のa-b間に断面図に相当し、図1(C)は図1(A)のc-d間に断面図に相当する。

**【0014】**

図1に示す半導体装置は、基板101上に絶縁膜102を介して設けられた半導体膜103a、103bと、当該半導体膜103a、103b上にゲート絶縁膜104を介して設けられたゲート電極105と、ゲート電極を覆って設けられた絶縁膜106、107と、半導体膜103a、103bのソース領域またはドレイン領域と電気的に接続し且つ絶縁膜107上に設けられた導電膜108とを有している。なお、図1においては、半導体膜103aの一部をチャネル形成領域として用いたn型の薄膜トランジスタ110aと半導体膜103bの一部をチャネル形成領域として用いたp型の薄膜トランジスタ110bとを設けた場合を示している。

**【0015】**

基板101は、バリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板またはステンレスを含む金属基板等を用いることができる。他にも、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。可撓性を有する基板を用いることによって、折り曲げが可能である半導体装置を作製することが可能となる。また、このような基板であれば、その面積や形状に大きな制限はないため、基板101として、例えば、1辺が1メートル以上あって、矩形状のものを用いれば、生産性を格段向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。

**【0016】**

絶縁膜102は、下地膜として機能し、基板101からNaなどのアルカリ金属やアルカリ土類金属が、半導体膜103a、103b中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。絶縁膜102としては、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiNx)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)( $x > y$ )、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)( $x > y$ )等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。例えば、絶縁膜102を2層構造で設ける場合、1層目の絶縁膜として窒化酸化珪素膜で設け、2層目の絶縁膜として酸化窒化珪素膜を設けるとよい。また、絶縁膜102を3層構造で設ける場合、1層目の絶縁膜として酸化窒化珪素膜を設け、2層目の絶縁膜として窒化酸化珪素膜を設け、3層目の絶縁膜として酸化窒化珪素膜を設けるとよい。

**【0017】**

半導体膜103a、103bは、非晶質(アモルファス)半導体またはセミアモルファス半導体(SAS)で形成することができる。また多結晶半導体膜を用いていても良い。SASは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5~20nmの結晶領域を観測することができ、珪素を主成分とする場合にはラマンスペクトルが520cm<sup>-1</sup>よりも低波数側にシフトしている。X線回折では珪素結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。未結合手(ダンギングボンド)を終端化させるため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。SASは、珪素を含む気体をグロー放電分解(プラズマCVD)して形成する。珪素を含む気体としては、SiH<sub>4</sub>、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることが可能である。またGeF<sub>4</sub>を混合させても良い。この珪素を含む気体をH<sub>2</sub>、またはH<sub>2</sub>とHe、Ar、Kr、Neから選ばれた一種

10

20

30

40

50

または複数種の希ガス元素で希釈してもよい。希釈率は2~1000倍の範囲にする。圧力は概略0.1Pa~133Paの範囲、電源周波数は1MHz~120MHz、好ましくは13MHz~60MHz、基板加熱温度は300以下でよい。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は $1 \times 10^{-20}$ cm<sup>-1</sup>以下とすることが望ましく、特に、酸素濃度は $5 \times 10^{-9}$ /cm<sup>3</sup>以下、好ましくは $1 \times 10^{-9}$ /cm<sup>3</sup>以下とする。ここでは、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>1-x</sub>等)で非晶質半導体膜を形成し、当該非晶質半導体膜をレーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法などの公知の結晶化法により結晶化させる。また、結晶化の方法として、他にもDCバイアスを印加して熱プラズマを発生することにより、当該熱プラズマを半導体膜に作用することによって行ってもよい。

10

#### 【0018】

ゲート絶縁膜104は、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。

#### 【0019】

絶縁膜106は、スパッタ法やプラズマCVD法等により、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜や DLC(ダイヤモンドライカーボン)等の炭素を含む膜の単層構造、またはこれらの積層構造で設けることができる。

20

#### 【0020】

絶縁膜107は、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜や DLC(ダイヤモンドライカーボン)等の炭素を含む膜はもちろん、その他にもエポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料やシロキサン樹脂からなる単層または積層構造で設けることができる。なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。なお、図1における半導体装置において、絶縁膜106を設けずにゲート電極105を覆うように直接絶縁膜107を設けることも可能である。

30

#### 【0021】

導電膜108としては、アルミニウム(A1)、チタン(Ti)、タンゲステン(W)、ニッケル(Ni)、炭素(C)、モリブデン(Mo)、白金(Pt)、銅(Cu)、タンタル(Ta)、金(Au)、マンガン(Mn)から選ばれた一種の元素または当該元素を複数含む合金からなる単層または積層構造を用いることができる。例えば、当該元素を複数含む合金からなる導電膜として、例えばCとTiを含有したA1合金、Niを含有したA1合金、CとNiを含有したA1合金、CとMnを含有したA1合金等を用いることができる。また、積層構造で設ける場合、A1とTiを積層させることによって設けることができる。

40

#### 【0022】

また、図1において、n型の薄膜トランジスタ110aはゲート電極105の側壁に接してサイドウォール111を有し、半導体膜103aにn型の導電性を付与する不純物が選択的に添加されたソース領域、ドレイン領域およびサイドウォールの下方に設けられたLDD領域が形成されている。また、p型の薄膜トランジスタ110bはゲート電極105の側壁に接してサイドウォールを有し、半導体膜103bにp型の導電性を付与する不純物が選択的に添加されたソース領域およびドレイン領域が形成されている。なお、本発

50

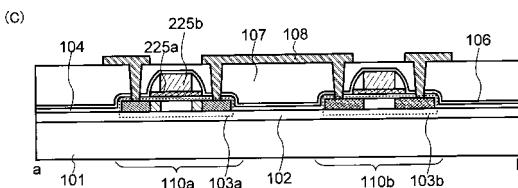

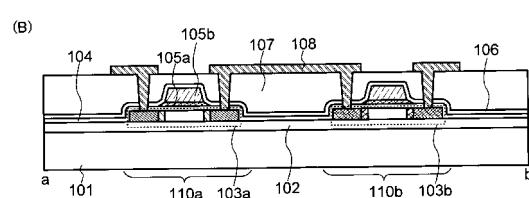

明の半導体装置に含まれる薄膜トランジスタの構造は上述した構造に限られない。例えば、図1では、n型の薄膜トランジスタ110aにLDD領域を設け、p型の薄膜トランジスタ110bにはLDD領域を設けていないが、両方にLDD領域を設けた構成としてもよいし、両方にLDD領域およびサイドウォールを設けない構造(図26(A))としても可能である。また、薄膜トランジスタの構造として上述した構造に限らず、チャネル形成領域が1つ形成されるシングルゲート構造でもよいし、2つ形成されるダブルゲート構造または3つ形成されるトリプルゲート構造等のマルチゲート構造を用いることができる。また、ボトムゲート構造としてもよいし、チャネル形成領域の上下にゲート絶縁膜を介して配置された2つのゲート電極を有するデュアルゲート型としてもよい。また、ゲート電極を積層構造で設ける場合に、ゲート電極下方に形成される第1の導電膜105aと当該第1の導電膜105a上に形成される第2の導電膜105bで設け、当該第1の導電膜をテーパー状で形成し、第1の導電膜にのみ重なるようにソースまたはドレイン領域として機能する不純物領域より低い濃度の不純物領域を設ける構造(図26(B))で設けることもできる。また、ゲート電極を積層構造で設ける場合に、ゲート電極の下方に形成される第1の導電膜225aと当該第1の導電膜225a上に形成される第2の導電膜225bで設け、当該第2の導電膜225bの側壁に接し且つ導電膜225aの上方に形成されるようにサイドウォールを設ける構造(図26(C))としても可能である。なお、上記構成において、半導体膜103a、103bのソースまたはドレイン領域として機能する不純物領域をNi、Co、W等のシリサイドで設けることも可能である。

## 【0023】

10

なお、本発明の半導体装置では、上記基板101、絶縁膜102、半導体膜103aおよび103b、ゲート絶縁膜104、絶縁膜106または絶縁膜107のうち少なくともいずれか一層に、プラズマ処理を用いて酸化処理または窒化処理を行うことにより半導体膜または絶縁膜を酸化または窒化する。このように、プラズマ処理を用いて半導体膜または絶縁膜を酸化または窒化することによって、当該半導体膜または絶縁膜の表面を改質し、CVD法やスパッタ法により形成した絶縁膜と比較してより緻密な絶縁膜を形成することができるため、膜に生じるピンホール等の欠陥を抑制し半導体装置の特性を向上させることができる。なお、上記構成において、半導体膜103a、103bのソースまたはドレイン領域として機能する不純物領域をNi、Co、W等のシリサイドで設けることも可能となる。

## 【0024】

20

以下に図面を参照して、プラズマ処理を用いて半導体装置を作製する方法を説明する。具体的には、プラズマ処理を用いて、基板101、絶縁膜102、半導体膜103aおよび103b、ゲート絶縁膜104、絶縁膜106または絶縁膜107を酸化または窒化させて半導体装置を作製する場合について説明する。

## 【0025】

30

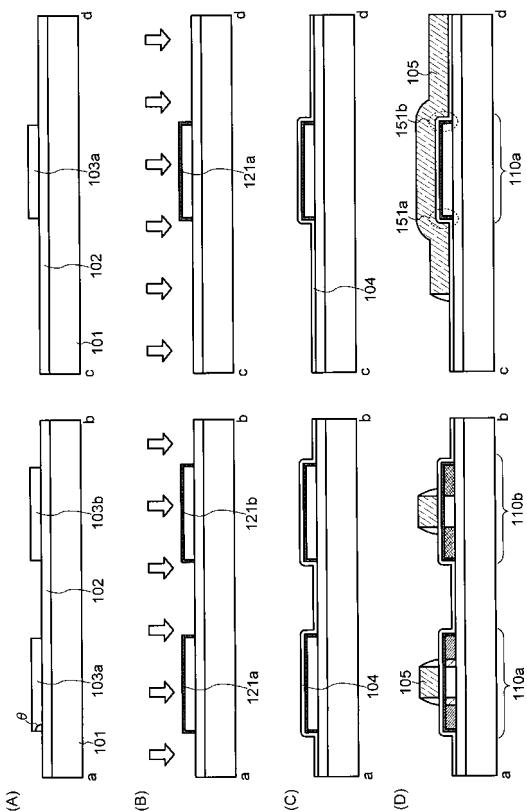

## (実施の形態1)

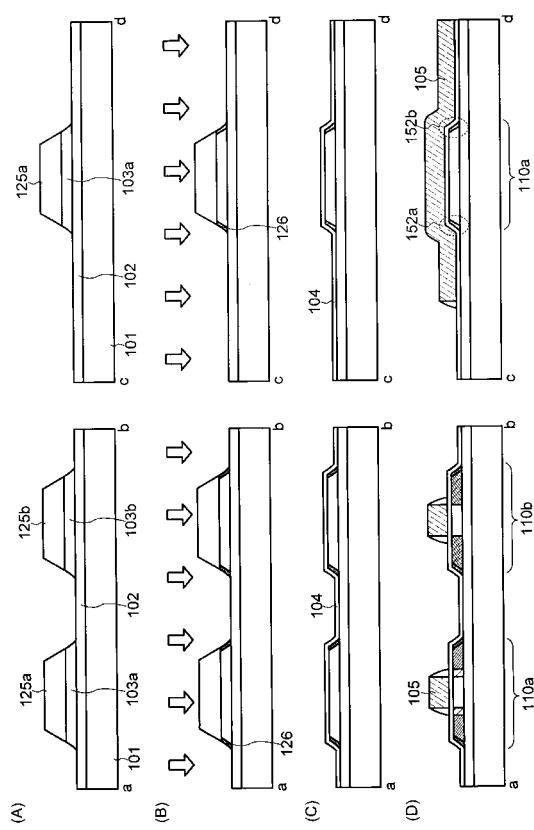

本実施の形態では、上記図1における半導体膜103aおよび103bまたはゲート絶縁膜104にプラズマ処理を行い、当該半導体膜103aおよび103bまたはゲート絶縁膜104に酸化処理または窒化処理を行うことによって半導体装置を作製する方法について図面を参照して説明する。

## 【0026】

40

はじめに、基板上に設けられた島状の半導体膜において、当該島状の半導体膜の端部を直角に近い形状で設ける場合について示す。

## 【0027】

まず、基板101上に島状の半導体膜103a、103bを形成する(図2(A))。島状の半導体膜103a、103bは、基板101上にあらかじめ形成された絶縁膜102上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えば $Si_xGe_{1-x}$ 等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させ、半導体膜を選択的にエッチングすることにより設けることができる。なお、非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら

50

方法を組み合わせた方法等により行うことができる。なお、図2では、島状の半導体膜103a、103bの端部を直角に近い形状(85°～100°)で設ける。

#### 【0028】

次に、プラズマ処理を行い半導体膜103a、103bに酸化処理または窒化処理を行うことによって、当該半導体膜103a、103bの表面にそれぞれ酸化膜、窒化膜121a、121b(以下、絶縁膜121a、絶縁膜121bとも記す)を形成する(図2(B))。なお、半導体膜103a、103bに酸化処理または窒化処理を行う前に前処理としてAr雰囲気下でプラズマ処理を行ってもよい。

#### 【0029】

例えは、半導体膜103a、103bとしてSiを用いた場合、絶縁膜121aおよび絶縁膜121bとして、酸化珪素(SiO<sub>x</sub>)または窒化珪素(SiN<sub>x</sub>)が形成される。また、プラズマ処理により半導体膜103a、103bを酸化させた後に、再度プラズマ処理を行うことによって窒化させてもよい。この場合、半導体膜103a、103bに接して酸化珪素(SiO<sub>x</sub>)が形成され、当該酸化珪素の表面に酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)または窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)が形成される。

#### 【0030】

なお、プラズマ処理により半導体膜を酸化する場合には、酸素を含む雰囲気下(例えは、酸素(O<sub>2</sub>)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、酸素と水素(H<sub>2</sub>)と希ガス雰囲気下、一酸化二窒素と希ガス雰囲気下または一酸化二窒素と水素と希ガス雰囲気下)でプラズマ処理を行う。一方、プラズマ処理により半導体膜を窒化する場合には、窒素を含む雰囲気下(例えは、窒素(N<sub>2</sub>)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下または窒素と水素と希ガス雰囲気下またはNH<sub>3</sub>と希ガス雰囲気下)でプラズマ処理を行う。

#### 【0031】

希ガスとしては、例えは、Arを用いることができる。また、ArとKrを混合したガスを用いてもよい。また、絶縁膜121a、121bには、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)が含まれており、Arを用いた場合には絶縁膜121a、121bにArが含まれている。

#### 【0032】

本実施の形態では、プラズマ処理により半導体膜103a、103bに酸化処理を行う場合、酸素(O<sub>2</sub>)、水素(H<sub>2</sub>)とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、酸素を0.1～100sccm、水素を0.1～100sccm、アルゴンを100～5000sccmとして導入すればよい。なお、酸素：水素：アルゴン=1:1:100の比率で混合ガスを導入することが好ましい。例えは、酸素を5sccm、水素を5sccm、アルゴンを500sccmとして導入すればよい。

#### 【0033】

なお、プラズマ処理による酸化よりの工程において、酸化膜に希ガスが含有されていることが推測されるため、基板上に本工程のプラズマ処理を行って酸化膜を形成したサンプルを作製し、このサンプルについてTXRFを用いて測定を行った。ここでは、希ガスとしてArを用いてプラズマ処理を行った。その結果、酸化膜にはArが1×10<sup>15</sup>～1×10<sup>16</sup>atoms/cm<sup>3</sup>程度の濃度で含有されていた。よって、プラズマ処理に用いた希ガスがこの工程で形成される酸化膜に同程度(1×10<sup>15</sup>～1×10<sup>16</sup>atoms/cm<sup>3</sup>)含有されている。

#### 【0034】

また、プラズマ処理により窒化処理を行う場合、窒素(N<sub>2</sub>)とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、窒素を20～2000sccm、アルゴンを100～10000sccmとして導入すればよい。例えは、窒素を200sccm、アルゴンを1000sccmとして導入すればよい。

#### 【0035】

また、プラズマ処理は、上記ガスの雰囲気中において、電子密度が1×10<sup>11</sup>cm<sup>-3</sup>

10

20

30

40

50

<sup>3</sup>以上であり、プラズマの電子温度が1.5eV以下で行う。より詳しくいうと、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下で、プラズマの電子温度が0.5eV以上1.5eV以下で行う。プラズマの電子密度が高密度であり、基板101上に形成された被処理物（ここでは、半導体膜103a、103b）付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止することができる。また、プラズマの電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上と高密度であるため、プラズマ処理を用いて、被照射物を酸化または窒化することによって形成される酸化物または窒化膜は、CVD法やスパッタ法等により形成された膜と比較して膜厚等が均一性に優れ、且つ緻密な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で酸化または窒化処理を行うことができる。例えば、ガラス基板の歪点よりも100度以上低い温度でプラズマ処理を行っても十分に酸化または窒化処理を行うことができる。プラズマを形成するための周波数としては、マイクロ波（2.45GHz）等の高周波を用いることができる。

10

#### 【0036】

なお、以下に特に断らない場合は本明細書中において、プラズマ処理によって被処理物に酸化処理または窒化処理を行う場合は上記条件を用いて行うことができる。

#### 【0037】

次に、絶縁膜121a、121bを覆うようにゲート絶縁膜104を形成する（図2（C））。ゲート絶縁膜104は、スパッタ法、LPCVD法、プラズマCVD法等を用いて、酸化珪素（SiO<sub>x</sub>）、窒化珪素（SiN<sub>x</sub>）、酸化窒化珪素（SiO<sub>x</sub>N<sub>y</sub>）（x>y）、窒化酸化珪素（SiN<sub>x</sub>O<sub>y</sub>）（x>y）等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。例えば、半導体膜103a、103bとしてSiを用い、プラズマ処理により当該Siを酸化させることによって当該半導体膜103a、103b表面に絶縁膜121a、121bとして酸化珪素を形成した場合、当該絶縁膜121a、121b上にゲート絶縁膜104として酸化珪素（SiO<sub>x</sub>）を形成する。また、膜厚を薄く形成した場合等は、上記図2（B）において、プラズマ処理により半導体膜103a、103bを酸化または窒化することによって形成された絶縁膜121a、121bをゲート絶縁膜として用い、当該絶縁膜121a、121b上にゲート電極105を形成することも可能である。

20

#### 【0038】

次に、ゲート絶縁膜104上にゲート電極105等を形成することによって、ゲート電極105の下方に位置する半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製することができる（図2（D））。

#### 【0039】

このように、半導体膜103a、103b上にゲート絶縁膜104を設ける前に、プラズマ処理により半導体膜103a、103bの表面を酸化または窒化することによって、チャネル形成領域の端部151a、151b等におけるゲート絶縁膜104の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。つまり、島状の半導体膜の端部が直角に近い形状（85°～100°）を有する場合には、CVD法やスパッタ法等により半導体膜を覆うようにゲート絶縁膜を形成した際に、半導体膜の端部においてゲート絶縁膜の段切れ等による被覆不良の問題が生じる恐れがあるが、あらかじめ半導体膜の表面にプラズマ処理を用いて酸化または窒化しておくことによって、半導体膜の端部におけるゲート絶縁膜の被覆不良等を防止することが可能となる。

40

#### 【0040】

また、上記図2において、ゲート絶縁膜104を形成した後にプラズマ処理を行うことによって、ゲート絶縁膜104を酸化または窒化させてもよい。この場合、半導体膜103a、103bを覆うようにゲート絶縁膜104を形成し（図3（A））、当該ゲート絶縁膜104にプラズマ処理を行い、ゲート絶縁膜104を酸化または窒化することによって、ゲート絶縁膜104の表面に酸化膜または窒化膜123（以下、絶縁膜123とも記

50

す)を形成する(図3(B))。プラズマ処理の条件は、上記図2(B)と同様に行うことによりできる。また、絶縁膜123は、プラズマ処理に用いた希ガスを含んでおり、例えばArを用いた場合には絶縁膜123にArが含まれている。

#### 【0041】

また、図3(B)において、一旦酸素を含む雰囲気下でプラズマ処理を行うことによりゲート絶縁膜104を酸化させた後に、再度窒素を含む雰囲気下でプラズマ処理を行うことにより窒化させてもよい。この場合、半導体膜103a、103bに酸化珪素(SiO<sub>x</sub>)または酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)が形成され、ゲート電極105に接して酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)または窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)からなるサイドウォールが形成される。その後、絶縁膜123上にゲート電極105等を形成することによって、ゲート電極105の下方に位置する半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製することができる(図3(C))。このように、ゲート絶縁膜にプラズマ処理を行うことにより、当該ゲート絶縁膜の表面を酸化または窒化することによって、ゲート絶縁膜の表面を改質し緻密な膜を形成することができる。プラズマ処理を行うことによって得られた絶縁膜は、CVD法やスパッタ法で形成された絶縁膜と比較して緻密でピンホール等の欠陥も少ないため、薄膜トランジスタの特性を向上させることができる。10

#### 【0042】

なお、図3においては、あらかじめ半導体膜103a、103bにプラズマ処理を行うことによって、当該半導体膜103a、103bの表面を酸化または窒化させた場合を示したが、半導体膜103a、103bにプラズマ処理を行わずにゲート絶縁膜104を形成した後にプラズマ処理を行う方法を用いてもよい。このように、ゲート電極を形成する前にプラズマ処理を行うことによって、半導体膜の端部においてゲート絶縁膜の段切れ等による被覆不良が生じた場合であっても、被覆不良により露出した半導体膜を酸化または窒化することができるため、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。20

#### 【0043】

このように、島状の半導体膜の端部を直角に近い形状で設けた場合であっても、半導体膜またはゲート絶縁膜にプラズマ処理を行い、当該半導体膜またはゲート絶縁膜を酸化または窒化することによって、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。30

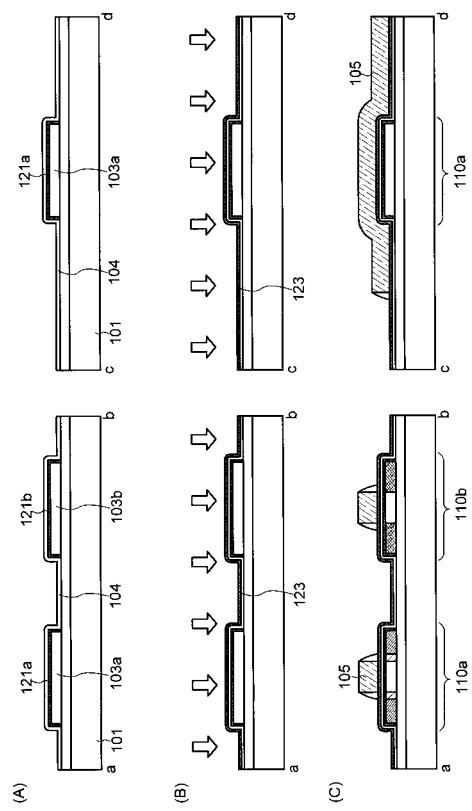

#### 【0044】

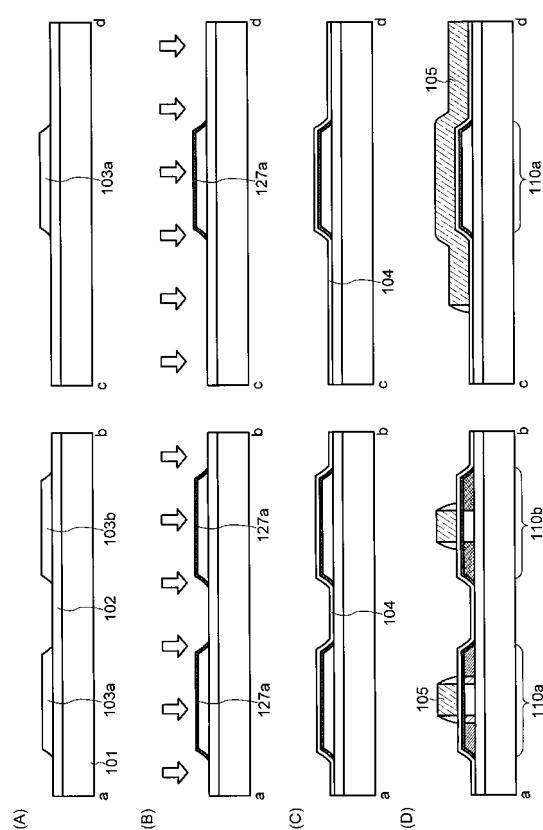

次に、基板上に設けられた島状の半導体膜において、当該島状の半導体膜の端部をテーパー形状(30°<85°)で設ける場合について示す。

#### 【0045】

まず、基板101上に島状の半導体膜103a、103bを形成する(図4(A))。島状の半導体膜103a、103bは、基板101上にあらかじめ形成された絶縁膜102上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>1-x</sub>等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜をレーザ結晶化法、RTA又はファーネスアーニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法などの結晶化法により結晶化させ、選択的に半導体膜をエッチングして除去することにより設けることができる。なお、図4では、島状の半導体膜の端部をテーパー形状(30°<85°)で設ける。40

#### 【0046】

次に、半導体膜103a、103bを覆うようにゲート絶縁膜104を形成する(図4(B))。ゲート絶縁膜104は、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いて、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。50

## 【0047】

次に、プラズマ処理を行いゲート絶縁膜104に酸化処理または窒化処理を行うことによって、当該ゲート絶縁膜104の表面にそれぞれ酸化膜または窒化膜124（以下、絶縁膜124とも記す）を形成する（図4（C））。なお、プラズマ処理の条件は上記と同様に行うことができる。例えば、ゲート絶縁膜104として酸化珪素（SiO<sub>x</sub>）または酸化窒化珪素（SiO<sub>x</sub>N<sub>y</sub>）（x > y）を用いた場合、酸素を含む雰囲気下でプラズマ処理を行いゲート絶縁膜104を酸化することによって、ゲート絶縁膜の表面にはCVD法やスパッタ法等により形成されたゲート絶縁膜と比較してピンホール等の欠陥の少ない緻密な膜を形成することができる。一方、窒素を含む雰囲気下でプラズマ処理を行いゲート絶縁膜104を窒化することによって、ゲート絶縁膜104の表面に絶縁膜124として酸化窒化珪素（SiO<sub>x</sub>N<sub>y</sub>）（x > y）または窒化酸化珪素（SiN<sub>x</sub>O<sub>y</sub>）（x > y）を設けることができる。また、一旦酸素を含む雰囲気下でプラズマ処理を行うことによりゲート絶縁膜104を酸化させた後に、再度窒素を含む雰囲気下でプラズマ処理を行うことにより窒化させてもよい。また、絶縁膜124は、プラズマ処理に用いた希ガスを含んでおり、例えばArを用いた場合には絶縁膜124中にArが含まれている。

## 【0048】

次に、絶縁膜124上にゲート電極105等を形成することによって、ゲート電極105の下方に位置する半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製することができる（図4（D））。

## 【0049】

このように、ゲート絶縁膜にプラズマ処理を行うことにより、ゲート絶縁膜の表面に酸化膜または窒化膜からなる絶縁膜を設け、ゲート絶縁膜の表面の改質をすることができる。プラズマ処理を行うことによって酸化または窒化された絶縁膜は、CVD法やスパッタ法で形成されたゲート絶縁膜と比較して緻密でピンホール等の欠陥も少ないため、薄膜トランジスタの特性を向上させることができる。また、半導体膜の端部をテーパー形状とすることによって、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を抑制することができるが、ゲート絶縁膜を形成した後にプラズマ処理を行うことによって、より一層ゲート電極と半導体膜のショート等を防止することができる。

## 【0050】

次に、図4とは、異なる半導体装置の作製方法に関して図面を参照して説明する。具体的には、テーパー形状を有する半導体膜の端部に選択的にプラズマ処理を行う場合について示す。

## 【0051】

まず、基板101上に島状の半導体膜103a、103bを形成する（図5（A））。島状の半導体膜103a、103bは、基板101上にあらかじめ形成された絶縁膜102上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン（Si）を主成分とする材料（例えばSi<sub>x</sub>Ge<sub>1-x</sub>等）等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させ、レジスト125a、125bをマスクとして半導体膜を選択的にエッチングすることにより設けることができる。なお、非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら方法を組み合わせた方法等の結晶化法により行うことができる。

## 【0052】

次に、半導体膜のエッチングのために使用したレジスト125a、125bを除去する前に、プラズマ処理を行い島状の半導体膜103a、103bの端部を選択的に酸化または窒化することによって、当該半導体膜103a、103bの端部にそれぞれ酸化膜または窒化膜126（以下、絶縁膜126とも記す）を形成する（図5（B））。プラズマ処理は、上述した条件下で行う。また、絶縁膜126は、プラズマ処理に用いた希ガスを含

んでいる。

**【0053】**

次に、半導体膜103a、103bを覆うようにゲート絶縁膜104を形成する(図5(C))。ゲート絶縁膜104は、上記と同様に設けることができる。

**【0054】**

次に、ゲート絶縁膜104上にゲート電極105等を形成することによって、島状の半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製することができる(図5(D))。

**【0055】**

半導体膜103a、103bの端部をテーパー形状に設けた場合、半導体膜103a、103bの一部に形成されるチャネル形成領域の端部152a、152bもテーパー形状となり半導体膜の膜厚やゲート絶縁膜の膜厚が中央部分と比較して変化するため、薄膜トランジスタの特性に影響を及ぼす場合がある。そのため、ここではプラズマ処理によりチャネル形成領域の端部を選択的に酸化または窒化して、当該チャネル形成領域の端部となる半導体膜に絶縁膜を形成することによって、チャネル形成領域の端部に起因する薄膜トランジスタへの影響を低減することができる。

**【0056】**

なお、図5では、半導体膜103a、103bの端部に限ってプラズマ処理により酸化または窒化を行った例を示したが、もちろん上記図4で示したようにゲート絶縁膜104にもプラズマ処理を行って酸化または窒化させることも可能である(図7(A))。

**【0057】**

次に、上記とは異なる半導体装置の作製方法に関して図面を参照して説明する。具体的には、テーパー形状を有する半導体膜にプラズマ処理を行う場合に関して示す。

**【0058】**

まず、基板101上に上記と同様に島状の半導体膜103a、103bを形成する(図6(A))。

**【0059】**

次に、プラズマ処理を行い半導体膜103a、103bを酸化または窒化することによって、当該半導体膜103a、103bの表面にそれぞれ酸化膜または窒化膜127a、127b(以下、絶縁膜127a、絶縁膜127bとも記す)を形成する(図6(B))。プラズマ処理は上述した条件下で同様に行うことができる。例えば、半導体膜103a、103bとしてSiを用いた場合、絶縁膜127aおよび絶縁膜127bとして、酸化珪素(SiO<sub>x</sub>)または窒化珪素(SiN<sub>x</sub>)が形成される。また、プラズマ処理により半導体膜103a、103bを酸化させた後に、再度プラズマ処理を行うことによって窒化させてもよい。この場合、半導体膜103a、103bに接して酸化珪素(SiO<sub>x</sub>)が形成され、当該酸化珪素の表面に酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)または窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)が形成される。また、絶縁膜127a、127bは、プラズマ処理に用いた希ガスを含んでいる。なお、プラズマ処理を行うことにより半導体膜103a、103bの端部も同時に酸化または窒化される。

**【0060】**

次に、絶縁膜127a、127bを覆うようにゲート絶縁膜104を形成する(図6(C))。ゲート絶縁膜104は、スパッタ法、LPCVD法、プラズマCVD法等を用いて、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。例えば、半導体膜103a、103bとしてSiを用いてプラズマ処理により酸化させることによって、当該半導体膜103a、103b表面に絶縁膜127a、127bとして酸化珪素を形成した場合、当該絶縁膜127a、127b上にゲート絶縁膜104として酸化珪素(SiO<sub>x</sub>)を形成する。

10

20

30

40

50

## 【0061】

次に、絶縁膜127a、127b上にゲート電極105等を形成することによって、ゲート電極105の下方に位置する半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製することができる(図6(D))。

## 【0062】

半導体膜103a、103bの端部をテーパー形状に設けた場合、半導体膜103a、103bの一部に形成されるチャネル形成領域の端部153a、153bもテーパー形状となるため、半導体素子の特性に影響を及ぼす場合がある。そのため、プラズマ処理により半導体膜を酸化または窒化することによって、結果的にチャネル形成領域の端部も酸化または窒化されるため半導体素子への影響を低減することができる。10

## 【0063】

なお、図6では、半導体膜103a、103bに限ってプラズマ処理により酸化または窒化を行った例を示したが、もちろん上記図4で示したようにゲート絶縁膜104にプラズマ処理を行って酸化または窒化させることも可能である(図7(B))。この場合、一旦酸素を含む雰囲気下でプラズマ処理を行うことによりゲート絶縁膜104を酸化させた後に、再度窒素を含む雰囲気下でプラズマ処理を行うことにより窒化させてもよい。この場合、半導体膜103a、103bに酸化珪素(SiO<sub>x</sub>)または酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)が形成され、ゲート電極105に接して酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)または窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)が形成される。20

## 【0064】

また、上述した構成において、水素と希ガス雰囲気化でプラズマ処理を行うことにより水素を導入することができる。例えば、図2(D)において、ソース領域またはドレイン領域として機能する不純物領域の欠陥を修復するために活性化を行った後に、水素と希ガス雰囲気下でプラズマ処理を行うことにより当該ゲート絶縁膜104に水素を導入する。そして、その後の工程で350～450で熱処理を行いゲート絶縁膜104に含まれる水素を半導体膜103a、103bに移動させることにより、当該半導体膜103a、103bのダングリングボンド等の欠陥を修復する(水素化処理)ことができる。ここでは、ゲート絶縁膜104として、上述したいずれかの材料を用いて、プラズマ処理により水素を導入し、水素化処理を行う。また、また、NH<sub>3</sub>と希ガス雰囲気下でプラズマ処理を行うことによって、ゲート絶縁膜104に水素を導入し、同時に当該ゲート絶縁膜の表面を窒化して表面を改質することができる。また、NH<sub>3</sub>と希ガス雰囲気下でプラズマ処理を行う際に350°～450°の熱処理を行うことによって水素化処理と窒化を同時にを行うことができる。なお、プラズマ処理による水素の導入は、上述した工程と自由に組み合わせて行うことができる。なお、プラズマ処理は上述した条件で行うことができる。30

## 【0065】

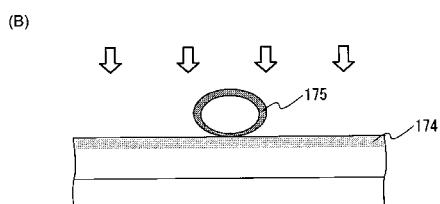

また、上述したようにプラズマ処理を行うことによって、半導体膜や絶縁膜に付着したゴミ等の不純物の除去を容易に行うことができる。一般的に、CVD法やスパッタ法等により形成された膜にはゴミ(パーティクルともいう)が付着していることがある。例えば、図25(A)に示すように、絶縁膜または導電膜または半導体膜等の膜171上にCVD法やスパッタ法等により形成された絶縁膜172上にゴミ173が形成される場合がある。このような場合であっても、プラズマ処理を行い絶縁膜172を酸化または窒化することによって、絶縁膜172の表面に酸化膜または窒化膜174(以下、絶縁膜174ともいう)が形成される。絶縁膜174は、ゴミ173が存在しない部分のみならず、ゴミ173の下側の部分にも回り込むように酸化または窒化されることによって、絶縁膜174の体積が増加する。一方、ゴミ173の表面もプラズマ処理によって酸化または窒化され絶縁膜175が形成され、その結果ゴミ173の体積も増加する(図25(B))。40

## 【0066】

このとき、ゴミ173は、ブラシ洗浄等の簡単な洗浄により、絶縁膜174の表面から容易に除去される状態になる。このように、プラズマ処理を行うことによって、当該絶縁50

膜または半導体膜に付着した微細なゴミであっても当該ゴミの除去が容易になる。なお、これはプラズマ処理を行うことによって得られる効果であり、本実施の形態のみならず、他の実施の形態においても同様のことがいえる。

#### 【0067】

このように、プラズマ処理を行い半導体膜またはゲート絶縁膜を酸化または窒化して表面を改質することにより、緻密で膜質のよい絶縁膜を形成することができる。また、絶縁膜の表面に付着したゴミ等を洗浄によって、容易に除去することが可能となる。その結果、絶縁膜を薄く形成する場合であってもピンホール等の欠陥を防止し、薄膜トランジスタ等の半導体素子の微細化および高性能化を実現することが達成できる。

#### 【0068】

10

##### (実施の形態2)

本実施の形態は、本発明の半導体装置について上記実施の形態とは異なる構造に関して図面を参照して説明する。

#### 【0069】

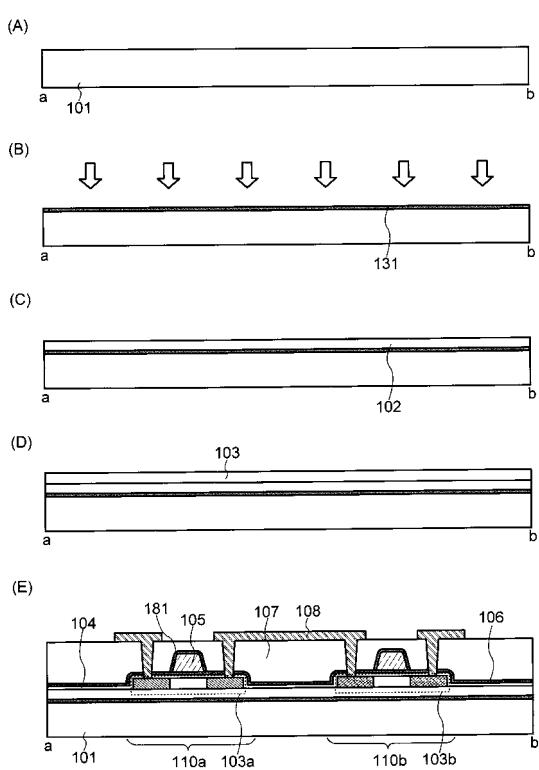

本実施の形態では、上記図1における基板101または絶縁膜102にプラズマ処理を行い、当該基板101または絶縁膜102を酸化または窒化することによって半導体装置を作製する方法について図面を参照して説明する。

#### 【0070】

はじめに、基板上101にプラズマ処理を行うことによって、当該基板101を酸化または窒化させる場合について、図面を参照して説明する。

20

#### 【0071】

まず、基板101を用意し、基板101表面をフッ酸(HF)、アルカリまたは純水を用いて洗浄する(図8(A))。基板101は、バリウムホウケイ酸ガラスや、アルミニウムホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板またはステンレスを含む金属基板等を用いることができる。他にも、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。なお、ここでは基板101としてガラス基板を用いる場合を示す。

#### 【0072】

次に、プラズマ処理を行い基板101を酸化または窒化することによって、当該基板101の表面に酸化膜または窒化膜131(以下、絶縁膜131とも記す)を形成する(図8(B))。一般的に、ガラスやプラスチック等の基板上に薄膜トランジスタ等の半導体素子を設ける場合、ガラスやプラスチック等に含まれるNaなどのアルカリ金属やアルカリ土類金属等の不純物元素が半導体素子に混入して汚染することによって、半導体素子の特性に影響を及ぼす恐れがある。しかし、ガラスやプラスチック等からなる基板の表面を窒化することにより、基板に含まれるNaなどのアルカリ金属やアルカリ土類金属等の不純物元素が半導体素子に混入するのを防止することができる。なお、プラズマ処理は上記実施の形態1と同様の条件下で行うことができる。また、絶縁膜131は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)が含まれている。

30

#### 【0073】

次に、絶縁膜131上に下地膜として機能する絶縁膜102を形成する(図8(C))。絶縁膜102としては、スピッタ法、LPCVD法、プラズマCVD法等を用いて、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。ここでは、基板101の表面をプラズマ処理を行い窒化させ、絶縁膜102として窒化珪素または酸化窒化珪素を形成することが好ましい。絶縁膜102にN原子が多く含まれていると、固定電荷量が増加し当該絶縁膜102上に形成される薄膜トランジスタ等の半導体素子に影響を及ぼすからである。つまり、基板101からの不純物元素が素子へ混入するのを防ぐためにN原子を含む膜が

40

50

必要であるが、N原子を含む膜が多い場合には半導体素子に影響が生じる。そのため、図8では、基板101の表面を窒化し、その窒化した膜上に酸化珪素または酸化窒化珪素を形成する。

#### 【0074】

次に、絶縁膜102上に半導体膜103を形成する(図8(D))。半導体膜103としては、スパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えば $Si_xGe_{1-x}$ 等)等で形成することができる。ここでは、絶縁膜102と半導体膜103をCVD法により連続して形成する。絶縁膜102と半導体膜103を大気に曝さずに連続して形成することによって、半導体膜103への不純物の混入を防止することができる。

10

#### 【0075】

次に、半導体膜103を選択的にエッチングして島状の半導体膜103a、103bを形成し、当該島状の半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製することができる(図8(E))。なお、ここでは、基板101としてガラス基板を用い、窒素を含む雰囲気下でプラズマ処理を行うことにより当該ガラス基板の表面を窒化して窒化膜131を形成し、その上に絶縁膜102として酸化珪素(SiOx)を形成し、当該絶縁膜102上に半導体膜103a、103bを形成する。そして、半導体膜103a、103bを覆うようにゲート絶縁膜104として酸化珪素を形成し、当該ゲート絶縁膜104を窒素を含む雰囲気下でプラズマ処理により窒化する。その後、ゲート電極105としてスパッタ法等の公知の方法を用いてMo、W、Cr、Ta、Ni等で形成し、窒素を含む雰囲気下プラズマ処理を行うことによりゲート電極105の表面を窒化する。例えば、ゲート電極105として、Moを用いた場合にはMoの表面にMoの窒化膜181が形成されている。なお、ゲート電極105として、Moを用いた場合、通常Moは酸化されやすいが窒素を含む雰囲気下でプラズマ処理を行うことにより当該Moの表面を窒化することによって、Moの酸化を防止することができる。

20

#### 【0076】

このように、プラズマ処理により基板101表面を酸化または窒化することによって、基板に含まれるNaなどのアルカリ金属やアルカリ土類金属等の不純物元素が半導体素子に混入して汚染することを防止することができる。

30

#### 【0077】

次に、プラズマ処理を用いた基板101上に形成する絶縁膜102の作製方法について、図面を参照して説明する。なお、ここでは、絶縁膜102の作製方法として2通りの方法についてそれぞれ図9、図10に示す。

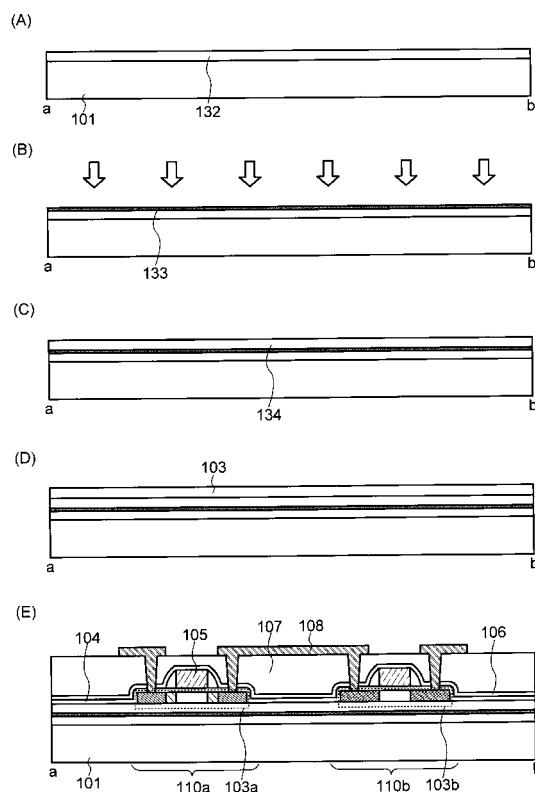

#### 【0078】

まず、基板101上に、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いて絶縁膜132を形成する(図9(A))。絶縁膜132としては、酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x>y)を用いる。

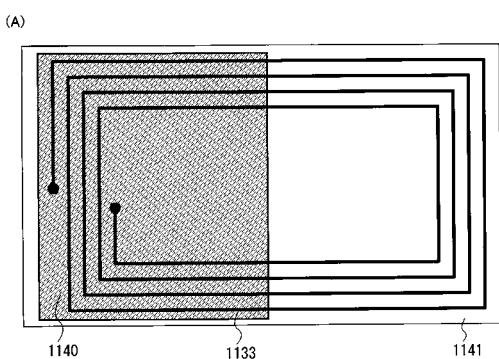

#### 【0079】

次に、プラズマ処理を行い絶縁膜132に酸化処理または窒化処理を行うことによって、当該絶縁膜132の表面に酸化膜または窒化膜133(以下、絶縁膜133とも記す)を形成する(図9(B))。ここでは、窒素を含む雰囲気下(例えば、窒素(N<sub>2</sub>)と希ガス雰囲気下またはNH<sub>3</sub>と希ガス雰囲気下)でプラズマ処理を行い、絶縁膜132表面を窒化する。そのため、絶縁膜132の表面には絶縁膜133として、窒化酸化珪素(SiNxOy)(x>y)が形成される。また、絶縁膜133には、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)が含まれており、例えばArを用いた場合には絶縁膜133中にArが含まれている。なお、プラズマ処理は上述した条件下で同様に行うことができる。

40

#### 【0080】

次に、絶縁膜133上にスパッタ法、LPCVD法、プラズマCVD法等を用いて絶縁

50

膜134を形成する(図9(C))。絶縁膜134としては、酸化珪素(SiO<sub>x</sub>)または酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)を用いる。

#### 【0081】

次に、絶縁膜134上に半導体膜103を形成する(図9(D))。半導体膜103としては、スパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>1-x</sub>等)等で形成することができる。ここでは、絶縁膜134と半導体膜103をCVD法により連続して形成する。絶縁膜134と半導体膜103を大気に曝さずに連続して形成することによって、半導体膜103への不純物の混入を防止することができる。

#### 【0082】

次に、半導体膜103を選択的にエッチングして島状の半導体膜103a、103bを形成し、当該島状の半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製する(図9(E))。

#### 【0083】

このように、プラズマ処理により下地膜として機能する絶縁膜を酸化または窒化して表面を改質することによって、CVD法やスパッタ法で絶縁膜と比較して緻密でピンホール等の欠陥の少ない良質な絶縁膜を形成することができる。また、基板101に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜103a、103b中に拡散し汚染するのを抑制し、薄膜トランジスタ等の半導体素子の特性を向上させることができる。

#### 【0084】

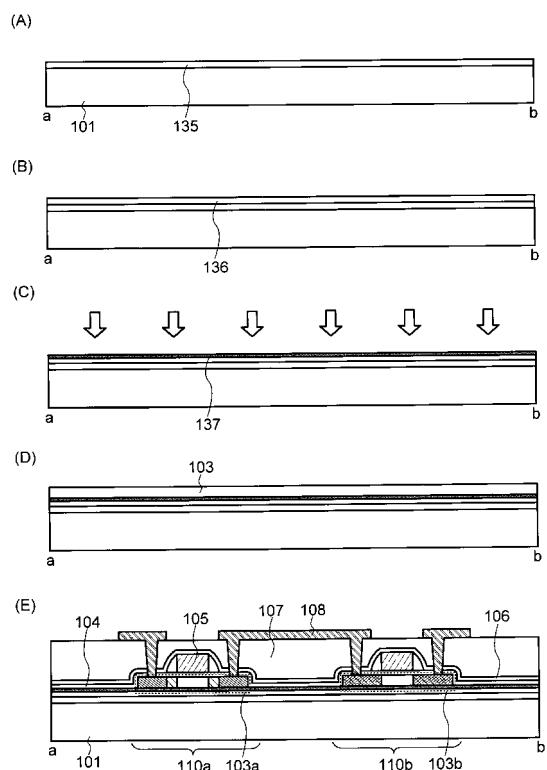

次に、上記図9とは異なる絶縁膜102の作製方法に関して説明する。

#### 【0085】

まず、基板101上にスパッタ法、LPCVD法、プラズマCVD法等を用いて絶縁膜135を形成する(図10(A))。絶縁膜135としては、窒化珪素(SiNx)、窒化酸化珪素(SiNxOy)(x>y)を用いる。

#### 【0086】

次に、絶縁膜135上にスパッタ法、LPCVD法、プラズマCVD法等を用いて絶縁膜136を形成する(図10(B))。絶縁膜136としては、酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x>y)を用いる。

#### 【0087】

次に、プラズマ処理を行い絶縁膜136を酸化または窒化することによって、当該絶縁膜136の表面に酸化膜または窒化膜137(以下、絶縁膜137とも記す)を形成する(図10(C))。ここでは、絶縁膜136をプラズマ処理により酸化することにより絶縁膜136表面に酸化膜を形成する。絶縁膜136の表面を酸化することによって、当該絶縁膜136の表面を改質しピンホール等の欠陥の少ない緻密な膜を得ることができる。また、絶縁膜136の表面を酸化することによって、N原子の含有率が低い絶縁膜137を形成することができるため、当該絶縁膜137上に半導体膜を設けた場合に絶縁膜137と半導体膜界面特性が向上する。また、絶縁膜137は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる。なお、プラズマ処理は上述した条件下で同様に行うことができる。

#### 【0088】

次に、絶縁膜137上に半導体膜103を形成する(図10(D))。半導体膜103としては、スパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>1-x</sub>等)等で形成することができる。

#### 【0089】

次に、半導体膜103を選択的にエッチングして島状の半導体膜103a、103bを形成し、当該島状の半導体膜103a、103bをチャネル形成領域として用いたn型の薄膜トランジスタ110a、p型の薄膜トランジスタ110bを有する半導体装置を作製する(図10(E))。

10

20

30

40

50

## 【0090】

このように、プラズマ処理により下地膜として機能する絶縁膜を酸化または窒化して表面を改質することによって、CVD法やスパッタ法で絶縁膜と比較して緻密でピンホール等の欠陥の少ない良質な膜を形成することができるため、薄膜トランジスタ等の半導体素子の特性を向上させることができる。

## 【0091】

なお、本実施の形態は上記実施の形態と自由に組み合わせて行うことができる。つまり、本実施の形態2に示した構成と上記実施の形態1に示した構成を自由に組み合わせたものの全てが本発明に含まれる。

## 【0092】

10

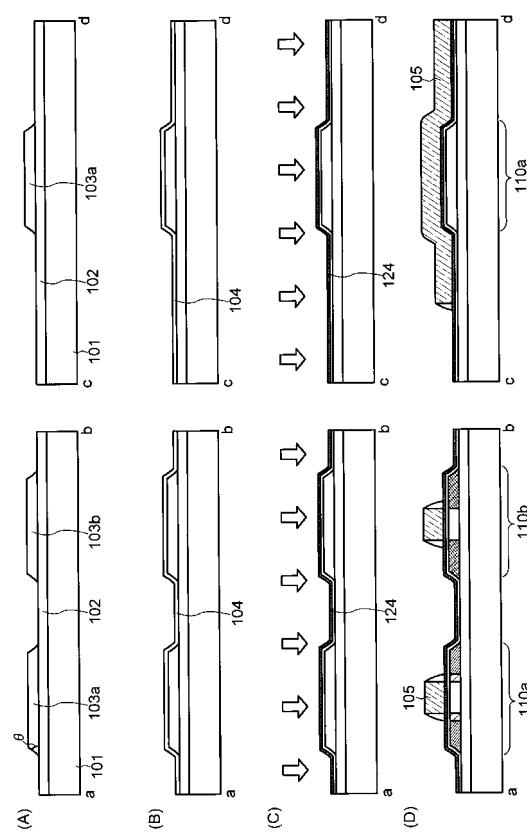

## (実施の形態3)

本実施の形態は、本発明の半導体装置について上記実施の形態とは異なる構造に関して図面を参照して説明する。

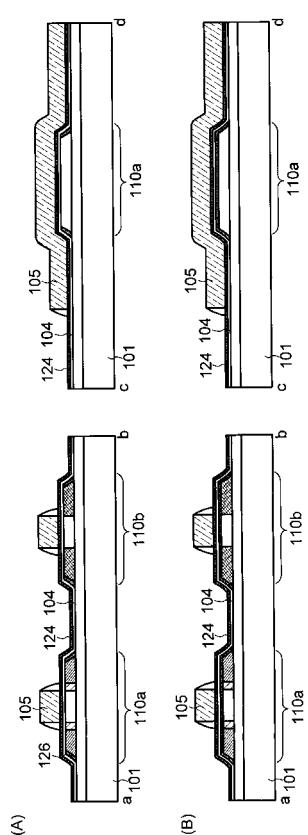

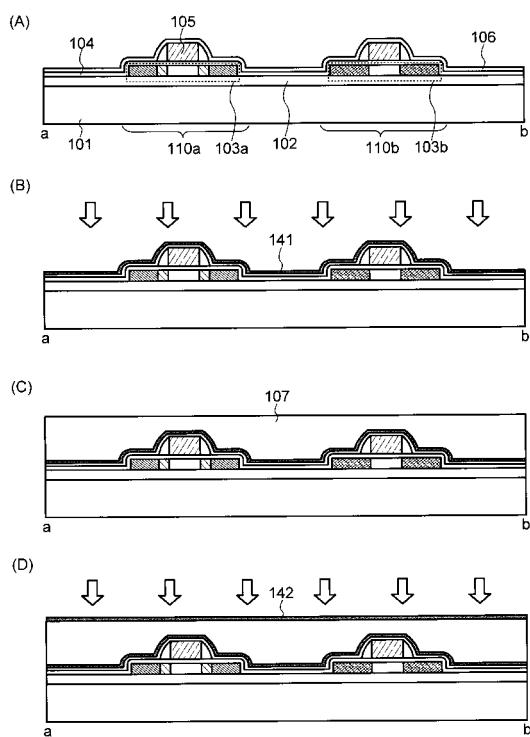

## 【0093】

本実施の形態では、上記図1における絶縁膜106または絶縁膜107にプラズマ処理を行うことによって、当該絶縁膜106または絶縁膜107を酸化または窒化させる場合について、図面を参照して説明する。

## 【0094】

まず、基板101上に絶縁膜102を介して島状の半導体膜103a、103bを設け、当該半導体膜103a、103b上にゲート絶縁膜104を介してゲート電極105を形成し、当該ゲート電極105を覆うようにスパッタ法、LPCVD法、プラズマCVD法等を用いて絶縁膜106を形成する(図11(A))。

20

## 【0095】

次に、プラズマ処理を行い絶縁膜106を酸化または窒化することによって、当該絶縁膜106の表面にそれぞれ酸化膜または窒化膜141(以下、絶縁膜141とも記す)を形成する(図11(B))。絶縁膜106は、スパッタ法やプラズマCVD法等により、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜の単層構造、またはこれらの積層構造で設けることができる。つまり、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜にプラズマ処理を行うことによって、当該膜の表面を酸化または窒化する。そのため、絶縁膜141には、プラズマ処理に用いた希ガス(H<sub>e</sub>、Ne、Ar、Kr、Xeの少なくとも一つを含む)が含まれており、例えばArを用いた場合には絶縁膜141中にArが含まれている。

30

## 【0096】

また、上記構成に限られず、絶縁膜106にプラズマ処理によって水素を導入することも可能である。この場合、図11(A)に示すように、ゲート電極を覆って絶縁膜106をもうけた後に、プラズマ処理を行い当該絶縁膜106に水素を導入してもよい。プラズマ処理は、水素と希ガス雰囲気下で上述した条件で行う。また、NH<sub>3</sub>と希ガス雰囲気下で絶縁膜106にプラズマ処理を行うことによって、当該絶縁膜106に水素を導入し、さらに絶縁膜106の表面を窒化することができる。また、水素と希ガス雰囲気下でプラズマ処理を行い絶縁膜106に水素を導入した後に、窒素を含む雰囲気下でプラズマ処理を行い当該絶縁膜の表面を窒化させてもよい。その後の工程で350°～450°で熱処理を行い水素化処理することによって、半導体膜103a、103bのダングリングボンド等の欠陥を修復することができる。また、NH<sub>3</sub>と希ガス雰囲気下でプラズマ処理を行う際に350°～450°で熱処理をすることによって、水素化と窒化を同時に進行することができる。ここでは、絶縁膜106として、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)

40

50

)等を用いて、プラズマ処理により水素を導入し、水素化処理を行う。また、希ガスとしてはArを用いることができる。

#### 【0097】

次に、絶縁膜141を覆うようにスパッタ法、LPCVD法、プラズマCVD法等を用いて絶縁膜107を形成する(図11(C))。

#### 【0098】

次に、プラズマ処理を行い絶縁膜107を酸化または窒化することによって、当該絶縁膜107の表面にそれぞれ酸化膜または窒化膜142(以下、絶縁膜142とも記す)を形成する(図11(D))。絶縁膜107は、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜はもちろん、その他にもエポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料やシロキサン樹脂からなる単層または積層構造で設けることができる。なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、絶縁膜142には、プラズマ処理に用いた希ガス(H<sub>e</sub>、Ne、Ar、Kr、Xeの少なくとも一つを含む)が含まれており、例えばArを用いた場合には絶縁膜142中にArが含まれている。

10

#### 【0099】

絶縁膜107としてポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料やシロキサン樹脂等を用いた場合、絶縁膜107の表面をプラズマ処理により酸化または窒化することにより、当該絶縁膜の表面を改質することができる。表面を改質することによって、絶縁膜107の強度が向上し開口部形成時等におけるクラックの発生やエッティング時の膜減り等の物理的ダメージを低減することが可能となる。また、絶縁膜107の表面が改質されることによって、当該絶縁膜107上に導電膜を形成する場合に導電膜との密着性が向上する。例えば、絶縁膜107としてシロキサン樹脂を用いてプラズマ処理を用いて窒化を行った場合、シロキサン樹脂の表面が窒化されることにより窒素または希ガスを含む絶縁膜142が形成され、物理的強度が向上する。

20

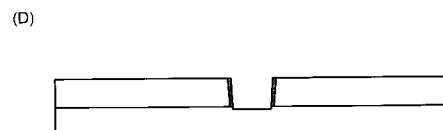

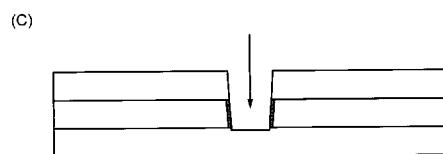

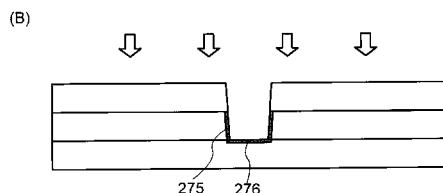

#### 【0100】

また、絶縁膜に開口部を形成した際に、プラズマ処理を行い当該絶縁膜の開口部の側壁の酸化または窒化を行うことも可能である。この場合について図面を参照して以下に説明する。

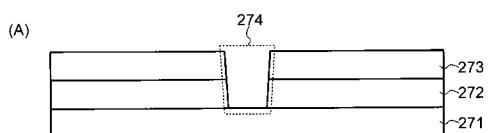

#### 【0101】

まず、膜271上に設けられた絶縁膜272にレジスト273をマスクとして開口部274を形成する(図27(A))。なお、膜271としては、当該膜271上に形成される絶縁膜272に開口部が設けられる構造であればどのようなものでも適用することができ、例えば、Si等の半導体膜、銅(Cu)、アルミニウム(Al)、チタン(Ti)等の導電膜またはNi、Co、W等のシリサイド等を適用することができる。また、絶縁膜272としては、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜はもちろん、その他にもエポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料やシロキサン樹脂からなる単層または積層構造で設けることができる。なお、開口部274を設ける前に酸素を含む雰囲気または窒素を含む雰囲気下で絶縁膜272にプラズマ処理を行い当該絶縁膜272表面を酸化または窒化させてもよい。

30

#### 【0102】

次に、酸素を含む雰囲気下または窒素を含む雰囲気下でプラズマ処理を行い、開口部2

40

50

74における絶縁膜272の側壁を酸化または窒化することにより、酸化膜または窒化膜275（以下、絶縁膜275とも記す）を形成する。また、この際、プラズマ処理によって膜271の表面も酸化または窒化されるため、酸化膜または窒化膜276（以下、絶縁膜276とも記す）が形成される。ここでは、窒素を含む雰囲気下でプラズマ処理を行い絶縁膜272の側壁を窒化する（図27（B））。

#### 【0103】

次に、異方性エッティングを行うことにより、膜271に形成された酸化膜または窒化膜からなる絶縁膜276を選択的に除去する（図27（C））。

#### 【0104】

次に、レジスト273を除去することにより、開口部274における絶縁膜272の側面に窒化された絶縁膜275を形成することができる（図27（D））。

10

#### 【0105】

以上のように、プラズマ処理により開口部における絶縁膜の側面を酸化または窒化することによって、当該絶縁膜の側面に酸化膜または窒化膜を形成して表面を改質することによって、強度を向上させクラック等の発生を防止することができる。また、開口部における絶縁膜の表面が改質されることによって、当該開口部に導電膜を形成する場合に絶縁膜と導電膜との密着性が向上する。

#### 【0106】

なお、本実施の形態は上記実施の形態と自由に組み合わせて行うことができる。つまり、本実施の形態3に示した構成と上記実施の形態1または実施の形態2に示した構成を自由に組み合わせたもの全てが本発明に含まれる。

20

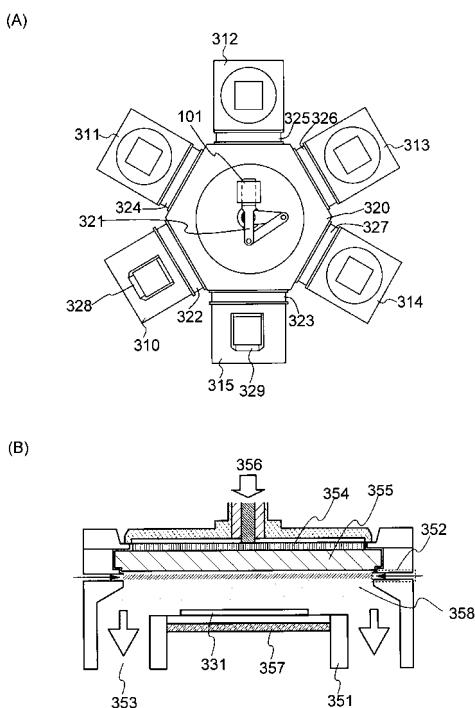

#### 【0107】

##### （実施の形態4）

本実施の形態では、絶縁膜、導電膜または半導体膜の成膜およびプラズマ処理を連続して行う半導体装置の作製方法に関して図面を用いて説明する。

#### 【0108】

絶縁膜、導電膜または半導体膜の成膜およびプラズマ処理を連続して行う場合には、複数のチャンバーを備えた装置を用いることができる。複数のチャンバーを備えた装置の一例を図12（A）に示す。なお、図12（A）は、本実施の形態で示す装置（連続成膜システム）の一構成例を上面からみた図である。

30

#### 【0109】

図12（A）に示す装置は、第1のチャンバー311、第2のチャンバー312、第3のチャンバー313、第4のチャンバー314、ロードロック室310、315、共通室320を有しており、それぞれのチャンバーは気密性を有している。各チャンバーには、真空排気ポンプ、不活性ガスの導入系が備えられている。

#### 【0110】

ロードロック室310、315は、試料（処理基板）をシステムに搬入するための部屋である。また、第1～第4のチャンバーは、基板101に導電膜、絶縁膜または半導体膜の成膜や、エッティングやプラズマ処理等を行うための部屋である。共通室320は、それぞれのロードロック室310、315および第1～第4のチャンバーに対して共通に配置されている。また、共通室320とロードロック室310、315、第1～第4のチャンバー311～314との間にはゲート弁322～327が設けられている。なお、共通室320には、ロボットアーム321が設けてあり、ロボットアーム321によって、基板101が各部屋へ運ばれる。

40

#### 【0111】

以下に、具体例として、基板101に対して、第1のチャンバー311において絶縁膜102を成膜し、第2のチャンバー312においてプラズマ処理を行い、第3のチャンバー313において半導体膜103を成膜する例を示す。

#### 【0112】

まず、基板101は多数枚が収納されたカセット328ごとロードロック室310に搬

50

入される。カセット328の搬入後、ロードロック室310の搬入扉を閉鎖する。この状態において、ゲート弁322を開けてカセット328から処理基板を1枚取り出し、ロボットアーム321によって共通室320に配置させる。この際、共通室320において基板101の位置合わせが行われる。

#### 【0113】

次に、ゲート弁322を閉鎖し、ついでゲート弁324を開ける。そして、第1のチャンバー311へ基板101を移送する。第1のチャンバー311内で、150～300の温度で成膜処理を行い、絶縁膜102を形成する。絶縁膜102としては、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)( $x > y$ )、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)( $x > y$ )等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。ここでは、第1のチャンバー311において、プラズマCVD法により、1層目の絶縁膜として窒化酸化珪素膜を形成し、2層目の絶縁膜として酸化窒化珪素膜を形成する。なお、プラズマCVD法に限らず、ターゲットを用いたスパッタ法により形成してもよい。10

#### 【0114】

次に、絶縁膜102を成膜した後、基板101はロボットアーム321によって共通室320に引き出され、第2のチャンバー312に移送される。第2のチャンバー312内では、絶縁膜102に対してプラズマ処理を行うことによって、絶縁膜102を酸化または窒化させる。ここでは、第2のチャンバー312において、酸素を含む雰囲気下(例えば、酸素と希ガス雰囲気下、酸素と水素と希ガス雰囲気下、一酸化二窒素と希ガス雰囲気下または一酸化二窒素と水素と希ガス雰囲気下)でプラズマ処理を行うことによって、絶縁膜102の表面を酸化させる。20

#### 【0115】

次に、絶縁膜102を成膜した後、基板101はロボットアーム321によって共通室320に引き出され、第3のチャンバー313に移送される。第3のチャンバー313内では、150～300の温度で成膜処理を行い、プラズマCVD法により半導体膜103を形成する。なお、半導体膜103としては、微結晶半導体膜、非晶質ゲルマニウム膜、非晶質シリコンゲルマニウム膜またはこれらの積層膜等を使用することができる。また、半導体膜の形成温度を350～500として水素濃度を低減するための熱処理を省略してもよい。なお、ここではプラズマCVD法を用いて形成する例を示したが、ターゲットを用いたスパッタ法を用いて形成してもよい。30

#### 【0116】

以上のように、半導体膜を成膜した後、基板101はロボットアーム321によってロードロック室315に移送され、カセット329に収納される。

#### 【0117】

なお、図12(A)に示したのはあくまで一例であり、例えば、半導体膜を形成した後に続けて第4のチャンバー314を用いて導電膜や絶縁膜を形成してもよいし、さらにチャンバーの数を増やすことも可能である。また、上記実施の形態2に示したように、絶縁膜102を形成する前に基板101にプラズマ処理をして、当該基板101の表面を酸化または窒化することもできる。つまり、上記実施の形態で示した工程や材料を用いて自由に図12(A)に示した装置と組み合わせて半導体装置を作製することができる。また、図12(A)において第1～第4のチャンバー311～314はシングル型のチャンバーを用いた例を示したが、バッチ型のチャンバーを用いて多数枚を一度に処理する構成としてもよい。40

#### 【0118】

このように、本実施の形態で示した装置を用いることによって、大気に一度も曝されることなく導電膜、絶縁膜または半導体膜の成膜やプラズマ処理を連続して行うことができる。そのため、汚染物の混入の防止や生産効率の向上を実現することができる。

#### 【0119】

次に、本発明において、プラズマ処理を行う場合の装置の一例について図12(B)を50

参照して説明する。

**【0120】**

図12(B)に示す装置は、プラズマ処理を行う被処理物331を配置するための支持台351と、ガスを導入するためのガス供給部352と、排気口353と、アンテナ354と、誘電板355と、プラズマ発生用の高周波を供給する高周波供給部356とを有している。また、支持台351に温度制御部357を設けることによって、被処理物331の温度を制御することも可能である。以下に、プラズマ処理の一例に関して説明する。なお、被処理物としては、上記実施の形態においてプラズマ処理を行うものであれば用いることができる。

**【0121】**

まず、処理室内を真空にし、ガス供給部352から酸素または窒素を含むガスを導入する。例えば、酸素を含むガスとしては、酸素( $O_2$ )と希ガスまたは酸素と水素と希ガスの混合ガスを導入することができる。また窒素を含むガスとしては、窒素と希ガスまたは $NH_3$ と希ガスの混合ガスを導入することができる。次に、被処理物331を温度制御部357を有する支持台351に配置させ、被処理物331を100～550に加熱する。なお、被処理物331と誘電板355との間隔は、20～80mm(好ましくは20～60mm)の範囲内とする。

**【0122】**

次に、高周波供給部356からアンテナ354にマイクロ波を供給する。ここでは、周波数2.45GHzのマイクロ波を供給する。そして、マイクロ波をアンテナ354から誘電板355を通して処理室内に導入することによって、プラズマ励起により活性化された高密度プラズマ358が生成される。例えば、 $NH_3$ ガスとArガス雰囲気中でプラズマ処理を行った場合、マイクロ波により $NH_3$ ガスとArガスとが混合された高密度励起プラズマが生成される。 $NH_3$ ガスとArガスとが混合された高密度励起プラズマ中では、導入されたマイクロ波によりArガスが励起されてラジカル(Ar·)が生成され、当該Arラジカルと $NH_3$ 分子とが衝突することによりラジカル(NH·)が生成される。このNH·と被処理物331とが反応して、当該被処理物331の窒化を行うことができる。その後、 $NH_3$ ガスとArガスとが、排気口353から処理室外へ排気される。

**【0123】**

このように、図12(B)に示した装置を用いてプラズマ処理を行うことによって、低電子温度(1.5eV以下)で且つ高電子密度( $1 \times 10^{11} cm^{-3}$ 以上)であるので、プラズマダメージが非常に少ない被処理物を形成することができる。

**【0124】**

なお、本実施の形態は上記実施の形態と自由に組み合わせて行うことができる。つまり、本実施の形態4に示した構成と上記実施の形態1～実施の形態3に示した構成を自由に組み合わせたもの全てが本発明に含まれる。

**【0125】**

(実施の形態5)

本実施の形態は、本発明の半導体装置について上記実施の形態とは異なる構造に関して図面を参照して説明する。具体的には、記憶素子を有し、非接触でデータの送受信ができる半導体装置の一例に関して説明する。

**【0126】**

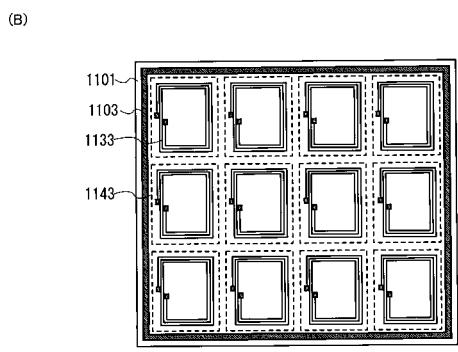

本実施の形態で示す半導体装置は、図19(A)に示すように、基板1141上に複数の薄膜トランジスタを含む素子群1140とアンテナとして機能する導電膜1133が設けられている。なお、アンテナとして機能する導電膜1133は、素子群1140に含まれる薄膜トランジスタと電気的に接続している。また、当該半導体装置は、アンテナとして機能する導電膜1133を介して、非接触で外部の機器(リーダ/ライタ)とデータのやりとりを行うことができる。

**【0127】**

以下に、上記半導体装置の作製方法の一例に関して図面を参照して説明する。ここでは

10

20

30

40

50

、図19(B)に示すように、1枚の基板1101から半導体装置1145を複数(ここでは縦4個、横3個からなる12個)作製する場合に関して説明する。また、ここでは、可撓性を有する半導体装置を形成するために、薄膜トランジスタ等の半導体素子やアンテナを剥離層1103を介してガラス等の剛性を有する基板1101上に一旦設けた後に、当該基板1101から半導体素子とアンテナ等を剥離して、可撓性を有する基板上に半導体素子とアンテナ等を設ける例を示す。

#### 【0128】

まず、基板1101上に絶縁膜1102、剥離層1103を形成する(図13(A))。

#### 【0129】

基板1101としては、上述した基板101と同様の材料を用いて設けることができる。ここでは、基板1101としてガラス基板を用いる。また、上記実施の形態2で示したように、基板1101にプラズマ処理を行い当該基板1101の表面を酸化または窒化させてもよい。

10

#### 【0130】

絶縁膜1102としては、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiNx)、酸化窒化珪素(SiO<sub>x</sub>Ny)(x>y)、窒化酸化珪素(SiNxOy)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。ここでは、基板1101としてガラス基板を用い、絶縁膜1102として酸化窒化珪素を50~150nmの厚さに形成する。また、絶縁膜1102に上記実施の形態で示したように20

プラズマ処理を行い当該絶縁膜1102を酸化または窒化させてもよい。

#### 【0131】

剥離層1103としては、金属膜や金属膜と金属酸化膜の積層構造等を用いることができる。金属膜としては、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タントル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、鉛(Pd)、オスミウム(Os)、イリジウム(Ir)から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる膜を単層又は積層して形成する。また、これらの材料は、公知の手段(スパッタ法やプラズマCVD法等の各種CVD法)を用いて形成することができる。金属膜と金属酸化膜の積層構造としては、上述した金属膜を形成した後に、酸素を含む雰囲気化におけるプラズマ処理、酸素を含む雰囲気下における加熱処理を行うことによって、金属膜表面に当該金属膜の酸化物を設けることができる。例えば、金属膜としてスパッタ法により形成したタンゲステン膜を設けた場合、タンゲステン膜にプラズマ処理を行うことによって、タンゲステン膜表面にタンゲステン酸化物からなる金属酸化膜を形成することができる。また、この場合、タンゲステンの酸化物は、WO<sub>x</sub>で表され、Xは2~3であり、Xが2の場合(WO<sub>2</sub>)、Xが2.5の場合(W<sub>2</sub>O<sub>5</sub>)、Xが2.75の場合(W<sub>4</sub>O<sub>11</sub>)、Xが3の場合(WO<sub>3</sub>)などがある。タンゲステンの酸化物を形成するにあたり、上記に挙げたXの値に特に制約はなく、エッティングレート等を基に、どの酸化物を形成するかを決めるといい。また、金属酸化膜の他にも、金属窒化物や金属酸化窒化物を用いてもよい。この場合、上記金属膜に窒素を含む雰囲気下または窒素と酸素を含む雰囲気下でプラズマ処理や加熱処理を行えばよい。また、他の方法として金属膜を形成した後に、当該金属膜上に絶縁膜を酸素を含む雰囲気下でスパッタ法を用いて形成することによって金属膜表面に金属酸化膜と絶縁膜との積層構造を設けることができる。また、金属膜を形成した後に、金属をターゲットとして酸素を含む雰囲気下でスパッタを行うことにより金属膜表面に金属酸化膜を設けることも可能である。この場合、金属膜と金属酸化膜はことなる金属元素で設けることが可能となる。なお、これらの方法も窒素を含む雰囲気下または窒素と酸素を含む雰囲気下でスパッタを行うことにより金属膜上に金属窒化物や金属酸化窒化物を形成することができる。

20

#### 【0132】

次に、剥離層1103上に下地膜として機能する絶縁膜1104を形成し、当該絶縁膜

30

40

50

1104 上に非晶質半導体膜を形成し、その後非晶質半導体膜をレーザ結晶化法、R T A 又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれらを組み合わせた方法等を用いて結晶化させ、結晶性半導体膜 1105 を形成する(図 13 (B))。

#### 【0133】

絶縁膜 1104 は、上記実施の形態 2 で示した絶縁膜 102 のいずれかの構造を用いて形成することができる。ここでは、下地膜 1104 として窒化酸化珪素(SiNxOy)(x > y)を形成した後、当該窒化酸化珪素膜に窒素を含む雰囲気中でプラズマ処理を行うことにより、当該窒化酸化珪素膜の表面を窒化し、その後当該窒化酸化珪素膜上に酸化窒化珪素(SiOxNy)(x > y)を形成して積層する構造とする。一般的に、CVD 法やスパッタ法により形成した窒化酸化珪素膜は、膜の内部に欠陥を有し膜質が十分でないため、窒素を含む雰囲気中でプラズマ処理を行い窒化することによって、当該窒化酸化珪素膜の表面を改質しより緻密な膜を形成することができる。その結果、絶縁膜 1104 上に半導体素子を設ける場合に、基板 1101 や剥離層 1103 からの不純物元素の混入を防止することができる。10

#### 【0134】

次に、結晶性半導体膜 1105 に対して p 型の導電型を付与する不純物元素をドーピングする。ここでは、不純物元素としてボロン(B)をドーピングする(図 13 (C))。

#### 【0135】

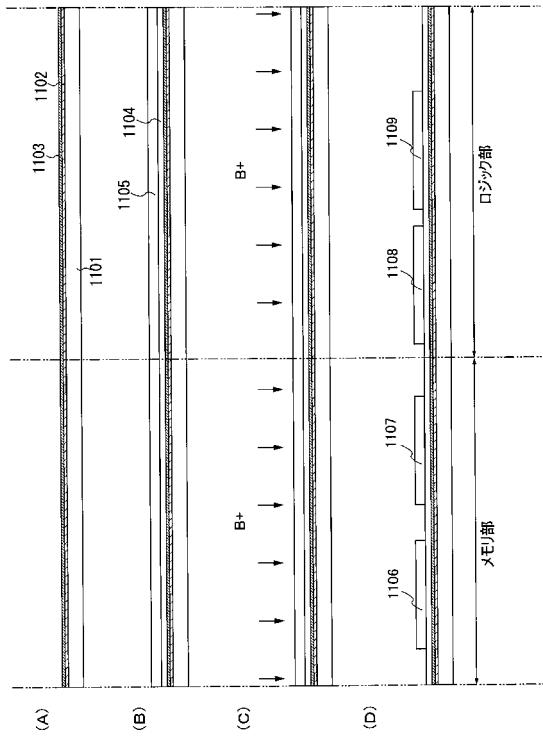

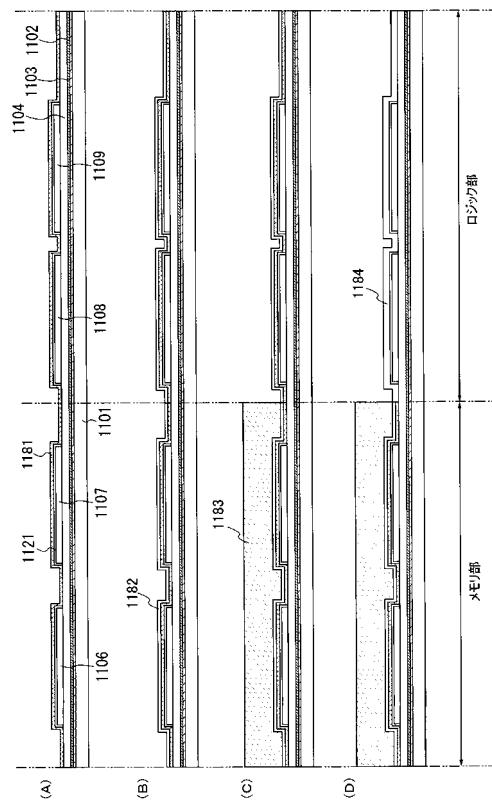

次に、結晶性半導体膜 1105 を選択的にエッチングして、第 1 の半導体膜 1106 ~ 第 4 の半導体膜 1109 を形成する(図 13 (D))。ここでは、第 1 の半導体膜 1106 および第 2 の半導体膜 1107 はメモリ部に用いるものであり、第 3 の半導体膜 1108 および第 4 の半導体膜 1109 はロジック回路に用いるものとする。20

#### 【0136】

次に、第 4 の半導体膜 1109 を覆うようにレジストマスク 1110 を形成した後、第 1 の半導体膜 1106 ~ 第 3 の半導体膜 1108 に対して p 型の導電型を付与する不純物元素をドーピングする(図 14 (A))。本実施の形態では、不純物元素としてボロン(B)をドーピングする。

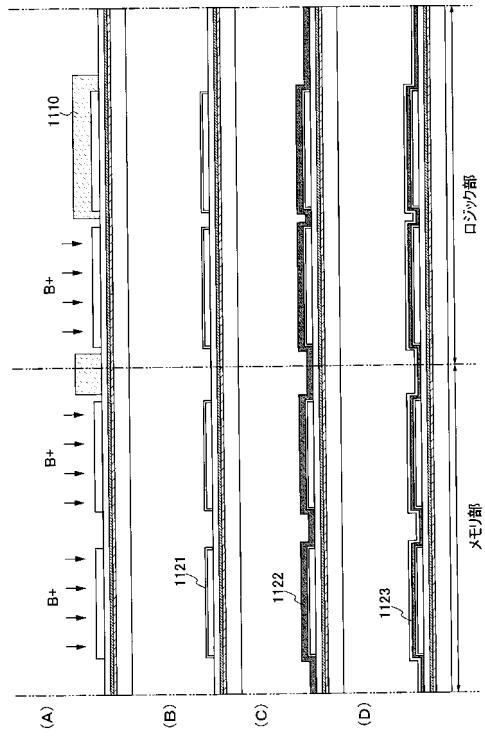

#### 【0137】

次に、レジストマスク 1110 を除去し、第 1 の半導体膜 1106 ~ 第 4 の半導体膜 1109 に対してプラズマ処理を行い酸化または窒化させることによって、当該半導体膜の表面に酸化膜または窒化膜 1121(以下、絶縁膜 1121 とも記す)を形成する(図 14 (B))。ここでは、酸素を含む雰囲気中でプラズマ処理を行い、第 1 の半導体膜 1106 ~ 第 4 の半導体膜 1109 を酸化することによって絶縁膜 1121 として酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x > y)を形成する。一般的に、CVD 法やスパッタ法により形成した酸化珪素膜または酸化窒化珪素膜は、膜の内部に欠陥を含んでいるため膜質が十分でない。そのため、酸素を含む雰囲気下で半導体膜にプラズマ処理を行い酸化することによって、当該半導体膜上に、CVD 法やスパッタ法等により形成した絶縁膜より緻密な絶縁膜を形成することができる。また、半導体膜の上方に CVD 法やスパッタ法等を用いて設けられた絶縁膜を介して導電膜を設ける場合、半導体膜の端部において絶縁膜の段切れ等による被覆不良が生じ半導体膜と導電膜間でショート等が発生する恐れがあるが、あらかじめ半導体膜の表面にプラズマ処理を用いて酸化または窒化することによって、半導体膜の端部における絶縁膜の被覆不良を防止することができる。なお、絶縁膜 1121 は、メモリ部の記憶素子においてトンネル絶縁膜として機能する。3040

#### 【0138】

次に、絶縁膜 1121 及び絶縁膜 1104 を覆うように窒化珪素(SiNx)または窒化酸化珪素(SiNxOy)(x > y) 1122(以下、絶縁膜 1122 とも記す)を形成する。ここでは、絶縁膜 1122 としてプラズマ CVD 法を用いて窒化珪素膜を 4 ~ 20 nm の厚さで形成する(図 14 (C))。なお、絶縁膜 1122 は、メモリ部の記憶素子において電荷をトラップする膜として機能する。50

## 【0139】

次に、絶縁膜1122に対して酸素を含む雰囲気中でプラズマ処理を行い、当該絶縁膜1122の表面を酸化させ絶縁膜1123を形成する(図14(D))。なお、プラズマ処理は上述した条件下で行うことができる。ここではプラズマ処理により、絶縁膜1122の表面に絶縁膜1123として酸化珪素膜または酸化窒化珪素膜2~10nmで形成される。

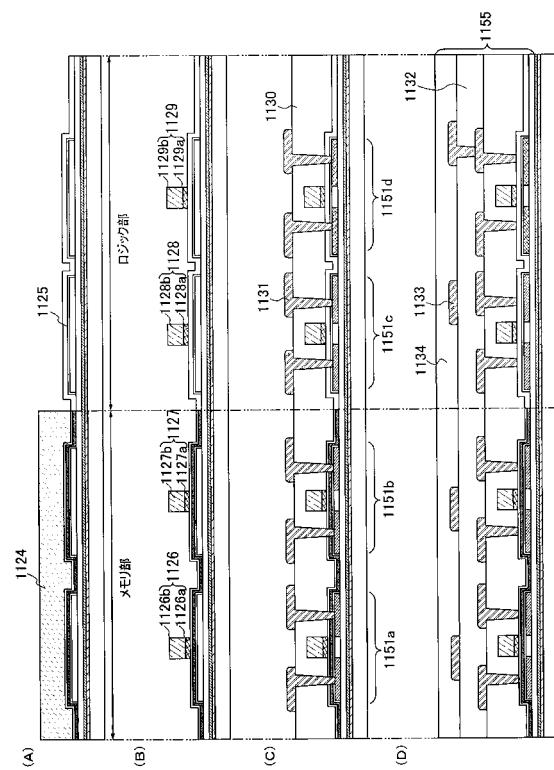

## 【0140】

次に、メモリ部のみに選択的にレジストマスク1124を形成した後、ロジック部を選択的に酸化する(図15(A))。具体的には、ロジック部の窒化珪素膜1122及び酸素を含む窒化珪素膜1123に対して酸素を含む雰囲気中でプラズマ処理を行い酸化する。ここでは、このプラズマ処理により、ロジック部の窒化酸化珪素からなる絶縁膜1122および酸化窒化珪素膜または窒化酸化珪素膜からなる絶縁膜1123が酸化され、酸化膜1125が形成される。

10

## 【0141】

次に、レジストマスク1124を除去し、第1の半導体膜1106~第4の半導体膜1109の上方にゲート電極として機能する導電膜1126~1129を形成する(図15(B))。なお、ここでは導電膜1126~1129は、第1の導電膜1126a~1129aと第2の導電膜1126b~1129bとの積層構造で設けられている。ここでは、第1の導電膜1126a~1129aとして窒化タンタルを用い、第2の導電膜1126b~1129bとしてタングステン用いて積層構造で設ける。なお、この構成に限定されず、単層構造としてもよい。また、材料もこれに限定されるものではなく、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金材料若しくは化合物材料で形成することができる。また、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。

20

## 【0142】

次に、導電膜1126~1128をマスクとして第1の半導体膜1106~第3の半導体膜1108にそれぞれn型を付与する不純物元素を導入し、導電膜1129をマスクとして第4の半導体膜1109にp型を付与する不純物元素を導入してソースまたはドレイン領域を形成する。その後導電膜1126~1129を覆って絶縁膜1130を形成し、当該第1の半導体膜1106~1109のソースまたはドレイン領域と電気的に接続するように絶縁膜1130上に導電膜1131を形成することによって、第1の半導体膜1106、第2の半導体膜1107をチャネル形成領域として利用する記憶素子1151a、1151bと、第3の半導体膜1108をチャネル形成領域として利用するn型の薄膜トランジスタ1151cと、第4の半導体膜1109をチャネル形成領域として利用するp型の薄膜トランジスタ1151dを設ける(図15(C))。

30

## 【0143】

次に、導電膜1131を覆うように絶縁膜1132を形成し、当該絶縁膜1132上にアンテナとして機能する導電膜1133を形成し、さらに導電膜1133を覆うように絶縁膜1134を形成する(図15(D))。なお、ここで記憶素子1151a、1151b、薄膜トランジスタ1151c、1151dおよび導電膜1133等を含む層を便宜上素子群1155と記す。

40

## 【0144】

絶縁膜1130、1132、1134としては、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜はもちろん、その他にもエポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料、シリコン系材料等の単層または積層構造を用いて形成することができる。特にエポキシ、ポリイミド、ポリアミド、

50

ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料、シロキサン系材料等の材料は、スピンドルコートィング法、液滴吐出法または印刷法等を用いることによって形成することができるため、平坦化や処理時間の効率化を図ることができる。絶縁膜1130、1132、1133は、同じ材料を用いて形成してもよいし、別々の材料を用いて形成してもよい。また、上記実施の形態3で示したように、絶縁膜1130、1132、1134にプラズマ処理を行い酸化または窒化させることも可能である。

#### 【0145】

導電膜1133としては、銅(Cu)、アルミニウム(Al)や銀(Ag)や金(Au)、クロム(Cr)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、ニッケル(Ni)、炭素(C)等の金属、金属化合物を1つまたは複数有する導電材料を用いることができる。10

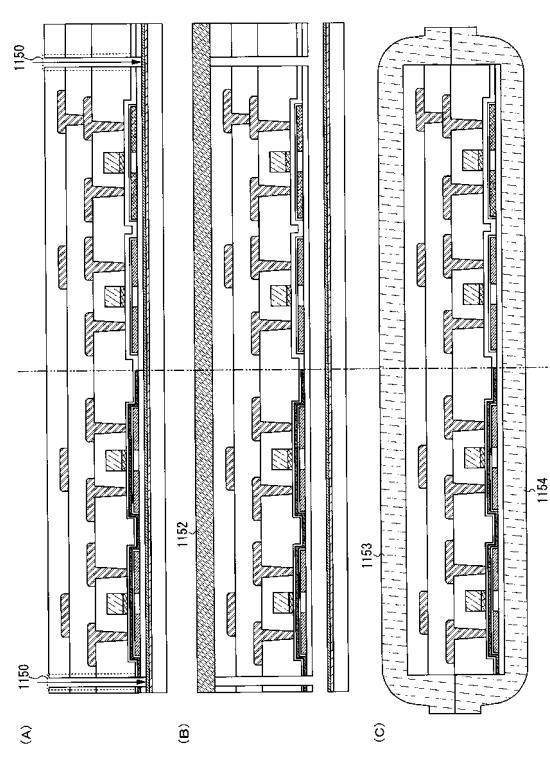

#### 【0146】

次に、記憶素子1151a、1151b、薄膜トランジスタ1151c、1151dを避けた領域にレーザー光の照射等によって、開口部1150を形成して剥離層1103を露出させ、物理的手段を用いて基板1101から素子群1155を剥離させる。また、図16(A)に示すように、物理的手段を用いて剥離する前に当該開口部1150からエッチング剤を導入することによって剥離層1103を除去してもよい。剥離層1103の除去を行う場合には、剥離層1103は、全て除去してもよいし、完全に除去せずに選択的に一部残してもよい。剥離層1103の一部を残すことによって、エッチング剤によって剥離層1103を除去した後であっても、基板1101上に記憶素子1151a、1151b、薄膜トランジスタ1151c、1151dを保持することができ、後の工程において取扱が簡便となる。エッチング剤としては、三フッ化塩素ガス等のフッ化ハロゲンまたはハロゲンを含む気体や液体を使用することができる。他にも、CF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>、F<sub>2</sub>等を用いることもできる。20

#### 【0147】

基板1101から素子群を剥離させる場合には、例えば、図16(B)に示すように、絶縁膜1134に接着性を有する第1のシート材1152を接着させて、物理的手段を用いて基板1101から素子群1155を剥離させることができる。

#### 【0148】

第1のシート材1152は、可撓性のフィルムを利用することができ、少なくとも一方の面に粘着剤を有する面が設けてある。例えば、ポリエチレン等の基材として用いるベースフィルム上に粘着剤が設けてあるシート材を利用することができる。粘着剤としては、アクリル樹脂等を含んだ樹脂材料または合成ゴム材料からなる材料を用いることができる。30

#### 【0149】

次に、剥離させた素子群1155を可撓性を有するフィルムで封止する。ここでは、第2のシート材1153および第3のシート材1154を用いて素子群1155の封止を行う(図16(C))。

#### 【0150】

第2のシート材1153、第3のシート材1154は、可撓性のフィルムを利用することができます、例えば、ポリプロピレン、ポリエチレン、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、纖維質な材料からなる紙、基材フィルム(ポリエチレン、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルム等を利用することができる。また、フィルムは、熱圧着により接着が行われるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、または最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により接着する。また、第1のシート材17と第2のシート材18とで素子形成層を封止する場合には、第1のシート材も同様の材料を用いて封止を行えばよい。40

#### 【0151】

以上の工程により、記憶素子を有し、非接触でデータのやりとりが可能である半導体装置を得ることができる。また、本実施の形態で示した半導体装置は、可携性を有している。

#### 【0152】

なお、ロジック部を選択的に酸化する方法は、図15(A)で示したように、メモリ部に形成されている酸素を含む絶縁膜1123の上面にレジストマスク1124を形成する方法以外を用いてもよい。例えば、図17(A)に示すように、メモリ部に形成されている絶縁膜1123の上面に導電膜1160を形成する方法がある。メモリ部のみに選択的に導電膜1160を形成することにより、ロジック部を選択的に酸化して酸化膜1125を形成することができる(図17(B))。この方法を用いた場合は、導電膜を除去せずにそのまま第1の導電膜及び第2の導電膜を積層し、選択的にエッチングすればよい。このため、メモリ部に形成される導電膜は、3層構造になっている(図17(C))。導電膜1160としては、銅(Cu)、アルミニウム(Al)や銀(Ag)や金(Au)、クロム(Cr)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、ニッケル(Ni)、炭素(C)等の金属、金属化合物を1つまたは複数有する導電材料を用いることができる。

#### 【0153】

本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。つまり、上記実施の形態で示した材料や形成方法は、本実施の形態でも利用することができるし、本実施の形態で示した材料や形成方法は上記実施の形態でも利用することができる。

#### 【0154】

##### (実施の形態6)

本実施の形態では、実施の形態5で説明した記憶素子を有する半導体装置の作製方法とは別の作製方法について、図面を参照して説明する。

#### 【0155】

まず、上記実施の形態5で説明したように図14(B)の状態になるまで作製する。

#### 【0156】

次に、酸化膜1121及び下地膜1104上に、分散された導電性粒子または半導体粒子を含む層(以下、「分散粒子層1181」と示す。)を形成する(図18(A))。分散粒子層1181の作製方法としては、スパッタリング法、プラズマCVD法、減圧CVD(LPCVD)法、蒸着法、液滴吐出法等の公知の手法を用いることができる。分散粒子の大きさは、0.1~10nm、好ましくは2~5nmである。また、導電性粒子の材料としては、金、銀、銅、パラジウム、白金、コバルト、タンゲステン、ニッケル等を用いることができる。半導体粒子の材料としては、シリコン(Si)、ゲルマニウム(Ge)、またシリコンゲルマニウム合金等を用いることができる。ここでは、分散粒子層1181としてシリコン微結晶膜を形成する。また、酸素を含む雰囲気下または窒素を含む雰囲気下でプラズマ処理を行うことにより、分散粒子1181層の表面を酸化または窒化してもよい。なお、分散微粒子の他にも導電膜を設けることも可能である。

#### 【0157】

次に、分散粒子層1181上に絶縁膜1182を形成する(図18(B))。絶縁膜1182としては、酸化珪素(SiO<sub>x</sub>)または酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)等を用いる。

#### 【0158】

次に、図18(C)に示すように記憶素子部のみに選択的にレジストマスク1183を形成した後、ロジック部のみを選択的に酸化する。具体的には、ロジック部の分散粒子1181及び窒素を含む酸化珪素膜からなる絶縁膜1182に対して酸素を含む雰囲気中で高密度プラズマ処理を行う。このプラズマ処理により、ロジック部の分散粒子1181及び窒素を含む酸化珪素膜1182は酸化され、酸化膜1184が形成される(図18(D))。

#### 【0159】

10

20

30

40

50

この後の工程については、上記で説明したものを用いることによって、記憶素子を有し、非接触でデータのやりとりが可能である半導体装置を得ることができる。なお、図18の工程において、分散微粒子1181の変わりに結晶質半導体膜を形成し、当該結晶質半導体膜にプラズマ処理を行い酸化または窒化することによって酸化窒化珪素膜1182を設ける構成とすることもできる。結晶質半導体膜は、直接設けてもよいし一旦非晶質半導体膜を設けた後に結晶化を行うことにより設けてもよい。

#### 【0160】

##### (実施の形態7)

本実施の形態では、上記実施の形態5、6で説明した半導体装置の作製方法とは別の作製方法について、図面を参照して説明する。

10

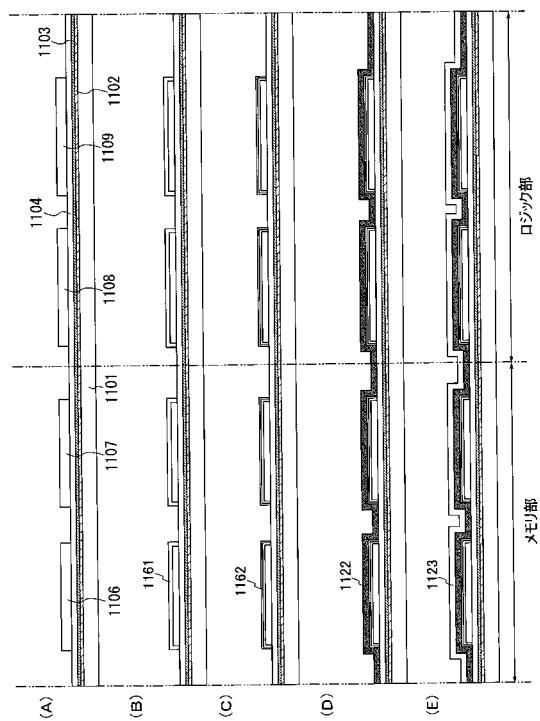

#### 【0161】

まず、実施の形態5で説明したように(図14(A))の状態になるまで作製し、第4の半導体膜1109を覆って形成されたレジストマスク1110を除去する(図29(A))。

#### 【0162】

次に、第1の半導体膜1106～第4の半導体膜1109に対して酸素を含む雰囲気中で高密度プラズマ処理を行うことにより、第1の半導体膜1106～第4の半導体膜1109の表面(上面及び側面)に酸化膜1161を形成する(図29(B))。酸化膜1161の厚さは、2～10nmに形成する。

#### 【0163】

次に、酸化膜1161に対して窒素を含む雰囲気中で高密度プラズマ処理を行うことにより、酸化膜1161の表面(上面及び側面)を窒化して窒素を含む酸化膜1162を形成する(図29(C))。窒化処理により酸化膜1161の表面に形成される窒素を含む酸化膜1162の厚さは、1～5nmとなる。なお、プラズマ処理の条件は、上述した実施の形態に記した条件を用いればよい。また、酸化膜1161及び窒素を含む酸化膜1162はメモリ部の記憶素子におけるトンネル絶縁膜として機能する。

20

#### 【0164】

なお、酸化膜1161及び窒素を含む酸化膜1162の代わりに、第1の半導体膜1106～第4の半導体膜1109に酸素及び窒素を含む雰囲気中で高密度プラズマ処理を行うことにより、当該第1の半導体膜1106～第4の半導体膜1109の表面(上面及び側面)に窒素を含む酸化膜を形成してもよい。

30

#### 【0165】

次に、窒素を含む酸化膜1162上に絶縁膜1122を形成する(図29(D))。絶縁膜1122としては、プラズマCVD法により窒化珪素膜を4～20nmの厚さに形成することが好ましい。また、メモリ部における絶縁膜1122は、電荷をトラップ(捕獲)する絶縁膜として機能する。

#### 【0166】

次に、絶縁膜1122上に絶縁膜1123を形成する。(図29(E))。絶縁膜1123としては、ここではプラズマCVD法を用いて酸化窒化珪素膜を4～20nmの厚さに形成することが好ましい。

40

#### 【0167】

この後の工程については、実施の形態5で説明した(図15(A))以降の工程にしたがって、メモリ部及びロジック部を完成させることができる。

#### 【0168】

本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。つまり、上記実施の形態で示した材料や形成方法は、本実施の形態でも利用することができるし、本実施の形態で示した材料や形成方法は上記実施の形態でも利用することができる。

#### 【0169】

##### (実施の形態8)

本実施の形態では、非接触でデータのやりとりが可能である半導体装置の適用例に関し

50

て図面を参照して以下に説明する。なお、非接触でデータのやりとりが可能である半導体装置は利用の形態によっては、RFID (Radio Frequency Identification)、IDタグ、ICタグ、ICチップ、RFタグ (Radio Frequency)、無線タグ、電子タグまたは無線チップともよばれる。

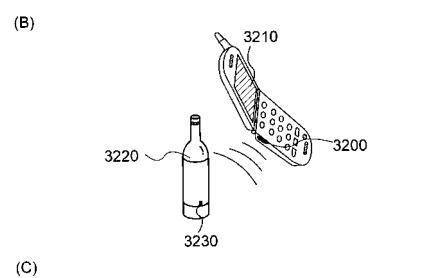

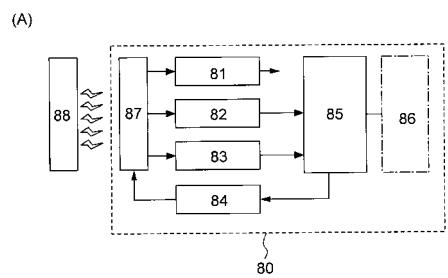

#### 【0170】

RFID80は、非接触でデータを交信する機能を有し、電源回路81、クロック発生回路82、データ復調回路83、データ変調回路84、他の回路を制御する制御回路85、記憶回路86およびアンテナ87を有している（図20（A））。なお、記憶回路は1つに限定されず、複数であっても良く、SRAM、フラッシュメモリ、ROMまたはFeRAM等や上記実施の形態で示した有機化合物層を記憶素子部に用いたものを用いることができる。10

#### 【0171】

リーダ／ライタ88から電波として送られてきた信号は、アンテナ87において電磁誘導により交流の電気信号に変換される。電源回路81では、交流の電気信号を用いて電源電圧を生成し、電源配線を用いて各回路へ電源電圧を供給する。クロック発生回路82は、アンテナ87から入力された交流信号を基に、各種クロック信号を生成し、制御回路85に供給する。復調回路83では、当該交流の電気信号を復調し、制御回路85に供給する。制御回路85では、入力された信号に従って各種演算処理を行う。記憶回路86では、制御回路85において用いられるプログラムやデータ等が記憶されている他、演算処理時の作業エリアとしても用いることができる。そして、制御回路85から変調回路84にデータが送られ、変調回路84から当該データに従ってアンテナ87に負荷変調を加えることができる。リーダ／ライタ88は、アンテナ87に加えられた負荷変調を電波で受け取ることにより、結果的にデータを読み取ることが可能となる。20

#### 【0172】

また、RFIDは、各回路への電源電圧の供給を電源（バッテリー）を搭載せず電波により行うタイプとしてもよいし、電源（バッテリー）を搭載して電波と電源（バッテリー）により各回路に電源電圧を供給するタイプとしてもよい。

#### 【0173】

上記実施の形態で示した構成を用いることによって、折り曲げることが可能なRFIDを作製することが可能となるため、曲面を有する物体に貼り付けて設けることが可能となる。30

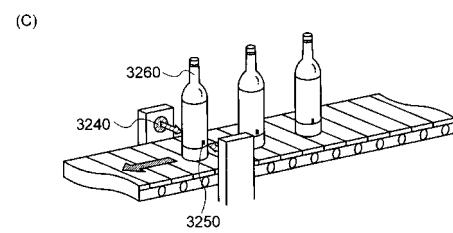

#### 【0174】

次に、可撓性を有するRFIDの使用形態の一例について説明する。表示部3210を含む携帯端末の側面には、リーダ／ライタ3200設けられ、品物3220の側面にはRFID3230が設けられる（図20（B））。品物3220が含むRFID3230にリーダ／ライタ3200をかざすと、表示部3210に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品3260をベルトコンベアにより搬送する際に、リーダ／ライタ3240と、商品3260に設けられたRFID3250を用いて、該商品3260の検品を行うことができる（図20（C））。このように、システムにRFIDを活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。また、上記実施の形態で示したように、曲面を有する物体に貼り付けた場合であっても、RFIDに含まれるトランジスタ等の損傷を防止し、信頼性の高いRFIDを提供することが可能となる。40

#### 【0175】

また、上述した以外にも可撓性を有するRFIDの用途は広範にわたり、非接触で対象物の履歴等の情報を明確にし、生産・管理等に役立てる商品であればどのようなものにも適用することができる。例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図21を用いて説明する。50

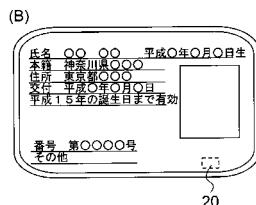

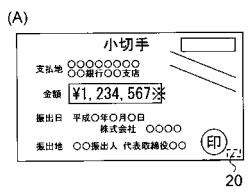

## 【0176】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの（金券）、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指す（図21（A）参照）。証書類とは、運転免許証、住民票等を指す（図21（B）参照）。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す（図21（C）参照）。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指す（図21（D）参照）。書籍類とは、書物、本等を指す（図21（E）参照）。記録媒体とは、DVDソフト、ビデオテープ等を指す（図21（F）参照）。乗物類とは、自転車等の車両、船舶等を指す（図21（G）参照）。身の回り品とは、鞄、眼鏡等を指す（図21（H）参照）。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話機等を指す。

## 【0177】

紙幣、硬貨、有価証券類、証書類、無記名債券類等にRFIDを設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、生活用品類、電子機器等にRFIDを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等にRFIDを設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。RFIDの設け方としては、物品の表面に貼ったり、物品に埋め込んだりして設ける。例えば、本ならば紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。可撓性を有するRFIDを用いることによって、紙等に設けた場合であっても、上記実施の形態で示した構造を有する半導体装置を用いてRFIDを設けることにより、当該RFIDに含まれる素子の破損等を防止することができる。

## 【0178】

このように、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等にRFIDを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類にRFIDを設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にセンサを備えたRFIDを埋め込むことによって、生まれた年や性別または種類等はもちろん現在の体温等の健康状態を容易に管理することが可能となる。

## 【0179】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。

## 【0180】

（実施の形態9）

本実施の形態では、本発明の半導体装置について上記実施の形態とは異なる構造に関して図面を参照して説明する。具体的には、画素部を有する半導体装置の一例について説明する。

## 【0181】

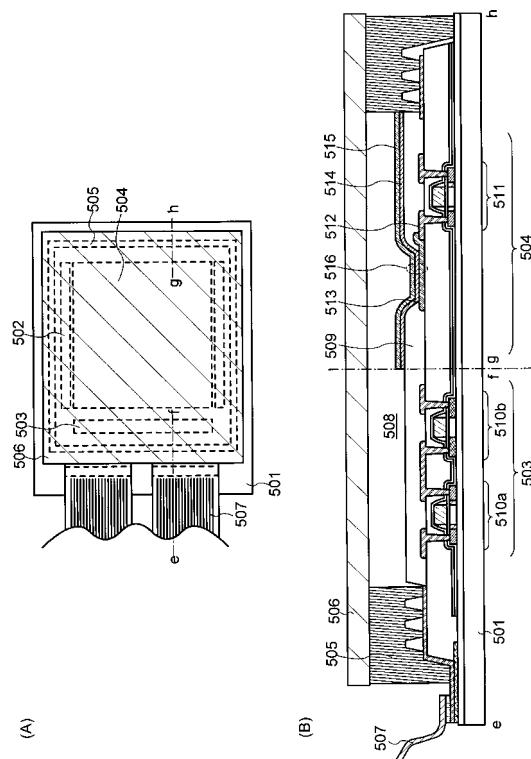

まず、画素部に発光素子を有する場合について図22に示す。なお、図22（A）は、半導体装置の一例を示す上面図、図22（B）は図22（A）をe-f間とg-h間で切断した断面図である。

## 【0182】

図22（A）に示すように、本実施の形態で示す半導体装置は、基板501上に設けられた走査線駆動回路502、信号線駆動回路503および画素部504等を有している。また、少なくとも画素部504を基板501と共に挟むように対向基板506が設けられている。走査線駆動回路502、信号線駆動回路503および画素部504は、基板501上に上記実施の形態で示したいずれかの構造を有する薄膜トランジスタを形成して設け

る。基板 501 と対向基板 506 は、シール材 505 により貼り合わされている。また、走査線駆動回路 502 および信号線駆動回路 503 は、外部入力端子となる FPC 507 からビデオ信号、クロック信号、スタート信号、リセット信号等を受け取る。なお、ここでは FPC (flexible printed circuit) しか図示されていないが、この FPC にはプリント配線基盤 (PWB) が取り付けられていても良い。

#### 【0183】

また、図 22 (B) は、図 22 (A) の e - f 間と g - h 間で切断した場合の断面図を示しており、基板 501 上に信号線駆動回路 503 と画素部 504 に含まれる薄膜トランジスタが設けられている。信号線駆動回路 503 は、上記実施の形態で示したいずれかの構造を有する n 型の薄膜トランジスタ 510a と p 型の薄膜トランジスタ 510b とを組み合わせた CMOS 回路が形成されている。また、走査線駆動回路 502 や信号線駆動回路 503 等の駆動回路は、公知の CMOS 回路、PMOS 回路もしくは NMOS 回路で形成しても良い。また、本実施の形態では、基板 501 上に走査線駆動回路 502 や信号線駆動回路 503 等の駆動回路を形成したドライバー一体型を示すが、必ずしもその必要はなく、基板 501 上ではなく外部に形成することもできる。

#### 【0184】

また、画素部 504 は、発光素子 516 と当該発光素子 516 駆動するための薄膜トランジスタ 511 とを含む複数の画素により形成されている。薄膜トランジスタ 511 は、上記実施の形態で示したいずれかの構造を有する薄膜トランジスタを適用することができる。また、ここでは、薄膜トランジスタ 511 のソースまたはドレイン領域に接続されている導電膜 512 に接続するように第 1 の電極 513 が設けられ、当該第 1 の電極 513 の端部を覆うように絶縁膜 509 が形成されている。絶縁膜 509 は、複数の画素において隔壁として機能している。

#### 【0185】

絶縁膜 509 として、ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。また、カバーレッジを良好なものとするため、絶縁膜 509 は、当該絶縁物 509 の上端部または下端部に曲率を有する曲面が形成されるように設ける。例えば、絶縁物 509 の材料としてポジ型の感光性アクリルを用いた場合、絶縁物 509 の上端部のみに曲率半径 (0.2 μm ~ 3 μm) を有する曲面を持たせることが好ましい。絶縁物 509 としては、感光性の光によってエッチャントに不溶解性となるネガ型、或いは光によってエッチャントに溶解性となるポジ型のいずれも使用することができる。他にも、絶縁膜 509 としてエポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン等の有機材料やシリコキサン樹脂からなる単層または積層構造で設けることができる。また、上記実施の形態で示したように、絶縁膜 509 にプラズマ処理を行い、当該絶縁膜 509 を酸化または窒化することによって、絶縁膜 509 の表面を改質して緻密な膜を得ることも可能である。絶縁膜 509 の表面を改質することによって、当該絶縁膜 509 の強度が向上し開口部等の形成時におけるクラックの発生やエッチング時の膜減り等の物理的ダメージを低減することができる。また、絶縁膜 509 の表面が改質されることによって、当該絶縁膜 509 上に設けられる発光層 514 との密着性等の界面特性が向上する。

#### 【0186】

また、図 22 に示す半導体装置は、第 1 の電極 513 上に発光層 514 が形成され、当該発光層 514 上に第 2 の電極 515 が形成されている。これら第 1 の電極 513、発光層 514 および第 2 の電極 515 の積層構造により発光素子 516 が設けられている。

#### 【0187】

発光層 514 としては、低分子系材料、中分子材料（オリゴマー、デンドリマーを含む）、または高分子系材料等による有機化合物を単層または積層構造を、蒸着マスクを用いた蒸着法、インクジェット法、スピンドルコート法等の公知の方法によって形成することができる。また、発光層 514 として、有機化合物の他に無機化合物を用いることも可能である。一般的に、発光層に用いられる発光材料が有機化合物であるか、無機化合物であるか

10

20

30

40

50

によって、前者は有機 E L 素子、後者は無機 E L 素子と呼ばれており、本実施の形態ではどちらを適用してもよい。

#### 【 0 1 8 8 】

無機 E L 素子は、その素子構成により、分散型無機 E L 素子と薄膜型無機 E L 素子とに分類される。前者は、発光材料の粒子をバインダ中に分散させた発光層を有し、後者は、蛍光材料の薄膜からなる発光層を有している点に違いがある。しかし、そのメカニズムは共通しており、高電界で加速された電子と母体材料又は発光中心の衝突励起により発光が得られる。本実施の形態では、無機 E L 素子を設ける場合には、分散型無機 E L 素子又は薄膜型無機 E L 素子のいずれかを適用すればよい。

#### 【 0 1 8 9 】

第 1 の電極 5 1 3 および第 2 の電極 5 1 5 は、第 1 の電極 5 1 3 および第 2 の電極 5 1 5 を直流で駆動する場合には、一方を陽極として用い、他方を陰極として用いる。陽極として用いる場合には、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウム錫酸化物)膜、珪素を含有したインジウム錫酸化物膜、酸化インジウムに 2 ~ 20 wt % の酸化亜鉛(ZnO)を混合したターゲットを用いてスパッタ法により形成した透明導電膜、酸化亜鉛(ZnO)、窒化チタン膜、クロム膜、タンゲステン膜、Zn 膜、Pt 膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との 3 層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。陰極として用いる場合には、仕事関数の小さい材料(A1、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、またはCa<sub>3</sub>N<sub>2</sub>)を用いることが好ましい。なお、陰極として用いる電極を透光性とする場合には、電極として、膜厚を薄くした金属薄膜と、透明導電膜(ITO、珪素を含有したインジウム錫酸化物、酸化インジウムに 2 ~ 20 wt % の酸化亜鉛(ZnO)を混合したターゲットを用いてスパッタ法により形成した透明導電膜、酸化亜鉛(ZnO)等)との積層を用いるのが良い。ここでは第 1 の電極 5 1 3 として透光性を有する ITO を用い、基板 5 0 1 側から光を取り出す構造とする。なお、第 2 の電極 5 1 5 に透光性を有する材料を用いることにより対向基板 5 0 6 側から光を取り出す構造としてもいし、第 1 の電極 5 1 3 および第 2 の電極 5 1 5 を透光性を有する材料で設けることによって、基板 5 0 1 および対向基板 5 0 6 の両側に光を取り出す構造(両面射出)することも可能である。また、第 1 の電極 5 1 3 および第 2 の電極 5 1 5 を交流で駆動する場合には、第 1 の電極 5 1 3 または第 2 の電極 5 1 5 として、上述したいずれかの材料を用いて形成すればよく、一方または両方を透光性を有する材料で設ければよい。

#### 【 0 1 9 0 】

また、ここではシール材 5 0 5 で対向基板 5 0 6 を基板 5 0 1 と貼り合わせることにより、基板 5 0 1 、対向基板 5 0 6 、およびシール材 5 0 5 で囲まれた空間 5 0 8 に本発明の発光素子 5 1 6 が備えられた構造になっている。なお、空間 5 0 8 には、不活性気体(窒素やアルゴン等)が充填される場合の他、シール材 5 0 5 で充填される構成も含むものとする。

#### 【 0 1 9 1 】

なお、シール材 5 0 5 にはエポキシ系樹脂を用いるのが好ましい。また、これらの材料はできるだけ水分や酸素を透過しない材料であることが望ましい。また、対向基板 5 0 6 に用いる材料としてガラス基板や石英基板の他、FRP(Fiberglass-Reinforced Plastics)、PVF(ポリビニルフロライド)、マイラー、ポリエステルまたはアクリル等からなるプラスチック基板を用いることができる。

#### 【 0 1 9 2 】

以上のようにして、高い密度を有するプラズマ処理(高密度プラズマ処理)で形成された半導体膜または窒化膜を有する発光装置を設けることができる。

#### 【 0 1 9 3 】

なお、画素部を有する半導体装置としては、上述したように画素部に発光素子用いた構

10

20

30

40

50

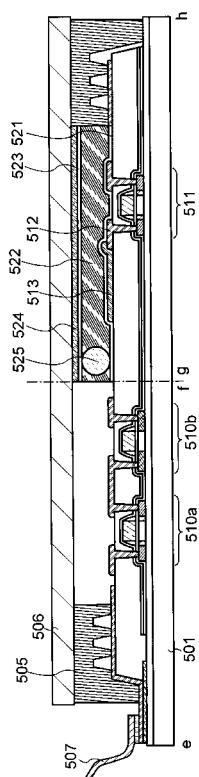

成に限られず、画素部に液晶を用いた半導体装置も含まれる。画素部に液晶を用いた場合の半導体装置を図23に示す。

#### 【0194】

図23は、液晶を画素部に有する半導体装置の一例を示しており、導電膜512および第1の電極513を覆うように設けられた配向膜521と対向基板506に設けられた配向膜523との間に液晶522が設けられている。また、第2の電極524が対向基板506に設けられており、第1の電極513と第2の電極524間に設けられた液晶に加える電圧を制御して光の透過率を制御することにより像の表示を行う。また、液晶522中に第1の電極513と第2の電極524との間の距離(セルギャップ)を制御するために球状のスペーサ525が設けられている。なお、薄膜トランジスタ510a、510bまたは511としては、上記実施の形態で示したいずれかの構造を適用することができる。そのため、上述したように高い密度を有するプラズマ処理(高密度プラズマ処理)で形成された半導体膜または窒化膜を有する液晶表示装置を設けることができる。10

#### 【0195】

このように、本実施の形態で示す半導体装置は、画素部を発光素子で設けてもよいし液晶で設けてもよい。

#### 【0196】

次に、上記画素部を有する半導体装置の利用形態について図面を参照して説明する。

#### 【0197】

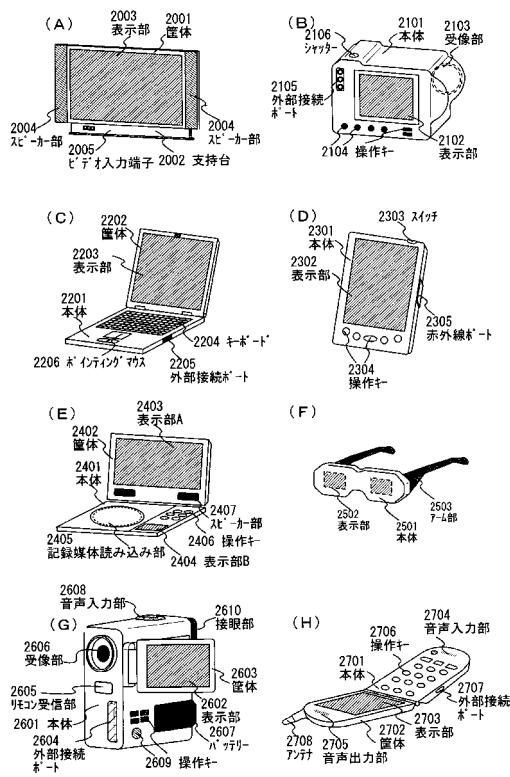

上記画素部を有する半導体装置の利用形態として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話機、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDVD(digital versatile disc)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などの電子機器が挙げられる。それらの具体例を以下に示す。20

#### 【0198】

図24(A)はテレビ受像機であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。上記実施の形態に示した構造または作製方法を表示部2003や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、テレビ受像機を作製することができる。30

#### 【0199】

図24(B)はデジタルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。上記実施の形態に示した構造または作製方法を表示部2102や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、デジタルカメラを作製することができる。

#### 【0200】

図24(C)はコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。上記実施の形態に示した構造または作製方法を表示部2203や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、コンピュータを作製することができる。40

#### 【0201】

図24(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。上記実施の形態に示した構造または作製方法を表示部2302や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、モバイルコンピュータを作製することができる。

#### 【0202】

図24(E)は記録媒体を備えた携帯型の画像再生装置(DVD再生装置など)であり50

、本体 2401、筐体 2402、表示部 A2403、表示部 B2404、記録媒体（D V D 等）読み込み部 2405、操作キー 2406、スピーカー部 2407 等を含む。表示部 A2403 は主として画像情報を表示し、表示部 B2404 は主として文字情報を表示する。上記実施の形態に示した構造または作製方法を表示部 A2403 や表示部 B2404 や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、画像再生装置を作製することができる。なお、記録媒体を備えた画像再生装置にはゲーム機器なども含まれる。

#### 【0203】

図 24 (F) はゴーグル型ディスプレイ（ヘッドマウントディスプレイ）であり、本体 2501、表示部 2502、アーム部 2503 を含む。上記実施の形態に示した構造または作製方法を表示部 2502 や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、ゴーグル型ディスプレイを作製することができる。10

#### 【0204】

図 24 (G) はビデオカメラであり、本体 2601、表示部 2602、筐体 2603、外部接続ポート 2604、リモコン受信部 2605、受像部 2606、バッテリー 2607、音声入力部 2608、操作キー 2609、接眼部 2610 等を含む。上記実施の形態に示した構造または作製方法を表示部 2602 や駆動回路等に設けられる薄膜トランジスタ等の半導体素子に適用することによって、ビデオカメラを作製することができる。

#### 【0205】

図 24 (H) は携帯電話機であり、本体 2701、筐体 2702、表示部 2703、音声入力部 2704、音声出力部 2705、操作キー 2706、外部接続ポート 2707、アンテナ 2708 等を含む。上記実施の形態に示した構造または作製方法を表示部 2703 や駆動回路に設けられる薄膜トランジスタ等の半導体素子に適用することによって、携帯電話機を作製することができる。20

#### 【0206】

以上の様に、本発明の半導体装置の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。なお、本実施の形態は上記実施の形態と自由に組み合わせて行うことができる。

#### 【実施例 1】

#### 【0207】

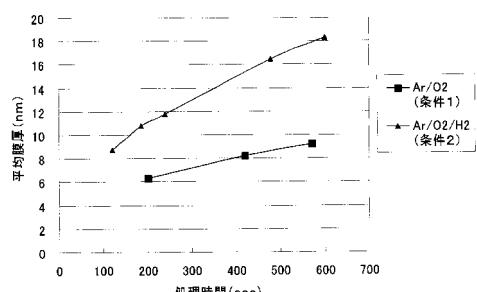

本実施例では、上記実施の形態で示した高密度プラズマ処理により被処理物に酸化処理を行った場合の酸化特性に関して説明する。具体的には、高密度プラズマ処理を行う際に用いるガスの違いによる被処理物の酸化速度の特性に関して示す。30

#### 【0208】

まず、基板上に CVD 法により下地膜として酸化窒化珪素（SiO<sub>x</sub>N<sub>y</sub> (x > y)）を形成し、当該下地膜上に CVD 法により非晶質珪素膜を形成した。次に、非晶質珪素膜に膜中に含まれる水素を離脱させるために熱処理を行い、その後、レーザ光を照射して非晶質珪素膜を結晶化して結晶質半導体膜とした。そして、結晶質半導体膜に高密度プラズマ処理により酸化処理を行った。なお、基板としてはガラス基板を用い、酸化窒化珪素は概略 100 nm 形成し、非晶質半導体膜は概略 66 nm 形成した。40

#### 【0209】

高密度プラズマ処理は、133.33 Pa の圧力下で、Ar と酸素を含む雰囲気下（Ar : 500 sccm、O<sub>2</sub> : 5 sccm）（条件 1）又は Ar と酸素と水素雰囲気下（Ar : 500 sccm、O<sub>2</sub> : 5 sccm、H<sub>2</sub> : 5 sccm）（条件 2）で行った。そして、条件 1 又は条件 2 で行った場合の、結晶質半導体膜の酸化速度の特性に関して観察を行った。

#### 【0210】

条件 1 及び条件 2 の結晶質半導体膜の酸化速度を図 28 に示す。なお、図 28 は、縦軸が平均膜厚 (nm) を示し、横軸が処理時間 (sec) を示している。処理時間とは結晶質半導体膜にプラズマ処理を行った時間をいい、平均膜厚とはプラズマ処理により結晶質

半導体膜が酸化されることにより形成された酸化膜の膜厚をいう。

**【0211】**

条件1及び条件2とともに、プラズマの処理時間が増えるにつれ結晶質半導体膜が酸化され、当該結晶質半導体膜に形成される酸化膜の膜厚が増加することが観察された。また、条件1(Arと酸素を含む雰囲気下)でプラズマ処理を行った場合と比較して、条件1に水素を加えた条件2(Arと酸素と水素雰囲気下)でプラズマ処理を行った場合の方が、処理時間に対して結晶質半導体膜が酸化される割合が高かった。つまり、高密度プラズマ処理を用いて結晶質半導体膜に酸化処理を行う場合に、水素を加えた雰囲気下で行うことによって、より短時間で結晶質半導体膜を酸化させ当該結晶質半導体膜表面に膜厚が厚い酸化膜を形成されることが分かった。

10

**【0212】**

以上の結果より、結晶質半導体膜に高密度プラズマ処理により酸化膜を形成する場合、反応ガスに水素を加えることによって、より短時間で所望の膜厚の酸化膜を形成することができ、処理時間を短縮することが可能となった。

**【図面の簡単な説明】**

**【0213】**

【図1】本発明の半導体装置の一例を示す図。

【図2】本発明の半導体装置の作製方法の一例を示す図。

【図3】本発明の半導体装置の作製方法の一例を示す図。

【図4】本発明の半導体装置の作製方法の一例を示す図。

20

【図5】本発明の半導体装置の作製方法の一例を示す図。

【図6】本発明の半導体装置の作製方法の一例を示す図。

【図7】本発明の半導体装置の作製方法の一例を示す図。

【図8】本発明の半導体装置の作製方法の一例を示す図。

【図9】本発明の半導体装置の作製方法の一例を示す図。

【図10】本発明の半導体装置の作製方法の一例を示す図。

【図11】本発明の半導体装置の作製方法の一例を示す図。

【図12】本発明の半導体装置の作製する装置の一例を示す図。

【図13】本発明の半導体装置の作製方法の一例を示す図。

【図14】本発明の半導体装置の作製方法の一例を示す図。

30

【図15】本発明の半導体装置の作製方法の一例を示す図。

【図16】本発明の半導体装置の作製方法の一例を示す図。

【図17】本発明の半導体装置の作製方法の一例を示す図。

【図18】本発明の半導体装置の作製方法の一例を示す図。

【図19】本発明の半導体装置の作製方法の一例を示す図。

【図20】本発明の半導体装置の使用形態の一例を示す図。

【図21】本発明の半導体装置の使用形態の一例を示す図。

【図22】本発明の半導体装置の一例を示す図。

【図23】本発明の半導体装置の一例を示す図。

【図24】本発明の半導体装置の使用形態の一例を示す図。

40

【図25】本発明の半導体装置の作製方法の一例を示す図。

【図26】本発明の半導体装置の一例を示す図。

【図27】本発明の半導体装置の作製方法の一例を示す図。

【図28】本発明の半導体装置の作製方法における酸化速度の特性を示す図。

【図29】本発明の半導体装置の作製方法の一例を示す図。

**【符号の説明】**

**【0214】**

10 基板

17 シート材

18 シート材

50

|       |           |    |

|-------|-----------|----|

| 8 0   | R F I D   |    |

| 8 1   | 電源回路      |    |

| 8 2   | クロック発生回路  |    |

| 8 3   | データ復調回路   |    |

| 8 3   | 復調回路      |    |

| 8 4   | 変調回路      |    |

| 8 5   | 制御回路      |    |

| 8 6   | 記憶回路      |    |

| 8 7   | アンテナ      |    |

| 8 8   | リーダ / ライタ | 10 |

| 1 0 1 | 基板        |    |

| 1 0 2 | 絶縁膜       |    |

| 1 0 3 | 半導体膜      |    |

| 1 0 4 | ゲート絶縁膜    |    |

| 1 0 5 | ゲート電極     |    |

| 1 0 6 | 絶縁膜       |    |

| 1 0 7 | 絶縁膜       |    |

| 1 0 8 | 導電膜       |    |

| 1 2 3 | 絶縁膜       |    |

| 1 2 4 | 絶縁膜       | 20 |

| 1 2 6 | 絶縁膜       |    |

| 1 2 8 | カセット      |    |

| 1 3 1 | 絶縁膜       |    |

| 1 3 2 | 絶縁膜       |    |

| 1 3 3 | 絶縁膜       |    |

| 1 3 4 | 絶縁膜       |    |

| 1 3 5 | 絶縁膜       |    |

| 1 3 6 | 絶縁膜       |    |

| 1 3 7 | 絶縁膜       |    |

| 1 4 1 | 絶縁膜       | 30 |

| 1 4 2 | 絶縁膜       |    |

| 1 7 1 | 膜         |    |

| 1 7 2 | 絶縁膜       |    |

| 1 7 3 | ゴミ        |    |

| 1 7 4 | 絶縁膜       |    |

| 1 7 5 | 絶縁膜       |    |

| 1 8 1 | 窒化膜       |    |

| 2 0 5 | 絶縁膜       |    |

| 2 7 1 | 膜         |    |

| 2 7 2 | 絶縁膜       | 40 |

| 2 7 3 | レジスト      |    |

| 2 7 4 | 開口部       |    |

| 2 7 5 | 絶縁膜       |    |

| 2 7 6 | 絶縁膜       |    |

| 3 1 0 | ロードロック室   |    |

| 3 1 1 | チャンバー     |    |

| 3 1 2 | チャンバー     |    |

| 3 1 3 | チャンバー     |    |

| 3 1 4 | チャンバー     |    |

| 3 1 5 | ロードロック室   | 50 |

|         |          |    |

|---------|----------|----|

| 3 2 0   | 共通室      |    |

| 3 2 1   | ロボットアーム  |    |

| 3 2 2   | ゲート弁     |    |

| 3 2 4   | ゲート弁     |    |

| 3 2 8   | カセット     |    |

| 3 2 9   | カセット     |    |

| 3 3 1   | 被処理物     |    |

| 3 5 1   | 支持台      |    |

| 3 5 2   | ガス供給部    |    |

| 3 5 3   | 排気口      | 10 |

| 3 5 4   | アンテナ     |    |

| 3 5 5   | 誘電板      |    |

| 3 5 6   | 高周波供給部   |    |

| 3 5 7   | 温度制御部    |    |

| 3 5 8   | 高密度プラズマ  |    |

| 5 0 1   | 基板       |    |

| 5 0 2   | 走査線駆動回路  |    |

| 5 0 3   | 信号線駆動回路  |    |

| 5 0 4   | 画素部      |    |

| 5 0 5   | シール材     | 20 |

| 5 0 6   | 対向基板     |    |

| 5 0 7   | F P C    |    |

| 5 0 8   | 空間       |    |

| 5 0 9   | 絶縁膜      |    |

| 5 1 1   | 薄膜トランジスタ |    |

| 5 1 2   | 導電膜      |    |

| 5 1 3   | 電極       |    |

| 5 1 4   | 発光層      |    |

| 5 1 5   | 電極       |    |

| 5 1 6   | 発光素子     | 30 |

| 5 2 1   | 配向膜      |    |

| 5 2 2   | 液晶       |    |

| 5 2 3   | 配向膜      |    |

| 5 2 4   | 電極       |    |

| 5 2 5   | スペーサ     |    |

| 1 0 3 a | 半導体膜     |    |

| 1 0 3 b | 半導体膜     |    |

| 1 0 5 a | 導電膜      |    |

| 1 0 5 b | 導電膜      |    |

| 1 1 0 1 | 基板       | 40 |

| 1 1 0 2 | 絶縁膜      |    |

| 1 1 0 3 | 剥離層      |    |

| 1 1 0 4 | 絶縁膜      |    |

| 1 1 0 5 | 結晶性半導体膜  |    |

| 1 1 0 6 | 半導体膜     |    |

| 1 1 0 7 | 半導体膜     |    |

| 1 1 0 8 | 半導体膜     |    |

| 1 1 0 9 | 半導体膜     |    |

| 1 1 0 a | 薄膜トランジスタ |    |

| 1 1 0 b | 薄膜トランジスタ | 50 |

|         |            |    |

|---------|------------|----|

| 1 1 1 0 | レジストマスク    |    |

| 1 1 2 1 | 絶縁膜        |    |

| 1 1 2 2 | 絶縁膜        |    |

| 1 1 2 3 | 絶縁膜        |    |

| 1 1 2 4 | レジストマスク    |    |

| 1 1 2 5 | 酸化膜        |    |

| 1 1 2 6 | 導電膜        |    |

| 1 1 2 7 | 導電膜        |    |

| 1 1 3 0 | 絶縁膜        |    |

| 1 1 3 1 | 導電膜        | 10 |

| 1 1 3 2 | 絶縁膜        |    |

| 1 1 3 3 | 導電膜        |    |

| 1 1 3 4 | 絶縁膜        |    |

| 1 1 4 0 | 素子群        |    |

| 1 1 8 1 | 分散粒子層      |    |

| 1 1 8 2 | 絶縁膜        |    |

| 1 1 8 3 | レジストマスク    |    |

| 1 1 8 4 | 酸化膜        |    |

| 1 1 4 5 | 半導体装置      |    |

| 1 1 5 0 | 開口部        | 20 |

| 1 1 5 2 | シート材       |    |

| 1 1 5 3 | シート材       |    |

| 1 1 5 5 | 素子群        |    |

| 1 2 1 a | 絶縁膜        |    |

| 1 2 1 b | 絶縁膜        |    |

| 1 2 5 a | レジスト       |    |

| 1 2 7 a | 絶縁膜        |    |

| 1 2 7 b | 絶縁膜        |    |

| 1 5 1 a | 端部         |    |

| 1 5 2 a | 端部         | 30 |

| 1 5 3 a | 端部         |    |

| 2 0 0 1 | 筐体         |    |

| 2 0 0 2 | 支持台        |    |

| 2 0 0 3 | 表示部        |    |

| 2 0 0 4 | スピーカー部     |    |

| 2 0 0 5 | ビデオ入力端子    |    |

| 2 1 0 1 | 本体         |    |

| 2 1 0 2 | 表示部        |    |

| 2 1 0 3 | 受像部        |    |

| 2 1 0 4 | 操作キー       | 40 |

| 2 1 0 5 | 外部接続ポート    |    |

| 2 1 0 6 | シャッター      |    |

| 2 2 0 1 | 本体         |    |

| 2 2 0 2 | 筐体         |    |

| 2 2 0 3 | 表示部        |    |

| 2 2 0 4 | キーボード      |    |

| 2 2 0 5 | 外部接続ポート    |    |

| 2 2 0 6 | ポインティングマウス |    |

| 2 2 5 a | 導電膜        |    |

| 2 2 5 b | 導電膜        | 50 |

|           |          |    |

|-----------|----------|----|

| 2 3 0 1   | 本体       |    |

| 2 3 0 2   | 表示部      |    |

| 2 3 0 3   | スイッチ     |    |

| 2 3 0 4   | 操作キー     |    |

| 2 3 0 5   | 赤外線ポート   |    |

| 2 4 0 1   | 本体       |    |

| 2 4 0 2   | 筐体       |    |

| 2 4 0 3   | 表示部 A    |    |

| 2 4 0 4   | 表示部 B    |    |

| 2 4 0 5   | 部        | 10 |

| 2 4 0 6   | 操作キー     |    |

| 2 4 0 7   | スピーカー部   |    |

| 2 5 0 1   | 本体       |    |

| 2 5 0 2   | 表示部      |    |

| 2 5 0 3   | アーム部     |    |

| 2 6 0 1   | 本体       |    |

| 2 6 0 2   | 表示部      |    |

| 2 6 0 3   | 筐体       |    |

| 2 6 0 4   | 外部接続ポート  |    |

| 2 6 0 5   | リモコン受信部  | 20 |

| 2 6 0 6   | 受像部      |    |

| 2 6 0 7   | バッテリー    |    |

| 2 6 0 8   | 音声入力部    |    |

| 2 6 0 9   | 操作キー     |    |

| 2 6 1 0   | 接眼部      |    |

| 2 7 0 1   | 本体       |    |

| 2 7 0 2   | 筐体       |    |

| 2 7 0 3   | 表示部      |    |

| 2 7 0 4   | 音声入力部    |    |

| 2 7 0 5   | 音声出力部    | 30 |

| 2 7 0 6   | 操作キー     |    |

| 2 7 0 7   | 外部接続ポート  |    |

| 2 7 0 8   | アンテナ     |    |

| 5 1 0 a   | 薄膜トランジスタ |    |

| 5 1 0 b   | 薄膜トランジスタ |    |

| 1 1 2 6 a | 導電膜      |    |

| 1 1 2 6 b | 導電膜      |    |

| 1 1 5 1 a | 薄膜トランジスタ |    |

| 1 1 5 1 b | 薄膜トランジスタ |    |

| 3 2 0 0   | リーダ／ライタ  | 40 |

| 3 2 1 0   | 表示部      |    |

| 3 2 2 0   | 品物       |    |

| 3 2 3 0   | R F I D  |    |

| 3 2 4 0   | リーダ／ライタ  |    |

| 3 2 5 0   | R F I D  |    |

| 3 2 6 0   | 商品       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

(C)

(D)

(E)

(F)

(G)

(H)

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 21/318

A

審査官 宮澤 尚之

(56)参考文献 国際公開第03/056622(WO, A1)

特開2004-343031(JP, A)

特開平06-314698(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/336

H 01L 29/786

H 01L 21/31 - 21/32