(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-505896

(P2006-505896A)

(43) 公表日 平成18年2月16日(2006.2.16)

(51) Int.C1.

HO1J 11/02

(2006.01)

F1

HO1J 11/02

テーマコード(参考)

B

5C04O

審査請求 未請求 予備審査請求 未請求 (全 16 頁)

(21) 出願番号 特願2003-577292 (P2003-577292)

(86) (22) 出願日 平成15年3月17日 (2003.3.17)

(85) 翻訳文提出日 平成16年9月21日 (2004.9.21)

(86) 國際出願番号 PCT/IB2003/000954

(87) 國際公開番号 WO2003/079392

(87) 國際公開日 平成15年9月25日 (2003.9.25)

(31) 優先権主張番号 02076143.3

(32) 優先日 平成14年3月19日 (2002.3.19)

(33) 優先権主張国 歐州特許庁 (EP)

(71) 出願人 590000248

コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

Koninklijke Philips Electronics N. V.

オランダ国 5621 ベーー アインドーフェン フルーネヴアウツウェッハ

1

G roenewoudseweg 1, 5

621 BA Eindhoven, The Netherlands

(74) 代理人 100072051

弁理士 杉村 興作

(74) 代理人 100100125

弁理士 高見 和明

最終頁に続く

(54) 【発明の名称】 プラズマディスプレイパネル電極及び発光体構造

## (57) 【要約】

本発明は、表面放電型のAC プラズマディスプレイパネル(12)に関し、より特には、前記パネルのアドレス電極(5)及び発光体の構造と、このようなパネルを用いるプラズマディスプレイパネル装置とに関する。本発明によれば、1つのアドレス電極(5)のみが、2つの列ごとに1つの列に使用される。走査電極(8)及び共通電極(7)は、透明部分(11)を具えててもよい。これらの部分(11)は、チャッカーボード式に、2つのセルごとに1つのセルを覆って延在してもよい。好適実施例において、行は、交互に広い(15)セル(2)及び狭い(16)セル(2)を有してもよい。さらに、各々のセルは、同じアドレス電極において、しかし、近傍にある行及び近傍にある列において、同じ色の近傍セルを有する。前記ディスプレイパネル装置は、サブフィールドの1つにおいて、近傍にあるセルが同時にアドレスされるように配置された駆動回路(22)を有する。

**【特許請求の範囲】****【請求項 1】**

その上に形成された、第1方向において延在する一組の共通電極と、前記共通電極と交互に、同じ方向において延在する一組の走査電極とを有し、共通電極と走査電極との間の空間が行を規定する、第1基板と、その上に形成された双方とも前記第1方向と実質的に垂直に延在する一組のアドレス電極と一組のバリアリップとを有し、1対の隣接するバリアリップによって境界を定められた空間が列を規定する、前記第1基板と平行な第2基板とを具え、行及び列の交点における空間がセルを規定する、プラズマディスプレイパネルにおいて、あるアドレス電極は、2つ以上の列に渡って延在し、ある行における第2の列におけるセルの少なくとも一部と、すぐ下の行における他の列におけるセルの一部とを覆い、他のアドレス電極は、第1セルのすぐ下のセル上にも、第2セルのすぐ上のセル上にも延在せず、各々のセルは、同じアドレス電極におけるが、近傍にある列及び近傍にある行において、同じ色の近傍セルを有することを特徴とするプラズマディスプレイパネル。10

**【請求項 2】**

請求項1に記載のプラズマディスプレイパネルにおいて、前記角度は実質的に90度であり、前記近傍列は隣接列であり、前記近傍行は隣接行であることを特徴とするプラズマディスプレイパネル。

**【請求項 3】**

請求項2に記載のプラズマディスプレイパネルにおいて、前記共通電極及び走査電極は、導電性部分と、一組の透明部分とを具え、各々の透明部分は、対応する導電性部分の一方の側において延在し、ある共通電極の透明部分と、隣接する走査電極の透明部分とは、チェックカーボード式に、2つのセルごとに1つのセルを覆って互いの方に向かって延在し、これら2つの透明部部の間にギャップが残り、前記2つのセルごとに1つのセルはアドレス電極によって覆われることを特徴とするプラズマディスプレイパネル。20

**【請求項 4】**

請求項3に記載のプラズマディスプレイパネルにおいて、前記透明部分の少なくともいくつかは金属グリッドで形成されたことを特徴とするプラズマディスプレイパネル。

**【請求項 5】**

請求項3に記載のプラズマディスプレイパネルにおいて、前記アドレス電極は、2つの隣接行を分離するバリアリップの下に形成されたストレートストリップであることを特徴とするプラズマディスプレイパネル。30

**【請求項 6】**

請求項1に記載のプラズマディスプレイパネルにおいて、前記アドレス電極は、ジグザグ形状において形成されたことを特徴とするプラズマディスプレイパネル。

**【請求項 7】**

請求項3に記載のプラズマディスプレイパネルにおいて、前記透明部分は、前記導電性部分の他の側を覆って延在することを特徴とするプラズマディスプレイパネル。

**【請求項 8】**

請求項3に記載のプラズマディスプレイパネルにおいて、前記透明部分は、セルの幅の一部のみを覆って延在することを特徴とするプラズマディスプレイパネル。40

**【請求項 9】**

請求項8に記載のプラズマディスプレイパネルにおいて、前記透明部分は、前記ギャップの近くでより太い部分を有することを特徴とするプラズマディスプレイパネル。

**【請求項 10】**

請求項8に記載のプラズマディスプレイパネルにおいて、前記2つの透明部分は並んで延在し、これら2つの透明部分間のギャップは前記セルを覆って前記第1方向に垂直に延在することを特徴とするプラズマディスプレイパネル。

**【請求項 11】**

請求項3に記載のプラズマディスプレイパネルにおいて、前記アドレス電極は、実質的に前記ギャップを覆って延在する延長部を具えることを特徴とするプラズマディスプレイ50

パネル。

【請求項 1 2】

請求項 1 に記載のプラズマディスプレイパネルにおいて、前記バリアリブは、列の幅は第 1 幅と第 2 幅との間で変化し、第 1 列は偶数行上でより大きい幅を有し、奇数行上でより小さい幅を有し、前記第 1 列に隣接する列は、前記奇数行上で延在する前記第 1 幅及び第 2 幅のうちより大きい方を有し、前記偶数行上で延在する前記第 1 幅及び第 2 幅のうちより小さい方を有するように、ジグザグ構造を有することを特徴とするプラズマディスプレイパネル。

【請求項 1 3】

請求項 3 に記載のプラズマディスプレイパネルにおいて、前記透明部分は、対応する導電性部分の長さに沿って延在するストリップであることを特長とするプラズマディスプレイパネル。

【請求項 1 4】

請求項 1 に記載のプラズマディスプレイパネルにおいて、1 列におけるセルは同じ色のものであることを特徴とするプラズマディスプレイパネル。

【請求項 1 5】

請求項 1 に記載のプラズマディスプレイパネルにおいて、アドレス電極が上に延在するセルは、同じ色のものであることを特徴とするプラズマディスプレイパネル。

【請求項 1 6】

請求項 1 に記載のプラズマディスプレイパネルを具えるプラズマディスプレイパネル装置において、サブフィールドにおいて前記セルをアドレスする駆動回路を具え、前記駆動回路は、前記サブフィールドの少なくとも 1 つにおいて、前記近傍にあるセルが同時にアドレスされるように構成されたことを特徴とするプラズマディスプレイパネル装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、その上に形成された、第 1 方向において延在する一組の共通電極と、前記共通電極と交互に、同じ方向において延在する一組の走査電極とを有し、共通電極と走査電極との間の空間が行を規定する、第 1 基板と、その上に形成された双方とも前記第 1 方向と実質的に垂直に延在する一組のアドレス電極と一組のバリアリブとを有し、1 対の隣接するバリアリブによって境界を定められた空間が列を規定する、前記第 1 基板と平行な第 2 基板とを具え、行及び列の交点における空間がセルを規定する、プラズマディスプレイパネルと、より特には、その電極構造及び発光体構造とに関する。

【0002】

本発明は、表面放電型の A C プラズマディスプレイパネルに関する。

【0003】

本発明は、プラズマディスプレイパネル及び駆動回路を具えるプラズマパネルディスプレイ装置にも関する。

【背景技術】

【0004】

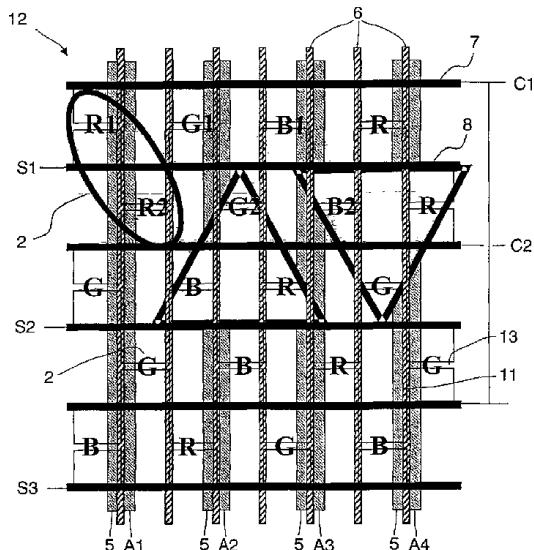

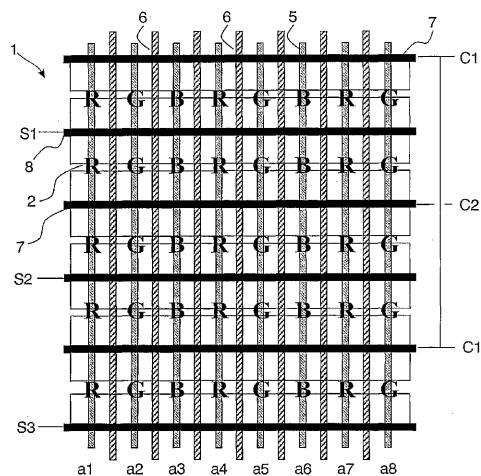

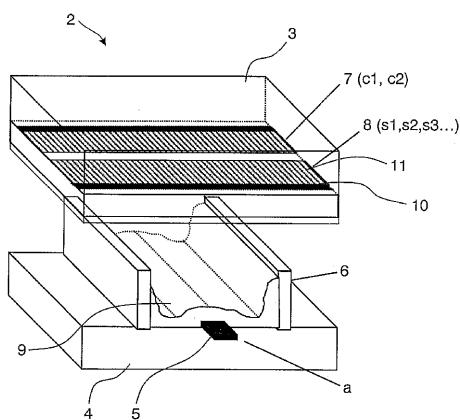

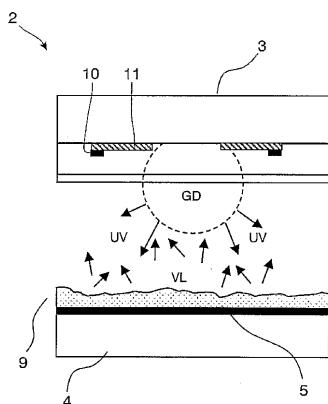

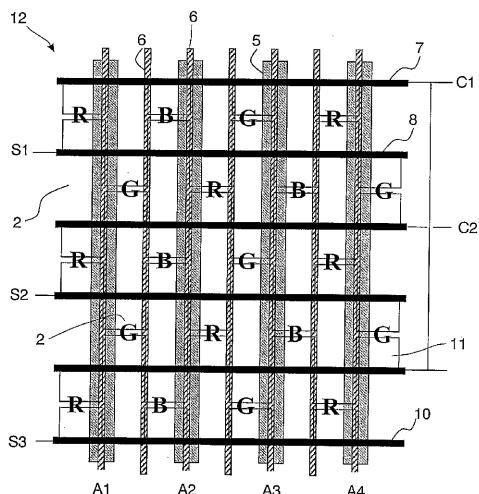

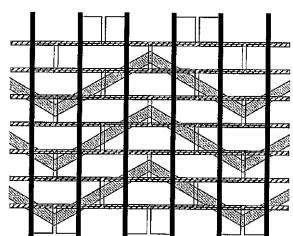

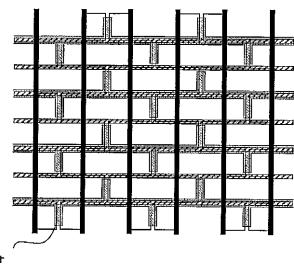

プラズマディスプレイパネル及びこのようないわゆるパネルを駆動する方法は、当該技術分野において既知である。プラズマディスプレイパネルは、行及び列の交点によって規定される個々のセルを具えるマトリクス装置である。欧州特許出願公開明細書第 0762373 号から既知のパネル 1 の構造は、図 1 において前面図において図式的に示される。図 2 a 及び 2 b は、単独のセル 2 の各々詳細な斜視図及び側面図である。このパネルは、透明材料から成る前面プレート 3 と、背面プレート 4 とを具える。平行アドレス電極 5 の第 1 の組  $a_1, a_2, a_3, \dots, a_n, a_{n+1}, \dots$  は、前記背面プレートにおいて第 1 方向と垂直方向に配置される。背面プレート 4 において、アドレス電極 5 と平行に配置されたバリアリブ 6 は、近傍にある列からセル 2 を分離する機能を行う。電極の第 2 の組は、共通電極 7 及び走査電極 8 を具える。これらの電極は、前面プレート 3 において、背面ブ

10

20

30

40

50

レート 4 におけるアドレス電極 5 と向かい合って配置される。共通電極 7 は、この例において、2つのグループ、すなわち、c 1 及び c 2 に分割される。走査電極 8 s 1, s 2, s 3 . . . は、別々にアドレス可能である。前記電極の第 2 の組は、第 1 の、この図においては水平方向において向けられ、この方向は、実質的にアドレス電極 5 に垂直である。背面プレート 4 上に置かれた発光体 9 は、共通電極 7 と走査電極 8 との間のガス放電 G D によって生じた紫外線 U V を可視光 V L に変換する機能を行う。所望の色、例えば、赤、緑、青の光は、異なった形式の発光体 9 を選択することによって発生される。

#### 【 0 0 0 5 】

当該技術分野において既知の共通電極及び走査電極は、金属部分 1 0 及び透明部分 1 1 10 から形成されることができる。金属部分 1 0 は、電極を流れる電流の導通を保証する。導電透明部 1 1 を経て、電極に印加された電圧は、セル 2 の所望の領域の両端間に存在する。透明部分 1 1 は、金属酸化物 ( I T O ) の薄い層から形成されてもよい。

#### 【 0 0 0 6 】

このようなプラズマディスプレイパネルにおける連続するピクチャフレームの表示において、1つのフレームは、奇数フィールドと、それに続く偶数フィールドとに分割される。奇数行、すなわち、図 1 における電極 c 1 と s 1, c 2 と s 2, c 1 と s 3 との間の行は、奇数フィールドの間に光を発生し、偶数行、s 1 と c 2, s 2 と c 1 の間の行は、偶数フィールドの間に光を発生する。

#### 【 0 0 0 7 】

既知のプラズマディスプレイパネルにおいて、各々の列は、1つのアドレス電極を必要とする。640 行を具える V G A ディスプレイは、1920 のアドレス電極 ( 各々の色に 20 関して 1 つ ) を必要とする。

#### 【 発明の開示 】

#### 【 発明が解決しようとする課題 】

#### 【 0 0 0 8 】

本発明の目的は、減少した数の電極を有し、したがって、コストを減少し、それにもかかわらず良好なピーク輝度を可能にするプラズマディスプレイパネルを提供することである。

#### 【 0 0 0 9 】

本発明の他の目的は、減少した数の電極を有し、良好なピーク輝度を可能にするプラズマディスプレイパネルを有するプラズマディスプレイパネル装置を提供することである。

#### 【 課題を解決するための手段 】

#### 【 0 0 1 0 】

本発明は、請求項 1 において規定されるプラズマディスプレイパネルを提供する。あるアドレス電極は、2つ以上の列に渡って延在し、ある行における第 2 の列におけるセルの少なくとも一部と、すぐ下の行における他の列におけるセルの一部とを覆い、他のアドレス電極は、第 1 セルのすぐ下のセル上にも、第 2 セルのすぐ上のセル上にも延在しない。アドレス電極の数は、したがって、既知の形式のプラズマディスプレイパネルに対して半分に減少される。列ドライバの数も、二分の一に減少され、したがって、合計のコスト減少は、多大である。本プラズマディスプレイパネルは、チエッカーボードに見え、2セルごとに 1 セルはアドレス可能である。本発明によるプラズマディスプレイパネルに加えて、各々のセルは、同じアドレス電極において、しかし、近傍にある列及び近傍にある行における同じ色の近傍セルをする。近傍という言葉は、列又は行が別の列又は行の隣にある必要はなく、いくつかの他の列又は行が間に配置されてもよいことを示すのに使用される。隣接という言葉は、2つの隣接する列又は2つの隣接する行の間に他の列又は行がないことを示すのに使用される。

#### 【 0 0 1 1 】

これは、プラズマ表示パネルを、サブフィールドにおいてセルをアドレスする駆動回路との組み合わせにおいて使用することを可能にし、この回路は、サブフィールドの少なくとも 1 つにおいて、前記近傍にあるセルが同時にアドレスされるように配置される。（異

10

20

30

40

50

なった列及び異なった行における) 2つのセルは、ここで同時にアドレスされることができ、これは、アドレス時間を減少し、したがって、持続時間を増加する。

#### 【0012】

本発明によるプラズマディスプレイパネル装置は、請求項1において規定されたプラズマディスプレイパネルを具え、前記サブフィールドの1つにおいて、前記近傍にあるセルが同時にアドレスされるように配置された駆動回路を有する。

#### 【0013】

上述されたようなマトリクスディスプレイパネル形式に関して、光の発生は、CRTディスプレイに関する場合であるように、グレイスケールの異なったレベルを形成するように強度において変調されることができない。前記マトリクスディスプレイパネル形式において、グレイレベルは、時間において変調することによって形成され、より高い強度に関して、発光期間の持続時間は増加される。輝度データは、一組のサブフィールドにおいて符号化され、各々のサブフィールドは、ゼロレベルと最大レベルとの間の光強度の範囲を表示する適切な持続時間又は重みを有する。サブフィールドの異なった組み合わせは、異なったグレイレベルを結果として生じる。グレイスケールに関してここに記載されたこのようなサブフィールド分解は、以後、カラーディスプレイの個々の色に対しても適合する。

#### 【0014】

1フレームを表示するのに必要な時間を減少するために、多行アドレッシング方法が用いられてもよい。この方法において、2つ以上、通常2つの近傍にあって好適には隣接する行は、同時にアドレスされ、これによって、同じデータを受け、表示する。

#### 【0015】

このいわゆるダブルラインアドレッシング方法(2つのラインが同時にアドレスされる場合)は、各々のフレームはより少ないアドレッシング動作を必要とするため、発光のためのより多くの時間及び/又は1フレームのアドレスの高速化を可能にする。

#### 【0016】

解像度の損失を減少するために、まだ時間を得ている間、ライン二重化は、同じサブフィールドのみに関して行われることができる。結果として生じる部分的ライン二重化(PLD)は、解像度における少ない損失を与える。

#### 【0017】

本発明の枠組み内で、ライン二重化及びPLDは可能であるが、好適には、PLDが行われ、すなわち、多数の最下位ビットに関して好適である。

#### 【0018】

好適実施例において、共通電極及び走査電極は、導電性好適には金属の部分と、一組の透明部分とを具える。これらの透明部分は、前記パネルの2セルごとに1セルにおいて放電を可能にするように、すなわち、チェックカード式に形成される。

#### 【0019】

前記透明部分は、金属酸化物(ITO)の薄膜の領域で形成されてもよい。他の好適実施例において、共通電極及び走査電極は、薄い金属グリッドの領域で形成された透明部分を有する。これは、電極の前記導電性好適には金属の部分と前記透明部分との製造が、単一のプロセスステップにおいて行われることができるという利点を有する。

#### 【0020】

2つのバリアリブごとに1つのバリアリブの下にストレートストリップとして形成されたアドレス電極は、製造するのが特に容易で、ロバストでもある。チェックカード式における前記透明部のレイアウトは、所望のセルのみが光を発生することを保証する。

#### 【0021】

ジグザグアドレス電極は、各々の連続する行における隣接する列におけるセルに達することができ、依然として狭いままである。狭い電極は、減少したキャパシタンスの利点を有し、したがって、あまり電力を必要としない。ジグザグ電極の周期は、2つ又はそれ以上の行を含んでもよい。アドレス電極は、さらに、前記パネルの高さ全体を横切る対角線

において形成されてもよい。ジグザグ電極は、これらは、放電が望まれるセルのみを覆い、これによって、偽放電の危険性を減少するという追加の利点を有する。

【0022】

共通電極及び走査電極の透明部分は、同じ列におけるすぐ上又は下のセルをわずかに覆って延在してもよい。これによって、放電空間は、垂直方向においてさらに拡大される。これは、前記パネルの表面の光を発生する部分を増加し、これによって、輝度が上昇する。

【0023】

前記透明部分は、セルの幅の一部のみを覆って延在してもよい。これによって、電極のキャパシティは減少され、したがって、前記パネルを駆動するのに必要な電流は減少される。前記透明部分は、ギャップの近くでより広い部分を有してもよい。これは、前記透明部分の対の間に生じる放電の品質を改善する。

10

【0024】

2つの透明部部は、並んで延在してもよく。これら2つの透明部分間のギャップは前記セルを覆って垂直に延在する。これら2つの透明部分間の表面ガス放電は、増加されたギャップ長に渡って生じ、したがって改善される。

【0025】

前記アドレス電極は、ギャップを実質的に覆って延在する延長部を具えてもよい。この延長部は、所望のセルへのアドレス電極の適用範囲を増加する。これらの延長部は、ストレートアドレス電極並びにジグザグアドレス電極に用いられてもよい。

20

【0026】

好適実施例において、前記バリアリップは、拡大された、光を発生するのに使用されるセル、すなわち、アクティブセルと、幅が減少された、残りの光を発生しないセル、すなわち、インアクティブセルとを形成する形状を有する。光を発生する領域の光を発生しない領域に対する比は、したがって増加され、前記パネルの輝度は大きく改善される。この実施例におけるアドレス電極は、ストレートタイプのものであってもよく、又は、ジグザグタイプのものであってもよい。前記幅が減少されたセルは、ゼロ領域又はゼロ領域の近くまで減少されてもよい。

【0027】

前記共通電極及びアドレス電極の透明部分は、連続的なストリップとして形成されてもよい。これによって、前記パネルの製造コストは減少される。前記前面プレートの前記背面プレートに対する水平方向における正確な整列は必要ない。

30

【0028】

前記第1方向に対して90度以外の角度における列を有することによって、セルのパターンを得てもよく、このパターンにおいて、ある列におけるすべてのセルは同じ色のものである。これは、2つのバリアリップ間の列において、1つの色のみの発光体を適用すればよいため、これは製造するのがより容易である。

【0029】

前記アドレス電極は、ジグザグ形状を有してもよく、これによって、同じ色のセルを覆うその後の行において延長する。このような配置は、同じ電極に接続された、近傍にある行における2つのセルが同じ色のものであるようなPLDスキームを可能にする。

40

【0030】

本発明のこれら及び他の態様は、以下に記載された実施例への参照によって明らかになる。図面は、一定の比例で描かれていらない。一般的に言って、図面において、同一の構成要素は同じ参照数字によって示される。

【発明を実施するための最良の形態】

【0031】

図1及び2A、2Bは、すでに説明されている。

【0032】

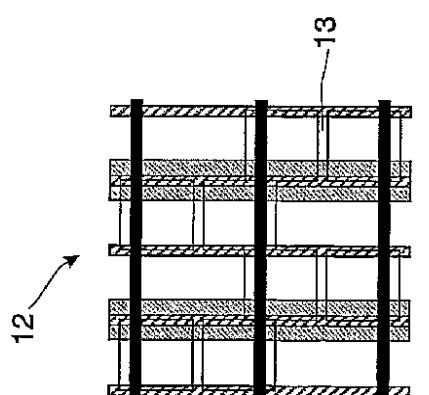

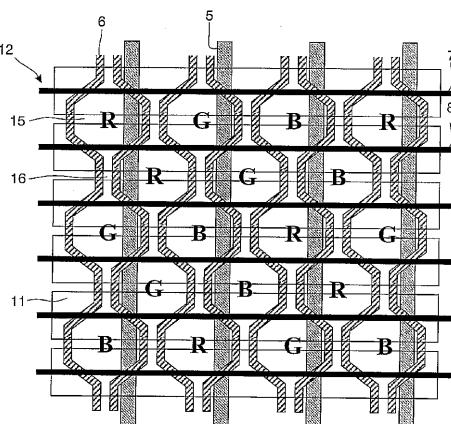

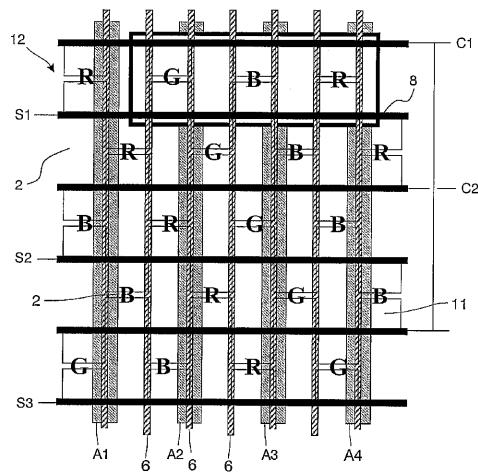

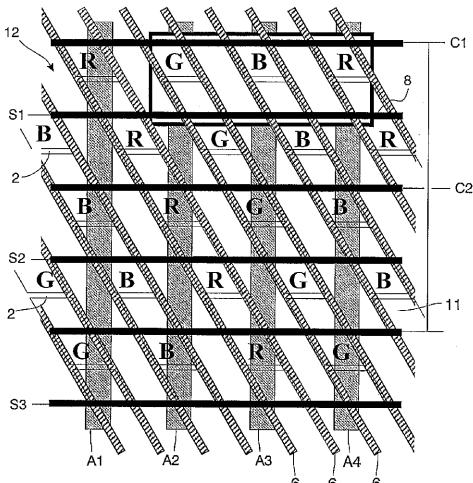

標準的な発光体パターンを有するプラズマディスプレイパネル12は、図3Aにおいて

50

示され、本発明によるプラズマディスプレイパネル 12 は、図 3B において示される。共通電極 7 C1、C2 と、これらと交互にある走査電極 8 S1、S2、S3 は、水平方向において延在する。アドレス電極 5 A1、A2、A3、A4 は、2 列ごとに 1 列に関する背面パネルにおけるストリップとして形成される。バリアリブ 6 は、前記背面パネルにおいて形成され、2 つのバリアリブ 6 ごとに 1 つのバリアリブ 6 は、アドレス電極 5 の上に形成される。アドレス電極 5 及びバリアリブ 6 の幅は、アドレス電極 5 A1...A4 がバリアリブ 6 の両側において現れるようにする。共通電極 7 及び走査電極 8 は、チエッカーボード式に、2 つのセル 2 ごとに 1 つのセル 1 を覆って延在する透明部分 11 を具える。したがって、アドレッシング段階中にアドレス電極 5 に印加される電圧は、走査されている行の 2 つの近傍にあるセルに印加される。走査されている共通電極 7 及び走査電極 8 の透明部分は、書き込み放電が透明部分 11 によって覆われているセルにおいてのみ生じ、近傍にあるセルにおいては生じないことを保証する。図 3 のアドレス電極 5 A1 は、アドレス電極 5 a1 及び a2 の融合とみなすことができ、アドレス電極 5 A2 は、a3 及び a4 の融合とみなすことができ、等である。電極 A1 に印加される電圧は、奇数行の走査中に a1 に印加される電圧と、偶数行の走査中に a2 に印加される電圧である。

### 【0033】

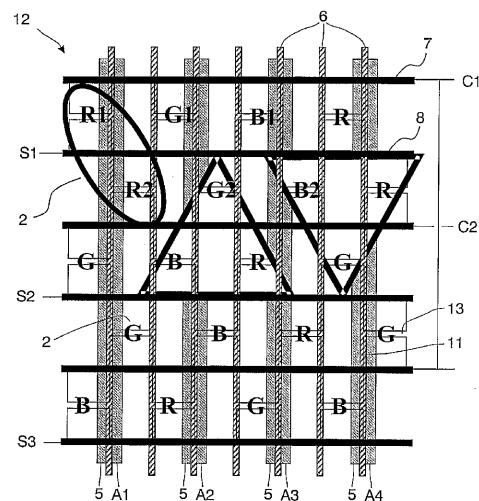

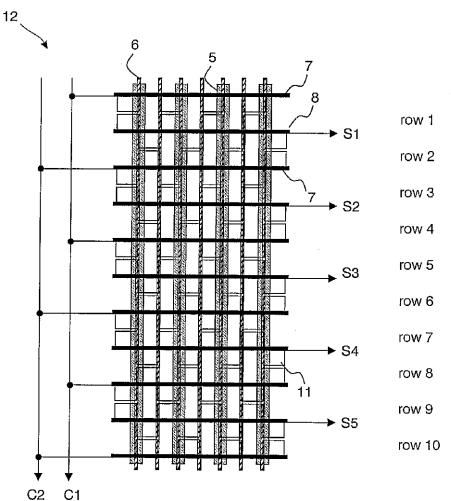

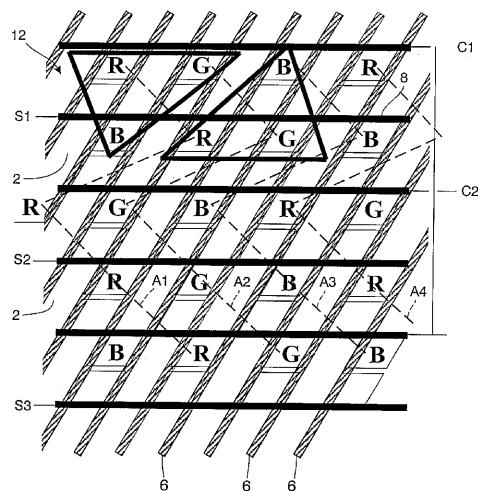

図 4 は、奇数列電極 7 C1 が単独のドライバに接続され、偶数列電極 7 C2 が他の単独のドライバに接続される方法を示す。各々の走査電極 8 S1、S2、S3、S4、S5 は、単独のドライバに接続される。プラズマディスプレイパネル (PDL) に関するこの新奇なレイアウトは、必要なアドレス電極の数を二分の一に減少する。列ドライバの数も二分の一に減少され、したがって全体のコスト減少は大きくなる。これは、図 3A 及び 3B の双方に適用される。しかしながら、図 3A において示されるような標準発光体パターンを部分的ライン二重化 (PLD) と組み合わせた場合、画質は最適にはならない。異なった色、例えば、各々文字 R、G 及び B によって示されるような赤、緑及び青を有するセルのパターンは、2 つの隣接する行の間でかなりシフトされるため、部分的ライン二重化は、結果として、2 つの隣接する行に用いられる場合、画質の低下を生じる。この場合において、PLD を、例えば、2 つの連続する偶数行又は 2 つの連続する奇数行に用いることがより適切であろう。しかしながら、2 つのこののような行の間の距離がより大きくなると、PLD を用いる場合、画質のいくらかの低下がある。PLD が用いられない場合、結果として生じる比較的長いアドレス時間は、光出力に利用可能な時間が短くなることを意味し、したがって、より低いピーク輝度を招く。標準発光体パターンレイアウトが使用される場合、隣接する行における近傍にあるセルが異なった色を有するのに反して、本発明によるプラズマディスプレイパネルにおいて、図 3B において示されるように、各々のセルは、同じアドレス電極において、しかし隣接する列及び隣接する行において、同じ色を有する近傍セルを有する。標準発光体パターンを使用すると、各々のセルは、異なった色の近傍セルを有し、すなわち、アドレス電極に沿って、一続きのセルは、R - G - R - G - R、B - R - B - R 及び G - B - G - B - G である。本発明によるプラズマディスプレイパネルにおいて、アドレス電極に沿った発光体素子は、R - R - G - G - R - R 等のように配置される。したがって、各々のセルは、隣接列及び隣接行 (行はラインとも呼ばれる) において同じアドレスにおいて同じ色の近傍セルを有する。これは、PLD 又はビットライン反復 (BLR) を用いることによりセルをアドレスするのに必要な時間の減少を可能にする。PLD が用いられてもよいセルの対の例として、いくつかの対 R1、R2；G1、G2；及び B1、B2 が示され、橢円が対 R1、R2 の周りに描かれている。

### 【0034】

図 5 は、フレーム時間中の異なった周期を図式的に示す。プラズマディスプレイパネルは、三原色、すなわち、赤、緑及び青におけるセルから成る。これらのセルは、オン又はオフのいずれかになる。多グレイレベルを表示するために、パルス幅変調の原理が使用される。全体のフレーム時間は、多数のいわゆるサブフィールドに分割される。これらのサ

ブフィールドは、異なった持続時間のものである。各々のサブフィールドにおいて、セルはオン又はオフのいずれかになる。異なったグレイレベルは、サブフィールドの適切な組み合わせを選択し、発光することによって形成することができる。スクリーン全体におけるすべてのセルは、同じ方法において作用し、サブフィールドごとに、各々のセルに関して、発光すべきか否かが決定される。これらのセルは、ここで、一度に1ラインを基本にアドレスされ、垂直アドレス電極において、情報は第1ラインに関して設定される。次に、パルスが水平電極に印加され、第1ラインを実際にアドレスする。その後、前記アドレスラインにおける情報は変化され、第2ライン等を描写する。この原理のため、パネル全体のアドレッシングは、かなりの時間をとる。

## 【0035】

図5は、单一のフレーム時間のすべての部分を示し、黒い長方形は消去周期に関して有効であり、グレイの三角形はアドレス周期に関して有効であり、白い長方形は保持周期に関して有効である。アドレッシングは、かなりの時間、すなわち、通常、合計フレーム時間の約60-70%をとる。光は、保持段階においてのみ放射される。減少したアドレス時間は、保持に、すなわち、発光に利用可能なより多くの時間を残すことができる。本発明は、各々のセルが近傍行における同じアドレス電極において同じ色の近傍セルを有するため、このようなアドレス時間の減少を可能にする。

## 【0036】

図6Aないし6Gは、本発明によるプラズマディスプレイパネルにおける電極の透明部分11の異なった実現化を示す。図6Aの実現化において、透明部分11は、すぐ上又は下のセルを部分的に覆って延在する。したがって、光発生領域は拡大され、輝度は改善される。

## 【0037】

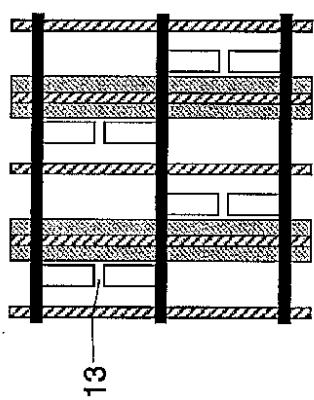

図6Bないし6Eは、アドレス電極5がセルの幅の一部のみを覆って延在する実施例を示す。図6Cにおいて、狭いアドレス電極5は、ギャップ13の近くでより広い部分を有する。図6Dないし6Gにおいて示されたすべての実施例は、ギャップ13の長さの増加を可能にする。走査電極8と共に共通電極7との間の表面ガス放電は、これによって改善される。

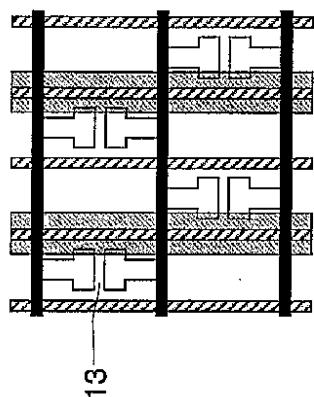

## 【0038】

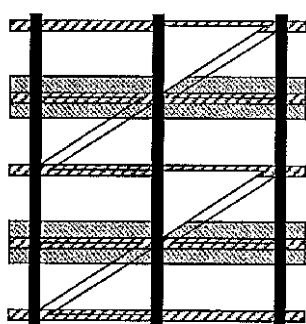

図7A及び7Bは、アドレス電極5がジグザグ形状を有する実施例を示す。図7Aにおいて、ジグザグの垂直周期性は2行であるが、図7Bにおいては4行である。前記パネルの2つのセルごとに1つのセルがチェックカーボード式にアドレス電極5によって横切られるならば、アドレス電極5が前記パネルの上部から下部まで斜めに延在する直線である場合を含む他の実現化も可能である。

## 【0039】

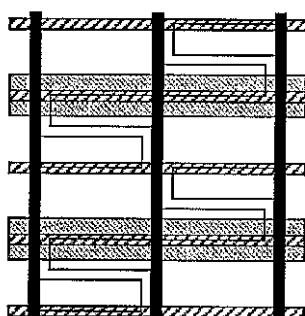

図7Cにおいて、アドレス電極5は、延長部14を具える。これらの延長部14は、透明部分11と、好適には2つの透明部分11の間のギャップ13領域とによって2セルごとに1セルを部分的に覆う。アドレス電極5の主な部分は、より狭くなてもよく、バリアリブ6によって完全に覆われてもよい。

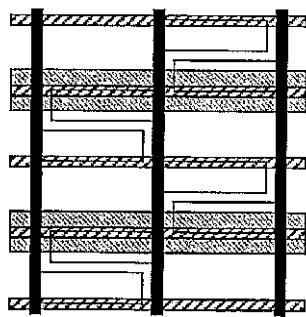

## 【0040】

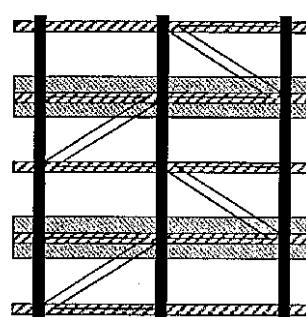

図8は、本発明の好適実施例を示す。バリアリブ6は、列が、第1幅と第2幅との間で変化する幅を有するような形状において形成される。奇数列は、奇数行を覆うより大きい幅15と、偶数行を覆うより小さい幅16とを有し、偶数列は、偶数行を覆うより大きい幅と、奇数行を覆うより小さい幅とを有する。したがって、パネル12は、蜂の巣の全体的構造を有する。アドレス電極5は、この好例の実施例において、直線垂直ストリップである。前記より大きい列幅、より小さい列幅、及びアドレス電極5の幅は、光発生が望まれるセルのみがアドレス電極5によって部分的に覆われるようである。より狭いセルは、アドレス電極5によって覆われない。透明部分11は、光の発生が望まれないセルも覆って延在してもよく、前記走査電極及び共通電極の長さに沿って単純な直線ストリップとして形成されてもよい。この実施例は、きわめてより高い輝度の利点を有する。前記

10

20

30

40

50

共通電極及び走査電極は、垂直ラインによってリンクされた一組の水平の細いラインによって形成されてもよく、これによって金属の薄いグリッドのストリップを形成する。

【0041】

本発明をRGBディスプレイに適用する場合、画素、すなわち、赤いセル、緑のセル及び青いセルの組み合わせは、示した例において三角形の形状を有する。図3A及び3Bにおいて見られるように、1対の行を考える場合、その頂点が下を向く第1RGB三角形と、それに続く、その頂点が上を向く隣接する三角形とを見る。これは、いわゆるデルタ-ナブラ構造を与える。図3Bは、2つのこのような三角形を明示して示す。

【0042】

本発明は、好適実施例を参照して説明されたが、上記で概説された原理の範囲内でのこれらの変更は当業者に明らかであることは理解され、したがって、本発明は、好適実施例に限定されず、これらの変更を包含するように意図される。水平及び垂直方向は交換されてもよい。本発明は3色（赤、緑、青）を使用するカラーディスプレイを参照して説明されたが、本発明は、他の色の組み合わせを使用するディスプレイに適用されてもよい。本発明は、各々の新たな特徴及び特徴の各々の組み合わせにおいて具体化される。どの参照符号も、請求項の範囲を限定しない。“見える”という言葉は、請求項において列挙されたもの以外の他の要素の存在を除外しない。要素に先立つ“1つの”という言葉は、複数のこのような要素の存在を除外しない。特定の手段が相互に異なる従属請求項において列挙される單なる事実は、これらの手段の組み合わせがよい利点に使用されることができないことを示さない。

10

20

30

40

【0043】

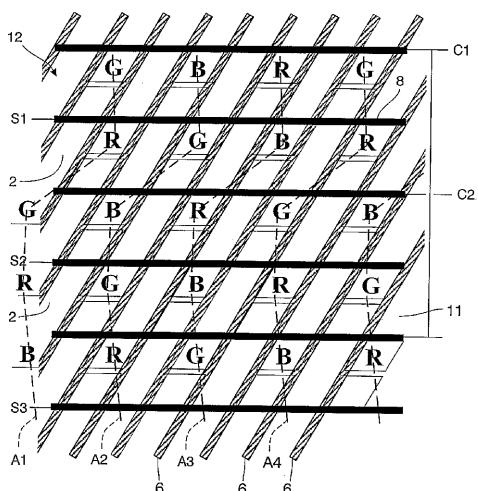

明瞭にするために、図面は、限られた数の行及び列を示す。しかしながら、本発明は、より多くの数の行及び列を有するプラズマディスプレイパネルに適合する。「列方向」は、ここでは、明瞭するために、「垂直方向」として記載され、「行又はライン方向」は、「水平方向」として記載される。前の図面において示された例は、デルタ-ナブラ構造を有するが、本発明は、このような構造のみに限定されない。図9は、発光体素子が、ある色の発光体素子が平行の対角線において配置された実施例を示し、この例において、画素は長方形を形成し、その1つは図9において図式的に示される。

【0044】

図9におけるバリアリブ6は、前記第1方向に対して実質的に90度の角度の下に配置される。バリアリブ6は、図10において示されるように、前記第1方向に対して90度と異なる角度の下で配置されてもよい。図9において示される実施例と比べた利点は、2つのバリアリブ6の間の列において、1つの色の発光体のみが存在することであり、これは製造するのがより容易である。異なった色は、文字R、G、Bで示される。

【0045】

図11は、ある角度の下で配置されたバリアリブ6を有する本発明の他の実施例を示す。再び、2つのバリアリブ6の間に、1つの色の発光体のみが存在する。しかしながら、図10と比べて、アドレス電極A1...A4は、ジグザグ形状を経て、共通電極C1、C2に実質的に垂直な方向において延在する。この実施例は、再び、図11において2つの三角形によって示されるようなデルタ-ナブラ構造を与える。

【0046】

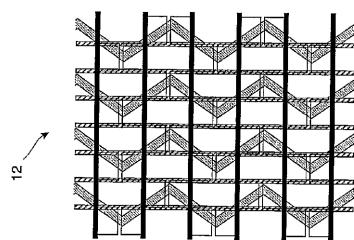

ある角度の下で配置されたバリアリブ6を有する依然として他の実施例は、図12において示される。アドレス電極A1...A4の各々は、2つの連続する奇数行における同じ色の2つのセルと、2つの連続する奇数行における同じ色（この色は前記奇数行における2つのセルの色と異なってもよい）の2つのセルとを覆って延在する。このアドレス電極構造は、製造するのが容易である。PLDは、連続する偶数行の対又は連続する奇数行の対を同時にアドレスすることによって、適用されることができる。

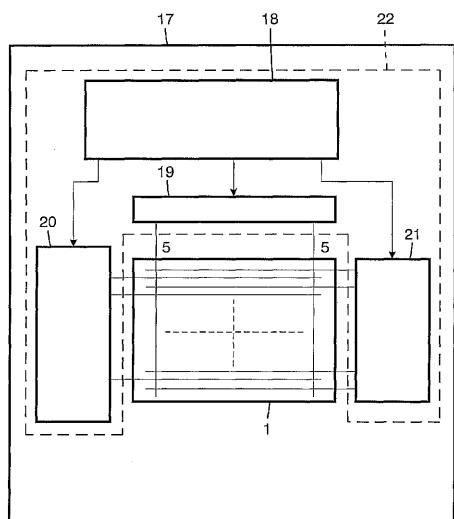

【0047】

最後に、図13は、本発明によるプラズマパネルディスプレイ装置を図式的に例示する。プラズマパネルディスプレイ装置17は、プラズマディスプレイパネル1と、この例に

50

おいて、アドレスドライバ(19)、yドライバ(20)、Xドライバ(21)、及び、これらのドライバに結合された制御回路(18)を具える駆動回路(22)とを具える。駆動回路22は、部分的ライン二重化(PLD)又はライン二重化又はビットライン反復(BLR)が行われる、すなわち、サブフィールドの少なくとも1つにおいて又は関して、近傍にあるセル(R1、R2；G1、G2；B1、B2)が同時にアドレスされるよう配置される。

【0048】

‘プラズマディスプレイパネル装置’は、本発明の枠組み内で、プラズマディスプレイパネルと、このディスプレイパネルから分離された駆動回路とを有するTVセットであるが、駆動回路が取り付けられた又は物理的に結合された又は集積されたディスプレイパネルから成るモジュールであろうが、任意の他の形式の装置であろうが、言及された要素を有する任意の装置を含む。

【0049】

本発明は、以下のように要約されることができる。本発明は、表面放電型のACプラズマディスプレイパネル(12)に関し、より特には、前記パネルのアドレス電極(5)と発光体素子の構造と、このようなパネルを具えるディスプレイパネル装置とに関する。本発明によれば、1つのアドレス電極(5)のみが、2つの列ごとに1つの列に関して使用される。走査電極(8)及び共通電極(7)は、透明部分(11)を具えてもよい。これらの部分(11)は、チエッカーボード式に、2つのセルごとに1つのセルを覆って延在してもよい。図7において示されるような好適実施例において、列は、交互に広い(15)セル(2)及び狭い(16)セル(2)を有してもよい。さらに、各々のセルは、同じアドレス電極において、しかし、隣接列及び隣接行において、同じ色の近傍セルを有する。前記ディスプレイパネル装置は、サブフィールドの少なくともいくつかにおいて、前記近傍セルが同時にアドレスされるように配置されたセルをアドレスする駆動回路(22)を具える。

【図面の簡単な説明】

【0050】

【図1】先行技術において既知のプラズマディスプレイパネルの前面図である。

【図2】A及びBは、先行技術において既知のプラズマディスプレイパネルの単一のセルの各々斜視図及び側面図である。

【図3】Aは、標準発光体パターンを有するプラズマディスプレイパネルの前面図であり、Bは、本発明によるプラズマディスプレイパネルの前面図である。

【図4】共通電極がグループ化される方法を示す同じプラズマディスプレイパネルの前面図である。

【図5】単一フレーム時間のアドレス周期、消去周期及び保持周期を例示する。

【図6】AないしGは、走査電極及び共通電極の透明部分の異なった実施例を示す本発明によるプラズマディスプレイパネルの前面図である。

【図7】A及びBは、アドレス電極がジグザグタイプのものである本発明によるプラズマディスプレイパネルの前面図であり、Cは、アドレス電極が延長部を有する本発明によるプラズマディスプレイパネルの前面図である。

【図8】本発明の好適実施例によるプラズマディスプレイパネルの前面図である。

【図9】本発明の他の実施例を例示する。

【図10】ある角度の下で配置されたバリアリブを有する本発明の一実施例を例示する。

【図11】ある角度の下で配置されたバリアリブを有する本発明の他の実施例を例示する。

【図12】ある角度の下で配置されたバリアリブを有する本発明の依然として他の実施例を例示する。

【図13】本発明によるプラズマディスプレイ装置を図式的に例示する。

【図1】

FIG.1

【図2A】

FIG.2A

【図2B】

FIG.2B

【図3A】

FIG.3A

【図3B】

FIG.3B

【図4】

FIG.4

【図5】

FIG.5

【図6a】

FIG.6a

【図 6 b】

FIG. 6b

【図 6 c】

FIG. 6c

【図 6 d】

FIG. 6d

【図 6 f】

FIG. 6f

【図 6 e】

FIG. 6e

【図 6 g】

FIG. 6g

【図 7 a】

FIG. 7a

【図 7 b】

FIG. 7b

【 図 7 c 】

FIG. 7C

【 図 8 】

FIG. 8

【図9】

FIG.9

【 図 1 0 】

FIG.10

【図11】

FIG.11

【図12】

FIG.12

【図13】

FIG.13

## フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100101096

弁理士 德永 博

(74)代理人 100086645

弁理士 岩佐 義幸

(74)代理人 100107227

弁理士 藤谷 史朗

(74)代理人 100114292

弁理士 来間 清志

(74)代理人 100119530

弁理士 富田 和幸

(72)発明者 パート アー サルタース

オランダ国 5 6 5 6 アーアー アンドーフェン プロフ ホルストラーン 6

(72)発明者 シエベ テー デ ズワルト

オランダ国 5 6 5 6 アーアー アンドーフェン プロフ ホルストラーン 6

F ターム(参考) 5C040 FA01 FA04 GB03 GB12 GB14 GC01 GC02 GC11