(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4508721号

(P4508721)

(45) 発行日 平成22年7月21日(2010.7.21)

(24) 登録日 平成22年5月14日(2010.5.14)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO4N 5/225 (2006.01) | HO4N 5/225 F   |

| G06F 1/18 (2006.01)  | G06F 1/00 320J |

| G06F 3/06 (2006.01)  | G06F 3/06 304N |

| G06K 17/00 (2006.01) | G06K 17/00 B   |

| HO4M 1/73 (2006.01)  | HO4M 1/73      |

請求項の数 8 (全 21 頁) 最終頁に続く

(21) 出願番号 特願2004-142322 (P2004-142322)

(22) 出願日 平成16年5月12日 (2004.5.12)

(65) 公開番号 特開2005-328153 (P2005-328153A)

(43) 公開日 平成17年11月24日 (2005.11.24)

審査請求日 平成19年4月20日 (2007.4.20)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 10012524

弁理士 別役 重尚

(72) 発明者 芝 秀規

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 遠藤 庄蔵

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 黒川 信二

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】携帯機器及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

機器全体の制御を司るCPUと、情報を記憶する記憶メディアが着脱可能な接続手段を備えた携帯機器において、

前記CPUの動作状態に関わらず、前記接続手段に対する前記記憶メディアの着脱状態を監視する監視回路と、

前記監視回路による前記記憶メディアの着脱状態の監視に基づく監視結果を記憶する監視結果記憶手段と、

前記CPUが起動処理を行う際に、前記監視結果記憶手段に記憶されている前記監視結果に前記CPUからアクセス可能とする通信手段とを備え、

前記監視回路は、前記記憶メディアが前記接続手段から取り外されたことを検知した後は前記記憶メディアの着脱状態の監視を停止することを特徴とする携帯機器。

## 【請求項 2】

前記携帯機器内部の時刻を管理する時刻管理手段を更に備え、

前記監視回路と前記監視結果記憶手段と前記時刻管理手段を1つのデバイスとして構成したことを特徴とする請求項1記載の携帯機器。

## 【請求項 3】

前記記憶メディアのファイル管理情報を記憶する管理情報記憶手段を更に備え、

前記CPUが起動処理を行う際に、前記監視結果記憶手段に記憶されている前記監視結果から、前記記憶メディアが前記接続手段から取り外されていないと判断した場合は、前

記管理情報記憶手段に記憶されているファイル管理情報を読み出して起動処理を行い、前記記憶メディアが前記接続手段から取り外されると判断した場合は、前記記憶メディアからファイル管理情報を読み出して起動処理を行うことを特徴とする請求項1または2に記載の携帯機器。

**【請求項4】**

前記監視回路は、前記記憶メディアの着脱状態を所定時間毎に監視することを特徴とする請求項1乃至3の何れか1項に記載の携帯機器。

**【請求項5】**

前記監視回路が前記記憶メディアの着脱状態を監視する時間は、前記CPUから前記通信手段を介して設定可能であることを特徴とする請求項1乃至4の何れか1項に記載の携帯機器。

10

**【請求項6】**

前記監視回路が前記記憶メディアの着脱状態を監視する時間は、前記監視結果記憶手段に記憶されている前記監視結果に基づいて決定されることを特徴とする請求項1乃至4の何れか1項に記載の携帯機器。

**【請求項7】**

前記携帯機器は、デジタルカメラを含む撮像装置であることを特徴とする請求項1乃至6の何れか1項に記載の携帯機器。

**【請求項8】**

機器全体の制御を司るCPUと、情報を記憶する記憶メディアが着脱可能な接続手段を備えた携帯機器の制御方法において、

20

前記CPUの動作状態に関わらず、前記接続手段に対する前記記憶メディアの着脱状態を監視回路により監視する監視工程と、

前記監視工程による前記記憶メディアの着脱状態の監視に基づく監視結果を監視結果記憶手段に記憶する監視結果記憶工程と、

前記CPUが起動処理を行う際に、前記監視結果記憶手段に記憶されている前記監視結果に前記CPUから通信手段によりアクセス可能とする通信工程とを備え、

前記監視工程では、前記記憶メディアが前記接続手段から取り外されたことを検知した後は前記監視回路による前記記憶メディアの着脱状態の監視を停止することを特徴とする制御方法。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、記憶メディアが着脱可能な撮像装置等の機器の起動時間を短縮し消費電力を低減する場合に適用可能な携帯機器及びその制御方法に関する。

**【背景技術】**

**【0002】**

従来、情報を記憶する記憶メディアを着脱可能に装着することができる携帯機器がある。この種の携帯機器としてデジタルカメラを例に挙げて説明する。

**【0003】**

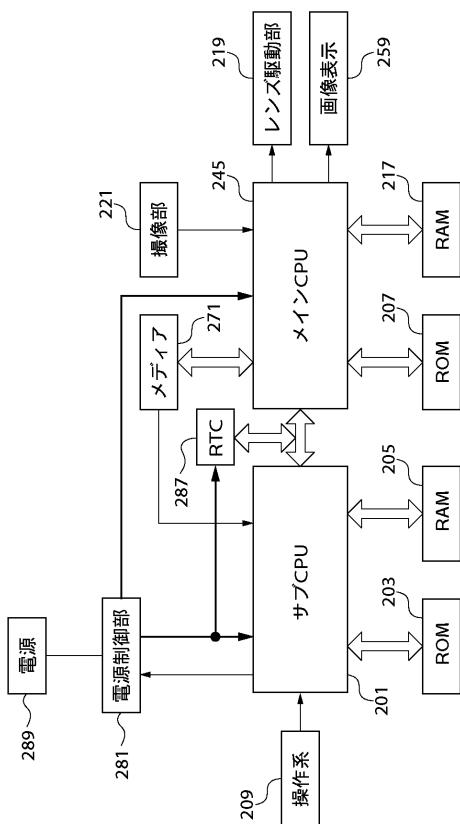

図14は、従来例に係るデジタルカメラの構成を示すブロック図である。

40

**【0004】**

図14において、RTC(Real Time Clock)287は、サブCPU201とデジタルカメラ内の時間を管理する時計管理デバイスであり、常に電源が供給されている。サブCPU201は、消費電力の少ないCPUで構成されており、サブCPU201が使用するRAM205とサブCPU201のプログラムが記憶されているROM203が接続されている。また、サブCPU201には、デジタルカメラの動作モードを指示するモードダイヤルや各種ボタン等の操作系209、撮影した画像を記憶しておくコンパクトフラッシュ(登録商標)等の記憶メディア271の着脱状態を示す信号が接続されている。サブCPU201は、常に操作系209の操作状態や記憶メディア271の着脱状態を示す信号の

50

監視を行っている。

#### 【0005】

また、サブCPU201は、デジタルカメラ全体の電源を制御するために電源制御部281に接続されており、操作系209の操作状態に基づき電源のON/OFFを判定し、電源制御部281を介して電源のON/OFFを行っている。電源制御部281は、電源289に接続されており、電源289の電圧からデジタルカメラの各部に必要な電圧をそれぞれ生成し、各部に電力を供給している。また、各部に供給している電力のON/OFFの制御はサブCPU201からの制御で行われている。

#### 【0006】

メインCPU245には、ROM207が接続されており、ROM207には、メインCPU245が動作するためのプログラムが記憶されている。メインCPU245が起動する際には、ROM207からプログラムを読み出して起動する。また、メインCPU245には、RAM217が接続されており、RAM217は、撮影した画像データを一時記憶しておいたり、メインCPU245の動作に必要なデータを一時的に記憶しておいたりするための作業用のメモリである。

#### 【0007】

また、メインCPU245には、レンズ駆動部219、撮像素子やタイミングジェネレータ等からなる撮像部221、LCD等からなる画像表示部259、記憶メディア271が接続されている。これらのレンズ駆動部219～記憶メディア271は、メインCPU245により制御され目的の処理を行うように構成されている。そして、サブCPU201とメインCPU245は、互いの状態を検知できるように通信手段によって接続されている。メインCPU245は、この通信手段を用いて操作系209の操作状態の検知を行い、撮影モード、プレイバックモード等のモードを判定して、モード毎の処理を行うように構成されている。

#### 【0008】

また、メインCPU245は、サブCPU201を介して操作系209の操作状態や記憶メディア271の着脱状態の監視を行っている。メインCPU245は、操作系209により電源OFFに操作されると、記憶メディア271が装着されているときには、記憶メディア271のファイルシステム等の情報をROM207に待避させておく処理や、電源OFFのための処理を行い、処理が終了するとサブCPU201に対して電源OFF処理終了を通知する。

#### 【0009】

サブCPU201は、メインCPU245から電源OFF処理終了が通知されるとシステムの電源供給を停止させる。サブCPU201は、電源OFF状態においても操作系209の操作状態や記憶メディア271の着脱状態の履歴をとっており、操作系209により電源ONに操作されると、電源制御部281を介して電源をONにする。これにより、メインCPU245に電源が供給されて起動する。メインCPU245は、電源OFF状態において記憶メディア271の着脱が行われなかった場合には、ROM207に待避させておいた記憶メディア271のファイルシステム等の情報を読み出し、記憶メディア271を初期化する時間の短縮を図っている。勿論、記憶メディア271の着脱が行われていた場合には、記憶メディア271の初期化を行っている。

#### 【0010】

他方、上述したようなメインCPU及びサブCPUを備えた機器においてサブCPUによる制御に関する技術が提案されている（例えば、特許文献1参照）。

#### 【特許文献1】特開2002-237977号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0011】

しかしながら、上記従来例に示したような、常時電源が供給されている第一のCPU（メインCPU）を搭載して記憶メディアの着脱状態を常に監視している構成の携帯機器に

10

20

30

40

50

おいては、機器全体を管理する第一のCPU以外に別の第二のCPU(サブCPU)を搭載しなければならない。そのため、部品点数が増加すると共に高価になってしまうという問題がある。

#### 【0012】

また、近年の携帯機器は、小型化されてきているため、携帯機器に搭載できるデバイスの実装面積も減少してきている。そのため、小型化された携帯機器においては、第一のCPUに加えて第二のCPUを搭載するための実装面積を確保するのが難しくなっているという問題がある。

#### 【0013】

また、近年、消費電力の少ない省電力CPUが開発されてきているが、それでも省電力CPUを駆動するために必要な消費電力はRTC等の省電力なデバイスの消費電力よりが多い。そのため、省電力CPUを搭載した携帯機器において、電源OFF状態において常に省電力CPUを駆動しておくと、常にCPUを駆動していない機器と比べると消費電力が多くなってしまうという問題がある。

10

#### 【0014】

しかしながら、電源OFF状態において記憶メディアの着脱状態の監視をやめてしまうと、起動時に毎回、記憶メディアの情報を取得して初期化を行わなければならないので、起動時間が長くなってしまう。一般に記憶メディアの容量が増加するに従って初期化に費やされる時間は長くなっていくが、近年では記憶メディアの容量の増加が著しいので、起動時間が年々長くなっているという問題がある。

20

#### 【0015】

本発明の目的は、複数のCPUを搭載することを不要とし、起動時間の短縮及び消費電力の低減を可能とした携帯機器及びその制御方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0016】

上述の目的を達成するために、本発明の携帯機器は、機器全体の制御を司るCPUと、情報を記憶する記憶メディアが着脱可能な接続手段を備えた携帯機器において、前記CPUの動作状態に関わらず、前記接続手段に対する前記記憶メディアの着脱状態を監視する監視回路と、前記監視回路による前記記憶メディアの着脱状態の監視に基づく監視結果を記憶する監視結果記憶手段と、前記CPUが起動処理を行う際に、前記監視結果記憶手段に記憶されている前記監視結果に前記CPUからアクセス可能とする通信手段とを備え、前記監視回路は、前記記憶メディアが前記接続手段から取り外されたことを検知した後は前記記憶メディアの着脱状態の監視を停止することを特徴とする。

30

#### 【0017】

上述の目的を達成するために、本発明の制御方法は、機器全体の制御を司るCPUと、情報を記憶する記憶メディアが着脱可能な接続手段を備えた携帯機器の制御方法において、前記CPUの動作状態に関わらず、前記接続手段に対する前記記憶メディアの着脱状態を監視回路により監視する監視工程と、前記監視工程による前記記憶メディアの着脱状態の監視に基づく監視結果を監視結果記憶手段に記憶する監視結果記憶工程と、前記CPUが起動処理を行う際に、前記監視結果記憶手段に記憶されている前記監視結果に前記CPUから通信手段によりアクセス可能とする通信工程とを備え、前記監視工程では、前記記憶メディアが前記接続手段から取り外されたことを検知した後は前記監視回路による前記記憶メディアの着脱状態の監視を停止することを特徴とする。

40

#### 【0019】

更に、本発明は、前記監視回路が、前記接続手段を介して入力される信号が所定レベルとなった場合、或いは、前記接続手段に付設したスイッチの作動に伴い前記接続手段を介して入力される信号が所定レベルとなった場合、或いは、前記接続手段に付設したメディア収納蓋の開放に伴い前記接続手段を介して入力される信号が所定レベルとなった場合に、前記接続手段に対する前記記憶メディアの着脱を検出する構成としてもよい。

#### 【0020】

50

更に、本発明は、前記携帯機器の電源がオフ状態でも、前記監視回路及び前記監視結果記憶手段に電源を供給するように制御する電源制御手段を備える構成としてもよい。

#### 【発明の効果】

##### 【0021】

本発明によれば、C P Uの動作状態に関わらず、携帯機器の接続手段に対する記憶メディアの着脱状態を監視し、記憶メディアの着脱状態の監視に基づく監視結果を記憶し、C P Uが起動処理を行う際に監視結果記憶手段に記憶されている監視結果にC P Uからアクセス可能とする。更に、監視回路は記憶メディアが接続手段から取り外されたことを検知した後は記憶メディアの着脱状態の監視を停止する。これにより、少ない消費電力で記憶メディアの着脱状態を監視することが可能となる。また、従来のように携帯機器全体を管理する第一のC P U以外に第二のC P Uを携帯機器に搭載することが不要となり、価格の低減が可能となる。

10

##### 【0022】

また、C P Uが起動処理を行うときに、記憶メディアの着脱状態の監視結果を通信手段を介して監視結果記憶手段から読み出すことにより、記憶メディアを初期化せずに起動できるので、起動時間を短縮することができる。

##### 【0023】

また、C P Uの動作状態に関わらず、換言すれば携帯機器が電源オフ状態でも、監視回路により記憶メディアの着脱状態を監視するので、少ない消費電力で記憶メディアの着脱状態監視を行うことができる。

20

#### 【発明を実施するための最良の形態】

##### 【0024】

以下、本発明の実施の形態を図面に基づき説明する。

##### 【0025】

###### [第1の実施の形態]

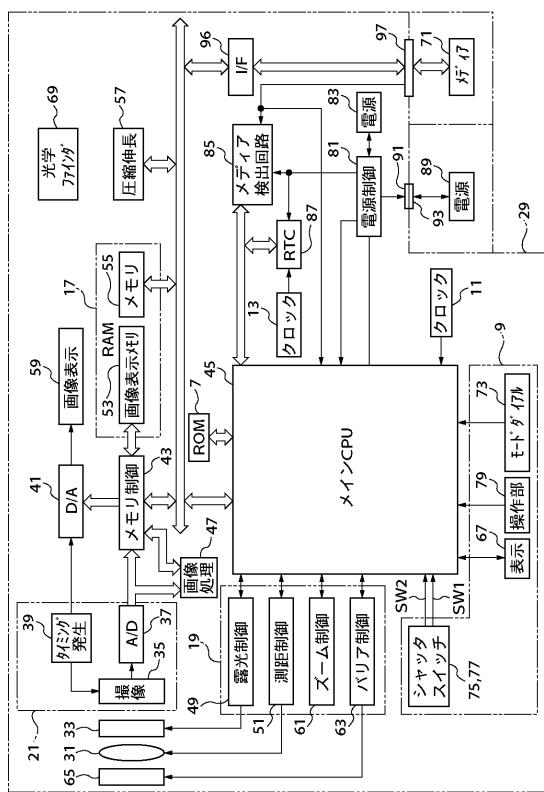

図1は、本発明の第1の実施の形態に係る携帯機器としてのデジタルカメラの構成を示すブロック図である。

##### 【0026】

図1において、デジタルカメラは、カメラ本体29の各部に、撮影レンズ31、シャッタ33、撮像素子35、メインC P U45、光学ファインダ69、メディア検出回路85等を備えており、記憶メディア71が着脱可能に構成されている。

30

##### 【0027】

撮影レンズ31は、被写体の光学像を取り込む。バリア65は、撮影レンズ31を含む撮像部を覆うことにより撮像部の汚れや破損を防止する保護機構である。シャッタ33は、絞り機能を備える。撮像素子35は、光学像を電気信号に変換する。A / D変換器37は、撮像素子35から出力されるアナログ信号をデジタル信号に変換する。タイミング発生回路39は、撮像素子35、A / D変換器37、D / A変換器41にそれぞれクロック信号や制御信号を供給するものであり、メモリ制御回路43及びメインC P U45により制御される。

##### 【0028】

40

画像処理回路47は、A / D変換器37から出力される画像データ或いはメモリ制御回路43から出力される画像データに対して所定の画素補間処理や色変換処理を行うと共に、撮像された画像データを用いて所定の演算処理を行う。メインC P U45は、画像処理回路47で得られた演算結果に基づいて露光制御部49、測距制御部51に対してA F(オートフォーカス)処理、A E(自動露出)処理、E F(フラッシュプリ発光)処理を行う。更に、画像処理回路47は、所定の演算処理の結果に基づいてA W B(オートホワイトバランス)処理も行う。

##### 【0029】

メモリ制御回路43は、A / D変換器37、タイミング発生回路39、画像処理回路47、画像表示メモリ53、D / A変換器41、メモリ55、圧縮・伸長回路57をそれぞ

50

れ制御する。画像表示メモリ53とメモリ55は、同じRAM17で構成されるが、RAM17の所定領域を画像表示メモリ53、RAM17の別の所定領域をメモリ55とする。A/D変換器37でA/D変換された画像データが、画像処理回路47及びメモリ制御回路43を介して或いは直接メモリ制御回路43を介して、画像表示メモリ53或いはメモリ55に書き込まれる。

#### 【0030】

画像表示メモリ53に書き込まれた表示用の画像データは、D/A変換器41を介してLCD等からなる画像表示部59により表示される。撮像された画像データを画像表示部59により逐次表示すれば、電子ファインダ機能を実現することが可能である。画像表示部59は、メインCPU45の指示により任意に表示をON/OFFすることが可能であり、表示をOFFにした場合にはカメラ本体29の電力消費を大幅に低減することができる。10

#### 【0031】

メモリ55は、撮像された静止画像や動画像を格納するためのメモリであり、所定枚数の静止画像や所定時間の動画像を格納するのに十分な記憶容量を備えている。これにより、複数枚の静止画像を連続して撮影する連写撮影やパノラマ撮影の場合にも、高速且つ大量の画像データの書き込みをメモリ55に対して行うことが可能となる。また、メモリ55は、メインCPU45の作業領域としても使用することが可能である。圧縮・伸長回路57は、画像データを圧縮／伸長する回路であり、メモリ55に格納された画像データを読み込んで圧縮処理或いは伸長処理を行い、処理が終了した画像データがメモリ55に書き込まれる。20

#### 【0032】

露光制御部49は、シャッタ33を制御する。測距制御部51は、撮影レンズ31のフォーカシングを制御する。ズーム制御部61は、撮影レンズ31のズーミングを制御する。バリア制御部63は、バリア65の動作を制御する。撮像された画像データを画像処理回路47により演算した結果に基づき、メインCPU45が露光制御部49、測距制御部51に対して制御を行う。

#### 【0033】

メインCPU45は、デジタルカメラの制御を司る中央処理装置であり、電源89或いはバックアップ用電源83から電源制御部81を介して各部に供給する電源の制御、操作部79における操作キーの入力の検出等を行い、操作キーの入力に基づいてデジタルカメラ各部の動作を制御する。また、メインCPU45は、ROM7に格納されたプログラムに基づいて図9のフローチャートに示す処理を実行する。30

#### 【0034】

表示部67は、メインCPU45におけるプログラムの実行に応じて、文字、画像、音声等を用いてデジタルカメラの動作状態やメッセージ等を表示する。表示部67は、カメラ本体29の操作部79近辺の視認し易い位置に単数或いは複数個所設置されており、例えばLCD、LED、発音素子等の組み合わせにより構成されている。また、表示部67は、その一部の機能が光学ファインダ69内に設置されている。

#### 【0035】

表示部67の表示内容のうち、LCD等に表示するものとしては、シングルショット／連写撮影表示、セルフタイマ表示、圧縮率表示、記録画素数表示、記録枚数表示、残撮影可能枚数表示、シャッタスピード表示、絞り値表示、露出補正表示、フラッシュ表示、赤目緩和表示、マクロ撮影表示、ブザー設定表示、時計用電池残量表示、電池残量表示、エラー表示、複数桁の数字による情報表示、記憶メディア71の着脱状態表示、通信I/F動作表示、日付・時刻表示等がある。また、表示部67の表示内容のうち、光学ファインダ69内に表示するものとしては、合焦表示、手振れ警告表示、フラッシュ充電表示、シャッタスピード表示、絞り値表示、露出補正表示等がある。40

#### 【0036】

モードダイヤルスイッチ73、シャッタスイッチ75、77及び操作部79は、カメラ50

本体 29に対する各種の指示を入力するためのものであり、スイッチ、ダイヤル、タッチパネル、視線検知によるポインティング、音声認識機構等の単数或いは複数の組み合わせにより構成される。

#### 【0037】

モードダイヤルスイッチ 73は、電源オフ、自動撮影モード、撮影モード、パノラマ撮影モード、再生モード、マルチ画面再生・消去モード、PC接続モード等の各機能モードを切り替え、設定することができる。

#### 【0038】

シャッタースイッチ SW1・75は、不図示のシャッタボタンの操作途中でONとなり、AF処理、AE処理、AWB処理、EF処理等の動作開始を指示する。シャッタースイッチ SW2・77は、不図示のシャッタボタンの操作完了でONとなり、撮像素子35から読み出した信号をA/D変換器37、メモリ制御回路43を介してメモリ55に画像データとして書き込む露光処理、画像処理回路47やメモリ制御回路43における演算を用いた現像処理、メモリ55から画像データを読み出し、圧縮・伸長回路57で圧縮を行い、記憶メディア71に画像データを書き込む記録処理、という一連の処理の動作開始を指示する。

10

#### 【0039】

操作部79は、メニューボタン、セットボタン、マクロボタン、マルチ画面再生改ページボタン、フラッシュ設定ボタン、単写/連写/セルフタイマ切り替えボタン、メニュー移動+（プラス）ボタン、メニュー移動-（マイナス）ボタン、再生画像移動+（プラス）ボタン、再生画像-（マイナス）ボタン、撮影画質選択ボタン、露出補正ボタン、日付/時間設定ボタン等を備えている。

20

#### 【0040】

電源制御部81は、電池検出回路、DC-DCコンバータ、通電するブロックを切り替えるスイッチ回路等から構成されており、メインCPU45の制御に基づいて、必要な電圧を必要な期間だけ各部へ供給する。図1においては、メインCPU45、メディア検出回路85とRTC87に電源を供給するラインだけを図示しているが、勿論、他の各部にも電源を供給している。

#### 【0041】

バックアップ用電源83は、コイン電池やスパコン等から構成されており、電源89からの電源供給がない時に常時電源を供給しなくてはならないメディア検出回路85とRTC87に電源制御部81を介して電源を供給する。バックアップ用電源83が2次電池である場合には、電源89からの電源が供給されているときには、バックアップ用電源83で充電を行うこともある。コネクタ91、93は、カメラ本体29と電源89を接続する。電源89は、アルカリ電池やリチウム電池等の1次電池、NiCd電池やNiMH電池やLi電池等の2次電池、ACアダプタ等から構成される。

30

#### 【0042】

インターフェース96は、メモリカードやハードディスク等の記憶メディア71とのインターフェースを司る。コネクタ97は、カメラ本体29と記憶メディア71を接続する。尚、本実施の形態では、カメラ本体29が、記憶メディア71を取り付けるインターフェース及びコネクタを1系統備える構成としているが、勿論、記憶メディアを取り付けるインターフェース及びコネクタを単数或いは複数の何れの系統数を備える構成としても構わない。また、異なる規格のインターフェース及びコネクタとしては、PCMCIA(Personal Computer Memory Card International Association)カードやCF(コンパクトフラッシュ(登録商標))カード等の規格に準拠したものを用いて構成して構わない。

40

#### 【0043】

光学ファインダ69は、画像表示部59による電子ファインダ機能を使用することなしに、該光学ファインダ69のみを用いて撮影を行うことが可能である。光学ファインダ69は、表示部67の一部の機能、例えば、合焦表示、手振れ警告表示、フラッシュ充電表

50

示、シャッタースピード表示、絞り値表示、露出補正表示等を行うことが可能である。

#### 【0044】

R T C (Real Time Clock) 8 7 は、デジタルカメラ内部の時刻を管理する時刻管理手段であり、カメラ本体 2 9 が電源オフ状態でも、常に電源 8 9 またはバックアップ用電源 8 3 から電源制御部 8 1 を介して電源が供給されるように構成されている。メイン C P U 4 5 は、シリアル通信を介して R T C 8 7 から時刻を読み出すことが可能である。R T C 8 7 には、R T C 8 7 を動作させるためのクロックを出力するクロック発振器 1 3 が接続されている。R T C 8 7 は、クロック発振器 1 3 のクロックを基準に時刻管理を行う。メイン C P U 4 5 には、比較的高周波なクロックを出力するクロック発振器 1 1 が接続されている。クロック発振器 1 3 から出力されるクロックは、クロック発振器 1 1 から出力されるクロックよりも低い周波数に設定されている。10

#### 【0045】

メディア検出回路 8 5 には、コネクタ 9 7 に対する記憶メディア 7 1 の着脱状態を示すメディア検出信号がコネクタ 9 7 を介して接続（入力）されている。メディア検出回路 8 5 は、メイン C P U 4 5 の動作状態に関わらず、メディア検出信号に基づき記憶メディア 7 1 の着脱状態を検出する。メディア検出信号は、メイン C P U 4 5 にも接続（入力）されている。メディア検出回路 8 5 は、R T C 8 7 と同様にカメラ本体 2 9 が電源オフ状態でも常に電源制御部 8 1 から電源が供給されるように構成されている。メイン C P U 4 5 からシリアル通信を介してメディア検出回路 8 5 にアクセスを行うことで、記憶メディア 7 1 の着脱状態を認識できるように構成されている。20

#### 【0046】

尚、図 1 の符号 9 で示す線で囲んだブロックは操作系を示し、符号 1 7 で示す線で囲んだブロックは R A M を示し、符号 1 9 で示す線で囲んだブロックは撮像部（撮影レンズ 3 1、シャッタ 3 3、バリア 6 5）の制御系を示し、符号 2 1 で示す線で囲んだブロックは撮像部（像素子 3 5）の信号処理系を示す。

#### 【0047】

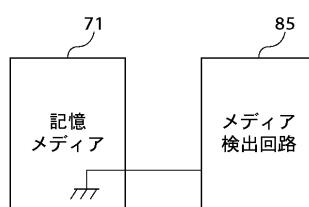

次に、デジタルカメラのメディア検出回路 8 5 に対するメディア検出信号の接続（入力）形態について図 2 乃至図 6 を参照しながら説明する。

#### 【0048】

図 2 に示すように、デジタルカメラのコネクタ（不図示）に記憶メディア 7 1 が装着されると、メディア検出回路 8 5 に接続されるメディア検出信号が L o w レベルになる構成となっている。30

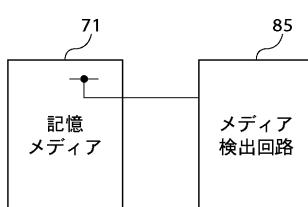

#### 【0049】

また、図 3 に示すように、デジタルカメラのコネクタ（不図示）に記憶メディア 7 1 が装着されると、メディア検出回路 8 5 に接続されるメディア検出信号が H i g h レベルになる構成としてもよい。

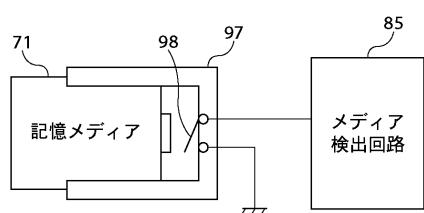

#### 【0050】

また、図 4 に示すように、デジタルカメラのコネクタ 9 7 にスイッチ 9 8 を配設しておき、コネクタ 9 7 に記憶メディア 7 1 が装着されると、記憶メディア 7 1 に押圧されたスイッチ 9 8 が作動することで、メディア検出回路 8 5 に接続されるメディア検出信号が L o w レベルになる構成としてもよい。40

#### 【0051】

また、図 5 に示すように、デジタルカメラのコネクタ 9 7 にスイッチ 9 8 を配設しておき、コネクタ 9 7 に記憶メディア 7 1 が装着されると、記憶メディア 7 1 に押圧されたスイッチ 9 8 が作動することで、メディア検出回路 8 5 に接続されるメディア検出信号が H i g h レベルになる構成としてもよい。

#### 【0052】

尚、図 4 と図 5 では、スイッチ 9 8 は通常メカ的に記憶メディア 7 1 に接触しておらず、コネクタ 9 7 に記憶メディア 7 1 が装着されると、スイッチ 9 8 がメカ的に記憶メディア 7 1 に接触するような構成としている。これに対し、スイッチ 9 8 が通常メカ的に記憶50

メディア71に接触しており、コネクタ97に記憶メディア71が装着されると、スイッチ98がメカ的に記憶メディア71に接触しなくなる構成としもよい。

#### 【0053】

また、図6に示すように、デジタルカメラのコネクタ(不図示)に記憶メディア71を収納するためのメディア収納蓋70を配設しておき、メディア収納蓋70を開けるとLowレベルまたはHighレベルになる蓋検出信号をメディア検出信号としてメディア検出回路85に接続する構成としてもよい。

#### 【0054】

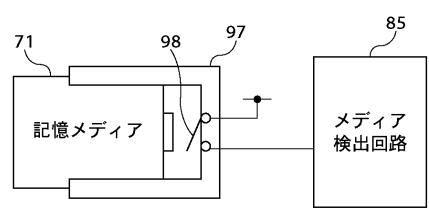

次に、メディア検出信号の接続(入力)形態が上記図2の場合におけるメディア検出回路85の構成について図7を参照しながら説明する。

10

#### 【0055】

図7は、メディア検出回路85の構成を示すブロック図である。

#### 【0056】

図7において、メディア検出回路85は、スイッチ99、スイッチ107、バッファ103、コントローラ108、コントローラ109、クロック供給源111、タイマ113、レジスタ115、レジスタ116、バスインターフェース117、内部バス119を備えている。

#### 【0057】

記憶メディア71がコネクタ97に装着されると、記憶メディア71が装着されたことを示すメディア検出信号がメディア検出回路85に入力される。メディア検出信号は、記憶メディア71がコネクタ97に装着されるとLowレベルとなり、記憶メディア71が装着されたことを示す。メディア検出信号が供給される信号線には、抵抗101が接続されており、スイッチ99の制御によってプルアップのオン／オフができるように構成されている。また、メディア検出信号が供給される信号線には、抵抗105が接続されており、スイッチ107の制御によってプルダウンのオン／オフができるように構成されている。

20

#### 【0058】

メディア検出信号は、バッファ103を介してコントローラ108に入力される。尚、メディア検出信号は、記憶メディア71がコネクタ97に装着されたときに起こるチャタリングを除去するためのチャタリング除去回路(不図示)を介してバッファ103に入力された後、コントローラ108に入力される構成でも構わない。スイッチ99とスイッチ107は、コントローラ108によって制御されるが、両方が同時にオンされることも同時にオフされることもなく、必ずどちらか一方がオン状態で他方がオフ状態になるように制御される。

30

#### 【0059】

コントローラ108は、コントローラ109からの制御信号により、スイッチ99とスイッチ107を制御し、記憶メディア71の着脱状態を検出してコントローラ109へ信号を渡す、記憶メディア検出用のコントローラである。コントローラ109は、メディア検出回路85全体の制御を司るものであり、コントローラ108に記憶メディア71の着脱状態を検出させる制御信号を出力し、コントローラ108から記憶メディア71の着脱状態検出結果を示す信号を受け取り、レジスタ115に着脱状態検出結果を記憶させる。また、コントローラ109は、プログラムに基づいて図10～図13のフローチャートに示す処理を実行する。

40

#### 【0060】

タイマ113は、コントローラ109がコントローラ108へ記憶メディア71の着脱状態を検出させる制御信号を出力するためのタイミングを計測する。タイマ113は、コントローラ109からの信号により計測動作の開始／停止が制御される。

#### 【0061】

レジスタ115は、上述した記憶メディア71の着脱状態検出結果を記憶する。レジスタ115は、メインCPU45等の外部デバイスからバスインターフェース117を介して

50

アクセス可能に構成されている。これにより、メインC P U 4 5等の外部デバイスはレジスタ115を読み出すことにより記憶メディア71の着脱状態を認識することが可能である。また、メインC P U 4 5は、レジスタ115に記憶された着脱状態検出結果に基づいて起動処理を行う。

#### 【0062】

レジスタ116は、メディア検出回路85全体の設定を記憶する。コントローラ109は、レジスタ116に記憶されている設定に従ってメディア検出回路85を制御する。レジスタ116は、メインC P U 4 5等の外部デバイスからバスインターフェース117を介して読み出し/書き込み可能に構成されている。これにより、メインC P U 4 5等の外部デバイスからメディア検出回路85を制御することが可能である。

10

#### 【0063】

クロック供給源111は、メディア検出回路85を動作させるためのクロックを供給する。尚、クロック供給源111は、メディア検出回路85の内部ではなく外部に配設する構成としてもよい。タイマ113は、クロック供給源111から供給されるクロックを基準に動作する。内部バス119は、タイマ113、レジスタ115、レジスタ116とバスインターフェース117をメディア検出回路85内部で接続する。

#### 【0064】

以上説明したように、本実施の形態によれば、デジタルカメラは、デジタルカメラの制御を司るメインC P U 4 5と、コントローラ109、レジスタ115、バスインターフェース117を有するメディア検出回路85と、時刻管理を行うR T C 8 7と、記憶メディア71が着脱されるコネクタ97等を備える。メディア検出回路85は、メインC P U 4 5の動作状態に関わらず、コネクタ97に対する記憶メディア71の着脱状態を監視し、記憶メディア71の着脱状態検出結果をレジスタ115に記憶する。メインC P U 4 5が起動処理を行う際に、レジスタ115内の着脱状態検出結果をメインC P U 4 5からバスインターフェース117を介してアクセス可能とする。

20

#### 【0065】

これにより、従来のようにデジタルカメラ全体を管理する第一のC P U(メインC P U)以外に第二のC P Uをデジタルカメラに搭載することが不要となり、また、コントローラやレジスタからなるメディア検出回路85は第二のC P Uをデジタルカメラに搭載するよりも安価に構成できるので、価格を低減することが可能となる。

30

#### 【0066】

また、メインC P U 4 5が起動するときに、記憶メディア71の着脱状態検出結果をバスインターフェース117を介してレジスタ115から読み出すことにより、記憶メディア71を初期化せずに起動できるので、起動時間を短縮することができる。

#### 【0067】

また、メインC P U 4 5の動作状態に関わらず、換言すればカメラ本体29が電源オフ状態でも、電源制御部81を介して電源が供給されているメディア検出回路85により記憶メディア71の着脱状態を監視するので、少ない消費電力で記憶メディア着脱状態監視を行うことができる。

#### 【0068】

40

##### [第2の実施の形態]

本発明の第2の実施の形態は、上述した第1の実施の形態に対して、R T C 8 7とメディア検出回路85を一体化し1つのデバイスとして構成した点において相違する。本実施の形態のその他の要素は、上述した第1の実施の形態(図1)の対応するものと同一なので、説明を省略する。

#### 【0069】

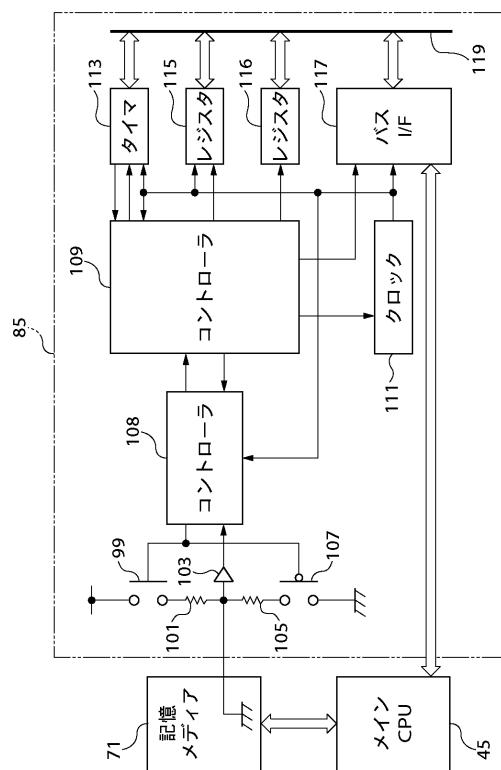

まず、R T C 8 7とメディア検出回路85を1つのデバイスとして構成する説明を行う前に、R T C 8 7の構成を図8を用いて説明する。

#### 【0070】

図8は、R T C 8 7の構成を示すブロック図である。

50

**【0071】**

図8において、RTC87は、コントローラ121、タイマ123、レジスタ125、バスインターフェース127、内部バス129、クロック供給部131を備えている。

**【0072】**

RTC87外部のクロック発振器13から、RTC87が動作するための基準信号となるクロックがクロック供給部131に入力される。クロック供給部131は、PLL(Phase Lock Loop)を内蔵し、入力されたクロックの遅延などができるように構成されており、コントローラ121、タイマ123、レジスタ125、バスインターフェース127の動作に必要なクロックを供給している。コントローラ121は、RTC87全体の制御を司るものであり、レジスタ125に記憶されている設定値に基づいてRTC87全体の制御を決定している。10

**【0073】**

タイマ123は、一定の時間または任意の時間を計測して割り込みを発生させる機能や、時間・分・秒を計測しその計測値をレジスタ125に記憶させる機能を有する。レジスタ125は、RTC87の動作の設定値や、時間・分・秒の計測値を記憶するものであり、メインCPU45等の外部デバイスからバスインターフェース127を介してアクセス可能に構成されている。これにより、メインCPU45等の外部デバイスは、時間の認識やRTC87の制御を行うことが可能である。

**【0074】**

図7のメディア検出回路85と図8のRTC87を比較すると、メディア検出回路85は、RTC87と同様に、コントローラ、タイマ、レジスタ、バスインターフェースを構成要素として内蔵している。従って、RTC87のコントローラ121をメディア検出回路85のコントローラ109に、RTC87のレジスタ125をメディア検出回路85のレジスタ116に、RTC87のタイマ123をメディア検出回路85のタイマ113に組み込み、バスインターフェースは共通にする。これにより、RTC87をメディア検出回路85に組み込むことができ、RTC87とメディア検出回路85を1つのデバイスで構成することができる。20

**【0075】**

以上説明したように、本実施の形態によれば、RTC87とメディア検出回路85を1つのデバイスとして構成することにより、コントローラ、レジスタ、タイマ等を共通化できるので、部品点数や実装面積を増やすずにRTC機能と記憶メディア検出機能をデジタルカメラに搭載することができる。また、メインCPU45は、RTC87とメディア検出回路85に対し別々にアクセスすることが不要となるので、制御を簡易化することができる。30

**【0076】****[第3の実施の形態]**

本発明の第3の実施の形態は、上述した第1及び第2の実施の形態に対して、メインCPU45が図9に示すように動作する点において相違する。本実施の形態のその他の要素は、上述した第1の実施の形態(図1)の対応するものと同一なので、説明を省略する。

**【0077】**

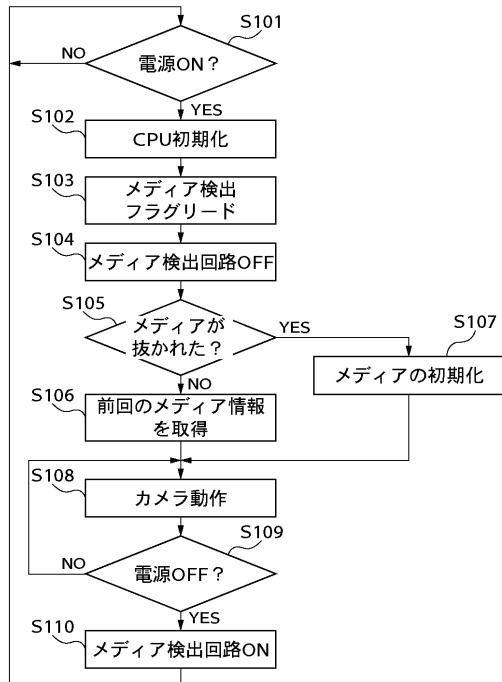

図9は、メインCPU45の動作を示すフローチャートである。40

**【0078】**

図9において、メインCPU45は、デジタルカメラの起動を示す電源ONの検出の有無を判定し(ステップS101)、電源ONを検出した場合は、ステップS102に移行し、電源ONを検出しない場合は、電源ON検出まで待機する。メインCPU45は、電源ONを検出すると、メインCPU45が動作できる状態になるための初期設定を行った後(ステップS102)、メディア検出回路85と通信を行い、記憶メディア71の着脱状態検出結果を示すフラグであるメディア検出フラグをメディア検出回路85のレジスタ115から読み出す(ステップS103)。

**【0079】**

50

電源ON状態ではメインCPU45で記憶メディア71の着脱状態を監視可能であり、メディア検出回路85を動作させておく必要がないので、メインCPU45は、メディア検出回路85の動作を停止する(ステップS104)。次に、メインCPU45は、上記ステップS103で読み出したメディア検出フラグから、記憶メディア71がコネクタ97から抜かれたか否かを判断する(ステップS105)。記憶メディア71がコネクタ97から抜かれていないと判断した場合は、ステップS106に移行し、記憶メディア71がコネクタ97から抜かれたと判断した場合は、ステップS107に移行する。

#### 【0080】

記憶メディア71がコネクタ97から抜かれた場合、メインCPU45は、記憶メディア71の初期化を行うと共に、初期化した記憶メディア71からファイル管理情報を読み出しROM7に記憶した後(ステップS107)、ステップS108に移行する。他方、記憶メディア71がコネクタ97から抜かれていないと判断した場合は、記憶メディア71の前回のファイル管理情報はROM7に記憶されているので、メインCPU45は、ROM7から記憶メディア71の前回のファイル管理情報を読み出した後(ステップS106)、ステップS108に移行する。

#### 【0081】

次に、メインCPU45は、ユーザの操作に応じた通常のカメラ動作を行う(ステップS108)。本処理には直接関係ないためカメラ動作の説明は省略する。次に、メインCPU45は、電源OFFの検出の有無を判定し(ステップS109)、電源OFFを検出した場合は、メディア検出回路85を起動し、電源OFF処理を行う(ステップS110)。電源ONを検出した場合は、カメラ動作を続行するので、ステップS108に移行する。

#### 【0082】

上記制御をまとめると、メインCPU45が起動処理を行う際に、メディア検出フラグの内容から、記憶メディア71がコネクタ97から抜かれていないと判断した場合は、ROM7に記憶されているファイル管理情報を読み出して起動処理を行い、記憶メディア71がコネクタ97から抜かれていると判断した場合は、記憶メディア71からファイル管理情報を読み出して起動処理を行う。

#### 【0083】

以上説明したように、本実施の形態によれば、記憶メディア71がコネクタ97から抜かれなかった場合には、記憶メディア71よりもアクセス速度の速いROM7に記憶されているファイル管理情報を使用するので、起動時に毎回、記憶メディア71からファイル管理情報を読み出すことが不要となり、起動時間を短縮することができる。

#### 【0084】

##### [第4の実施の形態]

本発明の第4の実施の形態は、上述した第1乃至第3の実施の形態に対して、図10に示すように、メディア検出回路85が記憶メディア71の着脱状態を常に監視するのではなく、監視を行ったら所定の待ち時間を経て再び監視を行うという点において相違する。本実施の形態のその他の要素は、上述した第1の実施の形態(図1)の対応するものと同一なので、説明を省略する。

#### 【0085】

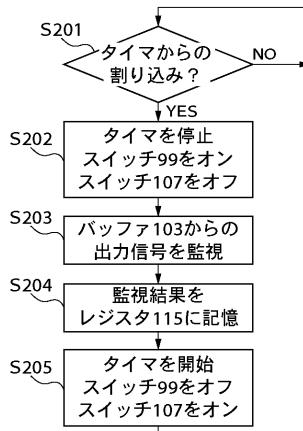

図10は、メディア検出回路85の動作を示すフローチャートである。

#### 【0086】

図10において、メディア検出回路85のタイマ113は、所定時間(例えば0.1msec)毎に割り込みを発生する。まず、コントローラ109は、タイマ113から記憶メディア71の着脱状態を監視するための時間が経過したことを知らせる割り込みを待つ(ステップS201)。タイマ113からの割り込みが発生すると、コントローラ109は、一旦タイマ113を停止させ、スイッチ99をオンとし、スイッチ107をオフとする(ステップS202)。

#### 【0087】

10

20

30

40

50

次に、コントローラ109は、バッファ103から出力される、記憶メディア71がコネクタ97に装着されているかを示すメディア検出信号を監視する（ステップS203）。メディア検出信号がLowレベルならば、記憶メディア71がコネクタ97に装着されていることを示しており、メディア検出信号が電源レベルならば、記憶メディア71がコネクタ97に装着されていないことを示している。

#### 【0088】

次に、コントローラ109は、ステップS203の監視で取得した記憶メディア71の監視結果（着脱状態検出結果）をレジスタ115に記憶する（ステップS204）。この後、コントローラ109は、停止させていたタイマ113の動作を再開させ、スイッチ99をオフとし、スイッチ107をオンとして（ステップS205）、ステップS201に移行する。

10

#### 【0089】

以上説明したように、本実施の形態によれば、メディア検出回路85が所定時間毎に記憶メディア71の着脱状態を監視するので、記憶メディア71の着脱状態を常時監視している場合に比べて消費電力を低減することができる。

#### 【0090】

##### [第5の実施の形態]

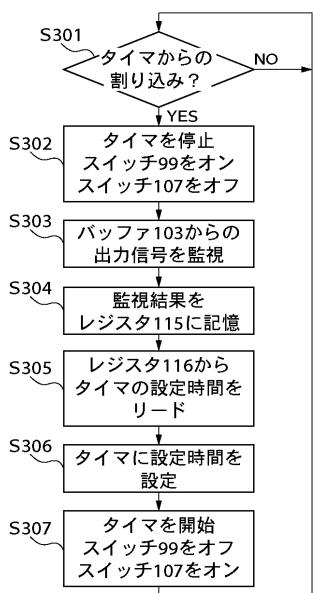

本発明の第5の実施の形態は、上述した第4の実施の形態に対して、図11に示すように、メディア検出回路85のタイマ113が割り込みを発生する時間を任意の時間に設定可能とし、タイマ113が割り込みを発生する設定時間を記憶する設定時間領域をレジスタ116に設けた点において相違する。本実施の形態のその他の要素は、上述した第1の実施の形態（図1）の対応するものと同一なので、説明を省略する。

20

#### 【0091】

図11は、メディア検出回路85の動作を示すフローチャートである。

#### 【0092】

図11において、メディア検出回路85のタイマ113は、レジスタ116の設定時間領域に記憶されている設定時間毎に割り込みを発生する。まず、コントローラ109は、タイマ113から記憶メディア71の着脱状態を監視するための時間が経過したことを知らせる割り込みを待つ（ステップS301）。タイマ113からの割り込みが発生すると、コントローラ109は、一旦タイマ113を停止させて、スイッチ99をオンとし、スイッチ107をオフとする（ステップS302）。

30

#### 【0093】

次に、コントローラ109は、バッファ103から出力される、記憶メディア71がコネクタ97に装着されているかを示すメディア検出信号を監視する（ステップS303）。次に、コントローラ109は、ステップS303の監視で取得した記憶メディア71の監視結果（着脱状態検出結果）をレジスタ115に記憶する（ステップS304）。次に、コントローラ109は、タイマ113に設定すべき設定時間をレジスタ116から読み出し（ステップS305）、設定時間をタイマ113に設定する（ステップS306）。この後、コントローラ109は、停止させていたタイマ113の動作を再開させ、スイッチ99をオフとし、スイッチ107をオンとして（ステップS307）、ステップS301に移行する。

40

#### 【0094】

メインCPU45は、メディア検出回路85のバスインターフェース117を介してレジスタ116にアクセスすることにより、タイマ113の割り込み発生時間を任意の時間に設定することができるので、メディア検出回路85が記憶メディア71の着脱状態を監視する時間を状況に応じて任意に設定できる。例えば、メインCPU45が停止するときに電源89の電圧が低くなっているときには、電源89を長持ちさせるためにメディア検出回路85が記憶メディア71の着脱状態を監視する時間を長くする、という設定が想定される。

#### 【0095】

以上説明したように、本実施の形態によれば、メディア検出回路 85 が記憶メディア 71 の着脱状態を監視する監視時間をメイン C P U 45 から設定可能とすることにより、電源 89 の電圧が低下した場合などの状況に応じて監視時間を適宜変更できるので、第 4 の実施の形態よりも更に消費電力を低減することができる。

#### 【0096】

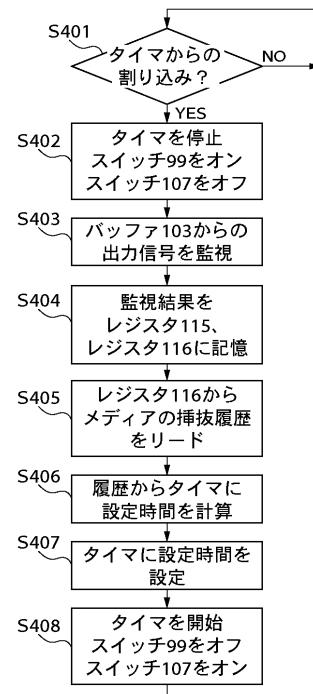

##### [ 第 6 の実施の形態 ]

本発明の第 6 の実施の形態は、上述した第 5 の実施の形態に対して、メディア検出回路 85 が記憶メディア 71 の着脱状態を監視する監視時間をメイン C P U 45 が設定するのではなく、記憶メディア 71 が着脱（挿抜）された着脱履歴をレジスタ 116 に記憶しておき、コントローラ 109 がレジスタ 116 の着脱履歴を基に上記監視時間を決定する点において相違する。本実施の形態のその他の要素は、上述した第 1 の実施の形態（図 1）の対応するものと同一なので、説明を省略する。10

#### 【0097】

図 12 は、メディア検出回路 85 の動作を示すフロー チャートである。

#### 【0098】

図 12において、メディア検出回路 85 のタイマ 113 は、レジスタ 116 に設定されている時間毎に割り込みを発生する。まず、コントローラ 109 は、タイマ 113 から記憶メディア 71 の着脱状態を監視するための時間が経過したことを知らせる割り込みを待つ（ステップ S401）。タイマ 113 からの割り込みが発生すると、コントローラ 109 は、一旦タイマ 113 を停止させて、スイッチ 99 をオンとし、スイッチ 107 をオフとする（ステップ S402）。20

#### 【0099】

次に、コントローラ 109 は、バッファ 103 から出力される、記憶メディア 71 がコネクタ 97 に装着されているかを示すメディア検出信号を監視する（ステップ S403）。次に、コントローラ 109 は、ステップ S303 の監視で取得した記憶メディア 71 の監視結果（着脱状態検出結果）をレジスタ 115 に記憶すると共に、監視結果を着脱履歴としてレジスタ 116 の着脱履歴領域に記憶する（ステップ S404）。次に、コントローラ 109 は、レジスタ 116 の着脱履歴領域から着脱履歴を読み出し（ステップ S405）、着脱履歴から、記憶メディア 71 が着脱された時間間隔の平均値やヒストグラム等の統計計算を行い、記憶メディア 71 の着脱を監視する時間間隔の最適値を計算する（ステップ S406）。30

#### 【0100】

次に、コントローラ 109 は、計算した記憶メディア 71 の着脱を監視する時間間隔の最適値をタイマ 113 に設定する（ステップ S407）。この後、コントローラ 109 は、停止させていたタイマ 113 の動作を再開させ、スイッチ 99 をオフとし、スイッチ 107 をオンとして（ステップ S307）、上記ステップ S301 に移行する。

#### 【0101】

以上説明したように、本実施の形態によれば、記憶メディア 71 が着脱された着脱履歴に基づいて、記憶メディア 71 の着脱状態を監視する時間を決定するので、記憶メディア 71 の着脱が頻繁に行われていないときは記憶メディア 71 の着脱を監視する回数が減少する結果、第 4 の実施の形態よりも更に消費電力を低減することができる。40

#### 【0102】

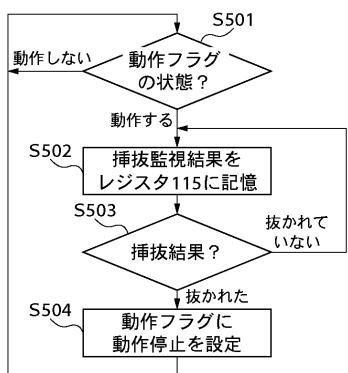

##### [ 第 7 の実施の形態 ]

本発明の第 7 の実施の形態は、上述した第 1 乃至第 6 の実施の形態に対して、メディア検出回路 85 が一度、記憶メディア 71 がコネクタ 97 から抜かれたことを検出した場合は、記憶メディア 71 の着脱状態の監視を停止する点において相違する。本実施の形態のその他の要素は、上述した第 1 の実施の形態（図 1）の対応するものと同一なので、説明を省略する。

#### 【0103】

図 13 は、メディア検出回路 85 の動作を示すフロー チャートである。

10

30

40

50

**【0104】**

図13において、メディア検出回路85のコントローラ109は、レジスタ115に装備されているメディア検出回路85を動作させたり停止させたりするための動作フラグを読み出し、動作フラグの状態を判定する(ステップS501)。動作フラグが停止を示している場合は、ステップS501に戻る。他方、動作フラグが動作を示している場合は、コントローラ109は、記憶メディア71の着脱状態を監視した結果である着脱監視結果(挿抜監視結果)をレジスタ115に記憶する(ステップS502)。

**【0105】**

次に、コントローラ109は、着脱監視結果(挿抜監視結果)を判定する(ステップS503)。記憶メディア71がコネクタ97から抜かれていないと判定した場合は、ステップS502へ移行する。他方、記憶メディア71がコネクタ97から抜かれたと判定した場合は、コントローラ109は、動作フラグを停止を示す状態に設定して(ステップS504)、ステップS501へ移行する。

10

**【0106】**

以上説明したように、本実施の形態によれば、記憶メディア71がコネクタ97から一度抜かれた後は、メディア検出回路85による記憶メディアの着脱状態の監視を停止するので、更に消費電力を低減することができる。

**【0107】****[他の実施の形態]**

上記第1乃至第7の実施の形態では、携帯機器としてデジタルカメラを例に挙げたが、これに限定されるものではなく、記憶メディアが着脱可能な形態を有する他の携帯機器にも適用することができる。

20

**【0108】**

上記第1の実施の形態では、メディア検出回路85において、記憶メディア71の着脱状態検出結果を記憶するレジスタ115と、メディア検出回路85の全体の設定を記憶するレジスタ116を別個に設ける構成とした。この変形例として、1つのレジスタに着脱状態検出結果を記憶する領域とメディア検出回路85の全体の設定を記憶する領域を設ける構成としてもよい。

**【0109】**

上記第4の実施の形態では、メディア検出回路85が所定の待ち時間において記憶メディア71の着脱状態を監視する構成とした。この変形例として、記憶メディア71の着脱状態を監視する複数の待ち時間に各々対応付けた複数段階の省電力モードを設け、ユーザが表示部67等に表示された複数段階の省電力モードの中から所望の省電力モードを選択すると、選択された省電力モードに対応した待ち時間において記憶メディア71の着脱状態を監視する構成としてもよい。

30

**【0110】**

上記第5の実施の形態では、メディア検出回路85のタイマ113が割り込みを発生する時間を任意の時間に設定可能とし、設定時間をレジスタ116に記憶する構成とした。この変形例として、タイマ113が割り込みを発生する複数の設定時間に各々対応付けた複数段階の省電力モードを設け、ユーザが表示部67等に表示された複数段階の省電力モードの中から所望の省電力モードを選択すると、選択された省電力モードに対応した設定時間をレジスタ116に記憶する構成としてもよい。

40

**【0111】**

本発明は、上述した実施の形態の機能を実現するソフトウェアのプログラム(図9～図13のフローチャート)をコンピュータ又はCPUに供給し、そのコンピュータ又はCPUが該供給されたプログラムを読出して実行することによって、達成することができる。

**【0112】**

この場合、上記プログラムは、該プログラムを記録した記憶媒体から直接供給されるか、又はインターネット、商用ネットワーク、若しくはローカルエリアネットワーク等に接続される不図示の他のコンピュータやデータベース等からダウンロードすることにより供

50

給される。

**【0113】**

上記プログラムの形態は、オブジェクトコード、インタプリタにより実行されるプログラムコード、OS（オペレーティングシステム）に供給されるスクリプトデータ等の形態から成ってもよい。

**【0114】**

また、本発明は、上述した実施の形態の機能を実現するソフトウェアのプログラムを記憶した記憶媒体をコンピュータ又はCPUに供給し、そのコンピュータ又はCPUが記憶媒体に記憶されたプログラムを読み出して実行することによっても、達成することができる。

10

**【0115】**

この場合、格納媒体から読み出されたプログラムコード自体が上述した各実施の形態の機能を実現すると共に、そのプログラムコードを記憶した記憶媒体は本発明を構成する。

**【0116】**

プログラムコードを記憶する記憶媒体としては、例えば、ROM、RAM、NV-RAM、フロッピー（登録商標）ディスク、ハードディスク、光ディスク（登録商標）、光磁気ディスク、CD-ROM、MO、CD-R、CD-RW、DVD-ROM、DVD-RAM、DVD-RW、DVD+RW、磁気テープ、不揮発性メモリカード等がある。

**【0117】**

上述した実施の形態の機能は、コンピュータから読み出されたプログラムコードを実行することによるばかりでなく、コンピュータ上で稼動するOS等がプログラムコードの指示に基づいて実際の処理の一部又は全部を行うことによっても実現することができる。

20

**【図面の簡単な説明】**

**【0118】**

【図1】本発明の第1の実施の形態に係る携帯機器としてのデジタルカメラの構成を示すプロック図である。

【図2】記憶メディアとメディア検出回路の構成例を示す概略図である。

【図3】記憶メディアとメディア検出回路の構成例を示す概略図である。

【図4】記憶メディアとメディア検出回路の構成例を示す概略図である。

【図5】記憶メディアとメディア検出回路の構成例を示す概略図である。

30

【図6】コネクタのメディア収納蓋とメディア検出回路の構成例を示す概略図である。

【図7】メディア検出回路の構成を示すプロック図である。

【図8】本発明の第2の実施の形態に係るRTCの構成を示すプロック図である。

【図9】本発明の第3の実施の形態に係るメインCPUの動作を示すフローチャートである。

【図10】本発明の第4の実施の形態に係るメディア検出回路の動作を示すフローチャートである。

【図11】本発明の第5の実施の形態に係るメディア検出回路の動作を示すフローチャートである。

【図12】本発明の第6の実施の形態に係るメディア検出回路の動作を示すフローチャートである。

40

【図13】本発明の第7の実施の形態に係るメディア検出回路の動作を示すフローチャートである。

【図14】従来例に係るデジタルカメラの構成を示すプロック図である。

**【符号の説明】**

**【0119】**

7 ROM（管理情報記憶手段に対応）

29 カメラ本体（携帯機器、撮像装置に対応）

45 メインCPU（CPUに対応）

71 記憶メディア

50

- 8 5 メディア検出回路（監視回路に対応）

8 7 RTC（時刻管理手段に対応）

9 7 コネクタ（接続手段に対応）

1 0 9 コントローラ（監視回路に対応）

1 1 5、1 1 6 レジスタ（監視結果記憶手段に対応）

1 1 7 バスインターフェース（通信手段に対応）

【図 1】

【図 2】

【図 3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

| (51)Int.Cl. |                  | F I     |        |

|-------------|------------------|---------|--------|

| H 0 4 N     | 5/232 (2006.01)  | H 0 4 N | 5/232  |

| H 0 4 N     | 5/907 (2006.01)  | H 0 4 N | 5/907  |

| H 0 4 N     | 101/00 (2006.01) | H 0 4 N | 101:00 |

(72)発明者 湖山 理

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 仲間 晃

(56)参考文献 特開2002-150230 (JP, A)

特開2004-007319 (JP, A)

特開2002-237977 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| H 0 4 N | 5 / 2 2 5   |

| G 0 6 F | 1 / 1 8     |

| G 0 6 F | 3 / 0 6     |

| G 0 6 K | 1 7 / 0 0   |

| H 0 4 M | 1 / 7 3     |

| H 0 4 N | 5 / 2 3 2   |

| H 0 4 N | 5 / 9 0 7   |

| H 0 4 N | 1 0 1 / 0 0 |